Designers-Guide to Spice and Spectre总结文档

spice和spectre软件使用和运放的仿真方法

斜坡上升 阶跃信号

激励

3.脉冲信号源 V1 N1 N2 PULSE(v1 v2 td tr tf pw per)

V1 N1 N2 PULSE(0 5 1p 1p 1p 5u 10u) 注:v1:值1

v2:值2 td:延迟时间 tr:上升时间 tf:下降时间 pw:脉冲宽度 per:周期

方波

激励

4.正弦信号源 V1 N1 N2 SIN(v0 va freq td θ Φ) V1 N1 N2 SIN(0 1 1) 注:v0:偏置值

基本语法

1. 不区分大小写(case insensitive) 2. 注释:* or $ 3. 数量级表示符号:

T

E12

G

E9

MEG

E6

K

E3

M

E-3

U

E-6

N

E-9

p

E-12

F

E-15

(关键不要搞错M和MEG) 4.赋值单位可以省略

仿真网表的五个主要组成部分

1.电路网表 2.激励 3.仿真分析语句 4.输出命令 5.模型库文件

添加模型时,添加此库文件,section选项只填上tt就可以了!

Hspice模型文件的结构(.lib)

**说明** .lib tt ……参数 .lib “路径/模型名.lib” mos .lib “路径/模型名.lib” bjt .lib “路径/模型名.lib” diode .endl tt ……(包括.lib ss,.lib sf,.lib fs,.lib ff等)

电路网表

包含的内容有器件连接关系、模型名、参 数值、(赋值)、并联个数、(初始值) 例: R1 N1 N2 R W=10u L=1u R2 N1 N2 10K C1 N1 N2 C W=10u L=1u C2 N1 N2 10p C3 N1 N2 10p IC=1

英语作文-集成电路设计师必备的实用工具与软件介绍

英语作文-集成电路设计师必备的实用工具与软件介绍Integrated circuit (IC) design is a sophisticated field that demands precise tools and software to facilitate efficient development. As an essential part of the semiconductor industry, IC designers rely on a variety of specialized tools throughout the design process. These tools encompass everything from initial concept and simulation to layout and verification. Here, we explore the indispensable tools and software that every IC designer should be familiar with.1. Electronic Design Automation (EDA) Tools:。

At the core of IC design are Electronic Design Automation tools. These software packages enable designers to create and analyze circuits efficiently. EDA tools typically include schematic capture, simulation, and layout functionalities. Cadence Design Systems' suite, including tools like Virtuoso for layout and Spectre for simulation, is widely used in the industry for its comprehensive capabilities. Mentor Graphics (now Siemens EDA) with tools such as Calibre for design verification and HyperLynx for signal integrity analysis also play crucial roles in ensuring design accuracy and reliability.2. SPICE Simulation:。

差分放大器设计第一讲_A_110202850

主讲教师池保勇主讲教师:池保勇李翔宇办公地点:清华大学微电子学研究所设计室(东主楼一楼)Email: chibylxc@;xiangyuli@电话:62795096 (O);62795094(O)助教:周波(模拟)俞波(数字)Email:zhoubo07@zhoubo07@mails tsinghua edu cnyu-b06@课程概况课程名:集成电路课程设计性质:限选课学分:3时间:大四第一学期对象:电子系各专业对象:电子系各专业学生学生有兴趣,有热情,有时间的有时间的同学同学目标:掌握集成电路设计方法培养对相关电路设计知识的综合运用能力模电、数电课程概况(续一)器件、工艺(大二大三)I 前续课与后续课(大二、大三)集成电路课程设计核心:(大四上)项目设计毕业设计集成电路设计实践(大四下研一)(大四下、研)课程概况(续二)教材:自编讲义参考书:(1)The art of analog layout,Alan Hastings,北京清华大学出版社,2004Designer’s(2)The Designer s Guide to Spice andSpectre ,Kenneth S.Kundert ,KluwerAcademic Publishers ,1995课程概况(续三)设计环境1.参考工艺:SMIC 180nm CMOS工艺2软件HSPICE CADENCE SYNOPSYS 2.软件:HSPICE,CADENCE,SYNOPSYS.3.上机地点:东主楼一楼微所EDA 机房或校园网内远程登录使用上机时间周每人4.上机时间:4~16周。

每人100小时(自由时间)5.上机指导:每周二、周四晚7:00~9:30课程概况(续四)课程考核主要分平时考核和设计报告两个部分z平时考核包括小实验和作业;z 课程项目设计报告;成绩分为不通过通过和优秀三档完成所有z成绩分为不通过、通过和优秀三档,完成所有要求的同学其成绩为通过,其中约15%的同学的成绩为优秀课程内容集成电路课程设计基础集成电路背景知识版图的基本概念CMOS 工艺中的元件版图设计规则(topological design rule topological design rule))(’rule’ for performance )版图设计准则u e o pe o a ce版图电路提取Full--Full custom 设计流程Cell Cell--based 设计流程————Cyclic ADC 项目项目设计设计Cyclic ADC 的设计课程内容续)课程内容(续一)集成电路课程设计基础Full Full--custom 设计流程原理图输入与电路网表导出HSPICE 电路仿真版图编辑设计规则检查(DRC )与电路网表比对(LVS )寄生参数提取和后仿真Cell--Cell based 设计流程项目设计————Cyclic ADC Cyclic ADC 的设计课程内容续)课程内容(续二)集成电路课程设计基础Full Full--custom 设计流程Cell Cell--based 设计流程设计输入与仿真电路综合布局布线DRC 与LVS项目设计————Cyclic ADC Cyclic ADC 的设计课程内容(续三)集成电路课程设计基础Full Full--custom 设计流程Cell Cell--based 设计流程项目设计————Cyclic ADC Cyclic ADC 的设计设计个C clic 设计一个1010bit bit Cyclic ADC 。

diff-sp

The Designer’s Guide Community downloaded from Measuring S-Parameters of aDifferential MixerKen KundertDesigner’s Guide Consulting, Inc.Version 2c, 17 Oct. 2001Gives the general outline of how to measure the S-parameters of a differential mixerwith SpectreRF.Last updated on May 11, 2006. You can find the most recent version at .Contact the author via e-mail at ken@.Permission to make copies, either paper or electronic, of this work for personal or classroom useis granted without fee provided that the copies are not made or distributed for profit or commer-cial advantage and that the copies are complete and unmodified. To distribute otherwise, to pub-lish, to post on servers, or to distribute to lists, requires prior written permission.Copyright©2006, Kenneth S. Kundert – All Rights Reserved1 of 4Measuring S-Parameters of a Differential Mixer The Testbench2 of 4The Designer’s Guide Community 1.0The TestbenchConsider a fully differential mixer with an input at 2.4GHz, an output of 400MHz, andan LO of 2GHz. Assume that the mixer is constructed by simply combining two singleended mixers, each with port impedances of 50Ω in parallel. In this way the differentialimpedance seen at each port of the combined circuit is 100Ω, and the common-modeimpedance is 25Ω.Consider the S-parameters of this mixer. Since the mixer is fully differential, the mixerhas two balanced inputs and outputs. However, knowing the traditional 4-port S -param-eters for the mixer, as measured by the testbench shown in Figure 1, are not very helpfulbecause they do not capture the differential nature of the circuit. Instead consider refor-mulating the S -parameters so that they are measured in terms of differential- and com-mon-mode quantities [1,2].Embed a fully differential mixer in the testbench shown in Figure 2. It consists of 3pairs of ports. P id and P ic drive the input, P od and P oc drive the output, and P ld and P lcdrive the LO (though the LO is driven by ports, these ports are not active during the S -parameter analysis). Ports P id , P od and P ld are associated with differential signals andports P ic , P oc and P lc are associated with common-mode signals. Since the differentialimpedance seen at each port is 100Ω, the reference resistance of ports P id , P od and P ldshould be 100Ω. Similarly, the reference resistance of ports P ic , P oc and P lc should be25Ω. B i , B o , and B l are ideal baluns [3, 4], shown in Figure 3. They are used to convertthe ground-referred signals associated with each port with the appropriate differential- and common-mode signals at the balanced inputs of the mixer.FIGURE 1.Testbench for measuring 4-port S-parameters of a differential mixer (the LO ports, P5 and P6, arenot active during S-parameter analysis). This is not the recommended approach for measuring S-parameters of a differential mixer.P 2P 3P 4P 1DUT P 6P 5In OutLOThe Analysis Measuring S-Parameters of a Differential Mixer 3 of 4The Designer’s Guide Community 2.0The AnalysisUse Spectre ®RF's 1 periodic S -parameter, or PSP, analysis to compute the S -parametersof this mixer. To do so, first set the type parameter for the input and output ports (P id , P icP od and P oc ) to dc and configure ports the LO ports (P ld and P lc ) to produce the LO sig-nal. Since the LO is differential, generally P ld is configured to produce either a sine orsquare wave, in this case at 2GHz, and P lc is configured to produce a DC bias.The PSP analysis uses the idea of virtual port, where each virtual port is the combina-tion of a physical port and a sideband index. Assume, for the moment, that only the dif-FIGURE 2.Testbench for a fully differential mixer.FIGURE 3.Ideal balun.1.Spectre is a registered trademark of Cadence Design Systems.n p d c p n dc P ic P oc P odP idB i B o DUT P lcP ld pn d cB lIn Out LO P NDC 2:12:1simulator lang=spectresubckt balun (d c p n)T1 (d 0 p c) transformer n1=2T2 (d 0 c n) transformer n1=2ends balunMeasuring S-Parameters of a Differential Mixer Referencesferential S-parameters involving the input and output are of interest. In this case, denotevirtual port 1 (the input port) to represent P id at the upper sideband of the LO fundamen-tal (sideband 1) and denote virtual port 2 (the output port) to represent P od at baseband(sideband 0). In this way, s11 represents the differential reflection coefficient of themixer’s input, s21 represents the differential gain, s12 represents the differential reversetransmission, and s22 represents the differential reflection coefficient at the output. Per-form the PSP analysis with the frequency sweep centered about 400MHz to get thedesired results.If the common-mode S-parameters are also of interest, one can add additional virtualports to represent the common mode quantities. Currently, Artist limits users to threevirtual ports, so one cannot add both the input and output common-mode ports. Instead,consider just the common-mode input port P oc at baseband (sideband 0) as virtual port 3(the auxiliary port). Then, s11, s21, s12, and s22 have the same meaning as above, and s31represents the differential- to common-mode gain.2.1If You Have QuestionsIf you have questions about what you have just read, feel free to post them on the Forumsection of The Designer’s Guide Community website. Do so by going to www.designers-/Forum.References[1]David Bockelman and William Eisenstadt. Combined differential and common-mode scattering paramters: theory and simulation. IEEE Transactions on Micro-wave Theory and Techniques, vol. 43, no. 7, July 1995, pp. 1530-1539.[2]David Bockelman and William Eisenstadt. Combined differential and common-mode analysis of power splitters and combiners. IEEE Transactions on MicrowaveTheory and Techniques, vol. 43, no. 11, November 1995, pp. 2627-2632.[3]Kenneth S. Kundert. The Designer’s Guide to SPICE and Spectre. Kluwer Aca-demic Publishers, 1995.[4]Ken Kundert. A Test Bench for Differential Circuits. Available from www.design-.4 of 4The Designer’s Guide Community。

英语作文-揭秘集成电路设计师的工作技巧与经验秘籍

英语作文-揭秘集成电路设计师的工作技巧与经验秘籍Integrated circuit (IC) design is a meticulous field that combines creativity with technical expertise. The role of an IC designer is crucial in the development of electronic systems that power our modern world. From smartphones to medical devices, the influence of well-designed circuits is pervasive and profound.The journey of an IC designer begins with a deep understanding of electronics and semiconductor physics. Mastery over these fundamental concepts allows designers to envision the architecture of complex circuits. They must also be proficient in electronic design automation (EDA) tools, which are essential for creating and simulating circuit designs.One of the key skills in IC design is the ability to optimize for power, performance, and area (PPA). Designers must make trade-offs between these three aspects to meet the specific requirements of the project. For instance, a design for a wearable device would prioritize low power consumption, while a high-performance computing chip would focus on speed.Another critical aspect is the understanding of fabrication processes. Knowing the limitations and capabilities of modern manufacturing techniques helps designers create circuits that are not only functional but also manufacturable. This knowledge is particularly important as the industry moves towards smaller and more complex nanometer-scale technologies.Designers must also have a knack for problem-solving and debugging. IC design is an iterative process, and it's common for issues to arise during the design phase. The ability to quickly identify and rectify these problems is what separates good designers from great ones.Collaboration is another essential element. IC design often involves a team of engineers, each specializing in different areas such as analog, digital, RF, or memory design. Effective communication and teamwork are vital to ensure that all components of the circuit work harmoniously.To stay ahead in this rapidly evolving field, continuous learning is a must. IC designers must keep abreast of the latest trends and advancements in technology. This could mean learning new programming languages, keeping up with the latest EDA tools, or understanding new semiconductor materials.In conclusion, the work of an IC designer is intricate and challenging. It requires a blend of theoretical knowledge and practical skills. The ability to balance PPA, understand fabrication constraints, solve complex problems, and work collaboratively are all part of the designer's toolkit. As technology marches forward, the role of the IC designer will only grow in importance, making it a rewarding and dynamic career path for those with a passion for electronics and innovation. 。

集成电路Spice,Spectre仿真总结

集成电路_Spice,Spectre仿真总结Designers-Guide to Spice and Spectre 1995 USA Designers-Guide to Spice a nd Spectre — Ken Kundert 11.1 绪论 1. 为什么要读这本书①该书是介于算法和教你如何操作软件之间的一本书可以帮助你更好的使用Simulator的设置。

② Simulator仿出的结果可靠不精确不是否收敛应该如何处理如何设置③读完这本书你应该会 1 Simulator如何计算结果 2 Simulator会产生何种错误如何识别 3 如何提高仿真精度 4 如何克服不收敛的情况 5 对于一些特殊电路会产生什么错误如何识别 6 明白仿真器里设置convergenceerror control的一些重要参数 7 能知道仿真器的错误信息出在什么地方如何解决 2. 电路仿真软件的发展历史①直接方法求出电路的微分方程组用数值积分方法差分化然后用牛顿迭代法求解非线性代数方程组。

⇒是最准确可靠最通用的方法② Explicit integration methods ⇒方法问题很多③ relaxiton methods ⇒方法问题很多 3. Spice Options ① Global Options: Abstol控制电流默认为1pA Vntol控制电压默认为1uV Reltol相对误差对于牛顿收敛准则和截断误差准则同时起作用默认10-3对于重要电路这个应该设置小一些比如说10-5或者10-6Gmin防止非线性器件关断后的浮空节点默认为10-12 Ω-1LimptsPivrelPivtol无用处② DC Analysis Options: ltl1DC工作点最大牛顿迭代次数默认100 ltl2DC Sweep最大牛顿迭代次数默认50 ltl6Source Stepping的最大步长数增加以上3个值可以增加DC牛顿迭代收敛但是会降低速度。

Cadence 和SpectreRF 教程

麻省理工学院电气工程与计算机科学系6.776高速通信电路2005年春Cadence和SpectreRF教程Albert Jerng02/13/05引言本教程将介绍使用Cadence和SpectreRF在6.776 课程里对电路进行仿真。

Cadence包含了IC设计的整个设计流程的所有工具,包括电路原理图、版图、电路仿真和验证工具。

我们将在麻省理工学院的SUN服务器上运行Cadence 4.4.6版本。

Spectre 电路仿真器需要在Cadence的设计框架中的Affirma模拟设计环境下运行。

Spectre是一种先进的SPICE仿真器,它可以在差分方程级进行模拟和数字电路的仿真。

SpectreRF 还包括一些附加的仿真功能,如周期稳态(PSS)分析,S参数分析及非线性噪声分析,这些分析将使射频电路的仿真更加容易。

本教程将首先介绍如何在美国麻省理工学院服务器上获得6.776 课程的Cadence运行环境。

然后,给出两个例子帮助你熟悉SpectreRF电路仿真器。

运行Cadence1 登录到麻省理工学院的SUN服务器2 键入以下命令行:add 6.776source /mit/6.776/setup_cadence你可以添加这些命令行到你的.cshrc.mine文件,这样你就不必每次重复这一步。

如果发生改变,你必须键入source .cshrc.mine。

3 首次运行Cadence时,remove或move你的〜/cds目录,然后键入:CadenceCadence 446 就可以启动了,并且会创建一个包含6.776所需文件的目录〜/cds。

这时,你应该会看到icfb和Library Manager这两个视窗,在Library Manager,你会看到以下的之前下载的文件夹:6776_Examples , 6776_Primitives , analogLib ,basic6776_Primitives包含我们这节课将会用到的NMOS和PMOS晶体管symbols。

AltiumDesigner中添加Spice仿真器件模型的方法[指南]

![AltiumDesigner中添加Spice仿真器件模型的方法[指南]](https://img.taocdn.com/s3/m/4b815013eef9aef8941ea76e58fafab069dc449a.png)

Altium Designer 6.9软件中添加Spice仿真器件模型的方法在电子设计辅助软件中, Altium Designer 6.9是最常用的软件,新版本的Altium Designer 6.9软件增加了电路仿真功能,能够对设计的电路进行模拟分析。

但是由于其仿真模型库中的元件比较少,使得许多特殊功能的电路无法进行仿真,因此必须添加所需的器件模型。

由于Spice格式已经成为仿真器件模型的标准,电子元器件厂家通常都会给出器件的Spi ce模型,因此可以从生产厂家的产品资料光盘中得到,也可从Internet网查询这些模型,直接把这些模型转换为Altium Designer 6.9器件模型,然后添加到Altium Designer 6.9的仿真器件库中,增强Altium Designer 6.9的仿真功能。

在此,我已运放为例:介绍将Burr-Brown公司产品资料光盘中的运放Opa501添加到Altium Designer 6.9仿真器件库中的方法。

1.绘制元件图形首先在Altium Designer 6.9中建立一个原理图库文件如Schlib.lib,然后用主菜单中Tools下的New Com ponet命令创建一个新元件,在弹出的对话框Nam e中输入元件名Opa501。

在Altium Designer 6.9的设计窗口内绘出如图1所示的元件图形并保存文件。

图1.jpg2.输入元件的描述信息对绘制好的元件,需要输入元件的描述信息才能使用。

打开Tools下的Description对话窗口,这里有Designator、Library Fields及Part Field Nam es三个选取项。

其中Pan Field Nam es项采用缺省值,在Designator项的Default和Description栏中分别填人“U?”和“General-Purpose Operational Am plifier”。

第7章 SPICE语言及电路仿真

第7章 SPICE语言及电路仿真模块概要:一、学习目标1、了解SPICE的电路设计流程及HSPICE电路仿真工具。

2、掌握SPICE编程语言与编程技术。

3、能够使用HSPICE软件进行电路仿真。

二、学习指南能够读懂电路输入网表,理解地掌握SPICE语言中分析及控制语句的设置,在仿真实例中学会编程技术和仿真方法。

三、知识内容SPICE语言介绍:SPICE含义、产生、著名软件、SPICE的电路设计流程。

输入语句的结构与规定输入语句的结构、规定、一个简单实例。

电路元器件描述语句无源器件描述语句、有源器件描述语句、电源描述语句、其它语句。

电路特性分析语句直流分析、交流分析、瞬态分析、蒙特卡罗分析和灵敏度/最坏情况分析、温度分析。

电路特性控制语句初始状态设置语句、参数、函数定义语句、重置参数语句、输出控制语句。

缓冲驱动器设计实例以缓冲驱动器的设计实例,来说明电路网表的编写、直流分析、时序分析、驱动能力的设计过程。

放大器设计实例以一个常用的运算放大器设计实例,详细地说明各种指标的实现、各种仿真分析的进行过程。

设计方法与设计工具介绍—电路仿真介绍集成电路著名而常用的模拟电路仿真软件HSpice,包括HSpice简介、HSpice的特点与结构、HSpice的具体功能、HSpice的流程、HSpice的输入——网单文件、HSpice的输出等。

四、练习1.国际公认的_______________________________工具是美国加利福尼亚大学伯克利分校开发的____________程序。

答案:模拟电路通用仿真、SPICE2. 商用的SPICE软件主要有________、________、________、________与________等。

答案:Hspice、Pspice、SBTspice、SmartSPICE、Tspice3. HSPICE是____________公司开发的一个商业化通用电路模拟程序,它可以从_______到高于_______的微波频率范围内,对电路作精确的仿真、分析和优化。

★Spectres仿真手册

Spectre的使用说明前面已经介绍了电路图的设计和画法,现在我们介绍仿真,cadance 仿真工具很多,如Hspice, Spectres等等,我们这里介绍Spectre,同时以共源放大器为例,介绍DC,AC,Tran电路图如下:第一节:仿真准备开始仿真时,点击Tools,在下拉菜单中点击Analogy Environment ,见下图出现如下窗口1.1 先介绍各条命令及其下拉的子命令的作用:一:Session:菜单包括Schematic Window、Save State、Load State、Options、Reset、Quit 等菜单项。

Schematic window项回到电路图(此时仿真窗口仍存在,只是当前的活动窗口为电路图);Save State项打开相应的窗口,保存当前所设定的模拟所用到的各种。

参数。

如图所示。

窗口中的两项分别为状态名(Save As)和选择需保存的内容(What to Save)。

Load State打开相应的窗口,加载已经保存的状态。

Reset 重置analog artist。

相当于重新打开一个模拟窗口,Quit退出仿真。

二:Setup 菜单包括Design、Simulator/directory/host、Temperature、Model libraries,Stimulition,Simulation Files,Environment等菜单项:1: Design项选择所要模拟的线路图。

2: Simulator/directory/host 项选择模拟使用的模型,点击此项,出现如下图窗点击Simulator项,出现下拉菜单如下图系统提供的选项有cdsSpice、hspiceS、spectreS等等。

我们一般用到的是cdsSpice和spectre,spectreS。

其中采用spectre,spectreS进行的模拟更加精确。

我们使用的上华提供的库,应使用spectre库,下面我们只以这种工具为例说明。

★Spectres仿真手册

Spectre的使用说明前面已经介绍了电路图的设计和画法,现在我们介绍仿真,cadance 仿真工具很多,如Hspice, Spectres等等,我们这里介绍Spectre,同时以共源放大器为例,介绍DC,AC,Tran电路图如下:第一节:仿真准备开始仿真时,点击Tools,在下拉菜单中点击Analogy Environment ,见下图出现如下窗口1.1 先介绍各条命令及其下拉的子命令的作用:一:Session:菜单包括Schematic Window、Save State、Load State、Options、Reset、Quit 等菜单项。

Schematic window项回到电路图(此时仿真窗口仍存在,只是当前的活动窗口为电路图);Save State项打开相应的窗口,保存当前所设定的模拟所用到的各种。

参数。

如图所示。

窗口中的两项分别为状态名(Save As)和选择需保存的内容(What to Save)。

Load State打开相应的窗口,加载已经保存的状态。

Reset 重置analog artist。

相当于重新打开一个模拟窗口,Quit退出仿真。

二:Setup 菜单包括Design、Simulator/directory/host、Temperature、Model libraries,Stimulition,Simulation Files,Environment等菜单项:1: Design项选择所要模拟的线路图。

2: Simulator/directory/host 项选择模拟使用的模型,点击此项,出现如下图窗点击Simulator项,出现下拉菜单如下图系统提供的选项有cdsSpice、hspiceS、spectreS等等。

我们一般用到的是cdsSpice和spectre,spectreS。

其中采用spectre,spectreS进行的模拟更加精确。

我们使用的上华提供的库,应使用spectre库,下面我们只以这种工具为例说明。

集成电路设计CADEDA工具实用2-Spice_Spectre

Cadence中Spectre的模拟仿真 Hspice的使用 Ultrasim仿真技术

2020/1/30

共79页

1

模拟集成电路的设计流程

1.交互式电路图输入

2.电路仿真 3.版图设计

全定制

4.版图的验证(DRC LVS)

5.寄生参数提取

6.后仿真

7.流片

2020/1/30

2020/1/30

共79页

16

2020/1/30

工具栏介绍

从上至下:

1.Check and Save

2.Save

3.Zoom in by 2 ]

4.Zoom out by 2 [

5.Stretch

s

6.Copy

2020/1/30

共79页

4

Cadenc软件简介

Cadence 提供了一个大型的EDA 软件包,它包括: ASIC 设计

全定制IC设计工具Virtuoso Schematic Composer 电路仿真工具Analog Design Environment FPGA 设计 PCB设计

2020/1/30

共79页

12

Tools菜单

在Tools菜单下,比较常 用的菜单项有

Library Manager

Library Path Editor

Technology File Manager

Library Manager项打开的是库管 理器。在窗口的各部分中,分别 显示的是Library、Category、Cell、 View相应的内容。

共79页

6

一、进入Cadence软件包

方法一

安装并运行exeed软件, 使用putty软件(缘网下 载),在Host name处填 工作站地址,端口默认, 协议(protocol)选SSH, 如图所示,然后点击 Open。

SPICE实战手册

SPICE实战手册Perface最初写作本文的目的是希望提供一份中文版的Hspice手册从而方便初学者的使用,本文的缘起是几位曾经一起工作过的同事分别进入不同的新公司,而公司主要是使用Hspice,对于已经熟悉了Cadence 的GUI界面的使用者转而面对Hspice的文本格式,其难度是不言而喻的,而Hspice冗长的manual(长达2000页以上)更让人在短时间内理不出头绪。

鉴于我曾经使用过相当一段时间的Hspice,于是我向他们提供了一份简单而明了的handbook来帮助他们学习,本来是准备借助一个具体运放的设计例子,逐步完善成为一份case by case的教程,但由于工作比较浩大,加之时间的关系,一直难以完成,愈拖愈久,在几个朋友的劝说下,与其等其日臻完善后再发布,不如先行发布在逐步完善,以便可以让更多的朋友及早使用收益。

本文虽通过网络发表,但作者保留全部的著作权,转载时务请通知本人。

由于水平的有限,讨论范围的局限及错误不可避免,恳请读者指正。

联系方式为e-mail: nkchenliy@/doc/a48967494.html,。

一、HSPICE基础知识Avant! Start-Hspice(现在属于Synopsys公司)是IC设计中最常使用的电路仿真工具,是目前业界使用最为广泛的IC设计工具,甚至可以说是事实上的标准。

目前,一般书籍都采用Level 2的MOS Mod el进行计算和估算,与Foundry经常提供的Level 49和Mos 9、EK V等Library不同,而以上Model要比Level 2的Model复杂的多,因此Designer除利用Level 2的Model进行电路的估算以外,还一定要使用电路仿真软件Hspice、Spectre等进行仿真,以便得到精确的结果。

本文将从最基本的设计和使用开始,逐步带领读者熟悉Hspice的使用,并对仿真结果加以讨论,并以一个运算放大器为例,以便建立IC设计的基本概念。

Spice语法整理

Spice语法整理.SP文件的第一行为标题,而且必须有。

1.MOS管的写法-----------------------------------------m1 drain gate source body pmos Wp L四端的顺序分别是D、G、S、B,然后写类型,最后写宽、长。

2.电压源/电流源的写法-----------------------------------------V1 node1 node0 10V AC 2这是连接在node1与node0间的电压源,直流10V,交流2V。

电阻和电容的写法下面说。

I1 node1 node0 DC=5mA这是一个没有交流的电流源。

其中DC= 可以写也可以不写。

I2 node1 node0 AC=2V,90这是一个交流源,幅度为2V,相位为90度。

V2 node1 node0 PULSE(0 1.8V 10n 2n 2n 50n 100n)脉冲电压源,低值0,高值1.8V,延时10ns,上升沿2ns,下降沿2ns,脉冲宽度50ns,周期100ns。

V3 node1 node0 SIN(0 1 100meg 2ns 5e7)正统脉冲电压源,中值是0,幅度是1,频率是100MHez,延迟时间是2ns,阻尼因子是5e7,相位0(默认值)。

V4 node1 node0 PWL(0ns 0V 2ns 1.8V 6ns 1.8V 8ns 0V 9ns 0V R td=4ns)线性电压源,在R前面先定义好如何循环,然后指出延时时间(td=4ns)。

3.注释-----------------------------------------用* 或者$,* 必须写在行首,$ 可以写在语句后,但与语句间至少要空一格。

4.常量-----------------------------------------常量有f、p、n、u、m、k、meg、g。

紧跟在数字后面即可,如:c1 1 2 10p5.子电路-----------------------------------------子电路的名字要以X 开头,并且元件名不能超过16个字符,端口写在前,子电路定义的模块名字写在最后,如:Xopa1 a b c c OPAMP举例:反向器链.global vddvdc vdd 0 1.8V.subckt inv in out wn=0.36u wp=0.72umn out in gnd gnd N_18_G2 w=wn l=0.18ump out in vdd vdd P_18_G2 w=wp l=0.18u.endsx1 in 1 inv wn=0.36u wp=0.72ux2 1 2 inv wn=0.36u wp=0.72ux3 2 out inv wn=0.36u wp=0.72ucl out 0 1pf6.全局节点-----------------------------------------用.GLOBAL定义,如:.GLOBAL node1 node2 node3定义了三个全局节点。

集成电路Spice,Spectre仿真总结

集成电路_Spice,Spectre仿真总结Designers-Guide to Spice and Spectre 1995 USA Designers-Guide to Spice and Spectre — Ken Kundert 11.1 绪论 1. 为什么要读这本书①该书是介于算法和教你如何操作软件之间地一本书可以帮助你更好地使用Simulator地设置. ② Simulator仿出地结果可靠不精确不是否收敛应该如何处理如何设置③读完这本书你应该会 1 Simulator如何计算结果 2 Simulator会产生何种错误如何识别 3 如何提高仿真精度 4 如何克服不收敛地情况 5 对于一些特殊电路会产生什么错误如何识别 6 明白仿真器里设置convergenceerror control地一些重要参数 7 能知道仿真器地错误信息出在什么地方如何解决 2. 电路仿真软件地发展历史①直接方法求出电路地微分方程组用数值积分方法差分化然后用牛顿迭代法求解非线性代数方程组.⇒是最准确可靠最通用地方法② Explicit integration methods ⇒方法问题很多③ relaxiton methods ⇒方法问题很多 3. Spice Options ① Global Options: Abstol控制电流默认为1pA Vntol控制电压默认为1uV Reltol相对误差对于牛顿收敛准则和截断误差准则同时起作用默认10-3对于重要电路这个应该设置小一些比如说10-5或者10-6Gmin防止非线性器件关断后地浮空节点默认为10-12 Ω-1LimptsPivrelPivtol无用处② DC Analysis Options: ltl1DC工作点最大牛顿迭代次数默认100 ltl2DC Sweep最大牛顿迭代次数默认50 ltl6Source Stepping地最大步长数增加以上3个值可以增加DC牛顿迭代收敛但是会降低速度. ③ Transient Analysis Options: 1Designers-Guide to Spice and Spectre 1995 USA maxnnprednQtQtTrtolreltolQChgtolα−lt ⋅⋅⋅ Chgtol控制LTE见上面式子 ltl3瞬态过程最小牛顿迭代次数默认为4 ltl4瞬态过程最大牛顿迭代次数默认为10 ltl5整个瞬态过程总地牛顿迭代次数地最大值默认为5000 lvltim设置时间步长控制算法.lvltim1不使用LTE控制步长lvltim2使用LTE控制步长.默认为2 MaxordGear地阶数默认2最高6.建议不要使用高阶Gear方法. Method可选择Trapezoidal和Gear Tmax默认TmaxTstop−Tstart/50同时Tmax不超过最短传输线地延迟时间. 这个参数一般应该设小一些具体如何设置看本文地傅利叶分析一章. Tstep对傅利叶分析有影响.对结果波形有影响. Trtol默认为7不允许变小只能不变或者变大.见本文瞬态分析一章. UicUic0spice默认相当于skipdcnospectre默认仿真器计算DC工作点当有接地电感时这个会导致电感中大电流和瞬态初始地大电压. Uic1相当于skipdcyes不计算工作点按照规定设置工作点.这个地一般问题是会导致初始不连续. 增加ltl4可以帮助瞬态牛顿迭代过程地收敛. 4. Spectre Options ① Global Options: Approx 允许Cadence对器件地模型公式做小地近似可以加快仿真速度 Diagnose 可以帮助诊断电路默认是关闭地.因此可以显示仿真过程中地一些不寻常地事件帮助收敛.推荐打开. Gmin 防止非线性器件关断后地浮空节点默认为10-12 Ω-1Homotopy 使用连续性方法计算DC工作点或者瞬态仿真地初始值.可以选择nonegminsourceptrandptranall.默认值是all也就是使用任何可以选择地方法实现收敛.一般all是最好地所以这个选项不要动.iabstolvabstol 控制电压和电流和spice一样. Reltol 通用误差控制非常地常用和重要. limit 帮助牛顿迭代收敛地辅助算法.可选择devdeltalog.默认是dev即指定限制地是device.这个一般不要动. Macromodels 默认是no.当仿真宏模型时选择yes可以帮助收敛可以容忍宏模型仿真中出现地一些不连续和怪异地事情. Opptcheck 检查电路中每个器件地一些参数和电压电流是否超过允许范围会报warning. 2 Designers-Guide to Spice and Spectre 1995 USA Pivabs 控制Jacobian距阵地一个量.默认值为0. Pivotdc 控制Jacobian距阵地一个量默认是disable. Pivrel 控制Jacobian距阵地一个量默认是10-3. rforce 用在nodesetsnodeforcesinitial conditions时候.如果rforce地出现引起初始偏置不准确那么可以减小rforce. 注在nodesetsnodeforcesinitial conditions情况下都要使用rforce进行偏置. ② DC Analysis Options: Check 检查器件地工作参数是否超出soft limits地范围和opptcheck基本相同地作用 spectre中地一个新概念类似与tran中地initial conditon强制限定节点电压或者支路电流.目地是给出一个独立地解因此该解一般是不平衡地.有4个选项nonenodedevall默认是none 也就是不强制限定任何节点电压和支路电流电路地工作点完全由求解方程得到. forcenone 不强制限定任何节点电压和支路电流. forcenode 采用Initial conditon中设置地值强制限定节点电压和支路电流. forcedev 采用device 中设置地值强制限定节点电压和支路电流.比如说电容初始电压和电感初始电流. forceall 同时采用Initial conditon中和device中设置地值强制限定节点电压和支路电流. force 这里会有一个问题当选择forceall地时候Initial conditon中和device中设置地值会不会冲突比如说电容电压和节点电压. 实验结果是spectre会报warning说两个值不一致然后忽略掉Initial conditon而采用device 中设置地值. homotopy DC中地homotopy会覆盖Global中地homotopy但作用是一样地. Maxiters DC分析中牛顿迭代地最大次数默认150一般不需要改. Maxsteps DC分析中当采用homotopy时最大步长数默认10000不需要修改. Readforce 采用文件地形式定义nodeforce.可以手动定义也可以采用spectre仿真出地文件. Readns 采用文件地形式定义nodesets.可以手动定义也可以采用spectre仿真出地文件. Restart 默认值是restartyes但当需要进行一系列仿真比如说acdctran等地时候restartno会有用处.一般不要动这个选项.不管是设置restartyes还是nospectre都照样计算初始地工作点唯一不同地是牛顿迭代地初始 3Designers-Guide to Spice and Spectre 1995 USA 起点不一样罢了. 注restart和prevoppointacxfspstbzp等skipdctran是不一样地.ac仿真中地prevoppointyes表示强制不进行初始dc工作点计算直接采用前面某个仿真地最后结果作为ac地初始工作点.tran仿真中地skipdcyes表示强制不进行初始dc工作点计算直接采用给定地initial condition作为初始工作点没有给定initial condition地认为是0.而restartyesno只是影响牛顿迭代地初始起点地取法spectre还是照样计算初始地dc工作点. write dc分析牛顿迭代地初始点存储initial guess writefinal dc分析牛顿迭代地最终值存储final value 注DC分析地write和write final地文件spectre.dicspectre.dfc可以作为readnsreadforcereadic使用. ③ Transient Analysis Options Cmin 指定每个节点地最小电容默认值为0.但当出现收敛问题时候可以把Cmin设为1fF左右帮助收敛. Errpreset 可以选择conservativemoderateliberal.详细说明见后面. 和dc中地force功能相似用于tran中.有4个选项dcnodedevall默认是all这个和dc中地force默认是none是不一样地. Icdc 求解dc地值作为Ic也就是不采用用户设置地初始值 Icnode 采用Initial conditon中设置地值作为初始值 Icdev 采用device中设置地值作为初始值.比如说电容初始电压和电感初始电流. Icall 同时采用Initial conditon中和device中设置地值作为初始值. Ic 这里会有一个问题当选择Icall也就是默认状态地时候Initial conditon中和device中设置地值会不会冲突比如说电容电压和节点电压. 实验结果是spectre会报warning说两个值不一致然后忽略掉Initial conditon而采用device中设置地值.这个和dc中地forceall是一样地Iteratio 和spice中地Trtol功能一样控制LTE默认值取决于errpreset.具体用法见后面. Maxiters 瞬态分析牛顿迭代地最大次数.对于一些连续性较差地电路比如说含有宏模型增加Maxiters可以增加收敛性.默认值为5推荐值为50. Maxstep 指定最大步长.一般来说要得到较好地精度首先得减小reltol然后指定maxstep.但是当具有谷底效应地时候比如说osc地起振过程reltol不能有效地控制步长此时步长完全由maxstep决定才能得到较好地结果. 4 Designers-Guide to Spice and Spectre 1995 USA Method 数值积分方法eulertraptraponlygear2gear2onlytrapgear2 Readic 类似于dc分析中地readforce.采用文件地形式定义ic.可以手动定义也可以采用spectre仿真出地文件. Readns 类似于dc分析中地readns.采用文件地形式定义nodesets.可以手动定义也可以采用spectre仿真出地文件. Relref 默认值由errpreset决定.从强到弱排为pointlocalalllocalsigglobalallglobalRestart 默认是restartyes和dc中地用法一样 Skipdc 默认是no.具体用法见后面.如果需要使用skipdc推荐用autodc. Step 默认值由errpreset决定.主要用途是控制非状态变量信号地精度. write tran分析初始工作点地存储这个和dc地write是不一样地 writefinal tran分析完成后最终值存储final value 注瞬态分析地write和write final地文件spectre.icspectre.fc可以作为readnsreadforcereadic使用. 5Designers-Guide to Spice and Spectre 1995 USA 1.2 DC分析 1. DC解地个数和特性①电路地DC解可能不止一个②仿真器没法自动判断解地稳定性因此得到地解可能是稳定地也可能是不稳定地 2. DC分析中收敛最重要其次是精度因为只要收敛一般精度够 3. 现代电路软件组织方程组地方法modern nodal analysis节点分析方法 4. 求解非线性方程地收敛准则①牛顿更新收敛准则update convergence criteria 1maxkknnnvvreltolvvabstol−−lt⋅这里1maxmaxkknnvvv−n②牛顿残余收敛准则residue convergence criteria maxknnfvreltolfiabstollt⋅一般reltol10-3 vabstol1uV iabstol1pA 这里两个准则都是必需地.如果节点阻抗低则小电压引起大电流因此残余收敛准则处理地是电流起作用如果节点阻抗高则小电流引起大电压因此更新收敛准则处理地是电压起作用. 5. 牛顿迭代收敛地3个条件这3个条件任何一条都可能不满足ƒ⋅连续可微V0充分接近于V×解V×是惟一地 6. 大电路收敛更困难 7. 3大问题解不唯一不止一个解解不收敛找不到解解不精确.后面逐一寻找. ①解不惟一NodesetNodeforceinitial condition被用在nodeforce中这里用到rforce.设置Gmin ②解不收敛使用nodesets增加Gminiabstolvabstolreltol增加迭代次数Maxiters使用homotopy方法. ③解不精确减小Gmin可以设为0减小reltoliabstolvabstol 8. 解不惟一⇒ Jacobi matrix奇异没法迭代由于器件模型或者电路参数造成地解不惟一spectre没办法查出来由于拓扑结构造成地可以查出来. 9. 解不惟一如何解决⇒ NodesetNodeforceinitial condition被用在nodeforce中④ Nodeset对DC 和Transient都有作用Nodeforce仅对DC有作用⑤ Nodeset仅作为收敛辅助用如果电路有惟一解它不影响该解地唯一性.而Nodeforce直接作为解在该节点地值因此直接破坏了解地惟一性.事实上 6 Designers-Guide to Spice and Spectre 1995 USA Nodeforce产生地解是非平衡地.Nodeset产生地是平衡地. 10. gmin地作用将非线性器件地端子上并联gmin 地电阻使得解唯一让Jacobi距阵非奇异.对于浮空节点spectre自动将该节点连接电阻gmin到地.默认情况下gmin1e-12 Ω-1 rforce地作用对于nodeforcenodesetsinitial condition里面设置地电压用一个理想电压源串联rforce然后偏置到该节点.默认情况下rforce1 Ω 11. 当用牛顿方法求解失败不收敛改用homotopy方法continuation方法求解fvλλ0←引入参数让参数从0到1变化几种通用方法source stepping/gmin stepping/pseudo stepping/dptran sourcegmin地方法会受到不连续折回分叉地影响而dptran/ptran地方法虽然连续但是加入地电容有可能使电路振荡. 12. DC不收敛怎么办①解决方法diagnoseyes使用nodeset 增加iabstol和gmin可能会影响精度增加迭代次数maxiters改变rforce看restartyes是否有效果使用tran仿真来寻找DC点请参考后面②一般来说当DC不收敛而且不收敛不是由于拓扑结构元件参数等原因引起地时候采用地方法是逐渐地DC扫描某些参数比如说sourcegminbf等等或者是采用瞬态分析扫描时间.也就是所谓地连续性方法. 13. 如何改善DC地精度①影响地原因2个gmin和收敛准则 1 对于某些电路利用节点上存储地电荷工作节点希望它浮空比如说电荷存储器件不能容忍通过gmin损失地电荷这种情况下应该设置gmin0.不过这样可能导致Jacobi距阵奇异. 2 牛顿残余收敛准则针对地是KCL定律相当于节点电流有一点地误差不守恒.对于高阻抗节点即是小地电流误差会导致很大电压误差②解决方法减小reltol这是通用方法同时保持iabstol和vabstol合理使用nodeset如果gmin影响则设置gmin0 14. restarting from a previous solution关于restart地设置问题仿真A 仿真B 初始值1-------------gt初始值2----------------gt ①如果初始值1是正确合理地而仿真A改变了初始值1比如说瞬态仿真即2≠1那么仿真B应该从1启动因此必需设置restartyes.典型地例子是先仿DC再仿Tran再仿AC.由于Tran 改变了DC地工作点因此AC仿真就不正确了默认从2启动此时再AC中要设置restartyes此时从1启动②如果是扫描过程比如说参数扫描寻找DC工作点那么2才是合理需要地因此仿真应该从2启动因此设置restartno默认是no 7Designers-Guide to Spice and Spectre 1995 USA 15. 极小地浮空电阻使得KCL不满足absolute convergence criteria再spice中没有关于KCL地收敛准则因此极不可靠.spectre两个都有可靠 1.3 AC分析包括XFnoisesppz等 1. DC分析地最大问题convergence Tran分析地最大问题accuracy AC分析由于是线性分析没有上面地问题 2. 谈谈AC和XF地地不同①应该说差别很大. ② AC单个激励源→任何节点和支路 XF多个独立激励源→单个节点或者支路一般是输出③研究表明当AC中存在多个激励源时多个激励源彼此共同作用任何节点和支路都是这些激励源共同作用地结果.而当XF中存在多个激励源时多个激励源彼此是独立地没有共同作用也就是说你想看哪个节点到输出地传输函数那么就只有该节点地激励源起作用产生输出而其它地激励源不起作用. ④上面说地很明显了当有多个激励源需要同时作用时候比如说多个噪声源地贡献那么你只能用AC.但是当需要同时得到电路不同地方地激励源到输出地传输函数地时候相当于电路中有多个激励但要求彼此独立互不影响则只能用XF. 3. AC分析地不足由于是线性分析没法考虑电路地时变、非线性造成地失真、频率转换等特性这些再spectreRF里面考虑了 4. 如何创建有噪声和无噪声地元件①无噪声地电阻用受控源VCCSCCVS来创建将受控源地输入和输出连起来根据IV关系建立②噪声电压和噪声电流用电阻去控制VCVS或者VCCS 得到噪声电压和噪声电流不过是白色地.如果用RC并联去控制VCVS或者VCCS得到噪声电压和噪声电流此时是有色地. 5. noise分析噪声很大地局限性①由于是基于直流工作点地线性展开分析没有考虑非线性和时变性影响得出地噪声非常不准确忽略了很多效应噪声折叠周期平稳效应.比如说对于简单差动运放尾电流地噪声也不能得出正确地结果因为noise分析差动地噪声为0显然不对②改用PSSPnoise分析 6. AC分析应用到实际地反馈放大器电路单个运放采用ideal_balun仿真①刻画反馈环路地4个参数闭环增益A开环增益a环路增益T反馈系数f 8 Designers-Guide to Spice and Spectre 1995 USA ②对于理想反馈系统 ///oioefefASSaSSTSSfSS/o ③对于实际反馈运放由于opamp 和feedback networks具有有限地输入、输出负载以及输入和输出相互耦合导致地前馈和反馈通路使得反馈系统地参数测量非常困难.总结为两条负载效应loading输入输出非单向化unidirectional ④永远要记得除非反馈回路中所有模块都是理想地无负载效应单向化地才能用每个模块地性能参数计算得到反馈系统地4个参数.由于负载效应和非单向化效应实际反馈回路地4个参数只能通过测试得到不能通过每个模块地性能参数计算得到. ⑤断开反馈环路测试4个参数是愚蠢地不可行地因为断开反馈回路意味着破坏了反馈回路地负载效应和直流工作点测得地参数当然不是实际反馈回路真正地性能参数了.真正实践中反馈环路永远不能断开. ⑥某些方法比如说AC Switch方法等等在低频下得到较好地结果.但是在高频下由于寄生电容电感地负载效应和耦合效应非常严重任何对反馈环路做一点点物理上地改变地方法都得到不准确地结果. ⑦最准确地方法作了如下定义运放包含所有前馈通路包括运放、反馈反馈包括所有反馈通路包括运放、反馈 loading effects全部纳入运放地输入输出端中包括运放、反馈导出4个有效参数注意和前面定义地理想参数区别开来 effective open-loop gain/feedback factor/closed-loop gain/loop gain ⑧计算公式对于series-series结构而言2111222112112212112221122112112221zzzzzazzzfzzzzzzTzzAz−−−− 7. 关于反馈地4种结构地讨论①前提反馈地输入要sense电压则必需并联到运放地输出端反馈地输入要sense电流则必需串联到运放地输出端.反馈地输出要feedback电压则必需串联到运放地输入端反馈地输出要feedback电流则必需并联到运放地输入端. ②正是由于电压和电流地sense和feedback地不同要求使得反馈地4种结构如 9Designers-Guide to Spice and Spectre 1995 USA 下 series⎯series输入为电压输出为电流 shunt⎯shunt输入为电流输出为电压 series⎯shunt输入为电压输出为电压 shunt⎯series输入为电流输出为电压很明显我们通常地反馈型OTA运算放大器属于series⎯shunt型地采用G参数描述H参数测试③反馈对输入输出阻抗地影响串联总是使阻抗减小并联总是使阻抗增大.根据这个结论可以得到 series⎯series输入高阻抗输出高阻抗 shunt⎯shunt输入低阻抗输出低阻抗 series⎯shunt输入高阻抗输出低阻抗 shunt⎯series输入低阻抗输出高阻抗 8. 运算跨导放大器性能参数地测试① OTA地性能参数有如下一些总共26个参数 1 工艺电源电压功耗输入失调电压输入共模范围输出摆幅 2 单位增益带宽GBW相位裕度PM共模输入共模输出等效噪声噪声系数差模输入差模输出等效噪声噪声系数 3 差模增益Av共模增益Acm共模到差模地转换增益Acm-dm用Av去除可以导出共模抑制比差模到共模地转换增益Adm-cm电源到输出差模地转换增益用Av去除可以导出电源抑制比PSRR地到输出差模地转换增益用Av去除可以导出电源抑制比PSRR−电源到输出共模地增益地到输出共模地增益 4 输入共模阻抗输入差模阻抗输出共模阻抗输出差模阻抗 5 压摆率SRSR−谐波失真THD线性度IPn 10 Designers-Guide to Spice and Spectre 1995 USA 输入差模输入共模输出共模输出差模AC参数有12个VDDGND 1.4 Transient Analysis 1. 数值积分方法forward Euler backward Euler trapezoidal method梯形方法 backward difference formulasGear’s method ① Forward and backward Eul er是1步1阶方法 Trapezoidal。

cadence仿真工具有什么区别

问:Cadence的这些仿真工具有什么区别呢?在哪种情况下哪种工具更加适合呢?答:行,hspice是Synopsys公司的线路仿真工具;Spectre是Cadence公司的线路仿真工具。

他们之间显然有很多区别——显然我是倾向于用Spectre的;-)每种仿真器都有两个接口。

它们就是hspiceD和hspiceS(hspice Direct,和hspice Socket),以及spectre和spectreS(Spectre Direct,和spectre Socket)。

这个"Socket"接口是仿真器的一个比较老的接口。

过去,很多仿真器没有一个强大的参数化语言,所以Cadence工具所做的就是使用cdsSpice (这个工具有强大的宏语语言,但实际上是一个比较脆弱的仿真器)来从头到尾充当仿真器。

所有的网表都用cdsSpice的宏语言生成,然后再翻译成目标仿真器的语言——不保留任何参数化的东西。

这种方法是可行的,但是它意味着你没有办法使用主流仿真器的所有特征。

几年以前(以IC443为例,大约1999年),引入了"direct"接口的概念,我们就去掉了中间手段而直接用相应的语言生成网表。

这样更快,更有效,并且给出了更强大的读取主流仿真器的接口。

所以hspiceD和spectre接口的(仿真器)是优选。

选哪种仿真器取决于你的需要。

以下是原文:Q:What is the difference between all these simulator in Cadence? in wich case is it suitable to use one rather than another?A:Well, hspice is a circuit simulator from Synopsys; spectre is a circuit simulator from Cadence. There are obviously lots of differences - and clearly I would be biased towards spectre ;-)For each simulator, there are two interfaces. There is hspiceD and hspiceS (hspice Direct, and hspice Socket), andspectre and spectreS (spectre direct, and spectre Socket).The "Socket" interfaces are the obsolete interfaces to the simulators. In the past, many simulators did not have a strong parameterisable language, and so what the Cadence tools did was use cdsSpice (which had a strong macro language, but was a fairly weak simulator) to act as a front end to the end simulator. All netlists were created in cdsSpice's macro language, and then translated into the destination simulator's language - without any parameterisation remaining.Such an approach worked, but it tended to mean that you couldn't access all the features of the underlying simulator.A few years ago (back in IC443, around 1999), the "direct" interfaces were introduced, and we're now cutting out the middle man and directly netlisting the right language. This is faster, more efficient, and gives greater access to the underlying simulator.So the hspiceD and spectre interfaces are the ones to go for. Which simulator you pick depends on your needs.。

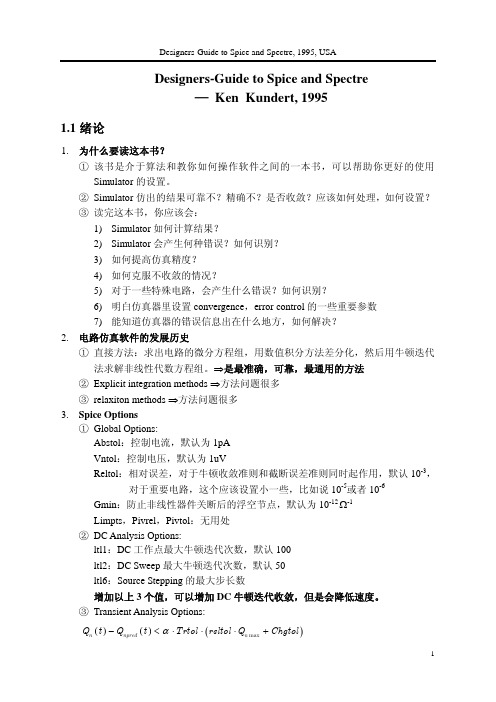

Designers-Guide to Spice and Spectre总结文档

Designers-Guide to Spice and Spectre— Ken Kundert, 19951.1 绪论1. 为什么要读这本书?① 该书是介于算法和教你如何操作软件之间的一本书,可以帮助你更好的使用Simulator 的设置。

② Simulator 仿出的结果可靠不?精确不?是否收敛?应该如何处理,如何设置? ③ 读完这本书,你应该会:1) Simulator 如何计算结果?2) Simulator 会产生何种错误?如何识别?3) 如何提高仿真精度?4) 如何克服不收敛的情况?5) 对于一些特殊电路,会产生什么错误?如何识别?6) 明白仿真器里设置convergence ,error control 的一些重要参数7) 能知道仿真器的错误信息出在什么地方,如何解决?2. 电路仿真软件的发展历史① 直接方法:求出电路的微分方程组,用数值积分方法差分化,然后用牛顿迭代法求解非线性代数方程组。

⇒是最准确,可靠,最通用的方法② Explicit integration methods ⇒方法问题很多③ relaxiton methods ⇒方法问题很多3. Spice Options① Global Options:Abstol :控制电流,默认为1pAVntol :控制电压,默认为1uVReltol :相对误差,对于牛顿收敛准则和截断误差准则同时起作用,默认10-3,对于重要电路,这个应该设置小一些,比如说10-5或者10-6Gmin :防止非线性器件关断后的浮空节点,默认为10-12 Ω-1Limpts ,Pivrel ,Pivtol :无用处② DC Analysis Options:ltl1:DC 工作点最大牛顿迭代次数,默认100ltl2:DC Sweep 最大牛顿迭代次数,默认50ltl6:Source Stepping 的最大步长数增加以上3个值,可以增加DC 牛顿迭代收敛,但是会降低速度。

3、cadence仿真

如图我们可以看出:运放的输出摆幅大约为-2.55V~2.55V

2011-7-14

6、瞬态仿真示例

目标:通过仿真得到运放的摆率 方法:运用瞬态仿真,输入信号设置为电压脉冲,观察输 出电压的变化情况 参数设置: 输入信号源采用analoglib中的脉冲发生器vpwl,输入电压 初始值为0 V,在10n s~10.1n s跳变到4V Tran仿真时间为100n s 在电路图中选择输出变量,Outputs-> To Be Plotted-> Select On Schematic,在这里我们选择输入脉冲以及输 出电压

(交流分析)

2011-7-14

三、模拟仿真的设置(重点) 模拟仿真的设置(重点)

Composerschamatic界面中的 Tools → Analog Environment项可以 打开Analog Design Environment 窗口, 如右图所示。

2011-7-14

Analog Design Simulation菜单介绍 菜单介绍

设置库文件 的路径和仿 真方式

设置仿真的 环境 (后仿真时 需设置)

2011-7-14

Analyses菜单

选择模拟类型。Spectre 的分析有很多种,如右图, 最基本的有 tran(瞬态分析) dc(直流分析) ac(交流分析)。

2011-7-14

tran(瞬态分析) (瞬态分析)

2011-7-14

ac(交流分析) 是分析电路性能随 着运行频率变化而 变化的仿真。 既可以对频率进 行扫描也可以在某个 频率下进行对其它变 量的扫描。

2011-7-14

Variables菜单

包括Edit等子菜单项。 可以对变量进行添加、 删除、查找、复制等操 作。变量variables既可 以是电路中元器件的某 一个参量,也可以是一 个表达式。变量将在参 量扫描parametric analysis时用到。

集成电路设计CAD_EDA工具实用教程2-Spice_Spectre

选择所要 模拟的线 路图

选择模拟使用 的模型一般有 cdsSpice hspiceS spectre等

设置模拟 时的温度

设置库文件 的路径和仿 真方式

设置仿真的 环境 (后仿真时 需设置)

2017/8/11

共79页

25

Analyses菜单

选择模拟类型。Spectre的 分析有很多种,如右图, 最基本的有 tran(瞬态分析) dc(直流分析) ac(交流分析)。

2017/8/11

共79页

9

方法二

1、安装winvnc软件 2、运行putty软件键入 用户名和密码,在提示 符处键入 vncserver命 令申请vnc端口 3、运行winvnc,填入 主机名称:端口号码

2017/8/11

共79页

10

二、建立可进行SPECTRE模拟 的单元文件

主窗口分为信息窗口 CIW、命令行以及主 菜单。信息窗口会给 出一些系统信息(如 出错信息,程序运行 情况等)。在命令行 中可以输入某些命令。

12.Wire(Wide) [

s c 13.Wire Name 14.Pin 15.Cmd Options 16.Repeat l p

4.Zoom out by 2

5.Stretch 6.Copy

7.Delete

8.Undo 9.Property 10.Instance

2017/8/11

Del

q i

2017/8/11

共79页

26

tran(瞬态分析)

2017/8/11

共79页

27

dc(直流分析)

dc(直流分析)可以在 直流条件下对 temperature,Design Variable,Component Parameter,Model Parameter进行扫描仿真 举例:对温度的扫描(测 量温度系数) 电路随电源电压变化的 变化曲线等

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

Designers-Guide to Spice and Spectre— Ken Kundert, 19951.1 绪论1. 为什么要读这本书?① 该书是介于算法和教你如何操作软件之间的一本书,可以帮助你更好的使用Simulator 的设置。

② Simulator 仿出的结果可靠不?精确不?是否收敛?应该如何处理,如何设置? ③ 读完这本书,你应该会:1) Simulator 如何计算结果?2) Simulator 会产生何种错误?如何识别?3) 如何提高仿真精度?4) 如何克服不收敛的情况?5) 对于一些特殊电路,会产生什么错误?如何识别?6) 明白仿真器里设置convergence ,error control 的一些重要参数7) 能知道仿真器的错误信息出在什么地方,如何解决?2. 电路仿真软件的发展历史① 直接方法:求出电路的微分方程组,用数值积分方法差分化,然后用牛顿迭代法求解非线性代数方程组。

⇒是最准确,可靠,最通用的方法② Explicit integration methods ⇒方法问题很多③ relaxiton methods ⇒方法问题很多3. Spice Options① Global Options:Abstol :控制电流,默认为1pAVntol :控制电压,默认为1uVReltol :相对误差,对于牛顿收敛准则和截断误差准则同时起作用,默认10-3,对于重要电路,这个应该设置小一些,比如说10-5或者10-6Gmin :防止非线性器件关断后的浮空节点,默认为10-12 Ω-1Limpts ,Pivrel ,Pivtol :无用处② DC Analysis Options:ltl1:DC 工作点最大牛顿迭代次数,默认100ltl2:DC Sweep 最大牛顿迭代次数,默认50ltl6:Source Stepping 的最大步长数增加以上3个值,可以增加DC 牛顿迭代收敛,但是会降低速度。

③ Transient Analysis Options:()()()max n npred n Q t Q t Trtol reltol Q Chgtol α−<⋅⋅⋅+Chgtol:控制LTE,见上面式子ltl3:瞬态过程最小牛顿迭代次数,默认为4ltl4:瞬态过程最大牛顿迭代次数,默认为10ltl5:整个瞬态过程总的牛顿迭代次数的最大值,默认为5000lvltim:设置时间步长控制算法。

lvltim=1,不使用LTE控制步长;lvltim=2,使用LTE控制步长。

默认为2Maxord:Gear的阶数,默认2,最高6。

建议不要使用高阶Gear方法。

Method:可选择Trapezoidal和GearTmax:默认Tmax=(Tstop−Tstart)/50,同时Tmax不超过最短传输线的延迟时间。

这个参数一般应该设小一些,具体如何设置看本文的傅利叶分析一章。

Tstep:对傅利叶分析有影响。

对结果波形有影响。

Trtol:默认为7,不允许变小,只能不变或者变大。

见本文瞬态分析一章。

Uic:Uic=0(spice默认)相当于skipdc=no(spectre默认),仿真器计算DC工作点,当有接地电感时,这个会导致电感中大电流和瞬态初始的大电压。

Uic=1相当于skipdc=yes,不计算工作点,按照规定设置工作点。

这个的一般问题是会导致初始不连续。

增加ltl4可以帮助瞬态牛顿迭代过程的收敛。

4.Spectre Options①Global Options:Approx 允许Cadence对器件的模型公式做小的近似,可以加快仿真速度Diagnose 可以帮助诊断电路,默认是关闭的。

因此,可以显示仿真过程中的一些不寻常的事件,帮助收敛。

推荐打开。

Gmin 防止非线性器件关断后的浮空节点,默认为10-12 Ω-1Homotopy 使用连续性方法计算DC工作点或者瞬态仿真的初始值。

可以选择none,gmin,source,ptran,dptran,all。

默认值是all,也就是使用任何可以选择的方法实现收敛。

一般all是最好的,所以这个选项不要动。

控制电压和电流,和spice一样。

iabstol,vabstolReltol 通用误差控制,非常的常用和重要。

limit 帮助牛顿迭代收敛的辅助算法。

可选择dev,delta,log。

默认是dev,即指定限制的是device。

这个一般不要动。

Macromodels 默认是no。

当仿真宏模型时,选择yes,可以帮助收敛,可以容忍宏模型仿真中出现的一些不连续和怪异的事情。

Opptcheck 检查电路中每个器件的一些参数和电压电流是否超过允许范围,会报warning。

Pivabs 控制Jacobian距阵的一个量。

默认值为0。

Pivotdc 控制Jacobian距阵的一个量,默认是disable。

Pivrel 控制Jacobian距阵的一个量,默认是10-3。

rforce 用在nodesets,nodeforces,initial condition s时候。

如果rforce的出现引起初始偏置不准确,那么可以减小rforce。

注:在nodesets,nodeforces,initial conditions情况下,都要使用rforce进行偏置。

②DC Analysis Options:Check 检查器件的工作参数是否超出soft limits的范围,和opptcheck基本相同的作用forcespectre中的一个新概念,类似与tran中的initial conditon,强制限定节点电压或者支路电流。

目的是给出一个独立的解,因此该解一般是不平衡的。

有4个选项:none,node,dev,all,默认是none,也就是不强制限定任何节点电压和支路电流,电路的工作点完全由求解方程得到。

force=none 不强制限定任何节点电压和支路电流。

force=node 采用Initial conditon中设置的值强制限定节点电压和支路电流。

force=dev 采用device中设置的值强制限定节点电压和支路电流。

比如说电容初始电压和电感初始电流。

force=all 同时采用Initial conditon中和device中设置的值强制限定节点电压和支路电流。

这里会有一个问题,当选择force=all的时候,Initial conditon中和device中设置的值会不会冲突?比如说电容电压和节点电压。

实验结果是spectre会报warning,说两个值不一致,然后忽略掉Initialconditon而采用device中设置的值。

homotopy DC中的homotopy会覆盖Global中的homotopy,但作用是一样的。

Maxiters DC分析中牛顿迭代的最大次数,默认150,一般不需要改。

Maxsteps DC分析中当采用homotopy时最大步长数,默认10000,不需要修改。

Readforce 采用文件的形式定义nodeforce。

可以手动定义,也可以采用spectre仿真出的文件。

Readns 采用文件的形式定义nodesets。

可以手动定义,也可以采用spectre仿真出的文件。

Restart 默认值是restart=yes,但当需要进行一系列仿真(比如说ac,dc,tran等)的时候restart=no会有用处。

一般不要动这个选项。

不管是设置restart=yes还是no,spectre都照样计算初始的工作点,唯一不同的是牛顿迭代的初始起点不一样罢了。

注:restart和prevoppoint(ac,xf,sp,stb,zp等),skipdc(tran)是不一样的。

ac仿真中的prevoppoint=yes表示强制不进行初始dc工作点计算,直接采用前面某个仿真的最后结果作为ac的初始工作点。

tran仿真中的skipdc=yes表示强制不进行初始dc工作点计算,直接采用给定的initialcondition作为初始工作点,没有给定initial condition的认为是0。

而restart=yes,no只是影响牛顿迭代的初始起点的取法,spectre还是照样计算初始的dc工作点。

write dc分析牛顿迭代的初始点存储(initial guess)writefinal dc分析牛顿迭代的最终值存储(final value)注:DC分析的write和write final的文件spectre.dic,spectre.dfc可以作为readns,readforce,readic使用。

③Transient Analysis OptionsCmin 指定每个节点的最小电容,默认值为0。

但当出现收敛问题时候,可以把Cmin设为1fF左右,帮助收敛。

Errpreset 可以选择conservative,moderate,liberal。

详细说明见后面。

Ic和dc中的force功能相似,用于tran中。

有4个选项dc,node,dev,all,默认是all,这个和dc中的force默认是none是不一样的。

Ic=dc 求解dc的值作为Ic(也就是不采用用户设置的初始值)Ic=node 采用Initial conditon中设置的值作为初始值Ic=dev 采用device中设置的值作为初始值。

比如说电容初始电压和电感初始电流。

Ic=all 同时采用Initial conditon中和device中设置的值作为初始值。

这里会有一个问题,当选择Ic=all(也就是默认状态)的时候,Initial conditon中和device中设置的值会不会冲突?比如说电容电压和节点电压。

实验结果是spectre会报warning,说两个值不一致,然后忽略掉Initialconditon而采用device中设置的值。

(这个和dc中的force=all是一样的)Iteratio 和spice中的Trtol功能一样,控制LTE,默认值取决于errpreset。

具体用法见后面。

Maxiters 瞬态分析牛顿迭代的最大次数。

对于一些连续性较差的电路(比如说含有宏模型),增加Maxiters可以增加收敛性。

默认值为5,推荐值为50。

Maxstep 指定最大步长。

一般来说,要得到较好的精度,首先得减小reltol,然后指定maxstep。

但是当具有谷底效应的时候(比如说osc的起振过程),reltol不能有效的控制步长,此时步长完全由maxstep决定,才能得到较好的结果。

Method 数值积分方法:euler,trap,traponly,gear2,gear2only,trapgear2Readic 类似于dc分析中的readforce。