update of Quartus II_Version chinese_new

第2章_Quartus_II开发环境的使用

第2章_Quartus_II开发环境的使用Quartus II是一款由英特尔公司开发的集成电路设计软件,广泛应用于数字电路设计和可编程逻辑设备(PLD)的开发环境。

本章将介绍Quartus II开发环境的使用方法,并详细讲解其主要功能和操作流程。

首先,打开Quartus II软件,点击“文件”菜单,然后选择“新建项目”选项。

在出现的对话框中,输入项目名称和存储位置,并选择FPGA芯片型号。

点击“下一步”按钮,然后选择项目类型(一般为“普通VHDL项目”或“普通Verilog项目”),点击“下一步”按钮即可完成项目创建。

接下来,我们需要向项目中添加源文件。

点击“项目”菜单,然后选择“添加文件”选项。

在出现的对话框中,选择需要添加的源文件,点击“确定”按钮。

如果项目中有多个源文件,可以重复操作多次。

在项目中添加源文件后,我们需要进行编译。

点击“编译”菜单,然后选择“编译项目”选项。

Quartus II将对项目中的源文件进行语法检查和综合,并生成目标设备可执行文件。

接下来,我们需要进行功能仿真。

点击“工具”菜单,然后选择“RTL仿真器”选项。

在出现的对话框中,选择仿真源文件和仿真时长,点击“确定”按钮。

Quartus II将对源文件进行仿真,并生成波形图。

波形图生成后,我们可以对设计进行优化。

点击“工具”菜单,然后选择“组合逻辑优化器”选项。

在出现的对话框中,选择设计文件和优化选项,点击“确定”按钮。

Quartus II将对设计进行优化,并生成优化后的电路文件。

优化后的设计可以进行布局布线。

点击“工具”菜单,然后选择“物理编译器”选项。

在出现的对话框中,选择物理约束和布局布线选项,点击“确定”按钮。

Quartus II将根据物理约束对设计进行布局布线,并生成布局布线后的电路文件和报告。

布局布线完成后,我们可以进行时序分析。

点击“工具”菜单,然后选择“时序分析器”选项。

在出现的对话框中,选择设计文件和时钟约束,点击“确定”按钮。

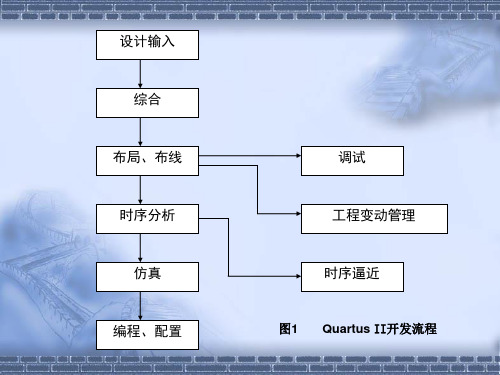

QuartusII软件使用及设计流程

Quartus II 设计流程

一、 设计输入

1.建立工程Project

任何一项设计都是一项工程(Project),都必须首先为 此工程建立一个放置与此工程相关的所有设计文件的文件 夹。此文件夹将被EDA软件默认为工作库(Work Library)。一般,不同的设计项目最好放在不同的文件夹 中,而同一工程的所有文件都必须放在同一文件夹中。

(2)选择元件。在原理图编辑窗中的任何一个位置上双

击鼠标的左键将跳出一个元件选择窗。

参数可设置的强函数元件库

MAX+plus库

基本逻辑元件库

基本逻辑元件库中的元件

由此输入所需要的元件名

(3)连接各元器件并命名。

在图1-39中,将光标移到input右侧,待变成十字形光标 时,按下鼠标左键(或选中工具栏中的 工具,光标自动 会变成十字形的连线状态),再将光标移动到异或门的左 侧,待连接点上出现蓝色的小方块后释放鼠标左键,即可 看到input和异或门之间有一条连线生成。 重复上面的方法将1-39图中各种符号连接起来,如图1-40 所示。

(4)第三方工 具选择。 如图1-7所示ቤተ መጻሕፍቲ ባይዱ 用户可以选择所 用到的第三方工 具,比如 ModleSim、 Synplify等。在 本例中并没有调 用第三方工具, 可以都不选.

(5)确认信息对话框。 图1-8所示。建立的工程的名称、选择的器件和 选择的第三方工具等信息,如果无误的话就可 以单击“Finish”按钮,弹出如图1-9所示的窗口, 在资源管理窗口可以看到新建的工程名称 half_add。

(1)打开建立新工程管理窗。选择菜单File→New Preject Wizard 命令,即弹出“工程设置”对话框(图1-3),以 此来建立新的工程。

Quartus II 中文注释乱码解决办法

Quartus II 中文注释乱码解决办法

2015-02-10

有些时候我们用Quartus II 打开不同版本创建的工程文件时,往往会出现下列提示

点Yes后,Quartus II 会自动把文件转换成我们安装的版本。

但是却出现了下图中糟糕的情况,我们发现中文注释变成了乱码,影响到了我们阅读代码的心情。

这点,相信很多刚学FPGA的新人们,热衷于下载代码例程学习时,都有遇到到这样的情况。

造成这种乱码的原因是,在Quartus II版本升级时,更换了编码标准Quartus II 11.0 以下的版本使用的是ANSI编码,而 12.0 到更新的版本14.0,则是使用UTF-8编码。

知道了这个原因后,我们就很容易想出解决办法了。

办法很简单,如下所示:

用记事本或者notepad++打开对应有乱码的.v文件,另存为UTF-8编码的文件,并保存。

注意如果安装使用的是11.0以下(包括11.0sp1)版本的Quartus II,想将UTF-8编码的转换成ANSI编码,中文仍会乱码。

所以建议还是使用较新版本的Quartus II更加省事。

转换后重新打开效果如图:。

Quartus_II的安装和使用说明 (1)

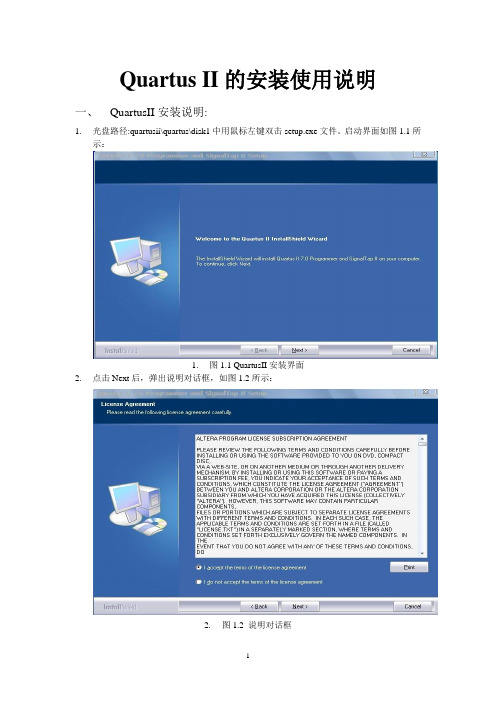

Quartus II的安装使用说明一、QuartusII安装说明:1.光盘路径:quartusii\quartus\disk1中用鼠标左键双击setup.exe文件。

启动界面如图1.1所示:1.图1.1 QuartusII安装界面2.点击Next后,弹出说明对话框,如图1.2所示:2.图1.2 说明对话框3.继续点击Next按钮后,弹出如图1.3所示的对话框,在上面空白处输入用户名,下面的输入公司的名字,这个可以任意填写。

写好后Next按钮编程可选状态。

(我的安装软件用户名默认为微软用户,公司的名字默认为微软中国)3.图1.3 用户信息输入对话框4.按下Next按钮后,进入安装路径选择界面,如图1.4所示。

(建议安装在默认的路径)5.图1.4 安装路径选择对话框选择好安装路径之后,点击Next按钮之后会看见相关的安装信息,一直点击Next按钮知道进入安装过程。

安装之后会弹出一个结束对话框,点击finish按钮,完成安装。

二、Quartus II软件的授权1.授权过程是将光盘路径:quartusii7\Altera-Quartus_V7_Win_Crack中的license.dat文件复制到安装目录下。

2.还有在这个路径下的sys_cpt.dll文件复制到安装目录下的bin的文件夹里。

3.在开始菜单栏,选择运行,输入cmd,按回车弹出如下图的对话框所示4.输入ipconfig/all,弹出如下图的对话框所示5.用红色圈起来的是你自己电脑的网卡号。

6.以记事本方式打开license,替换你的网卡号进去。

7.打开QuartusII,导入license.dat菜单下tools/license.setup。

三、QuartusII软件的使用说明主界面由3个子窗口组成,分别是设计输入编辑窗口(完成设计描述源文件的编辑)、消息窗口(编译/仿真过程的消息说明)和工程浏览窗口(快速浏览工程的各描述文件)。

图1.6 Quartus II的系统主界面1.设计输入Quartus II支持多种设计输入方法,即允许用户使用多种方法描述设计,常用的设计输入方式有:原理图输入,文本输入和第三方EDA工具输入。

Quartus_II使用教程-完整实例之欧阳文创编

Quartus Ⅱ入门教程时间:2021.03.12创作:欧阳文(一个Verilog 程序的编译和功能仿真)Quartus Ⅱ是Altera 公司推出的专业EDA 工具,支持原理图输入、硬件描述语言的输入等多种输入方式。

硬件描述语言的输入方式是利用类似高级程序的设计方法来设计出数字系统。

接下来我们对这种智能的EDA 工具进行初步的学习。

使大家以后的数字系统设计更加容易上手。

第一步:打开软件快捷工具栏信息栏菜单栏工作区资源管理窗口任务管理窗口●快捷工具栏:提供设置(setting ),编译(compile )等快捷方式,方便用户使用,用户也可以在菜单栏的下拉菜单找到相应的选项。

●菜单栏:软件所有功能的控制选项都可以在其下拉菜单中找到。

●信息栏:编译或者综合整个过程的详细信息显示窗口,包括编译通过信息和报错信息。

第二步:新建工程(file>new Project Wizard )1工程名称:2添加已有文件(没有已有文件的直接跳过next ) 3选择芯片型号(我们选择MAX3000A 系列下的EPM3256AQC208-所建工程的保存路径工程名称顶层模块名(芯片级设计为实体名),要求与工程名称相同如果有已经存在的文件就在该过程中添加,软件将直接将用户所添加的文件添加到工程中。

10芯片)(注:如果不下载到开发板上进行测试,这一步可以不用设置)4选择仿真,综合工具(第一次实验全部利用quartus 做,三项都选None ,然后next )所选的芯片的系列型号快速搜索所需的芯片选择芯片5工程建立完成(点finish)选择第三方综合工具,如果使用Quartus内部综合工具则选择none选择第三方仿真工具,如果使用Quartus内部仿真工具则选择none选择时序分析仪工程建立完成,该窗口显示所建立工程所有的芯片,其他第三方EDA工具选择情况,以及模块名等等信息。

第三步:添加文件(file>new>VHDL file),新建完成之后要先保存。

图解Quartus II使用教程

图解Quartus2使用教程编译程序:file---new---VHDL file-----okBy:酱油跑龙套编译程序---点保存---选择文件夹----修改文件名为of之前内容(注意大小写,保持相同)----点保存By:酱油跑龙套之后弹出建立工程的对话框,选…------选中文件,点打开,再添加By:酱油跑龙套Next之后按如下选择By:酱油跑龙套点finish---然后编译By:酱油跑龙套之后等待弹出编译成功的对话框,点确定。

编译文件完成By:酱油跑龙套原理图文件---左上窗口点file----选中文件右键----创建@¥#……¥By:酱油跑龙套创建原理图文件By:酱油跑龙套加入工程元件By:酱油跑龙套加入输入输出文件By:酱油跑龙套修改输入输出名字(强调方括号,中间两点)By:酱油跑龙套点保存(这个名字无要求)---设置顶层文件----点编译---弹出编译成功的对话框---点确定----原理图文件完成By:酱油跑龙套时序图文件,新建文件By:酱油跑龙套Edit---end timeBy:酱油跑龙套一般为55usBy:酱油跑龙套在时序图中加入引脚By:酱油跑龙套By:酱油跑龙套By:酱油跑龙套之后可以设置输入的高低电平,以及时钟信号By:酱油跑龙套保存,编译,名字无影响,编译成功By:酱油跑龙套●程序下载——pins●By:酱油跑龙套设置硬件引脚By:酱油跑龙套插上usb线后,会安装驱动,按默认安装就好连接成功后选择下载By:酱油跑龙套驱动安装成功后,点击start,下载完成后测试以上所有原文来自天津工业大学:酱油跑龙套By:酱油跑龙套。

QUARTUSII使用

在菜单中选择Tools->Simulator Tool

选择仿真类型(Functional),并创建功 能仿真网表(点击绿色荐头所指按钮)

功 能 仿 真

此处应为刚才保 存的波形文件

功 能 仿 真

网表创建完后点击Start运行,运 行完成后关闭此窗口.

功 能 仿 真 点击此处,开始仿真

运行结束后会弹出功能仿真的波形 报告,观察仿真波形并验证

QUARTUS II使用说明

创建一个新的工程

输入工程路径

输入工程名和实体 名,必须一样

点击NEXT

点击NEXT

点击NEXT

点击NEXT

点击结束

点击创建新 文件图标

选择新文件 类型为 VHDL,然 后点击OK

在编辑窗口录入源文件

顶层文件的实体名 必须和工程名一致

保存源文件

点击编译图 标,开始编译

给输入信号添ቤተ መጻሕፍቲ ባይዱ激励。如图按住鼠标左键不放,拖动一 定距离,再将鼠标放在图中的浅兰色区域双击左键,这 时会弹出一个窗口,在该窗口中输入波形值(位数据输 入0或1,位矢量输二进制序列)并点击ok。

这时就给A端口加上了一段高电平,依此 方法给所有的输入都加上指定激励。

将输入的激励都加上以后,保存该波形文件

在编译过程中如果有错会给出错误提示,否则 显示编译成功

创建波形文件(还是创建一个新文件,并选 择类型)

选中波形文件,点 击OK

一个空的波形文件被建立

波形文件窗口

按快捷键Alt+1,弹出如下窗口,按图中所示设置 好后,点击List.所有端口信号会被列出来.

如图,将输入输出信号拖动到波形文件窗口

在菜单中选择Tools->Simulator Tool弹 出下面的窗口,改变仿真类型(选Timing), 点击Start运行.运行结束后,关闭该窗口.

Altera公司Quartus II 中英文菜单对照

file文件new新建open打开close关闭new project wizard 新建项目向导open project打开项目convert MAX+PLUS project转化为MAX+PLUS工程save project保存工程close project关闭工程save保存save as.... 另存为...save current report section as保存当前部分的报告为file properties文件属性create/update生成/更新----------------------------export输出convert programming file转换编程文件page setup页面设置print preview打印预览print打印recent files最近的文档 -------文件路径recent project最近的项目------文件路径exit退出edit编辑undo撤销redo重做cut剪切copy复制paste粘贴delete删除select all全选find...查找find next查找下一个find matching delimiter找到匹配的定界符replace代替go to转到increase indent增加缩进decrease indent减少缩进insert page break插入分页符insert file插入文件insert template插入模板set bookmark设置书签delete bookmark删除书签jump to bookmark跳转到书签View视图utility windows实用程序窗口;project navigator项目领航员;node finder节点发现者;Tcl console集团控制台;messages信息,便条status .地位,身份;情形,状况;change manager变更经理full screen全屏project工程add current file to project将当前文件添加到工程add\remove file in project...在工程中添加或删除文件revisions...版本信息copy project.. 复制工程archive project..工程档案restore archived project .. 复位工程import database..导入数据库export database...输出数据库import design partition ..导入设计分割export project as design partition .输出设计分割generate bottom-up design partiti生成底层设计分割脚本generate tcl file for project ..生成tcl文件generate powerplay early power e生成早期电源估测文件organize quartus 2 setting .. quar初始化设置hardcopy utilities硬拷贝功用项目hardcopy timing optimization wiz硬拷贝定时优化专项hardcopy file wizard硬拷贝文件向导locate位于locate in assignment editor在任务编辑器设置locate in pin planner在管脚设计器设置set as top-leve entity file设置为顶层文件hierarchy结构组织Assignmen任务Device设备Pins引脚Timing analysis settings时序分析设置EDA tool settings EDA 工具的设置Settings设置Timing wizard 时序向导Assignments editor分配编辑器Pin planner引脚规划Remove Assignments删除指定Demote Assignments降低指定Back-annotate Assignments反标作业Import assignment导入任务Export assignment到处任务Assignment (time) groups分配时间组Timing closure floorplan时序收敛平面布置图Logiclock region Window逻辑锁定区域窗口Design partition Window设计分区窗口PROCESS调试stop process停止进程start compilation开始编辑analyze current file分析当前的文件start开始start EDA physical synthesis开始的EDA物理综合Update Memory Initialization File更新存储器初始化文件Compilation Report 编译报告Start Compilation & Simulation开始编译与仿真Generate Functionl Simulation Ne模拟网表生成功能Start Simulation开始模拟Simulation Debug仿真调试Breakpoints断点Tools工具eda simulation tool EDA仿真工具run eda rtl simulation运行RTL仿真run eda gate level simulation运行门级仿真run eda timing analysis tool运行EDA时序分析工具launch design space explorer启动工作环境管理器Advanced List Paths高级列表路径TimeQuest Timing Analyzer TimeQuest时序分析仪Advisors顾问Resource Optimization Advisor资源优化向导Timing Optimization Advisor时序优化向导Power Optimization Advisor电源优化向导Chip Editor芯片编辑器Netlist Viewers 网络表查看器RTL Viewer RTL查看器Technology Map Viewer技术映射查看器State Machine Viewer状态机查看器SignalTap II Logic Analyzer SignalTap II逻辑分析仪IN-System Memory Content Edito在系统内存内容编辑Logic Analyzer Interface Editor逻辑分析仪接口编辑器Signal Probe pins引脚信号探头Programmer编程器MegaWizard Plug-In Manager MegaWizard插件管理器SOPC BuiLder SOPC生成器tcl Scripts TCL脚本Customize定制options 选项License Setup许可证设置Windows窗口New windows新建窗口Close All全部关闭Cascade层叠Tile Horizontally水平排列Tile Vertically 垂直排列Help帮助Index索引Search查找Contents概述Messages留言板Glossary术语表Megafunctions/LPM LPM函数Devices & Adapters器件和适配器EDA InerfacesTutorial教程PDF tutorials PDF教程MAX+PLUS II Quick Start Guide MAX+PLUS II快速启动向导What’s New什么是新建Readme File 自述文件MegaCore IP Library Readme大型核心IP库自述Release Notes发布通知How to Use Help如何使用“帮助”Contacting Altera Altera联机Altera on the web Altera网络服务About Quartus II关于Quartus IIAX+PLUS工程告为--------------------------------create HDL design file for current file为当前文件生成HDL设计文件----create symbol file for current file为当前文件生成符号文件----create AHDL include file for current file为当前文件生成AHDL包含库文件----create design file from selected block从选择的块生成设计文件----update design file from selected block从选择的块更新设计文件----create signaltap II file from design instance从设计实例中生成signaltap II文件----create signaltap II list file生成signaltap II文件清单----create JAM 、SVF or ISC file生成JAM、SVF 或 ISC文件----create/update IPS file.. 生成/更新IPS文件 -------文件路径------文件路径,状况;件添加到工程添加或删除文件设计分割脚本电源估测文件hardcopy 2 utilities硬拷贝功用项目 2create\overwrite hardcopy 2 companion revisio创建\覆盖硬拷贝2 同步修订set current hardcopy 2 companion revision设置当前硬拷贝2 同步修订compare hardcopy 2 companion revision比较硬拷贝2 同步修订generate hardcopy 2 handoff report生成硬拷贝2 同步报告archive hardcopy 2 file文件归档硬拷贝hardcopy 2 advisor硬拷贝2的设计器start analysis & elaboration开始分析和阐述start analysis & synthesis开始分析和综合start fitter开始钳工start assembler开始汇编start timing analyzer开始计时仪start timequest timing analyzer TimeQuest时序分析仪启动start EDA netlist writer作家的EDA网表开始start design assistant开始辅助设计start powerplay power analyzer启动PowerPlay功耗分析仪start signalprobe compilation开始signalprobe编译start I/O assignment analysis启动I/O分配分析start timing analyzer (fast timing model)启动计时仪(快速定时模式)start early timing estimate起步早的时间估计start timing constraint check开始计时约束检查start check & save all netlist changes开始办理登机及保存所有网表变化start partition merge启动分区合并start VQM writer作家开始VQMstart equation writer(post-synthesis)开始方程作家(后合成)start equation writer(post-fitting)开始方程作家(后接头)start test bench template writer开始测试台模板作家start EDA synthesis启动EDA综合文件Embedded Memory嵌入式存储器Update Simulator with Current Memory Conte更新模拟器与当前的内存内容Update Current Memory with Simulation Data更新当前的内存仿真数据Last Simulation Vector Outputs最后仿真矢量输出Current Vector Inputs输入电流矢量Overwrite Vector Inputs with Simulation Outp覆盖向量与模拟输入输出Compiler Tool编译工具Simulator Tool仿真工具Timing Analyzer Tool时序分析工具PowerPlay power Analyzer Tool PowerPlay功耗分析工具时序分析工具时序分析仪逻辑分析仪辑器插件管理器PDF tutorials for VHDL usersPDF tutorials for Verilog HDL users快速启动向导Quartus II Home Page Quartus II首页Download Quartus II Updates下载Quartus II更新Download PCB Footpints下载pcb封装Training培训Quartus II Service Request Quartus II服务需求TroubleshootersSOPC Builder Home Page SOPC团队首页Altera IP MagaStore Page Altera IP在线商店Altera Home Page Altera首页New Quartus II Information最新Quartus II消息Quartus II Handbook Quartus II手册。

QuartusII安装及下载步骤

QuartusII安装及下载步骤⽬录1. QuartusII 12.0 安装 (3)2. 下载FPGA程序步骤 (33)3. 下载新程序注意项 (42)1. QuartusII 12.0 安装1、在盘⾥找到并双击“12.0_178_quartus_windows.exe”,弹出如下窗⼝,点击“Browse…”选择路径(路径不要有汉字和空格,后⾯也⼀样),可以保持默认路径(若保持默认路径的话,后⾯的也都保持默认路径),然后点击“Install”,2、开始安装,3、安装迚程结束后会弹出如下窗⼝,直接点击“Next”,4、勾选“I agree…”,再点击“Next”,5、点击“Browse…”选择和之前相同的路径,默认路径,点击“Next”,⼀般要安装在盘的跟⽬录(如:D:\altera E:\altera等)6、显⽰安装所需空间和可⽤空间(若可⽤空间不够的话,请退出重新选择安装路径),点击“Next”,7、点击“Next”,8、开始安装,9、需要等待⼏分钟,根据电脑配置不同,安装时间会有所不同,出现如下界⾯后,点击“Yes”,11、点击“Finish”,安装完quartus软件后,需要安装芯⽚的驱动来⽀持各款芯⽚13、双击“12.0_178_devices_cyclone_max_legacy_windows.exe”,弹出如下界⾯,“Browse…”点击选择和之前相同的路径,戒默认路径,“Install”点击,14、开始安装,15、直接“Next”,16、勾选“I agree…”,点击“Next”,17、点击“Browse…”选择和之前同相同的路径,戒默认路径,点击“Next”,选择和Quartus 相同的路径,⼀般会⾃动选择。

18、显⽰安装所需空间和可⽤空间,点“Next”,这⾥如⽆特别需要,只选择cyclone IV系列的器具即可,节省盘空间。

19、直接“Next”,20、开始安装,21、完成后,弹出如下界⾯,点击“Yes”,。

quartusII详细使用指南

3.2.1 Design Entry . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6 3.2.2 Cerate a Project . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6 3.2.3 Add Sources Files . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8 3.2.4 Compile . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9 3.2.5 Timing Analyze . . . . . . . .

QuartusII中文完整教程

Quartus II 的使用 (2)1 工程建立 (2)2 原理图的输入 (5)3 文本编辑(verilog) (15)4 波形仿真 (16)Quartus II 的使用在这里,首先用最简单的实例向读者展示使用Quartus II软件的全过程。

进入WINDOWS XP后,双击Quartus II图标,屏幕如图1.1所示。

图 1.1 Quartus II 管理器1.1 工程建立使用 New Project Wizard,可以为工程指定工作目录、分配工程名称以及指定最高层设计实体的名称。

还可以指定要在工程中使用的设计文件、其它源文件、用户库和 EDA 工具,以及目标器件系列和器件(也可以让Quartus II 软件自动选择器件)。

建立工程的步骤如下:(1)选择File菜单下New Project Wizard ,如图1.2所示。

图 1.2 建立项目的屏幕(2)输入工作目录和项目名称,如图1.3所示。

可以直接选择Finish,以下的设置过程可以在设计过程中完成。

图 1.3 项目目录和名称(3)加入已有的设计文件到项目,可以直接选择Next,设计文件可以在设计过程中加入,如图1.4所示。

图 1.4 加入设计文件(4)选择设计器件:选择仿真器和综合器类型(默认“None”为选择QuartusII自带的),选择目标芯片(开发板上的芯片类型),如图1.5所示。

图 1.5 选择器件(5)选择第三方EDA综合、仿真和时序分析工具(若都不选择,则使用QuartusII自带的所有设计工具)如图1.6所示。

图 1.6 选择EDA 工具(6)建立项目完成,显示项目概要,如图1.7所示。

图 1.7 项目概要工程建立后,若需要新增设计文件,可以通过 Project/Add_Remove……在工程中添加新建立的设计文件,也可以删除不需要的设计文件。

编译时将按此选项卡中显示文件处理。

注意:通过工程向导做作的设置都是可以在Assignments/settings下再进行修改的。

QuartusII中文完整教程

Quartus II 的使用 (1)1 工程建立 (1)2 原理图的输入 (5)3 文本编辑(verilog) (13)4 波形仿真 (15)Quartus II 的使用在这里,首先用最简单的实例向读者展示使用Quartus II软件的全过程。

进入WINDOWS XP后,双击Quartus II图标,屏幕如图1.1所示。

图 1.1 Quartus II 管理器1.1 工程建立使用New Project Wizard,可以为工程指定工作目录、分配工程名称以及指定最高层设计实体的名称。

还可以指定要在工程中使用的设计文件、其它源文件、用户库和EDA 工具,以及目标器件系列和器件(也可以让Quartus II 软件自动选择器件)。

建立工程的步骤如下:(1)选择File菜单下New Project Wizard ,如图1.2所示。

图 1.2 建立项目的屏幕(2)输入工作目录和项目名称,如图1.3所示。

可以直接选择Finish,以下的设置过程可以在设计过程中完成。

图 1.3 项目目录和名称(3)加入已有的设计文件到项目,可以直接选择Next,设计文件可以在设计过程中加入,如图1.4所示。

图 1.4 加入设计文件(4)选择设计器件:选择仿真器和综合器类型(默认“None”为选择QuartusII自带的),选择目标芯片(开发板上的芯片类型),如图1.5所示。

图 1.5 选择器件(5)选择第三方EDA综合、仿真和时序分析工具(若都不选择,则使用QuartusII自带的所有设计工具)如图1.6所示。

图 1.6 选择EDA 工具(6)建立项目完成,显示项目概要,如图1.7所示。

图 1.7 项目概要工程建立后,若需要新增设计文件,可以通过 Project/Add_Remove……在工程中添加新建立的设计文件,也可以删除不需要的设计文件。

编译时将按此选项卡中显示文件处理。

注意:通过工程向导做作的设置都是可以在Assignments/settings下再进行修改的。

QuartusII软件操作

Quartus II 软件操作

第二步 根据电路图综合电路 电路图输入到CAD系统之后,许多CAD工具会对其进行处

理。流程的第一步是使用综合工具,将电路图编译成逻辑表 达式,然后,电路综合的下一步是工艺映射,通过使用可用 的逻辑元件,确定每个逻辑表达式如何在目标芯片中实现。

使用编译器。选择Processing/Compile tool 命令,打 开对应窗口,共包括四个模块。分析与综合模块执行 Quartus II 中的综合步骤,它产生逻辑元件组成的一个电路。 装配模块(Fitter)模块决定芯片上各电路元件的精确布局。 其中综合模块产生的每个元件都将在芯片上实现。每个模块 也可以单独运行。也可以使用其他命令启动编译。编译完成 时,可以查看编译报告。出现错误时,点击错误信息,可以 突出显示错误出现的位置。

Quartus II 软件操作

第三步 对设计的电路进行仿真 Quartus II包含仿真工具,它

们用于仿真已设计电路的行为功能。 在电路仿真之前,必须先创建输入 波形文件。

1) 使用波形编辑器。 选择File/New命令,在弹出的对 话框中选择Vector Waveform File 选项,单击OK按钮。将文件 命名为example_schematic.vwf并保 存。

Quartus II 软件操作

① 功能仿真 选择Assignments/settings命令,打开settings窗口。

在该窗口的左面,单击Simulator项,在弹出的窗口中,选 择fuctional选项作为仿真模式。为了完成仿真器的设置, 需要选择Processing/Generate functional simulation Netlist命令。 Quartus II根据测试输入,产生 example_schematic.vwf文件中定义的输出。选择 Processing/start simulation(或使用快捷图标),开始 运行电路的功能仿真。仿真结束之后, Quartus II指出仿 真完成,并给出仿真报告。

EDA软件QuartusII安装步骤及补丁使用方法

QuartusII6.0安装手册一)安装软件1、选择quartusii_60_pc/disk1文件夹,运行安装向导: Install.exe;2、点击Install QuartusII and Related Software按钮, 进入欢迎界面,点击Next进入安装QuartusII软件的安装向导界面。

在这个安装向导界面中,选中QuartusII 6.0,其它项目不选,点击Next按钮,进入下一步。

3、在License Agreement对话框上选中I accept the terms of the License agreement选项,点击Next按钮,进入下一步。

4、在Custom information对话框上,输入用户信息,User Name:欣欣工作室,Company Name:, 点击Next按钮,进入下一步。

(注意姓名和公司可任填)5、在Choose Destination Location对话框上选择安装路径,也可使用默认路径。

确保硬盘上有足够的空间,点击Next按钮进入下一步。

6、在Setup Type对话框上选中Complete选项,点击Next按钮,进入下一步。

7、确认安装设置,点击Next按钮,安装向导开始复相关文件。

8、当向导提示需要disk2时,输入disk2\quartus的完整路径,点击OK按钮,继续安装。

9、在QuartusII Talkback对话框上,点击确定按钮继续安装。

10、在Installshield Wizard Complete对话框上,去掉Launch QuartusII 6.0选项,点击Finish按钮,完成安装。

11、回到安装向导主界面,点击Install Stand-Alone Programmer按钮,启动Programmer 和SignalTapII的安装向导。

在欢迎对话框上点击Next按钮,进入下一步。

12、在****** Agreement对话框上选中Accept the terms of the ****** agreement选项,点击Next按钮,进入下一步。

QuartusII中文完整教程

Quartus II 的使用 (1)1 工程建立 (1)2 原理图的输入 (5)3 文本编辑〔verilog〕 (14)4 波形仿真 (16)Quartus II 的使用在这里,首先用最简单的实例向读者展示使用Quartus II软件的全过程。

进入WINDOWS XP后,双击Quartus II图标,屏幕如图1.1所示。

图Quartus II 管理器工程建立使用New Project Wizard,可以为工程指定工作目录、分配工程名称以及指定最高层设计实体的名称。

还可以指定要在工程中使用的设计文件、其它源文件、用户库和EDA 工具,以及目标器件系列和器件〔也可以让Quartus II 软件自动选择器件〕。

建立工程的步骤如下:(1)选择File菜单下New Project Wizard ,如图1.2所示。

图 1.2 建立工程的屏幕(2)输入工作目录和工程名称,如图1.3所示。

可以直接选择Finish,以下的设置过程可以在设计过程中完成。

图 1.3 工程目录和名称(3)参加已有的设计文件到工程,可以直接选择Next,设计文件可以在设计过程中参加,如图1.4所示。

图 1.4 参加设计文件(4)选择设计器件:选择仿真器和综合器类型〔默认“None〞为选择QuartusII自带的〕,选择目标芯片〔开发板上的芯片类型〕,如图1.5所示。

图 1.5 选择器件(5)选择第三方EDA综合、仿真和时序分析工具〔假设都不选择,那么使用QuartusII自带的所有设计工具〕如图1.6所示。

图 1.6 选择EDA 工具(6)建立工程完成,显示工程概要,如图1.7所示。

图 1.7 工程概要工程建立后,假设需要新增设计文件,可以通过 Project/Add_Remove……在工程中添加新建立的设计文件,也可以删除不需要的设计文件。

编译时将按此选项卡中显示文件处理。

注意:通过工程向导做作的设置都是可以在Assignments/settings下再进行修改的。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

© 2001 Altera® Corporation 29新建项指南5. 加入设计文件

- Graphic (.BDF, .GDF) - AHDL - VHDL - Verilog - EDIF 注意: • 并不是该项目的目录下的所有文件都要 被加入 • 假如顶层设计和顶层文件的名字不一样 的话,一定要加入顶层文件的名字

原理图编辑方式:

输入设计模块和设计端口 - 从工具栏中输入 - 双击空白处产生 - 从菜单中产生:“Insert->Symbol…” 例如: Counter记数器

© 2001 Altera® Corporation 11

© 2001 Altera® Corporation 12

© 2001 Altera® Corporation 13

注意: 所有的项目设置中,除了项目名和顶层设计名不 一样之外,其它的设置都保留上一个项目的设置

© 2001 Altera® Corporation 33

编辑项目设置

改变项目的名字或顶层设计的名字

点击Rename 按钮 去改变项目的名字 或顶层设计的名字

© 2001 Altera® Corporation 34

© 2001 Altera® Corporation 19

© 2001 Altera® Corporation 20

© 2001 Altera® Corporation 21

© 2001 Altera® Corporation 22

© 2001 Altera® Corporation 23

© 2001 Altera® Corporation 45

编译设置 – 芯片和器件

1. 选择引脚号 2. 调用引脚查找器去查找引脚名 或类型 3. 增加到指定列表

© 2001 Altera® Corporation 46

编译设置 – 综合与配置

APEX™ 配置器: •PowerFit配置器 – 更好的Fmax和编译时间 – 对打包(Cliques)有限制 •标准配置器 – PTERM 模式 定时驱动式编译: •优化 I/O 引脚的延时 •优化 内部的延时

© 2001 Altera® Corporation 43

编辑编译选项

从下拉菜单中选择编 译设置

显示所有给编译模块的编 译设置

© 2001 Altera® Corporation 44

编译设置 – 芯片和器件

选择器件类型

说明器件和引脚选项 •概要 •配置 •下载文件 •不用的引脚 •双种用途的引脚 •电压值

– 第三方工具

• EDIF • HDL • VQM

– 或采用一些别的方法去优化和提高输入的灵活性:

• 混合设计格式 • 利用LPM和宏功能模块来加速设计输入

© 2001 Altera® Corporation 3

设计输入文件

Quartus II 模块编辑 Quartus II 文本编辑 Quartus II 内存编辑

编译设置指南

指定编译模快及设定名 字

•网表输出或完全编译? •优化速度或资源利用率? •削减接点名字?

© 2001 Altera® Corporation 41

编译设置指南

自动选择或给定器件? 选择一个器件

•运行延时分析? •运行仿真?

© 2001 Altera® Corporation 42

编译定义

Exemplar, Synopsys, Synplicity, etc...

.v, .vlg, .vhd, .vhdl, vqm Text 文件

Symbol 文件

Text 文件

Text 文件

Text 文件

由 Quartus II 产生

© 2001 Altera® Corporation 4

从第三方工具输入

双击空白处

© 2001 Altera® Corporation 14

© 2001 Altera® Corporation 15

© 2001 Altera® Corporation 16

© 2001 Altera® Corporation 17

© 2001 Altera® Corporation 18

打包

– 将选择好的逻辑模块放在一起来提高性能

I/O 标准 局部走线 单独的逻辑选项

– 利用Quartus II 的综合/配置的特殊选项,或ALTERA的器件特性s – 3 种类型

有参数限制的仿真

© 2001 Altera® Corporation 51

编译报告

包含了怎样将一个设计放到一个器件中的所有信息

© 2001 Altera® Corporation 36

© 2001 Altera® Corporation 37

© 2001 Altera® Corporation 38

© 2001 Altera® Corporation 39

Quartus II 编译

© 2001 Altera® Corporation 40

从工具栏中产生模块和输入端口

点击工具栏中的“模 块”来画一个图表

右键点击模块。选择 属性,从弹出的对话 框中输入端口信息。

© 2001 Altera® Corporation 8

模块编辑器- “智能” 连接

Quartus II 有 “智能” 模块连接和映射

– 如果连接不同模块时,两边端口的名字相同的话就不用标注出来 – 一个管道可以连接模块之间所有的普通 I/O

图表和原理图编辑器

该编辑器既可以编辑图表模块,又可以编辑原理图 图表模块编辑是主要的顶层设计的主要方法 原理图编辑是传统的设计输入方法 用户可以利用加入Quartus II 提供的LPMs,宏功能等涵数 以及用户自己的库涵数来设计 提供“智能”的模块链接和映射

© 2001 Altera® Corporation 5

配置组织器

3种类型的逻辑选项 - 只给单独的接点的选项 - 给接点和模块的选项 - 只给模块的选项 3. 点击 Add 去增 加一项新的设置 1. 点击,增加新的 配置

2. 选择一个已设定的配置

© 2001 Altera® Corporation 50

配置组织器的构成

定位 定时

– 增加定时设置来提高特性

EDA 驱动流程

EDA 工具驱动 Quartus II

© 2001 Altera® Corporation 27

文件驱动流程: 非内部链接

如果用一个非内部链接的 EDA 工具产生 VHDL, Verilog, EDIF 文 件, 就需要阐明 .lmf 文件来给定文件格式

菜单Project > EDA Tool Settings...

© 2001 Altera® Corporation 6

模块编辑器 – 产生一个新的文件

产生一个新的图表模块/原理图文件

菜单: File > New > Block/Schematic document

新建一个新 的文件

选择模块/原理图文档

© 2001 Altera® Corporation 7

模块编辑器- 设计模块

– – – – – – – – 器件使用统计 编译设置 底层显示 器件资源利用率 状态机的实现 方程式 延时分析结果 CPU 使用资源

这是一个只读的窗口

© 2001 Altera® Corporation 52

例如:Counter 记数器

流览并找到文件, 然后再加入

© 2001 Altera® Corporation 31

新建项目指南

列出项目名和目 录名字

7. 检查结果然后按 结束

© 2001 Altera® Corporation 32

项目菜单

编辑项目的设置t

– 增加/去除文件或库涵数

项目设置

– – – – HDL 类型界面 第三方EDA工具设计流程 定时设置 版本控制

编译类型

– 只是综合并输出网表 • 编译设计文件,综合产生门级代码 • 编译器只运行到综合这步就停止了 • 编译器只产生估算的延时数值 – 完全的编译,包括编译,网表输出,综合,配置器件 • 编译器除了完成以上的步骤,还要将设计配置到ALTERA的器件 中去 • 编译器根据器件特性产生真正的延时时间和给器件的配置文件

© 2001 Altera® Corporation 24

支持的第三方工具

综合工具 Leonardo Spectrum* Design Compiler FPGA Compiler II Standard* & Altera Edition* FPGA Express* Synplicity Synplify* 仿真工具 •ModelSim* •ModelSim OEM* •Cadence Verilog-XL •Innoveda BLAST •PrimeTime* •Synopsys VCS •Synopsys VSS

选择自定义 选择设置... 选择库涵数映射文 件 (lmf) 可以是 EDIF, VHDL, or Verilog

© 2001 Altera® Corporation 28

新建项目指南

1. 打开新建项目指南

2. 选择工作目录 3. 项目名称,可以是任何名字。 推荐使用和顶层设计名相同的名字.

4. 顶层设计 .名字必须和顶层文件名字相同

编辑项目设置

打开项目基本设置对话框

增加/去除项目文件

增加 - 找到文件 - 增加 去除 - 从列表中选择 - 去除

© 2001 Altera® Corporation 35

例如:Counter 记数器

产生一个Project 加入前面所产生的test_quartus.bdf 文件 Project创建完成

Quartus II 用户指南