74HC245中文资料

74HC245在LED显示中的应用

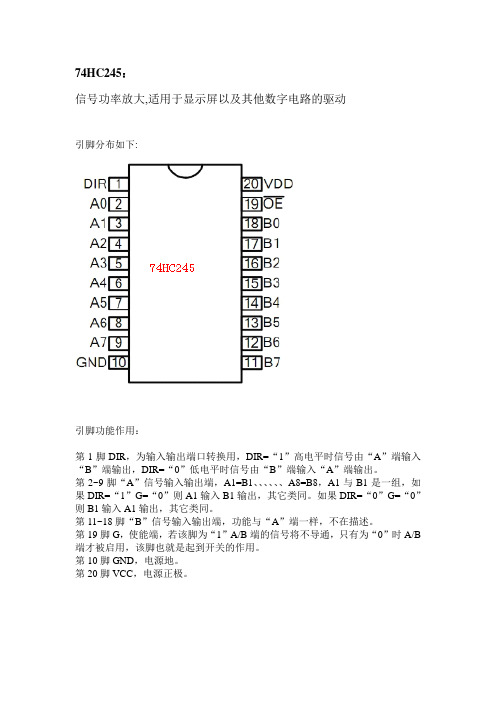

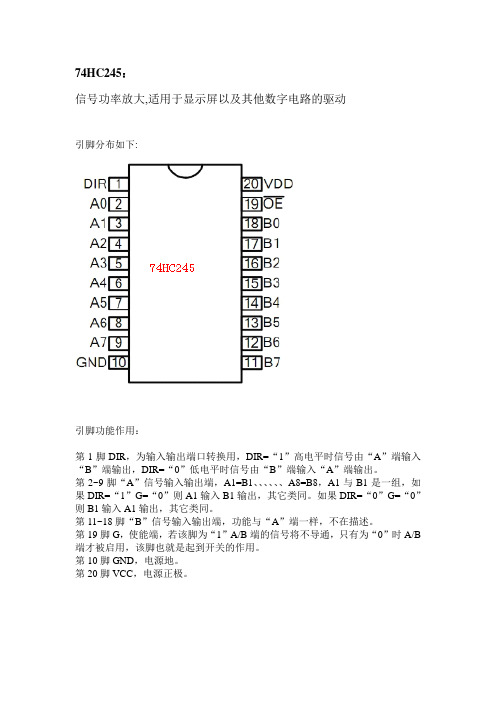

74HC245:

信号功率放大,适用于显示屏以及其他数字电路的驱动

引脚分布如下:

引脚功能作用:

第1脚DIR,为输入输出端口转换用,DIR=“1”高电平时信号由“A”端输入“B”端输出,DIR=“0”低电平时信号由“B”端输入“A”端输出。

第2~9脚“A”信号输入输出端,A1=B1、、、、、、A8=B8,A1与B1是一组,如果DIR=“1”G=“0”则A1输入B1输出,其它类同。

如果DIR=“0”G=“0”则B1输入A1输出,其它类同。

第11~18脚“B”信号输入输出端,功能与“A”端一样,不在描述。

第19脚G,使能端,若该脚为“1”A/B端的信号将不导通,只有为“0”时A/B 端才被启用,该脚也就是起到开关的作用。

第10脚GND,电源地。

第20脚VCC,电源正极。

在LED显示屏中,单元板/模组是由多块串接在一起的,而控制信号是比较弱的,在信号传递过程中需要将它的功率进行放大,74HC245作为一款8路总线收发器的作用就是将接收到的控制信号进行放大。

74hc245

74hc245目录74HC245简介:引脚定义:74HC245的作用:信号功率放大。

编辑本段74HC245简介:总线驱动器,典型的TTL型三态缓冲门电路。

由于单片机等CPU的数据/地址/控制总线端口都有一定的负载能力,如果负载超过其负载能力,一般应加驱动器。

另外,也可以使用74HC244等其他电路,74HC244比74HC245多了锁存器。

74HC245实物图:74HC245编辑本段引脚定义:第1脚DIR,为输入输出端口转换用,DIR=“1”高电平时信号由“A”端输入“B”端输出,DIR=“0”低电平时信号由“B”端输入“A”端输出。

±70 mAStorage Temperature Range 储存温度范围(TSTG)-65℃ to -150℃Power Dissipation (PD)功耗(Note 3)600 mWS.O. Package only500 mWLead Temperature (TL) (Soldering 10 seconds)260℃编辑本段74HC245的作用:信号功率放大。

第1脚DIR,为输入输出端口转换用,DIR=“1”高电平时信号由“A”端输入“B”端输出,DIR=“0”低电平时信号由“B”端输入“A”端输出。

第2~9脚“A”信号输入输出端,A1=B1﹑﹑﹑﹑﹑﹑A8=B8,A1与B1是一组,如果DIR=“1”G=“0”则A1输入B1输出,其它类同。

如果DIR=“0”G=“0”则B1输入A1输出,其它类同。

第11~18脚“B”信号输入输出端,功能与“A”端一样,不在描述。

第19脚G,使能端,若该脚为“1”A/B端的信号将不导通,只有为“0”时A/B端才被启用,该脚也就是起到开关的作用第10脚GND,电源地。

第20脚VCC,电源正极。

74HC04 的作用:6位反相器。

第七脚GND,电源地。

第14脚步VCC,电源正极信号由A端输入Y端反相输出,A1与Y1为一组,其它类推。

74HC245中文资料_数据手册_参数

74HC245八路巴士TRANCEIVER;三态 14.修订历史表13:修订记录文档ID发布日期数据表状态更改注意文档.数取代版本 74HC_HCT245_3 20050131产品数据表 - 9397 750 14502 74HC_HCT245_CNV_2莫迪科幻阳离子: ? 本数据表的格式经过重新设计以符 合新的演示文稿和飞利浦半导体的信息标准 ?第4节“订购信息”,第6节“固定信息”和第13节“包装大纲“修改为包含DHVQFN20 包. 74HC_HCT245_CNV_2 19930930产品SPECI FI CATION 9397 750 14502 ? 74HC245 NV 2005.保留所有权利. 74HC245产品数据表 2005年1月3日至31日 13的22飞利浦半导体 74HC245; 74HCT245八 路巴士TRANCEIVER;三态 12.波形测量点在表11中给出. V OL 和V OH 是输出负载时发生的典型电压输出下降.图5.输入(AN,BN) 输出(BN,AN)传播延迟和输出转换时间测量点在表11中给出. V OL 和V OH 是输出负载时发生的典型电压输出下降.图6. 3态输出 启用和禁用时间表11:测量点类型输入产量 74HC245保留所有权利.产品数据表 2005年1月3日至3月31日 13的22飞利浦半导体 74HC245; 74HCT245八路公交车三态波形测量点在表 11中给出. V OL 和V OH 是输出负载时发生的典型电压输出降.图5.输入(An,Bn)输出(Bn,An)传播延迟和输出转换时间测量点 在表11中给出. V OL 和V OH 是输出负载时发生的典型电压输出降.图6. 3状态输出使能和禁止时间表11:测量点类型输入产量 V M V M 74HC245 0.5V CC 0.5V CC 74HCT245 1.3 V 1.3 V 001aac433 t PLH t PHL VM V M 90% 10% V M V M Bn,输出 An,Bn输入 V 我 GND V OH V OL t TLH t THL 001aac479 t PLZ t PHZ输出残输出启用 90% 10%输出启用 OE输入 V 我 V CC V OL V OH GND GND V M t PZL t PZH V M V M产量 LOW-到关关到LOW产量 74HC245输出频率; C L = pF中的输出负载电容; V CC =电源电压V; N =输入切换次数; Σ(C L ×V CC 2 ×f o )=输出和.表10:动态特 性类型74HCT245 GND = 0 V;测试电路见图7.符号参数条件敏典型马克斯单元 T amb = 25°C t PHL ,t PLH传播延迟A到Bn或Bn到安见 图5 V CC = 4.5 V - 12 22 NS V CC = 5.0 V; C L = 15pF - 10 - NS t PZH ,t PZL 3状态输出使能时间OE A或OE到Bn V CC = 4.5V; 见图6 1630ns PHZ ,t PLZ 3状态输出禁用时间OE A或OE到Bn V CC = 4.5V; 见图6 - 1630ns t THL ,t TLH输出转换时间 V CC = 4.5V; 见图5 - 五 12 NS C PD功耗电容每个收发器 V I = GND至V CC - 1.5 V [1] -30 - pF的 T amb = -40°C至+85°C t PHL ,t PLH传播延迟A到Bn或Bn到 安 V CC = 4.5V; 见图5 --28 NS t PZH ,t PZL 3状态输出使能时间OE A或OE到Bn V CC = 4.5V; 见图6 --38 NS PHZ ,t PLZ 3状态输出禁 用时间OE A或OE到Bn V CC = 4.5V; 见图6 --38 NS t THL ,t TLH输出转换时间 V CC = 4.5V; 见图5 --15 NS T amb = -40°C至+125°C t PHL ,t PLH传播延迟A到Bn或Bn到安 V CC = 4.5V; 见图5 --33 NS t PZH ,t PZL 3状态输出使能时间

深圳市富满电子集团股份有限公司 74HC245TS 八同相三态总线收发器 商品说明书

74HC245TS(文件编号:S&CIC1482)八同相三态总线收发器

概述

74HC245TS是一款高速CMOS器件,引脚兼容低功耗肖特基TTL(LSTTL)系列。

74HC245TS是一款三态输出、八路信号双向收发器,有两个控制端(/OE、DIR);其中DIR为数据流向控制器,当DIR为高电平,数据流向为A—>B;当DIR为低电平时,数据流向为B—>A;/OE为输出状态控制端,当/OE 为高电平时,输出为高阻态;当/OE为低电平时,数据正常传输。

74HC245TS主要应用于LED屏显示,以及其它的消费类电子产品中增加驱动。

74HC245TS的工作温度范围为–40℃到85℃。

特点

采用COMS工艺

宽电压工作范围:3.0V~5.0V

74HC245TS(文件编号:S&CIC1482)八同相三态总线收发器

开关特性(CL=50pF,除非另有说明。

)

(CL=150pF,除非另有说明。

)

3、波形之间的相位关系是被任意选择的,所有输入脉冲是由具有以下特点的信号发生器提供:

PRR≤1MHz,Z O=50Ω,t r=6ns,t f=6ns.

4、每一次输入数据的改变测量一次输出。

5、t PLZ和t PHZ与t dis是一样的。

6、t PZL和t PZH与t en是一样的。

7、t PLH和t PHL与t pd是一样的。

74HC245TS(文件编号:S&CIC1482)八同相三态总线收发器封装信息

TSSOP-20。

74HC245

74HC245简介:总线驱动器,典型的TTL型三态缓冲门电路。

由于单片机等CPU的数据/地址/控制总线端口都有一定的负载能力,如果负载超过其负载能力,一般应加驱动器。

另外,也可以使用74HC244等其他电路,74HC244比74HC245多了锁存器。

74HC245实物图:引脚定义:第1脚DIR,为输入输出端口转换用,DIR=“1”高电平时信号由“A”端输入“B”端输出,DIR=“0”低电平时信号由“B”端输入“A”端输出。

第2~9脚“A”信号输入输出端,A1=B1、、、、、、A8=B8,A1与B1是一组,如果DIR=“1”OE=“0”则A1输入B1输出,其它类同。

如果DIR=“0”OE=“0”则B1输入A1输出,其它类同。

第11~18脚“B”信号输入输出端,功能与“A”端一样,不再描述。

第19脚OE,使能端,若该脚为“1”A/B端的信号将不导通,只有为“0”时A/B端才被启用,该脚也就是起到开关的作用。

第10脚GND,电源地。

第20脚VCC,电源正极。

TRUTH TABLE真值表H=高电平L=低电平×=不定Absolute Maximum Ratings绝对最大额定值Supply Voltage电源电压(VCC)-0.5 to -7.0VDC Input Voltage DIR and G pins (VIN) 直流输入电压方向和G引脚(输入电压)-1.5 to VCC -1.5VDC Input/Output Voltage (VIN, VOUT)直流输入/输出电压-0.5 to VCC -0.5VClamp Diode Current 钳位二极管电流(ICD)±20 mADC Output Current直流输出电流,每个引脚(输出)±35 mADC VCC or GND Current, per pin (ICC)±70 mAStorage Temperature Range 储存温度范围(TSTG)-65℃ to -150℃Power Dissipation (PD)功耗(Note 3)600 mWS.O. Package only500 mWLead Temperature (TL) (Soldering 10 seconds)260℃74HC245的作用:信号功率放大第1脚DIR,为输入输出端口转换用,DIR=“1”高电平时信号由“A”端输入“B”端输出,DIR=“0”低电平时信号由“B”端输入“A”端输出。

74HC245中文资料_数据手册_参数

74HC245八路巴士TRANCEIVER;三态 14.修订历史表13:修订记录文档ID发布日期数据表状态更改注意文档.数取代版本 74HC_HCT245_3 20050131产品数据表 - 9397 750 14502 74HC_HCT245_CNV_2莫迪科幻阳离子: ? 本数据表的格式经过重新设计以符 合新的演示文稿和飞利浦半导体的信息标准 ?第4节“订购信息”,第6节“固定信息”和第13节“包装大纲“修改为包含DHVQFN20 包. 74HC_HCT245_CNV_2 19930930产品SPECI FI CATION 9397 750 14502 ? 74HC245 NV 2005.保留所有权利. 74HC245产品数据表 2005年1月3日至31日 13的22飞利浦半导体 74HC245; 74HCT245八 路巴士TRANCEIVER;三态 12.波形测量点在表11中给出. V OL 和V OH 是输出负载时发生的典型电压输出下降.图5.输入(AN,BN) 输出(BN,AN)传播延迟和输出转换时间测量点在表11中给出. V OL 和V OH 是输出负载时发生的典型电压输出下降.图6. 3态输出 启用和禁用时间表11:测量点类型输入产量 74HC245保留所有权利.产品数据表 2005年1月3日至3月31日 13的22飞利浦半导体 74HC245; 74HCT245八路公交车三态波形测量点在表 11中给出. V OL 和V OH 是输出负载时发生的典型电压输出降.图5.输入(An,Bn)输出(Bn,An)传播延迟和输出转换时间测量点 在表11中给出. V OL 和V OH 是输出负载时发生的典型电压输出降.图6. 3状态输出使能和禁止时间表11:测量点类型输入产量 V M V M 74HC245 0.5V CC 0.5V CC 74HCT245 1.3 V 1.3 V 001aac433 t PLH t PHL VM V M 90% 10% V M V M Bn,输出 An,Bn输入 V 我 GND V OH V OL t TLH t THL 001aac479 t PLZ t PHZ输出残输出启用 90% 10%输出启用 OE输入 V 我 V CC V OL V OH GND GND V M t PZL t PZH V M V M产量 LOW-到关关到LOW产量 74HC245输出频率; C L = pF中的输出负载电容; V CC =电源电压V; N =输入切换次数; Σ(C L ×V CC 2 ×f o )=输出和.表10:动态特 性类型74HCT245 GND = 0 V;测试电路见图7.符号参数条件敏典型马克斯单元 T amb = 25°C t PHL ,t PLH传播延迟A到Bn或Bn到安见 图5 V CC = 4.5 V - 12 22 NS V CC = 5.0 V; C L = 15pF - 10 - NS t PZH ,t PZL 3状态输出使能时间OE A或OE到Bn V CC = 4.5V; 见图6 1630ns PHZ ,t PLZ 3状态输出禁用时间OE A或OE到Bn V CC = 4.5V; 见图6 - 1630ns t THL ,t TLH输出转换时间 V CC = 4.5V; 见图5 - 五 12 NS C PD功耗电容每个收发器 V I = GND至V CC - 1.5 V [1] -30 - pF的 T amb = -40°C至+85°C t PHL ,t PLH传播延迟A到Bn或Bn到 安 V CC = 4.5V; 见图5 --28 NS t PZH ,t PZL 3状态输出使能时间OE A或OE到Bn V CC = 4.5V; 见图6 --38 NS PHZ ,t PLZ 3状态输出禁 用时间OE A或OE到Bn V CC = 4.5V; 见图6 --38 NS t THL ,t TLH输出转换时间 V CC = 4.5V; 见图5 --15 NS T amb = -40°C至+125°C t PHL ,t PLH传播延迟A到Bn或Bn到安 V CC = 4.5V; 见图5 --33 NS t PZH ,t PZL 3状态输出使能时间

74HC245详细中文资料

74HC245详细中文资料74HC245是一款高速CMOS器件,74HC2 45引脚兼容低功耗肖特基TTL(LSTTL)系列。

74HC245译码器可接受3位二进制加权地址输入(A0, A1和A2),并当使能时,提供8个互斥的低有效输出(Y0至Y7)。

74HC245特有3个使能输入端:两个低有效(E1和E2)和一个高有效(E3)。

除非E1和E2置低且E3置高,否则74HC138将保持所有输出为高。

利用这种复合使能特性,仅需4片7 4HC245芯片和1个反相器,即可轻松实现并行扩展,组合成为一个1-32(5线到32线)译码器。

任选一个低有效使能输入端作为数据输入,而把其余的使能输入端作为选通端,则74HC245亦可充当一个8输出多路分配器,未使用的使能输入端必须保持绑定在各自合适的高有效或低有效状态。

74HC245与74HC 238逻辑功能一致,只不过74HC138为反相输出。

功能CD74HC245 ,CD74HC238和CD74HCT245, CD74HCT238是高速硅栅CMO S解码器,适合内存地址解码或数据路由应用。

74HC245作用原理于高性能的存贮译码或要求传输延迟时间短的数据传输系统,在高性能存贮器系统中,用这种译码器可以提高译码系统的效率。

将快速赋能电路用于高速存贮器时,译码器的延迟时间和存贮器的赋能时间通常小于存贮器的典型存取时间,这就是说由肖特基钳位的系统译码器所引起的有效系统延迟可以忽略不计。

HC138 按照三位二进制输入码和赋能输入条件,从8 个输出端中译出一个低电平输出。

两个低电平有效的赋能输入端和一个高电平有效的赋能输入端减少了扩展所需要的外接门或倒相器,扩展成24 线译码器不需外接门;扩展成32 线译码器,只需要接一个外接倒相器。

在解调器应用中,赋能输入端可用作数据输入端。

特性复合使能输入,轻松实现扩展兼容JEDEC标准no.7A 存储器芯片译码选择的理想选择低有效互斥输出 ESD保护 HBM EIA/JESD22-A114-C超过2000 V MM EIA/JESD22-A115-A超过200 V 温度范围 -40~+85 ℃ -40~+125 ℃多路分配功能74HC245是一款高速CMOS器件,74HC245引脚兼容低功耗肖特基T TL(LSTTL)系列。

74HC245中文资料,74HC245N规格书,74HC245D技术文档,DATASHEET,NXP代理商

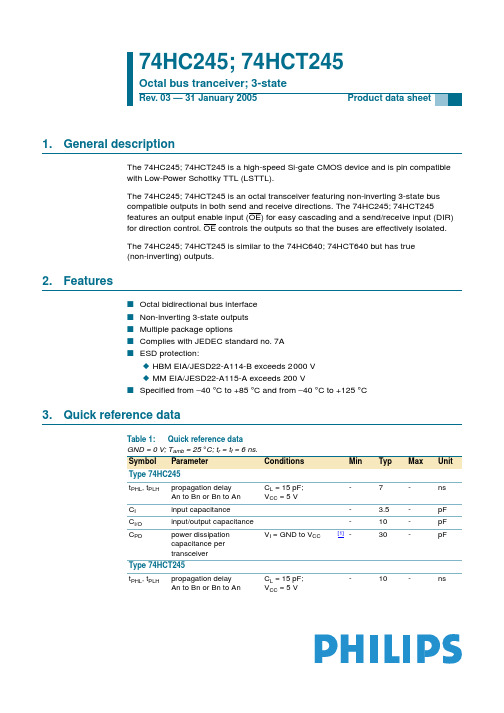

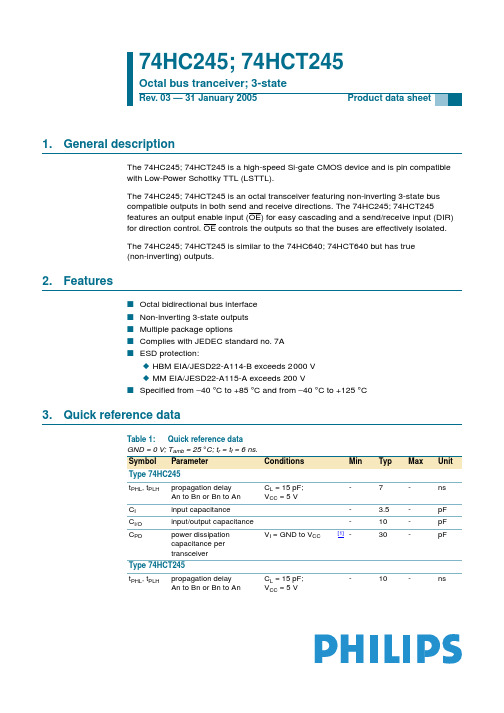

74HC245; 74HCT245

Octal bus tranceiver; 3-state

Rev. 03 — 31 January 2005

Product data sheet

1. General description

The 74HC245; 74HCT245 is a high-speed Si-gate CMOS device and is pin compatible with Low-Power Schottky TTL (LSTTL).

plastic shrink small outline package; 20 leads; body width 5.3 mm

SOT339-1

74HCT245BQ

−40 °C to +125 °C

DHVQFN20 plastic dual-in-line compatible thermal enhanced SOT764-1 very thin quad flat package no leads; 20 terminals; body 2.5 × 4.5 × 0.85 mm

x HBM EIA/JESD22-A114-B exceeds 2000 V x MM EIA/JESD22-A115-A exceeds 200 V s Specified from −40 °C to +85 °C and from −40 °C to +125 °C

3. Quick reference data

SOT163-1

74HCT245PW

−40 °C to +125 °C TSSOP20 plastic thin shrink small outline package; 20 leads; SOT360-1 body width 4.4 mm

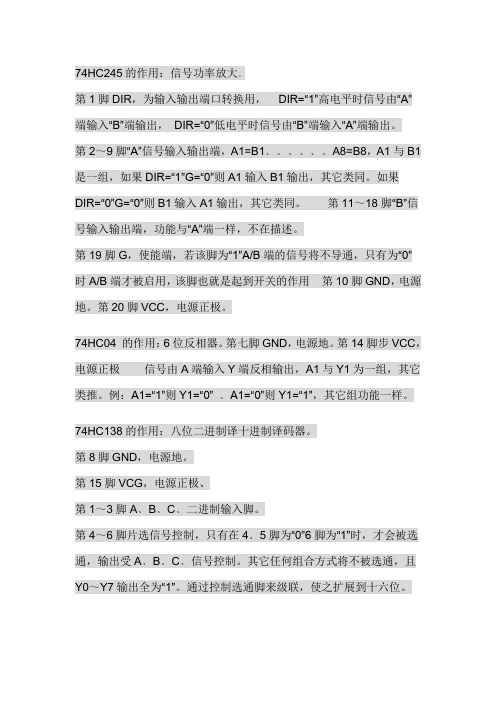

74HC245:信号功率放大

74HC245的作用:信号功率放大

单元板/模组是由多块串接在一起的,而控制信号是比较弱的,在信号传递过程中需要将它的功率进行放大

第1脚DIR,为输入输出端口转换用,DIR=“1”高电平时信号由“A”端输入“B”端输出,DIR=“0”低电平时信号由“B”端输入“A”端输出。

第2~9脚“A”信号输入输出端,A1=B1、、、、、、A8=B8,A1与B1是一组,

如果DIR=“1”G=“0”则A1输入B1输出,其它类同。

如果DIR=“0”G=“0”则B1输入A1输出,其它类同。

第11~18脚“B”信号输入输出端,功能与“A”端一样,不再描述。

第19脚G,使能端,若该脚为“1”A/B端的信号将不导通,只有为“0”时A/B 端才被启用,该脚也就是起到开关的作用。

第10脚GND,电源地。

第20脚VCC,电源正极。

74HC245的作用:信号功率放大

74HC245的作用:信号功率放大。

第1脚DIR,为输入输出端口转换用,DIR=“1”高电平时信号由“A”端输入“B”端输出,DIR=“0”低电平时信号由“B”端输入“A”端输出。

第2~9脚“A”信号输入输出端,A1=B1﹑﹑﹑﹑﹑﹑A8=B8,A1与B1是一组,如果DIR=“1”G=“0”则A1输入B1输出,其它类同。

如果DIR=“0”G=“0”则B1输入A1输出,其它类同。

第11~18脚“B”信号输入输出端,功能与“A”端一样,不在描述。

第19脚G,使能端,若该脚为“1”A/B端的信号将不导通,只有为“0”时A/B端才被启用,该脚也就是起到开关的作用第10脚GND,电源地。

第20脚VCC,电源正极。

74HC04 的作用:6位反相器。

第七脚GND,电源地。

第14脚步VCC,电源正极信号由A端输入Y端反相输出,A1与Y1为一组,其它类推。

例:A1=“1”则Y1=“0” ﹑A1=“0”则Y1=“1”,其它组功能一样。

74HC138的作用:八位二进制译十进制译码器。

第8脚GND,电源地。

第15脚VCG,电源正极、第1~3脚A﹑B﹑C﹑二进制输入脚。

第4~6脚片选信号控制,只有在4﹑5脚为“0”6脚为“1”时,才会被选通,输出受A﹑B﹑C﹑信号控制。

其它任何组合方式将不被选通,且Y0~Y7输出全为“1”。

通过控制选通脚来级联,使之扩展到十六位。

例:G2A=0,G2B=0,G1=1,A=1,B=0,C=0,则YO为“0”Y1~Y7为“1”,74HC595的作用:LED驱动芯片,8位移位锁存器。

第8脚GND,电源地。

第16脚VCC,电源正极第14脚DATA,串行数据输入口,显示数据由此进入,必须有时钟信号的配合才能移入。

第13脚EN,使能口,当该引脚上为“1”时QA~QH口全部为“1”,为“0”时QA~QH的输出由输入的数据控制。

第12脚STB,锁存口,当输入的数据在传入寄存器后,只有供给一个锁存信号才能将移入的数据送QA~QH口输出。

单片机模拟题B及单片机驱动芯片74HC245详细中文资料

一填空(每空1分,共20分)1、MCS-51有4个并行I/O口,其中是准双向口,所以由输出转输入时必须先写入“1”。

2、MCS—51单片机访问片外存储器时,利用信号锁存来自口的低8位地址信号。

3、PSW中RS1 RS0=10H时,R2的地址为。

4、假定(A)=85H,(20H)=0FFH,(CY)=1,执行指令:ADDC A,20H后,累加器A的内容为,CY的内容为,AC的内容为,OV的内容。

5、在直接寻址方式中,只能使用位二进制数作为直接地址,其寻址对象只限于。

6、堆栈设在存储区,程序存放在存储区,外部I/O接口设在存储器,中断服务程序存放在存储器7、假定DPTR的内容为8100H,累加器A的内容为40H,执行下列指令:MOVC A,@A+DPTR后,送入A的是程序存储器单元的内容。

8、定时器对外部脉冲计数,欲计满20个数产生中断,则对于定时器工作模式0,应预置的初值为。

9、MOVC A,@A+PC的寻址方式是,A中存放的,形成操作数地址有决定。

适用于存储器。

二单项选择(每小题2分,共20分)1、MCS-51上电复位后,SP的内容是()(A)00H (B)07H (C)60H (D)70H2、MCS-51响应中断时,下面哪一个条件不是必须的()(A)当前指令执行完毕(B)中断是开放的(C)没有同级或高级中断服务(D)必须有RETI3、ORG 0000HAJMP 0040HORG 0040HMOV SP,#00H 当执行完左边的程序后,PC的值是()(A)0040H (B)0041H (C)0042H (D)0043H 4、执行MOVX A,@DPTR指令时,MCS-51产生的控制信号()(A)/PSEN (B)ALE (C)/RD (D)/WR5、下面哪种指令将MCS-51的工作寄存器置成3区()(A)MOV PSW,#13H (B)MOV PSW,#18H(C)SETB PSW.4 CLR PSW.3 (D)SETB PSW.3 CLR PSW.4 6、若某存储器芯片地址线为12根,那么它的存储容量为()(A)1KB (B)2KB (C)4KB (D)8KB7、关于MCS-51的堆栈操作,正确的说法是()(A)先入栈,再修改栈指针(B)先修改栈指针,在出栈(C)先修改栈指针,在入栈(D)以上都不对8、某种存储器芯片是8KB×4片,那么它的地址线根数是()(A)11根(B)13根(C)12根(D)14根9、MOV C,#00H的寻址方式是()(A)位寻址(B)直接寻址(C)立即寻址(D)寄存器寻址10、在异步通讯接口,其帧格式由1个起始位(0)、7个数据位、1个偶校验和1个停止位“1”组成。

74HC245详细中文资料

74HC245详细中文资料74HC245是一款高速CMOS器件,74HC2 45引脚兼容低功耗肖特基TTL(LSTTL)系列。

74HC245译码器可接受3位二进制加权地址输入(A0, A1和A2),并当使能时,提供8个互斥的低有效输出(Y0至Y7)。

74HC245特有3个使能输入端:两个低有效(E1和E2)和一个高有效(E3)。

除非E1和E2置低且E3置高,否则74HC138将保持所有输出为高。

利用这种复合使能特性,仅需4片74HC 245芯片和1个反相器,即可轻松实现并行扩展,组合成为一个1-32(5线到3 2线)译码器。

任选一个低有效使能输入端作为数据输入,而把其余的使能输入端作为选通端,则74HC245亦可充当一个8输出多路分配器,未使用的使能输入端必须保持绑定在各自合适的高有效或低有效状态。

74HC245与74HC 238逻辑功能一致,只不过74HC138为反相输出。

功能CD74HC245 ,CD74HC238和CD74HCT245,CD74HCT238是高速硅栅CMOS解码器,适合内存地址解码或数据路由应用。

74HC245作用原理于高性能的存贮译码或要求传输延迟时间短的数据传输系统,在高性能存贮器系统中,用这种译码器可以提高译码系统的效率。

将快速赋能电路用于高速存贮器时,译码器的延迟时间和存贮器的赋能时间通常小于存贮器的典型存取时间,这就是说由肖特基钳位的系统译码器所引起的有效系统延迟可以忽略不计。

HC138 按照三位二进制输入码和赋能输入条件,从8 个输出端中译出一个低电平输出。

两个低电平有效的赋能输入端和一个高电平有效的赋能输入端减少了扩展所需要的外接门或倒相器,扩展成24 线译码器不需外接门;扩展成32 线译码器,只需要接一个外接倒相器。

在解调器应用中,赋能输入端可用作数据输入端。

特性复合使能输入,轻松实现扩展兼容JEDEC标准no.7A 存储器芯片译码选择的理想选择低有效互斥输出ESD保护HBM EIA/JESD22-A114-C超过20 00 V MM EIA/JESD22-A115-A超过200 V 温度范围-40~+85 ℃-40~+12 5 ℃多路分配功能 74HC245是一款高速CMOS器件,74HC245引脚兼容低功耗肖特基TTL(LSTTL)系列。

单片机驱动芯片74HC245详细中文资料(16.5)

单片机驱动芯片(74HC245)详细中文资料(74HC245是一款高速CMOS器件,74HC245引脚兼容低功耗肖特基TTL(LSTTL)系列) 74HC245译码器可接受3位二进制加权地址输入(A0, A1和A2),并当使能时,提供8个互斥的低有效输出(Y0至Y7)。

74HC245特有3个使能输入端:两个低有效(E1和E2)和一个高有效(E3)。

除非E1和E2置低且E3置高,否则74HC138将保持所有输出为高。

利用这种复合使能特性,仅需4片7 4HC245芯片和1个反相器,即可轻松实现并行扩展,组合成为一个1-32(5线到32线)译码器。

任选一个低有效使能输入端作为数据输入,而把其余的使能输入端作为选通端,则74HC245亦可充当一个8输出多路分配器,未使用的使能输入端必须保持绑定在各自合适的高有效或低有效状态。

74HC245与74HC238逻辑功能一致,只不过74HC138为反相输出。

一、功能CD74HC245 ,CD74HC238和CD74HCT245, CD74HCT238是高速硅栅CMOS解码器,适合内存地址解码或数据路由应用。

74HC245作用原理于高性能的存贮译码或要求传输延迟时间短的数据传输系统,在高性能存贮器系统中,用这种译码器可以提高译码系统的效率。

将快速赋能电路用于高速存贮器时,译码器的延迟时间和存贮器的赋能时间通常小于存贮器的典型存取时间,这就是说由肖特基钳位的系统译码器所引起的有效系统延迟可以忽略不计。

HC138 按照三位二进制输入码和赋能输入条件,从8 个输出端中译出一个低电平输出。

两个低电平有效的赋能输入端和一个高电平有效的赋能输入端减少了扩展所需要的外接门或倒相器,扩展成24 线译码器不需外接门;扩展成32 线译码器,只需要接一个外接倒相器。

在解调器应用中,赋能输入端可用作数据输入端。

特性复合使能输入,轻松实现扩展兼容JEDEC标准no.7A 存储器芯片译码选择的理想选择低有效互斥输出 ESD保护 HBM EIA/JESD22-A114-C超过2000 V MM EIA/JESD22-A115-A超过200 V 温度范围 -4 0~+85 ℃ -40~+125 ℃多路分配功能74HC245是一款高速CMOS器件,74HC245引脚兼容低功耗肖特基TTL(LSTTL)系列。

74HC245详细中文资料知识讲解

74HC245详细中文资料74HC245是一款高速CMOS器件,74HC2 45引脚兼容低功耗肖特基TTL(LSTTL)系列。

74HC245译码器可接受3位二进制加权地址输入(A0, A1和A2),并当使能时,提供8个互斥的低有效输出(Y0至Y7)。

74HC245特有3个使能输入端:两个低有效(E1和E2)和一个高有效(E3)。

除非E1和E2置低且E3置高,否则74HC138将保持所有输出为高。

利用这种复合使能特性,仅需4片74HC 245芯片和1个反相器,即可轻松实现并行扩展,组合成为一个1-32(5线到3 2线)译码器。

任选一个低有效使能输入端作为数据输入,而把其余的使能输入端作为选通端,则74HC245亦可充当一个8输出多路分配器,未使用的使能输入端必须保持绑定在各自合适的高有效或低有效状态。

74HC245与74HC 238逻辑功能一致,只不过74HC138为反相输出。

功能CD74HC245 ,CD74HC238和CD74HCT245,CD74HCT238是高速硅栅CMOS解码器,适合内存地址解码或数据路由应用。

74HC245作用原理于高性能的存贮译码或要求传输延迟时间短的数据传输系统,在高性能存贮器系统中,用这种译码器可以提高译码系统的效率。

将快速赋能电路用于高速存贮器时,译码器的延迟时间和存贮器的赋能时间通常小于存贮器的典型存取时间,这就是说由肖特基钳位的系统译码器所引起的有效系统延迟可以忽略不计。

HC138 按照三位二进制输入码和赋能输入条件,从8 个输出端中译出一个低电平输出。

两个低电平有效的赋能输入端和一个高电平有效的赋能输入端减少了扩展所需要的外接门或倒相器,扩展成24 线译码器不需外接门;扩展成32 线译码器,只需要接一个外接倒相器。

在解调器应用中,赋能输入端可用作数据输入端。

特性复合使能输入,轻松实现扩展兼容JEDEC标准no.7A 存储器芯片译码选择的理想选择低有效互斥输出ESD保护HBM EIA/JESD22-A114-C超过20 00 V MM EIA/JESD22-A115-A超过200 V 温度范围-40~+85 ℃-40~+12 5 ℃多路分配功能 74HC245是一款高速CMOS器件,74HC245引脚兼容低功耗肖特基TTL(LSTTL)系列。

74HC245在LED显示中的应用

74HC245:

信号功率放大,适用于显示屏以及其他数字电路的驱动

引脚分布如下:

引脚功能作用:

第1脚DIR,为输入输出端口转换用,DIR=“1”高电平时信号由“A”端输入“B”端输出,DIR=“0”低电平时信号由“B”端输入“A”端输出。

第2~9脚“A”信号输入输出端,A1=B1、、、、、、A8=B8,A1与B1是一组,如果DIR=“1”G=“0”则A1输入B1输出,其它类同。

如果DIR=“0”G=“0”则B1输入A1输出,其它类同。

第11~18脚“B”信号输入输出端,功能与“A”端一样,不在描述。

第19脚G,使能端,若该脚为“1”A/B端的信号将不导通,只有为“0”时A/B 端才被启用,该脚也就是起到开关的作用。

第10脚GND,电源地。

第20脚VCC,电源正极。

在LED显示屏中,单元板/模组是由多块串接在一起的,而控制信号是比较弱的,在信号传递过程中需要将它的功率进行放大,74HC245作为一款8路总线收发器的作用就是将接收到的控制信号进行放大。

74hc245和74hc573区别

4hc245和74hc573区别在于:

74hc245是八同相三态收发器,74hc573是8位三态锁存器。两者都有把一个三位二进制数进行锁存的功能,但是74hc245具有双向传输、双向锁存的功能,74hc573只能单向传输、单向锁存。

锁存器(Latch)是一种对脉冲电平敏感的存储单元电路,它们可以在特定输入脉冲电平作用下改变状态。锁存,就是把信号暂存以维持某种电平状态。锁存器的最主要作用是缓存,其次完成高速的控制器与慢速的外设的不同步问题,再其次是解决驱动的问题,最后是解决一个 I/O 口既能输出也能输入的问题。

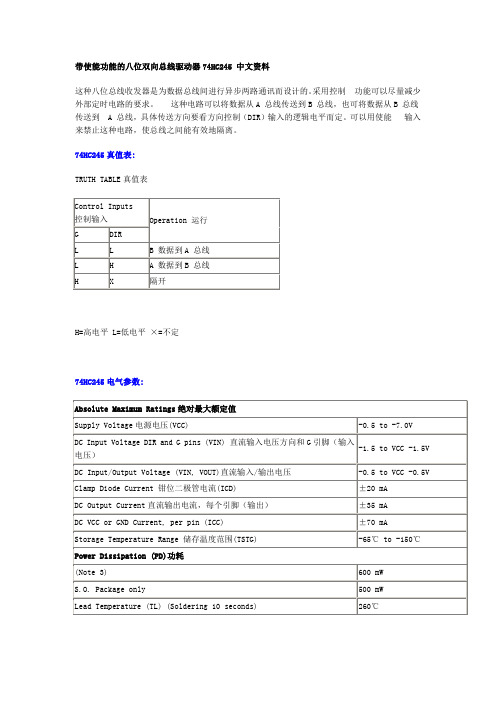

带使能功能的八位双向总线驱动器74HC245 中文资料

带使能功能的八位双向总线驱动器74HC245 中文资料

这种八位总线收发器是为数据总线间进行异步两路通讯而设计的。

采用控制功能可以尽量减少外部定时电路的要求。

这种电路可以将数据从A 总线传送到B 总线,也可将数据从B 总线传送到 A 总线,具体传送方向要看方向控制(DIR)输入的逻辑电平而定。

可以用使能输入来禁止这种电路,使总线之间能有效地隔离。

74HC245真值表:

TRUTH TABLE真值表

H=高电平 L=低电平×=不定

74HC245电气参数:

Note 1: Maximum Ratings are those values beyond which damage to the

device may occur.

Note 2: Unless otherwise specified all voltages are referenced to ground. Note 3: Power Dissipation temperature derating —plastic “N” package: 12 mW/℃ from 65℃ to 85℃.

DC SPECIFICATIONS直流电气规格

AC Electrical C haracteristics VCC=5V, TA=25℃, tr= tf =6ns交流电气特性

AC Electrical Characteristics VCC=2.0V to 6.0V, CL=50 pF, t r= tf =6ns 交流电气特性。

74HC245中文资料,74HC245N规格书,74HC245D技术文档,DATASHEET,NXP代理商

Table 1: Quick reference data GND = 0 V; Tamb = 25 °C; tr = tf = 6 ns.

Symbol Parameter

Conditions

Min Typ Max Unit

Type 74HC245

tPHL, tPLH propagation delay An to Bn or Bn to An

7#43;125 °C DIP20

plastic dual in-line package; 20 leads (300 mil)

SOT146-1

74HCT245D

−40 °C to +125 °C SO20

plastic small outline package; 20 leads; body width 7.5 mm

6. Pinning information

6.1 Pinning

1 DIR 20 VCC

DIR 1 A0 2 A1 3 A2 4 A3 5 A4 6 A5 7 A6 8 A7 9 GND 10

20 VCC 19 OE 18 B0 17 B1 16 B2 245 15 B3 14 B4 13 B5 12 B6 11 B7

SOT163-1

74HCT245PW

−40 °C to +125 °C TSSOP20 plastic thin shrink small outline package; 20 leads; SOT360-1 body width 4.4 mm

74HCT245DB

−40 °C to +125 °C SSOP20

74HC245DB

−40 °C to +125 °C SSOP20

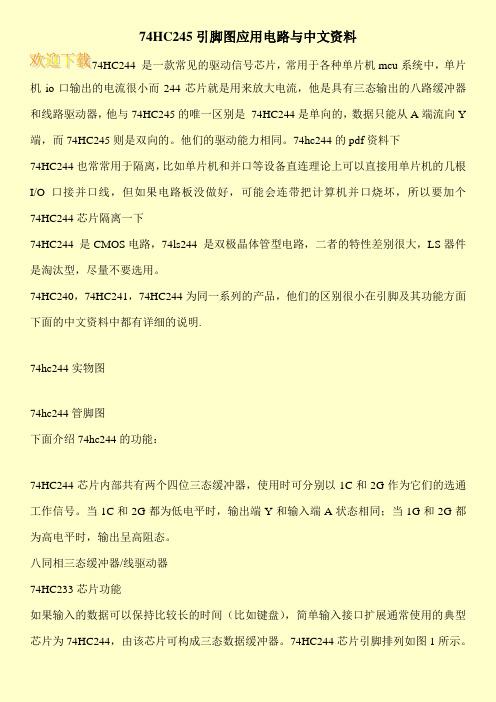

74HC245引脚图应用电路与中文资料

74HC245引脚图应用电路与中文资料

74HC244 是一款常见的驱动信号芯片,常用于各种单片机mcu系统中,单片机io口输出的电流很小而244芯片就是用来放大电流,他是具有三态输出的八路缓冲器和线路驱动器,他与74HC245的唯一区别是74HC244是单向的,数据只能从A端流向Y 端,而74HC245则是双向的。

他们的驱动能力相同。

74hc244的pdf资料下

74HC244也常常用于隔离,比如单片机和并口等设备直连理论上可以直接用单片机的几根I/O口接并口线,但如果电路板没做好,可能会连带把计算机并口烧坏,所以要加个74HC244芯片隔离一下

74HC244 是CMOS电路,74ls244 是双极晶体管型电路,二者的特性差别很大,LS器件是淘汰型,尽量不要选用。

74HC240,74HC241,74HC244为同一系列的产品,他们的区别很小在引脚及其功能方面下面的中文资料中都有详细的说明.

74hc244实物图

74hc244管脚图

下面介绍74hc244的功能:

74HC244芯片内部共有两个四位三态缓冲器,使用时可分别以1C和2G作为它们的选通工作信号。

当1C和2G都为低电平时,输出端Y和输入端A状态相同;当1G和2G都为高电平时,输出呈高阻态。

八同相三态缓冲器/线驱动器

74HC233芯片功能

如果输入的数据可以保持比较长的时间(比如键盘),简单输入接口扩展通常使用的典型芯片为74HC244,由该芯片可构成三态数据缓冲器。

74HC244芯片引脚排列如图1所示。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

74HC245是一款高速CMOS器件,74HC245引脚兼容低功耗肖特基TTL(LSTTL)系列。

74HC245译码器可接受3位二进制加权地址输入(A0, A1和A2),并当使能时,提供8个互斥的低有效输出(Y0至Y7)。

74HC245特有3个使能输入端:两个低有效(E1和E2)和一个高有效(E3)。

除非E1和E2置低且E3置高,否则74HC138将保持所有输出为高。

利用这种复合使能特性,仅需4片74HC 245芯片和1个反相器,即可轻松实现并行扩展,组合成为一个1-32(5线到3 2线)译码器。

任选一个低有效使能输入端作为数据输入,而把其余的使能输入端作为选通端,则74HC245亦可充当一个8输出多路分配器,未使用的使能输入端必须保持绑定在各自合适的高有效或低有效状态。

74HC245与74HC 238逻辑功能一致,只不过74HC138为反相输出。

功能CD74HC245 ,CD74HC238和CD74HCT245,CD74HCT238是高速硅栅CMOS解码器,适合内存地址解码或数据路由应用。

74HC245作用原理于高性能的存贮译码或要求传输延迟时间短的数据传输系统,在高性能存贮器系统中,用这种译码器可以提高译码系统的效率。

将快速赋能电路用于高速存贮器时,译码器的延迟时间和存贮器的赋能时间通常小于存贮器的典型存取时间,这就是说由肖特基钳位的系统译码器所引起的有效系统延迟可以忽略不计。

HC138 按照三位二进制输入码和赋能输入条件,从8 个输出端中译出一个低电平输出。

两个低电平有效的赋能输入端和一个高电平有效的赋能输入端减少了扩展所需要的外接门或倒相器,扩展成24 线译码器不需外接门;扩展成32 线译码器,只需要接一个外接倒相器。

在解调器应用中,赋能输入端可用作数据输入端。

特性复合使能输入,轻松实现扩展兼容JEDEC标准no.7A 存储器芯片译码选择的理想选择低有效互斥输出ESD保护HBM EIA/JESD22-A114-C超过20 00 V MM EIA/JESD22-A115-A超过200 V 温度范围-40~+85 ℃-40~+12 5 ℃多路分配功能 74HC245是一款高速CMOS器件,74HC245引脚兼容低功耗肖特基TTL(LSTTL)系列。

74HC245译码器可接受3位二进制加权地址输入(A0, A1和A2),并当使能时,提供8个互斥的低有效输出(Y0至Y7)。

74HC245特有3个使能输入端:两个低有效(E1和E2)和一个高有效(E3)。

除非E1和E2置低且E3置高,否则74HC245将保持所有输出为高。

利用这种复合使能特性,仅需4片74HC 245芯片和1个反相器,即可轻松实现并行扩展,组合成为一个1-32(5线到3 2线)译码器。

任选一个低有效使能输入端作为数据输入,而把其余的使能输入端作为选通端,则74HC245亦可充当一个8输出多路分配器,未使用的使能输入端必须保持绑定在各自合适的高有效或低有效状态。

74HC245与74HC238逻辑功能一致,只不过74HC245为反相输出。

功能CD74HC245 ,CD74HC238和CD74HCT138 ,CD74HCT238是高速硅栅CMOS解码器,适合内存地址解码或数据路由应用。

74HC138 作用原理于高性能的存贮译码或要求传输延迟时间短的数据传输系统,在高性能存贮器系统中,用这种译码器可以提高译码系统的效率。

将快速赋能电路用于高速存贮器时,译码器的延迟时间和存贮器的赋能时间通常小于存贮器的典型存取时间,这就是说由肖特基钳位的系统译码器所引起的有效系统延迟可以忽略不计。

HC245 按照三位二进制输入码和赋能输入条件,从8 个输出端中译出一个低电平输出。

两个低电平有效的赋能输入端和一个高电平有效的赋能输入端减少了扩展所需要的外接门或倒相器,扩展成24 线译码器不需外接门;扩展成32 线译码器,只需要接一个外接倒相器。

在解调器应用中,赋能输入端可用作数据输入端。

特性复合使能输入,轻松实现扩展兼容JEDEC标准no.7A 存储器芯片译码选择的理想选择低有效互斥输出ESD保护HBM EIA/JESD22-A114-C超过20 00 V MM EIA/JESD22-A115-A超过200 V 温度范围-40~+85 ℃-40~+12 5 ℃多路分配功能74HC系列功能简介型号功能74HC253 双4选1数据选择器(三态)74HC257 四2选1数据选择器(三态)74HC259 8位可寻址锁存器74HC266 四2输入异或非门(OC)74HC273 八D型触发器(带清除端)74HC279 四R—S锁存器74HC280 9位奇偶数产生器/校验器74HC283 4位二进制全加器(带超前进位)74HC298 4位2选1数据选择器74HC365 六缓冲器/总线驱动(同相)74HC366 六缓冲器/总线驱动(反相)74HC367 六缓冲器/总线驱动(同相)74HC368 六缓冲器/总线驱动(反相)74HC373 八D触发器(三态)74HC374 八D触发器(三态)74HC377 八D触发器74HC386 四2输入异或门74HC390 双4位十进制计数器74HC393 双4位二进制计数器(异步清除)74HC540 八缓冲器/总线驱动器74HC541 八缓冲器/总线驱动器74HC573 八D锁存器(三态)74HC574 八D锁存器(三态)74HC589 8位输入锁存输出移位寄存器74HC595 8位输出锁存移位寄存器74HC688 8位数值比较器/等值检测器74HC4002 从4输入或非门74HC4015 双4位串入并出移位寄存器74HC4017 十进制计数器/分配器74HC4040 12位二进制串行计数器74HC4046 锁相环74HC4049 六缓冲器/电平变换器(反相)74HC4050 六缓冲器/电平变换器(同相)74HC4051 单8通道模拟开关74HC4052 双4通道摸拟开关74HC4053 三2通道模拟开关74HC4060 14位二进制串行计数器74HC4066 四双向模拟开关74HC4520 双二进制加法计数器74HC4538 双精密单稳态触发器74HC4543 7段锁存/译码/驱动器74HC4551 四2通道模拟开关74HC132 四2输入与非施密特触发器74HC138 3—8线译码器/多路转换器74HC139 双2—4线译码器/多路转换器74HC145 BCD—十进制译码器/驱动器74HC147 10—4线BCD优先编码器74HC148 8选1数据选择器74HC151 双4选1数据选择器74HC153 4—16线多路分配器74HC154 4—16线多路分配器74HC155 双2—4线多路分配器74HC156 双2—4线多路分配器74HC157 四2选1数据选择器74HC158 四2选1数据选择器74HC160 同步BCD十进制计数器74HC161 同步4位二进制计数器74HC162 同步十进制计数器(同步清除)74HC163 4位二进制计数器(同步清除)74HC164 8位移位寄存器(并入并出)74HC165 8位移位寄存器(并入串出)74HC166 8位移位寄存器(串并入串出)74HC173 4位D型寄存器(三态)74HC174 六D型触发器(带清除端)74HC175 四D型触发器(带清除端)74HC181 运算器/函数发生器74HC182 超前进位发生器74HC190 BCD十进制同步可逆计数器74HC191 4位二进制同步可逆计数器74HC192 BCD十进制同步可逆计数器74HC193 4位二进制同步可逆计数器74HC194 4位双向通用移位寄存器74HC195 4位并行存取移位寄存器74HC221 双单稳态多谐振荡器74HC237 3—8线译码器(带地扯锁存)74HC238 3—8线译码器/多路分配器74HC240 八缓冲器/驱动器/接收器74HC241 八缓冲器/驱动器/接收器74HC242 四总线收发器(三态、反相)74HC243 四总线收发器(三态、同相)74HC244 八缓冲器/驱动器/接收器74HC245 八总线收发器(三态)74HC251 8选1数据选择器(三态)74HC00 四2输入与非门74HC02 四2输入或非门74HC04 六反相器74HC05 六反相器(OC)74HC08 四2输入与门74HC09 四2输入与门(OC)74HC10 三3输入与非门74HC11 三3输入与门74HC14 六反相器(施密特触发)74HC20 双4输入与非门74HC21 双4输入与门74HC27 三3输入或非门74HC30 8输入与非门74HC32 四2输入或门74HC42 BCD—十进制译码器74HC51 2输入/3输入双与或非门74HC58 2输入/3输入双与或门74HC73 双J—K触发器(带清除端)74HC74 双D型正沿触发器74HC75 4位双稳态D型锁存器74HC76 双J—K触发器(带预置清除端) 74HC85 4位幅度比较器74HC86 四2输入异或门74HC107 从J—K触发器(带清除端)74HC109 双J—K正沿触发器74HC123 双可再触发单稳多谐振荡器74HC125 四总线缓冲门(三态)74HC126 四总线缓冲门(三态)。