SSL-LX30448SRC;中文规格书,Datasheet资料

XC2C128资料

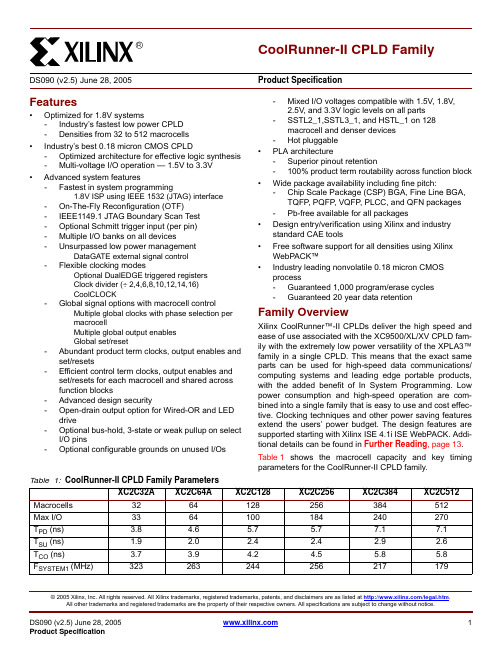

DS090 (v2.5) June 28, 1Product Specification© 2005 Xilinx, Inc. All rights reserved. All Xilinx trademarks, registered trademarks, patents, and disclaimers are as listed at /legal.htm .All other trademarks and registered trademarks are the property of their respective owners. All specifications are subject to change without notice.Features•Optimized for 1.8V systems-Industry’s fastest low power CPLD -Densities from 32 to 512 macrocells •Industry’s best 0.18 micron CMOS CPLD-Optimized architecture for effective logic synthesis -Multi-voltage I/O operation — 1.5V to 3.3V •Advanced system features-Fastest in system programming· 1.8V ISP using IEEE 1532 (JTAG) interface -On-The-Fly Reconfiguration (OTF)-IEEE1149.1 JTAG Boundary Scan Test -Optional Schmitt trigger input (per pin)-Multiple I/O banks on all devices-Unsurpassed low power management·DataGATE external signal control -Flexible clocking modes·Optional DualEDGE triggered registers ·Clock divider (÷ 2,4,6,8,10,12,14,16)·CoolCLOCK-Global signal options with macrocell control·Multiple global clocks with phase selection permacrocell ·Multiple global output enables ·Global set/reset-Abundant product term clocks, output enables andset/resets-Efficient control term clocks, output enables andset/resets for each macrocell and shared across function blocks-Advanced design security-Open-drain output option for Wired-OR and LEDdrive-Optional bus-hold, 3-state or weak pullup on selectI/O pins-Optional configurable grounds on unused I/Os-Mixed I/O voltages compatible with 1.5V, 1.8V, 2.5V, and 3.3V logic levels on all parts -SSTL2_1,SSTL3_1, and HSTL_1 on 128macrocell and denser devices -Hot pluggable •PLA architecture-Superior pinout retention-100% product term routability across function block •Wide package availability including fine pitch:-Chip Scale Package (CSP) BGA, Fine Line BGA,TQFP , PQFP , VQFP , PLCC, and QFN packages -Pb-free available for all packages•Design entry/verification using Xilinx and industry standard CAE tools•Free software support for all densities using Xilinx WebPACK™•Industry leading nonvolatile 0.18 micron CMOS process-Guaranteed 1,000 program/erase cycles -Guaranteed 20 year data retention Family OverviewXilinx CoolRunner™-II CPLDs deliver the high speed and ease of use associated with the XC9500/XL/XV CPLD fam-ily with the extremely low power versatility of the XPLA3™family in a single CPLD. This means that the exact same parts can be used for high-speed data communications/computing systems and leading edge portable products,with the added benefit of In System Programming. Low power consumption and high-speed operation are com-bined into a single family that is easy to use and cost effec-tive. Clocking techniques and other power saving features extend the users’ power budget. The design features are supported starting with Xilinx ISE 4.1i ISE WebPACK. Addi-tional details can be found in Further Reading , page 13.Table 1 shows the macrocell capacity and key timing parameters for the CoolRunner-II CPLD family.CoolRunner-II CPLD FamilyDS090 (v2.5) June 28, 2005Product SpecificationTable 1: CoolRunner-II CPLD Family ParametersXC2C32AXC2C64AXC2C128XC2C256XC2C384XC2C512Macrocells 3264128256384512Max I/O 3364100184240270T PD (ns) 3.8 4.6 5.7 5.77.17.1T SU (ns) 1.9 2.0 2.4 2.4 2.9 2.6T CO (ns) 3.73.94.24.55.85.8F SYSTEM1 (MHz)323 263 244256 217 179元器件交易网2DS090 (v2.5) June 28, 2005Product SpecificationTable 2 shows key DC characteristics for the CoolRunner-II family.Table 3 shows the CoolRunner-II CPLD package offering with corresponding I/O count. All packages are surface mount, with over half of them being ball-grid technologies.The ultra tiny packages permit maximum functional capacity in the smallest possible area. The CMOS technology used in CoolRunner-II CPLDs generates minimal heat, allowing the use of tiny packages during high-speed operation.With the exception of the new Pb-free QF packages, there are at least two densities present in each package with three in the VQ100 (100-pin 1.0mm QFP) and TQ144(144-pin 1.4mm QFP), and in the FT256 (256-ball 1.0mm spacing FLBGA). The FT256 is particularly important for slim dimensioned portable products with mid- to high-den-sity logic requirements.Table 4 details the distribution of advanced features across the CoolRunner-II CPLD family. The family has uniform basic features with advanced features included in densities where they are most useful. For example, it is very unlikely that four I/O banks are needed on 32 and 64 macrocellparts, but very likely they are for 384 and 512 macrocell parts. The I/O banks are groupings of I/O pins using any one of a subset of compatible voltage standards that share the same V CCIO level. (See Table 5 for a summary of CoolRunner-II I/O standards.)Table 2: CoolRunner-II CPLD DC CharacteristicsXC2C32AXC2C64AXC2C128XC2C256XC2C384XC2C512I CC (µA), 0 MHz, 25°C (typical)161719212325I CC (mA), 50 MHz, 70°C (max)2.5510274555CC Table 3: CoolRunner-II CPLD Family Packages and I/O CountXC2C32XC2C32AXC2C64XC2C64AXC2C128XC2C256XC2C384XC2C512QFG32(1)21------PC4433333333----PCG44(1)3333----VQ4433333333----VQG44(1)3333----QFG48(1)---37----CP5633334545----CPG56(1)3345----VQ100--64648080--VQG100(1)--648080--CP132----100106--CPG132(1)----100106--TQ144----100118118-TQG144(1)----100118118-PQ208-----173173173PQG208(1)-----173173173FT256-----184212212FTG256(1)-----184212212FG324------240270FGG324(1)------240270Notes:1.The letter "G" as the third character indicates a Pb-free package.DS090 (v2.5) June 28, 3Product SpecificationArchitecture DescriptionCoolRunner-II CPLD is a highly uniform family of fast, lowpower CPLDs. The underlying architecture is a traditional CPLD architecture combining macrocells into Function Blocks (FBs) interconnected with a global routing matrix,the Xilinx Advanced Interconnect Matrix (AIM). The Func-tion Blocks use a Programmable Logic Array (PLA) config-uration which allows all product terms to be routed and shared among any of the macrocells of the FB. Design soft-ware can efficiently synthesize and optimize logic that is subsequently fit to the FBs and connected with the ability to utilize a very high percentage of device resources. Design changes are easily and automatically managed by the soft-ware, which exploits the 100% routability of the Program-mable Logic Array within each FB. This extremely robustbuilding block delivers the industry’s highest pinout reten-tion, under very broad design conditions. The architecture will be explained by expanding the detail as we discuss the underlying Function Blocks, logic and interconnect.The design software automatically manages these device resources so that users can express their designs using completely generic constructs without knowledge of these architectural details. More advanced users can take advan-tage of these details to more thoroughly understand the software’s choices and direct its results.Figure 1 shows the high-level architecture whereby Func-tion Blocks attach to pins and interconnect to each other within the internal interconnect matrix. Each FB contains 16macrocells. The BSC path is the JTAG Boundary Scan Con-Table 4: CoolRunner-II CPLD Family FeaturesXC2C32XC2C32AXC2C64 XC2C64AXC2C128XC2C256XC2C384XC2C512IEEE 1532✓✓✓✓✓✓✓✓I/O banks 12122244Clock division ----✓✓✓✓DualEDGE Registers ✓✓✓✓✓✓✓✓DataGATE ----✓✓✓✓LVTTL✓✓✓✓✓✓✓✓LVCMOS33, 25, 18, and 15(1)✓✓✓✓✓✓✓✓SSTL2_1----✓✓✓✓SSTL3_1----✓✓✓✓HSTL_1----✓✓✓✓Configurable ground ✓✓✓✓✓✓✓✓Quadruple data security✓✓✓✓✓✓✓✓Open drain outputs ✓✓✓✓✓✓✓✓Hot plugging ✓✓✓✓✓✓✓✓Schmitt Inputs✓✓✓✓✓✓✓✓4DS090 (v2.5) June 28, 2005Product Specificationtrol path. The BSC and ISP block has the JTAG controller and In-System Programming Circuits.Function BlockThe CoolRunner-II CPLD Function Blocks contain 16 mac-rocells, with 40 entry sites for signals to arrive for logic cre-ation and connection. The internal logic engine is a 56product term PLA. All Function Blocks, regardless of the number contained in the device, are identical. For a high-level view of the Function Block, see Figure 2.At the high level, it is seen that the product terms (p-terms)reside in a programmable logic array (PLA). This structureis extremely flexible, and very robust when compared to fixed or cascaded product term function blocks.Classic CPLDs typically have a few product terms available for a high-speed path to a given macrocell. They rely on capturing unused p-terms from neighboring macrocells to expand their product term tally, when needed. The result of this architecture is a variable timing model and the possibil-ity of stranding unusable logic within the FB.The PLA is different — and better. First, any product term can be attached to any OR gate inside the FB macrocell(s).Second, any logic function can have as many p-terms as needed attached to it within the FB, to an upper limit of 56.Third, product terms can be re-used at multiple macrocell OR functions so that within a FB, a particular logical product need only be created once, but can be re-used up to 16times within the FB. Naturally, this plays well with the fitting software, which identifies product terms that can be shared. The software places as many of those functions as it can into FBs, so it happens for free. There is no need to force macrocell functions to be adjacent or any other restriction save residing in the same FB, which is handled by the soft-ware. Functions need not share a common clock, common set/reset or common output enable to take full advantage of the PLA. Also, every product term arrives with the same time delay incurred. There are no cascade time adders for putting more product terms in the FB. When the FB product term budget is reached, there is a small interconnect timing penalty to route signals to another FB to continue creating logic. Xilinx design software handles all this automatically.Figure 1: CoolRunner-II CPLD ArchitectureFigure 2: CoolRunner-II CPLD Function BlockDS090 (v2.5) June 28, 5Product SpecificationMacrocellThe CoolRunner-II CPLD macrocell is extremely efficient and streamlined for logic creation. Users can develop sum of product (SOP) logic expressions that comprise up to 40inputs and span 56 product terms within a single function block. The macrocell can further combine the SOP expres-sion into an XOR gate with another single p-term expres-sion. The resulting logic expression’s polarity is also selectable. As well, the logic function can be pure combina-torial or registered, with the storage element operating selectably as a D or T flip-flop, or transparent latch. Avail-able at each macrocell are independent selections of glo-bal, function block level or local p-term derived clocks, sets,resets, and output enables. Each macrocell flip-flop is con-figurable for either single edge or DualEDGE clocking, pro-viding either double data rate capability or the ability to distribute a slower clock (thereby saving power). For single edge clocking or latching, either clock polarity may be selected per macrocell. CoolRunner-II macrocell details are shown in Figure 3. Note that in Figure 4, standard logic symbols are used except the trapezoidal multiplexers have input selection from statically programmed configuration select lines (not shown). Xilinx application note XAPP376gives a detailed explanation of how logic is created in the CoolRunner-II CPLD family.When configured as a D-type flip-flop, each macrocell has an optional clock enable signal permitting state hold while a clock runs freely. Note that Control Terms (CT) are available to be shared for key functions within the FB, and are gener-ally used whenever the exact same logic function would be repeatedly created at multiple macrocells. The CT product terms are available for FB clocking (CTC), FB asynchro-nous set (CTS), FB asynchronous reset (CTR), and FB out-put enable (CTE).Any macrocell flip-flop can be configured as an input regis-ter or latch, which takes in the signal from the macrocell’s I/O pin, and directly drives the AIM. The macrocell combina-tional functionality is retained for use as a buried logic node if needed. F Toggle is the maximum clock frequency to which a T flip-flop can reliably toggle.Advanced Interconnect Matrix (AIM)The Advanced Interconnect Matrix is a highly connected low power rapid switch. The AIM is directed by the software to deliver up to a set of 40 signals to each FB for the cre-ation of logic. Results from all FB macrocells, as well as, all pin inputs circulate back through the AIM for additional con-nection available to all other FBs as dictated by the designFigure 3: CoolRunner-II CPLD MacrocellDS090 (v2.5) June 28, 2005Product Specificationsoftware. The AIM minimizes both propagation delay and power as it makes attachments to the various FBs.I/O BlockI/O blocks are primarily transceivers. However, each I/O is either automatically compliant with standard voltage ranges or can be programmed to become so. See XAPP382 for detailed information on CoolRunner-II I/Os.In addition to voltage levels, each input can selectively arrive through Schmitt-trigger inputs. This adds a small time delay, but substantially reduces noise on that input pin.Approximately 500 mV of hysteresis will be added when Schmitt-trigger inputs are selected. All LVCMOS inputs can have hysteresis input. Hysteresis also allows easy genera-tion of external clock circuits. The Schmitt-trigger path is best seen in Figure 4. See Table 5 for Schmitt-trigger com-patibility with I/O standards.Outputs can be directly driven, 3-stated or open-drain con-figured. A choice of slow or fast slew rate output signal isalso available. Table 5 summarizes various supported volt-age standards associated with specific part capacities. All inputs and disabled outputs are voltage tolerant up to 3.3V.The CoolRunner-II family supports SSTL2-1, SSTL3-1 and HSTL-1 high-speed I/O standards in the 128-macrocell and larger devices. Figure 4 details the I/O pin, where it is noted that the inputs requiring comparison to an external refer-ence voltage are available. These I/O standards all require VREF pins for proper operation. The CoolRunner-II CPLD allows any I/O pin to act as a VREF pin, granting the board layout engineer extra freedom when laying out the pins.However, if VREF pin placement is not done properly,additional VREF pins may be required, resulting in a loss of potential I/O pins or board re-work. See XAPP399 for details regarding VREF pins and their placement.V REF has pin-range requirements that must be observed.The Xilinx software aids designers in remaining within the proper pin range.Table 5 summarizes the single ended I/O standard support and shows which standards require V REF values and board termination. V REF detail is given in specific data sheets.Figure 4: CoolRunner-II CPLD I/O Block DiagramTable 5: CoolRunner-II CPLD I/O Standard SummaryIOSTANDARD Attribute V CCIO Input V REFBoard Termination Voltage(V TT )Schmitt-trigger SupportLVTTL 3.3 N/A N/A Optional LVCMOS33 3.3 N/A N/A Optional LVCMOS25 2.5 N/A N/A Optional LVCMOS18 1.8 N/A N/A Optional LVCMOS15 1.5 N/A N/A Not optional HSTL_1 1.5 0.75 0.75Not optional SSTL2_1 2.5 1.25 1.25Not optional SSTL3_13.31.51.5Not optionalDS090 (v2.5) June 28, 7Product SpecificationOutput BankingCPLDs are widely used as voltage interface translators. To that end, the output pins are grouped in large banks. The XC2C32 and XC2C64 devices are not banked, but the new XC2C32A and XC2C64A devices have two banks. The medium parts (128 and 256 macrocell) support two output banks. With two, the outputs will switch to one of two selected output voltage levels, unless both banks are set to the same voltage. The larger parts (384 and 512 macrocell)support four output banks split evenly. They can support groupings of one, two, three or four separate output voltage levels. This kind of flexibility permits easy interfacing to 3.3V, 2.5V, 1.8V, and 1.5V in a single part.DataGATELow power is the hallmark of CMOS technology. Other CPLD families use a sense amplifier approach to creating product terms, which always has a residual current compo-nent being drawn. This residual current can be several hun-dred milliamps, making them unusable in portable systems.CoolRunner-II CPLDs use standard CMOS methods to cre-ate the CPLD architecture and deliver the corresponding low current consumption, without doing any special tricks.However, sometimes designers would like to reduce their system current even more by selectively disabling circuitry not being used.The patented DataGATE technology was developed to per-mit a straightforward approach to additional power reduc-tion. Each I/O pin has a series switch that can block the arrival of free running signals that are not of interest. Sig-nals that serve no use may increase power consumption,and can be disabled. Users are free to do their design, then choose sections to participate in the DataGATE function.DataGATE is a logic function that drives an assertion rail threaded through the medium and high-density CoolRunner-II CPLD parts. Designers can select inputs to be blocked under the control of the DataGATE function,effectively blocking controlled switching signals so they do not drive internal chip capacitances. Output signals that do not switch, are held by the bus hold feature. Any set of input pins can be chosen to participate in the DataGATE function.Figure 5 shows the familiar CMOS I CC versus switching fre-quency graph. With DataGATE, designers can approach zero power, should they choose to, in their designs Figure 6 shows how DataGATE basically works. One I/O pin drives the DataGATE Assertion Rail. It can have any desired logic function on it. It can be as simple as mapping an input pin to the DataGATE function or as complex as a counter or state machine output driving the DataGATE I/O pin through a macrocell. When the DataGATE rail is asserted high, any pass transistor switch attached to it is blocked. Note that each pin has the ability to attach to theAIM through a DataGATE pass transistor, and thus be blocked. A latch automatically captures the state of the pin when it becomes blocked. The DataGATE Assertion Rail threads throughout all possible I/Os, so each can participate if chosen. Note that one macrocell is singled out to drive the rail, and that macrocell is exposed to the outside world through a pin, for inspection. If DataGATE is not needed,this pin is an ordinary I/O.Figure 5: CMOS I CC vs. Switching Frequency CurveDS090 (v2.5) June 28, 2005Product SpecificationGlobal SignalsGlobal signals, clocks (GCK), sets/resets (GSR) and output enables (GTS), are designed to strongly resemble each other. This approach enables design software to make the best utilization of their capabilities. Each global capability is supplemented by a corresponding product term version.Figure 7 shows the common structure of the global signal trees. The pin input is buffered, then drives multiple internal global signal traces to deliver low skew and reduce loading delays. The DataGATE assertion rail is also a global signal.Additional Clock Options: Division, DualEDGE, and CoolCLOCKDivisionCircuitry has been included in the CoolRunner-II CPLD architecture to divide one externally supplied global clock by standard values. Division by 2,4,6,8,10, 12, 14 and 16are the options (see Figure 8). This capability is supplied on the GCK2 pin. The resulting clock produced will be 50%duty cycle for all possible divisions. Note that a Synchro-nous Reset (CDRST) is included to guarantee no runt clocks can get through to the global clock nets. Note that again, the signal is buffered and driven to multiple traces with minimal loading and skew.DualEDGEEach macrocell has the ability to double its input clock switching frequency. Figure 9 shows the macrocell flip-flop with the DualEDGE option (doubled clock) at each macro-cell. The source to double can be a control term clock, a product term clock or one of the available global clocks. The ability to switch on both clock edges is vital for a number of synchronous memory interface applications as well as cer-tain double data rate I/O applications.Figure 6: DataGATE Architecture (output drivers not shown)Figure 7: Global Clocks (GCK), Sets/Resets (GSR) andOutput Enables (GTS)DS090 (v2.5) June 28, 9Product SpecificationCoolCLOCKIn addition to the DualEDGE flip-flop, additional power sav-ings can be had by combining the clock division circuitry with the DualEDGE circuitry. This capability is called Cool-CLOCK and is designed to reduce clocking power within the CPLD. Because the clock net can be an appreciable powerdrain, the clock power can be reduced by driving the net at half frequency, then doubling the clock rate using DualEDGE triggering at the macrocells. Figure 10 shows how CoolCLOCK is created by internal clock cascading with the divider and DualEDGE flip-flop working together. See XAPP378 for more detail.Figure 8: Clock Division Circuitry for GCK2Figure 9: Macrocell Clock Chain with DualEDGE Option ShownFigure 10: CoolCLOCK Created by Cascading Clock Divider and DualEDGE OptionDS090 (v2.5) June 28, 2005Product SpecificationDesign SecurityDesigns can be secured during programming to prevent either accidental overwriting or pattern theft via readback.Four independent levels of security are provided on-chip,eliminating any electrical or visual detection of configuration patterns. These security bits can be reset only by erasing the entire device. See WP170 for more detail.Timing ModelFigure 11 shows the CoolRunner-II CPLD timing model. It represents one aspect of the overall architecture from a tim-ing viewpoint. Each little block is a time delay that a signal will incur if the signal passes through such a resource. Tim-ing reports are created by tallying the incremental signal delays as signals progress within the CPLD. Software cre-ates the timing reports after a design has been mapped onto the specific part, and knows the specific delay values for a given speed grade. Equations for the higher level tim-ing values (i.e., T PD and F SYSTEM ) are available. Table 6summarizes the individual parameters and provides a brief definition of their associated functions.Xilinx application note XAPP375 details the CoolRunner-II CPLD family tim-ing with several examples.Figure 11: CoolRunner-II CPLD Timing ModelTable 6: Timing Parameter Definitions Symbol ParameterBuffer DelaysT lN Input Buffer DelayT DIN Direct data register input delay T GCK Global clock (GCK) buffer delay T GSR Global set/reset (GSR) buffer delay T GTS Global output enable (GTS) buffer delay T OUT Output buffer delayT EN Output buffer enable/disable delay T SLEW Output buffer slew rate control delay P-term Delays T CT Control Term delay (single PT or FB-CT)T LOGI1Single P-term logic delay T LOGI2Multiple P-term logic delay adderMacrocell DelaysT PDI Macro cell input to output valid T SUI Macro register setup before clock T HI Macro register hold after clock T ECSU Macro register enable clock setup time T ECHO Macro register enable clock hold time T COI Macro register clock to output valid T AOI Macro register set/reset to output valid T HYS Hysteresis selection delay adder Feedback DelaysT F Feedback delayT OEMMacrocell to Global OE delayTable 6: Timing Parameter Definitions (Continued)Symbol ParameterProgrammingThe programming data sequence is delivered to the device using either Xilinx iMPACT software and a Xilinx download cable, a third-party JTAG development system, a JTAG-compatible board tester, or a simple microprocessor interface that emulates the JTAG instruction sequence. The iMPACT software also outputs serial vector format (SVF) files for use with any tools that accept SVF format, including automatic test equipment. See CoolRunner-II Application Notes for more information on how to program.In System ProgrammingAll CoolRunner-II CPLD parts are 1.8V in system program-mable. This means they derive their programming voltage and currents from the 1.8V V CC (internal supply voltage) pins on the part. The V CCIO pins do not participate in this operation, as they may assume another voltage ranging as high as 3.3V down to 1.5V. A 1.8V V CC is required to prop-erly operate the internal state machines and charge pumps that reside within the CPLD to do the nonvolatile program-ming operations. The JTAG interface buffers are powered by a dedicated power pin, V CCAUX, which is independent of all other supply pins. V CCAUX must be connected. Xilinx software is provided to deliver the bit-stream to the CPLD and drive the appropriate IEEE 1532 protocol. To that end, there is a set of IEEE 1532 commands that are supported in the CoolRunner-II CPLD parts. Programming times are less than one second for 32 to 256 macrocell parts. Program-ming times are less than four seconds for 384 and 512 mac-rocell parts. Programming of CoolRunner-II CPLDs is only guaranteed when operating in the commercial temperature and voltage ranges as defined in the device-specific data sheets.On-The-Fly Reconfiguration (OTF)Xilinx ISE 5.2i supports OTF for CoolRunner-II CPLDs. This permits programming a new nonvolatile pattern into the part while another pattern is currently in use. OTF has the same voltage and temperature specifications as system program-ming. During pattern transition I/O pins are in high imped-ance with weak pullup to V CCIO. Transition time typically lasts between 50 and 300 µs, depending on density. See XAPP388 for more information.JTAG InstructionsTable7 shows the commands available to users. These same commands may be used by third party ATE products,as well. The internal controllers can operate as fast as 66 MHz.Power-Up CharacteristicsCoolRunner-II CPLD parts must operate under the demands of both the high-speed and the portable market places, therefore, they must support hot plugging for the high-speed world and tolerate most any power sequence to its various voltage pins. They must also not draw excessive current during power-up initialization. To those ends, the general behavior is summarized as follows:1.I/O pins are disabled until the end of power-up.2.As supply rises, configuration bits transfer fromnonvolatile memory to SRAM cells.3.As power up completes, the outputs become asconfigured (input, output, or I/O).4.For specific configuration times and power uprequirements, see the device specific data sheet. CoolRunner-II CPLD I/O pins are well behaved under all operating conditions. During power-up, CoolRunner-II devices employ internal circuitry which keeps the devices in the quiescent state until the V CCINT supply voltage is at a safe level (approximately 1.3V). In the quiescent state, JTAG pins are disabled, and all device outputs are disabled with the pins weakly pulled high, as shown in Table8. When the supply voltage reaches a safe level, all user registers become initialized, and the device is immediately available for operation, as shown in Figure12. Best results are obtained with a smooth V CC rise in less than 4 ms. Final V CC value should occur within 1 second.If the device is in the erased state (before any user pattern is programmed), the device outputs remain disabled with a weak pull-up. The JTAG pins are enabled to allow the Table 7: JTAG InstructionsCode Instruction Description 00000000EXTEST Force boundary scan data ontooutputs00000011PRELOAD Latch macrocell data intoboundary scan cells11111111BYPASS Insert bypass register betweenTDI and TDO00000010INTEST Force boundary scan data ontoinputs and feedbacks 00000001IDCODE Read IDCODE11111101USERCODE Read USERCODE11111100HIGHZ Force output into highimpedance state11111010CLAMP Latch present output state。

SFP+ 小型插槽架商品规格说明书

RESULTS PASS

PASS PASS PASS PASS

Mate and unmated modules with cages No functional damage

6 Cage Durability for 100 cycles with the latch retention

to cage

4.0 RATINGS

4.1 VOLTAGE 120 volts ac

4.2 CURRENT 0.5 amps max.

4.3 TEMPERATURE Operating: - 40°C to +85°C Non-operating: - 55°C to +105°C

4.4 DURABILITY See section 5.1 durability and module retention in cage testing.

J1

ECM No: 116984

DATE: 05/17/2017

PRODUCT SPECIFICATION FOR SFP+ CAGES

SHEET No.

2 of 10

DOCUMENT NUMBER:

747540001

CREATED / REVISED BY: DASH SUN

CHECKED BY: ROBBIE CHEN

PRODUCT SPECIFICATION

SFP+ CAGES

REVISION: ECR/ECN INFORMATION: TITLE:

J1

ECM No: 116984

DATE: 05/17/2017

PRODUCT SPECIFICATION FOR SFP+ CAGES

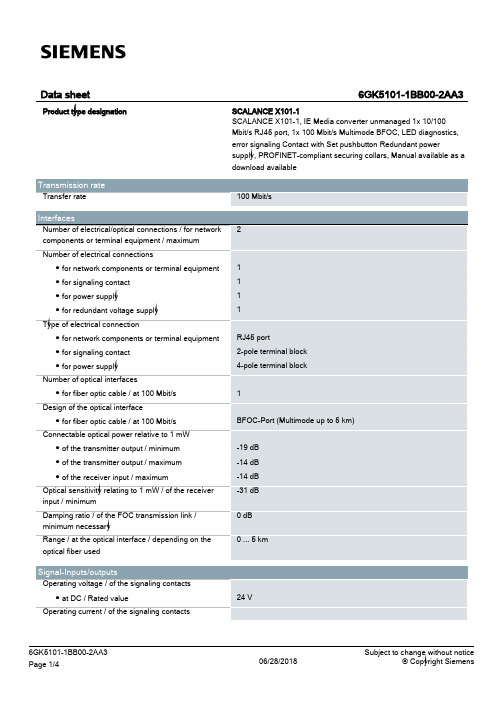

SCALANCE X101-1 商品说明书

24 V

6GK5101-1BB00-2AA3 Page 1/4

06/28/2018

Subject to change without notice © Copyright Siemens

● at DC / maximum

Supply voltage, current consumption, power loss Supply voltage ● external ● external Type of voltage / of the supply voltage Product component / fusing at power supply input Fuse protection type / at input for supply voltage Consumed current ● maximum Power loss [W] ● at DC / at 24 V

Compact 40 mm 125 mm 124 mm 0.55 kg

Yes Yes Yes

No No

FM3611: Class 1, Divison 2, Group A, B, C, D / T.., Class 1, Zone 2, Group IIC, T.. EN 600079-15 II 3 G EEx nA II T.. KEMA 06 ATEX 0021 X

Yes

Yes Yes Yes Yes Yes No 134 y

/snst

/simatic-net https:// /industry/infocenter /bilddb /cax https://

Security information

UL 60950-1, CSA C22.2 No. 60950-1 UL 1604 and UL 2279-15 (Hazardous Location), Class 1 / Division 2 / Group A, B, C, D / T.., Class 1 / Zone 2 / Group IIC / T.. EN 61000-6-3 EN 61000-6-4:2001 EN 61000-6-2:2001, EN 61000-6-4:2001 Yes Yes Yes

E28-2G4M12S 产品规格书说明书

E28-2G4M12S产品规格书SX1280 2.4GHz SPI贴片型高速LoRa模块目录第一章概述 (2)1.1 简介 (2)1.2 特点功能 (2)1.3 应用场景 (2)第二章规格参数 (3)2.1 极限参数 (3)2.2 工作参数 (3)第三章机械尺寸与引脚定义 (4)第四章基本操作 (5)4.1硬件设计 (5)4.2软件编写 (5)第五章基本应用 (6)5.1 基本电路 (6)第六章常见问题 (7)6.1 传输距离不理想 (7)6.2 模块易损坏 (7)6.3 误码率太高 (7)第七章焊接作业指导 (8)7.1 回流焊温度 (8)7.2 回流焊曲线图 (8)第八章相关型号 (9)第九章天线指南 (9)9.1 天线推荐 (9)9.2天线选择 (9)修订历史 (10)关于我们 (11)第一章概述1.1 简介E28-2G4M12S是亿佰特公司设计生产的2.4GHz射频收发模块,通信距离远;具有极低的低功耗模式流耗。

此模块为小体积贴片型(引脚间距1.27mm),模块自带高性能PCB板载天线与IPEX接口。

该系列采用52MHz工业级高精度低温漂有源晶振;保证其工业特性和其稳定性能。

采用Semtech公司的SX1280射频芯片,此芯片包含多样的物理层以及多种调制方式,如LORA,FLRC,GFSK。

特殊的调制和处理方式使得LoRa和FLRC调制的传输距离大大增加;是一款高性能物联网无线收发器,并可以兼容蓝牙协议。

出色的低功耗性能、片上DC-DC和Time-of-flight使得此芯片功功能强大,可用于智能家居、安全系统、定位追踪、无线测距、穿戴设备、智能手环与健康管理等等。

SX1280支持RSSI,用户可以根据需要实现深度的二次开发;SX1280亦集成飞行时间(time of flight),适用于测距功能。

由于该模块是纯射频收发模块,需要使用MCU驱动或使用专用的SPI调试工具。

1.2 特点功能⚫理想条件下,通信距离可达3km;⚫最大发射功率18mW,软件多级可调;⚫兼容 BLE 协议;⚫支持免许可ISM 2.4GHz频段;⚫支持0.476k~2Mbps的数据传输速率;⚫支持多种调制模式(GFSK Mode ,FLRC Mode,LoRa Mode);⚫支持1.8~3.6V供电,大于3.3V供电均可保证最佳性能;⚫工业级标准设计,支持-40~+85℃下长时间使用;⚫双天线可选(IPX/PCB),便于用户二次开发,利于集成;⚫速率可调,FLRC 调制方式下最高可达1.3Mbps;⚫卓越的抗阻塞特性;⚫测距,带有 Time-of-flight 功能。

258 Encoders 金属杆壳型绝对类型 EC18A 水抗性强、重力扭矩强 18mm 尺寸 金属

259EncodersMetal ShaftInsulatedShaftThroughShaft TypeRing TypeStandard Codes 1. The ●marks shows the ON position.2. The ●marks : Connections between terminals and the 5 (COM) are ON.Waterproof PropertyImmersion of encoder, not in operation, in water at depth of 1m at normal temperature for 30 minutes.EC18AGAPosition No.123456789101112Rotation angle (° )3060901201501802102402703003301●●●●●●2●●●●3●●●●●●4●●●●5(COM )●●●●●●●●●●●●T E R M I N A L N O .EC18AGB20401Position No.12345678910111213141516Rotation angle (° )22.54567.590112.5135157.5180202.5225247.5270292.5315337.51●●●●●●●●2●●●●●●●●3●●●●●●●●4●●●●●●●●5(COM )●●●●●●●●●●●●●●●●T E R M I N A L N O .EC18AGB20407Position No.123456789101112131415Rotation angle (° )244872961201441681922162402642883123361●●●●●●●●2●●●●●●●●3●●●●●●●●4●●●●●●●●5(COM )●●●●●●●●●●●●●●●T E R M I N A L N O .EC18A /18mm Size Insulated Shaft Type(Two phase A and B )275EncodersMetal ShaftInsulated Shaft Through Shaft TypeRing Type1. When using an infrared reflow oven, solder may sometimes not be applied. Be sure to use a hot air reflow oven or a type that uses infrared rays in combination with hot air.2. The temperatures given above are the maximum temperatures at the terminals of the encoder when employing a hot air reflow method. The temperature of the PC board and the surface temperature of the encoder may vary greatly depending on the PC board material, its size and thickness. Ensure that the surface temperature of the encoder does not rise to 250℃ or greater.3. Conditions vary to some extent depending on the type of reflow bath used. Be sure to give due consideration to this prior to use.NotesEC05E EC21CEC28C, EC35CH250℃ min.230℃ to 245℃260℃230℃ min.220℃ 230℃180℃200℃180℃150℃150℃150℃60s to 120s 60s to 120s 2 min. min.ーー3s30s to 40s 25s to 60s40sー300s max.230s max.2 times max.1 time max.1 time max.Soldering surfacetemperatureSoldering temperatureHeating timeSoldering timeNo. of soldersEC09E, EC111, EC11E, EC11M, EC11N, EC18A,EC21A, EC28A, EC35A, EC35AH, EC50A Series100℃ max.260±5℃2 min. max.5±1s 2 times max.PreheatingDip solderingReference for Dip SolderingExample of Reflow Soldering ConditionReference for Manual SolderingEC10E, EC12D, EC12E EM11BEC40A100℃ max.100℃ max.110℃ max.260±5℃260℃ max.260℃ max.1 min. max.1 min. max.1 min. max.3±1s 3s max.10s max.2 times max.2 times max.1 timeTemperature profile300200100A BC Time (s)G max.F max.H max.E max.RoomtemperatureT e m p e r a t u r e (˚C )Pre-heating DEncoders / Soldering ConditionsEC05E, EC09E, EC10E, EC111, EC11E, EC11M, EC11N, EC12D, EC12E, EC18A, EC21A, EC28A, EC35A, EC35AH, EC40A, EC50A, EM11B, EC21C, EC28C, EC35CHSeries350℃ max.3s max. 1 timeTip temperatureSoldering timeNo. of soldersSeries ABCDEFGHNo. of reflows。

山石智·感-智能内网威胁感知系统 硬件参考指南说明书

Copyright 2022 Hillstone Networks. All rights reserved.Information in this document is subject to change without notice. The software described in this document is furnished under a license agreement or nondisclosure agreement. The software may be used or copied only in accordance with the terms of those agreements. No part of this publication may be reproduced, stored in a retrieval system, or transmitted in any form or any means electronic or mechanical, including photocopying and recording for any purpose other than the purchaser's personal use without the written permission of Hillstone Networks.Hillstone Networks本文档禁止用于任何商业用途。

联系信息北京苏州地址:北京市海淀区宝盛南路1号院20号楼5层地址:苏州高新区科技城景润路181号邮编:100192 邮编:215000联系我们:https:///about/contact_Hillstone.html关于本手册本手册为硬件参考指南,帮助用户正确安装山石网科sBDS系列设备。

获得更多的文档资料,请访问:https://针对本文档的反馈,请发送邮件到:*************************山石网科https://TWNO:TW-HW-BDS-CN-V1.0-Y22M04产品中有毒有害物质或元素的名称及含量前言内容简介感谢您选用山石智·感-智能内网威胁感知系统(sBDS)产品。

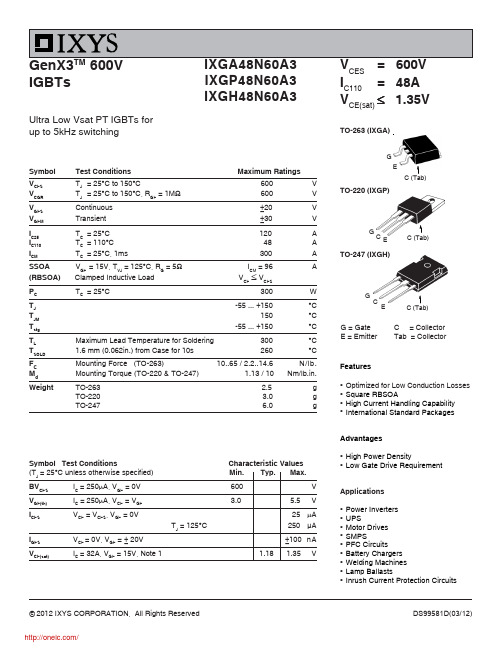

IXGH48N60A3;IXGA48N60A3;中文规格书,Datasheet资料

Symbol Test Conditions Characteristic Values (T J = 25°C unless otherwise specified) Min. Typ. Max.BV CES I C = 250μA, V GE = 0V 600VV GE(th) I C = 250μA, V CE = V GE 3.0 5.5 VI CES V CE = V CES , V GE = 0V25 μAT J = 125°C250 μAI GES V CE = 0V, V GE = ± 20V ±100 nAV CE(sat)I C = 32A, V GE = 15V, Note 11.18 1.35 VCES I C110= 48A V CE(sat)≤ 1.35VIGBTsUltra Low Vsat PT IGBTs for up to 5kHz switchingFeaturesz Optimized for Low Conduction Losses z Square RBSOAz High Current Handling Capability zInternational Standard PackagesAdvantageszHigh Power DensityzLow Gate Drive RequirementApplicationsz Power Invertersz UPSz Motor Drives z SMPSz PFC Circuits z Battery Chargers z Welding Machines z Lamp BallastszInrush Current Protection CircuitsIXGP48N60A3IXGH48N60A3TO-263 (IXGA)GEG C ETO-220 (IXGP)G = Gate C = Collector E = Emitter Tab = CollectorTO-247 (IXGH)Symbol Test ConditionsMaximum Ratings V CES T J = 25°C to 150°C600V V CGR T J = 25°C to 150°C, R GE = 1M Ω 600V V GES Continuous ±20V V GEM Transient±30VI C25T C = 25°C 120 A I C110T C = 110°C 48 AI CMT C = 25°C, 1ms 300ASSOA V GE = 15V, T VJ = 125°C, R G = 5ΩI CM = 96A (RBSOA) Clamped Inductive Load V CE ≤ V CES P C T C = 25°C300W T J -55 ... +150°C T JM 150°C T stg -55 ... +150°CT LMaximum Lead Temperature for Soldering 300°CT SOLD 1.6 mm (0.062in.) from Case for 10s 260°CF C Mounting Force (TO-263) 10..65 / 2.2..14.6 N/lb.M d Mounting Torque (TO-220 & TO-247) 1.13 / 10 Nm/lb.in.WeightTO-263 2.5g TO-220 3.0 g TO-2476.0gIXYS Reserves the Rght to Change Limits, Test Conditions and Dimensions.Notes:1. Pulse test, t ≤ 300μs, duty cycle, d ≤ 2%.2. Switching times & energy losses may increase for higher V CE (clamp), T J or R G .1 = Gate2 = Collector3 = Emitter4 = CollectorIXYS Reserves the Rght to Change Limits, Test Conditions and Dimensions.IXYS Reserves the Rght to Change Limits, Test Conditions and Dimensions.分销商库存信息:IXYSIXGH48N60A3IXGA48N60A3。

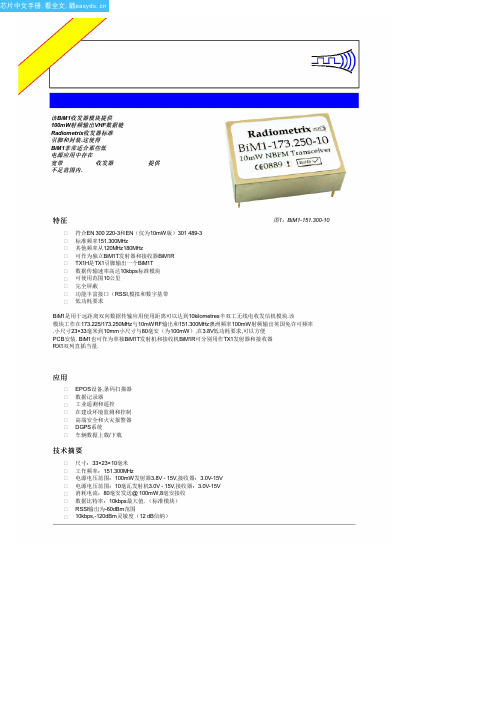

EN301489-3中文资料(List Unclassifed)中文数据手册「EasyDatasheet - 矽搜」

应用

EPOS设备,条码扫描器

数据记录器 工业遥测和遥控 在建设环境监测和控制 高端安全和火灾报警器

DGPS系统 车辆数据上载/下载

技术摘要

尺寸:33×23×10毫米 工作频率:151.300MHz 电源电压范围:100mW发射器3.8V - 15V,接收器:3.0V-15V 电源电压范围:10毫瓦发射机3.0V - 15V,接收器:3.0V-15V 消耗电流:80毫安发送@ 100mW,8毫安接收 数据比特率:10kbps最大值. (标准模块) RSSI输出为-60dBm范围 10kbps,-120dBm灵敏度(12 dB信纳)

typ.

max. units notes

-120

dBm

-115

dBm

-127

dBm

60

dB

kHz

85

dB

60

dB

70

dB

2

65

dB

-70

dBm

3

-60

dBm

3

5

kHz

400

mV P-P

7

0.8

V

TBD

%

TBD

pF

TBD

ms

2

10

ms

TBD

ms

TBD

ms

0.1 ms

8

50

80

%

8

侧视图(通过CAN)

侧视图(带CAN)

10 mm

RF GND 1 天线2 RF GND 3

4 5 无引脚 6 7 8 0电压 9

顶视图(不能够)

30.48 mm 33 mm

图 4: BiM1引 脚 和 维 43mm

18 0电压 17 Vcc 16 RX选择 15 TX选择 14 TXD 13 AF 12 RXD 11 RSSI 10 0电压

XCF128XFTG64C;中文规格书,Datasheet资料

© 2007–2010 Xilinx, Inc. XILINX, the Xilinx logo, Virtex, Spartan, ISE, and other designated brands included herein are trademarks of Xilinx in the United States and other countries. PCI, PCIe and PCI Express are trademarks of PCI-SIG and used under license. All other trademarks are the property of their respective owners.Features•In-System Programmable Flash Memory Optimized for Virtex®-5 or Virtex-6 FPGA Configuration •High-Performance FPGA Bitstream Transfer up to 800Mb/s (50MHz ×16-bits), Ideal for PCI Express® Endpoint Applications•MultiBoot Bitstream, Design Revision Storage •FPGA Configuration Synchronization (READY_WAIT) Handshake Signal•ISE® Software Support for In-System Programming via Xilinx® JTAG Cables•Standard NOR-Flash Interface for Access to Code or Data Storage•Operation over Full Industrial Temperature Range (–40°C to +85°C)•Common Flash Interface (CFI)•Low-Power Advanced CMOS NOR-Flash Process •Endurance of 10,000 Program/Erase Cycles Per Block •Power Supplies♦Industry-Standard Core Power Supply Voltage (V DD ) = 1.8V♦3.3V or 2.5V I/O (V DDQ ) Power Supply Voltage•Memory Organization♦128-Mb Main Array Capacity ♦16-bit Data Bus♦Multiple 8-Mb Bank Architecture for Dual Erase/Program and Read Operation ♦127 Regular 1-Mb Main Blocks ♦4 Small 256-Kb Parameter Blocks•Synchronous/Asynchronous Read Modes♦Power-On in Synchronous Burst Read Mode ♦Asynchronous Random Access Mode ♦Accelerated Asynchronous Page Read Mode •Protection♦Default Block Protection at Power-Up ♦Hardware Write Protection (when V PP = V SS )•Security♦Unique Device Number (64-bits)♦One-Time-Programmable (OTP) Registers•Small-Footprint (10mm ×13mm) FT64 PackagingDescriptionA reliable compact high-performance configurationbitstream storage and delivery solution is essential for the high-density FPGAs. Platform Flash XL is the industry's highest performing configuration and storage device and is specially optimized for high-performance FPGAconfiguration. Platform Flash XL integrates 128Mb of in-system programmable flash storage and performance features for configuration within a small-footprint FT64 package (Figure 5). Power-on burst read mode anddedicated I/O power supply enable Platform Flash XL to mate seamlessly with the native SelectMAP configuration interface. A wide, 16-bit data bus delivers the FPGAconfiguration bitstream at speeds up to 800Mb/s without wait states. See UG438, Platform Flash XL Configuration and Storage Device User Guide , for system-level usage and performance considerations.Platform Flash XL is supported for use with Virtex-5 or Virtex-6 FPGAs only . Use with older Virtex families, Spartan® families, or AES encrypted bitstreams is not supported.Platform Flash XL is a non-volatile flash storage solution, optimized for FPGA configuration. The device provides a READY_WAIT signal that synchronizes the start of the FPGA configuration process, improving both system reliability and simplifying board design. Platform Flash XL can download an XC5VLX330 bitstream (79,704,832bits) in less than 100ms, making the configuration performance of Platform Flash XL ideal for PCI Express endpoints and other high-performance applications.Platform Flash XL is a single-chip configuration solution with additional system-level capabilities. A standard NOR flash interface (Figure 2) and support for common flash interface (CFI) queries provide industry-standard access to the device memory space. The Platform Flash XL's 128Mb capacity can typically hold one or more FPGA bitstreams. Any memory space not used for bitstream storage can be used to hold general purpose data or embedded processor code.Platform Flash XL High-Density Configurationand Storage DeviceDS617 (v3.0.1) January 07, 2010Product SpecificationPlatform Flash XL support is integrated with the Xilinx design and debug tool suite.The iMPACT application,included with the ISE software, supports indirect, in-system programming of Platform Flash XL via the IEEE Standard 1149.1 (JT AG) port on the FPGA for prototype programming (Figure 3).Notes:1.System considerations can lower the configuration clock frequency below the maximum clock frequency for the device. To determine the maximum configuration clock frequency, check the minimum clock period (T KHKH ) for the chosen I/O voltage range (VDDQ ), the clock High-to-output valid time (T KHQV ), and the FPGA SelectMAP setup time.Figure 1:Platform Flash XL Delivers Reliable, High-Performance FPGA ConfigurationFigure 2:Standard NOR Flash Interface for UserAccess to MemoryFigure 3:Indirect Programming Solution for Platform Flash XLFlash Memory Architecture OverviewPlatform Flash XL is a 128-Mb (8Mb×16) non-volatile flash memory. The device is in-system programmable with a 1.8V core (V DD) power supply. A separate I/O (V DDQ) power supply enables I/O operation at 3.3V or 2.5V. An optional 9V V PP power supply can accelerate factory programming.A common flash interface (CFI) provides access to device memory (Figure3, page3). Moreover, Platform Flash XL supports multiple read modes. A 23-bit address bus provides random read access to each 16-bit word. Four words occupy each page for accelerated page mode reads. The device powers-up in a synchronous burst read mode capable of sequential read rates up to 54MHz.Platform Flash XL has a multiple-bank architecture. An array of 131 individually erasable blocks are divided into 16, 8-Mb banks. Fifteen main banks contain uniform blocks of64Kwords, and one parameter bank contains seven main blocks of 64Kwords, plus four parameter blocks of 16Kwords.Note:The device is electronically erasable at the block level and programmable on a word-by-word basis.The multiple-bank architecture allows dual operations — read operations can occur on one bank while a program or erase operation occurs in a different bank. However, only one bank at a time is allowed to be in program or erase mode. Burst reads are allowed to cross bank boundaries. Table1 summarizes the bank architecture, and the memory map is shown in Figure4, page5. The parameter blocks are located at the top of the memory address space in Platform Flash XL.Each block can be erased separately. Erase operations can be suspended in order to perform a program or read operation in any other block and then resumed. Program operations can be suspended to read data at any memory location except for the one being programmed, and then resumed.Program and erase commands are written to the command interface of the memory. An internal program/erase controller takes care of the timing necessary for program and erase operations. The end of a program or erase operation can be detected and any error conditions identified in the status register. The command set required to control the memory is consistent with JEDEC standards. The device supports synchronous burst read and asynchronous read from all blocks of the memory array. At power-up, the device is configured for synchronous read. In synchronous burst read mode, data is output on each clock cycle at frequencies of up to 54MHz. The synchronous burst read operation can be suspended and resumed. When the bus is inactive during asynchronous read operations, the device automatically switches to an automatic standby mode. In this condition the power consumption is reduced to the standby value, and the outputs are still driven.Platform Flash XL features an instant, individual block-locking scheme, allowing any block to be locked or unlocked with no latency, and enabling instant code and data protection. All blocks have three levels of protection. Blocks can be locked and locked-down individually preventing any accidental programming or erasure. There is an additional hardware protection against program and erase: when V PP = V PPLK all blocks are protected against program or erase. All blocks are locked at power-up.The device features a separate region of 17 programmable registers whose values can be protected against further programming changes. Sixteen of these registers are each 128-bits in size, with the 17th register subdivided into two 64-bit registers. One of the 64-bit registers contains a factory preprogrammed, unique device number, permanently protected against modification. The second 64-bit register is user-programmable.All bits within these registers (except for the permanently-protected unique number register) are one-time-programmable (OTP) — each bit can be programmed only once from a one-value to a zero-value.T wo protection lock registers can be programmed to lock any of the 17 protectable registers against further changes. One protection lock register contains bits that determine the protection state of the two special 64-bit registers. The bit corresponding to the unique device number register is pre-programmed to ensure the unique device number register is permanently protected against modification. The second protection lock register contains OTP bits that correspond the protection state each of the remaining 16 registers. Platform Flash XL is available in a 10×13mm, 1.0mm-pitch FT64 package and supplied with all the bits erased (set to '1').Table 1: Bank ArchitectureNumber Bank Size ParameterBlocks Main BlocksParameterBank8 Mbits 4 blocks of16Kwords7 blocks of64KwordsBank 18 Mbits–8 blocks of64KwordsBank 28 Mbits–8 blocks of64KwordsBank 38 Mbits–8 blocks of64Kwords …………Bank 148 Mbits–8 blocks of64KwordsBank 158 Mbits–8 blocks of64KwordsFigure 4:Platform Flash XL Memory Map (Address Lines A22 – A0)Pinout and Signal DescriptionsSee Figure5 and Table2 for a logic diagram and brief overview of the signals connected to this device.Address Inputs (A22-A0)The Address inputs select the words in the memory array to access during Bus Read operations. During Bus Write operations they control the commands sent to the Command Interface of the Program/Erase Controller. Data Inputs/Outputs (DQ15-DQ0)The Data I/O output the data stored at the selected address during a Bus Read operation or input a command or the data to be programmed during a Bus Write operation. Chip Enable (E)The Chip Enable input activates the memory control logic, input buffers, decoders and sense amplifiers. When Chip Enable is at V IL and Reset is at V IH, the device is in active mode. When Chip Enable is at V IH, the memory is deselected, the outputs are high impedance, and the power consumption is reduced to the standby level.Output Enable (G)The Output Enable input controls data outputs during the Bus Read operation of the memory. Before the start of the first address latching sequence (FALS), the Output Enable input must be held Low before the clock starts toggling. Write Enable (W)The Write Enable input controls the Bus Write operation of the memory’s Command Interface. The data and address inputs are latched on the rising edge of Chip Enable or Write Enable, whichever occurs first.Table 2:Signal NamesSignal Name Function Direction A22-A0Address Inputs InputsDQ15-DQ0Data Input/Outputs,Command InputsI/OE Chip Enable InputG Output Enable InputW Write Enable InputRP Reset InputWP Write Protect InputK Clock InputL Latch Enable Input READY_WAIT Ready/Wait I/O V DD Supply Voltage –V DDQSupply Voltage forInput/Output Buffers–V PPOptional(1) SupplyVoltage for FastProgram and Erase–V SS Ground –V SSQ Ground Input/outputSupply–NC Not ConnectedInternally–Notes:1.T ypically, V PP is tied to the V DDQ supply on a board. See the V PPProgram Supply Voltage section for alternate options.Figure 5:Logic DiagramWrite Protect (WP)Write Protect is an input that gives an additional hardware protection for each block. When Write Protect is at V IL, the Lock-Down is enabled, and the protection status of the Locked-Down blocks cannot be changed. When Write Protect is at V IH, the Lock-Down is disabled, and the Locked-Down blocks can be locked or unlocked.Reset (RP)The Reset input provides a hardware reset of the memory. When Reset is at V IL, the memory is in reset mode: the outputs are high impedance, and the current consumption is reduced to the Reset supply current I DD2. After Reset all blocks are in the Locked state, and the Configuration Register is reset. When Reset is at V IH, the device is in normal operation. Exiting reset mode the device enters the synchronous read mode and the FALS is executed.Notes:1.See the FT64/FTG64 package specifications at /support/documentation/package_specifications.htm.Figure 6:FT64 Package Connections (Top View through Package)Latch Enable (L)Latch Enable latches the address bits on its rising edge. The address latch is transparent when Latch Enable is at V IL and inhibited when Latch Enable is at V IH.The Latch Enable (L) signal must be held at V IH during the power-up phase, during the FALS restart phase and through the entire FALS.In asynchronous mode, the address is latched on L going High. or addresses are sent continuously if L is held Low. During Write operations, L can be tied Low (V IL) to allow the addresses to flow through.Clock (K)The Clock input synchronizes the memory to the FPGA during synchronous read operations. The address is latched on a Clock edge (rising or falling, according to the configuration settings) when Latch Enable is at V IL. Clock is ignored during asynchronous read and in write operations. Ready/Wait (READY_WAIT)Caution!The READY_WAIT requires an external pull-upresistor to V DDQ. The external pull-up resistor must besufficiently strong to ensure a clean, Low-to-High transition within less than one microsecond (T RWRT) when theREADY_WAIT pin is released to a high-impedance state. READ Y_WAIT can perform one of two functions. By default, READY_WAIT is an input/open-drain ready signal coordinating the initiation of the device's synchronous read operation with the start of an FPGA configuration sequence. Optionally, READ Y_WAIT can be dynamically configured as an output wait signal, indicating a wait condition during a synchronous read operation.Upon a power-on reset (POR) or RP-pin reset event, the device drives READ Y_WAIT to V IL until the device is ready to initiate a synchronous read or receive a command. When the device reaches an internal ready state from a reset condition, READY_WAIT is released to a high-impedance state (an external pull-up resistor to V DDQ is required to externally pull the READY_WAIT signal to a valid input High). The device waits until the READY_WAIT input becomes a valid input High before permitting a synchronous read or accepting a command. Connecting the READY_WAIT to the FPGA INIT_B pin in a wired-and circuit creates a handshake coordinating the initiation of the device synchronous read with the start of the FPGA configuration sequence.When READY_WAIT is an input/open-drain ready signal, the system can drive READY_WAIT to V IL to reinitiate a synchronous read operation. A valid address must be provided to the device for a reinitiated synchronous read operation. Optionally, READY_WAIT can be configured as an output signaling a wait condition during a synchronous read operation. The wait condition indicates a clock cycle during which the output data is not valid. When configured as an output wait signal, READY_WAIT is high impedance when Chip Enable is at V IH or Output Enable is at V IH. Only when configured as a wait signal, READ Y_WAIT can be configured to be active during the wait cycle or one clock cycle in advance, and the READY_WAIT polarity can be configured. V DD Supply VoltageV DD provides the power supply to the internal core of the memory device and is the main power supply for all operations (Read, Program and Erase).V DDQ Supply VoltageV DDQ provides the power supply to the I/O pins and enables all outputs to be powered independently of V DD.V PP Program Supply VoltageV PP is either a control input or a power supply pin, selected by the voltage range applied to the pin.If V PP is kept in a low voltage range (0V to V DDQ), V PP is seen as a control input. In this case a voltage lower than V PPLK gives absolute protection against program or erase, while V PP in the V PP1 range enables these functions. V PP is only sampled at the beginning of a program or erase — a change in its value after the operation starts does not have any effect, and all program or erase operations continue.If V PP is in the range of V PPH, the signal acts as a power supply pin. In this condition V PP must be stable until the Program/Erase algorithm is completed.V SS GroundV SS Ground is the reference for the core supply and must be connected to the system ground.V SSQ GroundV SSQ Ground is the reference for the input/output circuitry driven by V DDQ. V SSQ must be connected to V SS.Note:Each device in a system should have V DD, V DDQ and V PP decoupled with a 0.1 μF ceramic capacitor close to the pin (high-frequency, inherently low-inductance capacitors should be placedTable 3:Latch Enable Logic Levels in Synchronous and Asynchronous ModesOperation Asynchronous SynchronousBus Read X V IHBus Write X or toggling X or togglingAddress Latch T oggling T oggling Standby X XReset V IH V IHFALS V IH V IHPower-up V IH V IHNotes:1.See waveforms in the "DC and AC Parameters" section fordetails.as close as possible to the package). The PCB track widths should be sufficient to carry the required V PP program and erase currents.FPGA Configuration OverviewPlatform Flash XL enables the rich set of FPGAconfiguration features without additional glue logic. The device delivers the FPGA bitstream at power-on through a 16-bit data bus at data rates up to 800Mb/s. The FPGA can also be configured from one of many design/revisionbitstreams stored in the device. These revision bitstreams are accessed through the FPGA's MultiBoot addressing and fallback features available in specific system configurations with Platform Flash XL. For detailed descriptions of the FPGA configuration features and configuration procedure, refer to the respective FPGA configuration user guide.At a high level, the general procedure for FPGA configuration from Platform Flash XL is as follows:1. A system event, such as power-up, initiates the FPGAconfiguration process. The FPGA drives its INIT_B pin Low while it clears its configuration memory. The Platform Flash XL drives its READY_WAIT pin Low during its reset period.2.When ready, the FPGA and Platform Flash XL releasetheir respective INIT_B and READY_WAIT pins. An external resistor pulls the connectedINIT_B-READY_WAIT signal from Low to High, synchronizing the start of the FPGA configuration process.3.At the start of the configuration process, the FPGAsamples its mode pins to determine its configuration mode. For Master BPI-Up mode, the FPGA outputs an address to read from the flash. For Slave SelectMAP mode, onboard resistors set the initial flash read address.4.The Platform Flash XL latches the initial address fromthe FPGA or from onboard resistor settings into its internal address counter and the Platform Flash XL outputs the first 16-bit word.5.The bitstream is synchronously transferred from thePlatform Flash XL to the FPGA. During eachsuccessive FPGA CCLK period, the Platform Flash XL increments its internal address counter and outputs the next 16-bit word of the bitstream for the FPGA to consume.6.At the end of the configuration process, the FPGA startsoperation of the loaded bitstream and either drives DONE High or releases DONE to High, indicating the completion of the configuration procedure.Platform Flash XL can configure the FPGA in Slave SelectMAP (x16) (recommended for maximumperformance), Master SelectMAP (x16), or Master BPI-Up (x16) configuration mode. See Table 4 for a summary of attributes for different configuration modes and memories.Table 4:Overview of FPGA Configuration from Platform Flash XL and Standard BPI FlashPlatform Flash XLThird-Party Standard BPIFlash(110-ns Access Time)High-Performance Configuration ModeStandard BPI Flash Compatibility Mode FPGA Configuration Mode Slave SelectMAP mode (x16 data bus width)Master BPI-Up mode (x16 data bus width)Master BPI-Up mode (x16 data bus width)Guaranteed BitstreamTransfer Bandwidth at Best Clock Setting800Mb/s (1)248Mb/s (2)78Mb/s (3)Virtex-5 FPGA Support 999Virtex-6 FPGA Support 999ISE Software Programming Support99For limited setups (4)MultiBoot Capable 999Notes:1.The 800Mb/s rate is achieved using a Virtex-5 FPGA with an external 50MHz configuration clock source. Specific speed grades of the Virtex-6 FPGA or system-level considerations can limit the configuration performance to less than 800Mb/s.2.Bandwidth is based on an example Virtex-5 FPGA considering F MCCKTOL and BitGen ConfigRate =31MHz (nominal frequency).3.Bandwidth is based on an example Virtex-5 FPGA considering F MCCKTOL and BitGen ConfigRate =17MHz (nominal frequency), bpi_page_size =4, and bpi_1st_read_cycle =4. First word access time =110ns; Page word access time =25ns.4.See XAPP973, Indirect Programming of BPI PROMs with Virtex-5 FPGAs.Slave SelectMAP Configuration Mode Platform Flash XL achieves maximum configuration performance when the FPGA is in Slave SelectMAP configuration mode. In the Slave SelectMAP mode, a stable, external clock source can drive the synchronous bitstream transfer from the device to the FPGA up to the maximum burst read frequency (T CLK). See the SelectMAP Configuration Interface section in the respective FPGA Configuration User Guide for details of the Slave SelectMAP mode.Note:The FPGA fallback feature is disabled in the Slave SelectMAP mode.See UG438, Platform Flash XL Configuration and Storage Device User Guide, for guidance and examples of FPGAs connected to a Platform Flash XL for Slave SelectMAP configuration mode.Alternate Configuration ModesPlatform Flash XL is optimized for the Slave SelectMAP configuration mode. Alternatively, Platform Flash XL can configure an FPGA via the Master SelectMAP orMaster BPI-Up mode—albeit with compromises in configuration speed. See the respective FPGA configuration user guide for details regarding the Master SelectMAP mode or Master BPI-Up mode.See UG438, Platform Flash XL Configuration and Storage Device User Guide, for additional information on using the Platform Flash XL with the FPGA in Master SelectMAP or Master BPI-Up mode.Programming OverviewProgramming solutions satisfying the requirements for each product phase are available for Platform Flash XL. ISE software provides integrated programming support for the FPGA design engineer in the prototyping environment. Third-party programming support is also available for the demands of the manufacturing environments.iMPACT Programming Solution for Prototype FPGA DesignsXilinx ISE software has integral support for in-system programming enabling rapid develop-program-and-test cycles for prototype FPGA designs. The software can compile the FPGA design into a configuration bitstream and program the bitstream into a Platform Flash XL in-system via a Xilinx JTAG cable (Figure7).The iMPACT software tool within the ISE software suite formats the FPGA user design bitstream into a flash memory image file and programs the device via a Xilinx JTAG cable connection to the JTAG port of the FPGA. For the programming process, the iMPACT software first downloads a pre-built bitstream containing an in-system programming engine into the FPGA. Then, the iMPACT software indirectly programs the FPGA user design bitstream into a Platform Flash XL via the downloadedin-system programming engine in the FPGA.Note:For iMP ACT software indirect in-system programming support, a specific set of connections is required between the FPGA and Platform Flash XL. See UG438, Platform Flash XL Configuration and Storage Device User Guide, for recommended connections. iMP ACT supports reading and writing of only the main memory array. iMP ACT does not support reading or writing of special data registers, for example, electronic signature codes, protection registers, or OTP registers.Production Programming SolutionsFor the requirements of manufacturing environments, multiple solutions exist for programming Platform Flash XL. Programming support is available for the common production programming platforms.Note:Check with the third-party vendor for the availability of Platform Flash XL programming support.Device ProgrammersDevice programmers can gang program a high volume of Platform Flash XL in an minimum of time. Third-party device programmer vendors, such as BPM Microsystems, support programming of Platform Flash XL.See /support/programr/dev_sup.htm for a sample list of third-party programmer vendors supporting Platform Flash XL.Device programmers require the array data in the form of a standard PROM formatted data file, such as MCS. The FPGA .bit file is not a valid data input format for third-party device programmers. See the Platform Flash XL Configuration and Storage Device User Guide for instructions on preparing a programming file.Figure 7:Integrated FPGA Design and In-System Programming Solution for Platform Flash XL分销商库存信息: XILINXXCF128XFTG64C。

Nexus 3048 Quick Configuration Guide v1.2

Nexus 3048 QuickConfiguration Guide目录0.综述 (2)0.1 版本 (2)0.2 文档概述 (2)0.3 参考资料 (2)1.Hardware Installation (3)2.Software Upgrade (5)2.1 NX-OS Upgrade (5)2.2 License Installation (7)3.vPC Configuration (9)0.综述0.1 版本0.2 文档概述第一章:介绍了Nexus 3048的硬件配置信息以及上架安装步骤。

第二章:介绍了Nexus 3048的NX-OS升级方法。

介绍了Nexus 3048的License导入方法。

第三章:介绍了采用vPC技术所带来的好处。

介绍了vPC的术语及2种部署拓扑类型。

介绍了vPC的配置。

0.3 参考资料●Cisco官方文档《Cisco Nexus 3000 Series Hardware Installation Guide》●Cisco官方文档《Virtual PortChannel Quick Configuration Guide》●Cisco官方文档《Design and Configuration Guide: Best Practices for Virtual PortChannels (vPC) on Cisco Nexus 7000 Series Switches》●VMware官方文档《VMware KB_ Sample configuration of EtherChannel _ LinkAggregation Control Protocol (LACP) with ESXi_ESX and Cisco_HP switches》1.Hardware InstallationNexus 3048 Datasheet其外观如下图所示,需要注意的是,接口密集的一面为背面。

BNS 260 生活用电器安全设备手册说明书

DataOrdering dataProduct type descriptionBNS 260-11/01ZG-R Article number (order number)101184376EAN (European Article Number)4030661321745eCl@ss number, Version 9.027-27-24-02CertificationsCertificates DGUVTÜVcULus EACGeneral dataProduct nameBNS 260StandardsIEC 60947-5-3 BG-GS-ET-14 Installation conditions(mechanical)quasi-flush Enclosure materialGlass-fibre, reinforced thermoplastic Gross weight 60 g General data - FeaturesCoding Yes BNS260-11/01ZG-RLong lifeSmall bodyPre-wired cableno mechanical wear26 mm x 36 mm x 13 mmInsensitive to soilingThermoplastic enclosure Concealed mounting possible Insensitive to transverse misalignmentIntegral System Diagnostics,YesstatusNumber of openers2Number of shutters1Number of safety contacts2Number of cable wires6Safety appraisalStandards ISO 13849-1Mission Time20 Year(s)Safety appraisal - Safety outputsB10d- Value Normally-closed25,000,000 Operationscontact/Normally open contact(NC/NO)Mechanical dataActuating element MagnetDoor hinge RightEnsured switch distance "ON" S5 mmaoEnsured switch distance "OFF" S15 mmarAxial misalignment, a horizontal and vertical misalignment of the safetysensor and the actuator are tolerated. The possible misalignment dependson the distance of the active surfaces of the sensor and the actuator. Thesensor remains active within the tolerance range.Direction of motion Head-on to the active surfaceMechanical data - Connection techniqueTerminal Connector CableLength of cable 1 mWire cross-section0.25 mm2Material of the Cable mantle PVCMechanical data - DimensionsHeight of sensor36 mmLength of sensor13 mmWidth of sensor26 mmAmbient conditionsProtection class IP67Ambient temperature, minimum-25 °CAmbient temperature, maximum+70 °CStorage and transporttemperature, minimum-25 °CStorage and transporttemperature, maximum+70 °CResistance to vibrations to EN60068-2-610 … 55 Hz, amplitude 1 mmRestistance to shock30 g / 11 msElectrical dataVoltage type DC (direct current)Switching voltage, maximum24 VDCSwitching current, maximum0.01 ASwitching capacity, maximum0.24 WSwitching frequency, maximum 5 HzStatus indicationNote (Integral SystemDiagnostics, status )The LED is illuminated when the guard is closed. Scope of deliveryIncluded in delivery Actuators must be ordered separately. AccessoryRecommendation (actuator)BPS 260SRB-E-301STSRB-E-201LCNotesNote (General)Contact symbols shown for the closed condition of the guard device. The contact configuration for versions with or without LED is identical.Circuit exampleNote (Wiring diagram)Contact S21-S22; S13-S14 must be integrated in the safety circuit. Ordering codeProduct type description:BNS 260-(1)(2)Z(3)-(4)-(5)(1)11 1 NO contacts/1 NC contact02 2 NC contact(2)without with diagnostic output/01 1 NC contact(3)without without LED switching conditions displayG with LED switching conditions display(4)without Pre-wired cableST with connector(5)L Door hinge on left-hand sideR Door hinge on right-hand sidePicturesProduct picture (catalogue individual photo)ID: kbns2f23| 314,7 kB | .jpg | 352.778 x 246.239 mm - 1000 x 698Pixel - 72 dpi| 25,0 kB | .png | 74.083 x 51.858 mm - 210 x 147Pixel - 72 dpi| 39,7 kB | .jpg | 27.093 x 18.881 mm - 320 x 223 Pixel- 300 dpiDimensional drawing basic componentID: kbns2g05| 131,1 kB | .jpg | 352.425 x 417.336 mm - 999 x 1183Pixel - 72 dpi| 4,5 kB | .png | 73.731 x 87.489 mm - 209 x 248 Pixel- 72 dpi| 34,5 kB | .jpg | 112.536 x 133.35 mm - 319 x 378Pixel - 72 dpi| 37,3 kB | .cdr |DiagramID: kbns2k04| 25,1 kB | .jpg | 112.889 x 27.164 mm - 320 x 77 Pixel- 72 dpi| 19,5 kB | .cdr |Characteristic curveID: kbns2d03| 36,8 kB | .cdr || 40,4 kB | .jpg | 112.889 x 74.789 mm - 320 x 212Pixel - 72 dpi| 18,5 kB | .png | 74.083 x 49.036 mm - 210 x 139Pixel - 72 dpiCharacteristic curveID: kbns2d02| 19,2 kB | .png | 74.083 x 49.389 mm - 210 x 140Pixel - 72 dpi| 40,8 kB | .jpg | 112.889 x 75.142 mm - 320 x 213Pixel - 72 dpi| 36,3 kB | .cdr |Clipart| 20,1 kB | .cdr || 1,7 kB | .png | 74.083 x 52.564 mm - 210 x 149 Pixel- 72 dpiK.A. Schmersal GmbH & Co. KG, Möddinghofe 3, D-42279 WuppertalThe details and data referred to have been carefully checked. Images may diverge from original. Further technical data can be found in the manual. Technical amendments and errors possible.Generated on 08.07.2020 19:14:08。

微讯VSC8484数据手册:四通道WAN LAN 背板XAUI到SFP+ KR接收器说明书