集成电子学(第四章)

第四章光刻技术

二,光刻版(掩膜版)

基版材料:玻璃,石英. 要求:在曝光波长下的透光度高,热膨胀系数 与掩膜材料匹配,表面平坦且精细抛光.

二,光刻版(掩膜版)

掩膜版的质量要求 若每块掩膜版上图形成品率=90%,则 6块光刻版,其管芯图形成品率=(90%)6=53% 10块光刻版,其管芯图形成品率=(90%)10=35% 15块光刻版,其管芯图形成品率=(90%)15=21% 最后的管芯成品率当然比其图形成品率还要低 ①图形尺寸准确,符合设计要求; ②整套掩膜版中的各块版应能依次套准,套准误差应尽可能小; ③图形黑白区域之间的反差要高; ④图形边缘要光滑陡直,过渡区小; ⑤图形及整个版面上无针孔,小岛,划痕等缺陷; ⑥固耐用,不易变形.

三,光刻机(曝光方式)

④1:1扫描投影光刻机(美国Canon公司)

三,光刻机(曝光方式)

⑤分步重复投影光刻机--Stepper DSW:direct-step-on-wafer ⅰ)原理: 采用折射式光学系统和4X~5X的缩小透镜. 曝光场:一次曝光只有硅片的一部分,可以大大 提高NA(0.7),并避免了许多与高NA有关的聚 焦深度问题,加大了大直径硅片生产可行性. 采用了分步对准聚焦技术.

一,光刻胶

4.感光机理 ①负胶

聚乙烯醇肉桂酸脂-103B,KPR

一,光刻胶

双叠氮系(环化橡胶)-302胶,KTFR

一,光刻胶

②正胶 邻-叠氮萘醌系-701胶,AZ-1350胶

二,光刻版(掩膜版)

掩膜版在集成电路制造中占据非常重要的地位,因为 它包含着欲制造的集成电路特定层的图形信息,决定 了组成集成电路芯片每一层的横向结构与尺寸. 所用掩膜版的数量决定了制造工艺流程中所需的最少 光刻次数. 制作掩膜版首先必须有版图.所谓版图就是根据电路 ,器件参数所需要的几何形状与尺寸,依据生产集成 电路的工艺所确定的设计规则,利用计算机辅助设计 (CAD)通过人机交互的方式设计出的生产上所要求 的掩膜图案.

数字电子技术基础第四章重点最新版

发

这种触发方式称为边沿触发式。

器

EXIT

集成触发器

主从触发器和边沿触发器有何异同?

空翻可导致电路工作失控。

EXIT

集成触发器

4.3 无空翻触发器

主要要求:

了解无空翻触发器的类型,掌握其工作特点。 能根据触发器符号识别其逻辑功能和触发方式, 并进行波形分析。

EXIT

集成触发器

一、无空翻触发器的类型和工作特点

主

工作特点:CP = 1 期间,主触发器接收

从 输入信号;CP = 0 期间,主触发器保持 CP

EXIT

集成触发器

2. 工作原理及逻辑功能 Q 0 触发器被工置作0原1理Q

G1 11

1 SD

输入 RD SD 00 01 10 11

输出 QQ

01

G2

RD 0 功能说明

触发器置 0

EXIT

2. 工作原理及逻辑功能

集成触发器

Q 1 触发器被置 1 0 Q

G1

0 SD

输入 RD SD 00 01 10 11

触发器置 0 触发器置 1 触发器保持原状态不变

EXIT

2. 工作原理及逻辑功能

Q 1

G1

0 SD

输入 RD SD 00 01 10 11

输出

QQ 不定

01 10 不变

集成触发器

Q

输出既非 0 状态,

1 也非 1 状态。当 RD 和 SD 同时由 0 变 1 时, 输出状态可能为 0,也

G2 可能为 1,即输出状态 不定。因此,这种情况

EXIT

四、一些约定

集成触发器

1态: Qn=1,Qn=0 0态: Qn=0,Qn=1

集成电路教案

《半导体集成电路》课程教学教案课程总体介绍:教材:选用清华大学出版社出版的朱正涌编写的高等学校电子信息类规划教材《半导体集成电路》一书。

根据同学的基础情况参考了上海科技出版社张延庆,张开华编写《半导体集成电路》。

1.该教材参考教学学时为120学时。

2.本教案按教学学时数:64学时编制。

3.教学内容学时分配:第一篇半导体集成电路制造工艺与寄生效应11学时第0章绪论2学时第一章半导体集成电路基本制造工艺5学时第二章集成电路的寄生效应4学时第二篇双极型逻辑集成电路21学时第三章TTL集成电路11学时第四章TTL中大规模集成电路设计与版图设计8学时第五章ECL电路与IIL电路2学时第三篇MOS 逻辑集成电路24学时第六章MOS反相器与传输们10学时第七章MOS基本逻辑门与版图设计8学时第八章MOS存储器6学时第四篇模拟集成电路8学时第九章模拟集成电路中的元器件与基本单元8学时教案结构:课程内容;课程重点;课程难点;基本概念;基本要求。

基本概念视同学的基础可以适当删减。

:课程教案:第一篇半导体集成电路制造工艺与寄生效应11学时第0章绪论2学时第一章半导体集成电路基本制造工艺5学时第二章集成电路的寄生效应4学时绪论2学时课程内容: 认识集成电路;集成电路的定义:集成电路的应用特点;集成电路分类。

1 半导体集成电路的发展史2 集成电路发展的特点3 半导体集成电路的分类4 课程内容介绍及要求课程重点:介绍了何谓集成电路,集成电路发展过程,集成电路是如何分类的(即可分为膜集成电路.半导体集成电路和混合集成电路。

半导体集成电路)是以制造工艺分类的,以集成电路的发展史集成电路有何特点;介绍了何谓半导体集成电路,半导体集成电路的分类(即按照电路中晶体管的导电载流子状况分类,可分为双极型集成电路和单极型集成电路两种;按照电路工作性质分类,可分为数字集成电路和模拟集成电路两种),半导体集成电路的重要概念-集成度,以及半导体集成电路的优点(即体积小重量轻;技术指标先进可靠性高以及便于大批量生产和成本低等)。

集成电子技术基础教程浙大第三版上册答案

集成电子技术基础教程浙大第三版上册答案第一章线性电路基本理论1.1 电路分析方法1.节点电流法(KCL)2.超节点法3.网孔电流法(KVL)4.超网孔法5.节点电压法(KVL)1.2 基本电路元件1.电阻–定义:电流和电压成正比关系–特性:无记忆、无方向性、无频率依赖2.电容–定义:电压和电流成正比关系–特性:记忆性、有方向性、频率依赖3.电感–定义:磁场中储存能量–特性:记忆性、有方向性、频率依赖第二章二极管与其应用2.1 二极管的结构和特性1.P-N 结构–P型半导体:多数载流子为空穴–N型半导体:多数载流子为电子2.二极管的特性–正向偏置:导通状态,低电阻–反向偏置:截止状态,高电阻2.2 二极管的应用1.整流电路–单相半波整流电路–单相全波整流电路–三相整流电路2.限幅电路–正向限幅电路–反向限幅电路3.齐乳二极管–齐乳二极管的应用场景4.LED(发光二极管)–LED的特性和应用第三章功率放大电路3.1 小信号放大设计基本思路1.小信号模型2.低频二极管放大电路设计3.常用的小信号放大电路配置–共射放大电路–共集放大电路–共基放大电路–差模放大电路3.2 大信号放大电路设计1.类A放大器2.类AB放大器3.类B放大器4.类C放大器第四章 MOS场效应管及其应用4.1 MOSFET概述1.MOSFET的结构和工作原理2.MOSFET的I-V 特性曲线4.2 MOSFET的应用1.放大电路–CS放大电路–CD放大电路–CG放大电路2.开关电路–NMOS开关电路–PMOS开关电路第五章双极型及其应用5.1 双极型晶体管概述1.双极型晶体管的结构和工作原理2.双极型晶体管的I-V 特性曲线5.2 双极型晶体管的应用1.放大电路–CE放大电路–CB放大电路–CC放大电路2.开关电路–NPN开关电路–PNP开关电路以上是《集成电子技术基础教程浙大第三版上册》的答案总结,希望对您的学习有所帮助。

清华大学《数字集成电路设计》周润德 第4章 互连线

V = V inc (1 + ρ )

I = I inc (1 − ρ )

2004-9-22

清华大学微电子所《 数字大规模集成电路》 周润德

第 4 章 第 27 页

源电阻 > 特征阻抗 源电阻 < 特征阻抗

无损传输线的瞬态响应

源电阻 = 特征阻抗

2004-9-22

源电阻 < 特征阻抗 有限的上升斜率

清华大学微电子所《 数字大规模集成电路》 周润德

第 4 章 第 23 页

考虑连线RC延时的准则

• 当连线的 RC 延时与驱动门的延时相比较大,即:

(tpRC >> tpgate )时需要考虑连线的 RC 延时。

需要考虑RC延时的连线临界长度为:

Lcrit >> √ tpgate/0.38 rc

• 当连线输入端信号的上升或下降时间小于连线的上升或下

一般制造商会提供每层的面电容和周边电容。 实际设计时,可以查表或查图。

考虑性能时,电容的计算:

1。要用制造后的实际尺寸, 2。考虑延迟或动态功耗时, 一般用 最坏情况

(最大宽度W ,最薄介质) 3。考虑竞争情况时用最小宽度W 及最厚介质。

2004-9-22

清华大学微电子所《 数字大规模集成电路》 周润德

1.75

导线层

Poly

Al1

Al2

Al3

Al4

Al5

电容

40

95

85

85

85

115

2004-9-22

清华大学微电子所《 数字大规模集成电路》 周润德

第 4 章 第 11 页

导线电容 (0.25 µm CMOS)

《电工电子学》第4章 数字集成电路新

1

0

A

&

Y

0

B

C

跳转到第一页

例:

逻辑图

X &

A

B C

&

Y &

≥1

F

Z &

逻辑表 达式

X A ABC Y B ABC Z C ABC

F X Y Z A ABC B ABC C ABC

最简与或 表达式 F (A B C)(A B C ) ABC ABC

跳转到第一页

真值表

1 (A B)

AB

分配率 A+BC=(A+B)(A+C)

跳转到第一页

4.1.2 逻辑函数的表示方法

逻辑函数有3种表示形式:逻辑状态表、逻辑表达式、 逻辑图。

1、逻辑状态表

跳转到第一页

例如,要表示这样一个函数关系:当3个变量A、B、C的取值中有 偶数个1时,函数取值为1;否则,函数取值为0。此函数称为判偶 函数,可用真值表表示如下。

V4

A

FE

V5

& F

EN

符号

结论:电路的输出有高阻态、高电平和低电 平3种状态。

跳转到第一页

4.3 组合逻辑电路

4.3.1 组合逻辑电路的分析

A

&X

X AB Y BC Z CA

B

&Y

F &

F XYZ AB BC AC

C

&Z

F AB BC CA

跳转到第一页

F AB BCCA

ABC

EN

符号

②E=1时,二极管D截止,三态门的输出状态完全取决 于输入信号A的状态,电路输出与输入的逻辑关系和一 般反相器相同,即:F=A,A=0时F=1,为高电平;A =1时F=0,为低电平。

厚薄膜混合集成电路课件-4-5-6厚膜工艺

※ 4.1.7 低温共烧陶瓷(LTCC)

表4-3 低温共烧LTCC超过其他厚膜工艺的优点

超过HTCC的优点

较低的烧成温度(850-950℃对12001500℃)

标准的良好的烧成环境(空气对氢/氮气) 使用低电阻率的导体的能力(金、银和 铜对钨或钼) 不需要电镀

能共烧和集成无源元件(电阻、电容、 电感器)

※ 4.1.1 丝网印刷

丝网印刷所产生 的图形取决于使 用正的或负的原 图和已在丝网上 正的或负的光敏 乳胶

※4.1.1 丝网印刷

影响厚膜电路质量的因素

丝

流厚

网

性膜

本

和浆

身

流料

的

动的

质

性液

量

※4.1.1 丝网印刷

➢丝网是由贴到网框上的拉紧的网布,再加上光敏乳胶。 ➢丝网的目数:每英寸长的丝网布中的开口孔数,它决定了导体和电阻的 尺寸及它们的公差,导线之间的间隔和孔的尺寸。

气保护炉内烧成。 允许使用金、银等高导电率的导体浆料,适用于高速电路,如RF

电路; 无源器件能与陶瓷共烧,埋入单片结构中。 2)通过用LTCC将互连基片、封装和引线一体化的设计方法,能产生非常 扁薄的封装 3) 可产生复杂形状或三维电子线路和封装。

用LTCC工艺生产部件有如下缺点: 由于有高的玻璃含量(50%或更大),所以热传导率非常低(2-3 W/m∙K) 较低的结构强度,原因仍是由于高的玻璃含量; 当烧成时瓷带收缩。

低的介电常数

CTE与硅器件更匹配

更好的尺寸和翘曲度控制

超过顺序烧成厚膜工艺的优点 成批层压和共烧

做多层基片时层数可以做的更多 工艺步骤少,成本低

高密度互联基片能与密封封装集成 能形成空腔和特定形状的基片 能与埋入的无源器件共烧 导体有更大的附着力

第四章离子注入

离子/cm2)内变化,且在此范围内精度可控制 到±1%。与此相反,在扩散系统中,高浓度时 杂质浓度的精度最多控制到 5 - 10 % , 低浓度 时比这更差。

3、离子注入时,衬底一般是保持在室温或温

度不高(≤ 400℃), 因此,可用各种掩模 (如氧化硅、氮化硅、铝和光刻胶)进行选 择掺杂。在制备不能采用扩散工艺的器件时, 这为独特的自对准掩模技术的设计提供了很 大的自由度。 4、离子束的穿透深度随离子能量的增大而增 大,因此,控制同一种或不同种的杂质进行 多次注入时的能量和剂量,可以在很大的范 围内得到不同的掺杂剂浓度分布截面。用这 种方法比较 容易获得超陡的和倒置的掺杂截 面。

在 x = RP 的两侧,注入离子浓度对称地下降, 且下降速度越来越快: 峰值附近与实际分布符合较 好,当离峰值位置较远时,有较 大偏离。

注入离子的二维分布

注入离子的真实分布

真实分布非常复杂,不 服从严格的高斯分布 硼比硅原子质量轻得多, 硼离子注入就会有较多 的大角度散射。被反向 散射的硼离子数量也会 增多,因而分布在峰值 位置与表面一侧的离子 数量大于峰值位置的另 一侧,不服从严格的高 斯分布。 砷等重离子和硼轻离子 的分布正好相反。

于两者之间。因此,沟道效应 依<110 >、 <111>、 <100 >顺序减 弱。

100

倾斜旋转硅片后的无序方向

实践表明,沟道效应与多种因素有关,包括:

单晶靶的取向 离子的注入方向 离子的注入能量 注入时的靶温

注入剂量

将沟道效应降低到最小:

a. 在晶体上覆盖一层非晶体的表面层:常用非晶覆盖材料是一 层薄氧化层。使离子束方向随机化,离子以不同角度进入晶片; b. 将晶片晶向偏转:大部分注入系统将硅片倾斜7°,并从平边 扭转22°; c. 在晶片表面制作一个损伤层:在晶片表面注入大量硅或锗可 以损伤晶片表面,在晶片表面产生一个随机层。

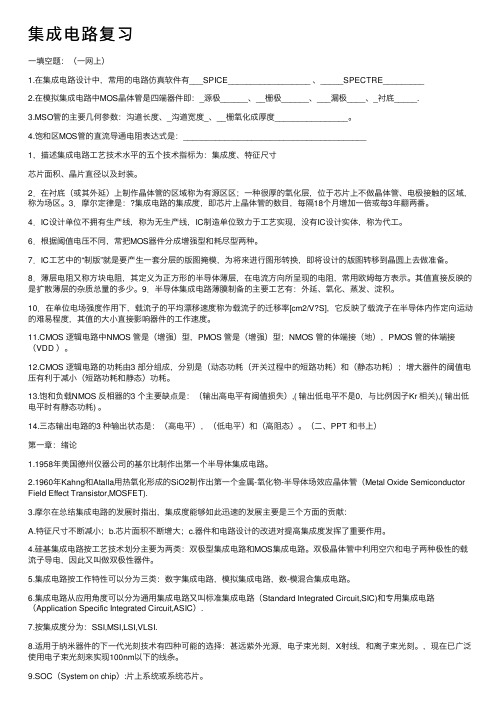

集成电路复习

集成电路复习⼀填空题:(⼀⽹上)1.在集成电路设计中,常⽤的电路仿真软件有___SPICE__________________ 、_____SPECTRE_________2.在模拟集成电路中MOS晶体管是四端器件即:_源极______、__栅极______、___漏极____、_衬底_____.3.MSO管的主要⼏何参数:沟道长度、_沟道宽度_、__栅氧化成厚度________________。

4.饱和区MOS管的直流导通电阻表达式是:________________________________________1,描述集成电路⼯艺技术⽔平的五个技术指标为:集成度、特征尺⼨芯⽚⾯积、晶⽚直径以及封装。

2.在衬底(或其外延)上制作晶体管的区域称为有源区区;⼀种很厚的氧化层,位于芯⽚上不做晶体管、电极接触的区域,称为场区。

3.摩尔定律是:?集成电路的集成度,即芯⽚上晶体管的数⽬,每隔18个⽉增加⼀倍或每3年翻两番。

4.IC设计单位不拥有⽣产线,称为⽆⽣产线,IC制造单位致⼒于⼯艺实现,没有IC设计实体,称为代⼯。

6.根据阈值电压不同,常把MOS器件分成增强型和耗尽型两种。

7.IC⼯艺中的“制版”就是要产⽣⼀套分层的版图掩模,为将来进⾏图形转换,即将设计的版图转移到晶圆上去做准备。

8.薄层电阻⼜称⽅块电阻,其定义为正⽅形的半导体薄层,在电流⽅向所呈现的电阻,常⽤欧姆每⽅表⽰。

其值直接反映的是扩散薄层的杂质总量的多少。

9.半导体集成电路薄膜制备的主要⼯艺有:外延、氧化、蒸发、淀积。

10.在单位电场强度作⽤下,载流⼦的平均漂移速度称为载流⼦的迁移率[cm2/V?S],它反映了载流⼦在半导体内作定向运动的难易程度,其值的⼤⼩直接影响器件的⼯作速度。

11.CMOS 逻辑电路中NMOS 管是(增强)型,PMOS 管是(增强)型;NMOS 管的体端接(地),PMOS 管的体端接(VDD )。

12.CMOS 逻辑电路的功耗由3 部分组成,分别是(动态功耗(开关过程中的短路功耗)和(静态功耗);增⼤器件的阈值电压有利于减⼩(短路功耗和静态)功耗。

集成电路设计ppt

第四章 半导体集成电路基本加工工艺与设计规则 4.1 引言 4.2 集成电路基本加工工艺 4.3 CMOS工艺流程 4.4 设计规则 4.5 CMOS反相器的闩锁效应 4.6 版图设计

第五章 MOS管数字集成电路基本逻辑单元设计 5.1 NMOS管逻辑电路 5.2 静态CMOS逻辑电路 5.3 MOS管改进型逻辑电路 5.4 MOS管传输逻辑电路 5.5 触发器 5.6 移位寄存器 5.7 输入输出(I/O)单元

[3] 陈中建主译. CMOS电路设计、布局与仿真.北京:机械工 业出版社,2006.

[4](美)Wayne Wolf. Modern VLSI Design System on Silicon. 北京:科学出版社,2002.

[5] 朱正涌. 半导体集成电路. 北京:清华大学出版社,2001. [6] 王志功,沈永朝.《集成电路设计基础》电子工业出版

第六章 MOS管数字集成电路子系统设计 6.1 引言 6.2 加法器 6.3 乘法器 6.4 存储器

6.5 PLA 第七章 MOS管模拟集成电路设计基础

7.1 引言 7.2 MOS管模拟集成电路中的基本元器件 7.3 MOS模拟集成电路基本单元电路 7.4 MOS管集成运算放大器和比较器 7. 5 MOS管模拟集成电路版图设计 第八章 集成电路的测试与可测性设计

1.2 集成电路的发展

1、描述集成电路工艺技术水平的五个技术指标 (1)集成度(Integration Level)

集成度是以一个IC芯片所包含的元件(晶体管或门/数)来 衡量(包括有源和无源元件)。随着集成度的提高,使IC及使用 IC的电子设备的功能增强、速度和可靠性提高、功耗降低、体积 和重量减小、产品成本下降,从而提高了性能/价格比,不断扩 大其应用领域,因此集成度是IC技术进步的标志。为了提高集成 度采取了增大芯片面积、缩小器件特征尺寸、改进电路及结构设 计等措施。为节省芯片面积普遍采用了多层布线结构。硅晶片集 成(Wafer Scale Integration -WSI)和三维集成技术也正在研 究开发。从电子系统的角度来看,集成度的提高使IC进入系统集 成或片上系统(SoC)的时代。

集成电路测试4

4.5.1 故障等价

f0(a,b,c)=d+c=ab+c;

Fault 1: A s-a-0 : f1(a,b,c)=c; Fault 2:

a b c d e

B s-a-0: f2(a,b,c)=c;

4.5.2 单固定故障的等价

一个n线的电路有2n个单固定故障,因此, 就有2(n2-n)个故障对。 故障对可通过不可分辨条件进行压缩。 在单个布尔门的故障中确定的等价性,可 应用于任意大的电路。

4.4 故障模型术语表

Physical Faults Pin Faults PLA Faults Potentially Detectable Faults Quiescent Current Faults Race Faults Redundant Faults Segment-Delay Faults

4.1 缺陷、错误和故障

4.1 缺陷、错误和故障

4.1 缺陷、错误和故障

4.1 缺陷、错误和故障

4.1 缺陷、错误和故障

缺陷: 一个节点短路到地。 故障: 信号b固定在逻辑0。 错误: a=1,b=1时,c=0。 注意:输入为其它情况时, 没有错误发生。

a b

c

4.2 功能测试与结构测试

4.5 单固定故障

4.5 单固定故障

4.5 单固定故障

EX:

4.5 单固定故障

4.5.1 故障等价

考虑一个带有n个输入变量的单输出组 合电路。将输出函数记为f0(V),V是一个 n位布尔矢量。考虑两个故障:故障1和 故障2,故障1的输出为f1(V),故障2的输 出为f2(V),若

f 1(V ) f 2 (V ) 0

表明两个故障函数一致,故障1和故障2 等价。

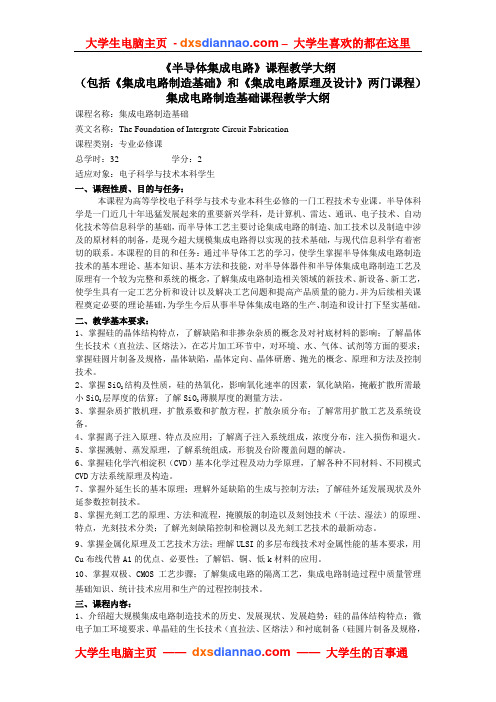

半导体集成电路课程教学大纲

《半导体集成电路》课程教学大纲(包括《集成电路制造基础》和《集成电路原理及设计》两门课程)集成电路制造基础课程教学大纲课程名称:集成电路制造基础英文名称:The Foundation of Intergrate Circuit Fabrication课程类别:专业必修课总学时:32 学分:2适应对象:电子科学与技术本科学生一、课程性质、目的与任务:本课程为高等学校电子科学与技术专业本科生必修的一门工程技术专业课。

半导体科学是一门近几十年迅猛发展起来的重要新兴学科,是计算机、雷达、通讯、电子技术、自动化技术等信息科学的基础,而半导体工艺主要讨论集成电路的制造、加工技术以及制造中涉及的原材料的制备,是现今超大规模集成电路得以实现的技术基础,与现代信息科学有着密切的联系。

本课程的目的和任务:通过半导体工艺的学习,使学生掌握半导体集成电路制造技术的基本理论、基本知识、基本方法和技能,对半导体器件和半导体集成电路制造工艺及原理有一个较为完整和系统的概念,了解集成电路制造相关领域的新技术、新设备、新工艺,使学生具有一定工艺分析和设计以及解决工艺问题和提高产品质量的能力。

并为后续相关课程奠定必要的理论基础,为学生今后从事半导体集成电路的生产、制造和设计打下坚实基础。

二、教学基本要求:1、掌握硅的晶体结构特点,了解缺陷和非掺杂杂质的概念及对衬底材料的影响;了解晶体生长技术(直拉法、区熔法),在芯片加工环节中,对环境、水、气体、试剂等方面的要求;掌握硅圆片制备及规格,晶体缺陷,晶体定向、晶体研磨、抛光的概念、原理和方法及控制技术。

2、掌握SiO2结构及性质,硅的热氧化,影响氧化速率的因素,氧化缺陷,掩蔽扩散所需最小SiO2层厚度的估算;了解SiO2薄膜厚度的测量方法。

3、掌握杂质扩散机理,扩散系数和扩散方程,扩散杂质分布;了解常用扩散工艺及系统设备。

4、掌握离子注入原理、特点及应用;了解离子注入系统组成,浓度分布,注入损伤和退火。

电路与电子学第四章

二极管例题

5K

1V

D1

Ua

D1截止, D2导通, Ua= -5V

求电路中的UO:

D3导通,UO=6V D2导通,UO= -6V, D3截止。 D1截止,UO= 6V

D2

D1 UO

D1截止, D2导通, D3截止, UO= - 6V

复习

+ ui (a) u01 t D R + u01 +

如图已知输入电压 ui=30sinωt ,

二极管的应用 t

输入电压小于5V:

+ ui D 5V

输入电压大于5V: + D 5V +

t

小于5V后

ui

-

u02

-

演示二极管2

●二极管整流电路 整流

半波整流电路

利用二极管的单向导电性,将双向变化的交流电转换为 单向脉动的直流电。 ui ①半波整流电路 D t + + ui RL u0 -

-

u0

t 脉动直流电

ui<0:上负下正,D2D4导通D1D3截止 。

0

π

2π

3π

全波整流电路输出电压平均值:

单向桥式整流电路

U0

1

o

( U m sin t )d ( t )

2 2

U 0.9U

i i t π 2π 3π

U U 负载中通过电流的平均值:I 0 0 0.9 RL RL

截止时二极管所承受的最大反向电压为峰值Um。 承担全波整流电路中二极管的参数为: 最大整流电流: I I 0.45 U F D + ui -

零偏,不通,ID=0 反偏,不通,ID=0

数字集成电路设计 第四章导线.ppt

导线. 17

合肥工业大学应用物理系

接触电阻(contact resistance)

• 布线层之间的转接将给导线带来额外的电阻 – 尽可能地使信号线保持在同一层上并避免过多的接触或通孔 – 使接触孔较大可以降低接触电阻(电流集聚在实际中将限制接触孔 的最大尺寸)

• 典型接触电阻,RC, (最小尺寸) – 金属或多晶至n+、p+以及金属至多晶为 5 ~ 20 – 通孔(金属至金属接触)为1 ~ 5

例4.1 金属导线电容

考虑一条布置在第一层铝上的10cm长,1m宽的铝线,计算总的电容值。

平面(平行板)电容: ( 0.1×106m2 )×30aF/m2 = 3pF

边缘电容:

2×( 0.1×106m )×40aF/m = 8pF

总电容:

11pF

现假设第二条导线布置在第一条旁边,它们之间只相隔最小允许的距离, 计算其耦合电容。

Capacitance-only

注意:这些附加的电路元件并不处在实际的单个点上,而是分布在导 线的整个长度上

导线. 6

合肥工业大学应用物理系

寄生简化

• 电感的影响可以忽略 – 如果导线的电阻很大(例如截面很小的长铝导线的情形) – 外加信号的上升和下降时间很慢

• 采用只含电容的模型 – 当导线很短,导线的截面很大时 – 当所采用的互连材料电阻率很低时

D2 C1R1 C2 R1 R2

r1

1 r2

2

Vin

c1

c2

ri-1 i-1 ri

i

ci-1

ci

rN

N VN

cN

Di C1R1 C2R1 R2 ... Ci R1 R2 ... Ri

集成电路工艺原理课后作业

集成电路工艺原理课后作业第一章1.单晶Si片的制备工艺流程答:a)石英沙⇒冶金硅(粗硅):SiO2+C⇒Si+CO2;b) 冶金硅粉末+HCl⇒三氯硅烷:将冶金硅压碎,制成冶金硅粉,通过与无水HCl 反应生成粗三氯硅烷,利用各组分沸点的不同来达到分离杂质的目的,通过气化和浓缩提纯三氯硅烷;c) 三氯硅烷+H2⇒多晶电子纯硅:精馏后的三氯硅烷,被高纯度H2带入“西门子反应器”还原。

d) 熔融的多晶电子纯硅(EGS)⇒单晶硅锭:①直拉法②区熔法e) 整型处理:去掉两端、径向研磨、定位边;单晶硅锭切片、磨片倒角、刻蚀、抛光;激光刻号,封装。

2.两种拉单晶的方法(CZ、FZ)及其特点答:直拉法:在石英坩埚中将多晶硅熔融,上面用单晶硅籽晶直接拉成单晶硅锭。

特点:便宜;大的硅片尺寸(直径300mm);材料可回收利用。

区熔法:将材料局部熔化,形成狭窄的熔区,然后令熔区沿着材料缓慢移动,利用分凝现象来分离杂质,生长单晶体。

特点:更纯的单晶硅(无坩埚);更贵,硅片尺寸小(150mm);主要用于功率器件。

3.单晶硅中硅的原子密度答:8/a3=5×1022/cm34.在硅半导体中形成替位式杂质的条件,可能的掺杂元素主要哪些?答:形成替位式杂质的条件:(1)原子大小:与原晶格上的原子大小接近。

(2)原子外部电子壳层和晶体结构具有相似性。

可能元素:Ⅲ、Ⅴ族元素B、P、As。

第二章1.热氧化法答:Si与氧或水汽等氧化剂在高温下发生化学反应生成SiO2。

2.SiO2在集成电路中的应用主要哪些?答:①自然层:无用②屏蔽层:离子注入③遮蔽层:扩散④场区氧化层及介局部氧化物:隔离⑤衬垫层:避免氮化物的强应力在Si中缺陷⑥牺牲层:消除Si表面缺陷。

⑦栅氧化层:栅极介质层。

⑧阻挡层:浅沟隔离STI。

3.热氧化法常用的氧化源有哪些?采用不同氧化源制备SiO2,其各自的特点是什么?答:①氧气(干氧氧化,薄膜均匀致密,生长速率慢)②水汽(水汽氧化,生长速率快,薄膜疏松,特性不好)③氢气与氧气(水汽氧化、湿氧氧化,氢气氧气摩尔比不同时,效果介于前两种之间)④含氯气体(掺入其它氧化剂中,使栅氧中可移动离子最小)4.在集成电路工艺中,制备厚的SiO2层主要采用什么氧化方式,其主要优点是什么?答:采用的是干氧-湿氧-干氧相结合的氧化方式。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

• 栅电极层、栅介质层和Si衬底构成的 栅电极层、栅介质层和 衬底构成的 衬底构成的MIS结 结 构称为栅结构。 构称为栅结构。 • 其中栅电极层的功函数、栅介质层的厚度、 其中栅电极层的功函数、栅介质层的厚度、 介电常数、 介电常数、介质层电荷及界面缺陷态度等 因素直接决定着CMOS器件的特性。 器件的特性。 因素直接决定着 器件的特性 • 栅电极层为重掺杂的多晶硅和硅化物的复 合结构,栅介质为高质量的热氧化SiO2,其 合结构,栅介质为高质量的热氧化SiO 氧化层电荷和界面缺陷态密度均很低。 氧化层电荷和界面缺陷态密度均很低。

通过MIS的电流 通过MIS的电流

较厚氧化层时热载流子注 强场下的F-N(Fowler-Nordheim)遂穿 遂穿 强场下的 薄氧化层时和低电场下的直接遂穿 对于超亚微米MOSFET,当栅氧化层的厚度 当栅氧化层的厚度 对于超亚微米 缩小至3nm以后 直接隧穿产生的栅电流将成 以后,直接隧穿产生的栅电流将成 缩小至 以后 为影响器件性能的主要因素. 为影响器件性能的主要因素

• 研究表明 在SiO2中引入氮 研究表明.在 中引入氮(N)\可以抑制硼的扩散。 可以抑制硼的扩散。 可以抑制硼的扩散 气氛中氧化生长的SiO2作 示出了利用在N 气氛中氧化生长的 图4-6示出了利用在 2O气氛中氧化生长的 示出了利用在 为栅介质层制成的‘ 电容样品的C-V特性曲 为栅介质层制成的‘MOS电容样品的 电容样品的 特性曲 线。 • 除了栅介质层的差别外,其余的条件均与图 中 除了栅介质层的差别外,其余的条件均与图4.5中 的相同。 的相同。 • 由图可见,随着退火时间的增加 样品间 由图可见,随着退火时间的增加.样品间 样品间C-V特性 特性 曲线的正向移动减小,退火10秒和 秒的样品相比. 秒和1秒的样品相比 曲线的正向移动减小,退火 秒和 秒的样品相比 平带电压的移动约为30mV。 平带电压的移动约为 。 • 可知在二氧化硅中引人氮以后,硼扩散带来的影 可知在二氧化硅中引人氮以后, 响减小, 响减小,硼的扩散得到抑制 。

• 当采用高介电常数介质等非二氧化硅材料时,通 当采用高介电常数介质等非二氧化硅材料时, 常采用等效氧化层厚度EOT表示栅介质层厚度 ox 表示栅介质层厚度t 常采用等效氧化层厚度 表示栅介质层厚度 • CETinv对应于 对应于MOSFET反型时的等效电容厚度, 反型时的等效电容厚度, 反型时的等效电容厚度 有 CETinv=EOT+tqm+tdp • CETacc对应于 对应于MOSFET积累时的等效电容厚度, 积累时的等效电容厚度, 积累时的等效电容厚度 有 CETacc=EOT+tqm

பைடு நூலகம்

平带电压

• 1、功函数 费米能级的电子逸出体外所需的能量。 费米能级的电子逸出体外所需的能量。 、功函数—费米能级的电子逸出体外所需的能量 • 2、电子亲和能 半导体中导带底的电子逸出体外 电子亲和能—半导体中导带底的电子逸出体外 所需的能量。 所需的能量。 • 3、接触电势差 金属费米能级与半导体费米能级 接触电势差—金属费米能级与半导体费米能级 的差。 的差。 • 对MIS结构,其金属和半导体之间的功函数差仅由 MIS结构 结构, 金属和半导体决定。 金属和半导体决定。由于通常金属和半导体的功 函数不同, 函数不同,而在平衡系统中费米能级必须保持平 因此必将引起能带的弯曲。 直,因此必将引起能带的弯曲。 • 弯曲的大小由栅电极和半导体间的功函数差决定。 弯曲的大小由栅电极和半导体间的功函数差决定。

• 能带弯曲分别为: 能带弯曲分别为: 型半导体) φms = φm − ( xs + Eg / q + φF ) (n型半导体) 型半导体) 型半导体 φms = φm − ( xs + Eg / q − φF ) (p型半导体)

φm 是栅电极的功函数,χ 是半导体材料的亲和能, 是栅电极的功函数, s是半导体材料的亲和能,

• 栅介质、栅电极、Si沟道之间的两个界面厚度通 栅介质、栅电极、 沟道之间的两个界面厚度通 常在几个埃的数量级,是栅电极、栅介质和Si沟 常在几个埃的数量级,是栅电极、栅介质和 沟 道之间材料的过渡。 道之间材料的过渡。 • 当界面层的厚度与栅介质层的厚度接近时,界面 当界面层的厚度与栅介质层的厚度接近时, 层将直接影响总的栅电容的大小, 层将直接影响总的栅电容的大小,从而影响着 MOSFET器件的性能。这些界面层还可以加以利 器件的性能。 器件的性能 用以获得某些所需的作用。 用以获得某些所需的作用。 • 栅介质层:热氧化硅(SiO2)——新型栅介质材 栅介质层:热氧化硅( 新型栅介质材 料如氮化二氧化硅材料。 料如氮化二氧化硅材料。 • MIS结构中栅介层的厚度tox决定了单位面积栅电 MIS结构中栅介层的厚度 结构中栅介层的厚度t 表面量子化效应和多晶硅耗尽效应(详见4.4 容,表面量子化效应和多晶硅耗尽效应(详见4.4 等的影响, 节)等的影响,使栅电容降低 ——等效的介质层 等效的介质层 厚度增加——等效电容厚度CET 。 等效电容厚度CET 厚度增加 等效电容厚度 •

SiSi-N-O系统的热动力学

• 图中包含四个相:Si、 图中包含四个相: 、 SiO2(方石英和磷石 )、Si 英)、 3N4、Si2N2O。 。 • SiO2为硅氧四面体结构, 为硅氧四面体结构, Si3N4为硅氮四面体结构, 为硅氮四面体结构, Si2N2O为略有畸变的 为略有畸变的 型四面体结构。 SiN3O型四面体结构。通 型四面体结构 过用氮替换氧,可以实 过用氮替换氧, 现由SiO2到Si2N2O最终 现由 最终 的相变。 到Si3N4的相变。

一、CMOS器件中的MIS栅结构 CMOS器件中的 器件中的MIS栅结构

• MIS结构 结构——MOSFET器件的重要组成部分。 器件的重要组成部分。 结构 器件的重要组成部分 • MIS ——(Metal Insulator Semiconductor,金属 ( ,金属绝缘层-半导体 半导体) 绝缘层 半导体) • 栅电极通常由多晶硅 -金属硅化物的复合结 构构成。 构构成。 • 栅介质与栅电极和Si 栅介质与栅电极和Si 沟道之间的两个界面 对于器件的性质起到 着至关重要作用。 着至关重要作用。

氮氧硅栅介质层的制备

CMOS技术中 CMOS技术中MIS栅电极结构的演变 技术中MIS栅电极结构的演变

Al栅 栅

重掺杂多 晶硅栅

金属栅

多晶硅-金 属硅化物栅

氮化的二 氧化硅栅

双搀杂 多晶硅栅

二、氮氧硅栅介质

• 目前,CMOS器件中已开始使用超薄氮氧硅 目前, 器件中已开始使用超薄氮氧硅 更准确地应称为掺氮的SiO2,或氮化二 (SiOxNy,更准确地应称为掺氮的 栅介质。 氧化硅)替代传统的纯SiO2栅介质。 氧化硅)替代传统的纯 • 氮氧硅中含有氮可以抑制硼的扩散, Si 2-Si界面 氮氧硅中含有氮可以抑制硼的扩散, SiO Si界面 附近含有少量的氮可以降低由热电子引起的界面退 提高器件的可靠性。 化,提高器件的可靠性。 • 氮氧硅SiO2Ny的介电常数在 ε ( SiQ2 ) = 3.9和ε ( Si3 N 4 ) = 7.8 氮氧硅SiO 之间随氮含量的多少成正比地变化。 之间随氮含量的多少成正比地变化。于是在相同的 等效栅氧化层厚度下,氮氧硅的物理厚度大于SiO 等效栅氧化层厚度下,氮氧硅的物理厚度大于SiO2的, 相应地使泄漏电流有所降低。 相应地使泄漏电流有所降低。 • 但是SiO2-Si界面附近若存在大量的氮,则由于界面 但是SiO Si界面附近若存在大量的氮 界面附近若存在大量的氮, 缺陷态的增加和迁移率的降低而使器件的性能退化。

• 然而平衡条件下,在体材料中Si3N4相和 然而平衡条件下,在体材料中 相和SiO2相是不 相分隔开。 可能共存的,这两个相总是被Si 相分隔开 可能共存的,这两个相总是被 2NO相分隔开。 Si2N2O是Si-N-O系统中惟一稳定的热动力学结构。 系统中惟一稳定的热动力学结构。 是 系统中惟一稳定的热动力学结构 • 在T=1400K时Si2N2O-SiO2相的边界,位于10-18atm 时 相的边界,位于10 处。而目前的各种快速热退火设备中的氧分压大于 该值。于是在体SiO2中的氮不是热力学稳定的。 中的氮不是热力学稳定的。 该值。于是在体 • 但实验上,在SiO2薄膜中是可以引入氮的,其主要 但实验上, 薄膜中是可以引入氮的, 原因在于氮原子能够动态地陷在表面附近的反应区 此时的氮处于非平衡状态, 内。此时的氮处于非平衡状态,但由非平衡态向平 衡态转变的速率很慢,于是一部分氮被陷。 衡态转变的速率很慢,于是一部分氮被陷。

为半导体材料的禁带宽度。 Eg为半导体材料的禁带宽度。半导体衬底的费米 势为 kT N sub φF = ln q ni • 介质层和界面上的电荷均会引起半导体表面能级 的弯曲。 的弯曲。其弯曲量为 ± Qo

Cox

当Qo为负电荷时取'+',当Qo为正电荷时取 为负电荷时取 ,

• 能带弯曲可以通过施加与弯曲量相当的偏压加以 补偿, 补偿,通常把所需施加的偏压称为平带电压 。 • 平带电压定义为:为使半导体中能带保持平直而 平带电压定义为: 使表面势为0时所需施加在栅电极上的偏压。由栅 使表面势为 时所需施加在栅电极上的偏压。 时所需施加在栅电极上的偏压 电极和半导体间的功函数差以及等效界面电荷决 Qo 定 V fb = φms ± Cox • 若Qo为负电荷则平带电压将出现正向的移动,若 为负电荷则平带电压将出现正向的移动, 为正电荷则平带电压将出现负向的移动。 Qo为正电荷则平带电压将出现负向的移动。

• 图4.5为具有 多晶硅栅电极的 为具有P+多晶硅栅电极的 电容的C一 为具有 多晶硅栅电极的MOS电容的 一V 电容的 特性曲线。 特性曲线。 • MOS电容的面积为 电容的面积为6.25 ×10-4cm2,在n型硅上热 电容的面积为 型硅上热 氧化生长了24 埃的SiO2,多晶硅栅电极厚1500埃, 氧化生长了 埃的 ,多晶硅栅电极厚 埃 采用硼离子注人形成P+多晶硅 随后在1000度Ar 多晶硅, 采用硼离子注人形成 多晶硅,随后在 度 气氛退火,时间1、 、 和 秒 气氛退火,时间 、2、5和10秒。 • 随着退火时间的增加,特性曲线向正方向移动, 随着退火时间的增加,特性曲线向正方向移动, 相应地平带电压增加,表明阈值电压增加。 相应地平带电压增加,表明阈值电压增加。 • 以I-V特性的变化作为失效器件的判据,即与退火 特性的变化作为失效器件的判据, 特性的变化作为失效器件的判据 时间最短(1秒 的器件相比 的器件相比、 时间最短 秒)的器件相比、电流增加两个数量级 以上的器件均视为失效。 以上的器件均视为失效。