5-146480-5中文资料

SCALANCE XB004-1LD 6GK5004-1BF00-1AB2 10 100M 工业以太

/bilddb

● to website: CAx-Download-Manager

/cax

● to website: Industry Online Support

https://

EN 60079-0:2009, EN60079-15:2010, II 3 G Ex nA IIC T4 Gc, KEMA 07ATEX0145 X

certificate of suitability

● CCC / for hazardous zone according to GB standard Yes

standards, specifications, approvals / other

certificate of suitability

EN 61000-6-2, EN 61000-6-4

● C-Tick

Yes

● KC approval

Yes

further information / internet-Links

KFE

standards, specifications, approvals / CE

certificate of suitability / CE marking

Yes

standards, specifications, approvals / hazardous environments

standard / for hazardous zone

supply voltage, current consumption, power loss type of voltage / 1 / of the supply voltage ● supply voltage / 1 / rated value ● power loss [W] / 1 / rated value ● supply voltage / 1 / rated value ● consumed current / 1 / maximum ● type of electrical connection / 1 / for power supply ● product component / 1 / fusing at power supply input ● fuse protection type / 1 / at input for supply voltage type of voltage / 2 / of the supply voltage ● supply voltage / 2 / rated value

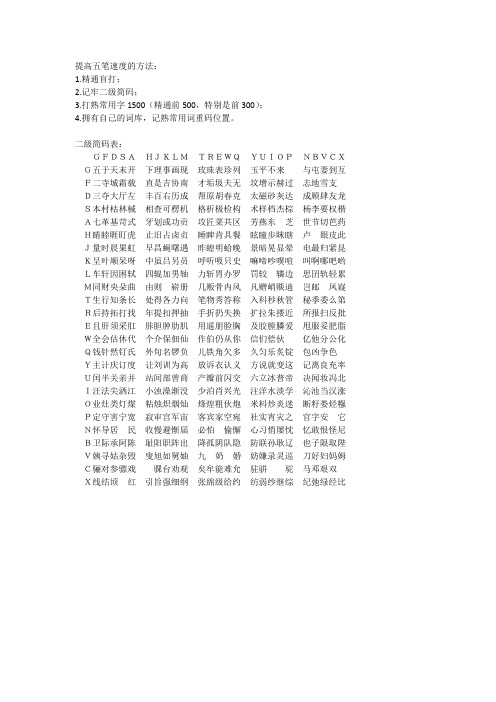

五笔二级简码表及常用1500字编码

提高五笔速度的方法:1.精通盲打;2.记牢二级简码;3.打熟常用字1500(精通前500,特别是前300);4.拥有自己的词库,记熟常用词重码位置。

二级简码表:GFDSAHJKLMTREWQYUIOPNBVCXG五于天末开下理事画现玫珠表珍列玉平不来与屯妻到互F二寺城霜载直是吉协南才垢圾夫无坟增示赫过志地雪支D三夺大厅左丰百右历成帮原胡春克太磁砂灰达成顾肆友龙S本村枯林械相查可楞机格析极检构术样档杰棕杨李要权楷A七革基苛式牙划或功贡攻匠菜共区芳燕东芝世节切芭药H睛睦睚盯虎止旧占卤贞睡睥肯具餐眩瞳步眯瞎卢眼皮此J量时晨果虹早昌蝇曙遇昨蝗明蛤晚景暗晃显晕电最归紧昆K呈叶顺呆呀中虽吕另员呼听吸只史嘛啼吵噗喧叫啊哪吧哟L车轩因困轼四辊加男轴力斩胃办罗罚较辚边思囝轨轻累M同财央朵曲由则崭册几贩骨内风凡赠峭赕迪岂邮凤嶷T生行知条长处得各力向笔物秀答称入科秒秋管秘季委么第R后持拓打找年提扣押抽手折扔失换扩拉朱搂近所报扫反批E且肝须采肛胩胆肿肋肌用遥朋脸胸及胶膛膦爱甩服妥肥脂W全会估休代个介保佃仙作伯仍从你信们偿伙亿他分公化Q钱针然钉氏外旬名锣负儿铁角欠多久匀乐炙锭包凶争色Y主计庆订度让刘训为高放诉衣认义方说就变这记离良充率U闰半关亲并站间部曾商产瓣前闪交六立冰普帝决闻妆冯北I汪法尖洒江小浊澡渐没少泊肖兴光注洋水淡学沁池当汉涨O业灶类灯煤粘烛炽烟灿烽煌粗伙炮米料炒炎迷断籽娄烃糨P定守害宁宽寂审宫军宙客宾家空宛社实宵灾之官字安它N怀导居民收慢避惭届必怕愉懈心习悄屡忱忆敢恨怪尼B卫际承阿陈耻阳职阵出降孤阴队隐防联孙耿辽也子限取陛V姨寻姑杂毁叟旭如舅妯九奶婚妨嫌录灵巡刀好妇妈姆C骊对参骠戏骒台劝观矣牟能难允驻骈驼马邓艰双X线结顷红引旨强细纲张绵级给约纺弱纱继综纪弛绿经比常用1500字(列出了86五笔原版的最简码):以下是常用字1到300的r一g是j在d了b不i和t有e大dd这p主y中k人w上h为o们wu个wh地f用et工a时jf要s动fcl国l产u以c我q到gc他wb会wf作wt来go分wv生tg对cf于gf学ip下gh级xe就yi年rh阶bwj义yq发v成dn部uk民n可sk出bm能ce方yy进fj同m行tf面dm说yu种tkh过fp命wgkb度ya革af而dmj多qq子bb后rg自thd社py加lk小ih机sm也bn经x力lt线xg本sg电jn高ym量jg长ta党ipk得tj实pu家pe定pg深ipw法if表ge着udh水ii理gj化wx争qv现gm所rn二fg起fhn政ght三dg好vb十fgh战hka无fq农pei使wgkq性ntg前ue等tffu反rc体wsg合wgk斗ufk路kht图ltu把rcn结xf第tx期adwe里jfd正ghd新usr开ga论ywx之pp物tr从ww当iv两gmww些hxf还gip天gd资uqwm事gk队bw批rx如vk应yid形gae想shn制rmhj心ny样su干fggh都ftjb向tm变yo关ud 点hko育yce重tgj其adw思ln与gn间uj内mw去fcu因ld件wrh日jjjj利tjh相sh由mh压dfy员km气rnb业og代wa全wg组xeg数ovt果js导nf平gu各tk基ad或ak月eee毛tfn然qd问ukd比xx展nae那vfb它px最jb及ey外qh没im看rhf治ick提rj五gg解qev系txi林ss者ftj米oy群vtk头udi意ujn只kw明je四lh 道uthp马cn认yw次uqw文yygy通cep但wjg条ts较lu克dq又ccc公wc孔bnn领wycm流iyc入ty接ruv军pl席yam位wug情nge运fcp器kkd并ua习nu原dr油img立uu放yt题jghm质rfm指rxj建vfhp区aq验cwg活itd众www很tve教ftbt决un特trf此hx常ipkh石dgtg强xk极se土ffff少it己nng根sve共aw直fh团lft统xyc式aa转lfn别klj造tfkp切av九vt你wq取bc西sghg持rf总ukn料ou连lpk任wtf志fn观cm调ymf么tc七ag山mmm程tkgg百dj报rb更gjq见mqb必nt真fhw 保wk热rvyo委tv手rt改nty管tp处th将uqf已nnnn修wht支fc识ykw病ugm象qje几mt先tfq老ftx以下是常用字301-500光iq专fny什wfh六uy型gajf具hw示fi复tjt安pv带gkp每txg东ai增fu则mj完pfq风mq回lkd南fm广yygt劳apl轮lwx科tu北ux打rs积tkw车lg计yf给xw节ab做wdt务tl被puhc整gkih联bu步hi类od集wys号kgn列gq温ijl装ufy即vcb 毫ypt轴lm知td研dga单ujfj色qc坚jcf据rnd速gkip防by史kq拉ru设ymc世an达dp尔qiu场fnrt织xkw历dl花awx受epc求fiy传wfny口kkkk断on况ukq采es精oge金qqqq界lwj品kkk判udjh参cd层nfc止hh边lp清ige至gcf万dnv确dqe究pwv书nnh术sy厂dgt状udy须ed离yb再gmf目hhhh海itx交uq且eg儿qt青gef才ft证ygh低wqa越fha际bf八wty试yaa规fwm斯adwr近rp注iy办lw 布dmh门uyh铁qr需fdm走fhu议yyq县egc虫jhny固ldd除bwt般tem引xh齿hwb千tfk胜etg细xl影jyie白rrr济iyj格st效uqt推rwyg兵rgw空pw配sgn刀vn叶kf率yx述syp今wynb选tfqp养udyj话ytd查sj差uda德tfl半uf敌tdt始vck 片thg施ytb响ktm收nh华wxf觉ipmq备tlf红xa名qk续xfn均fqu药ax标sfi记yn难cw存dhb士fghg身tmd测imj紧jc液iyw置lfhf派ire准uwy斤rtt角qe降bt维xwy板src许ytf破dhc技rfc端umd消iie底yqa床ysi田lll势rvyl感dgkn往tyg神pyj便wgj圆lkmi村sf构sq照jvko容pww非djd搞rym亚gog磨yssd族ytt火ooo以下是常用字501-1500段wdm算tha适tdp讲yfj按rpv值wfhg美ugdu态dyn黄amw易jqr彪hame服eb早jh班gyt麦gtu削iej信wy排rdj台ck声fnr该yynw击fmk素gxi张xt密pnt害pd候whn草ajj何wsk树scf肥ec继xo右dk属ntk市ymhj径tca严god螺jlx检sw左da页dmu抗rymn苏alw显jo苦adf英amd快nnw称tq坏fgi移tqq约xq巴cnh材sft省ith黑lfo武gah培fuk著aft河isk帝up仅wcy针qf怎thfn植sfhg京yiu助egl 升tak王ggg眼hv她vbn抓rrhy含wynk苗alf副gkl杂vs普uo谈yoo围lfnh食wyv 射tmdf源idr例wgq致gcft酸sgc旧hj却fcb充yc足khu短tdg划aj剂yjjh宣pgj环ggi落ait首uth尺nyi波ihc承bd粉ow践khg府ywf鱼qgf随bde考ftg刻ynt靠tfkd够qkqq满iagw夫fw失rw包qn住wygg促wkh枝sfc局nnk菌alt杆sfh周mfk 护ryn岩mdf师jgm举iwf曲ma春dw超fhv元fqb负qm砂di封fffy换rq太dy模saj贫wvm减udg阳bj扬rnr江ia析sr亩ylf木ssss言yyy球gfi朝fje医atd校suq古dgh呢knx稻tev宁ps听kr唯kwyg输lwg滑ime站uh另kl卫bg字pb鼓fkuc刚mqj写pgn刘yj良yv微tmg略ltk范aib供waw阿bs块fnw某afs功al套ddu限bv友dc项adm余wtu卷udbb创wbj律tvfh雨fghy让yh骨me远fqp帮dt初puv皮hc播rtol优wdn占hk死gqx毒gxgu伟wfn季tb训yk控rpw激iry叫kn找ra云fcu 互gx裂gqje粮oyv跟khv粒oug母xgu练xan塞pfjf钢qmq顶sdm策tgm双cc留qyvl误ykg础dbm吸ke阻begg故dty寸fghy盾rfh晚jq丝xxg女vvv散aet焊ojf攻at株sri亲us院bpf冷uwyc彻tavn弹xuj错qaj尼nx商um视pym艺anb灭goi版thgc烈gqjo零fwyc室pgc轻lc血tld倍wuk缺rmn厘djfd泵diu察pwfi绝xqc富pgk 城fd冲ukh喷kfa壤fyk简tuj否gik柱syg李sb望yneg盘tel磁du雄dcw似wny困ls巩amy益uwl洲iyt脱euk座yww投rmc奴vcy侧wmj润iugg盖ugl挥rpl距kha触qejy星jtg松swc送udp获aqt兴iw独qtj官pn混ijx纪xn依wye未fii突pwd架lks 宽pa冬tuu倒wgc章ujj湿ijo偏wyna纹xyy吃ktn执rvy阀uwa矿dyt寨pfjs责gmu 熟ybv稳tqv夺df硬dgj价wwj翻toln努vcl甲lhnh奇dskf预cbd职bk评ygu读yfn 背uxe协fl损rkm棉srm侵wvp灰do虽kj矛cbt厚djb罗lq泥inx辟nku告tfkf卵qyt箱tsh掌ipkr氧rnu恩ldn爱ep停wyp曾ul溶ipwk营apk终xtu纲xm孟blf钱qg待tffy尽nyu俄wtr缩xpw沙iit退vep陈ba讨yfy奋dlf旋ytn械sa载fa胞eqn 幼xln剥vijh哪kv迫rpd征tgh槽sgmj握rng担rjg仍we呀ka鲜qgu吧kc卡hhu粗oe介wj钻qhk逐epi弱xu脚efcb圈lud怕nr盐fhl末gs阴be丰dh编xyna印qgb 蜂jtd急qvn拿wgkr扩ry伤wtl飞nui露fkhk核synw缘xxe游iytb振rdf操rkk央md伍wgg域fakg甚adwn迅nfp辉iqpl异naj序ycb免qkq纸xqa夜ywt乡xte久qy隶vii缸rma夹guw念wynn兰uff映jmd沟iqc乙nnl吗kcg儒wfd杀qsu汽irn磷doq艰cv晶jjj插rtf埃fct燃oqdo欢cqw铣qtfq补puh演ipg烧oat咱kth语ygk贵khgm倾wxd阵bl碳dmd威dgv附bwf牙ah芽aah永yni瓦gny斜wtuf灌iak欧aqq 献fmud顺kd猪qtfj腐ywfw洋iu请yge透tep司ngk危qdb括rtd脉eyni笑ttd宜peg若adk尾ntf束gki壮ufg暴jaw企whf菜ae穗tgjn楚ssn汉ic愈wgen绿xv拖rtb牛rhk份wwv染ivs既vca秋to疗ubk遍ynm锻qwd玉gy夏dht尖id殖gqf井fjk费xjm州ytyh访yyn吹kqw荣aps铜qmgk沿imk替fwf滚iuc客pt召vkf旱jfj悟ngkg刺gmi脑eyb措raj贯xfm藏adnt敢nb令wyc隙bij炉oyn壳fpm硫dyc煤oa迎qbp铸qdt粘oh探rpws临jty薄aig旬qj善uduk福pyg纵xww择rcf礼pynn愿drin伏wdy残gqg雷flf延thp句qkd烟ol纯xgb渐il耕dif跑khq泽icf船temk慢nj栽fas鲁qgj赤fo繁txgi境fuj潮ifj横sam掉rhj锥qwy池ib希qdm败mty假wnh亮ypm谓yle托rta伙wo哲rrk怀ng割pdhj摆rlf贡am呈kg劲cal财mf沉ipm仪wyq炼oanw麻yss罪ldj祖pye息thn辅lgey穿pwat货wxm销qie齐yjj鼠vnu抽rm画gl饲qnnk龙dx库ylk守pf筑tam房yny歌sksw寒pfj喜fku哥sks蚀qnj洗itf废ynty纳xmw腹etj乎tuh录vi镜quj谋yaf妇vv恶gogn脂ex庄yfd擦rpwi险bwg赞tfqm钟qkhh摇rer典maw柄sgm辩uyu竹ttg谷wwk卖fnud乱tdn虚hao桥std奥tmo伯wr赶fhfk垂tga途wtp额ptkm壁nkuf截faw网mqq野jfc遗khgp静geq弄gaj挂rffg妄ynvf镇qfhw盛dnnl耐dmjf援ref扎rnn虑han键qvfp归jv符twf 庆yd聚bct摩yssr绕xat忙nynn舞rlg遇jm顾db索fpx胶eu羊udj湖ide钉qs仁wfg音ujf迹yop碎dyw伸wjh灯os避nk泛itp答tw亡ynv勇cel频hid皇rgf柳sqt 哈kwg揭rjq甘afd诺yad概svc宪ptf浓ipe岛qynm袭dxy谁ywyg洪iaw谢ytm炮oq斑gyg浇iat讯ynf徒tfhy懂nat灵vo蛋nhj闭uft孩bynw释toc乳ebn私tcy银qve伊wvt景jy坦fjg累lx匀qu霉ftxu杜sfg乐qi勒afl隔bgk巨and弯yox一ggl 招rvk绍xvk胡de呼kt痛uce峰mtd柴hxs簧tamw午tfj跳khi居nd尚imkf丁sgh 秦dwt稍tie追wnnp梁ivw耗ditn折rr碱ddg殊gqr岗mmq挖rpwn氏qa刃vyi堆fwy赫fof荷awsk胸eq衡tqdh勤akgl膜eajd篇tyna登wgku慧dhd驻cy案pvs刊fjh秧tmdy缓xef凸hgm役tmc剪uejv川kthh雪fv链qlp渔iqgg啦kru脸ew户yne 洛itk勃fpb盟jel买nudu杨sn宗pfi焦wyo旗yta赛pfjm滤iha硅dff股emc坐wwf 蒸abi凝uxt竟ujq陷bqv枪swb救fiyt黎tqt冒jhf暗ju洞imgk犯qtb筒tmgk您wqin弧xrc宋psu爆oja谬ynwe涂iwt味kfi臂nkue津ivfh障buj褐pujn陆bfm啊kb健wvf尊usg豆gku拔rdc莫ajd抵rqa坡fhc桑cccs缝xtdp警aqky挑riq冰ui污ifn柬gli嘴khx啥kwfk饭qnr塑ubtf寄pds赵fhq喊kdgt垫rvyf康yvi遵usgp牧trt 遭gmap幅mhg园lfq腔epw订ys香tjf弟uxh肉mww屋ngc敏txgt恢ndo忘ynnu衣ye孙bi龄hwbc岭mwyc骗cyna休ws借waj丹myd渡iya耳bgh刨qnjh笔tt虎ha稀tqd昆jx浪iyv萨abu茶aws滴ium浅igt拥reh穴pwu覆stt伦wwx娘vyv吨kgb浸ivp袖pum珠gr雌hxw妈vc紫hxx戏ca塔fawk锤qtgf震fdf岁mqu貌eerq洁ifk剖ukj锋qtd疑xtdh霸faf闪uw猛qtbl埔fgey诉yr刷nmh狠qtv忽qrn闹uym灾po刮tdjh唐yvh漏infy闻ub沈ipq氯rnv熔opw荒aynq茎aca男ll凡my抢rwb像wqj浆uqi旁upy玻ghc亦you唱kjj蒙apg忠khn予cbj纷xwv捕rge锁qim尤dnv乘tux乌qng智tdkj淡io允cq叛udrc畜yxl浮ieb摸rajd锈qten牢prh毕xxf璃gyb宝pgy芯anu爷wqb鉴jtyq净uqv秘tn蒋auq钙qgh肩yned腾eud枯sd抛rvl扫rv轨lv堂ipkf拌rufh爸wqc循trfh诱yte祝pyk励ddnl肯he酒isgg绳xkjn穷pwl塘fyv燥okk 袋waye泡iqn朗yvc喂klge铝qkk软lqw渠ians颗jsd惯nxf粪oawu贸qyv综xp墙ffuk趋fhqv彼thc届nm碍djg墨lfof启ynk逆ubt卸rhb航tey雾ftl丙gmw冠pfqf街tffh贝mhny莱ago辐lgk肠enr付wfy吉fk渗icd瑞gmd顿gbnm惊nyiy挤ryj秒ti姆vx悬egcn烂oufg森sss糖oyv圣cff凹mmgd陶bqr词yngk迟nyp蚕gdj亿wn矩tda 脊iwe歼gqt羽nny掩rdjn汗ifh。

中日部分黑色金属材料对照表

中日部分黑色金属材料对照表(参考) 返回散料机械金屬材料記號對照表機械構造用碳鋼鋼材鎳鉻鉬鋼鋼材机械零件所用金属材料多种多样,为了使生产、管理方便、有序,有关标准对不同金属材料规定了它们牌号的表示方法,以示统一和便于采纳、使用。

钢铁产品牌号表示方法(参照GB/T221—2000)--标准的基本概况GB/T221—2000标准是参照国外钢铁产品牌号表示方法和国内钢铁产品牌号表示方法变化(如Q345代替16Mn)等情况修订后,于2000年4月1日发布,并于2000年11月1日开始实施。

--主要技术内容变动情况(1)由于一些钢铁产品牌号有它们专用的标准,故取消了原标准中铁合金、铸造合金、高温合金、精密合金、耐蚀合金和铸铁、铸钢、粉末材料等牌号表示方法。

(2)一些新的钢铁产品的出现,更加完善了原标准。

新标准增加了脱碳低磷粒铁、含钒生铁、铸造耐磨生铁、保证淬透性钢、非调质机械结构钢、塑料模具钢、取向硅钢(电讯用)等牌号表示方法。

(3)对不适应科技发展和与生产不协调的一些用钢牌号作了彻底改变或修改。

如碳素结构钢A3改为Q235,低合金高强度结构钢16Mn改为Q345等。

对不锈钢、耐热钢和冷轧硅钢等的牌号表示方法也做了修改。

(4)原标准中“钢铁产品牌号表示方法举例”的表3,因不适用于新标准而被删除。

--钢铁产品牌号表示方法的基本原则(1)凡国家标准和行业标准中钢铁产品的牌号均应按GB/T221—2000标准规定的牌号表示方法编写。

凡不符合规定编写的钢铁产品牌号,应在标准修订时予以更改,一些新的钢铁产品,其牌号也应按此予以编写牌号。

(2)产品牌号的表示,一般采用汉语拼音字母,化学元素符号和阿拉伯数字相结合的方法来表示。

(3)采用汉语拼音字母表示产品名称、用途、特性和工艺方法时,一般从代表产品名称的汉语拼音中选取第一个字母。

当和另一个产品所选用的字母重复时,可改用第二个字母或第三个字母,或同时选取两个汉字中的第一个拼音字母。

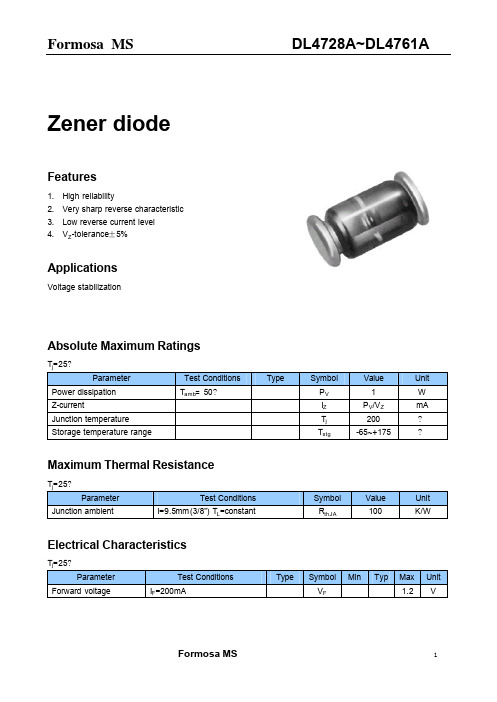

DL4754A中文资料

Zener diodeFeatures1. High reliability2. Very sharp reverse characteristic3. Low reverse current level4. V Z-tolerance±5%ApplicationsVoltage stabilizationAbsolute Maximum RatingsT j=25?Parameter Test Conditions Type Symbol Value Unit Power dissipation T amb=50?P V 1 WZ-current I Z P V/V Z mA Junction temperature T j200 ? Storage temperature range T stg-65~+175 ?Maximum Thermal ResistanceT j=25?Parameter Test Conditions Symbol Value Unit Junction ambient I=9.5mm(3/8”) T L=constant R thJA 100 K/WElectrical CharacteristicsT j=25?Parameter Test Conditions Type Symbol Min Typ Max Unit Forward voltage I F=200mA V F 1.2 VV Znom1) I ZT for r zjT r zjK at I Z K I R at V R TypeV mA O O mA µA V DL4728A 3.3 76 <10 <400 1 <100 1 DL4729A 3.6 69 <10 <400 1 <100 1 DL4730A 3.9 64 <9 <400 1 <50 1 DL4731A 4.3 58 <9 <400 1 <10 1 DL4732A 4.7 53 <8 <500 1 <10 1 DL4733A 5.1 49 <7 <550 1 <10 1 DL4734A 5.6 45 <5 <600 1 <10 2 DL4735A 6.2 41 <2 <700 1 <10 3 DL4736A 6.8 37 <3.5 <700 1 <10 4 DL4737A 7.5 34 <4.0 <700 0. 5 <10 5 DL4738A 8.2 31 <4.5 <700 0. 5 <10 6 DL4739A 9.1 28 <5.0 <700 0. 5 <10 7 DL4740A 10 25 <7 <700 0.25 <10 7.6 DL4741A 11 23 <8 <700 0.25 <5 8.4 DL4742A 12 21 <9 <700 0.25 <5 9.1 DL4743A 13 19 <10 <700 0.25 <5 9.9 DL4744A 15 17 <14 <700 0.25 <5 11.4 DL4745A 16 15.5 <16 <700 0.25 <5 12.2 DL4746A 18 14 <20 <750 0.25 <5 13.7 DL4747A 20 12.5 <22 <750 0.25 <5 15.2 DL4748A 22 11.5 <23 <750 0.25 <5 16.7 DL4749A 24 10.5 <25 <750 0.25 <5 18.2 DL4750A 27 9.5 <35 <750 0.25 <5 20.6 DL4751A 30 8.5 <40 <1000 0.25 <5 22.8 DL4752A 33 7.5 <45 <1000 0.25 <5 25.1 DL4753A 36 7.0 <50 <1000 0.25 <5 27.4 DL4754A 39 6.5 <60 <1000 0.25 <5 29.7 DL4755A 43 6.0 <70 <1500 0.25 <5 32.7 DL4756A 47 5.5 <80 <1500 0.25 <5 35.8 DL4757A 51 5.0 <95 <1500 0.25 <5 38.8 DL4758A 56 4.5 <110 <2000 0.25 <5 42.6 DL4759A 62 4.0 <125 <2000 0.25 <5 47.1 DL4760A 68 3.7 <150 <2000 0.25 <5 51.7 DL4761A 75 3.3 <175 <2000 0.25 <5 561) Based on DC-measurement at thermal equilibrium while maintaining the lead temperature(T L)at 30?,9.5mm(3/8”) from the diode body.Dimensions in mm Standard Glass Case JEDEC LL 410.40.4 5.0±0.2 f 2.6±0.2f 2.8max。

74435561100;中文规格书,Datasheet资料

74435561100

DATUM / DATE : 2009-11-02 Gurtspezifikation / Tape specification:

G H

SPEICHERDROSSEL WE-HCI POWER-CHOKE WE-HCI

I Rollenspezifikation / tape and reel specification:

74435561100

DATUM / DATE : 2009-11-02

SPEICHERDROSSEL WE-HCI POWER-CHOKE WE-HCI

H Induktivitätskurve / Inductance curve:

Induktivität vs Strom (typ.) Inductance vs Current (typ.)

08-09-29

Geprüft / checked

Kontrolliert / approved

Datum / date

D-74638 Waldenburg · Max-Eyth-Strasse 1 - 3 · Germany · Telefon (+49) (0) 7942 - 945 - 0 · Telefax (+49) (0) 7942 - 945 - 400 http://www.we-online.de

12,00

10,00

8,00

L (µH)

6,00

4,00

2,00

0,00 0 5 10 15 Current (A) 20 25 30 35

Freigabe erteilt / general release:

..................................................................................

DIN5480-5-1991中文版

e2 = s1

3,136 2,847 2,558 3,136 2,847 2,558 3,136 2,847 2,558 3,136 2,847 2,558 3,136 2,847 2,558 3,136 2,847 2,558 3,136 2,847 2,558 3,136 2,847 2,558 3,136 2,847 2,558 3,136 2,847 3,136 3,136 2,558 3,136 2,558 2,847 2,847 2,847 3,136 2,558 2,558 2,558 2,847 3,136 3,136 3,136 2,558 2,847 2,847 2,847 3,136 2,558 2,558 2,558 3,713 3,136 2,558

Adf1

-0,61 -0,65 -0,65 -0,65 -0,65 -0,65 -0,65 -0,65 -0,65 -0,65 -0,65 -0,65 -0,65 -0,65 -0,69 -0,69 -0,69 -0,69 -0,69 -0,69 -0,69 -0,69 -0,69 -0,69 -0,69 -0,69 -0,69 -0,69 -0,69 -0,69 -0,69 -0,69 -0,69 -0,69 -0,73 -0,73 -0,73 -0,73 -0,73 -0,73 -0,73 -0,73 -0,73 -0,73 -0,73 -0,73 -0,73 -0,73 -0,73 -0,73 -0,73 -0,73 -0,73 -0,73 -0,79 -0,79

db

7,794 9,093 10,392 10,392 11,691 12,990 12,990 14,289 15,588 15,588 16,887 18,187 18,187 19,486 20,785 20,785 22,084 23,383 23,383 24,682 25,981 25,981 27,280 28,579 28,579 29,898 31,777 31,777 32,476 33,775 36,373 38,971 38,971 41,569 42,868 45,466 48,064 49,363 51,962 54,560 57,158 58,457 59,756 62,354 64,952 67,550 68,849 71,447 74,075 75,344 77,942 80,540 83,138 83,138 88,334 93,530

五金手册查询表

金属材料理论重量表

黑色金属材料理论重量计算公式

表1

注:由于型材在制造过程中有允许偏差值,因此用公式计算的理论重量,与实际重量有一定的出入(误差一般约为0.2~0.7%之间),只能作为估算时的参考。

槽钢理论重量表

圆钢直径和方钢边长及理论重量表表1-1

2、表中带*者不推荐使用。

3、螺纹钢6、7、8、9、10、12、1

4、16、18、20、22、2

5、28、32、3

6、40的理论重量同

圆钢的理论重量。

工字钢理论重量

无缝钢管理论重量

D 为钢管的公称外径(㎜);S 为钢管的公称壁厚(㎜)。

花纹钢板理论重量

钢丝绳理论重量

等边角钢理论重量

不等边角钢理论重量

友情提示:本资料代表个人观点,如有帮助请下载,谢谢您的浏览!。

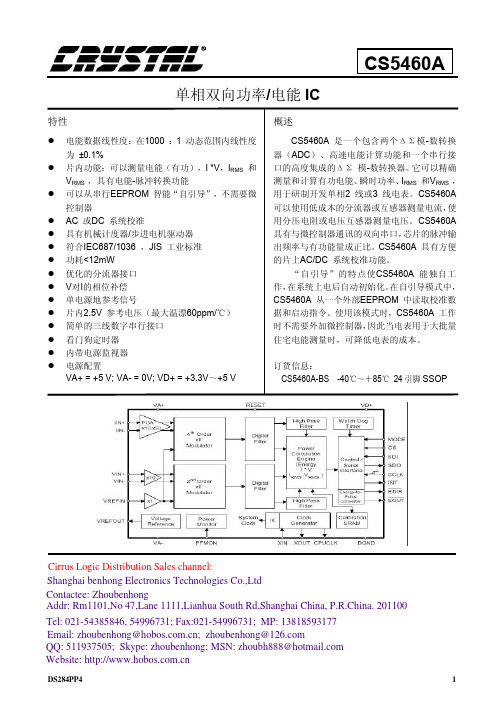

CS5460A中文数据手册

l 片内功能:可以测量电能(有功),I *V,IRMS 和 VRMS ,具有电能-脉冲转换功能

l 可以从串行EEPROM 智能“自引导”,不需要微 控制器

l AC 或DC 系统校准 l 具有机械计度器/步进电机驱动器 l 符合IEC687/1036 ,JIS 工业标准 l 功耗<12mW l 优化的分流器接口 l V对I的相位补偿 l 单电源地参考信号 l 片内2.5V 参考电压(最大温漂60ppm/℃) l 简单的三线数字串行接口 l 看门狗定时器 l 内带电源监视器 l 电源配置

VA+ = +5 V; VA- = 0V; VD+ = +3.3V~+5 V

概述

CS5460A 是一个包含两个ΔΣ模-数转换 器(ADC)、高速电能计算功能和一个串行接 口的高度集成的ΔΣ 模-数转换器。它可以精确 测量和计算有功电能、瞬时功率、IRMS 和VRMS , 用于研制开发单相2 线或3 线电表。CS5460A 可以使用低成本的分流器或互感器测量电流,使 用分压电阻或电压互感器测量电压。CS5460A 具有与微控制器通讯的双向串口,芯片的脉冲输 出频率与有功能量成正比。CS5460A 具有方便 的片上AC/DC 系统校准功能。

cs5460a单相双向功率电能ic特性rms具有电能脉冲转换功能可以从串行eeprom智能自引导不需要微控制器ac或dc系统校准符合iec6871036jis工业标准片内25v参考电压最大温漂60ppm电源配置va0v

【精品】职业危害物质接触限值

序号

中文名CASNo.

英文名

最高容许浓度

(mg/m3)

时间加权平均容许浓度

(mg/m3)

*短时间接触容许浓度

(mg/m3)

1.

安妥

(86—88-4)

Antu

-

0.3

0.9*

2。

氨

(7664-41-7)

Ammonia

-

20

30

3.

2—氨基吡啶(皮)

504—29—0

2-Aminopyridine(skin)

534-52—1

4,6—Dinitro—o—cresol(skin)

-

0.2

0.6*

80.

二氧化氮

10102—44—0

Nitrogendioxide

—

5

10

81。

二氧化硫

7446—09-5

Sulfurdioxide

—

5

10

82.

二氧化氯

10049-04-4

Chlorinedioxide

—

0.3

0。8

83。

二氧化碳

124-38-9

Carbondioxide

—

9000

18000

84。

二氧化锡(按Sn计)

1332-29-2

Tindioxdie,asSn

—

2

5*

85.

2—二乙氨基乙醇(皮)

100-37—8

2—Diethylaminoethanol(skin)

—

50

100*

86.

二乙撑三胺(皮)

111—40-0

XCS05XL-4BG144C中文资料

© 2001 Xilinx, Inc. All rights reserved. All Xilinx trademarks, registered trademarks, patents, and disclaimers are as listed at /legal.htm .All other trademarks and registered trademarks are the property of their respective owners. All specifications are subject to change without notice.IntroductionThe Spartan ™ and the Spartan-XL families are a high-vol-ume production FPGA solution that delivers all the key requirements for ASIC replacement up to 40,000 gates.These requirements include high performance, on-chip RAM, core solutions and prices that, in high volume,approach and in many cases are equivalent to mask pro-grammed ASIC devices.The Spartan series is the result of more than 14 years of FPGA design experience and feedback from thousands of customers. By streamlining the Spartan series feature set,leveraging advanced process technologies and focusing on total cost management, the Spartan series delivers the key features required by ASIC and other high-volume logic users while avoiding the initial cost, long development cycles and inherent risk of conventional ASICs. The Spar-tan and Spartan-XL families in the Spartan series have ten members, as shown in T able 1.Spartan and Spartan-XL FeaturesNote: The Spartan series devices described in this data sheet include the 5V Spartan family and the 3.3V Spartan-XL family. See the separate data sheet for the 2.5V Spartan-II family.•First ASIC replacement FPGA for high-volume production with on-chip RAM•Density up to 1862 logic cells or 40,000 system gates •Streamlined feature set based on XC4000 architecture •System performance beyond 80MHz•Broad set of AllianceCORE ™ and LogiCORE ™ predefined solutions available •Unlimited reprogrammability •Low cost•System level features-Available in both 5V and 3.3V versions -On-chip SelectRAM ™ memory -Fully PCI compliant-Full readback capability for program verificationand internal node observability -Dedicated high-speed carry logic -Internal 3-state bus capability-Eight global low-skew clock or signal networks -IEEE 1149.1-compatible Boundary Scan logic -Low cost plastic packages available in all densities -Footprint compatibility in common packages•Fully supported by powerful Xilinx development system -Foundation Series: Integrated, shrink-wrapsoftware-Alliance Series: Dozens of PC and workstationthird party development systems supported-Fully automatic mapping, placement and routing Additional Spartan-XL Features• 3.3V supply for low power with 5V tolerant I/Os •Power down input •Higher performance •Faster carry logic•More flexible high-speed clock network•Latch capability in Configurable Logic Blocks •Input fast capture latch•Optional mux or 2-input function generator on outputs •12 mA or 24 mA output drive •5V and 3.3V PCI compliant •Enhanced Boundary Scan •Express Mode configuration •Chip scale packagingSpartan and Spartan-XL Families Field Programmable Gate ArraysDS060 (v1.6) September 19, 2001Product Specification T able 1: Spartan and Spartan-XL Field Programmable Gate Arrays1.Max values of Typical Gate Range include 20-30% of CLBs used as RAM.2DS060 (v1.6) September 19, 2001General OverviewSpartan series FPGAs are implemented with a regular, flex-ible, programmable architecture of Configurable Logic Blocks (CLBs), interconnected by a powerful hierarchy of versatile routing resources (routing channels), and sur-rounded by a perimeter of programmable Input/Output Blocks (IOBs), as seen in Figure 1. They have generous routing resources to accommodate the most complex inter-connect patterns.The devices are customized by loading configuration data into internal static memory cells. Re-programming is possi-ble an unlimited number of times. The values stored in thesememory cells determine the logic functions and intercon-nections implemented in the FPGA. The FPGA can either actively read its configuration data from an external serial PROM (Master Serial mode), or the configuration data can be written into the FPGA from an external device (Slave Serial mode).Spartan series FPGAs can be used where hardware must be adapted to different user applications. FPGAs are ideal for shortening design and development cycles, and also offer a cost-effective solution for production rates well beyond 50,000 systems per month.Figure 1: Basic FPGA Block DiagramSpartan series devices achieve high-performance, low-cost operation through the use of an advanced architecture and semiconductor technology. Spartan and Spartan-XL devices provide system clock rates exceeding 80MHz and internal performance in excess of150MHz. In contrast to other FPGA devices, the Spartan series offers the most cost-effective solution while maintaining leading-edge per-formance. In addition to the conventional benefit of high vol-ume programmable logic solutions, Spartan series FPGAs also offer on-chip edge-triggered single-port and dual-port RAM, clock enables on all flip-flops, fast carry logic, and many other features.The Spartan/XL families leverage the highly successful XC4000 architecture with many of that family’s features and benefits. T echnology advancements have been derived from the XC4000XLA process developments.Logic Functional DescriptionThe Spartan series uses a standard FPGA structure as shown in Figure1, page2. The FPGA consists of an array of configurable logic blocks (CLBs) placed in a matrix of routing channels. The input and output of signals is achieved through a set of input/output blocks (IOBs) forming a ring around the CLBs and routing channels.•CLBs provide the functional elements for implementing the user’s logic.•IOBs provide the interface between the package pins and internal signal lines.•Routing channels provide paths to interconnect the inputs and outputs of the CLBs and IOBs.The functionality of each circuit block is customized during configuration by programming internal static memory cells. The values stored in these memory cells determine the logic functions and interconnections implemented in the FPGA.Configurable Logic Blocks (CLBs)The CLBs are used to implement most of the logic in an FPGA. The principal CLB elements are shown in the simpli-fied block diagram in Figure2. There are three look-up tables (LUT) which are used as logic function generators, two flip-flops and two groups of signal steering multiplexers. There are also some more advanced features provided by the CLB which will be covered in the Advanced Features Description, page13.Function GeneratorsTwo 16x1 memory look-up tables (F-LUT and G-LUT) are used to implement 4-input function generators, each offer-ing unrestricted logic implementation of any Boolean func-tion of up to four independent input signals (F1 to F4 or G1 to G4). Using memory look-up tables the propagation delay is independent of the function implemented.A third 3-input function generator (H-LUT) can implement any Boolean function of its three inputs. Two of these inputs are controlled by programmable multiplexers (see box "A" of Figure2). These inputs can come from the F-LUT or G-LUT outputs or from CLB inputs. The third input always comes from a CLB input. The CLB can, therefore, implement cer-tain functions of up to nine inputs, like parity checking. The three LUTs in the CLB can also be combined to do any arbi-trarily defined Boolean function of five inputs.4DS060 (v1.6) September 19, 2001A CLB can implement any of the following functions:•Any function of up to four variables, plus any second function of up to four unrelated variables, plus any third function of up to three unrelated variablesNote: When three separate functions are generated, one of the function outputs must be captured in a flip-flop internal to the CLB. Only two unregistered function generator outputs are available from the CLB.•Any single function of five variables•Any function of four variables together with some functions of six variables•Some functions of up to nine variables.Implementing wide functions in a single block reduces both the number of blocks required and the delay in the signal path, achieving both increased capacity and speed. The versatility of the CLB function generators significantly improves system speed. In addition, the design-software tools can deal with each function generator independently.This flexibility improves cell usage.Flip-FlopsEach CLB contains two flip-flops that can be used to regis-ter (store) the function generator outputs. The flip-flops and function generators can also be used independently (see Figure 2). The CLB input DIN can be used as a direct input to either of the two flip-flops. H1 can also drive either flip-flop via the H-LUT with a slight additional delay.The two flip-flops have common clock (CK), clock enable (EC) and set/reset (SR) inputs. Internally both flip-flops are also controlled by a global initialization signal (GSR) which is described in detail in Global Signals: GSR and GTS ,page 20.Latches (Spartan-XL only)The Spartan-XL CLB storage elements can also be config-ured as latches. The two latches have common clock (K)and clock enable (EC) inputs. Functionality of the storage element is described in Table 2.Figure 2: Spartan/XL Simplified CLB Logic Diagram (some features not shown)Clock InputEach flip-flop can be triggered on either the rising or falling clock edge. The CLB clock line is shared by both flip-flops.However, the clock is individually invertible for each flip-flop (see CK path in Figure 3). Any inverter placed on the clock line in the design is automatically absorbed into the CLB. Clock EnableThe clock enable line (EC) is active High. The EC line is shared by both flip-flops in a CLB. If either one is left discon-nected, the clock enable for that flip-flop defaults to the active state. EC is not invertible within the CLB. The clock enable is synchronous to the clock and must satisfy the setup and hold timing specified for the device.Set/ResetThe set/reset line (SR) is an asynchronous active High con-trol of the flip-flop. SR can be configured as either set or reset at each flip-flop. This configuration option determines the state in which each flip-flop becomes operational after configuration. It also determines the effect of a GSR pulse during normal operation, and the effect of a pulse on the SR line of the CLB. The SR line is shared by both flip-flops. If SR is not specified for a flip-flop the set/reset for that flip-flop defaults to the inactive state. SR is not invertible within the CLB.CLB Signal Flow ControlIn addition to the H-LUT input control multiplexers (shown in box "A" of Figure 2, page 4) there are signal flow control multiplexers (shown in box "B" of Figure 2) which select the signals which drive the flip-flop inputs and the combinatorial CLB outputs (X and Y).Each flip-flop input is driven from a 4:1 multiplexer which selects among the three LUT outputs and DIN as the data source.Each combinatorial output is driven from a 2:1 multiplexer which selects between two of the LUT outputs. The X output can be driven from the F-LUT or H-LUT, the Y output from G-LUT or H-LUT .Control SignalsThere are four signal control multiplexers on the input of the CLB. These multiplexers allow the internal CLB control sig-nals (H1, DIN, SR, and EC in Figure 2 and Figure 4) to be driven from any of the four general control inputs (C1-C4 in Figure 4) into the CLB. Any of these inputs can drive any of the four internal control signals.T able 2: CLB Storage Element FunctionalityLegend:XDon ’t careRising edge (clock not inverted).SR Set or Reset value. Reset is default.0*Input is Low or unconnected (default value)1*Input is High or unconnected (default value)Figure 3: CLB Flip-Flop Functional Block Diagram6DS060 (v1.6) September 19, 2001The four internal control signals are:•EC: Enable Clock•SR: Asynchronous Set/Reset or H function generator Input 0•DIN: Direct In or H function generator Input 2•H1: H function generator Input 1.Input/Output Blocks (IOBs)User-configurable input/output blocks (IOBs) provide the interface between external package pins and the internal logic. Each IOB controls one package pin and can be con-figured for input, output, or bidirectional signals. Figure 6shows a simplified functional block diagram of the Spar-tan/XL IOB.IOB Input Signal PathThe input signal to the IOB can be configured to either go directly to the routing channels (via I1 and I2 in Figure 6) or to the input register. The input register can be programmed as either an edge-triggered flip-flop or a level-sensitive latch. The functionality of this register is shown in Table 3,and a simplified block diagram of the register can be seen in Figure 5.Figure 4: CLB Control Signal InterfaceFigure 5: IOB Flip-Flop/Latch Functional BlockDiagramTable 3: Input Register FunctionalityX Don ’t care.Rising edge (clock not inverted).SR Set or Reset value. Reset is default.0*Input is Low or unconnected (default value)1*Input is High or unconnected (default value)The register choice is made by placing the appropriate library symbol. For example, IFD is the basic input flip-flop (rising edge triggered), and ILD is the basic input latch (transparent-High). Variations with inverted clocks are also available. The clock signal inverter is also shown in Figure5 on the CK line.The Spartan IOB data input path has a one-tap delay ele-ment: either the delay is inserted (default), or it is not. The Spartan-XL IOB data input path has a two-tap delay ele-ment, with choices of a full delay, a partial delay, or no delay. The added delay guarantees a zero hold time with respect to clocks routed through the global clock buffers. (See Glo-bal Nets and Buffers, page12 for a description of the glo-bal clock buffers in the Spartan/XL families.) For a shorter input register setup time, with positive hold-time, attach a NODELAY attribute or property to the flip-flop.The output of the input register goes to the routing channels (via I1 and I2 in Figure6). The I1 and I2 signals that exit the IOB can each carry either the direct or registered input signal.The 5V Spartan input buffers can be globally configured for either TTL (1.2V) or CMOS (VCC/2) thresholds, using an option in the bitstream generation software. The Spartan output levels are also configurable; the two global adjust-ments of input threshold and output level are independent. The inputs of Spartan devices can be driven by the outputs of any 3.3V device, if the Spartan inputs are in TTL mode. Input and output thresholds are TTL on all configuration pins until the configuration has been loaded into the device and specifies how they are to be used. Spartan-XL inputs are TTL compatible and 3.3V CMOS compatible. Supported sources for Spartan/XL device inputs are shown in Table4.Spartan-XL I/Os are fully 5V tolerant even though the V CC is 3.3V. This allows 5V signals to directly connect to the Spar-tan-XL inputs without damage, as shown in Table4. In addi-tion, the 3.3V V CC can be applied before or after 5V signals are applied to the I/Os. This makes the Spartan-XL devices immune to power supply sequencing problems.Figure 6: Simplified Spartan/XL IOB Block Diagram8DS060 (v1.6) September 19, 2001Spartan-XL V CC ClampingSpartan-XL FPGAs have an optional clamping diode con-nected from each I/O to V CC . When enabled they clamp ringing transients back to the 3.3V supply rail. This clamping action is required in 3.3V PCI applications. V CC clamping is a global option affecting all I/O pins.Spartan-XL devices are fully 5V TTL I/O compatible if V CC clamping is not enabled. With V CC clamping enabled, the Spartan-XL devices will begin to clamp input voltages to one diode voltage drop above V CC . If enabled, TTL I/O com-patibility is maintained but full 5V I/O tolerance is sacrificed.The user may select either 5V tolerance (default) or 3.3V PCI compatibility. In both cases negative voltage is clamped to one diode voltage drop below ground.Spartan-XL devices are compatible with TTL, LVTTL, PCI 3V, PCI 5V and LVCMOS signalling. The various standards are illustrated in Table 5.Additional Fast Capture Input Latch (Spartan-XL only)The Spartan-XL IOB has an additional optional latch on the input. This latch is clocked by the clock used for the output flip-flop rather than the input clock. Therefore, two different clocks can be used to clock the two input storage elements.This additional latch allows the fast capture of input data,which is then synchronized to the internal clock by the IOB flip-flop or latch.T o place the Fast Capture latch in a design, use one of the special library symbols, ILFFX or ILFLX. ILFFX is a trans-parent-Low Fast Capture latch followed by an active High input flip-flop. ILFLX is a transparent Low Fast Capture latch followed by a transparent High input latch. Any of the clock inputs can be inverted before driving the library element,and the inverter is absorbed into the IOB.IOB Output Signal PathOutput signals can be optionally inverted within the IOB,and can pass directly to the output buffer or be stored in an edge-triggered flip-flop and then to the output buffer. The functionality of this flip-flop is shown in T able 6.T able 4: Supported Sources for Spartan/XL InputsT able 5: I/O Standards Supported by Spartan-XL FPGAsTable 6: Output Flip-Flop Functionality X Don ’t careRising edge (clock not inverted). SR Set or Reset value. Reset is default.0*Input is Low or unconnected (default value)1*Input is High or unconnected (default value)Z3-stateOutput Multiplexer/2-Input Function Generator (Spartan-XL only)The output path in the Spartan-XL IOB contains an addi-tional multiplexer not available in the Spartan IOB. The mul-tiplexer can also be configured as a 2-input function generator, implementing a pass gate, AND gate, OR gate, or XOR gate, with 0, 1, or 2 inverted inputs.When configured as a multiplexer, this feature allows two output signals to time-share the same output pad, effec-tively doubling the number of device outputs without requir-ing a larger, more expensive package. The select input is the pin used for the output flip-flop clock, OK.When the multiplexer is configured as a 2-input function generator, logic can be implemented within the IOB itself. Combined with a Global buffer, this arrangement allows very high-speed gating of a single signal. For example, a wide decoder can be implemented in CLBs, and its output gated with a Read or Write Strobe driven by a global buffer. The user can specify that the IOB function generator be used by placing special library symbols beginning with the letter "O." For example, a 2-input AND gate in the IOB func-tion generator is called OAND2. Use the symbol input pin labeled "F" for the signal on the critical path. This signal is placed on the OK pin — the IOB input with the shortest delay to the function generator. Two examples are shown in Figure7.Output BufferAn active High 3-state signal can be used to place the out-put buffer in a high-impedance state, implementing 3-state outputs or bidirectional I/O. Under configuration control, the output (O) and output 3-state (T) signals can be inverted. The polarity of these signals is independently configured for each IOB (see Figure6, page7). An output can be config-ured as open-drain (open-collector) by tying the 3-state pin (T) to the output signal, and the input pin (I) to Ground.By default, a 5V Spartan device output buffer pull-up struc-ture is configured as a TTL-like totem-pole. The High driver is an n-channel pull-up transistor, pulling to a voltage one transistor threshold below V CC. Alternatively, the outputs can be globally configured as CMOS drivers, with additional p-channel pull-up transistors pulling to V CC. This option, applied using the bitstream generation software, applies to all outputs on the device. It is not individually programma-ble.All Spartan-XL device outputs are configured as CMOS drivers, therefore driving rail-to-rail. The Spartan-XL outputs are individually programmable for 12mA or 24mA output drive.Any 5V Spartan device with its outputs configured in TTL mode can drive the inputs of any typical 3.3V device. Sup-ported destinations for Spartan/XL device outputs are shown in Table7.Three-State Register (Spartan-XL Only)Spartan-XL devices incorporate an optional register control-ling the three-state enable in the IOBs. The use of the three-state control register can significantly improve output enable and disable time.Output Slew RateThe slew rate of each output buffer is, by default, reduced, to minimize power bus transients when switching non-criti-cal signals. For critical signals, attach a FAST attribute or property to the output buffer or flip-flop.Spartan/XL devices have a feature called "Soft Start-up," designed to reduce ground bounce when all outputs are turned on simultaneously at the end of configuration. When the configuration process is finished and the device starts up, the first activation of the outputs is automatically slew-rate limited. Immediately following the initial activation of the I/O, the slew rate of the individual outputs is deter-mined by the individual configuration option for each IOB. Pull-up and Pull-down NetworkProgrammable pull-up and pull-down resistors are used fortying unused pins to V CC or Ground to minimize power con-sumption and reduce noise sensitivity. The configurablepull-up resistor is a p-channel transistor that pulls to V CC.The configurable pull-down resistor is an n-channel transis-tor that pulls to Ground. The value of these resistors is typi-cally 20KΩ − 100KΩ (See "Spartan DC Characteristics Figure 7: AND and MUX Symbols in Spartan-XL IOB10DS060 (v1.6) September 19, 2001Over Operating Conditions" on page 43.). This high value makes them unsuitable as wired-AND pull-up resistors.After configuration, voltage levels of unused pads, bonded or unbonded, must be valid logic levels, to reduce noise sensitivity and avoid excess current. Therefore, by default,unused pads are configured with the internal pull-up resistor active. Alternatively, they can be individually configured with the pull-down resistor, or as a driven output, or to be driven by an external source. To activate the internal pull-up, attach the PULLUP library component to the net attached to the pad. To activate the internal pull-down, attach the PULL-DOWN library component to the net attached to the pad.Set/ResetAs with the CLB registers, the GSR signal can be used to set or clear the input and output registers, depending on the value of the INIT attribute or property. The two flip-flops can be individually configured to set or clear on reset and after configuration. Other than the global GSR net, no user-con-trolled set/reset signal is available to the I/O flip-flops (Figure 5). The choice of set or reset applies to both the ini-tial state of the flip-flop and the response to the GSR pulse.Independent ClocksSeparate clock signals are provided for the input (IK) and output (OK) flip-flops. The clock can be independently inverted for each flip-flop within the IOB, generating eitherfalling-edge or rising-edge triggered flip-flops. The clock inputs for each IOB are mon Clock EnablesThe input and output flip-flops in each IOB have a common clock enable input (see EC signal in Figure 5), which through configuration, can be activated individually for the input or output flip-flop, or both. This clock enable operates exactly like the EC signal on the Spartan/XL CLB. It cannot be inverted within the IOB.Routing Channel DescriptionAll internal routing channels are composed of metal seg-ments with programmable switching points and switching matrices to implement the desired routing. A structured,hierarchical matrix of routing channels is provided to achieve efficient automated routing.This section describes the routing channels available in Spartan/XL devices. Figure 8 shows a general block dia-gram of the CLB routing channels. The implementation soft-ware automatically assigns the appropriate resources based on the density and timing requirements of the design.The following description of the routing channels is for infor-mation only and is simplified with some minor details omit-ted. For an exact interconnect description the designer should open a design in the FPGA Editor and review the actual connections in this tool.The routing channels will be discussed as follows;•CLB routing channels which run along each row and column of the CLB array.•IOB routing channels which form a ring (called a VersaRing) around the outside of the CLB array. It connects the I/O with the CLB routing channels.•Global routing consists of dedicated networks primarily designed to distribute clocks throughout the device with minimum delay and skew. Global routing can also be used for other high-fanout signals.CLB Routing ChannelsThe routing channels around the CLB are derived from three types of interconnects; single-length, double-length,and longlines. At the intersection of each vertical and hori-zontal routing channel is a signal steering matrix called a Programmable Switch Matrix (PSM). Figure 8 shows the basic routing channel configuration showing single-length lines, double-length lines and longlines as well as the CLBs and PSMs. The CLB to routing channel interface is shown as well as how the PSMs interface at the channel intersec-tions.T able 7: Supported Destinations for Spartan/XL OutputsNotes:1.Only if destination device has 5V tolerant inputs.CLB InterfaceA block diagram of the CLB interface signals is shown in Figure9. The input signals to the CLB are distributed evenly on all four sides providing maximum routing flexibility. In general, the entire architecture is symmetrical and regular. It is well suited to established placement and routing algo-rithms. Inputs, outputs, and function generators can freely swap positions within a CLB to avoid routing congestion during the placement and routing operation. The exceptions are the clock (K) input and CIN/COUT signals. The K input is routed to dedicated global vertical lines as well as four single-length lines and is on the left side of the CLB. The CIN/COUT signals are routed through dedicated intercon-nects which do not interfere with the general routing struc-ture. The output signals from the CLB are available to drive both vertical and horizontal channels.Programmable Switch MatricesThe horizontal and vertical single- and double-length lines intersect at a box called a programmable switch matrix (PSM). Each PSM consists of programmable pass transis-tors used to establish connections between the lines (see Figure10).For example, a single-length signal entering on the right side of the switch matrix can be routed to a single-length line on the top, left, or bottom sides, or any combination thereof, if multiple branches are required. Similarly, a dou-ble-length signal can be routed to a double-length line on any or all of the other three edges of the programmable switch matrix.Single-Length LinesSingle-length lines provide the greatest interconnect flexibil-ity and offer fast routing between adjacent blocks. There are eight vertical and eight horizontal single-length lines associ-ated with each CLB. These lines connect the switching matrices that are located in every row and column of CLBs. Single-length lines are connected by way of the program-mable switch matrices, as shown in Figure10. Routing con-nectivity is shown in Figure8.Single-length lines incur a delay whenever they go through a PSM. Therefore, they are not suitable for routing signals for long distances. They are normally used to conduct sig-nals within a localized area and to provide the branching for nets with fanout greater than one.Figure 8: Spartan/XL CLB Routing Channels and Interface Block DiagramFigure 9: CLB Interconnect Signals。

5804中文资料

5804中⽂资料Combining low-power CMOS logic with high-current and high-voltage bipolar outputs, the UCN5804B and UCN5804LB BiMOS II translator/drivers provide complete control and drive for a four-phase unipolar stepper-motor with continuous output current ratings to 1.25 A per phase (1.5 A startup) and 35 V.The CMOS logic section provides the sequencing logic, DIRECTION and OUTPUT ENABLE control, and a power-on reset function. Three stepper-motor drive formats, wave-drive (one-phase), two-phase, and half-step are externally selectable. The inputs are compatible with standard CMOS, PMOS, and NMOS circuits. TTL or LSTTL may require the use of appropriate pull-up resistors to ensure a proper input-logic high.The wave-drive format consists of energizing one motor phase at a time in an A-B-C-D (or D-C-B-A) sequence. This excitation mode consumes the least power and assures positional accuracy regardless of any winding inbalance in the motor. Two-phase drive energizes two adjacent phases in each detent position (AB-BC-CD-DA). This sequence mode offers animproved torque-speed product, greater detent torque, and is less susceptible to motor resonance. Half-step excitation alternates between the one-phase and two-phase modes (A-AB-B-BC-C-CD-D-DA), providing an eight-step sequence.The bipolar outputs are capable of sinking up to 1.5 A and withstanding 50 V in the off state (sustaining voltages up to 35 V). Ground-clamp and flyback diodes provide protection against inductive transients. Thermal protection circuitry disables the outputs when the chip temperature is exces-sive.Both devices are rated for operation over the temperature range of -20°C to +85°C. The UCN5804B is supplied in a 16-pin dual in-line plastic batwing package with a copper lead frame and heat-sinkable tabs for improved power dissipation capabilities; the UCN5804LB is supplied in a 16-lead plastic SOIC batwing package with a copper lead frame and heat-sinkable tabs.FEATURESI 1.5 A Maximum Output Current I 35 V Output Sustaining VoltageI Wave-Drive, Two-Phase, and Half-Step Drive Formats I Internal Clamp DiodesI Output Enable and Direction Control I Power-On ResetI Internal Thermal Shutdown CircuitryBiMOS II UNIPOLARSTEPPER-MOTOR TRANSLATOR/DRIVERAlways order by complete part number, e.g., UCN5804B .Data Sheet 26184.12C*5804115 Northeast Cutoff, Box 15036Worcester, Massachusetts 01615-0036 (508) 853-********BiMOS II UNIPOLAR STEPPER-MOTORTRANSLATOR/DRIVERTRUTH TABLEDrive Format Pin 9Pin 10Two-Phase L L One-Phase H L Half-Step L H Step-InhibitHHTYPICAL INPUT CIRCUITDwg. EP-021-4TYPICAL OUTPUT DRIVERDwg. EP-010-5INCopyright ? 1987, 2000 Allegro MicroSystems, Inc.5075100125150510A L L O W A B L E P A C K A G E P O W E R D I S S I P A T I O N I N W A T T STEMPERATURE IN °C43225Dwg. GP-049-2A5804BiMOS II UNIPOLAR STEPPER-MOTOR TRANSLATOR/DRIVER/doc/a3712eddb9f3f90f76c61b7c.htmlELECTRICAL CHARACTERISTICS at T A = 25°C, T J ≤ 150°C, V DD = 4.5 V to 5.5 V (unless otherwise noted). Limits CharacteristicSymbol Test Conditions Min.Typ.Max.Units Output Leakage Current I CEX V OUT = 50 V—1050µA Output Sustaining Voltage V CE(sus)I OUT = 1.25 A, L = 3 mH 35——V Output Saturation VoltageV CE(SAT)I OUT = 700 mA — 1.0 1.2V I OUT = 1 A — 1.1 1.4V I OUT= 1.25 A— 1.2 1.5V Clamp Diode Leakage Current I R V R = 50 V —1050µA Clamp Diode Forward Voltage V F I F = 1.25 A — 1.53.0V Input CurrentI IN(1)V IN = V DD —0.5 5.0µA I IN(0)V IN = 0.8 V —-0.5-5.0µA Input VoltageV IN(1)V DD = 5 V3.5— 5.3V V IN(0)-0.3—0.8V Supply Current I DD 2 Outputs ON—2030mA Turn-Off Delay t ON 50% Step Inputs to 50% Output ——10µs Turn-On Delayt OFF 50% Step Inputs to 50% Output ——10µs Thermal Shutdown TemperatureT J—165—°CTIMING CONDITIONSA. Minimum Data Set Up Time . . . . . . . . . . . . . . . . . . . . . . . . 100 nsB. Minimum Data Hold Time . . . . . . . . . . . . . . . . . . . . . . . . . . 100 nsC. Minimum Step Input Pulse Width . . . . . . . . . . . . . . . . . . . . . 3.0 µsDwg. W-110AONE PHASE HALF STEPOOUTPUT ENABLEOUTPUT C OUTPUT DCLOCK115 Northeast Cutoff, Box 15036Worcester, Massachusetts 01615-0036 (508) 853-50005804BiMOS II UNIPOLAR STEPPER-MOTORTRANSLATOR/DRIVERWAVE-DRIVE SEQUENCEHalf Step = L, One Phase = H Step A B C D POR ON OFF OFF OFF 1ON OFF OFF OFF 2OFF ON OFF OFF 3OFF OFF ON OFF 4OFFOFFOFFONTWO-PHASE DRIVE SEQUENCEHalf Step = L, One Phase = LStep A B C D POR ON OFF OFF ON 1ON OFF OFF ON 2ON ON OFF OFF 3OFF ON ON OFF 4OFFOFFONONHALF-STEP DRIVE SEQUENCEHalf Step = H, One Phase = LStep A B C D POR ON OFF OFF OFF 1ON OFF OFF OFF 2ON ON OFF OFF 3OFF ON OFF OFF 4OFF ON ON OFF 5OFF OFF ON OFF 6OFF OFF ON ON 7OFF OFF OFF ON 8ONOFFOFFONAPPLICATIONS INFORMATIONInternal power-on reset (POR) circuitry resets OUTPUT A (and OUTPUT D in the two-phase drive format) to the on state with initial applica-tion of the logic supply voltage. After reset, the circuit then steps according to the tables.The outputs will advance one sequenceposition on the high-to-low transition of the STEP INPUT pulse. Logic levels on the HALF-STEP and ONE-PHASE inputs will determine the drive format (one-phase, two-phase, or half-step). The DIRECTION pin determines the rotation se-quence of the outputs. Note that the STEP INPUT must be in the low state when changing the state of ONE-PHASE, HALF-STEP, or DIRECTION to prevent erroneous stepping.All outputs are disabled (off) when OUTPUT ENABLE is at a logic high. If the function is not required, OUTPUT ENABLE should be tied low.In that condition, all outputs depend only on the state of the step logic.During normal commutation of a unipolar stepper motor, mutual coupling between the motor windings can force the outputs of the UCN5804B below ground. This condition will cause forward biasing of the collector-to-substrate junction and source current from the output. For many L/R applications, this substrate current is high enough to adversely affect the logic circuitry and cause misstepping. External series diodes (Schottky are recommended for increasedefficiency at low-voltage operation) will prevent substrate current from being sourced through the outputs. Alternatively, external ground clamp diodes will provide a preferred current path from ground when the outputs are pulled below ground.Internal thermal protection circuitry disables all outputs when the junction temperature reaches approximately 165°C. The outputs are enabled again when the junction cools down to approxi-mately 145°C.5804BiMOS II UNIPOLAR STEPPER-MOTOR TRANSLATOR/DRIVER/doc/a3712eddb9f3f90f76c61b7c.htmlTYPICAL APPLICATION L/R Stepper-Motor DriveThe products described here are manufactured under one or more U.S. patents or U.S. patents pending.Allegro MicroSystems, Inc. reserves the right to make, from time to time, such departures from the detail specifications as may berequired to permit improvements in the performance, reliability, or manufacturability of its products. Before placing an order, the user is cautioned to verify that the information being relied upon is current.Allegro products are not authorized for use as critical components in life-support devices or systems without express written approval.The information included herein is believed to be accurate and reliable. However, Allegro MicroSystems, Inc. assumes no responsi-bility for its use; nor for any infringement of patents or other rights of third parties which may result from its use.115 Northeast Cutoff, Box 15036Worcester, Massachusetts 01615-0036 (508) 853-50005804BiMOS II UNIPOLAR STEPPER-MOTORTRANSLATOR/DRIVERUCN5804BDimensions in Inches (controlling dimensions)Dimensions in Millimeters(for reference only)NOTES:1.Exact body and lead configuration at vendor’s option within limits shown.2.Lead spacing tolerance is non-cumulative.3.Lead thickness is measured at seating plane or below.4.Webbed lead frame. Leads 4, 5, 12, and 13 are internally one piece.5.Supplied in standard sticks/tubes of 25 devices.Dwg. MA-001-17A in18Dwg. MA-001-17A mm185804 BiMOS II UNIPOLAR STEPPER-MOTOR TRANSLATOR/DRIVER/doc/a3712eddb9f3f90f76c61b7c.htmlUCN5804LB(add “TR” to part number for tape and reel) Dimensions in Inches(for reference only)Dimensions in Millimeters(controlling dimensions)NOTES:1.Exact body and lead configuration at vendor’s option within limits shown.2.Lead spacing tolerance is non-cumulative.3.Lead thickness is measured at seating plane or below.4.Webbed lead frame. Leads 4, 5, 12, and 13 are internally one piece.5.Supplied in standard sticks/tubes of 47 devices or add “TR” to part number for tape and reel.115 Northeast Cutoff, Box 15036Worcester, Massachusetts 01615-0036 (508) 853-50005804BiMOS II UNIPOLAR STEPPER-MOTORTRANSLATOR/DRIVERMOTOR DRIVERSFunctionOutput Ratings*Part Number ?INTEGRATED CIRCUITS FOR BRUSHLESS DC MOTORS3-Phase Power MOSFET Controller —28 V 39333-Phase Power MOSFET Controller —50 V 39323-Phase Power MOSFET Controller —50 V 76002-Phase Hall-Effect Sensor/Driver 400 mA 26 V 3626Bidirectional 3-Phase Back-EMFController/Driver ±600 mA 14 V 89062-Phase Hall-Effect Sensor/Driver 900 mA 14 V 36253-Phase Back-EMFController/Driver ±900 mA 14 V 8902–A 3-Phase Controller/Drivers ±2.0 A 45 V 2936 & 2936-120INTEGRATED BRIDGE DRIVERS FOR DC AND BIPOLAR STEPPER MOTORSDual Full Bridge with Protection & Diagnostics ±500 mA 30 V 3976PWM Current-Controlled Dual Full Bridge ±650 mA 30 V 3966PWM Current-Controlled Dual Full Bridge ±650 mA 30 V 3968PWM Current-Controlled Dual Full Bridge ±750 mA 45 V 2916PWM Current-Controlled Dual Full Bridge ±750 mA 45 V 2919PWM Current-Controlled Dual Full Bridge ±750 mA 45 V 6219PWM Current-Controlled Dual Full Bridge ±800 mA 33 V 3964PWM Current-Controlled Full Bridge ±1.3 A 50 V3953PWM Current-Controlled Dual Full Bridge ±1.5 A 45 V 2917PWM Current-Controlled Microstepping Full Bridge ±1.5 A 50 V 3955PWM Current-Controlled Microstepping Full Bridge ±1.5 A 50 V 3957PWM Current-Controlled Dual DMOS Full Bridge ±1.5 A 50 V 3972Dual Full-Bridge Driver ±2.0 A 50 V 2998PWM Current-Controlled Full Bridge ±2.0 A 50 V3952DMOS Full Bridge PWM Driver ±2.0 A 50 V 3958Dual DMOS Full Bridge ±2.5 A 50 V 3971UNIPOLAR STEPPER MOTOR & OTHER DRIVERSVoice-Coil Motor Driver ±500 mA 6 V 8932–A Voice-Coil Motor Driver ±800 mA 16 V 8958Unipolar Stepper-Motor Quad Drivers 1 A 46 V 7024 & 7029Unipolar Microstepper-Motor Quad Driver 1.2 A 46 V 7042Unipolar Stepper-Motor Translator/Driver 1.25 A 50 V 5804Unipolar Stepper-Motor Quad Driver 1.8 A 50 V 2540Unipolar Stepper-Motor Quad Driver 1.8 A 50 V 2544Unipolar Stepper-Motor Quad Driver 3 A 46 V 7026Unipolar Microstepper-Motor Quad Driver 3 A 46 V 7044*Current is maximum specified test condition, voltage is maximum rating. See specification for sustaining voltage limits or over-current protection voltage limits. Negative current is defined as coming out of (sourcing) the output.?Complete part number includes additional characters to indicate operating temperature range and package style.Also, see 3175, 3177, 3235, and 3275 Hall-effect sensors for use with brushless dc motors.。

四亚乙基五胺-职业病危害告知牌

职业病危害告知牌对人体有损害,请注意防护!

四亚乙基五胺Tetraethylenepenta

minie

健康危害理化特性

吸入本品蒸气对呼吸道有刺激作用和致敏作用。

眼接触可致角膜损害。

皮肤接触可致灼伤,有致

敏作用。

摄入灼伤消化道,引起腹痛、恶心、呕

吐和腹泻。

黄色或橙红色粘稠液体。

易溶于水,溶于乙

醇,不溶于苯、乙醚,可混溶于甲醇、丙酮

等。

熔点-30℃,沸点340.3℃,闪点162.7℃。

职业接触限值:MAC:无资料

PC-TWA:无资料

PC-STEL:无资料

皮肤接触:脱去污染的衣着,立即用大量流动清水彻底冲洗至少15分钟。

就医。

眼睛接触:用流动清水或生理盐水冲洗至少15分钟。

就医。

吸入:迅速脱离现场至空气新鲜处。

保持呼吸道通畅。

呼吸困难时给输氧。

呼吸停止时,立即进行人工呼吸。

就医。

食入:误服者漱口,给饮牛奶或蛋清。

就医。

注意防护

密闭操作,全面通风。

操作人员必须经过专门培训,严格遵守操作规程。

建议操作人员佩戴直接式防毒面具,戴化学安全防护眼镜,穿防腐工作服,戴橡胶手套。

防止蒸气泄漏到工作场所空气中。

避免与酸类接触。

搬运时要轻装轻卸,防止包装及容器损坏。

急救电话:120 消防电话:119 职业卫生咨询电话:1031。

DIN5480-5

23

26 +0,41

24

27 +0,41

25

28 +0,41

26

29 +0,41

27

30 +0,41

28

31 +0,41

29

32 +0,41

30

33 +0,41

31

34 +0,41

32

35 +0,41

33

36 +0,41

34

37 +0,41

35

38 +0,41

36

39 +0,41

37

40 +0,41

da1

11,7 12,7 13,7 14,7 15,7 16,7 17,7 18,7 19,7 20,7 21,7 22,7 23,7 24,7 25,7 26,7 27,7 28,7 29,7 30,7 31,7 32,7 33,7 34,7 35,7 36,7 37,7 38,7 39,7 41,7 44,7 46,7 47,7 49,7 51,7 54,7 57,7 59,7 61,7 64,7 67,7 69,7 71,7 74,7 77,7 79,7 81,7 84,7 87,7 89,7 91,7 94,7 97,7 99,7 104,7 109,7

72

75 +0,42

75 (78) +0,42

77

80 +0,42

79 (82) +0,42

82

85 +0,42

85 (88) +0,42

87

90 +0,42

89 (92) +0,42

1,2,4,5-四氯苯

1、物质的理化常数CA国标编号: 6165995-94-3S:中文名称: 1,2,4,5-四氯苯英文名称: 1,2,4,5-Tetrachlorobenzene别名:分子分子式: C6H2Cl4215.89量:熔点: 138℃ 沸点:245℃密度: 相对密度(水=1)1.73;蒸汽压: 110℃溶解性: 溶于苯稳定性: 稳定外观与性白色薄片状:危险标记: 15(有害品,远离食品)用途: 用作有机合成中间体2.对环境的影响:一、健康危害侵入途径:吸入、食入、经皮吸收。

健康危害:本品对粘膜、上呼吸道、眼睛和皮肤的刺激性。

二、毒理学资料急性毒性:LD501500mg/kg(大鼠经口)危险特性:遇明火、高热可燃。

与强氧化剂可发生反应。

受高热分解产生有毒的腐蚀性气体。

燃烧(分解)产物:一氧化碳、二氧化碳、氯化氢。

3.现场应急监测方法:4.实验室监测方法:气相色谱法《固体废弃物试验分析评价手册》中国环境监测总站等译色谱/质谱法《固体废弃物试验分析评价手册》中国环境监测总站等译5.环境标准:前苏联(1975)水体中有害物质最高允许浓度 0.01mg/L嗅觉阈浓度 0.13mg/L6.应急处理处置方法:一、泄漏应急处理隔离泄漏污染区,周围设警告标志,切断火源。

建议应急处理人员戴好防毒面具,穿化学防护服。

不要直接接触泄漏物,避免扬尘,收集置于袋中转移至安全场所,如大量泄漏,收集回收或无害处理后废弃。

二、防护措施呼吸系统防护:高浓度环境中,应该佩带防毒面具。

眼睛防护:戴安全防护眼镜。

防护服:穿相应的防护服。

手防护:必要时戴防化学品手套。

其它:工作现场禁止吸烟、进食和饮水。

工作后,彻底清洗。

单独存放被毒物污染的衣服,洗后再用。

注意个人清洁卫生。

三、急救措施皮肤接触:脱去污染的衣着,用肥皂水及清水彻底冲洗。

眼睛接触:立即提起眼睑,用大量流动清水或生理盐水冲洗。

吸入:迅速脱离现场至空气新鲜处。

必要时进行人工呼吸。

就医。

食入:误服者给充分漱口、饮水,尽快洗胃。

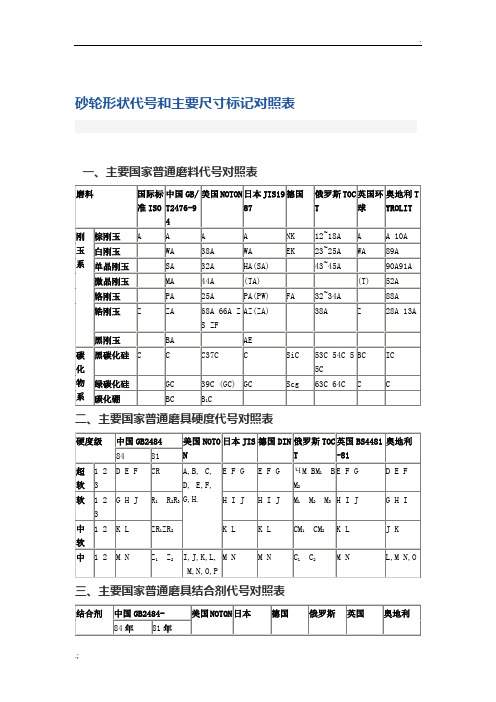

砂轮形状代号和主要尺寸标记对照表

G H J

R1R2R3

H I J

H I J

M1M2M3

H I J

G H I

中软

1 2

K L

ZR1ZR2

K L

K L

CM1CM2

K L

J K

中

1 2

M N

Z1Z2

I,J,K,L, M,N,O,P

M N

M N

C1C2

M N

L,M N,O

三、主要国家普通磨具结合剂代号对照表

结合剂

中国GB2484-

单结晶氧化铝

A?

?2A/HA

32A/SA (NA)44A

Al2O399.3% TiO20.1~0.3%

模具钢、合金钢、工具钢、淬火钢材的精密磨削镀硬铬、镍铬钼合金,Φ11-25mm之间最佳

超微晶粒陶瓷(高效率磨料)

AS5

KG

SG/CXY/TG

Al2O399.8% ZrO22.6%

一般钢材自由磨削,超重磨削,锐利持久性特优镀硬铬、镍铬钼合金。

白色氧化铝

WA

WA

89A/A 80A/82A

Al2O398.3%以上

淬火钢材的精密磨削,轻磨削淬火硬化钢80#-LΦ<10mm,60#-KLΦ11-15mm之间最佳

淡红色氧化铝

PA

PSA

86A

Al2O397% Cr2O30.1~0.45%

合金钢、工具钢、淬火钢材的精密磨削。镀硬铬、镍铬钼合金,Φ<10mm铬之间采用60#-KL

43~45A

90A91A

微晶刚玉

MA

44A

(TA)

(T)

52A

铬刚玉

PA