si5010

ifm5010流量传感器中文说明

3

2 功能和特性

2.1 应用范围 本设备可用于监控液体及气体介质的流量。 2.2 流量监控的工作原理 • 本设备采用量热原理,可检测流速并切换输出功能: -- 如果有介质流动,则关闭输出功能/如果无介质流动,则开启输出功能。 本设备交货时功能设定如下: 输出功能 = 常开。 如有需要,可将输出功能更改 为常闭 (→ 7.2)。 此时适用於: 如果有介质流动,则开启输出功能。 • 如果流速加快,且达到开关点时,开关状态将会改变。 • 如果流速再次减慢,且达到“开关点的迟滞还原”值时,开关状态将会改变。 迟滞状态随流速而改变,且主要受所设监控范围的影响。 设定范围为 5...100 cm/s (= 出厂设定)时,迟滞范围为 2...5 cm/s,流速加快 时迟滞值将增大。 • 设备的标准反应时间为 1...10 秒。 反应时间受开关点设定的影响: -- 低开关点 = 流量增加时快速反应。 -- 高开关点 = 流量减少时快速反应。

8

6.2 高流量调节(可选) 设备会将现有流量视为正常流量,并改变显示的指示状态(除开关点 LED 外,所 有 LED 呈绿色亮起)。 ►► 安装时,使用正常的流量环流。 不放。 ►► 按住按钮 >> LED 9 亮起,约 5 秒后开始闪烁。 ►► 释放按钮。 此时,设备已按流量条件调节。 设备进入工作模式,显示如示例 1 所示。 注意: 所作调节将影响开关点状态: 它将相应地增加(最高将达到 LED 7)。 CN 远程调节 → 7.5。

6

务必由合格的电工连接设备。 务必遵守电气设备安装相关的国内和国际法规。 电源电压应符合 EN 50178、SELV 和 PELV 标准。 ►► 切断电源。 ►► 按下图连接设备:

1 BN 2 3 4 1 A 4 BK 3 BU 2 WH L+ LP B 1 BN 4 BK 3 BU 2 WH L+ LP CN

Silicon Laboratories C8051F380 1 2 3 4 5 6 7 C USB

-10 位 ADC(仅 C8051F380/1/2/3/C)•高达 500ksps•内建模拟多路复用器,单端和差分模式•VREF 来自外部引脚、内部参考或 V DD•内建温度传感器•外部转换启动输入选项-两个比较器-内部参考电压(仅 C8051F380/1/2/3/C)-掉电检测器和上电复位电路USB 功能控制器-符合 USB 规格 2.0-全速 (12Mbps) 或低速 (1.5Mbps) 运行-集成时钟恢复;全速或低速无需外部晶体-支持八个灵活的终端-1kB USB 缓冲存储器-集成收发器;无需外部电阻片上调试-片上调试电路提供全速、非侵入式的系统内调试(无需仿真器)-提供断点、单步执行、检查/修改内存和寄存器-比使用 ICE 芯片、目标仿真头和仿真插座的仿真系统有更优越的性能电源电压输入: 2.7 至 5.25V-使用片内稳压器时,支持的电压范围为 2.7~5.25V -流水线指令体系结构;70% 指令的执行时间为 1 个或2个系统时钟-高达 48 MIPS 的操作-扩展的中断处理程序内存-4352 或 2304字节 RAM-64、32 或 16kB 闪存;可在系统内编程的 512 字节扇区数字外围设备-40/25 个端口 I/O;全部能承受 5V 高灌电流-硬件增强型SPI™、两个 I2C/SMBus™ 和两个增强型UART 串口-六个通用 16 位计数器/定时器-16 位可编程计数器阵列 (PCA),有五个采集/比较模块-外部存储器接口 (EMIF)时钟源-内部振荡器:启用时钟恢复时精度为 ±0.25%。

支持所有USB 和 UART 模式-外部振荡器:晶体、RC、C 或时钟(1 或 2 引脚模式)-低频 (80kHz) 内部振荡器-在运行中可切换时钟源封装-48 引脚 TQFP (C8051F380/2/4/6)-32 引脚 LQFP (C8051F381/3/5/7/C)-5x5mm 32 引脚 QFN (C8051F381/3/5/7/C)温度范围: –40 至 +85°CC8051F380/1/2/3/4/5/6/7/CC8051F380/1/2/3/4/5/6/7/CTable of Contents1. System Overview (16)2. C8051F34x Compatibility (20)2.1. Hardware Incompatibilities (21)3. Pinout and Package Definitions (22)4. Typical Connection Diagrams (34)4.1. Power (34)4.2. USB (36)4.3. Voltage Reference (VREF) (36)5. Electrical Characteristics (37)5.1. Absolute Maximum Specifications (37)5.2. Electrical Characteristics (38)6. 10-Bit ADC (ADC0, C8051F380/1/2/3/C only) (46)6.1. Output Code Formatting (47)6.3. Modes of Operation (50)6.3.1. Starting a Conversion (50)6.3.2. Tracking Modes (51)6.3.3. Settling Time Requirements (52)6.4. Programmable Window Detector (56)6.4.1. Window Detector Example (58)6.5. ADC0 Analog Multiplexer (C8051F380/1/2/3/C only) (59)7. Voltage Reference Options (62)8. Comparator0 and Comparator1 (64)8.1. Comparator Multiplexers (71)9. Voltage Regulators (REG0 and REG1) (74)9.1. Voltage Regulator (REG0) (74)9.1.1. Regulator Mode Selection (74)9.1.2. VBUS Detection (74)9.2. Voltage Regulator (REG1) (74)10. Power Management Modes (76)10.1. Idle Mode (76)10.2. Stop Mode (77)10.3. Suspend Mode (77)11. CIP-51 Microcontroller (79)11.1. Instruction Set (80)11.1.1. Instruction and CPU Timing (80)11.2. CIP-51 Register Descriptions (85)12. Prefetch Engine (88)13. Memory Organization (89)13.1. Program Memory (91)13.2. Data Memory (91)13.3. General Purpose Registers (92)13.4. Bit Addressable Locations (92)13.5. Stack (92)C8051F380/1/2/3/4/5/6/7/C14. External Data Memory Interface and On-Chip XRAM (93)14.1. Accessing XRAM (93)14.1.1. 16-Bit MOVX Example (93)14.1.2. 8-Bit MOVX Example (93)14.2. Accessing USB FIFO Space (94)14.3. Configuring the External Memory Interface (95)14.4. Port Configuration (95)14.5. Multiplexed and Non-multiplexed Selection (98)14.5.1. Multiplexed Configuration (98)14.5.2. Non-multiplexed Configuration (98)14.6. Memory Mode Selection (100)14.6.1. Internal XRAM Only (100)14.6.2. Split Mode without Bank Select (100)14.6.3. Split Mode with Bank Select (101)14.6.4. External Only (101)14.7. Timing (102)14.7.1. Non-multiplexed Mode (104)14.7.1.1. 16-bit MOVX: EMI0CF[4:2] = 101, 110, or 111 (104)14.7.1.2. 8-bit MOVX without Bank Select: EMI0CF[4:2] = 101 or 111 (105)14.7.1.3. 8-bit MOVX with Bank Select: EMI0CF[4:2] = 110 (106)14.7.2. Multiplexed Mode (107)14.7.2.1. 16-bit MOVX: EMI0CF[4:2] = 001, 010, or 011 (107)14.7.2.2. 8-bit MOVX without Bank Select: EMI0CF[4:2] = 001 or 011 (108)14.7.2.3. 8-bit MOVX with Bank Select: EMI0CF[4:2] = 010 (109)15. Special Function Registers (111)15.1. 13.1. SFR Paging (111)16. Interrupts (118)16.1. MCU Interrupt Sources and Vectors (119)16.1.1. Interrupt Priorities (119)16.1.2. Interrupt Latency (119)16.2. Interrupt Register Descriptions (119)16.3. INT0 and INT1 External Interrupt Sources (127)17. Reset Sources (129)17.1. Power-On Reset (130)17.2. Power-Fail Reset / VDD Monitor (131)17.3. External Reset (132)17.4. Missing Clock Detector Reset (132)17.5. Comparator0 Reset (132)17.6. PCA Watchdog Timer Reset (133)17.7. Flash Error Reset (133)17.8. Software Reset (133)17.9. USB Reset (133)18. Flash Memory (135)18.1. Programming The Flash Memory (135)18.1.1. Flash Lock and Key Functions (135)C8051F380/1/2/3/4/5/6/7/C18.1.2. Flash Erase Procedure (135)18.1.3. Flash Write Procedure (136)18.2. Non-Volatile Data Storage (137)18.3. Security Options (137)19. Oscillators and Clock Selection (142)19.1. System Clock Selection (143)19.2. USB Clock Selection (143)19.3. Programmable Internal High-Frequency (H-F) Oscillator (145)19.3.1. Internal Oscillator Suspend Mode (145)19.4. Clock Multiplier (147)19.5. Programmable Internal Low-Frequency (L-F) Oscillator (148)19.5.1. Calibrating the Internal L-F Oscillator (148)19.6. External Oscillator Drive Circuit (149)19.6.1. External Crystal Mode (149)19.6.2. External RC Example (151)19.6.3. External Capacitor Example (151)20. Port Input/Output (153)20.1. Priority Crossbar Decoder (154)20.2. Port I/O Initialization (158)20.3. General Purpose Port I/O (161)21. Universal Serial Bus Controller (USB0) (172)21.1. Endpoint Addressing (172)21.2. USB Transceiver (173)21.3. USB Register Access (175)21.4. USB Clock Configuration (179)21.5. FIFO Management (181)21.5.1. FIFO Split Mode (181)21.5.2. FIFO Double Buffering (182)21.5.1. FIFO Access (182)21.6. Function Addressing (183)21.7. Function Configuration and Control (183)21.8. Interrupts (186)21.9. The Serial Interface Engine (193)21.10. Endpoint0 (193)21.10.1. Endpoint0 SETUP Transactions (193)21.10.2. Endpoint0 IN Transactions (193)21.10.3. Endpoint0 OUT Transactions (194)21.11. Configuring Endpoints1-3 (196)21.12. Controlling Endpoints1-3 IN (197)21.12.1. Endpoints1-3 IN Interrupt or Bulk Mode (197)21.12.2. Endpoints1-3 IN Isochronous Mode (198)21.13. Controlling Endpoints1-3 OUT (201)21.13.1. Endpoints1-3 OUT Interrupt or Bulk Mode (201)21.13.2. Endpoints1-3 OUT Isochronous Mode (201)22. SMBus0 and SMBus1 (I2C Compatible) (205)C8051F380/1/2/3/4/5/6/7/C22.1. Supporting Documents (206)22.2. SMBus Configuration (206)22.3. SMBus Operation (206)22.3.1. Transmitter Vs. Receiver (207)22.3.2. Arbitration (207)22.3.3. Clock Low Extension (207)22.3.4. SCL Low Timeout (207)22.3.5. SCL High (SMBus Free) Timeout (208)22.4. Using the SMBus (208)22.4.1. SMBus Configuration Register (208)22.4.2. SMBus Timing Control Register (210)22.4.3. SMBnCN Control Register (214)22.4.3.1. Software ACK Generation (214)22.4.3.2. Hardware ACK Generation (214)22.4.4. Hardware Slave Address Recognition (217)22.4.5. Data Register (221)22.5. SMBus Transfer Modes (223)22.5.1. Write Sequence (Master) (223)22.5.2. Read Sequence (Master) (224)22.5.3. Write Sequence (Slave) (225)22.5.4. Read Sequence (Slave) (226)22.6. SMBus Status Decoding (226)23. UART0 (232)23.1. Enhanced Baud Rate Generation (233)23.2. Operational Modes (234)23.2.1. 8-Bit UART (234)23.2.2. 9-Bit UART (235)23.3. Multiprocessor Communications (236)24. UART1 (240)24.1. Baud Rate Generator (241)24.2. Data Format (242)24.3. Configuration and Operation (243)24.3.1. Data Transmission (243)24.3.2. Data Reception (243)24.3.3. Multiprocessor Communications (244)25. Enhanced Serial Peripheral Interface (SPI0) (250)25.1. Signal Descriptions (251)25.1.1. Master Out, Slave In (MOSI) (251)25.1.2. Master In, Slave Out (MISO) (251)25.1.3. Serial Clock (SCK) (251)25.1.4. Slave Select (NSS) (251)25.2. SPI0 Master Mode Operation (251)25.3. SPI0 Slave Mode Operation (253)25.4. SPI0 Interrupt Sources (254)25.5. Serial Clock Phase and Polarity (254)25.6. SPI Special Function Registers (256)26. Timers (263)26.1. Timer 0 and Timer 1 (266)26.1.1. Mode 0: 13-bit Counter/Timer (266)26.1.2. Mode 1: 16-bit Counter/Timer (267)26.1.3. Mode 2: 8-bit Counter/Timer with Auto-Reload (267)26.1.4. Mode 3: Two 8-bit Counter/Timers (Timer 0 Only) (268)26.2. Timer 2 (274)26.2.1. 16-bit Timer with Auto-Reload (274)26.2.2. 8-bit Timers with Auto-Reload (275)26.2.3. Timer 2 Capture Modes: USB Start-of-Frame or LFO Falling Edge (275)26.3. Timer 3 (281)26.3.1. 16-bit Timer with Auto-Reload (281)26.3.2. 8-bit Timers with Auto-Reload (282)26.3.3. Timer 3 Capture Modes: USB Start-of-Frame or LFO Falling Edge (282)26.4. Timer 4 (288)26.4.1. 16-bit Timer with Auto-Reload (288)26.4.2. 8-bit Timers with Auto-Reload (289)26.5. Timer 5 (293)26.5.1. 16-bit Timer with Auto-Reload (293)26.5.2. 8-bit Timers with Auto-Reload (294)27. Programmable Counter Array (298)27.1. PCA Counter/Timer (299)27.2. PCA0 Interrupt Sources (300)27.3. Capture/Compare Modules (301)27.3.1. Edge-triggered Capture Mode (302)27.3.2. Software Timer (Compare) Mode (303)27.3.3. High-Speed Output Mode (304)27.3.4. Frequency Output Mode (305)27.3.5. 8-bit Pulse Width Modulator Mode (306)27.3.6. 16-Bit Pulse Width Modulator Mode (307)27.4. Watchdog Timer Mode (308)27.4.1. Watchdog Timer Operation (308)27.4.2. Watchdog Timer Usage (309)27.5. Register Descriptions for PCA0 (311)28. C2 Interface (316)28.1. C2 Interface Registers (316)28.2. C2 Pin Sharing (319)Document Change List (320)Contact Information (321)List of FiguresFigure1.1. C8051F380/2/4/6 Block Diagram (18)Figure1.2. C8051F381/3/5/7/C Block Diagram (19)Figure3.1. TQFP-48 Pinout Diagram (Top View) (25)Figure3.2. TQFP-48 Package Diagram (26)Figure3.3. TQFP-48 Recommended PCB Land Pattern (27)Figure3.4. LQFP-32 Pinout Diagram (Top View) (28)Figure3.5. LQFP-32 Package Diagram (29)Figure3.6. LQFP-32 Recommended PCB Land Pattern (30)Figure3.7. QFN-32 Pinout Diagram (Top View) (31)Figure3.8. QFN-32 Package Drawing (32)Figure3.9. QFN-32 Recommended PCB Land Pattern (33)Figure4.1. Connection Diagram with Voltage Regulator Used and No USB (34)Figure4.2. Connection Diagram with Voltage Regulator Not Used and No USB (34)Figure4.3. Connection Diagram with Voltage Regulator Used and USB Connected (Bus-Powered) (35)Figure4.4. Connection Diagram with Voltage Regulator Used and USB Connected (Self-Powered) (35)Figure4.5. Connection Diagram for USB Pins (36)Figure4.6. Connection Diagram for Internal Voltage Reference (36)Figure6.1. ADC0 Functional Block Diagram (46)Figure6.2. Typical Temperature Sensor Transfer Function (48)Figure6.3. Temperature Sensor Error with 1-Point Calibration (49)Figure6.4. 10-Bit ADC Track and Conversion Example Timing (51)Figure6.5. ADC0 Equivalent Input Circuits (52)Figure6.6. ADC Window Compare Example: Right-Justified Data (58)Figure6.7. ADC Window Compare Example: Left-Justified Data (58)Figure7.1. Voltage Reference Functional Block Diagram (62)Figure8.1. Comparator0 Functional Block Diagram (64)Figure8.2. Comparator1 Functional Block Diagram (65)Figure8.3. Comparator Hysteresis Plot (66)Figure8.4. Comparator Input Multiplexer Block Diagram (71)Figure11.1. CIP-51 Block Diagram (79)Figure13.1. On-Chip Memory Map for 64kB Devices (C8051F380/1/4/5) (89)Figure13.2. On-Chip Memory Map for 32kB Devices (C8051F382/3/6/7) (90)Figure13.3. On-Chip Memory Map for 16kB Devices (C8051F38C) (91)Figure14.1. USB FIFO Space and XRAM Memory Map with USBFAE set to ‘1’ (94)Figure14.2. Multiplexed Configuration Example (98)Figure14.3. Non-multiplexed Configuration Example (99)Figure14.4. EMIF Operating Modes (100)Figure14.5. Non-Multiplexed 16-bit MOVX Timing (104)Figure14.6. Non-multiplexed 8-bit MOVX without Bank Select Timing (105)Figure14.7. Non-multiplexed 8-bit MOVX with Bank Select Timing (106)Figure14.8. Multiplexed 16-bit MOVX Timing (107)C8051F380/1/2/3/4/5/6/7/CFigure14.9. Multiplexed 8-bit MOVX without Bank Select Timing (108)Figure14.10. Multiplexed 8-bit MOVX with Bank Select Timing (109)Figure17.1. Reset Sources (129)Figure17.2. Power-On and VDD Monitor Reset Timing (130)Figure18.1. Flash Program Memory Map and Security Byte (137)Figure19.1. Oscillator Options (142)Figure19.2. External Crystal Example (150)Figure20.1. Port I/O Functional Block Diagram (Port 0 through Port 3) (153)Figure20.2. Port I/O Cell Block Diagram (154)Figure20.3. Peripheral Availability on Port I/O Pins (155)Figure20.4. Crossbar Priority Decoder in Example Configuration(No Pins Skipped) (156)Figure20.5. Crossbar Priority Decoder in Example Configuration (3 Pins Skipped) (157)Figure21.1. USB0 Block Diagram (172)Figure21.2. USB0 Register Access Scheme (175)Figure21.3. USB FIFO Allocation (181)Figure22.1. SMBus Block Diagram (205)Figure22.2. Typical SMBus Configuration (206)Figure22.3. SMBus Transaction (207)Figure22.4. Typical SMBus SCL Generation (209)Figure22.5. Typical Master Write Sequence (223)Figure22.6. Typical Master Read Sequence (224)Figure22.7. Typical Slave Write Sequence (225)Figure22.8. Typical Slave Read Sequence (226)Figure23.1. UART0 Block Diagram (232)Figure23.2. UART0 Baud Rate Logic (233)Figure23.3. UART Interconnect Diagram (234)Figure23.4. 8-Bit UART Timing Diagram (234)Figure23.5. 9-Bit UART Timing Diagram (235)Figure23.6. UART Multi-Processor Mode Interconnect Diagram (236)Figure24.1. UART1 Block Diagram (240)Figure24.2. UART1 Timing Without Parity or Extra Bit (242)Figure24.3. UART1 Timing With Parity (242)Figure24.4. UART1 Timing With Extra Bit (242)Figure24.5. Typical UART Interconnect Diagram (243)Figure24.6. UART Multi-Processor Mode Interconnect Diagram (244)Figure25.1. SPI Block Diagram (250)Figure25.2. Multiple-Master Mode Connection Diagram (252)Figure25.3. 3-Wire Single Master and 3-Wire Single Slave Mode Connection Diagram (252)Figure25.4. 4-Wire Single Master Mode and 4-Wire Slave Mode Connection Diagram (253)Figure25.5. Master Mode Data/Clock Timing (255)Figure25.6. Slave Mode Data/Clock Timing (CKPHA = 0) (255)C8051F380/1/2/3/4/5/6/7/C Figure25.7. Slave Mode Data/Clock Timing (CKPHA = 1) (256)Figure25.8. SPI Master Timing (CKPHA = 0) (260)Figure25.9. SPI Master Timing (CKPHA = 1) (260)Figure25.10. SPI Slave Timing (CKPHA = 0) (261)Figure25.11. SPI Slave Timing (CKPHA = 1) (261)Figure26.1. T0 Mode 0 Block Diagram (267)Figure26.2. T0 Mode 2 Block Diagram (268)Figure26.3. T0 Mode 3 Block Diagram (269)Figure26.4. Timer 2 16-Bit Mode Block Diagram (274)Figure26.5. Timer 2 8-Bit Mode Block Diagram (275)Figure26.6. Timer2 Capture Mode (T2SPLIT = 0) (276)Figure26.7. Timer2 Capture Mode (T2SPLIT = 0) (277)Figure26.8. Timer 3 16-Bit Mode Block Diagram (281)Figure26.9. Timer 3 8-Bit Mode Block Diagram (282)Figure26.10. Timer3 Capture Mode (T3SPLIT = 0) (283)Figure26.11. Timer3 Capture Mode (T3SPLIT = 0) (284)Figure26.12. Timer 4 16-Bit Mode Block Diagram (288)Figure26.13. Timer 4 8-Bit Mode Block Diagram (289)Figure26.14. Timer 5 16-Bit Mode Block Diagram (293)Figure26.15. Timer 5 8-Bit Mode Block Diagram (294)Figure27.1. PCA Block Diagram (298)Figure27.2. PCA Counter/Timer Block Diagram (299)Figure27.3. PCA Interrupt Block Diagram (300)Figure27.4. PCA Capture Mode Diagram (302)Figure27.5. PCA Software Timer Mode Diagram (303)Figure27.6. PCA High-Speed Output Mode Diagram (304)Figure27.7. PCA Frequency Output Mode (305)Figure27.8. PCA 8-Bit PWM Mode Diagram (306)Figure27.9. PCA 16-Bit PWM Mode (307)Figure27.10. PCA Module 4 with Watchdog Timer Enabled (308)Figure28.1. Typical C2 Pin Sharing (319)List of TablesTable1.1. Product Selection Guide (17)Table2.1. C8051F38x Replacement Part Numbers (20)Table3.1. Pin Definitions for the C8051F380/1/2/3/4/5/6/7/C (22)Table3.2. TQFP-48 Package Dimensions (26)Table3.3. TQFP-48 PCB Land Pattern Dimensions (27)Table3.4. LQFP-32 Package Dimensions (29)Table3.5. LQFP-32 PCB Land Pattern Dimensions (30)Table3.6. QFN-32 Package Dimensions (32)Table3.7. QFN-32 PCB Land Pattern Dimensions (33)Table5.1. Absolute Maximum Ratings (37)Table5.2. Global Electrical Characteristics (38)Table5.3. Port I/O DC Electrical Characteristics (39)Table5.4. Reset Electrical Characteristics (39)Table5.5. Internal Voltage Regulator Electrical Characteristics (40)Table5.6. Flash Electrical Characteristics (40)Table5.7. Internal High-Frequency Oscillator Electrical Characteristics (41)Table5.8. Internal Low-Frequency Oscillator Electrical Characteristics (41)Table5.9. External Oscillator Electrical Characteristics (41)Table5.10. ADC0 Electrical Characteristics (42)Table5.11. Temperature Sensor Electrical Characteristics (43)Table5.12. Voltage Reference Electrical Characteristics (43)Table5.13. Comparator Electrical Characteristics (44)Table5.14. USB Transceiver Electrical Characteristics (45)Table11.1. CIP-51 Instruction Set Summary (81)Table14.1. AC Parameters for External Memory Interface (110)Table15.1. Special Function Register (SFR) Memory Map (112)Table15.2. Special Function Registers (113)Table16.1. Interrupt Summary (120)Table21.1. Endpoint Addressing Scheme (173)Table21.2. USB0 Controller Registers (178)Table21.3. FIFO Configurations (182)Table22.1. SMBus Clock Source Selection (209)Table22.2. Minimum SDA Setup and Hold Times (210)Table22.3. Sources for Hardware Changes to SMBnCN (217)Table22.4. Hardware Address Recognition Examples (EHACK = 1) (218)Table22.5. SMBus Status Decoding: Hardware ACK Disabled (EHACK = 0) (227)Table22.6. SMBus Status Decoding: Hardware ACK Enabled (EHACK = 1) (229)Table23.1. Timer Settings for Standard Baud Rates Using Internal Oscillator (238)Table24.1. Baud Rate Generator Settings for Standard Baud Rates (241)Table25.1. SPI Slave Timing Parameters (262)Table27.1. PCA Timebase Input Options (299)Table27.2. PCA0CPM Bit Settings for PCA Capture/Compare Modules (301)Table27.3. Watchdog Timer Timeout Intervals1 (310)List of RegistersSFR Definition6.1. ADC0CF: ADC0 Configuration (53)SFR Definition6.2. ADC0H: ADC0 Data Word MSB (54)SFR Definition6.3. ADC0L: ADC0 Data Word LSB (54)SFR Definition6.4. ADC0CN: ADC0 Control (55)SFR Definition6.5. ADC0GTH: ADC0 Greater-Than Data High Byte (56)SFR Definition6.6. ADC0GTL: ADC0 Greater-Than Data Low Byte (56)SFR Definition6.7. ADC0LTH: ADC0 Less-Than Data High Byte (57)SFR Definition6.8. ADC0LTL: ADC0 Less-Than Data Low Byte (57)SFR Definition6.9. AMX0P: AMUX0 Positive Channel Select (60)SFR Definition6.10. AMX0N: AMUX0 Negative Channel Select (61)SFR Definition7.1. REF0CN: Reference Control (63)SFR Definition8.1. CPT0CN: Comparator0 Control (67)SFR Definition8.2. CPT0MD: Comparator0 Mode Selection (68)SFR Definition8.3. CPT1CN: Comparator1 Control (69)SFR Definition8.4. CPT1MD: Comparator1 Mode Selection (70)SFR Definition8.5. CPT0MX: Comparator0 MUX Selection (72)SFR Definition8.6. CPT1MX: Comparator1 MUX Selection (73)SFR Definition9.1. REG01CN: Voltage Regulator Control (75)SFR Definition10.1. PCON: Power Control (78)SFR Definition11.1. DPL: Data Pointer Low Byte (85)SFR Definition11.2. DPH: Data Pointer High Byte (85)SFR Definition11.3. SP: Stack Pointer (86)SFR Definition11.4. ACC: Accumulator (86)SFR Definition11.5. B: B Register (86)SFR Definition11.6. PSW: Program Status Word (87)SFR Definition12.1. PFE0CN: Prefetch Engine Control (88)SFR Definition14.1. EMI0CN: External Memory Interface Control (96)SFR Definition14.2. EMI0CF: External Memory Interface Configuration (97)SFR Definition14.3. EMI0TC: External Memory TIming Control (103)SFR Definition15.1. SFRPAGE: SFR Page (111)SFR Definition16.1. IE: Interrupt Enable (121)SFR Definition16.2. IP: Interrupt Priority (122)SFR Definition16.3. EIE1: Extended Interrupt Enable 1 (123)SFR Definition16.4. EIP1: Extended Interrupt Priority 1 (124)SFR Definition16.5. EIE2: Extended Interrupt Enable 2 (125)SFR Definition16.6. EIP2: Extended Interrupt Priority 2 (126)SFR Definition16.7. IT01CF: INT0/INT1 ConfigurationO (128)SFR Definition17.1. VDM0CN: VDD Monitor Control (132)SFR Definition17.2. RSTSRC: Reset Source (134)SFR Definition18.1. PSCTL: Program Store R/W Control (139)SFR Definition18.2. FLKEY: Flash Lock and Key (140)SFR Definition18.3. FLSCL: Flash Scale (141)SFR Definition19.1. CLKSEL: Clock Select (144)C8051F380/1/2/3/4/5/6/7/CSFR Definition19.2. OSCICL: Internal H-F Oscillator Calibration (145)SFR Definition19.3. OSCICN: Internal H-F Oscillator Control (146)SFR Definition19.4. CLKMUL: Clock Multiplier Control (147)SFR Definition19.5. OSCLCN: Internal L-F Oscillator Control (148)SFR Definition19.6. OSCXCN: External Oscillator Control (152)SFR Definition20.1. XBR0: Port I/O Crossbar Register 0 (159)SFR Definition20.2. XBR1: Port I/O Crossbar Register 1 (160)SFR Definition20.3. XBR2: Port I/O Crossbar Register 2 (161)SFR Definition20.4. P0: Port 0 (162)SFR Definition20.5. P0MDIN: Port 0 Input Mode (162)SFR Definition20.6. P0MDOUT: Port 0 Output Mode (163)SFR Definition20.7. P0SKIP: Port 0 Skip (163)SFR Definition20.8. P1: Port 1 (164)SFR Definition20.9. P1MDIN: Port 1 Input Mode (164)SFR Definition20.10. P1MDOUT: Port 1 Output Mode (165)SFR Definition20.11. P1SKIP: Port 1 Skip (165)SFR Definition20.12. P2: Port 2 (166)SFR Definition20.13. P2MDIN: Port 2 Input Mode (166)SFR Definition20.14. P2MDOUT: Port 2 Output Mode (167)SFR Definition20.15. P2SKIP: Port 2 Skip (167)SFR Definition20.16. P3: Port 3 (168)SFR Definition20.17. P3MDIN: Port 3 Input Mode (168)SFR Definition20.18. P3MDOUT: Port 3 Output Mode (169)SFR Definition20.19. P3SKIP: Port 3 Skip (169)SFR Definition20.20. P4: Port 4 (170)SFR Definition20.21. P4MDIN: Port 4 Input Mode (170)SFR Definition20.22. P4MDOUT: Port 4 Output Mode (171)SFR Definition21.1. USB0XCN: USB0 Transceiver Control (174)SFR Definition21.2. USB0ADR: USB0 Indirect Address (176)SFR Definition21.3. USB0DAT: USB0 Data (177)USB Register Definition21.4. INDEX: USB0 Endpoint Index (179)USB Register Definition21.5. CLKREC: Clock Recovery Control (180)USB Register Definition21.6. FIFOn: USB0 Endpoint FIFO Access (182)USB Register Definition21.7. FADDR: USB0 Function Address (183)USB Register Definition21.8. POWER: USB0 Power (185)USB Register Definition21.9. FRAMEL: USB0 Frame Number Low (186)USB Register Definition21.10. FRAMEH: USB0 Frame Number High (186)USB Register Definition21.11. IN1INT: USB0 IN Endpoint Interrupt (187)USB Register Definition21.12. OUT1INT: USB0 OUT Endpoint Interrupt (188)USB Register Definition21.13. CMINT: USB0 Common Interrupt (189)USB Register Definition21.14. IN1IE: USB0 IN Endpoint Interrupt Enable (190)USB Register Definition21.15. OUT1IE: USB0 OUT Endpoint Interrupt Enable (191)USB Register Definition21.16. CMIE: USB0 Common Interrupt Enable (192)USB Register Definition21.17. E0CSR: USB0 Endpoint0 Control (195)USB Register Definition21.18. E0CNT: USB0 Endpoint0 Data Count (196)C8051F380/1/2/3/4/5/6/7/C USB Register Definition21.19. EENABLE: USB0 Endpoint Enable (197)USB Register Definition21.20. EINCSRL: USB0 IN Endpoint Control Low (199)USB Register Definition21.21. EINCSRH: USB0 IN Endpoint Control High (200)USB Register Definition21.22. EOUTCSRL: USB0 OUT Endpoint Control Low Byte 202 USB Register Definition21.23. EOUTCSRH: USB0 OUT Endpoint Control High Byte (203)USB Register Definition21.24. EOUTCNTL: USB0 OUT Endpoint Count Low (203)USB Register Definition21.25. EOUTCNTH: USB0 OUT Endpoint Count High (204)SFR Definition22.1. SMB0CF: SMBus Clock/Configuration (211)SFR Definition22.2. SMB1CF: SMBus Clock/Configuration (212)SFR Definition22.3. SMBTC: SMBus Timing Control (213)SFR Definition22.4. SMB0CN: SMBus Control (215)SFR Definition22.5. SMB1CN: SMBus Control (216)SFR Definition22.6. SMB0ADR: SMBus0 Slave Address (218)SFR Definition22.7. SMB0ADM: SMBus0 Slave Address Mask (219)SFR Definition22.8. SMB1ADR: SMBus1 Slave Address (219)SFR Definition22.9. SMB1ADM: SMBus1 Slave Address Mask (220)SFR Definition22.10. SMB0DAT: SMBus Data (221)SFR Definition22.11. SMB1DAT: SMBus Data (222)SFR Definition23.1. SCON0: Serial Port 0 Control (237)SFR Definition23.2. SBUF0: Serial (UART0) Port Data Buffer (238)SFR Definition24.1. SCON1: UART1 Control (245)SFR Definition24.2. SMOD1: UART1 Mode (246)SFR Definition24.3. SBUF1: UART1 Data Buffer (247)SFR Definition24.4. SBCON1: UART1 Baud Rate Generator Control (248)SFR Definition24.5. SBRLH1: UART1 Baud Rate Generator High Byte (248)SFR Definition24.6. SBRLL1: UART1 Baud Rate Generator Low Byte (249)SFR Definition25.1. SPI0CFG: SPI0 Configuration (257)SFR Definition25.2. SPI0CN: SPI0 Control (258)SFR Definition25.3. SPI0CKR: SPI0 Clock Rate (259)SFR Definition25.4. SPI0DAT: SPI0 Data (259)SFR Definition26.1. CKCON: Clock Control (264)SFR Definition26.2. CKCON1: Clock Control 1 (265)SFR Definition26.3. TCON: Timer Control (270)SFR Definition26.4. TMOD: Timer Mode (271)SFR Definition26.5. TL0: Timer 0 Low Byte (272)SFR Definition26.6. TL1: Timer 1 Low Byte (272)SFR Definition26.7. TH0: Timer 0 High Byte (273)SFR Definition26.8. TH1: Timer 1 High Byte (273)SFR Definition26.9. TMR2CN: Timer 2 Control (278)SFR Definition26.10. TMR2RLL: Timer 2 Reload Register Low Byte (279)SFR Definition26.11. TMR2RLH: Timer 2 Reload Register High Byte (279)SFR Definition26.12. TMR2L: Timer 2 Low Byte (279)SFR Definition26.13. TMR2H Timer 2 High Byte (280)SFR Definition26.14. TMR3CN: Timer 3 Control (285)C8051F380/1/2/3/4/5/6/7/CSFR Definition26.15. TMR3RLL: Timer 3 Reload Register Low Byte (286)SFR Definition26.16. TMR3RLH: Timer 3 Reload Register High Byte (286)SFR Definition26.17. TMR3L: Timer 3 Low Byte (286)SFR Definition26.18. TMR3H Timer 3 High Byte (287)SFR Definition26.19. TMR4CN: Timer 4 Control (290)SFR Definition26.20. TMR4RLL: Timer 4 Reload Register Low Byte (291)SFR Definition26.21. TMR4RLH: Timer 4 Reload Register High Byte (291)SFR Definition26.22. TMR4L: Timer 4 Low Byte (291)SFR Definition26.23. TMR4H Timer 4 High Byte (292)SFR Definition26.24. TMR5CN: Timer 5 Control (295)SFR Definition26.25. TMR5RLL: Timer 5 Reload Register Low Byte (296)SFR Definition26.26. TMR5RLH: Timer 5 Reload Register High Byte (296)SFR Definition26.27. TMR5L: Timer 5 Low Byte (296)SFR Definition26.28. TMR5H Timer 5 High Byte (297)SFR Definition27.1. PCA0CN: PCA Control (311)SFR Definition27.2. PCA0MD: PCA Mode (312)SFR Definition27.3. PCA0CPMn: PCA Capture/Compare Mode (313)SFR Definition27.4. PCA0L: PCA Counter/Timer Low Byte (314)SFR Definition27.5. PCA0H: PCA Counter/Timer High Byte (314)SFR Definition27.6. PCA0CPLn: PCA Capture Module Low Byte (315)SFR Definition27.7. PCA0CPHn: PCA Capture Module High Byte (315)C2 Register Definition28.1. C2ADD: C2 Address (316)C2 Register Definition28.2. DEVICEID: C2 Device ID (317)C2 Register Definition28.3. REVID: C2 Revision ID (317)C2 Register Definition28.4. FPCTL: C2 Flash Programming Control (318)C2 Register Definition28.5. FPDAT: C2 Flash Programming Data (318)。

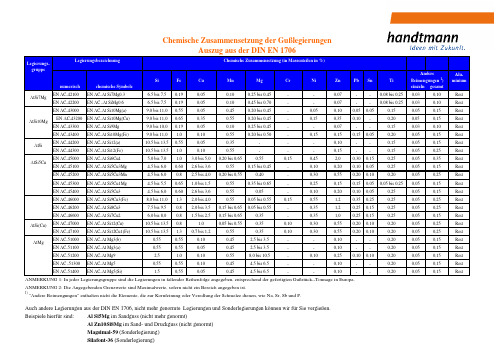

欧州铝合金标准

Chemische Zusammensetzung der Gußlegierungen1) "Andere Beimengungen" enthalten nicht die Elemente, die zur Kornfeinung oder Veredlung der Schmelze dienen, wie Na, Sr, Sb und P.Auch andere Legierungen aus der DIN EN 1706, nicht mehr genormte Legierungen und Sonderlegierungen können wir für Sie vergießen. Beispiele hierfür sind:Al Si5Mg im Sandguss (nicht mehr genormt)Al Zn10Si8Mg im Sand- und Druckguss (nicht genormt)Magsimal-59 (Sonderlegierung)Silafont-36 (Sonderlegierung)Anmerkung:Getrennt gegossene Probestäbe haben eine wertvolle Funktion zur Überprüfung der Qualität und Schmelze. Jedoch können die Werte, die an den Gussstücken erzielt werden von den in den Tabellen aufgeführten Mindestwerten abweichen, aufgrund von Veränderungen im Gefüge, die durch unterschiedliche Querschnittsdicke und Fehlerfreiheit entstehen. Bei den Streckgrenzen und der Zugfestigkeit dürfen die an den Gussstücken erzielen Werten über den in den Tabellen festgelegten Werten oder darunter liegen, aber nicht unter 70 % der festgelegten Werte. Bei der Dehnung dürfen die an den Gussstücken erzielten Werte über den in den Tabellen festgelegten Werten oder an bestimmten Punkten bis zu 50 % unter diesen Werten liegenMechanische Eigenschaften von Sandgußlegierungenfür getrennt gegossene ProbestäbeMechanische Eigenschaften von Kokillengußlegierungenfür getrennt gegossene ProbestäbeMechanische Eigenschaften für Druckgusslegierungennur zur InformationMindestwerte die von getrennt gegossenen Probestäben mit einem Querschnitt von 20,0mm² und einer Mindestdicke von 2,0mm erwartet werden dürfen.Die Werte die an Proben von aus Gussstücken entnommenen Probestücken ermittelt werden, können von den in den Tabellen festgelegten Mindestwerten abweichen, da sich aufgrund unterschiedlicher Gefüge und eine unterschiedliche Gussstückqualität (Fehlerfreiheit) ergeben können.Die mechanischen Eigenschaften von Druckgussstücken, die an aus getrennt gegossenen Probestücken hergestellten Proben ermittelt werden, haben eine starke Abhängigkeit von den Druckgießparametern. Die in der Tabelle angegebenen Eigenschaften sind deshalb nur Anhaltswerte.Chemische Zusammensetzung von Magnesiumlegierungen für GussstückeAnmerkung 1: Die in dieser Tabelle angegebenen Werte sind nur Anhaltswerte.Anmerkung 2: Die angegebenen Werte gelten für getrennt gegossene Proben mit einer Querschnittsfläche von 20 mm³und einer Mindestwanddicke von 2 mm.Anmerkung 3: N/mm² entspricht 1 MpaMechanische Eigenschaften von Druckguss-Magnesiumlegierungenfür getrennt gegossene Probestäbe。

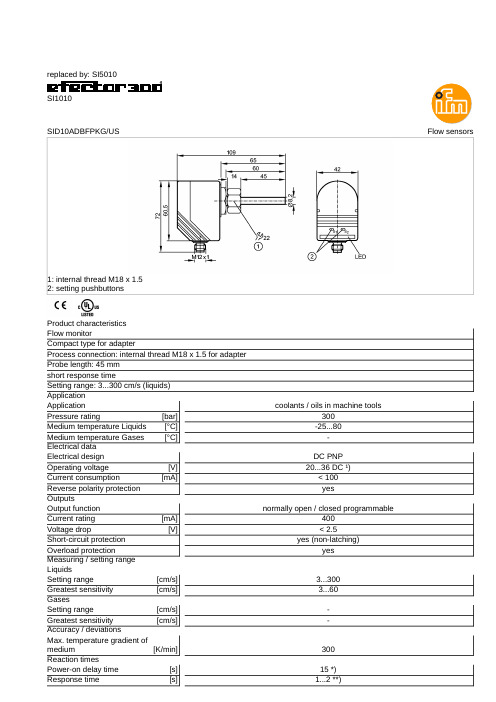

流量监测仪产品说明书

replaced by:SI5010SI1010Flow sensorsSID10ADBFPKG/US1:internal thread M18x 1.52:setting pushbuttonsProduct characteristics Flow monitorCompact type for adapterProcess connection:internal thread M18x 1.5for adapter Probe length:45mm short response timeSetting range:3...300cm/s (liquids)Application coolants /oils in machine toolsApplication 300Pressure rating [bar]-25 (80)Medium temperature Liquids [°C]-Medium temperature Gases [°C]Electrical data DC PNP Electrical design 20...36DC ¹)Operating voltage [V]<100Current consumption [mA]yesReverse polarity protection Outputsnormally open /closed programmableOutput function 400Current rating [mA]<2.5Voltage drop [V]yes (non-latching)Short-circuit protection yesOverload protectionMeasuring /setting range Liquids3...300Setting range [cm/s] 3...60Greatest sensitivity [cm/s]Gases-Setting range [cm/s]-Greatest sensitivity [cm/s]Accuracy /deviations300Max.temperature gradient of medium [K/min]Reaction times15*)Power-on delay time [s] 1...2**)Response time [s]Software /programmingpushbuttons Adjustment of the switch point Environment-25...80Ambient temperature [°C]IP 67ProtectionTests /approvals Shock resistance 50g (11ms)DIN IEC 68-2-27:Vibration resistance 20g (55...2000Hz)DIN EN 60068-2-6258MTTF [Years]Mechanical data internal thread M18x 1.5for adapterProcess connection stainless steel 316L /1.4404;O-ring:FKM 8x 1.5gr 80°Shore AMaterials (wetted parts)PBT-GF 20Housing materials 45Probe length L [mm]0.292Weight [kg]Displays /operating elements 10LEDs,three-colourFunction display LED Electrical connection M12connectorConnectionWiringP =programming wire (for remote adjustment)Remarks Remarks¹)to EN50178,SELV,PELV *)optically indicated**)for a temperature gradient of 1K/min1Pack quantity [piece]ifm efector,inc.•1100Atwater Drive •Malvern •PA 19355—We reserve the right to make technical alterations without prior notice.—US —SI1010—10.07.2013replaced by:SI5010SI1010-Flow monitor -eclass:27273101/27-27-31-01。

产品牌号及标准

宝钢【产品牌号及标准】[可供规格范围]【通常可供规格范围】【宝钢企标与其它常用标准对照】【产品分类】[制造范围]注:1.一次轧制钢板的调质度,本来不能只以单一的力学性能来表示,但作为最有用的力学性能指标,采用洛氏T硬度。

2.用于二片罐的DI材只使用与钢类D,按协议卷状供货;DI材的牌号为:D T—2.5CA DI,DT—3.4CA DI,D T——4CA DI。

***MR:残留微量成分较少,具有优秀的耐蚀性,用于容器与其他普遍的一般用途,L:Cu、Cr、Ni、Mo及其他的残留微量成分特别少,用于具有优秀耐蚀性的容器。

D:为AL镇静钢,用于深拉伸加工及易发生滑移线的加工等用途。

根据镀锡板分类【制造范围】标准供货规格范围【产品牌号及标准】【按用途、涂料、结构分类及代号】【通常可供货规格范围】【国内外标准对照】产品用途中、低牌号的无取向电工钢经冲片后、经焊接或铆接制成各种铁芯,宝钢此次引进的电工钢产品可广泛应用于中小型工业用电机、家用电器中的压缩机、电力用变频器、焊机用变压器和稳流器等电器设备的制造,同时宝钢引进了半有机和无机涂层,适用于不同的场合,产品特点a.尺寸精度高,表面质量好,叠装系数高。

b.表面涂有绝缘薄膜,具有良好的绝缘性能和加工性能。

c.铁损低、磁感高。

铁损;在给定频率f,给定磁感应强度Bm下,单位质量铁芯试样中消耗的功率。

磁感应强度峰值:铁芯试样状态、在标定频率下,当交流磁场的峰值达到某一标志定值时,铁芯试样磁感的峰值。

【可供规格】mm【品牌号及标准】[可供规格范围]【通常可供规格范围】【产品牌号及标准】[可供规格范围及用途举例][宝钢企业与其它常用标准对照]【宝刚企业与其它常用标准对照】【可供规格范围】【产品牌号及标准】[可供规格范围]【通常可供规格范围】:表面处理记号与牌号可任意组合,如SECC—P,SECD—N,SECE—0等【产品牌号及标准】[产品的种类及代号][镀层种类及可供范围][推荐的标准镀层重量][表面处理种类及特点]【产品的种类及代号】【镀层种类及可供范围】【镀锌层重量】【通常可供规格范围】【产品牌号及标准】[表面处理][表面结构][镀层种类][镀层重量][可供改写范围][宝钢企业牌号与引【镀层种类及可供范围】【推荐的标准镀层重量】【。

2SC系列三极管参数

2SC系列三极管参数2SC1000 SI-N 55V 0.1A 0.2W 80MHz2SC1008 SI-N 80V 0.7A 0.8W 75MHz2SC1012A SI-N 250V 60mA 0.75W >80MHz2SC1014 SI-N 50V 1.5A 7W2SC1017 SI-N 75V 1A 60mW 120MHz2SC1030 SI-N 150V 6A 50W | 2SC1046 SI-N 1000V 3A 25W2SC1047 SI-N 30V 20mA 0.4W 650MHz | 2SC1050 SI-N 300V 1A 40W2SC1051 SI-N 150V 7A 60W 8MHz | 2SC1061 SI-N 50V 3A 25W 8MHz=H1062SC1070 SI-N 30V 20mA 900MHz | 2SC1080 SI-N 110V 12A 100W 4MHz2SC109 SI-N 50V 0.6A 0.6W | 2SC1096 SI-N 40V 3A 10W 60MHz2SC1106 SI-N 350V 2A 80W | 2SC1114 SI-N 300V 4A 100W 10MHz2SC1115 SI-N 140V 10A 100W 10MHz | 2SC1116 SI-N 180V 10A 100W 10MHz2SC1161 SI-P 160V 12A 120W | 2SC1162 SI-N 35V 1.5A 10W 180MHz2SC1172 SI-N 1500V 5A 50W | 2SC1195 SI-N 200V 2.5A 100W2SC1213C SI-N 50V 0.5A 0.4W UNI | 2SC1214 SI-N 50V 0.5A 0.6W 50MHz2SC1215 SI-N 30V 50mA 0.4W 1.2GHZ | 2SC1216 SI-N 40V 0.2A 0.3W <20/402SC1226 SI-N 40/50V 2A 10W 150MHz |2SC1238 SI-N 35V 0.15A 5W 1.7GHz2SC1247A SI-N 50V 0.5A 0.4W 60MHz | 2SC1308 SI-N 1500V 7A 50W2SC1312 SI-N 35V 0.1A 0.15W 100MHz | 2SC1318 SI-N 60V 0.5A 0.6W 200MHz2SC1343 SI-N 150V 10A 100W 14MHz | 2SC1345 SI-N 55V 0.1A 0.1W 230MHz2SC1359 SI-N 30V 30mA 0.4W 250MHz | 2SC1360 SI-N 50V 0.05A 1W >300MHz2SC1362 SI-N 50V 0.2A 0.25W 140MHz | 2SC1368 SI-N 25V 1.5A 8W 180MHz2SC1382 SI-N 80V 0.75A 5W 100MHz | 2SC1384 SI-N 60V 1A 1W 200MHz2SC1393 SI-N 30V 20mA 250 mW 700MHz | 2SC1398 SI-N 70V 2A 15W2SC1413A SI-N 1200V 5A 50W | 2SC1419 SI-N 50V 2A 20W 5MHz2SC1426 SI-N 35V 0.2A 2.7GHz | 2SC1431 SI-N 110V 2A 23W 80MHz2SC1432 N-DARL 30V 0.3A 0.3W B=40 | 2SC1439 SI-N 150V 50mA 0.5W 130MHz2SC1445 SI-N 100V 6A 40W 10MHz | 2SC1446 SI-N 300V 0.1A 10W 55MHz2SC1447 SI-N 300V 0.15A 20W 80MHz | 2SC1448 SI-N 150V 1.5A 25W 3MHz2SC1449 SI-N 40V 2A 5W 60MHz | 2SC1450 SI-N 150V 0.4A 20W2SC1454 SI-N 300V 4A 50W 10MHz | 2SC1474-4 SI-N 20V 2A 0.75W 80MHz2SC1501 SI-N 300V 0.1A 10W 55MHz | 2SC1505 SI-N 300V 0.2A 15W2SC1507 SI-N 300V 0.2A 15W 80MHz | 2SC1509 SI-N 80V 0.5A 1W 120MHz2SC1515 SI-N 200V 0.05A 0.2W 110MHz | 2SC1520 SI-N 300V 0.2A 12,5W2SC1545 N-DARL 40V 0.3A 0.3W B=1K | 2SC1567 SI-N 100V 0.5A 5W 120MHz2SC1570 SI-N 55V 0.1A 0.2W 100MHz | 2SC1571 SI-N 40V 0.1A 0.2W 100MHz2SC1573 SI-N 200V 0.1A 1W 80MHz | 2SC1577 SI-N 500V 8A 80W 7MHz2SC1583 SI-N 50V 0.1A 0.4W 100MHz | 2SC1619 SI-N 100V 6A 50W 10MHz2SC1623 SI-N 60V 0.1A 0.2W 250MHz | 2SC1624 SI-N 120V 1A 15W 30MHz2SC1627 SI-N 80V 0.4A 0.8W 100MHz | 2SC1674 SI-N 30V .02A 600MC RF/IF2SC1675 SI-N 50V .03A 0.25W | 2SC1678 SI-N 65V 3A 3W2SC1685 SI-N 60V 0.1A 150MC UNI | 2SC1688 SI-N 50V 30mA 0.4W 550MHz2SC1708A SI-N 120V 50mA 0.2W 150MHz | 2SC1729 SI-N 35V 3.5A 16W 500MHz2SC1730 SI-N 30V 0.05A 1.1GHz UHF | 2SC1740 SI-N 40V 100mA 0.3W2SC1741 SI-N 40V 0.5A 0.3W 250MHz | 2SC1756 SI-N 300V 0.2A >50MHz2SC1760 SI-N 100V 1A 7.9W 80MHz |2SC1775A SI-N 120V 0.05A 0.2W UNI2SC1781 SI-N 50V 0.5A 0.35W | 2SC1815 SI-N 50V 0.15A 0.4W 80MHz2SC1815BL SI-N 60V 0.15A 0.4W B>350 | 2SC1815GR SI-N 60V 0.15A 0.4W B>2002SC1815Y SI-N 60V 0.15A 0.4W B>120 | 2SC1827 SI-N 100V 4A 30W 10MHz2SC1832 N-DARL 500V 15A 150W B>10 | 2SC1841 SI-N 120V 0.05A 0.5W2SC1844 SI-N 60V 0.1A 0.5W 100MHz | 2SC1845 SI-N 120V 0.05A 0.5W2SC1846 SI-N 120V 0.05A 0.5W | 2SC1847 SI-N 50V 1.5A 1.2W2SC1855 SI-N 20V 20mA 0.25W 550MHz | 2SC1871 SI-N 450V 15A 150W <1/3us2SC1879 N-DARL+D 120V 2A 0.8W B>1 | 2SC1890 SI-N 90V 0.05A 0.3W 200MHz2SC1895 SI-N 1500V 6A 50W 2MHz | 2SC1906 SI-N 19V 0.05A 0.3W2SC1907 SI-N 30V 0.05A 1100MHz | 2SC1913 SI-N 150V 1A 15W 120MHz2SC1914 SI-N 90V 50mA 0.2W 150MHz | 2SC1921 SI-N 250V 0.05A 0.6W2SC1922 SI-N 1500V 2.5A 50W | 2SC1923 SI-N 30V 20mA 10mW 550MHz2SC1929 SI-N 300V 0.4A 25W 80MHz | 2SC1941 SI-N 160V 50mA 0.8W2SC1944 SI-N 80V 6A PQ=16W | 2SC1945 SI-N 80V 6A 20W2SC1946A SI-N 35V 7A 50W |2SC1947 SI-N 35V 1A 4W/175MHz2SC1953 SI-N 150V 0.05A 1.2W 70MHz |2SC1957 SI-N 40V 1A 1.8W/27MHz2SC1959 SI-N 30V 0.5A 0.5W 200MHz |2SC1967 SI-N 35V 2A 8W 470MHz2SC1968 SI-N 35V 5A 3W 470MHz |2SC1969 SI-N 60V 6A 20W2SC1970 SI-N 40V 0.6A 5W |2SC1971 SI-N 35V 2A 12.5W2SC1972 SI-N 35V 3.5A 25W |2SC1975 SI-N 120V 2A 3.8W 50MHz2SC1980 SI-N 120V 20mA 0.25W 200MHz |2SC1984 SI-N 100V 3A 30W B=7002SC1985 SI-N 80V 6A 40W 10MHz |2SC2023 SI-N 300V 2A 40W 10MHz2SC2026 SI-N 30V 0.05A 0.25W |2SC2027 SI-N 1500/800V 5A 50W2SC2036 SI-N 80V 1A PQ=1..4W | 2SC2053 SI-N 40V 0.3A 0.6W 500MHz2SC2055 SI-N 18V 0,3A 0,5W | 2SC2058 SI-N 40V 0.05A 0.25W2SC2060 SI-N 40V 0.7A 0.75W 150MHz | 2SC2061 SI-N 80V 1A 0.75W 120MHz2SC2068 SI-N 300V 0.05A 95MHz | 2SC2073 SI-N 150V 1.5A 25W 4MHz2SC2078 SI-N 80V 3A 10W 150MHz | 2SC2086 SI-N 75V 1A0.45W/27MHz2SC2092 SI-N 75V 3A 5W 27MHz | 2SC2094 SI-N 40V 3.5APQ>15W 175MHz2SC2097 SI-N 50V 15A PQ=85W | 2SC2120 SI-N 30V 0.8A 0.6W 120MHz2SC2122 SI-N 800V 10A 50W | 2SC2166 SI-N 75V 4A 12.5W RFPOWER2SC2168 SI-N 200V 2A 30W 10MHz | 2SC2200 SI-N 500V 7A 40W 1US2SC2209 SI-N 50V 1.5A 10W 150MHz | 2SC2216 SI-N 45V 50mA 0.3W 300MHz2SC2228 SI-N 160V 0.05A 0.75W >50 | 2SC2229 SI-N 200V 50mA 0.8W 120MHz2SC2230 SI-N 200V 0.1A 0.8W 50MHz | 2SC2233 SI-N 200V 4A 40W 8MHz2SC2235 SI-N 120V 0.8A 0.9W 120MHz | 2SC2236 SI-N 30V 1.5A 0.9W 120MHz2SC2237 SI-N 35V 2A PQ>7.5W 175MHz | 2SC2238 SI-N 160V 1.5A 25W 100MHz2SC2240 SI-N 120V 50mA .3W 100MHz | 2SC2261 SI-N 180V 8A 80W 15MHz2SC2267 SI-N 400/360V 0.1A 0.4W | 2SC2270 SI-N 50V 5A 10W 100MHz2SC2271 SI-N 300V 0.1A 0.9W 50MHz | 2SC2275 SI-N 120V 1.5A 25W 200MHz2SC2283 SI-N 38V 0.75A 2.8W(500MHz | 2SC2287 SI-N 38V 1.5A 7.1W 175MHz2SC2295 SI-N 30V 0.03A 0.2W 250MHz | 2SC2307 SI-N 500V 12A 100W 18MHz2SC2308 SI-N 55V 0.1A 0.2W 230MHz | 2SC2310 SI-N 55V 0.1A 0.2W 230MHz2SC2312 SI-N 60V 6A 18.5W/27MHz | 2SC2314 SI-N 45V 1A 5W 2SC2320 SI-N 50V 0,2A 0,3W | 2SC2329 SI-N 38V 0.75A 2W 175MHz2SC2331 SI-N 150V 2A 15W POWER | 2SC2333 SI-N 500/400V 2A 40W2SC2334 SI-N 150V 7A 40W POWER | 2SC2335 SI-N 500V 7A 40W POWER2SC2336B SI-N 250V 1.5A 25W 95MHz | 2SC2344 SI-N 180V 1.5A 25W 120MHz2SC2347 SI-N 15V 50mA 250mW 650MHz | 2SC2362 SI-N 120V 50mA 0.4W 130MHz2SC2363 SI-N 120V 50mA 0.5W 130MHz | 2SC2365 SI-N 600V 6A 50W POWER2SC2369 SI-N 25V 70mA 0.25W 4.5GHz | 2SC2383 SI-N 160V 1A 0.9W 100MHz2SC2389 SI-N 120V 50mA 0.3W 140MHz | 2SC2407 SI-N 35V 0.15A 0.16W 500MHz2SC2412 SI-N 50V 0.1A 180MHz | 2SC2433 SI-N 120V 30A 150W 80MHz2SC2440 SI-N 450V 5A 40W | 2SC2458 SI-N 50V 0.15A 0.2W 80MHz2SC2466 SI-N 30V 0.05A 2.2GHz | 2SC2482 SI-N 300V 0.1A 0.9W 50MHz2SC2485 SI-N 100V 6A 70W 15MHz | 2SC2486 SI-N 120V 7A 80W 15MHz2SC2491 SI-N 100V 6A 40W 15MHz | 2SC2497 SI-N 70V 1.5A 5W 150MHz2SC2498 SI-N 30V 0.05A 0.3W 3.5GHz | 2SC2508 SI-N 40V 6A 50W 175MHz2SC2510 SI-N 55V 20A 250W(28MHz) | 2SC2512 SI-N 30V 50mA 900MHz TUNE2SC2516 SI-N 150V 5A 30W <0.5/2us | 2SC2517 SI-N 150V 5A 30W <0.5/2us2SC2538 SI-N 40V 0.4A 0.7W | 2SC2539 SI-N 35V 4A 17W 175MHz2SC2542 SI-N 450V 5A 40W | 2SC2547 SI-N 120V 0.1A 0.4W2SC2551 SI-N 300V 0.1A 0.4W 80MHz | 2SC2552 SI-N 500V 2A 20W 2SC2553 SI-N 500V 5A 40W 1us | 2SC2562 SI-N 60V 5A 25W 0.1us2SC2563 SI-N 120V 8A 80W 90MHz | 2SC2570A SI-N 25V 70mA 0.6W 2SC2579 SI-N 160V 8A 80W 20MHz | 2SC2581 SI-N 200V 10A 100W 2SC2590 SI-N 120V 0.5A 5W 250MHz | 2SC2592 SI-N 180V 1A 20W 250MHz2SC2603 SI-N 50V 0.2A 0.3W | 2SC2610 SI-N 300V 0.1A 0.8W 80MHz2SC2611 SI-N 300V 0.1A 0.8W 80MHz | 2SC2621E SI-N 300V 0.2A 10W >50MHz2SC2625 SI-N 450V 10A 80W | 2SC2630 SI-N 35V 14A 100W 2SC2631 SI-N 150V 50mA 0,75W 160MHz | 2SC2632 SI-N 150V 50mA 1W 160MHz2SC2634 SI-N 60V 0.1A 0.4W 200MHz | 2SC2653 SI-N 350V 0.2A 15W >50MHz2SC2654 SI-N 40V 7A 40W | 2SC2655 SI-N 50V 2A 0.9W 0.1us2SC2656 SI-N 450V 7A 80W <1.5/4.5 | 2SC2660 SI-N 200V 2A 30W 30MHz2SC2668 SI-N 30V 20mA 0.1W 550MHz | 2SC2671 SI-N 15V 80mA 0.6W5.5GHz2SC2682 SI-N 180V 0.1A 8W 180MHz | 2SC2690 SI-N 120V 1.2A 20W 160MHz2SC2694 SI-N 35V 20A 140W | 2SC2705 SI-N 150V 50mA 0.8W 200MHz2SC2706 SI-N 140V 10A 100W 90MHz | 2SC2712 SI-N 50V 0.15A 0.15W 80MHz2SC2714 SI-N 30V 20mA 0.1W 550MHz | 2SC2717 SI-N 30V 50mA 0.3W 300MHz2SC2724 SI-N 30V 30mA 200MHz | 2SC2749 SI-N 500V 10A 100W 50MHz2SC2750 SI-N 150V 15A 100W POWER | 2SC2751 SI-N 500V 15A 120W 50MHz2SC2752 SI-N 500V 0.5A 10W <1/3.5 | 2SC2753 SI-N 17V 0.07A 0.3W 5GHz2SC2759 SI-N 30V 50mA 0.2W 2.3GHz | 2SC2786 SI-N 20V 20mA 600MHz2SC2787 SI-N 50V 30mA 0.3W 250MHz | 2SC2791 SI-N 900V 5A 100W 2SC2792 SI-N 850V 2A 80W | 2SC2793 SI-N 900V 5A 100W 2SC2802 SI-N 300V 0.2A 10W 80MHz | 2SC2808 SI-N 100V 50mA 0.5W 140MHz2SC2810 SI-N 500V 7A 50W 18MHz | 2SC2812 SI-N 55V 0.15A 0.2W 100MHz2SC2814 SI-N 30V 0.03A 320MHz F | 2SC2825 SI-N 80V 6A 70W B>5002SC2837 SI-N 150V 10A 100W 70MHz | 2SC2839 SI-N 20V 30mA 0.15W 320MHz2SC2851 SI-N 36V 0.3A 1W 1.5GHz | 2SC2873 SI-N 50V 2A 0.5W 120MHz2SC2878 SI-N 20V 0.3A 0.4W 30MHz | 2SC2879 SI-N 45V 25A PEP=100W 28MHz2SC2882 SI-N 90V 0.4A 0.5W 100MHz | 2SC288A SI-N 35V 20mA 0.15W 2SC2898 SI-N 500V 8A 50W | 2SC2901 SI-N 40V 0.2A 0.6W <12/182SC2908 SI-N 200V 5A 50W 50MHz | 2SC2910 SI-N 160V 70mA 0.9W 150MHz2SC2911 SI-N 180V 140mA 10W 150MHz | 2SC2912 SI-N 200V 140mA 10W 150MHz2SC2922 SI-N 180V 17A 200W 50MHz | 2SC2923 SI-N 300V 0.1A 140MHz2SC2928 SI-N 1500V 5A 50W | 2SC2939 SI-N 500V 10A 100W 2.5us2SC2958 SI-N 160V 0.5A 1W | 2SC2979 SI-N 800V 3A 40W 2SC2987 SI-N 140V 12A 120W 60MHz | 2SC2988 SI-N 36V 0.5A 175MHz2SC2999 SI-N 20V 30mA 750MHz | 2SC3001 SI-N 20V 3APQ=7W(175MHz)2SC3019 SI-N 35V 0.4A 0.6W 520MHz | 2SC3020 SI-N 35V 1A 10W 2SC3022 SI-N 35V 7A 50W | 2SC3026 SI-N 1700V 5A 50W POWER2SC3030 N-DARL 900V 7A 80W | 2SC3039 SI-N 500V 7A 52W 2SC3042 SI-N 500/400V 12A 100W | 2SC3052F SI-N 50V 0.2A 0.15W 200MHz2SC3063 SI-N 300V 0.1A 1.2W 140MHz | 2SC3067 2xSI-N 130V 50mA 0.5W 1602SC3068 SI-N 30V 0.3A Ueb=15V B>8 | 2SC3071 SI-N 120V 0.2A Ueb=15V B>2SC3073 SI-N 30V 3A 15W 100MHz | 2SC3074 SI-N 60V 5A 20W120MHz2SC3075 SI-N 500V 0.8A 10W 1/1.5us | 2SC3089 SI-N 800V 7A 80W 2SC3101 SI-N 250V 30A 200W 25MHz | 2SC3102 SI-N 35V 18A 170W 520MHz2SC3112 SI-N 50V 0.15A 0.4W 100MHz | 2SC3116 SI-N 180V 0.7A 10W 120MHz2SC3117 SI-N 180V 1.5A 10W 120MHz | 2SC3133 SI-N 60V 6A 1.5W 27MHz2SC3148 SI-N 900V 3A 40W 1us | 2SC3150 SI-N 900V 3A 50W 15MHz2SC3153 SI-N 900V 6A 100W | 2SC3157 SI-N 150V 10A 60W 2SC3158 SI-N 500V 7A 60W | 2SC3164 SI-N 500V 10A 100W 2SC3169 SI-N 500V 2A 25W >8MHz | 2SC3175 SI-N 400V 7A 50W 40MHz2SC3178 SI-N 1200V 2A 60W | 2SC3179 SI-N 60V 4A 30W 15MHz2SC3180N SI-N 80V 6A 60W 30MHz | 2SC3181N SI-N 120V 8A 80W 30MHz2SC3182N SI-N 140V 10A 100W 30MHz | 2SC3195 SI-N 30V 20mA 0.1W 550MHz2SC3199 SI-N 60V 0.15A 0.2W 130MHz | 2SC3200 SI-N 120V 0.1A 0.3W 100MHz2SC3202 SI-N 35V 0.5A 0.5W 300MHz | 2SC3203 SI-N 35V 0.8A 0.6W 120MHz2SC3205 SI-N 30V 2A 1W 120MHz | 2SC3206 SI-N 150V 0.5A 0.8W 120MHz2SC3210 SI-N 500V 10A 100W 1us | 2SC3211 SI-N 800V 5A70W >3MHz2SC3212 SI-N 800V 7A 3W 3.5MHz | 2SC3225 SI-N 40V 2A 0.9W1us2SC3231 SI-N 200V 4A 40W 8MHz | 2SC3240 SI-N 50V 25A 110W 30MHz2SC3242 SI-N 20V 2A 0.9W 80MHz | 2SC3244E SI-N 100V 0.5A 0.9W 130MHz2SC3245A SI-N 150V 0.1A 0.9W 200MHz | 2SC3246 SI-N 30V 1.5A 0.9W 130MHz2SC3247 SI-N 50V 1A .9W 130MHz B> | 2SC3257 SI-N 250V 10A 40W 1/3.5us2SC3258 SI-N 100V 5A 30W 120MHz | 2SC3260 N-DARL 800V 3A 50W B>102SC3262 N-DARL 800V 10A 100W | 2SC3263 SI-N 230V 15A 130W 2SC3264 SI-N 230V 17A 200W 60MHz | 2SC3271 SI-N 300V 1A 5W 80MHz2SC3277 SI-N 500V 10A 90W 20MHz | 2SC3279 SI-N 10V 2A 0.75W 150MHz2SC3280 SI-N 160V 12A 120W 30MHz | 2SC3281 SI-N 200V 15A 150W 30MHz2SC3284 SI-N 150V 14A 125W 60MHz | 2SC3293 N-DARL+D 50V 1.2A 20W 1802SC3297 SI-N 30V 3A 15W 100MHz | 2SC3299 SI-N 60V 5A 20W 0.1us2SC3300 SI-N 100V 15A 100W | 2SC3303 SI-N 100V 5A 20W 0.2us2SC3306 SI-N 500V 10A 100W 1us | 2SC3307 SI-N 900V 10A 150W 1us2SC3309 SI-N 500V 2A 20W 1us | 2SC3310 SI-N 500V 5A 30W 1us2SC3311 SI-N 60V 0.1A 0.3W 150MHz | 2SC3320 SI-N 500V 15A 80W2SC3326 SI-N 20V 0.3A 0.15W 30MHz | 2SC3327 SI-N 50V 0.3A 0.2W 30MHz2SC3328 SI-N 80V 2A 0.9W 100MHz | 2SC3330 SI-N 60V 0.2A 0.3W 200MHz2SC3331 SI-N 60V 0.2A 0.5W 200MHz | 2SC3332 SI-N 180V 0.7A 0.7W 120MHz2SC3334 SI-N 250V 50mA 0.9W 100MHz | 2SC3345 SI-N 60V 12A 40W 90MHz2SC3346 SI-N 80V 12A 40W 0.2us | 2SC3355 SI-N 20V 0.1A 0.6W 6.5GHz2SC3356 SI-N 20V 0.1A 0.2W 7GHz | 2SC3377 SI-N 40V 1A 0.6W 150MHz2SC3378 SI-N 120V 0.1A 0.2W 100MHz | 2SC3379 SI-N 20V 1.5A PQ=3W 2SC3381 2xSI-N 80V 0.1A 0.4W 170MHz | 2SC3383 SI-N 60V 0.2A 0.5W 250MHz2SC3397 SI-N 50V 0.1A 250MHz 46K/ | 2SC3399 SI-N 50V 0.1A 250MHz2SC3400 SI-N 50V 0.1A 250MHz 22K/ | 2SC3401 SI-N 50V .1A46K/23KOHM2SC3402 SI-N 50V 0.1A 250MHz 10K/ | 2SC3405 SI-N 900V 0.8A 20W 1us2SC3409 SI-N 900V 2A 80W .8uS | 2SC3416 SI-N 200V 0.1A 5W 70MHz2SC3419 SI-N 40V 0.8A 5W 100MHz | 2SC3420 SI-N 50V 5A 10W 100MHz2SC3421O SI-N 120V 1A 1.5W BJT O-G | 2SC3421Y SI-N 120V 1A 10W 120MHz2SC3422Y SI-N 40V 3A 10W 100MHz | 2SC3423 SI-N 150V 50mA 5W 200MHz2SC3425 SI-N 500V 0.8A 10W | 2SC3446 SI-N 800V 7A 40W 18MHz2SC3447 SI-N 800V 5A 50W 18MHz | 2SC3456 SI-N 1100/800V 1.5A 40W2SC3457 SI-N 1100V 3A 50W | 2SC3460 SI-N 1100V 6A 100W 2SC3461 SI-N 1100/800V 8A 120W | 2SC3466 SI-N 1200/650V 8A 120W2SC3467 SI-N 200V 0.1A 1W 150MHz | 2SC3468 SI-N 300V 0.1A 1W 150MHz2SC3486 SI-N 1500V 6A 120W | 2SC3502 SI-N 200V 0.1A 1.2W2SC3503 SI-N 300V 0.1A 7W 150MHz | 2SC3504 SI-N 70V 0.05A 0.9W 500MHz2SC3505 SI-N 900V 6A 80W | 2SC3507 SI-N 1000/800V 5A 80W2SC3509 N-DARL+D 900V 10A 100W 0. | 2SC3514 SI-N 180V 0.1A 10W 200MHz2SC3518 SI-N 60V 5A 10W | 2SC3520 SI-N 500V 18A 130W 18MHz2SC3526 SI-N 110V 0.15A 7A 30W 1us | 2SC3528 SI-N 500V 20A 125W 2SC3549 SI-N 900V 3A 40W | 2SC3552 SI-N 1100V 12A 150W 15MHz2SC3568 SI-N 150V 10A 30W | 2SC3571 SI-N 500V 7A 30W 2SC3577 SI-N 850V 5A 80W 6MHz | 2SC3581 SI-N 55V 0.4A 0.9W 150MHz2SC3591 SI-N 400V 7A 50W | 2SC3595 SI-N 30V 0.5A 5W 2GHz2SC3596 SI-N 80V 0.3A 8W 700MHz | 2SC3597 SI-N 80V 0.5A 10W 800MHz2SC3599 SI-N 120V 0.3A 8W 500MHz | 2SC3600 SI-N 200V 0.1A 7W 400MHz2SC3601 SI-N 200V 0.15A 7W 400MHz | 2SC3608 SI-N 20V 0.08A 6.5GHz2SC3611 SI-N 50V 0.15A 4W 300MHz | 2SC3616 SI-N 25V 0.7A 250MHz2SC3621 SI-N 150V 1.5A 10W 100MHz | 2SC3623 SI-N 60V 0.15A 0.25W B=1K2SC3632 SI-N 600V 1A 10W 30MHz | 2SC3636 SI-N 900/500V 7A 80W2SC3642 SI-N 1200V 6A 100W 200ns | 2SC3655 SI-N 50V 0.1A 0.4W 46/23K2SC3656 SI-N 50V 0.1A 0.4W 10K/10 | 2SC3659 SI-N+D 1700/800V 5A 50W2SC3668 SI-N 50V 2A 1W 100MHz | 2SC3669 SI-N 80V 2A 1W 0.2us2SC3675 SI-N 1500/900V 0.1A 10W | 2SC3678 SI-N 900V 3A 80W 2SC3679 SI-N 900/800V 5A 100W | 2SC3680 SI-N 900/800V 7A 120W 6MHz2SC3684 SI-N+D 1500V 10A 150W | 2SC3688 SI-N 1500V 10A 150W 0.2us2SC3692 SI-N 100V 7A 30W <300/180 | 2SC373 SI-N 35V 0.1A 0.2W B>2002SC3746 SI-N 80V 5A 20W 100MHz | 2SC3748 SI-N 80V 10A 30W 100/600ns2SC3752 SI-N 1100/800V 3A 30W | 2SC3781 SI-N 120V 0.4A 15W 500MHz2SC3782 SI-N 200V 0.2A 15W 400MHz | 2SC3783 SI-N 800V 5A 100W 2SC3787 SI-N 180V 0.14A 10W 150MHz | 2SC3788 SI-N 200V 0.1A 5W150MHz2SC3789 SI-N 300V 0.1A 7W 70MHz | 2SC3790 SI-N 300V 0.1A 7W 150MHz2SC3792 SI-N 50V 0.5A 0.5W 250MHz | 2SC3795A SI-N 900V 5A 40W 2SC3807 SI-N 30V 2A 15W 260MHz | 2SC3808 N-DARL 80V 2A 170MHz B>802SC380TM SI-N 30V 50mA 0.3W 100MHz | 2SC3811 SI-N 40V 0.1A 0.4W 450MHz2SC3831 SI-N 500V 10A 100W | 2SC3833 SI-N 500/400V 12A 100W2SC3842 SI-N 600V 10A 70W 32MHz | 2SC3844 SI-N 600V 15A 75W 30MHz2SC3851 SI-N 80V 4A 25W 15MHz | 2SC3852 SI-N 80V 3A 25W 15MHz2SC3855 SI-N 200V 10A 100W 20MHz | 2SC3857 SI-N 200V 15A 150W 20MHz2SC3858 SI-N 200V 17A 200W 20MHz | 2SC3866 SI-N 900V 3A 40W 2SC3868 SI-N 500V 1.5A 25W 0.7us | 2SC3883 SI-N+D 1500V 6A 50W 2SC3884A SI-N 1500V 6A 50W | 2SC3886A SI-N 1500V 8A 50W 0.1us2SC388A SI-N 25V 50mA 0.3W 300MHz | 2SC3890 SI-N 500V 7A 30W 500NS2SC3892A SI-N+D 1500V 7A 50W 0.4us | 2SC3893A SI-N+D 1500V 8A 50W 2SC3895 SI-N 1500/800V 8A 70W | 2SC3896 SI-N 1500V 8A 70W 2SC3897 SI-N 1500V 10A 70W | 2SC3902 SI-N 180V 1.5A 10W 120MHz2SC3907 SI-N 180V 12A 130W 30MHz | 2SC3927 SI-N 900V 10A 120W 2SC394 SI-N 25V 0.1A 200MC RF | 2SC3940 SI-N 30V 1A 1W 200MHz2SC3943 SI-N 110V 0.15A 2W 300MHz | 2SC3944 SI-N 150V 1A 40W 300MHz2SC3948 SI-N 850V 10A 75W 20MHz | 2SC3950 SI-N 30V 0.5A 5W 2SC3952 SI-N 80V 0.5A 10W 700MHz | 2SC3953 SI-N 120V 0.2A 8W 400MHz2SC3954 SI-N 120V 0.3A 8W 400MHz | 2SC3955 SI-N 200V 0.1A 7W 300MHz2SC3956 SI-N 200V 0.2A 7W 70MHz | 2SC3964 SI-N 40V 2A 1.5W 1us2SC3972 SI-N 800/500V 5A 40W | 2SC3973A SI-N 900V 7A 45W 2SC3979A SI-N 800V 3A 2W 10MHz | 2SC3987 N-DARL+D 50V 3A 15W 2SC3996 SI-N 1500/800V 15A 180W | 2SC3998 SI-N 1500V 25A 250W POWER2SC3999 SI-N 300V 0.1A 0.75W 300MHz | 2SC4004 SI-N 900/800V 1A 30W <1/42SC4020 SI-N 900V 3A 50W 1us | 2SC4024 SI-N 100V 10A 35W B>3002SC4029 SI-N 230V 15A 150W 30MHz | 2SC4043 SI-N 20V 50mA 0.15W 3.2GHz2SC4046 SI-N 120V 0.2A 8W 350MHz | 2SC4052 SI-N 600V 3A 40W 20MHz2SC4056 SI-N 600V 8A 45W | 2SC4059 SI-N 600/450V 15A 130W2SC4064 SI-N 50V 12A 35W 40MHz | 2SC4107 SI-N 500/400V 10A 60W2SC4119 N-DARL+D 1500V 15A 250W B | 2SC4123 SI-N+D 1500V 7A 60W 2SC4125 SI-N+D 1500/800V 10A 70W | 2SC4131 SI-N 100V 15A 60W 18MHz2SC4135 SI-N 120V 2A 15W 200MHz | 2SC4137 SI-N 25V 0.1A300MHz2SC4138 SI-N 500V 10A 80W <1/3.5us | 2SC4153 SI-N 200V 7A 30W 0.5us2SC4157 SI-N 600V 10A 100W | 2SC4159 SI-N 180V 1.5A 15W 100MHz2SC4161 SI-N 500V 7A 30W | 2SC4169 N-DARL+D 50V 1.2A 1W B=4K2SC4199 SI-N 1400V 10A 100W | 2SC4200 SI-N 20V 0.6A 5W 2.5GHz2SC4204 SI-N 30V 0.7A 0.6W | 2SC4231 SI-N 1200/800V 2A 30W2SC4235 SI-N 1200/800V 3A 80W | 2SC4236 SI-N 1200/800V 6A 100W2SC4237 SI-N 1200/800V 10A 150W | 2SC4242 SI-N 450/400V 7A 40W2SC4256 SI-N 1500V 10A 175W 6MHz | 2SC4278 SI-N 150V 10A 100W 30MHz2SC4288A SI-N1600/600V 12A 200W | 2SC4289A SI-N 1500V 16A 200W2SC4290A SI-N 1500V 20A 200W | 2SC4297 SI-N 500V 12A 75W 10MHz2SC4298 SI-N 500V 15A 80W 10MHz | 2SC4300 SI-N 900V 5A 75W 1/6us2SC4304 SI-N 800V 3A 35W | 2SC4308 SI-N 30V 0.3A 0.6W 2.5GHz2SC4313 SI-N 900V 10A 100W 0.5us | 2SC4381 SI-N 150V 2A 25W 15MHz2SC4382 SI-N 200V 2A 25W 15MHz | 2SC4386 SI-N 160/120V 8A 75W 20MHz2SC4387 SI-N 200V 10A 80W 20MHz | 2SC4388 SI-N 200V 15A 85W 20MHz2SC4408 SI-N 80V 2A 0.9W 100/600ns | 2SC4429 SI-N 1100/800V 8A 60W2SC4430 SI-N 1100V 12A 65W 15MHz | 2SC4431 SI-N 120V 1.5A 20W 150MHz2SC4439 SI-N 180V 0.3A 8W 400MHz | 2SC4467 SI-N 160/120V 8A 80W 20MHz2SC4468 SI-N 200V 10A 80W 20MHz | 2SC4484 SI-N 30V 2.5A 1W 250MHz2SC4488 SI-N 120V 1A 1W 120MHz | 2SC4511 SI-N 120V 6A 30W 20MHz2SC4512 SI-N 120V 6A 50W 20MHz | 2SC4517 SI-N 900V 3A 30W 6MHz2SC4517A SI-N 1000V 3A 30W 0.5us | 2SC4531 SI-N+D 1500V 10A 50W2SC4532 SI-N 1700V 10A 200W 2uS | 2SC4538 SI-N 900V 5A 80W 2SC454 SI-N 30V 0.1A 230MHz | 2SC4542 SI-N 1500V 10A 50W 2SC4547 N-DARL+D 85V 3A 30W B>2K | 2SC4557 SI-N 900V 10A 80W <1/5.5us2SC4560 SI-N 1500V 10A 80W | 2SC458 SI-N 30V 0.1A 230MC UNI2SC4582 SI-N 600V 100A 65W 20MHz | 2SC460 SI-N 30V 0.1A 0.2W 230MHz2SC461 SI-N 30V 0.1A 0.2W 230MHz | 2SC4744 SI-N 1500V 6A POWER 2SC4745 SI-N 1500V 6A | 2SC4747 SI-N 1500V 10A 50W 0.3us2SC4758 SI-N 1500V 8A 50W HI-RES | 2SC4769 SI-N+D 1500V 7A 60W 2SC4770 SI-N 1500/800V 7A 60W | 2SC4793 SI-N 230V 1A 2W100MHz2SC4804 SI-N 900V 3A 30W 0.3us | 2SC4820 SI-N 450V 6A 30W 12MHz2SC4826 SI-N 200V 3A 1.3W 300MHz | 2SC4834 SI-N 500V 8A 45W <0.3/1.42SC4883A SI-N 180V 2A 20W 120MHz | 2SC4891 SI-N 1500V 15A 75W 2SC4908 SI-N 900V 3A 35W 1us | 2SC4924 SI-N 800V 10A 70W 2SC4977 SI-N 450V 7A 40W | 2SC5002 SI-N 1500V 7A 80W 2SC5003 SI-N+D 1500V 7A 80W | 2SC5027 SI-N 1100V 3A 50W 0.3us2SC5030 SI-N 50V 5A 1.3W 150MHz | 2SC5045 SI-N 1600V 15A 75W 2SC5047 SI-N 1600V 25A 250W | 2SC5048 SI-N 1500V 12A 50W 0.3us2SC5070 SI-N 30V 2A 1.5W B>800 | 2SC5086 SI-N 20V 80MA 7GHZ 2SC509 SI-N 35V 0.5A 0.6W 60MHz | 2SC5144 SI-N 1700V 20A 200W 2SC5148 SI-N 1500V 8A 50W 0.2us | 2SC5149 SI-N+D 1500V 8A 50W 0.2us2SC5150 SI-N 1700V 10A 50W 03us | 2SC5171 SI-N 180V 2A 20W 200MHz2SC5198 SI-N 140V 10A 100W 30MHz | 2SC5207 SI-N 1500V 10A 50W 0.4us2SC5242 SI-N 230V 15A 130W 30MHz | 2SC5244A SI-N 1600V 30A 200W 2SC5296 SI-N+D 1500V 8A 60W | 2SC5297 SI-N 1500V 8A 60W 2SC5299 SI-N 1500V 10A 70W 0.2US | 2SC535 SI-N 20V 20mA 0.1W 0.700M2SC536 SI-N 40V 0.1A 180MC UNI | 2SC620 SI-N 50V 0.2A 0.25W UNI2SC643 SI-N 1100V 2.5A 50W | 2SC644 SI-N 30V 50mA 0.25W2SC645 SI-N 30V 30mA 0.14W 200MHz | 2SC710 SI-N 30V 0.03A 200MHz2SC711 SI-N 30V 0.05A 150MHz | 2SC712 SI-N 30V 0.5A 150MHz2SC717 SI-N 30V 50mA 0.2W 600MHz | 2SC730 SI-N 40V 0.4A PQ=1.5W2SC732 SI-N 50V 0.15A 0.4W 150MHz | 2SC735 SI-N 35V 0.4A 0.3W UNI2SC752 SI-N 15V 100mA 0.1W | 2SC756 SI-N 40V 4A 10W 65MHz2SC784 SI-N 40V 0.02A 500MC RF | 2SC815 SI-N 60V 0.2A 0.25W 200MHz2SC828 SI-N 30V 0.05A 0.25W UNI | 2SC829 SI-N 30V 30mA 0.4W 230MHz2SC839 SI-N 50V 0.03A 250MHz | 2SC867 SI-N 400V 1A 23W 8MHz2SC869 SI-N 160V 30mA 0.2W 150MHz | 2SC898A SI-N 150V 7A 80W 15MHz2SC900 SI-N 30V 0.03A 100MHz | 2SC930 SI-N 15V 0.03A 300MC RF2SC936 SI-N 1000V 1A 22W POWER | 2SC941 SI-N 35V 20mA 0.2W 120MHz2SC943 SI-N 60V 0.2A 0.3W 220MHz | 2SC945 SI-N 50V 0.1A 250MC UNI2SC982 N-DARL 40V 0.3A 0.4W。

SI5010-GM中文资料

Rev. 1.3 12/04Copyright © 2004 by Silicon LaboratoriesSi5010Si5010OC-12/3, STM-4/1 SONET/SDH C LOCK AND D ATA R ECOVERY ICFeaturesComplete CDR solution includes the following:ApplicationsDescriptionThe Si5010 is a fully-integrated low-power clock and data recovery (CDR)IC designed for high-speed serial communication systems. It extracts timing information and data from a serial input at OC-12/3 or STM-4/1 data rates. DSPLL ® technology eliminates sensitive noise entry points thus making the PLL less susceptible to board-level interaction and helping to ensure optimal jitter performance in the application.The Si5010 represents an industry-leading combination of low-jitter,low-power, and small size for high-speed CDRs. It operates from a single 2.5V supply over the industrial temperature range (–40 to 85°C).Functional Block DiagramSupports OC-12/3, STM-4/1Low power, 293mW (TYP OC-12) Small footprint: 4x4mmDSPLL™ eliminates external loop filter components3.3V tolerant control inputsExceeds All SONET/SDH jitter specifications Jitter generation 1.6mUI rms (typ)Device powerdown Loss-of-lock indicator Single 2.5V supplySONET/SDH/ATM routers Add/drop multiplexers Digital cross connects Board level serial linksSONET/SDH test equipment Optical transceiver modules SONET/SDH regenerators元器件交易网Si50102Rev. 1.3Si5010Rev. 1.33Page1. Detailed Block Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .42. Electrical Specifications . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .53. Typical Application Schematic . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .94. Functional Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .104.1. DSPLL ® . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .104.2. PLL Self-Calibration . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .104.3. Multi-Rate Operation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .104.4. Reference Clock Detect . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .104.5. Lock Detect . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .104.6. PLL Performance . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .114.7. Powerdown . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .114.8. Device Grounding . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .114.9. Bias Generation Circuitry . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .114.10. Differential Input Circuitry . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .124.11. Differential Output Circuitry . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .135. Pin Descriptions: Si5010 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .146. Ordering Guide . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .167. Top Mark . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .168. Package Outline: Si5010-BM/GM . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .179. 4x4mm 20L QFN Recommended PCB Layout . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .18Document Change List . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .19Contact Information . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .20Si50104Rev. 1.3Si5010Rev. 1.35Si50106Rev. 1.3Si5010Rev. 1.37Si50108Rev. 1.3Si5010Rev. 1.39Si501010Rev. 1.3The information in this document is believed to be accurate in all respects at the time of publication but is subject to change without notice. Silicon Laboratories assumes no responsibility for errors and omissions, and disclaims responsibility for any consequences resulting from the use of information included herein. Additionally, Silicon Laboratories assumes no responsibility for the functioning of undescribed features or parameters. Silicon Laboratories reserves the right to make changes without further notice. Silicon Laboratories makes no warranty, rep-resentation or guarantee regarding the suitability of its products for any particular purpose, nor does Silicon Laboratories assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation conse-quential or incidental damages. Silicon Laboratories products are not designed, intended, or authorized for use in applications intended to support or sustain life, or for any other application in which the failure of the Silicon Laboratories product could create a situation where per-sonal injury or death may occur. Should Buyer purchase or use Silicon Laboratories products for any such unintended or unauthorized ap-plication, Buyer shall indemnify and hold Silicon Laboratories harmless against all claims and damages.。

LE5010 LinkedBlock Solo 使用手册说明书

凌思微电子(厦门)有限公司LINKEDSEMILE5010 LinkedBlock Solo使用手册修订记录目录第1章LE5010 Solo开发板硬件设计 (4)1. 1开发板硬件资源 (4)1. 2开发板IO口分配 (5)1. 2. 1板上外设 (5)1. 2. 2数字IO (5)1. 2. 3模拟IO (6)1. 2. 4IO配置注意事项 (6)1. 3开发板电源开关说明 (7)1. 3. 15V供电.................................................................................... 错误!未定义书签。

1. 3. 2 3.3V供电 (8)第2章LE5010 Solo开发板系统框图 (9)第3章LE5010 Solo开发板产品特性 (11)第4章开发板使用说明 (12)4. 1烧录与调试 (12)4. 2串口驱动安装 (12)4. 3软件调试注意事项 (12)第5章LE5010开发示例 (13)5. 1GPIO示例 (13)5. 2UART示例 (13)5. 3BLE串口透传示例 (13)第6章LE5010 Solo技术支持 (14)附录1例程路径:SCH&PCB&BOM (15)第1章LE5010 Solo开发板硬件设计1. 1 开发板硬件资源图1 LE5010 Solo Board 实物图图1 LE5010 Solo Board为凌思微LE5010 QFN48封装的开发学习板板宽为25.4*53.09mm,兼容面包板,板载天线保持黑漆倒角, PCB沉金工艺,丝印清晰,外观简洁美观。

25个外接IO(包括数字和模拟IO)TYPE-C口供电(5V),外部电源供电(3.3V)一个RGB灯, 不影响功耗测试具有USB-UART转换芯片(Type-C口兼容UART通信烧录)J-link(SWD模式)四线烧入调试口具有TX/RX 串口状态灯和PWR电源指示灯具有一个复位按键和唤醒按键(低电平有效)1. 2 开发板IO 口分配LE5010 Solo Board 开发板采用LE5010_QFN48封装IC 芯片,扣除电源、晶振、RF 管脚,共有34个IO 口(包括复位、BOOT 、烧录以及UART 口),这里将这34个IO 口分为3类,分别为学习板上外设、数字IO 口、模拟IO 口,具体如下表格。

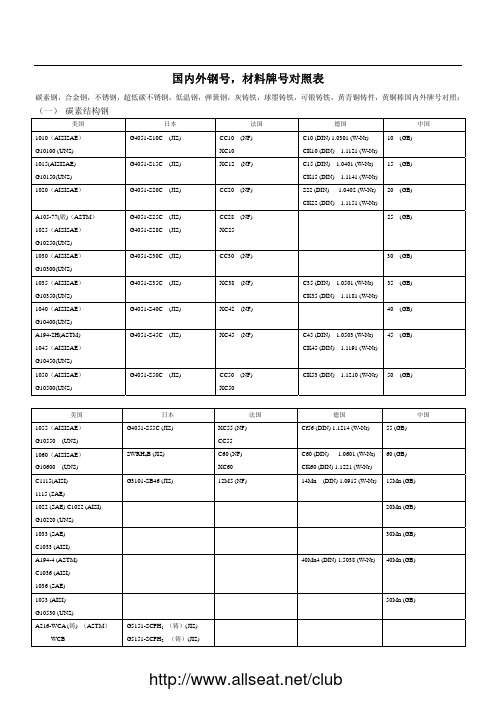

国内外钢号,材料牌号对照表

国内外钢号,材料牌号对照表碳素钢,合金钢,不锈钢,超低碳不锈钢,低温钢,弹簧钢,灰铸铁,球墨铸铁,可锻铸铁,黄青铜铸件,黄铜棒国内外牌号对照:(一) 碳素结构钢美国日本法国德国中国1010(AISISAE)G10100 (UNS) G4051-S10C (JIS) CC10 (NF)XC10C10 (DIN) 1.0301 (W-Nr)CK10 (DIN) 1.1121 (W-Nr)10 (GB)1015(AISISAE) G10150(UNS) G4051-S15C (JIS) XC12 (NF) C15 (DIN) 1.0401 (W-Nr)CK15 (DIN) 1.1141 (W-Nr)15 (GB)1020(AISISAE)G4051-S20C (JIS) CC20 (NF) S22 (DIN) 1.0402 (W-Nr)CK22 (DIN) 1.1151 (W-Nr)20 (GB)A105-77(锻)(ASTM)1025(AISISAE)G10250(UNS) G4051-S25C (JIS)G4051-S28C (JIS)CC28 (NF)XC2525 (GB)1030(AISISAE)G10300(UNS)G4051-S30C (JIS) CC30 (NF) 30 (GB)1035(AISISAE)G10350(UNS) G4051-S35C (JIS) XC38 (NF) C35 (DIN) 1.0501 (W-Nr)CK35 (DIN) 1.1181 (W-Nr)35 (GB)1040(AISISAE)G10400(UNS)G4051-S40C (JIS) XC42 (NF) 40 (GB)A194-2H(ASTM) 1045(AISISAE)G10450(UNS) G4051-S45C (JIS) XC45 (NF) C45 (DIN) 1.0503 (W-Nr)CK45 (DIN) 1.1191 (W-Nr)45 (GB)1050(AISISAE)G10500(UNS) G4051-S50C (JIS) CC50 (NF)XC50CK53 (DIN) 1.1210 (W-Nr) 50 (GB)美国日本法国德国中国1055(AISISAE)G10550 (UNS) G4051-S55C (JIS) XC55 (NF)CC55Cf56 (DIN) 1.1214 (W-Nr) 55 (GB)1060(AISISAE)G10600 (UNS) SWRH4B (JIS) C60 (NF)XC60C60 (DIN) 1.0601 (W-Nr)CK60 (DIN) 1.1221 (W-Nr)60 (GB)C1115(AISI)1115 (SAE)G3101-SB46 (JIS) 12M5 (NF) 14Mn (DIN) 1.0915 (W-Nr)15Mn (GB)1022 (SAE) C1022 (AISI) G10220 (UNS) 20Mn(GB)1033 (SAE) C1033 (AISI) 30Mn(GB)A194-4 (ASTM)C1036 (AISI)1036 (SAE)40Mn4 (DIN) 1.5038 (W-Nr)40Mn (GB)1053 (AISI)G10530 (UNS) 50Mn(GB)A216-WCA (铸) (ASTM)WCB G5151-SCPH1(铸)(JIS) G5151-SCPH2 (铸)(JIS)(二) 合金结构钢美国日本法国德国中国515 (SAE)G1150 (UNS) G4104-SCr415 (JIS)SCr21 (JIS旧)12C3 (NF) 15Cr3 (DIN)1.7015 (W-Nr)(EC60)15Cr (yB)5120 (AISI,SAE) G51200 (UNS) G4104-SCr420 (JIS)SCr22 (JIS旧)18Cr (NF) 20 (DIN) 1.7031 (W-Nr) 20 Cr (yB)5130 (AISI,SAE) G51300 (UNS) SCr2 (JIS) 32C4 (NF) 34Cr4(DIN)1 1.7033 (W-Nr)(VC-135)30 Cr (yB)美国日本法国德国中国5135 (AISI,SAE)G51350 (UNS)SCr1 (JIS) 38C4 (NF) 37Cr4(DIN) 1.7034 (W-Nr) 35 Cr (yB)5140 (AISI,SAE) G51400 (UNS) G4104-SCr440 (JIS)SCr1 (JIS旧)42C4 (NF) 41Cr4 (DIN)1.7035 (W-Nr)(VC140)40 Cr (yB)5145,5147 (AISI,SAE) G51450,G51470 (UNS) G4104-SCr445 (JIS)SCr5 (JIS旧)45C4 (NF) 45 Cr (yB)5150,5152 (AISI,SAE)G51500 (UNS)50C4 (NF) 50 Cr (yB)4017 (AISI,SAE)A182-F1 (锻)A302Gr,A (ASTM)A356Gr,2A204Gr-A,B,CG3213-SFHV12B (锻) (JIS) 15Mo3(DIN) 1.5415 (W-Nr) 16Mo (yB)4119 (SAE) 12CD4 (NF) 13CrMo44 (DIN)1.7335 (W-Nr)12 CrMo (yB)A387Gr.BA182-F11,F12 STT42,STB42,STC42 (JIS)G3213-SFHV23B,SFHV22B (JIS)(锻)12CD4 (NF) 16CrMo44 (DIN)1.7337 (W-Nr)15 CrMo (yB)4119 4118 (AISI,SAE)G41180 (UNS) (锻) (ASTM) G4105-SCM420 (JIS)G4105-SCM22 (JIS 旧)18CD4 (NF) 20CrMo5 (DIN)1.7264 (W-Nr) (ECM0100)20 CrMo (yB)25CD4 (NF) 25CrMo (DIN)1.7218 (W-Nr) (VCMo125)25 CrMo (yB旧))美国日本法国德国中国4130 (AISI,SAE) G4105-SCM430 (JIS)G4105-SCM2 (JIS旧)30CrMo(yB)E4132 (AISI) E4135 (AISI) G41350 (UNS)A193-B7 (ASTH) G4105-SCM435 (JIS)G4105-SCM3 (JIS旧)G4107 SNB735CD4 (NF)35CrMo4 (DIN) 1.7220(W-Nr)(VCMo135)35CrMo (yB)4140 (AISI,SAE) G41400 (UNS) G4105-SCM4 (JIS旧) 42CD4(NF)42 CrMo 4(DIN) 1.7225(W-Nr)(VCMo140)42CrMo (yB)20CDV6(NF)24 CrMo55(DIN) 1.7733(W-Nr) 24CrMoV (yB)13 CrMo42(DIN) 7709(W-Nr) 12CrMoV (yB)A356-Gr9 (ASTM)A405-P2415CrMoV (yB旧)A193-B16 (ASTM) G4107-SNB16 40CrMoV (yB旧)A217-WC1 (铸) (ASTM) G5151-SCPH11 (铸)(JIS)A217-WC6 (铸) (ASTM) G5151-SCPH21 (铸)(JIS) ZG20CrMoV A217-WC9 (铸) (ASTM) G5151-SCPH32(铸) (JIS) ZG15Cr1MoV A217-C5 (铸) (ASTM) G5151-SCPH61 (铸)(JIS) ZG2Cr5MoA182-F5 (铸) (ASTM)501 (AISI)502 (AISI) 51501 (SAE)S50100(UNS) S50200 (UNS) G3213-SFHV25(铸) (JIS)G3203-SFV AF5A (铸)(JIS)G3203-SFV AF5B (铸)(JIS)Z12CD5(NF)12 CrMo195(DIN)1.7362(W-Nr)1 Cr5Mo (GB)(三) 不锈钢美国日本法国德国中国410(AISI)S41008 (UNS) Z6CB (NF) X7Cr13 (DIN)4000 (W-Nr)0Cr13 (GB)430(AISI)51430 (SAE) CB-30 (ACI) S43000 (UNS) A276-430 (ASTM) JISG4303-SUS430 (JIS) Z8C17,Z10C17Z12C18 (NF)X8Cr17 (DIN) 1.4016 (W-Nr) 1Cr17 (GB)403(AISI)S40300 (UNS) A276-403,410 A182-F6a JISG4303-SUS403 (JIS)SUS410Z12C13 (NF) X10Cr13 (DIN) 1.4006 (W-Nr) 1Cr13 (GB)420 51210 (SAE)CA-15 S42000 (UNS)A276-420 (ASTM)JISG4303-SUS420J1 (JIS) Z20C13 (NF) X20Cr13 (DIN) 1.4021 (W-Nr) 2Cr13 (GB)420~(AISI)CA-40 (ACI)JISG4303-SUS420J2 (JIS) Z30C13 (NF) 3Cr13 (GB)Z40C13 (NF) X40Cr13 (DIN) 1.4034 (W-Nr) 4Cr13 (GB) A276-440C JISG4303-SUS440C (JIS) Z6CN18-10 (NF) 9Cr18 (GB)304 30304 (SAE)CF-8 S30400 (UNS)A182-F304A276-304 A193-B8,A194-8A320-B8,B8A (ASTM) JISG4303-SUS304 (JIS) X5CrNiL8 9 (DIN)1.4301 (W-Nr)0Cr18Ni9 (GB)美国日本法国德国中国A351-CF8 (铸)(ASTM)A296-CF8 (铸)(ASTM)JISG5121-SCS13 (JIS)SCS13AZG0Cr18Ni19(GB)302(AISI) 30302(SAE)CF-20(ACI) S30200 (UNS) JISG4303-SUS302 (JIS) Z12CN18-10 (NF) X12CrNi18 8 (DIN)1.4300 (W-Nr)1Cr18Ni9 (GB)321 (ASI) 30321 (SAE) S32100 (UNS)A182-F321A193-B8T(ASTM)A276-321 JISG4303-SUS321 (JIS) Z10CNT18-11 (NF) X10CrNiTi18 9 (DIN)1.4541 (W-Nr)1Cr18Ni9Ti (GB)A182-F316A276-316A193-B8M(ASTM)A194-8M JISG4303-SUS316 (JIS) Z8CNDT17-12 (NF) X10CrNiMoTi18 10 (DIN)1.4571 (W-Nr)X10CrNiMoTi18 12 (DIN)1.4573 (W-Nr)1Cr18Ni12Mo2Ti (GB)351-CF8M (铸) (ASTM)A296-CF8M (铸) (ASTM)JISG5121-SCS14 (铸) (JIS)SCS14AZGoCr18Ni12Mo2Ti347 (AISI) 30347 (SAE) S34700 (UNS)A182-F347A193-B8C (ASTM)A276-347 JISG4303-SUS347 (JIS) Z6CNNb18-10 (NF) X10CrNiNb18 9 (DIN)1.4550 (W-Nr)1Cr18Ni11Nb (GB)(四) 超低碳不锈钢美国日本法国德国中国304L(AISI) 30304L(SAE) S30403 (UNS)A182-F304L (ASTM)A276-304L (ASTM) G4303-SUS304L (JIS) Z2CN18-10 (NF) X3CrNi18 9 (DIN)1.4306 (W-Nr)00Cr18Ni10A351-CF3 A296-CF3 G5121-SCS19 (铸) (JIS)SCS19AZG00Gr18Ni10316L (AISI) 30316L S31603 (UNS)A182-F316L (ASTM) A276-316L (ASTM) G4303-SUS316L (JIS) Z2CND17-12 (NF) X2CrNiMo18.10 (DIN)1.4404 (W-Nr)00Cr17Ni14Mo2A351-CF3M (铸) (ASTM) A296-CF3M (铸) (ASTM) G5121-SCS16SCS16A (铸) (JIS)ZG00Cr17Ni14Mo2(五) 低温钢美国日本法国德国中国适应温度/℃A352-LCB(铸)(ASTM) G5152-SCPL1 (铸) (JIS)A350-LF2 (锻)(ASTM)-46A352-LC1(铸)(ASTM)G5152-SCP11 (铸) (JIS) -60 A352-LC2(铸)(ASTM) G5152-SCPL21 (铸) (JIS) -73 A352-LC3(铸)(ASTM)-LC4(铸)(ASTM)G5152-SCP31 (铸) (JIS)A350-LF3 (锻)(ASTM)-101A351-CF8(铸)(ASTM)A296-CF8(铸)(ASTM)SCS13G5121-SCS13A (铸) (JIS)ZGoCr18Ni9 -196A351-CF8M(铸)(ASTM)A296-CF8M(铸)(ASTM)SCS14G5121-SCS14A (铸) (JIS)ZGoCr18Ni12Mo2Ti -196A182-F304 (锻)(ASTM) G4303-SUS304(锻)(ASTM)0Cr18Ni9 -196A182-F316 (锻)(ASTM) G4303-SUS316(锻)(ASTM)01Cr18Ni12Mo2Ti -196(六)弹簧钢美国日本法国德国中国C1065 (AISI) 1065 (SAE)G10650 (UNS)G4801-SUP2 (JIS) XC65 (NF) CK67 (DIN) 1.1231 (W-Nr) 65 (YB)1084 (AISI,SAE)G10840VG4801-SUP3 (JIS) 85 (YB)9260 (AISI,SAE)G92600 (UNS)G4801-SUP6 (JIS) 60SiMn6 (DIN) 0908 (W-Nr) 60Si2Mn (yB旧)9260 (AISI,SAE)G92600 (UNS)G4801-SUP7(JIS) 65Si7 (DIN) 1.0906 (W-Nr) 63Si2Mn (yB旧)6150 (AISI)G65100 (UNS)G4801-SUP10 (JIS) 50CrV4 (DIN) 1.8159 (W-Nr) 50CrN A (yB)(七)灰铸铁美国日本法国德国中国JISG5501-FC15HT150(GB) ASTMA126-ClassAJISG5501-FC20HT200(GB) ASTMA126-ClassBJISG5501-FC25HT250(GB) JISG5501-FC30HT300(GB) JISG5501-FC35HT350(GB) (八)球墨铸铁美国日本法国德国中国JISG5502-FCD40QT400-17(GB) JISG5502-FCD45QT420-10(GB) (九) 可锻铸铁美国日本法国德国中国ASTMA47-32510JISG5702-FCMB28KTH300-6(GB) JISG5702-FCMB32KTH330-8(GB) JISG5702-FCMB35KTH350-10(GB) JISG5702-FCMB37KTH370-12(GB) (十) 黄青铜铸件美国日本法国德国中国ASTMB147-A110y No.7A JISH5102-HBSC1ASTMB147-A110y No.8A JISH5102-HBSC2ASTMB147-A110y No.8B JISH5102-HBSC3ASTMB145-A110y No.5A JISH5111-BC1ASTMB143-A110y No.1B JISH5111-BC2ZCuSn8Zn4ASTMB143-A110y No.1A JISH5111-BC3ZCuSn10Zn2ASTMB62-’ 52 JISH5111-BC6ZCuSn5Zn5.5ASTMB61-’ 52 JISH5111-BC7(十一)黄铜棒美国日本法国德国中国ASTMB283-Forging Brass JISH3423-B2BF1;B2BF2ASTMB21-A110yA、B、C JISH3424-NBSB1;NBSB2ASTMB135- A110yA、B JISH3425-NVSB1;HBSB2;HBSB3/club。

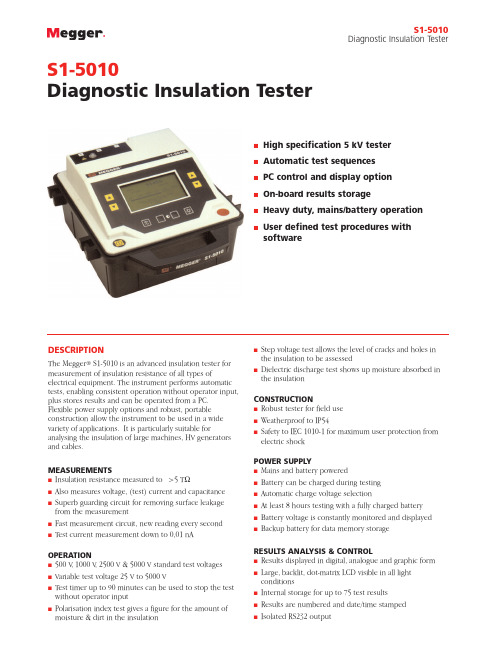

焊枪冷却系统介绍

用于焊枪冷却的流量监控系统© ifm electronic gmbh / KIA20091焊枪水冷循环-防止焊头过热,影响焊接质量 焊枪水冷循环-防止焊头过热,管道堵塞或水阀关闭= 管道堵塞或水阀关闭=》冷却不充分 焊头脱落= 焊头脱落=》空焊© ifm electronic gmbh / KIA20092水冷循环流量监测的要求1 反应速度快 2 稳定性 3 冷却水避免杂质堵塞 4 流量开关应不受污水影响 5 单向阀控制回水 6 截止阀防止水喷出-焊头脱落时 截止阀防止水喷出- 7 配合机器人© ifm electronic gmbh / KIA20093易福门焊枪冷却系统-Cooling Water Panel 易福门焊枪冷却系统- 大众定制——ZZ0064 大众定制1 流量监测 2 反应速度:1~3s 反应速度: ~ 3 数码显示 4 电压:20-28VDC 电压: - 5 保护等级:IP67 保护等级:© ifm electronic gmbh / KIA 2009 4易福门焊枪冷却系统-Cooling Water Panel 易福门焊枪冷却系统- 宝马定制——ZZ0057/ZZ0262(简装版) 宝马定制 (简装版)1 进水流量监控,回水压力监控 进水流量监控, 2 反应速度:<0.01s 反应速度: 3 数码显示 4 电压:18-36VDC 电压: - 5 保护等级:IP67 保护等级: 1 过滤 2 流量传感器 3 截止阀 4 单向阀 5 调节阀 6 压力传感器 7 保护盖© ifm electronic gmbh / KIA 2009 5易福门焊枪冷却系统-Cooling Water Panel 易福门焊枪冷却系统- 通用——SI5010 通用1 流量监控 2 反应速度:1~2s 反应速度: 3 十段 十段LED灯显示 灯显示 4 电压:18-36VDC 电压: - 5 保护等级:IP67 保护等级: 6 按钮调节开关点,自学习 按钮调节开关点,© ifm electronic gmbh / KIA20096易福门焊枪冷却系统-Cooling Water Panel 易福门焊枪冷却系统- OPEL——SBY332/4SBY1 流量监控 2 反应速度:<0.01s 反应速度: 3 旋钮调节开关点 4 电压:24VDC 电压: 5 保护等级:IP67 保护等级: 6 集成单向阀 7 设计紧凑,性价比高 设计紧凑,© ifm electronic gmbh / KIA 2009 7。

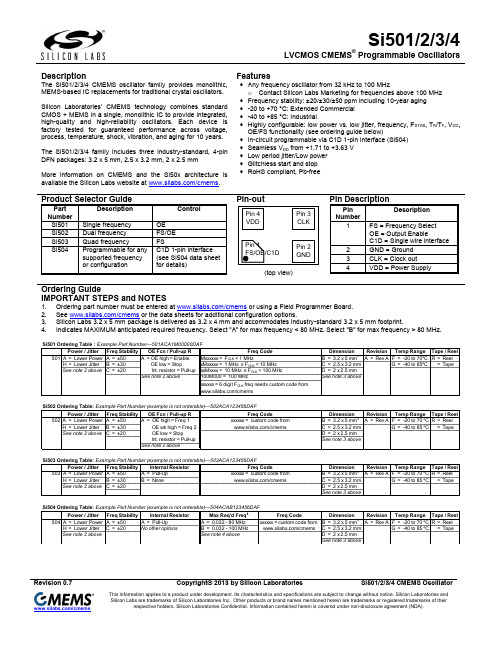

Si501 si502 SI503 SI504 DATASHEET

Ordering part number must be entered at /cmems or using a Field Programmer Board. See /cmems or the data sheets for additional configuration options. Silicon Labs 3.2 x 5 mm package is delivered as 3.2 x 4 mm and accommodates industry-standard 3.2 x 5 mm footprint. Indicates MAXIMUM anticipated required frequency. Select "A" for max frequency < 80 MHz. Select "B" for max frequency > 80 MHz.

Pin Description

Pin Number 1 2 3 4

Description

Single frequency Dual frequency Quad frequency Programmable for any supported frequency or configuration

Pin 2 GND

LVCMOS CMEMS Programmable Oscillators Selected Electrical Specifications

Parameter Frequency Range Supply Voltage Supply Current Static Supply Current Frequency Stability 1 CMOS Rise/Fall Time2, 3 Cycle-to-Cycle Jitter Period Jitter Pk-Pk Period Jitter Phase Jitter4 Duty Cycle

特瑞堡中文泛塞密封

2

特康® 泛塞®

■ 概述

特康® 泛塞® 是一种单作用,弹簧施力的密封件,用于 动态和静态运动。

泛塞® 在广泛的应用中是十分有效的。适用于要求具有 较好的耐化学介质的性能时,或者要求密封件工作在 极端温度下,以及用于需要良好的挤压和压缩性能的 场合。

最新资料请访问 2008年5月版

1

特康® 泛塞®

■ 选择正确的密封件

特康® 泛塞® 在所有工业领域的诸如液压缸和气缸之类 的元件设计中提供非常重要的作用,包括: - 极好的密封性能 - 非常耐磨损 - 抗间隙挤出性好 - 良好的耐腐蚀和耐磨性能 - 非常好的温度性能 - 摩擦系数小 - 结构紧凑 - 安装简单 特康® 泛塞® 有各种几何形状和结构,允许针对每种用 途选择最佳的形状。它们能够由各种特康® 材料(我们 的专利PTFE基复合物)制成,这些复合物是专门针对 密封件的配方,并且提供上乘的特性,专门满足我们 客户的要求。 当需要时,也能够用佐康® 材料(我们的专利聚乙烯基 复合物)制成。 为了针对您的用途,选择最好的特康® 泛塞® ,您必须 首先确定功能参数,第4页的表I和表II,以及第5页的 表III则能够用来对密封件和材料进行初选。这些表中详 细给出了在样本的何处能够找到进一步的细节。 考虑配合面的质量也是重要的,它对密封系统的使用 寿命和功能有重大的影响,有关这方面的指南在13页 和14页给出。 如果就有关密封件的技术规格需要帮助,请联系特瑞 堡密封系统公司,可以找您当地的市场部门,或登陆

下面列出泛塞在高达15ms49英尺s的速度下能够密封能够承受200mpa2000bar29000psi以上的高压能够安装在符合milg5514f和din3771的沟槽中弹簧力系统压力varisealvariseal选择表动态mpabapsi静态mpabapsim215454506527606008702709426050015m2s1645450652760600870270942605001005t40202002900606008702709423044615404005801808001160312018426050001t05hf28404005801808001160320032826050001t05roto2815150217525250362510014826050010c满足表ii外套材料选择指南turcont05turcont24turcont24turcont40turcont40turcont01zurconz80turcont78turcont01turcont01最新资料请访问wwwtsstrelleborgcom2008年5月版密封件接触的介质或工作条件静态或稍微动态往复旋转技术数据用途材料型式页码最高压力用途的类型工作温度最高速度标准材料空气气体水蒸气油原油普通化学品石油化学品食品药品真空材料选择指南t012500mm2500mm2500mm2500mm2500mm2500mm2500mm2500mm特殊材料适合较高的辐射负载有关这方面的进一步详细资料请联系特瑞堡密封系统公司

SI5000流量开关

7

(非水介质 → 7.1: 低流量调节)。 ►► 开启电源电压。 >> 所有 LED 逐个亮起,然后熄灭。 此时,将关闭输出功能(如果配置为常开)。 设备处于工作模式下。 ►► 安装时,使用正常的流量环流。 ►► 检查显示,并确定进一步操作。

6 用于水的安装与设定

1 2 3

Low

Flow

High

0 1 2 3 4 5 6 7 8 9

3

2 功能和特性

2.1 应用范围 本设备可用于监控液体及气体介质的流量。 2.2 流量监控的工作原理 • 本设备采用量热原理,可检测流速并切换输出功能: -- 如果有介质流动,则关闭输出功能/如果无介质流动,则开启输出功能。 本设备交货时功能设定如下: 输出功能 = 常开。 如有需要,可将输出功能更改 为常闭 (→ 7.2)。 此时适用於: 如果有介质流动,则开启输出功能。 • 如果流速加快,且达到开关点时,开关状态将会改变。 • 如果流速再次减慢,且达到“开关点的迟滞还原”值时,开关状态将会改变。 迟滞状态随流速而改变,且主要受所设监控范围的影响。 设定范围为 5...100 cm/s (= 出厂设定)时,迟滞范围为 2...5 cm/s,流速加快 时迟滞值将增大。 • 设备的标准反应时间为 1...10 秒。 反应时间受开关点设定的影响: -- 低开关点 = 流量增加时快速反应。 -- 高开关点 = 流量减少时快速反应。

4 电气连接

A: SI5010(正极开关);B: SI5011(负极开关) IFM 插座的芯线颜色: P: 编程线缆(适用于远程调节)→ 7.5) 1 = BN(棕色),2 = WH(白色),3 = BU(蓝色),4 = BK(黑色)

使用 4 线连接电缆,且未连接插脚 2 和 4。 使用插脚 2 和插脚 4 相连的 3 线插座,切换输出级来触发远程调节。

德国易福门流量监控器SI5010技术参数有现货

德国易福门流量监控器SI5010技术参数有现货德国易福门全系列产品都会有备货库存,全部原厂供货,全新原正品,质保一年。

只要您需要易福门产品,可以随时联系我们给您报价。

SI5010技术资料如下:流量监控器SI5010SID10ADBFPKG/US-100对管道中液体和气体的可靠监控通过适配器的多样过程连接开关点设定方便,适合快速安装坚固的不锈钢外壳,适用于严苛的工业环境LED 柱状图指示开关点和流量产品特征输入和输出总数数字输出数量: 1系统接口M18 x 1,5 内螺纹应用介质液体; 气体介质介质温度[°C]-25 (80)抗压强度 [bar]300允许工作压力的最大值(用于应用程序符合CRN标准) [bar] 208液体介质温度[°C]-25 (80)气体介质介质温度[°C]-25 (80)电气数据工作电压 [V]18...36 DC电流损耗 [mA]< 60防护等级III反相保护有开机延迟时间 [s]10总的输入/输出输入和输出总数数字输出数量: 1德国易福门产品部分型号如下:PN2094、PN7092、PN7093、PN7094、PN3094、PN7070、PN3071、PN2071、PN3071、PN2294、PN7294、PN3092、PN7096、PN2092、PN3093、PN7571、PN7594、PN3093、PN3070、PN2070、PN7099、PN2694、PN2594、PN3594。

SI5010中文资料