cadence常用器件及封装

Cadence各层作用及封装信息传输对应关系

Cadence 各层作用及封装信息传输关系(2013-12-20 22:48:04)转载▼silkscreen top:是字符层,一般称顶层字符或元件面字符,为各元器件的外框及名称标识等assemly top :是装配层,就是元器件含铜部分的实际大小,用来产生元器件的装配图。

我自己感觉这一层 如果对于贴片的元器件,如电容,就是两个贴片铜片的实际大小,而place_bound_top 层是整个贴片元器件的实际大小,这一点很多人都没真正搞懂!也可以使用此层进行布局;place_bound_top :是元器件封装实际大小,用来防止两个元器件叠加在一起不报错。

Autosilk top, Silkscreen top 和Assembly topAutosilk top :最后出gerber 的时候,自动生成的丝印层。

会自动调整丝印位置,以及碰到阻焊开窗的地方,丝印会自动消失,避免露锡的地方涂上丝印(一般画丝印层的时候,焊盘上不会画上丝印,所以过孔焊盘上有丝印,也不会有什么影响。

),所以我个人一般很少用到Autosilk top 层,毕竟最后出丝印的时候,都需要调整位置。

我一般直接用Silkscreen top 。

Silkscreen top :建库的时候,ref des 放置的层,及PCB 生产时,刷到板卡上的字符、器件外框或者公司LOGO 等放置的层。

我出gerber ,一般直接出这一层。

Assembly top :安装丝印层。

因为有些公司需要出安装图,有些为了手工焊接,喜欢把字符丝印放置在器件内部,比如电阻位号,喜欢把它的丝印放置在电阻符号外框的中间位置。

比如说电阻值等,想打印出来放置在安装图纸的电阻相应位置。

这时我们才会用到安装丝印层。

平时可以不用,或者平时只用Silkscreen top 。

所以这三个丝印层各有各的作用。

总体来说,cadence 软件定义的这些层使用很灵活,每个人用法可能稍微有差异,都是没关系的,只要实现你的使用目的即可。

常用元件库及原器件封装

RES1RES2 RES3RES4有极性电容对应的印制电路板封装形式为RB(桶状包装)系列。

RAD系列为RAD0.1~ RAD0.4,后面的数值表示两个焊点间的距离。

RB系列为RB.2/.4~RB.5/1.0,其后缀第一个数字表示封装模型中两个焊点间的距离,第二个数字表示电容外型的尺寸。

(通常为两焊盘间距的两倍)。

数值越大表示形状也越大,和ZENER1~ ZENER3(稳压二极管),对应的印制电路板封装有DIODE0.4(小功率)和DIODE0.7(大功率)两种,其中0.4、0.7指二极管的长短。

D11D54D105D146Q413Q811Q912Q1310Q178Q189CLK34006A17A25A33A41B16B24B32B415S110S211S312S413CO 9C4144008TRIG 2Q3R4CVo lt 5THR 6DIS7V C C8G N D1555OUT8GND 7Ct 6Rt 5Ofil 1Lfil 2IN 3V+4LM567D03Q02D14Q15D27Q26D38Q39D413Q412D514Q515D617Q616D718Q719OE 1LE1174LS373V c c20Io u t111lsb DI07Io u t212DI16DI25Rfb 9DI34DI416Vref8DI515DI614msb DI713ILE 19WR218CS 1WR12Xfer17DAC0831CRYSTAL(2)熔断丝:封装属性FUSEFUSE1部分分立元件库元件名称及中英对照AND 与门ANTENNA 天线BATTERY 直流电源BELL 铃,钟BVC 同轴电缆接插件BRIDEG 1 整流桥(二极管)BRIDEG 2 整流桥(集成块)BUFFER 缓冲器BUZZER 蜂鸣器CAP 电容CAPACITOR 电容CAPACITOR POL 有极性电容CAPVAR 可调电容CIRCUIT BREAKER 熔断丝COAX 同轴电缆CON 插口CRYSTAL 晶体整荡器DB 并行插口DIODE 二极管DIODE SCHOTTKY 稳压二极管DIODE VARACTOR 变容二极管DPY_3-SEG 3段LEDDPY_7-SEG 7段LEDDPY_7-SEG_DP 7段LED(带小数点) ELECTRO 电解电容FUSE 熔断器INDUCTOR 电感INDUCTOR IRON 带铁芯电感INDUCTOR3 可调电感JFET N N沟道场效应管JFET P P沟道场效应管LAMP 灯泡LAMP NEDN 起辉器LED 发光二极管METER 仪表MICROPHONE 麦克风MOSFET MOS管MOTOR AC 交流电机MOTOR SERVO 伺服电机NAND 与非门NOR 或非门NOT 非门NPN NPN三极管NPN-PHOTO 感光三极管OPAMP 运放OR 或门PHOTO 感光二极管PNP 三极管NPN DAR NPN三极管PNP DAR PNP三极管POT 滑线变阻器PELAY-DPDT 双刀双掷继电器RES1.2 电阻RES3.4 可变电阻RESISTOR BRIDGE ? 桥式电阻RESPACK ? 电阻SCR 晶闸管PLUG ? 插头PLUG AC FEMALE 三相交流插头SOCKET ? 插座SOURCE CURRENT 电流源SOURCE VOLTAGE 电压源SPEAKER 扬声器SW ? 开关SW-DPDY ? 双刀双掷开关SW-SPST ? 单刀单掷开关SW-PB 按钮THERMISTOR 电热调节器TRANS1 变压器TRANS2 可调变压器TRIAC ? 三端双向可控硅TRIODE ? 三极真空管VARISTOR 变阻器ZENER ? 齐纳二极管DPY_7-SEG_DP 数码管SW-PB 开关。

cadence快速手工画PCB封装步骤

cadence快速手工画PCB封装步骤主要记录封装必备的元素。

必备5项。

(a)setup,areas里package geometry的place_bound_top和height(b)add,line里的silkscreen_top/assembly top(c)layout,refdes里的silksreen_top与assembly top缺项的话,保存时会报错。

详细步骤:1.打开 Allegro PCB design gxl,选择file new drawing ,drawing type 选择package symbol,名字填,browse选择存储路径;2.设置画布大小。

setup,design parameters,弹出editor对话框,x,y输入值,单位选择mm。

3.放置引脚,输入坐标4.设置外形 setup ,areas,package boundary,使得 options 如下设置active class为package geometry,subclass选择place_bound_top,然后输入坐标;6.添加丝印外形add,line,确认options里,active class为package geometry,subclass为silkscreen_top,输入坐标画外形;完事右键done。

7.添加元器件标志layout,labels,refdes,options里主类为ref des,子类为silksreen_top,text_block选3,单击左键输入值,u*。

8.添加装配层add line,主类package geometry,子类assembly top,输入坐标,完事右键done。

9.添加元器件标志layout,labels,refdes,options主类选refdes,子类选assembly_top,text_block 选3、元件中间左键输入u*10.保存。

Cadence_Allegro元件封装制作流程含实例

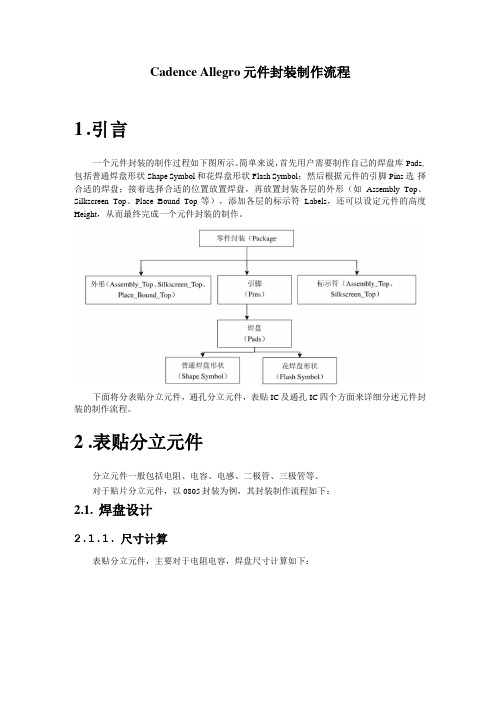

Cadence Allegro元件封装制作流程1.引言一个元件封装的制作过程如下图所示。

简单来说,首先用户需要制作自己的焊盘库Pads, 包括普通焊盘形状Shape Symbol和花焊盘形状Flash Symbol;然后根据元件的引脚Pins选择合适的焊盘;接着选择合适的位置放置焊盘,再放置封装各层的外形(如Assembly_Top、Silkscreen_Top、Place_Bound_Top等),添加各层的标示符Labels,还可以设定元件的高度Height,从而最终完成一个元件封装的制作。

下面将分表贴分立元件,通孔分立元件,表贴IC及通孔IC四个方面来详细分述元件封装的制作流程。

2.表贴分立元件分立元件一般包括电阻、电容、电感、二极管、三极管等。

对于贴片分立元件,以0805封装为例,其封装制作流程如下:2.1.焊盘设计2.1.1.尺寸计算表贴分立元件,主要对于电阻电容,焊盘尺寸计算如下:其中,K 为元件引脚宽度,H 为元件引脚高度,W 为引脚长度,P 为两引脚之间距离(边 距离,非中心距离),L 为元件长度。

X 为焊盘长度,Y 为焊盘宽度,R 为焊盘间边距离,G 为封装总长度。

则封装的各尺寸可按下述规则:1) X=Wmax+2/3*Hmax+8 mil2) Y=L ,当 L<50 mil ; Y=L+ (6~10) mil ,当 L>=50 mil 时3) R=P-8=L-2*Wmax-8 mil ;或者G=L+X 。

这两条选一个即可。

个人觉得后者更容易理解,相当于元件引脚外边沿处于焊盘中点,这在元件尺寸较小时很适合(尤其是当 Wmax 标得不准时,第一个原则对封装影响很大),但若元件尺寸较大(比如说钽电容 的封装)则会使得焊盘间距过大,不利于机器焊接,这时候就可以选用第一条原则。

本文介绍中统一使用第二个。

注:实际选择尺寸时多选用整数值,如果手工焊接,尺寸多或少几个mil 影响均不大, 可视具体情况自由选择;若是机器焊接,最好联系工厂得到其推荐的尺寸。

cadence封装中各层的区别作用

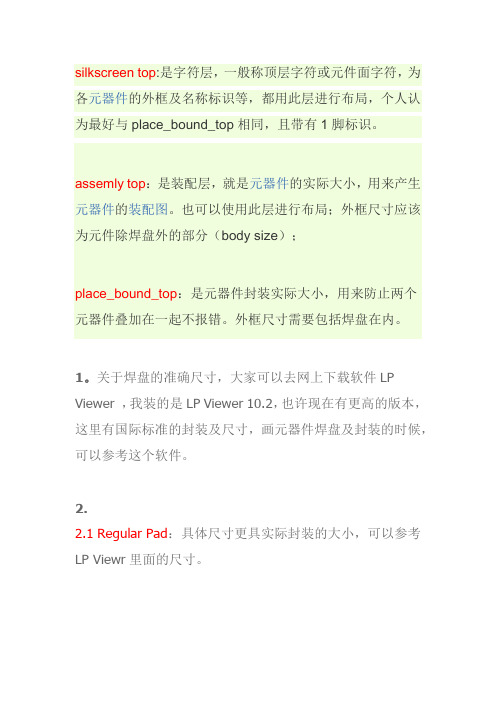

silkscreen top:是字符层,一般称顶层字符或元件面字符,为各元器件的外框及名称标识等,都用此层进行布局,个人认为最好与place_bound_top相同,且带有1脚标识。

assemly top:是装配层,就是元器件的实际大小,用来产生元器件的装配图。

也可以使用此层进行布局;外框尺寸应该为元件除焊盘外的部分(body size);place_bound_top:是元器件封装实际大小,用来防止两个元器件叠加在一起不报错。

外框尺寸需要包括焊盘在内。

1。

关于焊盘的准确尺寸,大家可以去网上下载软件LP Viewer ,我装的是LP Viewer 10.2,也许现在有更高的版本,这里有国际标准的封装及尺寸,画元器件焊盘及封装的时候,可以参考这个软件。

2.2.1 Regular Pad:具体尺寸更具实际封装的大小,可以参考LP Viewr里面的尺寸。

2.2 Thermal relief:热涨缩间隙,常用于相同NetList的填充铜薄与PAD 的间隙。

通常比Pad 直径大20mil(0.5mm),如果Pad 直径小于40mil,根据需要适当减小。

2.3 Anti Pad:抗电边距,常用于不同NetList的填充铜薄与PAD的间隙。

通常比Pad直径大20mil(0.5mm),如果Pad 直径小于40mil,根据需要适当减小。

2.4 SolderMask:通常比规则焊盘大4mil(0.1mm)。

2.5 Pastemask:通常和规则焊盘大小相仿。

2.6 Filmmask:应用比较少,用户自己设定。

再次归纳:1.贴片焊盘要有SolderMask_TOP和Pastemask_TOP。

通孔要有SolderMask_TOP和SolderMask_BOTTOM,因为两边都要露在外面。

盲孔要有SolderMask_TOP,因为一边露在外面。

埋孔焊盘不需要SolderMask和Pastemask,因为都在里面。

【阻焊层】干嘛用的?上面说就是涂绿油,蓝油,红油嘛,除了焊盘、过孔等不能涂『涂了你怎么能上、焊焊锡啊?是吧?』其他都要涂上阻焊剂,这个阻焊剂有绿色的蓝色的红色的。

cadence快速手工画PCB封装步骤

cadence快速手工画PCB封装步骤为了完成一个快速手工画PCB封装,以下是一般步骤和相关注意事项:步骤1:准备材料和工具首先,你需要准备以下材料和工具:-代表PCB封装的器件-PCB板-电子组件,如电阻、电容、晶体管等-焊接设备,如焊接铁、焊锡等-压力设备,如夹子、插头等步骤2:确定器件的封装类型在进行封装之前,你需要确认所需器件的封装类型。

封装类型通常可以在器件的数据手册中找到。

你可以根据器件封装的外形和引脚布局来确定封装类型。

步骤3:准备PCB板在开始封装之前,你需要准备好PCB板。

首先,确保PCB板是干净的,并且不含任何杂质。

然后,根据设计要求布置并固定电路元件的位置。

步骤4:焊接引脚在安装电路元件之前,你需要焊接引脚。

焊接可以通过在引脚和PCB板焊盘之间添加焊锡,并使用焊接铁进行加热来完成。

确保焊接的引脚完全与焊盘相连,并且没有冷焊、短路或其他电焊问题。

步骤5:安装电路元件一旦引脚焊接完成,你可以开始安装电路元件。

根据器件封装类型和PCB板的设计要求,安装电路元件的位置和方向。

使用夹子或其他固定装置将元件固定在PCB板上。

步骤6:焊接电路元件安装完所有电路元件后,你需要对它们进行焊接。

与焊接引脚一样,焊接电路元件可以通过添加焊锡并使用焊接铁进行加热来完成。

确保每个电路元件的引脚完全与焊盘相连,并且没有冷焊、短路或其他电焊问题。

步骤7:进行电气和机械测试完成焊接后,你需要对封装后的PCB进行电气和机械测试。

电气测试可以通过使用万用表或信号发生器来验证电路元件的连接和功能。

机械测试可以确保元件安装稳固,并且不会因外部力作用而脱落。

步骤8:修复和调整在电气和机械测试中,如果发现问题,你需要根据具体情况进行修复和调整。

例如,如果发现引脚焊接不良,你可以使用焊接铁重新加热并添加焊锡。

请注意以下几点:-在整个封装过程中,要小心并避免过度加热电路元件,以免损坏器件。

-确保所有焊接都是均匀且牢固的,以确保不会出现冷焊或脱落。

Cadence Allegro封装总结

Cad ence Allegro 封装尺寸总结1、 表贴ICa )焊盘表贴IC 的焊盘取决于四个参数:脚趾长度W ,脚趾宽度Z ,脚趾指尖与芯片中心的距离D ,引脚间距P ,如下图:焊盘尺寸及位置计算:X=W+48 S=D+24 Y=P/2+1,当P<=26mil 时 Y=Z+8,当P>26mil 时b )silkscreen丝印框与引脚内边间距>=10mil ,线宽6mil ,矩形即可。

对于sop 等两侧引脚的封装,长度边界取IC 的非引脚边界即可。

丝印框内靠近第一脚打点标记,丝印框外,第一脚附近打点标记,打点线宽视元件大小而定,合适即可。

对于QFP 和BGA 封装(引脚在芯片底部的封装),一般在丝印框上切角表示第一脚的位置。

c )place bound该区域是为防止元件重叠而设置的,大小可取元件焊盘外边缘以及元件体外侧+20mil 即可,线宽不用设置,矩形即可。

即,沿元件体以及元件焊盘的外侧画一矩形,然后将矩形的长宽分别+20mil 。

d )assembly该区域可比silkscreen 小10mil ,线宽不用设置,矩形即可。

对于外形不规则的器件,assembly 指的是器件体的区域(一般也是矩形),切不可粗略的以一个几乎覆盖整个封装区域的矩形代替。

PS :对于比较确定的封装类型,可应用LP Wizard 来计算详细的焊盘尺寸和位置,再得到焊盘尺寸和位置的同时还会得到silkscreen 和place bound 的相关数据,对于后两个数据,可以采纳,也可以不采纳。

2、通孔ICa)焊盘对于通孔元件,需要设置常规焊盘,热焊盘,阻焊盘,最好把begin层,internal层,bottom 层都设置好上述三种焊盘。

因为顶层和底层也可能是阴片,也可能被作为内层使用。

通孔直径:比针脚直径大8-20mil,通常可取10mil。

常规焊盘直径:一般要求常规焊盘宽度不得小于10mil,通常可取比通孔直径大20mil (此时常规焊盘的大小正好和花焊盘的内径相同)。

cadence元件封装总结

Cadence 封装尺寸总结1、 表贴ICa )焊盘表贴IC 的焊盘取决于四个参数:脚趾长度W ,脚趾宽度Z ,脚趾指尖与芯片中心的距离D ,引脚间距P ,如下图:焊盘尺寸及位置计算:X=W+48S=D+24 Y=P/2+1,当P<=26mil 时 Y=Z+8,当P>26mil 时b )silkscreen丝印框与引脚内边间距>=10mil ,线宽6mil ,矩形即可。

对于sop 等两侧引脚的封装,长度边界取IC 的非引脚边界即可。

丝印框内靠近第一脚打点标记,丝印框外,第一脚附近打点标记,打点线宽视元件大小而定,合适即可。

对于QFP 和BGA 封装(引脚在芯片底部的封装),一般在丝印框上切角表示第一脚的位置。

c )place bound该区域是为防止元件重叠而设置的,大小可取元件焊盘外边缘以及元件体外侧+20mil 即可,线宽不用设置,矩形即可。

即,沿元件体以及元件焊盘的外侧画一矩形,然后将矩形的长宽分别+20mil 。

d )assembly该区域可比silkscreen 小10mil ,线宽不用设置,矩形即可。

对于外形不规则的器件,assembly 指的是器件体的区域(一般也是矩形),切不可粗略的以一个几乎覆盖整个封装区域的矩形代替。

PS :对于比较确定的封装类型,可应用LP Wizard 来计算详细的焊盘尺寸和位置,再得到焊盘尺寸和位置的同时还会得到silkscreen 和place bound 的相关数据,对于后两个数据,可以采纳,也可以不采纳。

2、通孔ICa)焊盘对于通孔元件,需要设置常规焊盘,热焊盘,阻焊盘,最好把begin层,internal层,bottom 层都设置好上述三种焊盘。

因为顶层和底层也可能是阴片,也可能被作为内层使用。

通孔直径:比针脚直径大8-20mil,通常可取10mil。

常规焊盘直径:一般要求常规焊盘宽度不得小于10mil,通常可取比通孔直径大20mil (此时常规焊盘的大小正好和花焊盘的内径相同)。

Cadence-Allegro元件封装制作流程(含实例)..

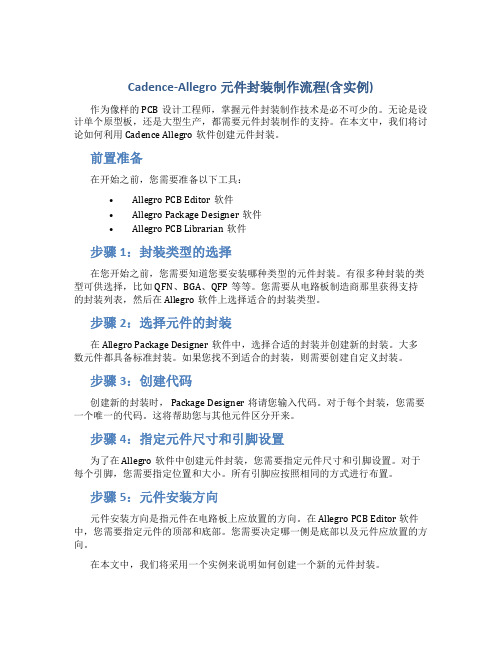

Cadence-Allegro元件封装制作流程(含实例)作为像样的PCB设计工程师,掌握元件封装制作技术是必不可少的。

无论是设计单个原型板,还是大型生产,都需要元件封装制作的支持。

在本文中,我们将讨论如何利用Cadence Allegro软件创建元件封装。

前置准备在开始之前,您需要准备以下工具:•Allegro PCB Editor软件•Allegro Package Designer软件•Allegro PCB Librarian软件步骤1:封装类型的选择在您开始之前,您需要知道您要安装哪种类型的元件封装。

有很多种封装的类型可供选择,比如QFN、BGA、QFP等等。

您需要从电路板制造商那里获得支持的封装列表,然后在 Allegro软件上选择适合的封装类型。

步骤2:选择元件的封装在 Allegro Package Designer软件中,选择合适的封装并创建新的封装。

大多数元件都具备标准封装。

如果您找不到适合的封装,则需要创建自定义封装。

步骤3:创建代码创建新的封装时, Package Designer将请您输入代码。

对于每个封装,您需要一个唯一的代码。

这将帮助您与其他元件区分开来。

步骤4:指定元件尺寸和引脚设置为了在 Allegro软件中创建元件封装,您需要指定元件尺寸和引脚设置。

对于每个引脚,您需要指定位置和大小。

所有引脚应按照相同的方式进行布置。

步骤5:元件安装方向元件安装方向是指元件在电路板上应放置的方向。

在 Allegro PCB Editor 软件中,您需要指定元件的顶部和底部。

您需要决定哪一侧是底部以及元件应放置的方向。

在本文中,我们将采用一个实例来说明如何创建一个新的元件封装。

实例:创建一个新的MCU元件封装MCU芯片有各种各样的封装类型。

我们选择TSOP28封装类型作为本实例的示范。

步骤1:打开 Allegro Package Designer打开 Allegro Package Designer软件,并选择新建TSOP28封装。

Cadence常用元器件对应表

SHIFTREGISTER.OLB 共 610 个零件,存放移位寄存器,如 4006,SNLS91 等。 SRAM.OLB 共 691 个零件,存放静态存储器,如 MCM6164,P4C116 等。 TRANSISTOR.OLB 共 210 个零件,存放晶体管(含 FET,UJT,PUT 等),如 2N2222A,2N2905 等。

ARITHMETIC.OLB 共 182 个零件,存放逻辑运算 IC,如 TC4032B,74LS85 等。 ATOD.OLB 共 618 个零件,存放 A/D 转换 IC,如 ADC0804,TC7109 等。 BUS DRIVERTRANSCEIVER.OLB 共 632 个零件,存放汇流排驱动 IC,如 74LS244,74LS373 等数字 IC。 CAPSYM.OLB 共 35 个零件,存放电源,地,输入输出口,标题栏等。 CONNECTOR.OLB 共 816 个零件,存放连接器,如 4 HEADER,CON AT62,RCA JACK 等。 COUNTER.OLB 共 182 个零件,存放计数器 IC,如 74LS90,CD4040B。 DISCRETE.OLB 共 872 个零件,存放分立式元件,如电阻,电容,电感,开关,变压器等常用零 件。 DRAM.OLB 共 623 个零件,存放动态存储器,如 TMS44C256,MN41100-10 等。 ELECTRO MECHANICAL.OLB 共 6 个零件,存放马达,断路器等电机类元件。 FIFO.OLB 共 177 个零件,存放先进先出资料暂存器,如 40105,SN74LS232。 FILTRE.OLB 共 80 个零件,存放滤波器类元件,如 MAX270,LTC1065 等。 FPGA.OLB 存放可编程逻辑器件,如 XC6216/LCC。 GATE.OLB 共 691 个零件,存放逻辑门(含 CMOS 和 TLL)。 LATCH.OLB 共 305 个零件,存放锁存器,如 4013,74LS73,74LS76 等。 LINE DRIVER RECEIVER.OLB 共 380 个零件,存放线控驱动与接收器。如 SN75125,DS275 等。

cad常用电子元件封装

常用电子元件封装2011-06-13 20:46:56 来源:互联网电阻:RES1,RES2,RES3,RES4;封装属性为axial系列无极性电容:cap;封装属性为RAD-0.1到rad-0.4电解电容:electroi;封装属性为rb.2/.4到rb.5/1.0电位器:pot1,pot2;封装属性为vr-1到vr-5二极管:封装属性为diode-0.4(小功率)diode-0.7(大功率)三极管:常见的封装属性为to-18(普通三极管)to-22(大功率三极管)to-3(大功率达林顿管)电源稳压块有78和79系列;78系列如7805,7812,7820等79系列有7905,7912,7920等常见的封装属性有to126h和to126v整流桥:BRIDGE1,BRIDGE2: 封装属性为D系列(D-44,D-37,D-46)电阻:AXIAL0.3-AXIAL0.7其中0.4-0.7指电阻的长度,一般用AXIAL0.4瓷片电容:RAD0.1-RAD0.3。

其中0.1-0.3指电容大小,一般用RAD0.1电解电容:RB.1/.2-RB.4/.8 其中.1/.2-.4/.8指电容大小。

一般<100uF用RB.1/.2,100uF-470uF用RB.2/.4,>470uF用RB.3/.6二极管:DIODE0.4-DIODE0.7 其中0.4-0.7指二极管长短,一般用DIODE0.4发光二极管:RB.1/.2集成块:DIP8-DIP40, 其中8-40指有多少脚,8脚的就是DIP8 贴片电阻0603表示的是封装尺寸与具体阻值没有关系,但封装尺寸与功率有关通常来说如下:0201 1/20W0402 1/16W0603 1/10W0805 1/8W1206 1/4W电容电阻外形尺寸与封装的对应关系是:0402=1.0mmx0.5mm0603=1.6mmx0.8mm0805=2.0mmx1.2mm1206=3.2mmx1.6mm1210=3.2mmx2.5mm1812=4.5mmx3.2mm2225=5.6mmx6.5mm零件封装是指实际零件焊接到电路板时所指示的外观和焊点的位置。

Cadence原理图封装PCB封装3D封装制作

Cadence原理图封装PCB封装3D封装制作趁着学习Cadence的时间,写⼀篇关于元器件的原理图封装、PCB封装和3D封装制作的⽂章分享给⼤家。

个⼈能⽤有限,有不⾜的地⽅,欢迎⼤家指出。

我使⽤的是Cadence 16.6版本。

这⾥以MP2359为例,先看技术⼿册,封装为SOT23-6,如下图所⽰。

⼀、焊盘制作打开Pad Designer软件因为我们做的是表贴焊盘,在Parametes选项卡中我们只修改Units为Millimeter,即单位修改为毫⽶。

选择Layers选项卡,勾选SIngle layer mode,表⽰我们使⽤的是表贴焊盘模式,选择BEGIN LAYER层,在Geometry中选择Rectangle焊盘,再根据⼿册输⼊Width 0.6mm和Height 1.2mm。

在BEGIN LAYER层前单击⿏标右键,选择Copy,粘贴到SOLDERMASK_TOP层和PASTEMASK_TOP层,即阻焊层和钢⽹层。

由于阻焊层要求要⽐实际焊盘边距⼤0.1mm,所有我们还要修改阻焊层,选择SOLDERMASK_TOP层,修改Width 0.8mm 和Height 1.4mm。

到这⾥我们焊盘制作完成,点击菜单栏File,选择Save as,命名s_rect_x0_6_y1_2.pad,我这⾥使⽤的规则s表⽰表贴,rect表⽰矩形,x为宽,y为⾼,点击保存即可。

注意命名除了数字、字母、下滑杠和中杆以外,其它字符都不要使⽤,在某些情况下可能出现乱码。

⼆、封装制作打开Allegro软件,选择菜单栏File,选择NEW,如下图,在弹出的对话框中输⼊Drawing Name:SOT23-6,点击Browse 选择保存的位置,再选择Drawing Type:Package symbol,点击OK。

设置环境参数,选择菜单栏Setup,选择Design Parameter,在弹出的对话框中,选择Design选项卡,在User units中选择Millimeter。

Cadence元件封装设计

Cadence元件圭寸装设计、进入封装编辑器要创建和编辑零件封装,先要进入Allegro P ackage封装编辑器界面,步骤如下:1、执行“开始/Cadence/Release 16.3/PCB Editor ”命令,弹出产品选择对话框,如下图,点击Allegro PCB Design GXL 即可进入PCB设计。

.. .... —. . . , . . 4 匕fd 巨"・■■■--U2、在PCB设计系统中,执行File/New 将弹出New Drawing对话框如下图,该对话框中,在Drawing Name中填入新建设计名称,并可点击后面Browse改变设计存储路径;在Temp late栏中可选择所需设计模板;在Drawi ng Type栏中,选择设计的类型。

这里可以用以设计电路板(Board) 、创建模型(Module) ,还可以用以创建以下各类封装:(1) 封装符号(Package Symbol)一般元件的封装符号, 后缀名为*.psm。

PCB 中所有元件像电阻、电容、电感、IC等的圭寸装类型都是Package Symbol;(2) 机械符号(Mechanical Symbol)由板外框及螺丝孔所组成的机构符号,后缀名为*.bsm。

有时设计PCB的外框及螺丝孔位置都是一样的,比如显卡,电脑主板,每次设计PCB时要画一次板外框及确定螺丝孔位置,显得较麻烦。

这时我们可以将PCB的外框及螺丝孔建成一个Mechanical Symbol, 设计PCB时,调用Mechanical Symbol 即可。

(3) 格式符号(Format Symbol)由图框和说明所组成的元件符号,后缀名为*.osm。

(4) 形状符号(Shape Symbol)用以建立特殊形状的焊盘用,后缀为*.ssm。

像金手指封装的焊盘即为一个不规则形状的焊盘, 在建立此焊盘时要先将不规则形状焊盘的形状建成一个Shape Symbol, 然后在建立焊盘中调用此Shape Symbol。

最新Cadence 元件封装及常见问题解决

Cadence 使用及注意事项12目录31 PCB工艺规则 (1)2 Cadence的软件模块 (3)452.1 Cadence的软件模块--- Pad Designer (4)62.2 Pad的制作 (5)72.2.1 PAD物理焊盘介绍 (6)83 Allegro中元件封装的制作 (9)93.1 PCB 元件(Symbol)必要的 CLASS/SUBCLASS (9)3.2 PCB 元件(Symbol)位号的常用定义 (13)10113.3 PCB 元件(Symbol)字符的字号和尺寸 (14)123.4 根据Allegro Board (wizard)向导制作元件封装 (15)133.5 制作symbol时常遇见的问题及解决方法 (23)144 Cadence易见错误总结 (24)15161 PCB工艺规则以下规则可能随中国国内加工工艺提高而变化171(1)不同元件间的焊盘间隙:大于等于 40mil(1mm),以保证各种批量在1819线焊板的需要。

20(2)焊盘尺寸:粘锡部分的宽度保证大于等于 10mil(0.254mm),如果焊脚(pin)较高,应修剪;如果不能修剪的,相应焊盘应增大…..2122(3)机械过孔最小孔径:大于等于 6mil(0.15mm)。

小于此尺寸将使用激23光打孔,为国内大多数PCB厂家所不能接受。

24(4)最小线宽和线间距:大于等于 4mil(0.10mm)。

小于此尺寸,为国内25大多数 PCB 厂家所不能接受,并且不能保证成品率!26(5)PCB 板厚:通常指成品板厚度,常见的是:0.8mm、1mm、1.2mm、1.6mm、2.0mm;材质为 FR-4。

当然也有其它类型的,比如:陶瓷基板的…2728(6)丝印字符尺寸:高度大于 30mil(0.75mm),线条宽大于 6mil(0.15mm),29高与宽比例3:2(7)最小孔径与板厚关系:目前国内加工能力为:板厚是最小孔径的 8~153031倍,大多数多层板 PCB 厂家是:8~10倍。

Cadence元件封装设计

Cadence元件圭寸装设计、进入封装编辑器要创建和编辑零件封装,先要进入Allegro P ackage封装编辑器界面,步骤如下:1、执行“开始/Cadence/Release 16.3/PCB Editor ”命令,弹出产品选择对话框,如下图,点击Allegro PCB Design GXL 即可进入PCB设计。

.. .... —. . . , . . 4 匕fd 巨"・■■■--U2、在PCB设计系统中,执行File/New 将弹出New Drawing对话框如下图,该对话框中,在Drawing Name中填入新建设计名称,并可点击后面Browse改变设计存储路径;在Temp late栏中可选择所需设计模板;在Drawi ng Type栏中,选择设计的类型。

这里可以用以设计电路板(Board) 、创建模型(Module) ,还可以用以创建以下各类封装:(1) 封装符号(Package Symbol)一般元件的封装符号, 后缀名为*.psm。

PCB 中所有元件像电阻、电容、电感、IC等的圭寸装类型都是Package Symbol;(2) 机械符号(Mechanical Symbol)由板外框及螺丝孔所组成的机构符号,后缀名为*.bsm。

有时设计PCB的外框及螺丝孔位置都是一样的,比如显卡,电脑主板,每次设计PCB时要画一次板外框及确定螺丝孔位置,显得较麻烦。

这时我们可以将PCB的外框及螺丝孔建成一个Mechanical Symbol, 设计PCB时,调用Mechanical Symbol 即可。

(3) 格式符号(Format Symbol)由图框和说明所组成的元件符号,后缀名为*.osm。

(4) 形状符号(Shape Symbol)用以建立特殊形状的焊盘用,后缀为*.ssm。

像金手指封装的焊盘即为一个不规则形状的焊盘, 在建立此焊盘时要先将不规则形状焊盘的形状建成一个Shape Symbol, 然后在建立焊盘中调用此Shape Symbol。

Cadence各层作用及封装信息传输对应关系

Cadence 各层作用及封装信息传输关系(2013-12-20 22:48:04)转载▼silkscreen top:是字符层,一般称顶层字符或元件面字符,为各元器件的外框及名称标识等assemly top :是装配层,就是元器件含铜部分的实际大小,用来产生元器件的装配图。

我自己感觉这一层 如果对于贴片的元器件,如电容,就是两个贴片铜片的实际大小,而place_bound_top 层是整个贴片元器件的实际大小,这一点很多人都没真正搞懂!也可以使用此层进行布局;place_bound_top :是元器件封装实际大小,用来防止两个元器件叠加在一起不报错。

Autosilk top, Silkscreen top 和Assembly topAutosilk top :最后出gerber 的时候,自动生成的丝印层。

会自动调整丝印位置,以及碰到阻焊开窗的地方,丝印会自动消失,避免露锡的地方涂上丝印(一般画丝印层的时候,焊盘上不会画上丝印,所以过孔焊盘上有丝印,也不会有什么影响。

),所以我个人一般很少用到Autosilk top 层,毕竟最后出丝印的时候,都需要调整位置。

我一般直接用Silkscreen top 。

Silkscreen top :建库的时候,ref des 放置的层,及PCB 生产时,刷到板卡上的字符、器件外框或者公司LOGO 等放置的层。

我出gerber ,一般直接出这一层。

Assembly top :安装丝印层。

因为有些公司需要出安装图,有些为了手工焊接,喜欢把字符丝印放置在器件内部,比如电阻位号,喜欢把它的丝印放置在电阻符号外框的中间位置。

比如说电阻值等,想打印出来放置在安装图纸的电阻相应位置。

这时我们才会用到安装丝印层。

平时可以不用,或者平时只用Silkscreen top 。

所以这三个丝印层各有各的作用。

总体来说,cadence 软件定义的这些层使用很灵活,每个人用法可能稍微有差异,都是没关系的,只要实现你的使用目的即可。

cadence 元件封装制作

元件封装制作一、制作焊盘1、打开焊盘制作软件Pad Designer:2、设置参数(parameters):Type:选择焊盘类型:过孔,盲孔/埋孔,表贴;Internal layers:选择内层结构:一般选择optional,盘片设置好后,内层可以更改。

Units:单位选择,精度一般选择3位即可;Multiple:焊盘上打多个小孔,一般用于固定孔;3设置层(layers):padstack layers设置:begin layer:default internal:end layer:soldermask:阻焊层设置:按照标准,一般只需要比正常的焊盘大0.1mm即可;pastemask:助焊层设置:可以在设置好其中某些项后用鼠标右键点击左边的按钮,选择复制操作。

设置完成后存档即完成焊盘制作工程。

二、封装制作1、打开软件窗口打开ORCAD PCB Editor软件,选择ORCAD PCB Dsigner,在File New 菜单中选择package symbol文件文件类型新建工程。

2、设置图纸参数栅格点设置:选择Setup >Design Parameters打开如下对话框在右下勾中Grids on,然后点击Setup Grids按钮,弹出如下对话框,将栅格设置成1mil。

设置图纸大小(仅为制作元件封装时操作方便):3、放置焊盘选择菜单Layout > Pin,然后在窗口右侧选择option,如下图所示:选中Connect表示表示有电器连接,在Padstack中选择需要放置的焊盘,然后在X:和Y:中分别设置焊盘的数量,间距,排放顺序,接着在Pin#:中设置当前焊盘标号,在Inc:设置递增量。

Text block设置标号字体大小。

Offset设置字体相对焊盘中心偏移。

4、画装配线在菜单中选择ADD > Line,然后在右边option对话框中进行如下配置,配置完成后画线。

装配线如下所示,即为元件轮廓线:5、画丝印层在菜单中选择ADD > Line,然后在右边option对话框中进行如下配置,配置完成后画线。

Cadence入门10LQFP贴片封装(实例)

Cadence入门10LQFP贴片封装(实例)1、打开PCB Editor(Allegro PCB Design GXL (legacy))2、file->new 设置如下:Setup->Design Parameter Editor因为芯片数据手册封装尺寸图所用单位为Millimeter,所以这里单位选Millimeter。

网格设置:Setup->Girds0.0254mm=1mil,一般PCB设计以mil为单位添加Pin脚:Layout->pins(option)Connect和mechanical的区别就是一个带电气连接一个不带电气连接,mechanical一般用于固定孔。

Pad stack:添加制作好的贴片焊盘,添加前需进行路径设置,参考flash制作Copy mode:Rectangular 矩形,Polar 极向型,默认即可Qty:一次放置焊盘个数Spacing:相邻Pin脚间距Order:焊盘排列方向Rotation:旋转角度Pin#:Pin脚号根据手册设置如下:1. 62.73.8右键Done 结束说明:所有焊盘分4次放置,第1管脚为坐标原点,其他三次放置主要计算12脚、23脚和34脚的坐标,分别为(1.7 -9.7)、(11.4 -8)、(9.71.7)。

我们希望芯片的管脚中心与焊盘中心对应,查看手册可知D=12mm,L=0.6mm,所以第23脚的X坐标为11.4;由e=0.8mm可知第1脚和11脚的中心距为8mm,所以四个角相邻管脚在X方向和Y方向均相差1.7mm。

综上,可得出我们需要的所有坐标。

4.9添加外框:Add -> Rectangleoption选项上:Package Geometry,下:Place Bound Top命令栏输出两对角坐标:(x -1 2.7 )及( x 12.4 -10.7 )右键Done 结束管脚中心坐标向外1mm,理论上所有管脚均在其内即可。

cadence元件库介绍

Cadence ORCAD CAPTURE元件库介绍-Cadence OrCAD Capture 具有快捷、通用的设计输入能力,使Cadence O rCAD Capture 线路图输入系统成为全球最广受欢迎的设计输入工具。

它针对设计一个新的模拟电路、修改现有的一个PCB 的线路图、或者绘制一个HDL 模块的方框图,都提供了所需要的全部功能,并能迅速地验证您的设计。

OrC AD Capture 作为设计输入工具,运行在PC 平台,用于FPGA 、PCB 和C adence? OrCAD? PSpice?设计应用中,它是业界第一个真正基于Windows 环境的线路图输入程序,易于使用的功能及特点已使其成为线路图输入的工业标准。

本文介绍在Cadence OrCAD Capture 设计的时候,在不同的元件库中,包含的元件资料,都是介绍Cadence OrCAD Capture 本身自带的元件库,所以大家在自己的软件中,都可以看到,方便的选择自己的元件了AMPLIFIER.OLB共182个零件,存放模拟放大器IC,如CA3280,TL027C,EL4093等。

ARITHMETIC.OLB共182个零件,存放逻辑运算IC,如TC4032B,74LS85等。

ATOD.OLB共618个零件,存放A/D转换IC,如ADC0804,TC7109等。

BUS DRIVERTRANSCEIVER.OLB共632个零件,存放汇流排驱动IC,如74LS244,74LS373等数字IC。

CAPSYM.OLB共35个零件,存放电源,地,输入输出口,标题栏等。

CONNECTOR.OLB共816个零件,存放连接器,如4 HEADER,CON AT62,RCA JACK等。

COUNTER.OLB共182个零件,存放计数器IC,如74LS90,CD4040B。

DISCRETE.OLB共872个零件,存放分立式元件,如电阻,电容,电感,开关,变压器等常用零件。