R480CPBB中文资料

HCF40208BEY中文资料

HCC/HCF40208BJune 19894x 4MULTIPORT REGISTERDESCRIPTION.FOUR 4-BIT REGISTERS.ONE INPUT AND TWO OUTPUT BUSES.UNLIMITED EXPANSION IN BIT AND WORD DIRECTIONS.DATA LINES HAVE LATCHED INPUTS .3-STATE OUTPUTS.SEPARATE CONTROL OF EACH BUS,ALLOWING SIMULTANEOUS INDEPENDENT READING OF ANY OF FOUR REGISTERS ON BUS A AND BUS B AND INDEPENDENT WRIT-ING INTO ANY OF THE FOUR REGISTERS .40108B IS PIN-COMPATIBLE WITH INDUS-TRY TYPE MC14580.STANDARDIZED,SYMMETRICAL OUTPUT CHARACTERISTICS.QUIESCENT CURRENT SPECIFIED AT 20V FOR HCC DEVICE.5V,10V,AND 15V PARAMETRIC RATINGS .INPUT CURRENT OF 100nA AT 18V AND 25°C FOR HCC DEVICE.100%TESTED FOR QUIESCENT CURRENT .MEETS ALL REQUIREMENTS OF JEDECTEN-TATIVE STANDARDN °13A,”STANDARD SPE-CIFICATIONS FOR DESCRIPTION OF ”B”SERIES CMOS DEVICES”BEY(Plastic Package)BF(Ceramic Frit Seal Package)BM1(Micro Package )ORDER CODES :HCC40208BF HCF40208BEYHCF40208BM1PIN CONNECTIONSThe HCC40208B (extended temperature range)and HCF40208B (intermediate temperature range)are monolithic integrated circuits,available in 24-lead dual in-line plastic or ceramic package and plastic micro package.The HCC/HCF40208B is a 4x 4multiport register containing four 4-bit registers,write address decoder,two separate read address decoders,and two 3-state output buses.When the ENABLE input is low,the corresponding output bus is switched,inde-pendently of the clock to a high-impedance state.The high-impedance third state provides the outputs with the capability of being connected to the bus lines in a bus-organized system without the need for interface or pull-up components.When the WRITE ENABLE input is high,all data input lines are latched on the positive transition of the CLOCKand the data is entered into the wordselected bythewrite address lines.When WRITE ENABLE is low,the CLOCK is inhibited and no new data isentered.In either case,the contents ofany word may be accessed via the read address lines inde-pendent of the state of the CLOCK input.1/13ABSOLUTE MAXIMUM RATINGSSymbol Parameter Value UnitV DD*Supply Voltage:HCC TypesHCF Types –0.5to+20–0.5to+18VVV i Input Voltage–0.5to V DD+0.5V I I DC Input Current(any one input)±10mAP t o t Total Power Dissipation(per package)Dissipation per Output Transistorfor T o p=Full Package-temperature Range 200100mWmWT o p Operating Temperature:HCC TypesHCF Types –55to+125–40to+85°C°CT s t g Storage Temperature–65to+150°C Stresses above those listed under”Absolute Maximum Ratings”may cause permanent damage to the device.This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied.Exposure to absolute maximum rating conditions for external periods may affect device reliability. *All voltages are with respect to V SS(GND).FUNCTIONAL DIAGRAMRECOMMENDED OPERATING CONDITIONSSymbol Parameter Value UnitV DD Supply Voltage:HCC TypesHCF Types 3to183to15VVV I Input Voltage0to V DD VT o p Operating Temperature:HCC TypesHCF Types –55to+125–40to+85°C°CHCC/HCF40208B 2/13HCC/HCF40208B SCHEMATIC DIAGRAM3/13HCC/HCF40208B LOGIC DIAGRAMTIMING DIAGRAM 4/13STATIC ELECTRICAL CHARACTERISTICS (over recommended operating conditions)Test ConditionsValueV IV O |I O |V D D T L o w *25°CT Hi g h *SymbolParameter (V)(V)(µA)(V)Min.Max.Min.Typ.Max.Min.Max.UnitI LQuiescent CurrentHCC Types 0/5550.045150µA0/1010100.04103000/1515200.04206000/20201000.081003000HCF Types0/55200.04201500/1010400.04403000/1515800.0480600V OHOutput High Voltage 0/5<15 4.95 4.95 4.95V0/10<1109.959.959.950/15<11514.9514.9514.95V OLOutput Low Voltage 5/0<150.050.050.05V10/0<1100.050.050.0515/0<1150.050.050.05V IHInput High Voltage 0.5/4.5<15 3.5 3.5 3.5V1/9<1107771.5/13.5<115111111V ILInput Low Voltage 4.5/0.5<15 1.5 1.5 1.5V9/1<11033313.5/1.5<115444I OHOutput Drive CurrentHCC Types0/5 2.55–2–1.6–3.2–1.15mA0/5 4.65–0.64–0.51–1–0.360/109.510–1.6–1.3–2.6–0.90/1513.515–4.2–3.4–6.8–2.4HCF Types0/5 2.55–1.53–1.36–3.2–1.10/5 4.65–0.52–0.44–1–0.360/109.510–1.3–1.1–2.6–0.90/1513.515–3.6–3.0–6.8–2.4*T Low =–55°C for HCC device :–40°C for HCF device.*T High =+125°C for HCC device :+85°C for HCF device.The Noise Margin for both ”1”and ”0”level is :1V min.with V DD =5V,2V min.with V DD =10V,2.5V min.with V DD =15V.**Forced output disable.TRUTH TABLEClock Write Enable Write 1Write 0Read 1A Read 0A Read 1B Read 0BEnableA EnableB D n Q n A Q n B –/–1S1S2S1S2S1S211111–/–1S1S2S1S2S1S211000X X X X X X X X 00X Z Z –/–11111D n to Word 0Word 1Out Word 2Out –/–000011011Word 0Not Altered Word 1Out Word 2Out X X X X 100111X Word 2Out Word 1Out –\–XXXXXXX11XNCNC1=HIGH LEVEL,0=LOW LEVEL,X =DON’T CARE,Z =HIGH IMPEDANCE.S1and S2refer to input strates of either 1or 0.HCC/HCF40208B5/13STATIC ELECTRICAL CHARACTERISTICS(continued)Test Conditions ValueV I V O|I O|V D D T L o w*25°C T Hi g h*Symbol Parameter(V)(V)(µA)(V)Min.Max.Min.Typ.Max.Min.Max.UnitI OL OutputSinkCurrent HCCTypes0/50.450.640.5110.36mA 0/100.510 1.6 1.3 2.60.90/15 1.515 4.2 3.4 6.8 2.4HCFTypes0/50.450.520.4410.360/100.510 1.3 1.1 2.60.90/15 1.515 3.6 3.0 6.8 2.4I IH,I IL InputLeakageCurrent HCCTypes0/18Any Input18±0.1±10–5±0.1±1µA HCFTypes0/1515±0.3±10–5±0.3±1I O H,I O L**3-StateOutputLeakageCurrent HCCTypes0/180/1818±0.4±10–4±0.4±12µA HCFTypes0/150/1515±1.0±10–4±1.0±7.5C I Input Capacitance Any Input57.5pF *T Low=–55°C for HCC device:–40°C for HCF device.*T High=+125°C for HCC device:+85°C for HCF device.The Noise Margin for both”1”and”0”level is:1V min.with V DD=5V,2V min.with V DD=10V,2.5V min.with V DD=15V. **Forced output disable.DYNAMIC ELECTRICAL CHARACTERISTICS(T amb=25°C,C L=50pF,R L=200kΩ,typical temperature coefficient for all V DD values is0.3%/°C,all input rise and fall time=20ns)Test Conditions ValueSymbol ParameterV D D(V)Min.Typ.Max.Unitt PHL, t P L H Propagation Delay Time:Clock to Write Enable to Q5360720ns1014028015100200Read or Write Address to Q5300600ns101202401585170t PZH, t P HZ 3-state Disable Delay Time5100200ns1050100154080t PZ L, t PL Z 3-State Disable Delay time5130260ns10601201550100t T HL, t T L H Output Transition Time5100200ns1050100154080t s e t u p Setup TimeData to Clock t s(D)50–95ns 100–35150–20Write Enable to Clock t s(WE)5250125ns1010050157035Write Address to Clock t s(WA)5250125ns1010050157035HCC/HCF40208B6/13DYNAMIC ELECTRICAL CHARACTERISTICS(continued)Test Conditions ValueSymbol ParameterV D D(V)Min.Typ.Max.Unit t r,t f Clock Rise and Fall Time515µs105155t h o l d Hold TimeData to Clock t h(D)5220110ns 1010050158040Write Enable to Clock t h(WE)5270135ns1013065158040Write Address to Clock t s(WA)53301651014070159045t W Clock Pulse WidthClock or Write Enable t W(CL)5350175ns 1013065159045Write Address t W(WA)5300150ns1015075159045f CL Maximum Clock Input Frequency5 1.53MHz10 3.5715 4.59Output Low(sink)Current Characteristics.Output High(source)Current Characteristics.HCC/HCF40208B7/13Typical Propagation Delay Time vs.Load Capacit-ance (CL or WE to Q).Typical Transition Time vs.Load Capacitance.TEST CIRCUITSOutput-enable-delay-times and Waveforms.Typical Dynamic Power Dissipation vs.Input Fre-quency.HCC/HCF40208B8/13HCC/HCF40208B Power-d issipation and Waveforms.Quiescent Device Current.Input Voltage.Input Current.9/13HCC/HCF40208BPlastic DIP24(0.25)MECHANICAL DATAmm inch DIM.MIN.TYP.MAX.MIN.TYP.MAX.a10.630.025b0.450.018b10.230.310.0090.012 b2 1.270.050D32.2 1.268 E15.216.680.5980.657e 2.540.100e327.94 1.100F14.10.555I 4.4450.175L 3.30.130P043A 10/13HCC/HCF40208B Ceramic DIP24MECHANICAL DATAmm inchDIM.MIN.TYP.MAX.MIN.TYP.MAX.A32.3 1.272B13.0513.360.5140.526C 3.9 5.080.1540.200D30.118E0.5 1.780.0200.070e327.94 1.100F 2.29 2.790.0900.110G0.40.550.0160.022I 1.17 1.520.0460.060L0.220.310.0090.012M 1.52 2.490.0600.098N14°(min.),15°(max.)P15.415.80.6060.622Q 5.710.225P058C11/13SO24MECHANICAL DATADIM.mm inch MIN.TYP.MAX.MIN.TYP.MAX.A 2.650.104a10.100.200.0040.007a2 2.450.096b 0.350.490.0130.019b10.230.320.0090.012C 0.500.020c145°(typ.)D 15.2015.600.5980.614E 10.0010.650.3930.420e 1.270.05e313.970.55F 7.407.600.2910.299L 0.50 1.270.190.050S8°(max.)FCLEa 1b 1Ae De3b 2413112c1sa 2HCC/HCF40208B12/13HCC/HCF40208B Information furnished is believed to be accurate and reliable.However,SGS-THOMSON Microelectronics assumes no responsability for the consequences of use of such information nor for any infringement of patents or other rights of third parties which may results from its use.No license is granted by implication or otherwise under any patent or patent rights of SGS-THOMSON Microelectronics.Specificationsmentioned in this publication are subject to change without notice.This publication supersedes and replaces all information previously supplied.SGS-THOMSON Microelectronics products are not authorized for use ascritical components in life support devices or systems without express written approval of SGS-THOMSON Microelectonics.©1994SGS-THOMSON Microelectronics-All Rights ReservedSGS-THOMSON Microelectronics GROUP OF COMPANIESAustralia-Brazil-France-Germany-Hong Kong-Italy-Japan-Korea-Malaysia-Malta-Morocco-The Netherlands-Singapore-Spain-Sweden-Switzerland-Taiwan-Thailand-United Kingdom-U.S.A13/13。

CD4050B中文资料

6 I=C

10 J=D

12 K=E

15 L=F

CD4049UB, CD4050B

CD4050B

3 A

5 B

7 C

9 D

11 E

14 F

1 VCC

8 VSS NC = 13 NC = 16

2 G=A

4 H=B

6 I=C

10 J=D

12 K=E

15 L=F

Schematic Diagrams

VCC

VCC 1 G=A 2

A3 H=B 4

B5 I=C 6

C7 VSS 8

16 NC 15 L = F 14 F 13 NC 12 K = E 11 E 10 J = D 9D

CD4050B (PDIP, CERDIP, SOIC, SOP) TOP VIEW

VCC 1 G=A 2

A3 H=B 4

B5 I=C 6

Ordering Information

PART NUMBER CD4049UBF3A CD4050BF3A CD4049UBD CD4049UBDR CD4049UBDT CD4049UBDW CD4049UBDWR CD4049UBE CD4049UBNSR CD4049UBPW CD4049UBPWR CD4050BD CD4050BDR CD4050UBDT CD4050BDW CD4050BDWR CD4050BE CD4050NSR CD4050BPW CD4050BPWR

PACKAGE 16 Ld CERDIP 16 Ld CERDIP 16 Ld SOIC 16 Ld SOIC 16 Ld SOIC 16 Ld SOIC 16 Ld SOIC 16 Ld PDIP 16 Ld SOP 16 Ld TSSOP 16 Ld TSSOP 16 Ld SOIC 16 Ld SOIC 16 Ld SOIC 16 Ld SOIC 16 Ld SOIC 16 Ld PDIP 16 Ld SOP 16 Ld TSSOP 16 Ld TSSOP

AD404M48VCB-5中文资料

ASCEND Semiconductor 4Mx4 EDO Data sheetDescriptionThe device CMOS Dynamic RAM organized as 4,194,304 words x 4 bits with extended data out access mode. It is fabricated with an advanced submicron CMOS technology and designed to operate from a single 3.3V oniy power supply. Low voltage operation is more suitable to be used on battery backup, portable elec-tronic application. lt is packaged in JEDEC standard 26/24-pin plastic SOJ or TSOP(II).Features• Single 3.3V(%) only power supply • High speed t RAC acess time: 50/60ns • Low power dissipation- Active mode : 432/396 mW (Mas) - Standby mode: 0.54 mW (Mas)• Extended - data - out(EDO) page mode access • I/O level: CMOS level (Vcc = 3.3V)• 2048 refresh cycle in 32 ms(Std.) or 128 ms(S-version)• 4 refresh modesh: - RAS only refresh- CAS - before - RAS refresh - Hidden refresh - Self-refresh(S-version)10±Pin Name FunctionA0-A10Address inputs- Row address - Column address - Refresh address DQ1~DQ4Data-in / data-out RAS Row address strobe CAS Column address strobe WE Write enable OE Output enable Vcc Power (+ 3.3V)VssGroundVCC 1DQ12DQ23DQ34DQ45VCC6891011 NC 12 WE 13A0 A117 A218 A319VSS RAS CAS OE A8A7A6A5A4VSSAD404M42VSPin Description Pin Configuration21222324 2526151416 A1026/24-PIN 300mil Plastic SOJA9VCC 1DQ12DQ23DQ34DQ45VCC6891011 NC 12 WE 13A0 A117 A218 A319VSS RAS CAS OE A8A7 A6A5 A4VSSAD404M42VT212223242526151416 A1026/24-PIN 300mil Plastic TSOP (ll)A9A0-A10A0-A10A0-A10WECASNO. 2 CLOCK GENERATORCOLUMN ADDRESS BUFFERS (11)REFRESH CONTROLLERREFRESH COUNTERBUFFERS (11)ADDRESS ROW NO. 1 CLOCK GENERATORA0RASA1A2A3A4A5A6A7A8CONTROLLOGICDATA-IN BUFFERDATA-OUT BUFFEROEDQ1.DQ4.COLUMN DECODER2048SENSE AMPLIFIERSI/O GATING2048x42048x2048x4MEMORY ARRAY2048R O W D E C O D E RVcc VssBlock DiagramA9A10TRUTH TABLENotes: 1. EARLY WRITE only.FUNCTIONRASCAS WE OE ADDRESSESDQ SNotesROW COL STANDBY H X X X X High-Z READL L H L ROW COL Data-Out WRITE: (EARLY WRITE )L L L X ROW COL Data-lnREAD WRITE L L ROW COL Data-Out,Data-ln EDO-PAGE-MODE READ1st Cycle L H L ROW COL Data-Out 2nd CycleL H L n/a COL Data-Out EDO-PAGE MODE WRITE1st CycleL L X ROW COL Data-In 2nd Cycle L L Xn/a COL Data-InEDO-PAGE-MODEREAD-WRITE 1st Cycle L ROW COL Data-Out, Data-In 2nd Cycle L n/a COL Data-Out, Data-In HIDDEN REFRESHREAD L H L ROW COL Data-Out WRITEL L X ROW COL Data-In 1RAS-ONLY REFRESH L H X X ROW n/a High-Z CBR REFRESHLHXXXHigh-ZH X →H L →L H →H L →H L →H L →H L →H L →H L →L H →H L →H L →L H→L H L →→L H L→→H L→Absolute Maximum RatingsRecommended DC Operating ConditionsCapacitanceTa = 25°C, V CC = 3.3V%, f = 1MHz Note: 1. Capacitance measured with effective capacitance measuring method. 2. RAS, CAS = V IH to disable Dout.ParameterSymbol Value Unit Voltage on any pin relative to Vss V T -0.5 to + 4.6V Supply voltage relative to Vss V CC -0.5 to + 4.6V Short circuit output current I OUT 50mA Power dissipation P D 1.0WOperating temperature T OPT 0 to + 70°C Storage temperatureT STG-55 to + 125°CParameter/Condition Symbol3.3 Volt VersionUnitMinTyp MaxSupply VoltageV CC 3.0 3.33.6V Input High Voltage, all inputs V IH 2.0-V CC + 0.3V Input Low Voltage, all inputsV IL-0.3-0.8VParameterSymbol Typ Max Unit Note Input capacitance (Address)C I1 -5pF 1Input capacitance (RAS, CAS, OE, WE)C I2-7pF 1Output capacitance(Data-in, Data-out)C I/O-7pF1, 210±DC Characteristics :(T a = 0 to 70°C, V CC = + 3.3V%, V SS = 0V)Parameter Symbol Test Conditions AD404M42V Unit Notes-5-6Min Max Min MaxOperating current I CC1RAS cyclingCAS, cyclingt RC = min-120-110mA1, 2Standby Current LowpowerS-versionI CC2LVTTL interfaceRAS, CAS = V IHDout = High-Z-0.5-0.5mACMOS interfaceRAS, -0.2VDout = High-Z-0.15-0.15mAStandardpowerversionLVTTL interfaceRAS, CAS = V IHDout = High-Z-2-2mACMOS interfaceRAS,-0.2VDout = High-Z-0.5-0.5mARAS- only refresh current I CC3RAS cycling, CAS = V IHt RC = min-120-110mA1, 2 EDO page mode current I CC4t PC = min-90-80mA1, 3CAS- before- RAS refresh current I CC5t RC = minRAS, CAS cycling-120-110mA1, 2Self- refresh current (S-Version)I CC8 - 550 - 55010±CAS V CC≥CAS V CC≥t RASS100µs≥µADC Characteristics :(T a = 0 to 70°C , V CC = +3.3V %, V SS = 0V)Notes:1. I CC is specified as an average current. It depends on output loading condition and cycle rate when the device is selected. I CC max is specified at the output open condition.2. Address can be changed once or less while RAS = V IL .3. For I CC4, address can be changed once or less within one EDO page mode cycle time.Parameter Symbol Test Conditions AD404M42VUnitNotes-5-6Min MaxMin MaxInput leakage current I LI + 0.3V -55-55Output leakage current I LO + 0.3V Dout = Disable -55-55Output high Voltage V OH I OH = -2mA 2.4- 2.4-V Output low voltage V OLI OL = +2mA-0.4-0.4V10±0V Vin V CC ≤≤µA 0V Vout V CC ≤≤µAAC Characteristics(T a = 0 to + 70°C , V cc = 3.3V %, V ss = 0V) *1, *2, *3, *4Test conditions• Output load: one TTL Load and 100pF (V CC = 3.3V %)• Input timing reference levels:V IH = 2.0V, V IL = 0.8V (V CC = 3.3V %)• Output timing reference levels:V OH = 2.0V, V OL = 0.8V10±10±10±Read, Write, Read- Modify- Write and Refresh Cycles (Common Parameters)ParameterSymbol AD404M42V UnitNotes-5-6Min MaxMin MaxRandom read or write cycle time t RC 84-104-ns RAS precharge timet RP 30-40-ns CAS precharge time in normal mode t CPN 10-10-ns RAS pulse width t RAS 50100006010000ns 5CAS pulse width t CAS 8100001010000ns 6Row address setup time t ASR 0-0-ns Row address hold time t RAH 8-10-ns Column address setup time t ASC 0-0-ns 7Column address hold time t CAH 8-10-ns RAS to CAS delay timet RCD 12371445ns 8RAS to column address delay time t RAD 10251230ns 9Column address to RAS lead time t RAL 25-30-ns RAS hold time t RSH 8-10-ns CAS hold timet CSH 38-40-ns CAS to RAS precharge time t CRP 5-5-ns 10OE to Din delay time t OED 12-15-ns Transition time (rise and fall)t T 150150ns 11Refresh periodt REF -32-32ms Refresh period (S- Version)t REF -128-128ms CAS to output in Low- Z t CLZ 0-0-ns CAS delay time from Din t DZC 0-0-ns OE delay time from Dint DZO-0-nsRead CycleWrite Cycle Parameter SymbolAD404M42V Unit Notes-5-6Min Max Min MaxAccess time from RAS t RAC-50-60ns12 Access time from CAS t CAC-14-15ns13, 14 Access time from column address t AA-25-30ns14, 15 Access time from OE t OEA-12-15nsRead command setup time t RCS0-0-ns7 Read command hold time to CAS t RCH0-0-ns10, 16 Read command hold time to RAS t RRH0-0-ns16 Output buffer turn-off time t OFF012015ns17 Output buffer turn-off time from OE t OEZ012015ns17Parameter SymbolAD404M42V Unit Notes -5-6Min Max Min MaxWrite command setup time t WCS0-0-ns7, 18 Write command hold time t WCH8-10-nsWrite command pulse width t WP8-10-nsWrite command to RAS lead time t RWL13-15-nsWrite command to CAS lead time t CWL8-10-nsData-in setup time t DS0-0-ns19 Data-in hold time t DH8-10-ns19 WE to Data-in delay t WED10-10-nsRead- Modify- Write CycleRefresh Cycle Parameter SymbolAD404M42V Unit Notes-5-6Min Max Min MaxRead-modify- write cycle time t RWC108-133-nsRAS to WE delay time t RWD64-77-ns18 CAS to WE dealy time t CWD26-32-ns18 Column address to WE delay time t AWD39-47-ns18 OE hold time from WE t OEH8-10-nsParameter SymbolAD404M42VUnit Notes -5-6Min Max Min MaxCAS setup time (CBR refresh) t CSR5-5-nsCAS hold time (CBR refresh)t CHR8-10-ns10 RAS precharge to CAS hold time t RPC5-5-ns7 RAS pulse width (self refresh)t RASS100-100-RAS precharge time (self refresh)t RPS90-110-nsCAS hold time (CBR self refresh)t CHS-50--50-nsWE setup time t WSR0-0-nsWE hold time t WHR10-10-nsµsEDO Page Mode CycleEDO Page Mode Read Modify Write CycleParameterSymbol AD404M42VUnit Notes-5-6Min MaxMin MaxEDO page mode cycle timet PC 20-25-ns EDO page mode CAS precharge time t CP 10-10-ns EDO page mode RAS pulse width t RASP 5010560105ns 20Access time from CAS precharge t CPA -30-35ns 10, 14RAS hold time from CAS precharge t CPRH 30-35-ns OE high hold time from CAS high t OEHC 5-5-ns OE high pulse widtht OEP 10-10-ns Data output hold time after CAS low t COH 5-5-ns Output disable delay from WEt WHZ 310310ns WE pulse width for output disable whenCAS hight WPZ7-7-nsParameterSymbol AD404M42V Unit Notes -5-6Min MaxMin MaxEDO page mode read- modify- write cycle CAS precharge to WE delay timet CPW 45-55-ns 10EDO page mode read- modify- write cycle timet PRWC56-68-nsNotes :1. AC measurements assume t T = 2ns.2. An initial pause of 100 is required after power up, and it followed by a minimum of eightinitialization cycles (RAS - only refresh cycle or CAS - before - RAS refresh cycle). If the internal refresh counter is used, a minimun of eight CAS - before - RAS refresh cycles are required.3. In delayed write or read-modify-write cycles, OE must disable output buffer prior to applying data to the device.4. All the V CC and V SS pins shall be supplied with the same voltages.5. t RAS (min) = t RWD (min)+t RWL (min)+t T in read-modify-write cycle.6. t CAS (min) = t CWD (min)+t CWL (min)+t T in read-modify-write cycle.7. t ASC (min), t RCS (min), t WCS (min), and t RPC are determined by the falling edge of CAS .8. t RCD (max) is specified as a reference point only, and t RAC (max) can be met with the t RCD (max) limit.Otherwise, t RAC is controlled exclusively by t CAC if t RCD is greater than the specified t RCD (max) limit. 9. t RAD (max) is specified as a reference point only, and t RAC (max) can be met with the t RAD (max) limit.Otherwise, t RAC is controlled exclusively by t AA if t RAD is greater than the specified t RAD (max) limit. 10. t CRP , t CHR , t RCH , t CPA and t CPW are determined by the rising edge of CAS .11. V IH (min) and V IL (max) are reference levels for measuring timing or input signals. Therefore, transitiontime is measured between V IH and V IL .12. Assumes that t RCD tRCD (max) and t RAD t RAD (max). If t RCD or t RAD is greater than the maximum recommended value shown in this table, t RAC exceeds the value shown. 13. Assumes that (max) and (max).14. Access time is determined by the maximum of t AA , t CAC , t CPA . 15. Assumes that (max) and (max). 16. Either t RCH or t RRH must be satisfied for a read cycle.17. t OFF (max) and t OEZ (max) define the time at which the output achieves the open circuit condition (highimpedance). t OFF is determined by the later rising edge of RAS or CAS.18. t WCS , t RWD , t CWD , and t AWD are not restrictive operating parameters. They are included in the datasheet as electrical characteristics only. If (min), the cycle is an early write cycle and the data out will remain open circuit (high impedance) throughout the entire cycle. If (min),(min), (min) and (min), the cycle is a read-modify-write and the data output will contain data read from the selected cell. If neither of the above sets of conditions is satisfied, the condition of the data output (at access time) is indeterminate.19. These parameters are referenced to CAS separately in an early write cycle and to WE edge in adelayed write or a read-modify-write cycle.20. t RASP defines RAS pulse width in EDO page mode cycles.µs ≤≤t RCD t RCD ≥t RADt RAD ≤t RCD t RCD ≤t RAD t RAD ≥t WCS t WCS ≥t RWD t RWD ≥t CWDt CWD ≥t AWD t AWD ≥t CPW t CPW≥Timing Waveforms• Read Cyclet RC t RASt RPtCRPtCPNtRRHtRCHt OEZ t OFF tOEA tCACt AAtRACt CLZD OUTtRCS t ASR tRAH tASC tCAH tRAD t RALtCAStRSH tRCDt TtCSHRASCASADDRESSWEDQ1~DQ4Note : = don’t care OEt OFFRowColumn= Invalid Dout•Early Write CycletRC t RASt RPt WCHt DSt DHt WCS t RALtCAStRSH tRCDt TtCSHRASCASWEDQ1~DQ4tCRPtASRtRAH tASCtCAH ADDRESSColumnRowtCPND INtRADt RAL• Delayed Write CycletRC t RASt RPt RWL t RCSt CAStRSH tRCDt TtCSHRASCAStASR tRAH tCAHADDRESSColumnRow tASC D INDQ1~DQ4WEtCRPtCPNt DHt DSt OEHt OEDOEt DSOPENt WPt CWL• Read - Modify - Write CycletRWC t RASt RPtRWDt WPtRADtRWL tCAStCWL tRCDt TtCPNRASCASWEtCRP t ASRtRAHtASCtCAHADDRESS Column RowDQ1~DQ4t DHt DSOEtRCStAWD tCWD D INt OEDt OEHt OEZt OEA t CAC t RACt AADQ1~DQ4D OUTOPENtDZCtDZO• EDO Page Mode Read CycletRASPtCPRHt RCStCAStRSH tRCDt OEAtCSHRASCAStASRtRAHtCAHADDRESStCASWEtCRPt CPOEDQ1~DQ4OPENtOEPD OUT 1t PCt CPtCAStCPNtCRPtRADtCAHtASCt ASCtCAHt ASCt RAL Row Column 1t OEAt OEHCtRRH tRCHt RACt AAt AAt AA t CPA t CPA t OEZt OFFt OFFt CACt OEZt CAC t CACt COHD OUT NWE OE Column 2Column N Rowt RPD OUT 2• EDO Page Mode Early Write CycletRASPtRPt WCSt CAStRSH tRCDRASCAStASRtRAHtCAHADDRESStCASWEt CPDQ1~DQ4t PCt CPt CAStCPNtCRP tCAH tASCtASC tCAH tASC Row Column 1t DS WE Column 2Column Nt WCH t WCS t WCH t WCS t WCHt DH t DS t DH t DS t DHD IN 1D IN 2D IN Nt TtCSH• EDO Page Mode Read-Early-Write Cyclet RASPtCPRHt RCStCAStRSH tRCDt OEAtCSHRASCAStASRtRAHtCAHADDRESStCASWEtCRPt CPOEDQ1~DQ4OPENtWEDt PCt CPtCAStCPNtCRPtRADtRAHtASCt ASCtCAHt ASCt RAL Row Column 1tWCStRCHt RACt AAt AAt CPA t DHt WHZt CACt CACt COHWE OE Column 2Column N Rowt RPt CAL tWCHDataDoutput 2Data Input NDataDoutput 1t DStCSH• EDO Page Mode Read-Modify-Write Cyclet RASPt CPRHt RCStCASt WP RASCASt ASRtRAHtCAHADDRESSt CASWEtRCDCPDQ1~DQ4tPRWCt CPtCAStCRPtRADtCAHtASCt ASCtCAH tASC Row Column 1tRWLtRCSt OEDt DZOt CAC WE OEt RPt RAL D OUT 2D OUT ND OUT 1tTt Column NColumn 2Column 1tRWD tAWD tCWDtCWLtRCStCWDtAWD tCPW tCWL tCPW tAWD tCWDtCWL t OEDt OEDt OEHt OEHt OEHt CAC t CAC t OEA t AAt RACt OEZt OEAt AA t CPAt OEZt OEAt AA t CPAt OEZ t DSt DHt WP t DSt DHt WP t DSt DHOPENOPENOPEN D IN 1D IN ND IN 2DQ1~DQ4t DZCt DZOt DZCt DZCt DZO• Read Cycle with WE Controlled Disablet WPZt RCStCAStRCDt TtCSHRASCASt ASRtRAHtCAHADDRESSColumnRow tASCD DQ1~DQ4WEt OEZt DSt WHZOEt RCH t OEA t CACt AAt RACt CLZOUTtRADRASADDRESSt RC t CRPt ASRt RAHt Tt RPCROWt OFFCAS t RASt RPOPENt CRPDQ1~DQ4RASt CSRt WSRt RPt T t RPCt OFFCAS t RASt RPOPENt CRPDQ1~DQ4t RPCt CHRt RASt RPt RCt RCt CHRt CSRt WHRt WSRt WHRWECAS-Before-RAS Refresh CycleRASWEt RPCt OFFt CSRt CHSt WSRCASt RASS t RPSOPENDQ1~DQ4t WHRHigh lmpedance• Hidden Refresh Cyclet RPt RASRASt RCDt CRPADDRESSWEt CHRt CASt RSHt RAHt ASRt ASCt CAHt RAL ROW t RCHt OEZCASDQ1~DQ4t Tt RCSD t RASt RASt RPt RPt RC t RCt RCt RADt RRHt OFF t OFFt OEA t CACt AAt RACCOlumnOUTOE(READ)(REFRESH)(REFRESH)Ordering informationAD404M42VSA-5• AD• Ascend Memory Product • 40 • Device Type• 4M4 • Density and Organization • 2• Refresh Rate, 2: 2K Refresh • V• T: 5V, V: 3.3V• S • Package Type (S : SOJ, T : TSOP II)• A• Version• 5• Speed (5: 50 ns, 6: 60 ns)Part Number Access time PackageAD404M42VSA-5AD404M42VSA-6AD404M42VTA-5AD404M42VTA-650 ns 60 ns 50 ns 60 ns300mil 26/24-Pin Plastic SOJTSOP IIPackaging information • 300 mil, 26/24-Pin Plastic SOJ• 300 mil, 26/24-Pin TSOP II。

CD4040BE中文资料

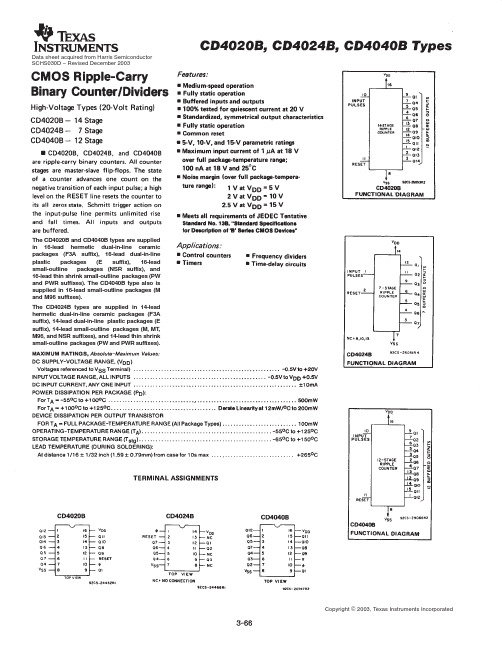

Data sheet acquired from Harris Semiconductor SCHS030D − Revised December 2003The CD4020B and CD4040B types are supplied in 16-lead hermetic dual-in-line ceramic packages (F3A suffix), 16-lead dual-in-line plastic packages (E suffix), 16-lead small-outline packages (NSR suffix), and 16-lead thin shrink small-outline packages (PW and PWR suffixes). The CD4040B type also is supplied in 16-lead small-outline packages (M and M96 suffixes).The CD4024B types are supplied in 14-lead hermetic dual-in-line ceramic packages (F3A suffix), 14-lead dual-in-line plastic packages (E suffix), 14-lead small-outline packages (M, MT, M96, and NSR suffixes), and 14-lead thin shrink small-outline packages (PW and PWR suffixes).IMPORTANT NOTICETexas Instruments Incorporated and its subsidiaries(TI)reserve the right to make corrections,modifications,enhancements, improvements,and other changes to its products and services at any time and to discontinue any product or service without notice. Customers should obtain the latest relevant information before placing orders and should verify that such information is current and complete.All products are sold subject to TI’s terms and conditions of sale supplied at the time of order acknowledgment.TI warrants performance of its hardware products to the specifications applicable at the time of sale in accordance with TI’s standard warranty.Testing and other quality control techniques are used to the extent TI deems necessary to support this warranty.Except where mandated by government requirements,testing of all parameters of each product is not necessarily performed.TI assumes no liability for applications assistance or customer product design.Customers are responsible for their products and applications using TI components.To minimize the risks associated with customer products and applications,customers should provide adequate design and operating safeguards.TI does not warrant or represent that any license,either express or implied,is granted under any TI patent right,copyright,mask work right,or other TI intellectual property right relating to any combination,machine,or process in which TI products or services are rmation published by TI regarding third-party products or services does not constitute a license from TI to use such products or services or a warranty or endorsement e of such information may require a license from a third party under the patents or other intellectual property of the third party,or a license from TI under the patents or other intellectual property of TI. Reproduction of information in TI data books or data sheets is permissible only if reproduction is without alteration and is accompanied by all associated warranties,conditions,limitations,and notices.Reproduction of this information with alteration is an unfair and deceptive business practice.TI is not responsible or liable for such altered documentation.Resale of TI products or services with statements different from or beyond the parameters stated by TI for that product or service voids all express and any implied warranties for the associated TI product or service and is an unfair and deceptive business practice.TI is not responsible or liable for any such statements.TI products are not authorized for use in safety-critical applications(such as life support)where a failure of the TI product would reasonably be expected to cause severe personal injury or death,unless officers of the parties have executed an agreement specifically governing such use.Buyers represent that they have all necessary expertise in the safety and regulatory ramifications of their applications,and acknowledge and agree that they are solely responsible for all legal,regulatory and safety-related requirements concerning their products and any use of TI products in such safety-critical applications,notwithstanding any applications-related information or support that may be provided by TI.Further,Buyers must fully indemnify TI and its representatives against any damages arising out of the use of TI products in such safety-critical applications.TI products are neither designed nor intended for use in military/aerospace applications or environments unless the TI products are specifically designated by TI as military-grade or"enhanced plastic."Only products designated by TI as military-grade meet military specifications.Buyers acknowledge and agree that any such use of TI products which TI has not designated as military-grade is solely at the Buyer's risk,and that they are solely responsible for compliance with all legal and regulatory requirements in connection with such use.TI products are neither designed nor intended for use in automotive applications or environments unless the specific TI products are designated by TI as compliant with ISO/TS16949requirements.Buyers acknowledge and agree that,if they use anynon-designated products in automotive applications,TI will not be responsible for any failure to meet such requirements. Following are URLs where you can obtain information on other Texas Instruments products and application solutions:Products ApplicationsAmplifiers AudioData Converters AutomotiveDSP BroadbandInterface Digital ControlLogic MilitaryPower Mgmt Optical NetworkingMicrocontrollers SecurityLow Power TelephonyWirelessVideo&ImagingWirelessMailing Address:Texas Instruments,Post Office Box655303,Dallas,Texas75265Copyright©2007,Texas Instruments IncorporatedPACKAGING INFORMATIONOrderable Device Status(1)PackageType PackageDrawingPins PackageQtyEco Plan(2)Lead/Ball Finish MSL Peak Temp(3)89271AKB3T OBSOLETE CFP WR16TBD Call TI Call TI89274AKB3T OBSOLETE CFP WR16TBD Call TI Call TICD4020BE ACTIVE PDIP N1625Pb-Free(RoHS)CU NIPDAU N/A for Pkg TypeCD4020BEE4ACTIVE PDIP N1625Pb-Free(RoHS)CU NIPDAU N/A for Pkg Type CD4020BF ACTIVE CDIP J161TBD A42SNPB N/A for Pkg Type CD4020BF3A ACTIVE CDIP J161TBD A42SNPB N/A for Pkg Type CD4020BNSR ACTIVE SO NS162000Green(RoHS&no Sb/Br)CU NIPDAU Level-1-260C-UNLIMCD4020BNSRE4ACTIVE SO NS162000Green(RoHS&no Sb/Br)CU NIPDAU Level-1-260C-UNLIMCD4020BNSRG4ACTIVE SO NS162000Green(RoHS&no Sb/Br)CU NIPDAU Level-1-260C-UNLIMCD4020BPW ACTIVE TSSOP PW1690Green(RoHS&no Sb/Br)CU NIPDAU Level-1-260C-UNLIMCD4020BPWE4ACTIVE TSSOP PW1690Green(RoHS&no Sb/Br)CU NIPDAU Level-1-260C-UNLIMCD4020BPWG4ACTIVE TSSOP PW1690Green(RoHS&no Sb/Br)CU NIPDAU Level-1-260C-UNLIMCD4020BPWR ACTIVE TSSOP PW162000Green(RoHS&no Sb/Br)CU NIPDAU Level-1-260C-UNLIMCD4020BPWRE4ACTIVE TSSOP PW162000Green(RoHS&no Sb/Br)CU NIPDAU Level-1-260C-UNLIMCD4020BPWRG4ACTIVE TSSOP PW162000Green(RoHS&no Sb/Br)CU NIPDAU Level-1-260C-UNLIMCD4024BE ACTIVE PDIP N1425Pb-Free(RoHS)CU NIPDAU N/A for Pkg TypeCD4024BEE4ACTIVE PDIP N1425Pb-Free(RoHS)CU NIPDAU N/A for Pkg Type CD4024BF ACTIVE CDIP J141TBD A42SNPB N/A for Pkg Type CD4024BF3A ACTIVE CDIP J141TBD A42SNPB N/A for Pkg Type CD4024BF3AS2534OBSOLETE CDIP J14TBD Call TI Call TI CD4024BM ACTIVE SOIC D1450Green(RoHS&no Sb/Br)CU NIPDAU Level-1-260C-UNLIMCD4024BM96ACTIVE SOIC D142500Green(RoHS&no Sb/Br)CU NIPDAU Level-1-260C-UNLIMCD4024BM96E4ACTIVE SOIC D142500Green(RoHS&no Sb/Br)CU NIPDAU Level-1-260C-UNLIMCD4024BM96G4ACTIVE SOIC D142500Green(RoHS&no Sb/Br)CU NIPDAU Level-1-260C-UNLIMCD4024BME4ACTIVE SOIC D1450Green(RoHS&no Sb/Br)CU NIPDAU Level-1-260C-UNLIMCD4024BMG4ACTIVE SOIC D1450Green(RoHS&no Sb/Br)CU NIPDAU Level-1-260C-UNLIMCD4024BMT ACTIVE SOIC D14250Green(RoHS&no Sb/Br)CU NIPDAU Level-1-260C-UNLIM CD4024BMTE4ACTIVE SOIC D14250Green(RoHS&CU NIPDAU Level-1-260C-UNLIMOrderable Device Status(1)PackageType PackageDrawingPins PackageQtyEco Plan(2)Lead/Ball Finish MSL Peak Temp(3)no Sb/Br)CD4024BMTG4ACTIVE SOIC D14250Green(RoHS&no Sb/Br)CU NIPDAU Level-1-260C-UNLIMCD4024BNSR ACTIVE SO NS142000Green(RoHS&no Sb/Br)CU NIPDAU Level-1-260C-UNLIMCD4024BNSRE4ACTIVE SO NS142000Green(RoHS&no Sb/Br)CU NIPDAU Level-1-260C-UNLIMCD4024BNSRG4ACTIVE SO NS142000Green(RoHS&no Sb/Br)CU NIPDAU Level-1-260C-UNLIMCD4024BPW ACTIVE TSSOP PW1490Green(RoHS&no Sb/Br)CU NIPDAU Level-1-260C-UNLIMCD4024BPWE4ACTIVE TSSOP PW1490Green(RoHS&no Sb/Br)CU NIPDAU Level-1-260C-UNLIMCD4024BPWG4ACTIVE TSSOP PW1490Green(RoHS&no Sb/Br)CU NIPDAU Level-1-260C-UNLIMCD4024BPWR ACTIVE TSSOP PW142000Green(RoHS&no Sb/Br)CU NIPDAU Level-1-260C-UNLIMCD4024BPWRE4ACTIVE TSSOP PW142000Green(RoHS&no Sb/Br)CU NIPDAU Level-1-260C-UNLIMCD4024BPWRG4ACTIVE TSSOP PW142000Green(RoHS&no Sb/Br)CU NIPDAU Level-1-260C-UNLIMCD4040BE ACTIVE PDIP N1625Pb-Free(RoHS)CU NIPDAU N/A for Pkg TypeCD4040BEE4ACTIVE PDIP N1625Pb-Free(RoHS)CU NIPDAU N/A for Pkg Type CD4040BF ACTIVE CDIP J161TBD A42SNPB N/A for Pkg Type CD4040BF3A ACTIVE CDIP J161TBD A42SNPB N/A for Pkg Type CD4040BM ACTIVE SOIC D1640Green(RoHS&no Sb/Br)CU NIPDAU Level-1-260C-UNLIMCD4040BM96ACTIVE SOIC D162500Green(RoHS&no Sb/Br)CU NIPDAU Level-1-260C-UNLIMCD4040BM96E4ACTIVE SOIC D162500Green(RoHS&no Sb/Br)CU NIPDAU Level-1-260C-UNLIMCD4040BM96G4ACTIVE SOIC D162500Green(RoHS&no Sb/Br)CU NIPDAU Level-1-260C-UNLIMCD4040BME4ACTIVE SOIC D1640Green(RoHS&no Sb/Br)CU NIPDAU Level-1-260C-UNLIMCD4040BMG4ACTIVE SOIC D1640Green(RoHS&no Sb/Br)CU NIPDAU Level-1-260C-UNLIMCD4040BNSR ACTIVE SO NS162000Green(RoHS&no Sb/Br)CU NIPDAU Level-1-260C-UNLIMCD4040BNSRE4ACTIVE SO NS162000Green(RoHS&no Sb/Br)CU NIPDAU Level-1-260C-UNLIMCD4040BNSRG4ACTIVE SO NS162000Green(RoHS&no Sb/Br)CU NIPDAU Level-1-260C-UNLIMCD4040BPW ACTIVE TSSOP PW1690Green(RoHS&no Sb/Br)CU NIPDAU Level-1-260C-UNLIMCD4040BPWE4ACTIVE TSSOP PW1690Green(RoHS&no Sb/Br)CU NIPDAU Level-1-260C-UNLIMCD4040BPWG4ACTIVE TSSOP PW1690Green(RoHS&no Sb/Br)CU NIPDAU Level-1-260C-UNLIMOrderable Device Status(1)PackageType PackageDrawingPins PackageQtyEco Plan(2)Lead/Ball Finish MSL Peak Temp(3)CD4040BPWR ACTIVE TSSOP PW162000Green(RoHS&no Sb/Br)CU NIPDAU Level-1-260C-UNLIMCD4040BPWRE4ACTIVE TSSOP PW162000Green(RoHS&no Sb/Br)CU NIPDAU Level-1-260C-UNLIMCD4040BPWRG4ACTIVE TSSOP PW162000Green(RoHS&no Sb/Br)CU NIPDAU Level-1-260C-UNLIM JM38510/05653BEA ACTIVE CDIP J161TBD A42SNPB N/A for Pkg Type JM38510/05655BCA ACTIVE CDIP J141TBD A42SNPB N/A for Pkg Type (1)The marketing status values are defined as follows:ACTIVE:Product device recommended for new designs.LIFEBUY:TI has announced that the device will be discontinued,and a lifetime-buy period is in effect.NRND:Not recommended for new designs.Device is in production to support existing customers,but TI does not recommend using this part in a new design.PREVIEW:Device has been announced but is not in production.Samples may or may not be available.OBSOLETE:TI has discontinued the production of the device.(2)Eco Plan-The planned eco-friendly classification:Pb-Free(RoHS),Pb-Free(RoHS Exempt),or Green(RoHS&no Sb/Br)-please check /productcontent for the latest availability information and additional product content details.TBD:The Pb-Free/Green conversion plan has not been defined.Pb-Free(RoHS):TI's terms"Lead-Free"or"Pb-Free"mean semiconductor products that are compatible with the current RoHS requirements for all6substances,including the requirement that lead not exceed0.1%by weight in homogeneous materials.Where designed to be soldered at high temperatures,TI Pb-Free products are suitable for use in specified lead-free processes.Pb-Free(RoHS Exempt):This component has a RoHS exemption for either1)lead-based flip-chip solder bumps used between the die and package,or2)lead-based die adhesive used between the die and leadframe.The component is otherwise considered Pb-Free(RoHS compatible)as defined above.Green(RoHS&no Sb/Br):TI defines"Green"to mean Pb-Free(RoHS compatible),and free of Bromine(Br)and Antimony(Sb)based flame retardants(Br or Sb do not exceed0.1%by weight in homogeneous material)(3)MSL,Peak Temp.--The Moisture Sensitivity Level rating according to the JEDEC industry standard classifications,and peak solder temperature.Important Information and Disclaimer:The information provided on this page represents TI's knowledge and belief as of the date that it is provided.TI bases its knowledge and belief on information provided by third parties,and makes no representation or warranty as to the accuracy of such information.Efforts are underway to better integrate information from third parties.TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals.TI and TI suppliers consider certain information to be proprietary,and thus CAS numbers and other limited information may not be available for release.In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s)at issue in this document sold by TI to Customer on an annual basis.TAPE AND REEL INFORMATION*All dimensions are nominalDevicePackage Type Package Drawing Pins SPQReel Diameter (mm)Reel Width W1(mm)A0(mm)B0(mm)K0(mm)P1(mm)W (mm)Pin1Quadrant CD4020BNSR SO NS 162000330.016.48.210.5 2.512.016.0Q1CD4020BPWR TSSOP PW 162000330.012.47.0 5.6 1.68.012.0Q1CD4024BM96SOIC D 142500330.016.4 6.59.0 2.18.016.0Q1CD4024BNSR SO NS 142000330.016.48.210.5 2.512.016.0Q1CD4024BPWR TSSOP PW 142000330.012.47.0 5.6 1.68.012.0Q1CD4040BM96SOIC D 162500330.016.4 6.510.3 2.18.016.0Q1CD4040BNSR SO NS 162000330.016.48.210.5 2.512.016.0Q1CD4040BPWRTSSOPPW162000330.012.47.05.61.68.012.0Q1*All dimensions are nominalDevice Package Type Package Drawing Pins SPQ Length(mm)Width(mm)Height(mm) CD4020BNSR SO NS162000346.0346.033.0 CD4020BPWR TSSOP PW162000346.0346.029.0 CD4024BM96SOIC D142500346.0346.033.0 CD4024BNSR SO NS142000346.0346.033.0 CD4024BPWR TSSOP PW142000346.0346.029.0 CD4040BM96SOIC D162500333.2345.928.6 CD4040BNSR SO NS162000346.0346.033.0 CD4040BPWR TSSOP PW162000346.0346.029.0。

R485CPBB中文资料

Handling Precautions

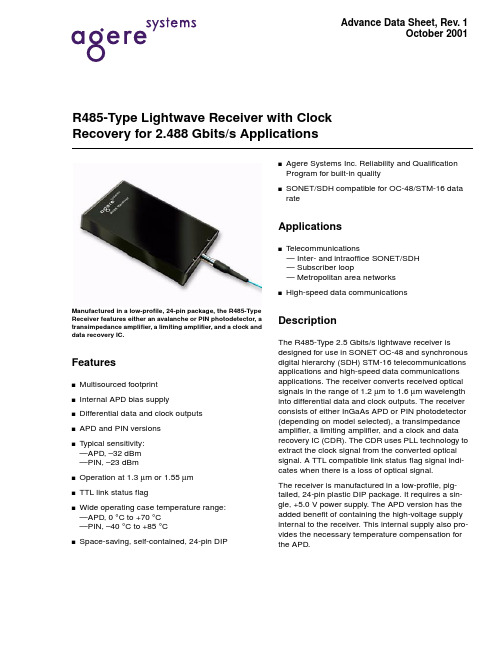

The R485-Type receiver is manufactured with a 39 in. ± 4 in. (100 cm ± 10 cm) single-mode fiber pigtail with a 900 µm OD PVC outer jacket. Both SC and FCPC connectors are offered on standard versions. Other optical connector options are available on special order. Please contact an Agere Systems Account Manager for availability and ordering information.

s SONET/SDH compatible for OC-48/STM-16 data rate

Manufactured in a low-profile, 24-pin package, the R485-Type Receiver features either an avalanche or PIN photodetector, a transimpedance amplifier, a limiting amplifier, and a clock and data recovery IC.

Installation Considerations

Although the receiver has been designed with ruggedness in mind, care should be used during handling. The optical connector should be kept free from dust. The optical connector process cap should be kept in place as a dust cover when the device is not connected to a cable. If contamination is present on the optical connector, the use of canned air with a extension tube should remove any loose debris. Other cleaning procedures are outlined in the Cleaning Fiber Optic Assemblies Technical Note (TN95-010LWP).

广州唯创电子 WTB 系列语音芯片说明书

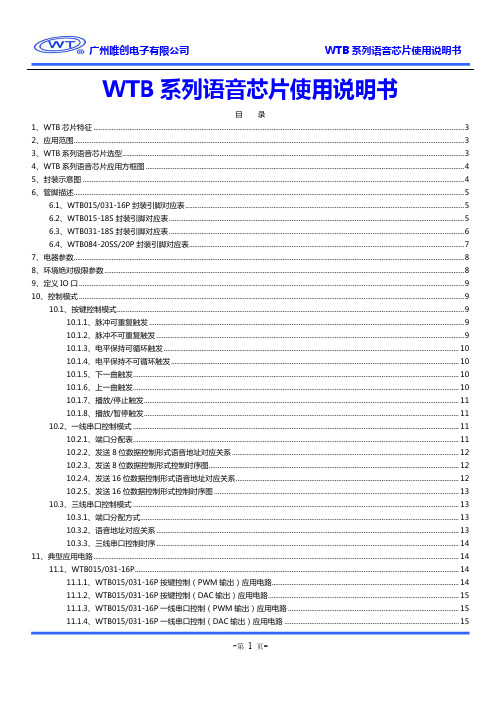

WTB系列语音芯片使用说明书目录1、WTB芯片特征 (3)2、应用范围 (3)3、WTB系列语音芯片选型 (3)4、WTB系列语音芯片应用方框图 (4)5、封装示意图 (4)6、管脚描述 (5)6.1、WTB015/031-16P封装引脚对应表 (5)6.2、WTB015-18S封装引脚对应表 (5)6.3、WTB031-18S封装引脚对应表 (6)6.4、WTB084-20SS/20P封装引脚对应表 (7)7、电器参数 (8)8、环境绝对极限参数 (8)9、定义IO口 (9)10、控制模式 (9)10.1、按键控制模式 (9)10.1.1、脉冲可重复触发 (9)10.1.2、脉冲不可重复触发 (9)10.1.3、电平保持可循环触发 (10)10.1.4、电平保持不可循环触发 (10)10.1.5、下一曲触发 (10)10.1.6、上一曲触发 (10)10.1.7、播放/停止触发 (11)10.1.8、播放/暂停触发 (11)10.2、一线串口控制模式 (11)10.2.1、端口分配表 (11)10.2.2、发送8位数据控制形式语音地址对应关系 (12)10.2.3、发送8位数据控制形式控制时序图 (12)10.2.4、发送16位数据控制形式语音地址对应关系 (12)10.2.5、发送16位数据控制形式控制时序图 (13)10.3、三线串口控制模式 (13)10.3.1、端口分配方式 (13)10.3.2、语音地址对应关系 (13)10.3.3、三线串口控制时序 (14)11、典型应用电路 (14)11.1、WTB015/031-16P (14)11.1.1、WTB015/031-16P按键控制(PWM输出)应用电路 (14)11.1.2、WTB015/031-16P按键控制(DAC输出)应用电路 (15)11.1.3、WTB015/031-16P一线串口控制(PWM输出)应用电路 (15)11.1.4、WTB015/031-16P一线串口控制(DAC输出)应用电路 (15)11.1.5、WTB015/031-16P三线串口控制(PWM输出)应用电路 (16)11.1.6、WTB015/031-16P三线串口控制(DAC输出)应用电路 (16)11.2、WTB015/031-18S (16)11.2.1、WTB015/031-18S按键控制(PWM输出)应用电路 (16)11.2.2、WTB031-18S按键控制(DAC输出)应用电路 (17)11.2.3、WTB015/031-18S一线串口控制(PWM输出)应用电路 (17)11.2.4、WTB015/031-18S一线串口控制(DAC输出)应用电路 (17)11.2.5、WTB015/031-18S三线串口(PWM输出)应用电路 (18)11.2.6、WTB015/031-18S三线串口(DAC输出)应用电路 (18)11.3、WTB084-20SS/20P (19)11.3.1、WTB084-20SS/20P按键控制(PWM输出)应用电路 (19)11.3.2、WTB084-20SS/20P按键控制(DAC输出)应用电路 (19)11.3.3、WTB084-20SS/20P一线串口(PWM输出)应用电路 (19)11.3.4、WTB084-20SS/20P一线串口(DAC输出)应用电路 (20)11.3.5、WTB084-20SS/20P三线串口(PWM输出)应用电路 (20)11.3.6、WTB084-20SS/20P三线串口(DAC输出)应用电路 (20)12、应用范例电路 (21)12.1、电动车应用电路 (21)12.2、定时药盒应用电路 (22)13、控制程序范例 (22)13.1、一线串口(发送8位数据控制形式)控制程序范例 (22)13.2、一线串口(发送16位数据控制形式)控制程序范例 (24)13.3、三线串口控制程序范例 (27)14、封装尺寸 (29)14.1、WTB015/031-16P封装尺寸 (29)14.2、WTB015/031-18S封装尺寸 (30)15、货源信息 (31)16、说明书版本记录 (31)1、WTB芯片特征WTB语音芯片是一款低成本OTP语音芯片;工业级性能,确保产品在多种场合下正常工作;内置音频合成器的4位微型语音处理器及4位数字逻辑运算器;WTB语音芯片完备的内部资源包括EPROM、RAM和I/O端口等;可定义多路输入端和输出端;随意定义控制输入端触发功能;自动休眠功能,有效降低功耗;支持WAV音频和两通道MIDI播放;可工作于4MHz和8MHz两种震荡模式,不同模式下的音频最高采样率分别为14KHz和28KHz;WTB系列语音芯片包括WTB015、WTB031、WTB084、WTB170,其存储时间分别为15秒、31秒、84秒、170秒,目前库存有WTB015、WTB031和WTB084三种;可加载128段语音进行控制播放;单芯片方案,可掩膜投产,降低批量生产成本;支持9bit D/A和8bit PWM输出;工作电压:DC2.2V~5.5V。

4050B中文资料

October 1987Revised January 1999CD4049UBC• CD4050BC Hex Inverting Buffer • Hex Non-Inverting Buffer © 1999 Fairchild Semiconductor Corporation DS005971.prf CD4049UBC • CD4050BCHex Inverting Buffer •Hex Non-Inverting BufferGeneral DescriptionThe CD4049UBC and CD4050BC hex buffers are mono-lithic complementary MOS (CMOS) integrated circuits con-structed with N- and P-channel enhancement modetransistors. These devices feature logic level conversionusing only one supply voltage (V DD). The input signal highlevel (V IH) can exceed the V DD supply voltage when thesedevices are used for logic level conversions. Thesedevices are intended for use as hex buffers, CMOS to DTL/TTL converters, or as CMOS current drivers, and at V DD=5.0V, they can drive directly two DTL/TTL loads over thefull operating temperature range.Featuress Wide supply voltage range: 3.0V to 15Vs Direct drive to 2 TTL loads at 5.0V over full temperatureranges High source and sink current capabilitys Special input protection permits input voltages greaterthan V DDApplications•CMOS hex inverter/buffer•CMOS to DTL/TTL hex converter•CMOS current “sink” or “source” driver•CMOS HIGH-to-LOW logic level converterOrdering Code:Devices also available in Tape and Reel. Specify by appending the suffix letter “X” to the ordering code.Connection DiagramsPin Assignments for DIPCD4049UBCTop ViewCD4050BCTop ViewOrder Number Package Number Package DescriptionCD4049UBCM M16A16-Lead Small Outline Integrated Circuit (SOIC), JEDEC MS-012, 0.150” NarrowCD4049UBCN N16E16-Lead Plastic Dual-In-Line Package (PDIP), JEDEC MS-001, 0.300” WideCD4050BCM M16A16-Lead Small Outline Integrated Circuit (SOIC), JEDEC MS-012, 0.150” NarrowCD4050BCN N16E16-Lead Plastic Dual-In-Line Package (PDIP), JEDEC MS-001, 0.300” Wide 2C D 4049U B C • C D 4050B CSchematic DiagramsCD4049UBC 1 of 6 Identical UnitsCD4050BC1 of 6 Identical UnitsCD4049UBC • CD4050BCAbsolute Maximum Ratings (Note 1)(Note 2)Recommended Operating Conditions (Note 2)Note 1: “Absolute Maximum Ratings” are those values beyond which the safety of the device cannot be guaranteed; they are not meant to imply that the devices should be operated at these limits. The table of “Recom-mended Operating Conditions” and “Electrical Characteristics” provides conditions for actual device operation.Note 2: V SS = 0V unless otherwise specified.DC Electrical Characteristics (Note 3)Note 3: V SS = 0V unless otherwise specified.Supply Voltage (V DD )−0.5V to +18V Input Voltage (V IN )−0.5V to +18V Voltage at Any Output Pin (V OUT )−0.5V to V DD + 0.5V Storage Temperature Range (T S )−65°C to +150°CPower Dissipation (P D )Dual-In-Line 700 mW Small Outline 500 mW Lead Temperature (T L )(Soldering, 10 seconds)260°C Supply Voltage (V DD )3V to 15V Input Voltage (V IN )0V to 15V Voltage at Any Output Pin (V OUT )0 to V DDOperating T emperature Range (T A )CD4049UBC, CD4050BC−40°C to +85°CSymbol ParameterConditions−40°C +25°C +85°C Units MinMax MinTyp Max MinMax I DDQuiescent Device CurrentV DD = 5V 40.03 4.030µA V DD = 10V 80.058.060µA V DD = 15V160.0716.0120µAV OLLOW Level Output VoltageV IH = V DD , V IL = 0V ,|I O | < 1 µA V DD = 5V 0.0500.050.05V V DD = 10V 0.0500.050.05V V DD = 15V0.050.050.05VV OHHIGH Level Output VoltageV IH = V DD , V IL = 0V ,|I O | < 1 µA V DD = 5V 4.95 4.955 4.95V V DD = 10V 9.959.95109.95V V DD = 15V14.9514.951514.95V V ILLOW Level Input Voltage |I O | < 1 µA(CD4050BC Only)V DD = 5V, V O = 0.5V 1.5 2.25 1.5 1.5V V DD = 10V , V O = 1V 3.0 4.5 3.0 3.0V V DD = 15V , V O = 1.5V4.0 6.75 4.0 4.0V V ILLOW Level Input Voltage |I O | < 1 µA(CD4049UBC Only)V DD = 5V, V O = 4.5V 1.0 1.5 1.0 1.0V V DD = 10V , V O = 9V 2.0 2.5 2.0 2.0V V DD = 15V , V O = 13.5V3.03.53.03.0V V IHHIGH Level Input Voltage |I O | < 1 µA(CD4050BC Only)V DD = 5V, V O = 4.5V 3.5 3.5 2.75 3.5V V DD = 10V , V O = 9V 7.07.0 5.57.0V V DD = 15V , V O = 13.5V11.011.08.2511.0V V IHHIGH Level Input Voltage |I O | < 1 µA(CD4049UBC Only)V DD = 5V, V O = 0.5V 4.0 4.0 3.5 4.0V V DD = 10V , V O = 1V 8.08.07.58.0V V DD = 15V , V O = 1.5V12.012.011.512.0V I OLLOW Level Output Current V IH = V DD , V IL = 0V (Note 4)V DD = 5V, V O = 0.4V 4.6 4.05 3.2mA V DD = 10V , V O = 0.5V 9.88.512 6.8mA V DD = 15V , V O = 1.5V29254020mA I OHHIGH Level Output Current V IH = V DD , V IL = 0V (Note 4)V DD = 5V, V O = 4.6V −1.0−0.9−1.6−0.72mA V DD = 10V , V O = 9.5V −2.1−1.9−3.6−1.5mA V DD = 15V , V O = 13.5V−7.1−6.2−12−5mA I INInput CurrentV DD = 15V , V IN = 0V −0.3−0.3−10−5−1.0µA V DD = 15V , V IN = 15V0.30.310−51.0µA 4C D 4049U B C • C D 4050B CDC Electrical Characteristics (Continued)Note 4: These are peak output current capabilities. Continuous output current is rated at 12 mA maximum. The output current should not be allowed to exceed this value for extended periods of time. I OL and I OH are tested one output at a time.AC Electrical Characteristics (Note 5)CD4049UBCT A = 25°C, C L = 50 pF , R L = 200k, t r = t f = 20 ns, unless otherwise specifiedNote 5: AC Parameters are guaranteed by DC correlated testing.AC Electrical Characteristics (Note 6)CD4050BCT A = 25°C, C L = 50 pF , R L = 200k, t r = t f = 20 ns, unless otherwise specifiedNote 6: AC Parameters are guaranteed by DC correlated testing.Symbol ParameterConditions Min Typ Max Units t PHLPropagation Delay Time V DD = 5V 3065ns HIGH-to-LOW LevelV DD = 10V 2040ns V DD = 15V 1530ns t PLHPropagation Delay Time V DD = 5V 4585ns LOW-to-HIGH LevelV DD = 10V 2545ns V DD = 15V 2035ns t THLT ransition Time V DD = 5V 3060ns HIGH-to-LOW LevelV DD = 10V 2040ns V DD = 15V 1530ns t TLHT ransition Time V DD = 5V 60120ns LOW-to-HIGH LevelV DD = 10V 3055ns V DD = 15V 2545ns C INInput CapacitanceAny Input1522.5pFSymbol ParameterConditions Min Typ Max Units t PHLPropagation Delay Time V DD = 5V 60110ns HIGH-to-LOW LevelV DD = 10V 2555ns V DD = 15V 2030ns t PLHPropagation Delay Time V DD = 5V 60120ns LOW-to-HIGH LevelV DD = 10V 3055ns V DD = 15V 2545ns t THLT ransition Time V DD = 5V 3060ns HIGH-to-LOW LevelV DD = 10V 2040ns V DD = 15V 1530ns t TLHT ransition Time V DD = 5V 60120ns LOW-to-HIGH LevelV DD = 10V 3055ns V DD = 15V 2545ns C INInput CapacitanceAny Input57.5pFCD4049UBC • CD4050BCSwitching Time WaveformsTypical ApplicationsCMOS to TLL or CMOS at a Lower V DDV DD1 ≥ V DD2In the case of the CD4049UBC the output drive capability increases with increasing input voltage. E.g., If V DD1 = 10V the CD4049UBC could drive 4 TTL loads. 6C D 4049U B C • C D 4050B CPhysical Dimensionsinches (millimeters) unless otherwise noted16-Lead Small Outline Integrated Circuit (SOIC), JEDEC MS-012, 0.150” NarrowPackage Number M16ACD4049UBC• CD4050BC Hex Inverting Buffer • Hex Non-Inverting Buffer LIFE SUPPORT POLICYFAIRCHILD’S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF THE PRESIDENT OF FAIRCHILD SEMICONDUCTOR CORPORATION. As used herein:1.Life support devices or systems are devices or systemswhich, (a) are intended for surgical implant into the body, or (b) support or sustain life, and (c) whose failure to perform when properly used in accordance with instructions for use provided in the labeling, can be rea-sonably expected to result in a significant injury to the user.2. A critical component in any component of a life supportdevice or system whose failure to perform can be rea-sonably expected to cause the failure of the life support device or system, or to affect its safety or effectiveness.Physical Dimensions inches (millimeters) unless otherwise noted (Continued)16-Lead Plastic Dual-In-Line Package (PDIP), JEDEC MS-001, 0.300” WidePackage Number N16EF a irch ild d o e s n o t a ssu m e a n y re sp o n sib ility fo r u se o f a n y circu itry d e scrib e d, no circu it p a te n t licen se s a re im p lie d an d F a irch ild re se rv e s th e rig h t a t an y tim e w itho u t n o tice to ch a n g e sa id circu itry a n d sp e cificatio n s.。

CM04MC10T中文资料

5

FERRITE PRODUCTS

Inductance decrease 04 30L 05 20L 06 10L

Commom mode choke coilD The maximum DC value having temperature increase within specified temperature,as detailed in individual specification. 4.Impedance Within the specified tolerance Commom mode choke coilD Measuring equipmentDHP 4291A or its equivalent Measuring frequencyDSpecified frequency 5. Inductance Within the specified tolerance Refer to individual specification SMD inductorD Measuring equipmentDHP 4284A or its equivalent Measuring frequencyD1kHz Measuring voltageD1V osc. Measurement in series connection 6.DC Resisitance Within the specified tolerance SMD transformer SMD inductor Commom mode choke coilD Measuring equipmentDDC ohmmeter 7.Self resonance frequency Within the specification SMD inductorD Measuring equipmentDImpedance analyzer fHP 4191A, 4192Ag or its equivalent 8.Temperature characteristic 04, 05, 06 TypeDWithin M10L 08TypeDWithinM5L SMD inductorD Change of maximum inductance deviation in step 1 to 5 Temperature at step 1 Temperature at step 2 Temperature at step 3 Temperature at step 4 Temperature st step 5 20C Minimum operating temperature 20C fStandard temperatureg Maximum oparating temperature 20C

B880 LTE无线网关维修手册V1.1

B880 LTE 无线网关维修手册 V1.0

修订记录

内部公开

日期 2013-04-10

修订版本 V1.0 V1.1

修订原因

初稿完成 根据评审意见修

改

修改章节

修改描述

作者 张帆、周杨

2013-06-07

华为机密,未经许可不得扩散

第 2 页,共 49 页

B880 LTE 无线网关维修手册 V1.0

目录

第 9 章 B880 系统原理及常见故障分析 .......................................................................................................................... 22

9.1 B880 系统框图及原理介绍...................................................................................................................................... 22 9.2 功能单元电路分析及故障排除 ............................................................................................................................... 23

9.2.1 基带单元........................................................................................................................................................................... 23 9.3 维修指导 ................................................................................................................................................................... 33

JUF4802 型 RS485 串口转 PWM 输出调速器 用户手册说明书

*此功能码查询出的信息为调速器根据相关配置实际判断出的风机故障状态, *此功能必须要配合“风机数量”参数及按要求接接风机才能正常使用 以 modbus 地址 01,风机数量为 4;3 号风机故障、124 号风机正常运转 为例 主机发送:01 02 00 01 00 04 28 09 调速器应答:01 02 01 0B E0 4F (0B=1011,也就对应出 3 号风机处于故障状态)

5.4.8 读取全部参数 (03 功能码,寄存器地址 0000~000B) 指令格式:01 03 00 00 00 0C 45 CF (0000:寄存器起始地址,000C:读取 12 个寄存器) 调速器返回: 01 03 18 00A8 0001 0001 0014 465A 0001 0004 0276 0000 0000 0000 0005 CB77 18:返回数据长度,共 24 个字节 00A8 对应寄存器 0000 的值,0001 对应寄存器 0001 的值,以此类推…

3.产品尺寸:

3.1,主板 70mm*46mm,安装孔尺寸:63mm*40mm

3

成都兢志成电子科技有限公司

4.接口说明

tel:028-66570969/18227618314

1 号端子:调速器供电电源﹢极接口(DC12~60V) 2 号端子:调速器供电电源 -极接口 3 号端子:RS485 串口 A / D+, 4 号端子:RS485 串口 B / D-, (5~8 号端子为第 1 路风机的 4 个接线端口,和 14 号端子的 4 针是直通的) 5 号(F1v-):接 1 号风机的电源线-,6 号(F1v+):接 1 号风机的电源线+, 7 号(F1-S):接 1 号风机的转速信号线,8 号(F1-P):接 1 号风机的 PWM 转速控制线, 13 号位置:LED 指示灯,POW 为整机电源指示灯,FAN 为 PWM 输出指示灯 14~17 号接口:第 1~4 路风机接口,标准 2510-4P 座子(线序:V-,V+,S=FG,P=PWM) *9~12 号为预留端口,不需接线 *全功能接线示意图: *直流电源的电压必须和所接风扇的额定电压一致,且输出电流必须大于风扇电流的总和 *尽可能的不要带电插拔风扇

神舟优雅 A480B参数

400-106-9999纠错

电话备注

8:00-18:00纠错

详细内容

神舟家用笔记本电脑实行硬件故障送修服务的保修方式。用户自购机之日起(以正式购机发票为准)有限保修期内,您所购买的神舟家用笔记本出现任何非人为硬件故障时,都将得到神舟电脑或神舟授权服务站的维修服务。神舟将为您所购买产品的主要部件提供3年免费保修服务,随机电池提供6个月免费保修服务。进入官网>>纠错

摄像头:集成摄像头130万像素

光驱类型:DVD刻录机支持DVD SuperMulti...

无线网卡:支持802.11b/g/n无线协议

有线网卡:100Mbps网卡

上市时间:2013年07月

产品定位:全1

电源适配器x1

电源线x1

说明书x1

保修卡x1

售后服务

保修政策:

屏幕尺寸:14英寸纠错

屏幕比例:16:9纠错

屏幕分辨率:1366x768纠错

背光技术:LED背光纠错

显卡

显卡类型:核芯显卡纠错

显卡芯片:Intel GMA HD 4000纠错

显存容量:共享内存容量纠错

显存类型:无纠错

DirectX:11纠错

多媒体设备

摄像头:集成摄像头纠错

音频系统:内置音效芯片纠错

扬声器:立体声扬声器纠错

加入对比栏+复制表格|复制图文混排表格

基本参数

上市时间:2013年07月纠错

产品类型:家用纠错

产品定位:全能学生本纠错

主板芯片组:Intel HM70纠错

处理器

CPU系列:英特尔赛扬双核纠错

CPU型号:Intel赛扬双核1005M纠错

CPU主频:1.9GHz纠错

AO4404B中文资料

SymbolTyp Max 374570100R θJL 2636Maximum Junction-to-AmbientASteady-State °C/W Maximum Junction-to-LeadCSteady-State°C/WThermal Characteristics ParameterUnits Maximum Junction-to-Ambient AFt ≤ 10s R θJA °C/W AO4404BAO4404BSymbolMin TypMaxUnits BV DSS 30V 0.0021T J =55°C5I GSS 100nA V GS(th)0.711.5V I D(ON)40A 1824T J =125°C25302230m Ω3248m Ωg FS 1026S V SD 0.711V I S4.5A C iss 9001100pF C oss 88pF C rss 65pF R g0.95 1.5ΩQ g 1012nC Q gs 1.8nC Q gd 3.75nC t D(on) 3.2ns t r 3.5ns t D(off)21.5ns t f 2.7ns t rr 16.820ns Q rr812nCTHIS PRODUCT HAS BEEN DESIGNED AND QUALIFIED FOR THE CONSUMER MARKET. APPLICATIONS OR USES AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS ARE NOT AUTHORIZED. AOS DOES NOT ASSUME ANY LIABILITY ARISING OUT OF SUCH APPLICATIONS OR USES OF ITS PRODUCTS. AOS RESERVES THE RIGHT TO IMPROVE PRODUCT DESIGN,FUNCTIONS AND RELIABILITY WITHOUT NOTICE.Gate resistanceV GS =0V, V DS =0V, f=1MHzm ΩV GS =4.5V, I D =8.5A I S =1A,V GS =0V V DS =5V, I D =5ATurn-Off Fall TimeMaximum Body-Diode Continuous CurrentInput Capacitance Output Capacitance Turn-On DelayTime DYNAMIC PARAMETERS I F =5A, dI/dt=100A/µs V GS =0V, V DS =15V, f=1MHz SWITCHING PARAMETERS Total Gate Charge V GS =4.5V, V DS =15V, I D =8.5AGate Source Charge Gate Drain Charge Turn-On Rise Time Turn-Off DelayTime V GS =10V, V DS =15V, R L =1.8Ω, R GEN =6ΩR DS(ON)Static Drain-Source On-ResistanceForward TransconductanceDiode Forward Voltage I DSS µA Gate Threshold Voltage V DS =V GS I D =250µA V DS =24V, V GS =0VV DS =0V, V GS = ±12V Zero Gate Voltage Drain Current Gate-Body leakage current Electrical Characteristics (T J =25°C unless otherwise noted)STATIC PARAMETERS ParameterConditions Body Diode Reverse Recovery Time Body Diode Reverse Recovery ChargeI F =5A, dI/dt=100A/µsDrain-Source Breakdown Voltage On state drain currentI D =250µA, V GS =0V V GS =2.5V, I D =5AV GS =4.5V, V DS =5V V GS =10V, I D =8.5AReverse Transfer Capacitance A: The value of R θJA is measured with the device mounted on 1in 2 FR-4 board with 2oz. Copper, in a still air environment with T A =25°C. The value in any given application depends on the user's specific board design. B: Repetitive rating, pulse width limited by junction temperature.C. The R θJA is the sum of the thermal impedence from junction to lead R θJL and lead to ambient.D. The static characteristics in Figures 1 to 6 are obtained using <300 µs pulses, duty cycle 0.5% max.E. These tests are performed with the device mounted on 1 in 2 FR-4 board with 2oz. Copper, in a still air environment with T A =25°C. The SOA curve provides a single pulse rating.F. The current rating is based on the t ≤ 10s junction to ambient thermal resistance rating.Rev0: Feb 2007AO4404BAO4404B。

多功能宽带路由器 TL-R480

1

l 端口支持自动协商功能,自动调整传输方式和传输速度 l 端口支持 Auto-MDI/MDIX 自动翻转 l 内建路由器工作指示灯 l 安装方式:可以架设于桌面或悬挂于墙上

l 外置电源适配器:电源输出 170-240V~50-60Hz ,0.1A l 使用环境:工作温度:0ºC - 40ºC;工作湿度:5% - 90% RH

l 提供 1 个 10M/100M 以太网(WAN)接口,可接 xDSL 或以太网

l 提供 4 个 10M/100M 以太网(LAN)接口,与内部局域网连接 l 符合 IEEE 802.3 Ethernet 以及 IEEE 802.3u Fast Ethernet 标准 l 支持 TCP/IP、PPPoE、DHCP、ICMP、NAT 协议 l 流控方式:全双工采用 IEEE 802.3x 标准,半双工采用 Backpressure 标准

软件特性

l 宽频分享:支持 xDSL 接入,或以太网接入,实现多台计算机共享上网 l 防火墙保护:路由器可设置不同的过滤规则,过滤来自外网的所有异常的信息包,使内部网络使用

者可以安心上网,无须担心遭受网络黑客入侵 l 即插即用:具有 DHCP Server 功能,无须作额外的 IP 地址设定 l 支持访问控制功能:允许为不同的用户设置不同的访问权限 l 支持虚拟服务器:提供架设服务器功能,可指定内部局域网络的特定主机为 Web、Mail、FTP 等类

型的服务器 l 支持 VPN Pass-through l 特殊应用:具有网络游戏端口、MSN 语音功能 l 支持 DMZ 主机:允许一台计算机完全暴露给 Internet,实现完全的 Internet 访问 l 灵活的定时控制:具有定时开启和关闭上网功能 l 按需连接,自动掉线:可以根据上网动作自动连通和断开上网连接 l 访问控制:管理员可以控制局域网内所有计算机的上网权限,支持 MAC 地址绑定 l 内置静态路由功能 l 支持域名过滤和 MAC 地址过滤 l 远程管理:管理员可利用 Internet 联机设定或操作路由器 l 支持在线升级管理软件 l 全中文配置界面,易于配置和管理

SC802B资料

SPECIFICATION OF SC802BCONTENT1. General description --------------------------------------------------------------------------32. Maximum absolute limit---------------------------------------------------------------------33. Mechanical characteristics------------------------------------------------------------------3a) Physical datab) External dimensions4. Electrical characteristics---------------------------------------------------------------------4a) DC characteristicsb) AC characteristicsc) EL backlightd) LED backlight5. Operating Principles--------------------------------------------------------------------------6a) Pin descriptionb) Block diagramc) Instruction description6. Operating Methods---------------------------------------------------------------------------13a) Interface with MPUb) Power supplyc) Operating example1.General descriptionSC802B, a dot-matrix character LCD module, design for displaying 2 line 8 row characters. Character font is 5X7 dots with cursor. The SC802B provides two types of interfaces to MPU: 4-bitSC802B can includes EL or LED backlight for custom design. The custom can design for color of EL or LED backlight, viewing angle and LCD type.2. Maximum absolute limitRatings RemarkCharacteristics SymbolOperating Voltage V DD-0.3V to +7.0VDriver Supply Voltage V LCD VDD - 12V to VDD + 0.3VInput Voltage Range V IN-0.3V to VDD + 0.3VT A1-10°C to+60°C Normal temperature LCM Operating TemperatureT a2-20°C to+60°C Wide temperature LCMto+70°CStorage Temperature T STO -25°CNote: Stresses beyond those given in the Absolute Maximum Rating table may cause operational errors or damage to the device.3. Mechanical characteristics4. Electrical characteristicsa) DC characteristicsa.1) DC CHARACTERISTICS (TA =25 °C, VDD = 2.7 to 4.5V)Limit Characteristics Symbol Min. Typ. Max.Unit Test ConditionInput High Voltage V Im 0.7VDD- VDD VInput Low Voltage V lL -0.3 0.55 VInput High Current I Ih -1.0 1.0 uAInput Low Current I lL -5.0 -15 -30 uAVDD = 3.0V Output High Voltage V oh 0.75VDD - - V IOH = - 0.1mA Pins: DB7-0 Output Low Voltage V OL - - 0.2VDD v |OL = 0.1mA Pins: DB7-0 LCD Voltage V lcd 3 4.5v 13 V Operating CurrentI dd1.0 mANote: VDD = 3Va.2) DC CHARACTERISTICS (TA = 25°C, VDD = 4.5 to 5.5V)Limit Characteristics Symbol Min. Typ. Max.Unit Test ConditionInput High Voltage V Im 2.2 VDD V Input Low Voltage V lL -0.3 0.6 VInput High Current I Ih -2.0 2.0 uA Input Low Current I lL -20 -50 -100 uAVDD = 5.0VOutput High Voltage V oh 2.4 - VDD V I OH = - 0.1mA Pins: DB7-0 Output Low Voltage V OL - - 0.4 V I OL = 0.1mA Pins: DB7-0 LCD Voltage V lcd 3 4.5 13 V Operating CurrentI dd1.0 mANote: VDD = 5Vb) AC characteristicsb.1) AC CHARACTERISTICS (TA = 25°C, VDD = 2.7 to 4.5V) Write Mode (Writing data from MPU to LCD module) Limit Characteristics Symbol Min. Typ. Max.Unit Test Condition E Cycle Time tc 1000 ns PinE E Pulse Width tpw 450 - - ns PinE E Rise/Fall Time tR,tF - - 25 ns PinEAddress Setup Time tsp-i 60 ns Pins: RS, R/W, E Address Hold Time tHD1 20 ns Pins: RS, R/W, E Data Setup Time tsP2 195 ns Pins: DB7-0Data Hold Time tHD210--nsPins: DB7-0Read Mode (Reading data from LCD module to MPU)LimitCharacteristics SymbolMin.Typ.Max.Unit Test Condition E Cycle Time tc 1000ns PinE E Pulse Width tw 450ns PinE E Rise/Fall Time tR,tF 25ns PinE Address Setup Time tsp-i 60ns Pins: RS, R/W,E Address Hold Time tHD1 20ns Pins: RS, R/W,E Data Output Delay Time tD 360ns Pins: DB7-0 Data hold time tHD2 5.0--ns Pin DB7- 0 b.2) AC CHARACTERISTICS (ta = 25°C, VDD = 4.5 to 5.5V) Write Mode (Writing Data from MPU to LCD module)Limit Characteristics SymbolMin. Typ. Max. UnitTest ConditionE Cycle Time tc 400ns PinE E Pulse Width tpw150 - - ns PinE E Rise/Fall Time tR,tF- - 25 ns PinE Address Setup Time tsp-i30 ns Pins: RS, R/W, E Address Hold TimetHD1 10 ns Pins: RS, R/W, E Data Setup TimetsP2 40 ns Pins: DB7-0 Data Hold Time tHD210--ns Pins: DB7-0 Read Mode (Reading Data from LCD module to MPU)Limit Characteristics SymbolMin.Typ. Max. Unit Test ConditionE Cycle Time tc 400ns Pin E E Pulse Width tw 150 ns Pin EE Rise/Fall Time tR,tF 25 ns Pin EAddress Setup Timetsp-i 30 ns Pins: RS, R/W,E Address Hold Time tHD1 10ns Pins: RS, R/W,E Data Output Delay Time tD 100 ns Pins: DB7-0 Data hold timetHD220 - - ns Pin DB7-05. Operating Principlesa) Pin descriptionPin NO. Symbol Level Function1 DB6 H/L2 DB7 H/LData bits3 DB4 H/L4 DB5 H/L5 R/W H/L H: Read signal L: Write signal6 E H→L enable signal7 V0 H/L Variable voltage for LCD8 RS H/L H: Instruction code L: Data9 VSS 0V Ground10 VDD 2.7V~5.5V Supply voltage for logic11 A 4.2V Supply voltage for LED-Backlight12 K 0V Supply voltage for LED-Backlighta. Data Register (DR): Dris a register used for temporary Storage of the data read/write form/into DDRAM and CG RAM.b. Instruction Register (IR): is a register available for storing the instruction codes and addressinformation of display data (DD) RAM and character generator (CG) RAM.c. BUSY FLAG (BF): When the Busy Flag is “1”,it shows that LCM is in internal operation and it cannot accept the next instruction.d. Character Generator (CG) ROM: This ROM Generates character pattern from 8-bit character codeand provides 192 character patterns.e. Character Generator (CG)RAM: This RAM allows the user to rewrite the character patterns freelyaccording to the program.f. Address Counter (AC): This address counter is used to give the address information of DD RAMand CG RAM.g. Display Data (DD) RAM: This display data RAM is used to store the display data expressed by 8-bitcharacter code . The capacity is 80x 8bits and data for 80 characters can be storage.h. Cursor and Blink Control Circuit: This circuit generates the cursor and blink.RAM's address and the LCD's position shown bellows. Display Character address code: Display position 1 2 3 4 5 6 7 8 9 101112 13 14151600 01 02 03 0405060708090A 0B 0C 0D 0E 0F DDRAM Address40 41 42 43 4445464748494A4B 4C 4D4E4FRelationship between Character Code (DDRAM) and character Pattern (CGRAM)Character code DD RAM DataCG RAM Address Character Pattern CG RAM Data B7 B6 B5 B4 B3 B2 B1 B0 B5B4B3B2B1B0B7B6B5 B4 B3 B2B1B0000 1 1 1110010 0 1000100 0 1000110 0 1001000 0 1001010 0 1001100 0 1000 0 0 0 x 0111xxx0 0 000000011100010 0 1000100 0 1000110 0 1001000 0 1001010 0 100110011100 0 0 0 x 011111xxx0 0 01. ▆ It means that the bit0~2 of the character code correspond to the bit3~5 of the CG RAM address.2. ▆ these areas are not used for display, but can be used for the general data RAM.3. When all of the bit4-7 of the character code is 0, CG RAM character patterns are selected.4. " 1 ": Selected," 0 ": No selected," X": Do not care (0 or 1).5. for example (1), to set character code (b2 = b1 = b0 = 0, b3 = 0 or 1, b7-b4 = 0) is to display" T". That means character code (00)16, and (08)16 can display" T” character.6. The bits 0-2 of the character code RAM is character pattern line position. The 8th line is the cursor position and display is formed by logical OR with the cursorSC802B VER2.1SC802B VER2.1c) Instruction descriptionControl and display instructions will show in details as following:c.1) Clear DisplayRS R/W D7 D6 D5 D4 D3 D2 D1 D00 0 0 0 0 0 0 0 0 1It clears the whole display and sets display data RAM's address 0 in address counter.c.2) Return HomeRS R/W D7 D6 D5 D4 D3 D2 D1 D00 0 0 0 0 0 0 0 1 XX: Do not care (0 or 1)It sets display data RAM's address 0 in address counter and display returns to its original position. The cursor or blink goes to the left edge of the display (to the 1st line if 2 lines are displayed). The contents of the Display Data RAM do not change.c.3) Entry Mode SetDuring writing and reading data, it sets cursor move direction and shifts the display.RS R/W D7 D6 D5 D4 D3 D2 D1 D00 0 0 0 0 0 0 1 I/D SI/ D = 1: Increment, I / D = 0: Decrement.S = 1: The display shift, S = 0: Thedisplay does not shiftS= 1 I/D= 1 It shifts the display to the leftS= 1 I/D=0 It shifts the display to the rightc.4) Display On/Off ControlRS R/W D7 D6 D5 D4 D3 D2 D1 D00 0 0 0 0 0 1 D C BD = 1: Display on, D = 0: Display offC = 1: Cursor on , C = 0: Cursor offB = 1: Blinks on, B= 0: Blinks offc.5) Cursor or Display ShiftWithout changing DD RAM's daters, it can move cursor and shift displayRS R/W D7 D6 D5 D4 D3 D2 D1 D00 0 0 0 0 1 S/C R/L X XCounterS/C R/L Description Address0 0 Shift cursor to the left AC = AC - 10 1 Shift cursor to the right AC = AC + 11 0 Shift display to the left. Cursor follows the display shift AC=AC1 1 Shift display to the right. Cursor follows the display shift AC=ACc.6) Function SetRS R/W D7 D6 D5 D4 D3 D2 D1 D00 0 0 0 1 DL N F X XX: Do not care (0 or 1)DL: It sets interface data length.DL = 1: Datas are transferred with 8-bit lengths (DB7 - 0).DL = 0: Datas are transferred with 4-bit lengths (DB7 - 4). (It needs two times to transfer datas) N: It sets the number of the display line. N = 0: One-line display. N = 1: Two-line display. F: It sets the character font. F = 0: 5 x 7 dots character font.F = 1: 5 x 10 dots character font.N F No. of Display Lines Character Font Duty Factor0 0 1 5X7 dots 1 /80 1 1 5x 10 dots 1 /111 X2 5x7 dots 1 /16c.7) Set Character Generator RAM AddressRS R/W D7 D6 D5 D4 D3 D2 D1 D00 0 0 1 a a a a a aIt sets character generator RAM address (aaaaaa)2 to the address counter. Character generator RAM data can read or write after this setting.c.8) Set Display Data RAM AddressRS R/W D7 D6 D5 D4 D3 D2 D1 D00 0 1 a a a a a a aIt sets display data RAM address (aaaaaaa)2 to the address counter.Display data RAM can read or write after this setting.In one-line display (N = 0), (aaaaaaa)2; (OO)16 - (4F)16In two-line display (N = 1), (aaaaaaa)2: (00)16 - (27)16,gfor the first line,(aaaaaaa)2: (40)16 - (67)16,gfor the second line.c.9) Read Busy Flag and AddressRS R/W D7 D6 D5 D4 D3 D2 D1 D00 1 BF a a a a a a aWhen (BF = 1) indicates that the system is busy now, it will not accept any instruction until no busy (BF = 0). At the same time, the address counter content’s (aaaaaaa)2; is read out.c.10) Write Data to Character Generator RAM or Display Data RAMRS R/W D7 D6 D5 D4 D3 D2 D1 D01 0 d d d d d d d dIt writes data (dddddddd)2 to character generator RAM or display data RAM.c.11) Read Data from Character Generator RAM or Display Data RAMRS R/W D7 D6 D5 D4 D3 D2 D1 D01 1 d d d d d d d dIt reads data (dddddddd)2 from character generator RAM or display data RAM. To get the correct data readout is shown below:(ⅰ)Set the address of the character generator RAM or display data RAM or shift the cursor instruction.(ii) Send the “Read “instruction.Instruction tableInstruction CodeInstruction RS RW D7D6D5D4D3D2D1D0Description Execution time (fosc=270KHz)Clear Display 0000000001Write "20H" to DDRAM andset DDRAM address to"OOH" from AC1.52msReturn Home 000000001-Set DDRAM address to"OOH" from AC and returncursor to its originalposition if shifted. Thecontents of DDRAM arenot changed.1.52msEntry Mode Set 00000001I/D S Assign cursor movingdirection and enable theshift of entire display38usDisplay ON/ OFF 0000001D C B Set display(D), cursor(C),and blinking of cursor(B)on/off control bit.38usCursor or Display Shift 000001S/C R/L--Set cursor moving anddisplay shift control bit,and the direction, withoutchanging of DDRAM data.38usFunction Set 00001DL N F--Set interface data length(DL: 8-bit/4-bit), numbersof display line (N: 2-line/1-line) and, display font type(F:5x10dots/5x8dots)38usSet CGRAM Address 0001AC5AC4AC3AC2AC1ACO Set CGRAM address inaddress counter.38usSet DDRAM Address 001AC6AC5AC4AC3AC2AC1ACO Set DDRAM address incounter38usRead Busy Flag and Address Counter 01BF AC6AC5AC4AC3AC2AC1ACO Whether during internaloperation or not can beknown by reading BF.The contents of addresscounter can also be read.38usWrite Data toRAM 10D7D6D5D4D3D2D1DO Write data into internalRAM (DDRAM/CGRAM).38usRead Data from RAM 11D7D6D5D4D3D2D1DO Read data from internalRAM (DDRAM/CGRAM).38usc) Operating example4-Bit operation and 8-digit 1-line display (using internal reset)No Instruction Display Operation 1 Power on . ( SPLC780A1 starts initializing )Power on reset. No display. Function set RS R/W D7 D6 D5 D420 0 0 0 1 0Set to 4-bit operationFunction set 0 0 0 0 1 0 3 0 0 0 0 X XSet to 4-bit operation and select 1-line display line and character font.Display on / off control 0 0 0 0 0 0 4 0 1 1 1 0 0_ Display on. Cursor appears.Entry mode set 0 0 0 0 0 0 50 0 1 1 0 0 _Increase address by one. It will shift the cursor to the right when writing to the DD RAM / CG RAM. Now the display has no shift. Write data to CG RAM / DD RAM1 0 0 1 0 161 0 0 1 1 1W_Write “W “. The cursor is incremented by one and shifted to the right.Reset functionAt power on, it starts the internal auto-reset circuit and executes the initial instructions . There are the initial procedures shown as bellows:。

MIC809_05中文资料

MIC810

3 VCC

MIC809 3-Lead SOT23 MIC809 3-Lead SC70

MIC810 3-Lead SOT23 MIC810 3-Lead SC70

Pin Description

Pin Number MIC809 1 2 Pin Number MIC810 1 N/A Pin Name GND /RESET Pin Function IC Ground Pin. /RESET goes low if VCC falls below the reset threshold and remains asserted for one reset timeout period (140ms min.) after VCC exceeds the reset threshold. RESET goes high if VCC falls below the reset threshold and remains asserted for one reset timeout period (140ms min.) after VCC exceeds the reset threshold. Power Supply Input.

Features

• Precision voltage monitor for 3V, 3.3V or 5V power supplies • /RESET remains valid with VCC as low as 1.4V for SOT23 packaged part • /RESET remains valid with VCC as low as 1V for SC70 packaged part • Typically less than15µA supply current for SOT-23 packaged part • 5µ typical supply current for SC70 packaged part • 140ms minimum reset pulse widths available • Available in 3-pin SOT-23 and SC-70 package

联想天工 R4802路由器 硬件安装手册

联想天工R4802路由器硬件安装手册目录第1章产品概述 (1)1.1 产品简介 (1)1.2 技术特性 (1)1.3 产品规格 (2)1.3.1 硬件性能指标 (2)1.4 ROHS说明 (3)第2章天工R4802的介绍 (4)2.1 天工R4802外观说明 (4)2.1.1 机箱 (4)2.1.2 主板说明 (4)2.1.3 电源分布 (4)2.2 R4802通风散热系统 (5)2.3 R4802面板简介 (5)2.3.1 前面板 (5)2.3.2 后面板 (6)第3章安装前准备 (8)3.1 安全性建议 (8)3.1.1 安装系统的安全 (8)3.1.2 搬移的安全 (8)3.1.3 电气安全性 (8)3.1.4 激光安全性 (9)3.2 安装场地的要求 (9)3.2.1 通风要求 (9)3.2.2 温度和湿度要求 (9)3.2.3 洁净度要求 (10)3.2.4 电源要求 (10)3.3 系统接地要求 (10)3.4 安装工具要求 (10)3.5 开箱验货检查要求 (11)第4章产品的安装 (12)4.1 安装流程 (12)4.2 安装确认 (12)4.3 安装机箱 (13)4.3.1 安装机箱于桌面 (13)4.3.2 安装机箱于机柜 (13)4.4 R4802路由器主板安装及维护 (13)4.4.1 安装R4802主板 (13)4.5 连接系统接地 (15)4.6 安装后检查 (16)4.6.1 机柜检查 (16)4.6.2 电缆连接检查 (16)4.6.3 电源检查 (16)4.7 连接监控口 (16)4.7.1 连接Console口 (16)4.7.2 连接AUX口 (18)4.8 搭建配置环境 (18)4.8.1 通过配置口(Console)搭建本地配置环境 (18)第5章硬件故障分析 (20)5.1 故障隔离 (20)5.1.1 电源和冷却系统故障 (20)5.1.2 端口、电缆和连接故障 (20)5.2 指示灯说明 (20)第6章路由器维护 (22)6.1 安装R4802主控板 (22)6.2 更换R4802主控板 (23)6.3 R4802主控板内存升级及BOOT ROM升级 (24)第1章产品概述1.1 产品简介天工R4802高端路由器作为我们公司推出的新款路由器,产品致力企业级汇聚网络;产品设计在保持对业界先进技术密切跟踪的同时,充分考虑了公司多年在路由器领域的研发经验和技术积累,以及对市场的充分了解,提出了简便、适用、新颖的以交换为核心,分布式处理的多处理器体系结构。

微雪-BB-BLACK-GPIO-RS485-CAN-扩展板-用户手册说明书

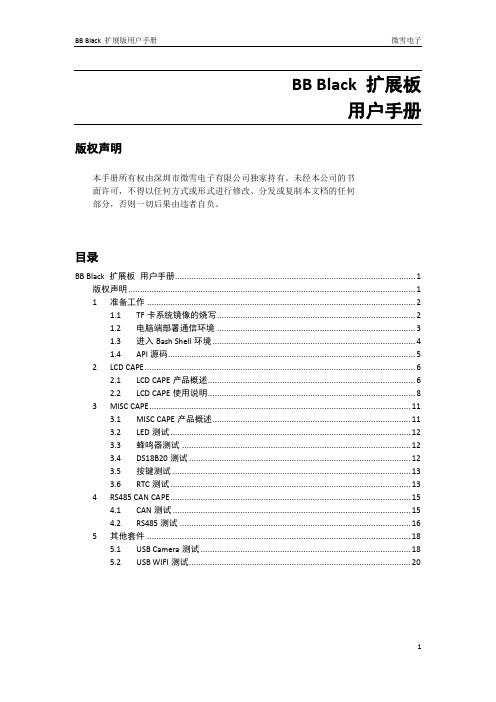

BB Black 扩展板用户手册版权声明本手册所有权由深圳市微雪电子有限公司独家持有。

未经本公司的书面许可,不得以任何方式或形式进行修改、分发或复制本文档的任何部分,否则一切后果由违者自负。

目录BB Black 扩展板用户手册 (1)版权声明 (1)1 准备工作 (2)1.1 TF卡系统镜像的烧写 (2)1.2 电脑端部署通信环境 (3)1.3 进入Bash Shell环境 (4)1.4 API源码 (5)2 LCD CAPE (6)2.1 LCD CAPE产品概述 (6)2.2 LCD CAPE使用说明 (8)3 MISC CAPE (11)3.1 MISC CAPE产品概述 (11)3.2 LED测试 (12)3.3 蜂鸣器测试 (12)3.4 DS18B20测试 (12)3.5 按键测试 (13)3.6 RTC测试 (13)4 RS485 CAN CAPE (15)4.1 CAN测试 (15)4.2 RS485测试 (16)5 其他套件 (18)5.1 USB Camera测试 (18)5.2 USB WIFI测试 (20)1准备工作1.1TF卡系统镜像的烧写烧写我们提供的基于TF卡启动的Angstrom镜像。

操作如下:1)解压系统镜像:使用7z920.exe压缩工具解压相应的镜像文件XXX.img.7z。

注意:“XXX”是泛指各种镜像文件名称,用户根据自己的扩展板模块选择相应的系统镜像,点击下面链接下载:LCD CPAE(4.3inch)测试镜像:/wiki/LCD-CAPE-4.3inch-IMGLCD CPAE(7inch)测试镜像:/wiki/LCD-CAPE-7inch-IMGMISC CAPE和RS485/CAN CAPE测试镜像:/wiki/MISC-CAPE-IMG说明:MISC CAPE和RS485/CAN CAPE共用一个镜像文件。

2)使用HPUSBDisk.exe格式化TF卡。

28F008B3资料

E

CONTENTS

PAGE 1.0 INTRODUCTION .............................................5 1.1 Smart 3 Advanced Boot Block Flash Memory Enhancements ..............................5 1.2 Product Overview.........................................6 2.0 PRODUCT DESCRIPTION..............................6 2.1 Package Pinouts ..........................................7 2.2 Block Organization .....................................11 2.2.1 Parameter Blocks ................................11 2.2.2 Main Blocks .........................................11 3.0 PRINCIPLES OF OPERATION .....................14 3.1 Bus Operation ............................................14 3.1.1 Read....................................................15 3.1.2 Output Disable.....................................15 3.1.3 Standby ...............................................15 3.1.4 Deep Power-Down/Reset ....................15 3.1.5 Write....................................................15 3.2 Modes of Operation....................................15 3.2.1 Read Array ..........................................16 3.2.2 Read Intelligent Identifier .....................17 3.2.3 Read Status Register ..........................17 3.2.4 Program Mode.....................................18 3.2.5 Erase Mode .........................................19 3.3 Block Locking.............................................26 3.3.1 VPP = VIL for Complete Protection .......26 3.3.2 WP# = VIL for Block Locking................26 3.3.3 WP# = VIH for Block Unlocking ............26 3.4 VPP Program and Erase Voltages ..............26 PAGE 3.5 Power Consumption ...................................26 3.5.1 Active Power .......................................26 3.5.2 Automatic Power Savings (APS) .........27 3.5.3 Standby Power ....................................27 3.5.4 Deep Power-Down Mode.....................27 3.6 Power-Up/Down Operation.........................27 3.6.1 RP# Connected to System Reset ........27 3.6.2 VCC, VPP and RP# Transitions .............27 3.7 Power Supply Decoupling ..........................28 3.7.1 VPP Trace on Printed Circuit Boards ....28 4.0 ABSOLUTE MAXIMUM RATINGS ................29 5.0 OPERATING CONDITIONS (VCCQ = 2.7V–3.6V).......................................29 5.1 DC Characteristics: VCCQ = 2.7V–3.6V.......30 6.0 OPERATING CONDITIONS (VCCQ = 1.8V–2.2V).......................................34 6.1 DC Characteristics: VCCQ = 1.8V–2.2V.......34 7.0 AC CHARACTERISTICS...............................39 7.1 Reset Operations .......................................43 APPENDIX A: Ordering Information .................45 APPENDIX B: Write State Machine Current/ Next States ..................................................46 APPENDIX C: Access Time vs. Capacitive Load...........................................47 APPENDIX D: Architecture Block Diagram ......48 APPENDIX E: Additional Information ...............49

CF8141B资料

SM8141

SPECIFICATIONS

Absolute Maximum Ratings

VSS = 0 V

Parameter Supply voltage range Input voltage range

Output voltage

Storage temperature range Power dissipation Soldering temperature Soldering time

fO C L 1 R O C L = 200 kΩ A

fO C L 2

OSC oscillator frequency OSC oscillator frequency range

fO S C 1 R O S C = 200 kΩ B

fO S C 2

OUT1, OUT2 output frequency OUT1, OUT2 output frequency range

I Enable input (built-in pull-down resistor)

– Supply

O Output 2

O Output 1

NIPPON PRECISION CIRCUITS—2

元器件交易网

BLOCK DIAGRAM

• SM8141A

SM8141

VDD LDR CHV OUT1 OUT2

I High-voltage DC input O Booster coil driver output – Ground I Coil driver oscillator (oscillator frequency determined by external variable resistor) I EL driver oscillator (oscillator frequency determined by external variable resistor) – Supply O Output 2 O Output 1

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

the presence or absence of a minimum acceptable level of optical input. A TTL logic HIGH indicates the absence of a valid optical input signal. § Analog optical input level voltage (OILV) is proportional to the optical input power.

When the incoming optical signal falls below the linkstatus switching threshold, the FLAG output is asserted and the FLAG output logic level changes from a TTL low to a TTL high.

22 VCC 21 NUC†

20 Ground

19 Ground

18 NIC*

17 Ground

16 Ground

15 Ground

14 Ground

13 NIC*

* Pins labeled NIC have no internal connection. † Pins designated as no user connect (NUC) are connected inter-

Handling Precautions

The R480-Type receiver is manufactured with a 39 in. ± 4 in. (100 cm ± 10 cm) single-mode or multimode fiber pigtail. SC, FC/PC, LC, and MU connectors are offered on standard versions. Other optical connector options are available on special order. Please contact an Agere Systems’ Account Manager for availability and ordering information.

Pin Information

The R480-Type receiver devices can withstand normal wave-soldering processes. The complete receiver module is not hermetically sealed; therefore, it should not be immersed in, or sprayed with, any solutions. The optical connector process cap deformation temperature is 85 °C. The receiver pins can be wave soldered at 250 °C for 10 seconds.

Table 1. Pin Information

பைடு நூலகம்Pin

Name

1 NIC* 2 NUC† 3 LOS Flag‡ 4 Ground 5 NIC* 6 NIC* 7 Ground 8 VCC 9 Ground 10 DATA 11 DATA 12 Ground

Pin

Name

24 NUC†

23 OILV §

Data Sheet, Rev. 1 September 2001

R480-Type Lightwave Receiver with CML Data Output for up to 2.488 Gbits/s Applications

Applications

s Telecommunications: — Inter- and intraoffice SONET/SDH — Subscriber loop — Metropolitan area networks

The minimum fiber bending radius is 1.5 inches (38 mm).

Electrostatic Discharge

CAUTION: This device is susceptible to damage as a result of electrostatic discharge (ESD). Take proper precautions during both handling and testing. Follow guidelines such as JEDEC Publication No. 108-A (Dec. 1988).