EPM3064ATC100-7N中文资料

EPM3064ATC44-10N中文资料

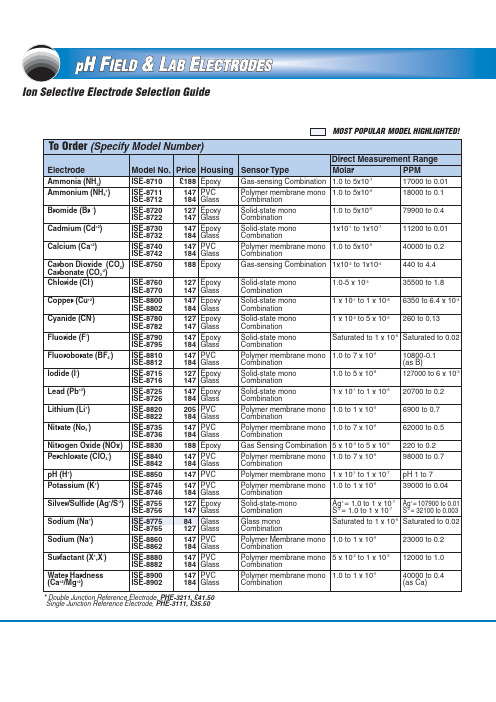

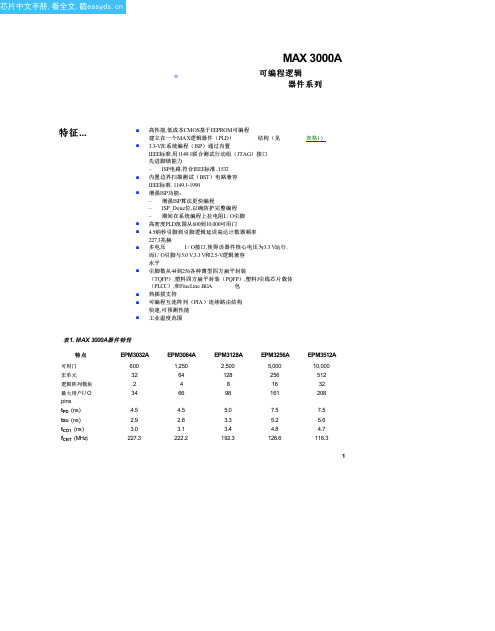

Table 1. MAX 3000A Device Features

Feature

Usable gates Macrocells Logic array blocks Maximum user I/O pins tPD (ns) tSU (ns) tCO1 (ns) fCNT (MHz)

EPM3032A

32 product terms per macrocell ■ Programmable security bit for protection of proprietary designs ■ Enhanced architectural features, including:

– 6 or 10 pin– or logic–driven output enable signals – Two global clock signals with optional inversion – Enhanced interconnect resources for improved routability – Programmable output slew–rate control ■ Software design support and automatic place–and–route provided by Altera’s development systems for Windows–based PCs and Sun SPARCstations, and HP 9000 Series 700/800 workstations ■ Additional design entry and simulation support provided by EDIF 2 0 0 and 3 0 0 netlist files, library of parameterized modules (LPM), Verilog HDL, VHDL, and other interfaces to popular EDA tools from third–party manufacturers such as Cadence, Exemplar Logic, Mentor Graphics, OrCAD, Synopsys, Synplicity, and VeriBest ■ Programming support with the Altera master programming unit (MPU), MasterBlasterTM communications cable, ByteBlasterMVTM parallel port download cable, BitBlasterTM serial download cable as well as programming hardware from third–party manufacturers and any in–circuit tester that supports JamTM Standard Test and Programming Language (STAPL) Files (.jam), Jam STAPL Byte-Code Files (.jbc), or Serial Vector Format Files (.svf)

FPGA可编程逻辑器件芯片EPM3064ATC44-10N中文规格书

Figure2–66.EP2SGX60, EP2SGX90 and EP2SGX130 Device I/O Clock GroupsYou can use the Quartus II software to control whether a clock input pindrives either a global, regional, or dual-regional clock network. TheQuartus II software automatically selects the clocking resources if notspecified.Clock Control BlockEach global clock, regional clock, and PLL external clock output has itsown clock control block. The control block has two functions:■Clock source selection (dynamic selection for global clocks)■Clock power-down (dynamic clock enable or disable)Figure2–69.External PLL Output Clock Control BlocksNotes to Figure2–69:(1)These clock select signals can only be set through a configuration file (.sof or .pof) and cannot be dynamicallycontrolled during user mode operation.(2)The clock control block feeds to a multiplexer within the PLL_OUT pin’s IOE. The PLL_OUT pin is a dual-purposepin. Therefore, this multiplexer selects either an internal signal or the output of the clock control block.For the global clock control block, the clock source selection can becontrolled either statically or dynamically. You have the option ofstatically selecting the clock source by using the Quartus II software to setspecific configuration bits in the configuration file (.sof or .pof) or you cancontrol the selection dynamically by using internal logic to drive themultiplexer select inputs. When selecting statically, the clock source canbe set to any of the inputs to the select multiplexer. When selecting theclock source dynamically, you can either select between two PLL outputs(such as the C0 or C1 outputs from one PLL), between two PLLs (such asthe C0/C1 clock output of one PLL or the C0/C1 c1ock output of the otherPLL), between two clock pins (such as CLK0 or CLK1), or between acombination of clock pins or PLL outputs.For the regional and PLL_OUT clock control block, the clock sourceselection can only be controlled statically using configuration bits. Any ofthe inputs to the clock select multiplexer can be set as the clock source.Operating Conditionsreconfig_clk clockfrequency2.5 -50 2.5 -50 2.5 -50MHzT ransceiverblock minimumpower-downpulse width100--100--100--nsReceiverData rate600-6375600-5000600-4250Mbps Absolute V M A Xfor a receiverpin (1)-- 2.0-- 2.0-- 2.0VAbsolute V M I Nfor a receiverpin-0.4---0.4---0.4--VMaximumpeak-to-peakdifferentialinput voltageV I D (diff p-p)V C M = 0.85V-- 3.3-- 3.3-- 3.3VMinimum peak-to-peak differential input voltage V I D (diff p-p)V C M = 0.85VDC Gain =≥3dB160--160--160--mVV I C M V I C M=0.85V setting850±10%850±10%850±10%mVV I C M=1.2Vsetting (11)1200±10%1200±10%1200±10%mVOn-chip termination resistors 100Ω setting100±15%100±15%100±15%Ω120Ω setting120±15%120±15%120±15%Ω150Ω setting150±15%150±15%150±15%ΩBandwidth at 6.375 Gbps BW = Low-20-------MHz BW = Med-35-------MHz BW = High-45-------MHzTable4–6.Stratix II GX Transceiver Block AC Specification(Part 3 of6)Symbol / Description Conditions-3 Speed CommercialSpeed Grade-4 Speed Commercialand Industrial SpeedGrade-5 Speed CommercialSpeed Grade Unit Min Typ Max Min Typ Max Min Typ Max。

EPM3032ATC44-10中文资料

®Altera Corporation 1MAX 3000AProgrammable Logic Device FamilyJune 2002, ver. 3.0Data Sheet DS-M3000A-3.0Features...■High–performance, low–cost CMOS EEPROM–based programmable logic devices (PLDs) built on a MAX ® architecture (see Table 1)■3.3-V in-system programmability (ISP) through the built–in IEEE Std. 1149.1 Joint Test Action Group (JTAG) interface with advanced pin-locking capability –ISP circuitry compliant with IEEE Std. 1532■Built–in boundary-scan test (BST) circuitry compliant with IEEE Std. 1149.1-1990■Enhanced ISP features:–Enhanced ISP algorithm for faster programming –ISP_Done bit to ensure complete programming –Pull-up resistor on I/O pins during in–system programming ■High–density PLDs ranging from 600 to 10,000 usable gates ■4.5–ns pin–to–pin logic delays with counter frequencies of up to 227.3MHz ■MultiVolt TM I/O interface enabling the device core to run at 3.3 V, while I/O pins are compatible with 5.0–V, 3.3–V, and 2.5–V logic levels ■Pin counts ranging from 44 to 256 in a variety of thin quad flat pack (TQFP), plastic quad flat pack (PQFP), plastic J–lead chip carrier (PLCC), and FineLine BGA TM packages ■Hot–socketing support ■Programmable interconnect array (PIA) continuous routing structurefor fast, predictable performance Table 1.MAX3000A Device Features FeatureEPM3032A EPM3064A EPM3128A EPM3256A EPM3512A Usable gates6001,2502,5005,00010,000Macrocells3264128256512Logic array blocks2481632Maximum user I/Opins346696158208t PD (ns)4.5 4.55.0 5.57.5t SU (ns)2.9 2.83.3 3.9 5.6t CO1 (ns)3.0 3.1 3.4 3.54.7f CNT (MHz)227.3222.2192.3172.4116.3捷多邦,您值得信赖的PCB打样专家!MAX 3000A Programmable Logic Device Family Data Sheet...and More Features ■PCI compatible■Bus–friendly architecture including programmable slew–rate control ■Open–drain output option■Programmable macrocell flipflops with individual clear, preset, clock, and clock enable controls■Programmable power–saving mode for a power reduction of over 50% in each macrocell■Configurable expander product–term distribution, allowing up to32 product terms per macrocell■Programmable security bit for protection of proprietary designs■Enhanced architectural features, including:– 6 or 10 pin– or logic–driven output enable signals–Two global clock signals with optional inversion–Enhanced interconnect resources for improved routability–Programmable output slew–rate control■Software design support and automatic place–and–route provided by Altera’s development systems for Windows–based PCs and Sun SPARCstations, and HP 9000 Series 700/800 workstations■Additional design entry and simulation support provided by EDIF2 0 0 and3 0 0 netlist files, library of parameterized modules (LPM),Verilog HDL, VHDL, and other interfaces to popular EDA tools from third–party manufacturers such as Cadence, Exemplar Logic, Mentor Graphics, OrCAD, Synopsys, Synplicity, and VeriBest■Programming support with the Altera master programming unit (MPU), MasterBlaster TM communications cable, ByteBlasterMV TMparallel port download cable, BitBlaster TM serial download cable as well as programming hardware from third–party manufacturers and any in–circuit tester that supports Jam TM Standard Test andProgramming Language (STAPL) Files (.jam), Jam STAPL Byte-Code Files (.jbc), or Serial Vector Format Files (.svf)General Description MAX3000A devices are low–cost, high–performance devices based on the Altera MAX architecture. Fabricated with advanced CMOS technology, the EEPROM–based MAX3000A devices operate with a 3.3-V supply voltage and provide 600 to 10,000 usable gates, ISP, pin-to-pin delays as fast as 4.5 ns, and counter speeds of up to 227.3MHz. MAX3000A devices in the –4, –5, –6, –7, and –10 speed grades are compatible with the timing requirements of the PCI Special Interest Group (PCI SIG) PCI Local Bus Specification, Revision2.2. See Table2.2Altera CorporationAltera Corporation 3MAX 3000A Programmable Logic Device Family Data Sheet The MAX 3000A architecture supports 100% transistor-to-transistor logic (TTL) emulation and high–density small-scale integration (SSI), medium-scale integration (MSI), and large-scale integration (LSI) logic functions. The MAX 3000A architecture easily integrates multiple devices ranging from PALs, GALs, and 22V10s to MACH and pLSI devices. MAX 3000A devices are available in a wide range of packages, including PLCC, PQFP, and TQFP packages. See Table 3.Note:(1)When the IEEE Std. 1149.1 (JTAG) interface is used for in–system programming or boundary–scan testing, four I/O pins become JTAG pins.MAX 3000A devices use CMOS EEPROM cells to implement logic functions. The user–configurable MAX 3000A architecture accommodates a variety of independent combinatorial and sequential logic functions. The devices can be reprogrammed for quick and efficient iterations during design development and debugging cycles, and can be programmed and erased up to 100 times.Table 2.MAX 3000A Speed Grades Device Speed Grade –4–5–6–7–10EPM3032A v v v EPM3064A vv v EPM3128A v v v EPM3256A v v EPM3512A v v Table 3.MAX 3000A Maximum User I/O Pins Note (1)Device 44–Pin PLCC 44–Pin TQFP 100–Pin TQFP 144–Pin TQFP 208–Pin PQFP 256-Pin FineLine BGA EPM3032A 3434EPM3064A 343466EPM3128A 8096EPM3256A 116158EPM3512A 172208MAX 3000A Programmable Logic Device Family Data SheetMAX3000A devices contain 32 to 512 macrocells, combined into groupsof 16 macrocells called logic array blocks (LABs). Each macrocell has aprogrammable–AND/fixed–OR array and a configurable register withindependently programmable clock, clock enable, clear, and presetfunctions. To build complex logic functions, each macrocell can besupplemented with shareable expander and high–speed parallelexpander product terms to provide up to 32 product terms per macrocell.MAX3000A devices provide programmable speed/power optimization.Speed–critical portions of a design can run at high speed/full power,while the remaining portions run at reduced speed/low power. Thisspeed/power optimization feature enables the designer to configure oneor more macrocells to operate at 50% or lower power while adding only anominal timing delay. MAX3000A devices also provide an option thatreduces the slew rate of the output buffers, minimizing noise transientswhen non–speed–critical signals are switching. The output drivers of allMAX3000A devices can be set for 2.5V or 3.3V, and all input pins are2.5–V,3.3–V, and 5.0-V tolerant, allowing MAX3000A devices to be usedin mixed–voltage systems.MAX3000A devices are supported by Altera development systems,which are integrated packages that offer schematic, text—includingVHDL, Verilog HDL, and the Altera Hardware Description Language(AHDL)—and waveform design entry, compilation and logic synthesis,simulation and timing analysis, and device programming. The softwareprovides EDIF 2 0 0 and 3 0 0, LPM, VHDL, Verilog HDL, and otherinterfaces for additional design entry and simulation support from otherindustry–standard PC– and UNIX–workstation–based EDA tools. Thesoftware runs on Windows–based PCs, as well as Sun SPARCstation, andHP 9000 Series 700/800 workstations.f For more information on development tools, see the MAX+PLUS IIProgrammable Logic Development System & Software Data Sheet andtheQuartus Programmable Logic Development System & Software Data Sheet.Functional Description The MAX3000A architecture includes the following elements:■Logic array blocks (LABs)■Macrocells■Expander product terms (shareable and parallel)■Programmable interconnect array (PIA)■I/O control blocksThe MAX3000A architecture includes four dedicated inputs that can be used as general–purpose inputs or as high–speed, global control signals (clock, clear, and two output enable signals) for each macrocell and I/O pin. Figure1 shows the architecture of MAX3000A devices.4Altera CorporationMAX 3000A Programmable Logic Device Family Data Sheet Figure 1. MAX3000A Device Block DiagramNote:(1)EPM3032A, EPM3064A, EPM3128A, and EPM3256A devices have six output enables. EPM3512A devices have10output enables.Logic Array BlocksThe MAX3000A device architecture is based on the linking ofhigh–performance LABs. LABs consist of 16–macrocell arrays, as shownin Figure1. Multiple LABs are linked together via the PIA, a global busthat is fed by all dedicated input pins, I/O pins, and macrocells.Each LAB is fed by the following signals:■36 signals from the PIA that are used for general logic inputs■Global controls that are used for secondary register functionsAltera Corporation 5MAX 3000A Programmable Logic Device Family Data SheetMacrocellsMAX3000A macrocells can be individually configured for eithersequential or combinatorial logic operation. Macrocells consist of threefunctional blocks: logic array, product–term select matrix, andprogrammable register. Figure2 shows a MAX3000A macrocell.Figure 2. MAX3000A MacrocellQCLRNTo PIACombinatorial logic is implemented in the logic array, which providesfive product terms per macrocell. The product–term select matrixallocates these product terms for use as either primary logic inputs (to theOR and XOR gates) to implement combinatorial functions, or as secondaryinputs to the macrocell’s register preset, clock, and clock enable controlfunctions.Two kinds of expander product terms (“expanders”) are available tosupplement macrocell logic resources:■Shareable expanders, which are inverted product terms that are fedback into the logic array■Parallel expanders, which are product terms borrowed from adjacentmacrocellsThe Altera development system automatically optimizes product–termallocation according to the logic requirements of the design.6Altera CorporationMAX 3000A Programmable Logic Device Family Data SheetFor registered functions, each macrocell flipflop can be individuallyprogrammed to implement D, T, JK, or SR operation with programmableclock control. The flipflop can be bypassed for combinatorial operation.During design entry, the designer specifies the desired flipflop type; theAltera development system software then selects the most efficientflipflop operation for each registered function to optimize resourceutilization.Each programmable register can be clocked in three different modes:■Global clock signal mode, which achieves the fastest clock–to–outputperformance.■Global clock signal enabled by an active–high clock enable. A clockenable is generated by a product term. This mode provides an enableon each flipflop while still achieving the fast clock–to–outputperformance of the global clock.■Array clock implemented with a product term. In this mode, theflipflop can be clocked by signals from buried macrocells or I/O pins.Two global clock signals are available in MAX3000A devices. As shownin Figure1, these global clock signals can be the true or the complement ofeither of the two global clock pins, GCLK1 or GCLK2.Each register also supports asynchronous preset and clear functions. Asshown in Figure2, the product–term select matrix allocates product termsto control these operations. Although the product–term–driven presetand clear from the register are active high, active–low control can beobtained by inverting the signal within the logic array. In addition, eachregister clear function can be individually driven by the active–lowdedicated global clear pin (GCLRn).Expander Product TermsAlthough most logic functions can be implemented with the five productterms available in each macrocell, highly complex logic functions requireadditional product terms. Another macrocell can be used to supply therequired logic resources. However, the MAX3000A architecture alsooffers both shareable and parallel expander product terms (“expanders”)that provide additional product terms directly to any macrocell in thesame LAB. These expanders help ensure that logic is synthesized with thefewest possible logic resources to obtain the fastest possible speed. Altera Corporation 78Altera Corporation MAX 3000A Programmable Logic Device Family Data SheetShareable Expanders Each LAB has 16 shareable expanders that can be viewed as a pool of uncommitted single product terms (one from each macrocell) with inverted outputs that feed back into the logic array. Each shareable expander can be used and shared by any or all macrocells in the LAB to build complex logic functions. Shareable expanders incur a small delay (t SEXP ). Figure 3 shows how shareable expanders can feed multiple macrocells.Figure 3. MAX 3000A Shareable Expanders Shareable expanders can be shared by any or all macrocells in an LAB.Parallel Expanders Parallel expanders are unused product terms that can be allocated to a neighboring macrocell to implement fast, complex logic functions. Parallel expanders allow up to 20 product terms to directly feed the macrocell OR logic, with five product terms provided by the macrocell and 15 parallel expanders provided by neighboring macrocells in the LAB. MacrocellProduct-Term Logic Product-Term Select Matrix Macrocell Product-Term Logic 36 Signals from PIA 16 Shared ExpandersMAX 3000A Programmable Logic Device Family Data SheetThe Altera development system compiler can automatically allocate up tothree sets of up to five parallel expanders to the macrocells that requireadditional product terms. Each set of five parallel expanders incurs asmall, incremental timing delay (t PEXP). For example, if a macrocellrequires 14product terms, the compiler uses the five dedicated productterms within the macrocell and allocates two sets of parallel expanders;the first set includes five product terms, and the second set includes fourproduct terms, increasing the total delay by 2 ×t PEXP.Two groups of eight macrocells within each LAB (e.g., macrocells 1through 8 and 9through 16) form two chains to lend or borrow parallelexpanders. A macrocell borrows parallel expanders from lower–numbered macrocells. For example, macrocell 8 can borrow parallelexpanders from macrocell 7, from macrocells 7 and 6, or from macrocells7, 6, and 5. Within each group of eight, the lowest–numbered macrocellcan only lend parallel expanders and the highest–numbered macrocell canonly borrow them. Figure4 shows how parallel expanders can beborrowed from a neighboring macrocell.Figure 4. MAX3000A Parallel ExpandersUnused product terms in a macrocell can be allocated to a neighboring macrocell.Altera Corporation 9MAX 3000A Programmable Logic Device Family Data SheetProgrammable Interconnect ArrayLogic is routed between LABs on the PIA. This global bus is aprogrammable path that connects any signal source to any destination onthe device. All MAX3000A dedicated inputs, I/O pins, and macrocelloutputs feed the PIA, which makes the signals available throughout theentire device. Only the signals required by each LAB are actually routedfrom the PIA into the LAB. Figure5 shows how the PIA signals are routedinto the LAB. An EEPROM cell controls one input to a two-input AND gate,which selects a PIA signal to drive into the LAB.Figure 5. MAX3000A PIA RoutingWhile the routing delays of channel–based routing schemes in masked orFPGAs are cumulative, variable, and path–dependent, the MAX3000APIA has a predictable delay. The PIA makes a design’s timingperformance easy to predict.I/O Control BlocksThe I/O control block allows each I/O pin to be individually configuredfor input, output, or bidirectional operation. All I/O pins have a tri–statebuffer that is individually controlled by one of the global output enablesignals or directly connected to ground or V CC. Figure6 shows the I/Ocontrol block for MAX3000A devices. The I/O control block has 6 or10global output enable signals that are driven by the true or complementof two output enable signals, a subset of the I/O pins, or a subset of theI/O macrocells.10Altera CorporationMAX 3000A Programmable Logic Device Family Data Sheet Figure 6. I/O Control Block of MAX3000A DevicesNote:(1)EPM3032A, EPM3064A, EPM3128A, and EPM3256A devices have six output enables. EPM3512A devices have10output enables.When the tri–state buffer control is connected to ground, the output istri-stated (high impedance), and the I/O pin can be used as a dedicatedinput. When the tri–state buffer control is connected to V CC, the output isenabled.The MAX3000A architecture provides dual I/O feedback, in whichmacrocell and pin feedbacks are independent. When an I/O pin isconfigured as an input, the associated macrocell can be used for buriedlogic.Altera Corporation 1112Altera Corporation MAX 3000A Programmable Logic Device Family Data SheetIn–SystemProgramma-bilityMAX 3000A devices can be programmed in–system via an industry–standard four–pin IEEE Std. 1149.1-1990 (JTAG) interface. In-system programmability (ISP) offers quick, efficient iterations during design development and debugging cycles. The MAX 3000A architecture internally generates the high programming voltages required to program its EEPROM cells, allowing in–system programming with only a single 3.3–V power supply. During in–system programming, the I/O pins are tri–stated and weakly pulled–up to eliminate board conflicts. The pull–up value is nominally 50 k Ω.MAX 3000A devices have an enhanced ISP algorithm for faster programming. These devices also offer an ISP_Done bit that ensures safe operation when in–system programming is interrupted. This ISP_Done bit, which is the last bit programmed, prevents all I/O pins from driving until the bit is programmed.ISP simplifies the manufacturing flow by allowing devices to be mounted on a printed circuit board (PCB) with standard pick–and–place equipment before they are programmed. MAX 3000A devices can be programmed by downloading the information via in–circuit testers, embedded processors, the MasterBlaster communications cable, the ByteBlasterMV parallel port download cable, and the BitBlaster serial download cable. Programming the devices after they are placed on the board eliminates lead damage on high–pin–count packages (e.g., QFP packages) due to device handling. MAX 3000A devices can be reprogrammed after a system has already shipped to the field. For example, product upgrades can be performed in the field via software or modem. The Jam STAPL programming and test language can be used to program MAX 3000A devices with in–circuit testers, PCs, or embedded processors.fFor more information on using the Jam STAPL programming and test language, see Application Note 88 (Using the Jam Language for ISP & ICR via an Embedded Processor), Application Note 122 (Using Jam STAPL for ISP & ICR via an Embedded Processor) and AN 111 (Embedded Programming Using the 8051 and Jam Byte-Code).The ISP circuitry in MAX 3000A devices is compliant with the IEEE Std. 1532 specification. The IEEE Std. 1532 is a standard developed to allow concurrent ISP between multiple PLD vendors.Programmingwith ExternalHardwareMAX 3000A devices can be programmed on Windows–based PCs with an Altera Logic Programmer card, MPU, and the appropriate device adapter. The MPU performs continuity checking to ensure adequate electrical contact between the adapter and the device. fFor more information, see the Altera Programming Hardware Data Sheet.Altera Corporation 13MAX 3000A Programmable Logic Device Family Data SheetThe Altera software can use text– or waveform–format test vectors createdwith the Altera Text Editor or Waveform Editor to test the programmeddevice. For added design verification, designers can perform functionaltesting to compare the functional device behavior with the results ofsimulation.Data I/O, BP Microsystems, and other programming hardwaremanufacturers also provide programming support for Altera devices.fFor more information, see Programming Hardware Manufacturers .IEEE Std.1149.1 (JTAG)Boundary–ScanSupport MAX 3000A devices include the JTAG BST circuitry defined by IEEE Std.1149.1–1990. Table 4 describes the JTAG instructions supported by MAX 3000A devices. The pin-out tables found on the Altera web site ( ) or the Altera Digital Library show the location of the JTAG control pins for each device. If the JTAG interface is notrequired, the JTAG pins are available as user I/O pins.The instruction register length of MAX 3000A devices is 10 bits. TheIDCODE and USERCODE register length is 32 bits. Tables 5 and 6 showthe boundary–scan register length and device IDCODE information forMAX 3000A devices.Table 4.MAX 3000A JTAG InstructionsJTAG InstructionDescription SAMPLE/PRELOADAllows a snapshot of signals at the device pins to be captured and examined during normal device operation, and permits an initial data pattern output at the device pins EXTESTAllows the external circuitry and board–level interconnections to be tested by forcing a test pattern at the output pins and capturing test results at the input pins BYPASS Places the 1–bit bypass register between the TDI and TDO pins, which allows the BSTdata to pass synchronously through a selected device to adjacent devices during normaldevice operationIDCODE Selects the IDCODE register and places it between the TDI and TDO pins, allowing theIDCODE to be serially shifted out of TDOUSERCODE Selects the 32–bit USERCODE register and places it between the TDI and TDO pins,allowing the USERCODE value to be shifted out of TDOISP InstructionsThese instructions are used when programming MAX 3000A devices via the JTAG portswith the MasterBlaster, ByteBlasterMV, or BitBlaster cable, or when using a Jam STAPLfile, JBC file, or SVF file via an embedded processor or test equipment14Altera Corporation MAX 3000A Programmable Logic Device Family Data SheetNotes:(1)The most significant bit (MSB) is on the left.(2)The least significant bit (LSB) for all JTAG IDCODEs is 1.fSee Application Note 39 (IEEE 1149.1 (JTAG) Boundary–Scan Testing in Altera Devices) for more information on JTAG BST.Table 5.MAX 3000A Boundary–Scan Register Length Device Boundary–Scan Register Length EPM3032A 96EPM3064A 192EPM3128A 288EPM3256A 480EPM3512A 624Table 6.32–Bit MAX 3000A Device IDCODE Value Note (1)Device IDCODE (32 bits)Version (4 Bits)Part Number (16 Bits) Manufacturer’s Identity (11 Bits) 1 (1 Bit) (2)EPM3032A 00010111 0000 0011 0010000011011101EPM3064A 00010111 0000 0110 0100000011011101EPM3128A 00010111 0001 0010 1000000011011101EPM3256A 00010111 0010 0101 0110000011011101EPM3512A 00010111 0101 0001 0010000011011101MAX 3000A Programmable Logic Device Family Data SheetFigure7 shows the timing information for the JTAG signals.Figure 7. MAX3000A JTAG WaveformsTable7 shows the JTAG timing parameters and values for MAX3000Adevices.Table 7.JTAG Timing Parameters & Values for MAX3000A DevicesSymbol Parameter Min Max Unitt JCP TCK clock period 100nst JCH TCK clock high time 50nst JCL TCK clock low time 50nst JPSU JTAG port setup time 20nst JPH JTAG port hold time 45nst JPCO JTAG port clock to output25nst JPZX JTAG port high impedance to valid output25nst JPXZ JTAG port valid output to high impedance25nst JSSU Capture register setup time20nst JSH Capture register hold time45nst JSCO Update register clock to output25nst JSZX Update register high impedance to valid output25nst JSXZ Update register valid output to high impedance25ns Altera Corporation 15MAX 3000A Programmable Logic Device Family Data SheetProgrammable Speed/Power Control MAX3000A devices offer a power–saving mode that supports low-power operation across user–defined signal paths or the entire device. This feature allows total power dissipation to be reduced by 50% or more because most logic applications require only a small fraction of all gates to operate at maximum frequency.The designer can program each individual macrocell in a MAX3000A device for either high–speed or low–power operation. As a result, speed-critical paths in the design can run at high speed, while the remaining paths can operate at reduced power. Macrocells that run at low power incur a nominal timing delay adder (t LPA) for the t LAD, t LAC, t IC, t ACL, t EN, t CPPW and t SEXP parameters.Output Configuration MAX3000A device outputs can be programmed to meet a variety of system–level requirements.MultiVolt I/O InterfaceThe MAX3000A device architecture supports the MultiVolt I/O interface feature, which allows MAX3000A devices to connect to systems with differing supply voltages. MAX3000A devices in all packages can be set for 2.5–V, 3.3–V, or 5.0–V I/O pin operation. These devices have one set of V CC pins for internal operation and input buffers (VCCINT), and another set for I/O output drivers (VCCIO).The VCCIO pins can be connected to either a 3.3–V or 2.5–V power supply, depending on the output requirements. When the VCCIO pins are connected to a 2.5–V power supply, the output levels are compatible with 2.5–V systems. When the VCCIO pins are connected to a 3.3–V power supply, the output high is at 3.3V and is therefore compatible with 3.3-V or 5.0–V systems. Devices operating with V CCIO levels lower than 3.0V incur a nominally greater timing delay of t OD2 instead of t OD1. Inputs can always be driven by 2.5–V, 3.3–V, or 5.0–V signals.Table8 summarizes the MAX3000A MultiVolt I/O support.Note:(1)When V CCIO is 3.3 V, a MAX 3000A device can drive a 2.5–V device that has 3.3–Vtolerant inputs.Table 8.MAX3000A MultiVolt I/O SupportV CCIO Voltage Input Signal (V)Output Signal (V)2.53.3 5.0 2.5 3.3 5.02.5v v v v3.3v v v v v v16Altera CorporationMAX 3000A Programmable Logic Device Family Data SheetOpen–Drain Output OptionMAX3000A devices provide an optional open–drain (equivalent toopen-collector) output for each I/O pin. This open–drain output enablesthe device to provide system–level control signals (e.g., interrupt andwrite enable signals) that can be asserted by any of several devices. It canalso provide an additional wired–OR plane.Open-drain output pins on MAX3000A devices (with a pull-up resistor tothe 5.0-V supply) can drive 5.0-V CMOS input pins that require a high V IH.When the open-drain pin is active, it will drive low. When the pin isinactive, the resistor will pull up the trace to 5.0V, thereby meeting CMOSrequirements. The open-drain pin will only drive low or tri-state; it willnever drive high. The rise time is dependent on the value of the pull-upresistor and load impedance. The I OL current specification should beconsidered when selecting a pull-up resistorSlew–Rate ControlThe output buffer for each MAX3000A I/O pin has an adjustable outputslew rate that can be configured for low–noise or high–speedperformance. A faster slew rate provides high–speed transitions forhigh-performance systems. However, these fast transitions may introducenoise transients into the system. A slow slew rate reduces system noise,but adds a nominal delay of 4 to 5 ns. When the configuration cell isturned off, the slew rate is set for low–noise performance. Each I/O pinhas an individual EEPROM bit that controls the slew rate, allowingdesigners to specify the slew rate on a pin–by–pin basis. The slew ratecontrol affects both the rising and falling edges of the output signal. Design Security All MAX3000A devices contain a programmable security bit that controlsaccess to the data programmed into the device. When this bit isprogrammed, a design implemented in the device cannot be copied orretrieved. This feature provides a high level of design security becauseprogrammed data within EEPROM cells is invisible. The security bit thatcontrols this function, as well as all other programmed data, is reset onlywhen the device is reprogrammed.Generic Testing MAX3000A devices are fully tested. Complete testing of eachprogrammable EEPROM bit and all internal logic elements ensures 100%programming yield. AC test measurements are taken under conditionsequivalent to those shown in Figure8. Test patterns can be used and thenerased during early stages of the production flow.Altera Corporation 17。

泛达电气(PANDUIT)扎带枪选型产品大全

泛达电气(PANDUIT)扎带枪产品大全全自动扎线枪供应输送器PDM 全自动扎带枪PAT1.5M 手持电动不锈钢扎带枪PBTMT/E 气动扎带枪PTH扎带枪ST3EH 不锈钢扎带枪RT2HT 不锈钢扎带枪ST2MT 扎带枪GTH扎带枪GS4EH 扎带枪GTSL 扎带枪GS2BL 不锈钢扎带枪GS4MT扎带枪、扎线枪GS2B 扎带枪GTS 扎带枪GS4H 不锈钢扎带枪T2HTN全自动扎带枪 PAT2S气动扎带枪 PTS全自动扎线枪供应输送器 PDM∙ 型号:PDM说明PANDUIT AUTOMATIC CABLE TIE GUN DISPENSERS PDMDispenses cable ties by separating ties from the carrier ribbon and sending them through a feeder hose to the tool head. System operates on 65 psig (minimum) non-lubricated filtered air and 100 – 24 FAC/TP or 60 Mhz. Extended arm holds a reel of 5000 cable ties for continuous processing. -EI option provides the capability to remotely control the PAT system. Integrators are able to electrically tie the tool cycling in with their automation controls. The 15-pin D-Sub female port is located on the back side of the unit.Product DetailsStd. Pkg. Qty.1Std. Ctn. Weight (lb)0.0000 Std. Ctn. Volume (cf) 0.0000 Std. Pallet Weight (lb) 0.0000Std. Pallet Volume (cf)0.000000RoHS Compliancy Status CompliantPart DescriptionDispenses cable ties by separating ties from the carrier ribbon and sending them through a feeder hose to the tool head. System operates on 65 psig (minimum) non-lubricated filtered airand 100 – 24 FAC/TP or 60 Mhz. Extended arm holds a reel of 5000 cable ties for continuous processing. -EI option provides the capability to remotely control the PAT system. Integrators are able to electrically tie the tool cycling in with their automation controls. The 15-pin D-Sub female port is located on the back side of the unit.Product Type Automatic Cable Tie ToolColorBlackPricing Description Electrical Interface Enabled PDM DispenserUsed With Cable TiesPLT1M-XMR, PLT1.5M-XMR, BT1M-XMR, BT1.5M-XMRMin. Order Qty.1.0000全自动扎带枪 PAT1.5M∙ 型号:PAT1.5M说明PANDUIT AUTOMATIC CABLE TIE GUN PAT1.5Automatic Cable Tie Installation Tool with Plastic Ergonomic Housing.Product DetailsStd. Pkg. Qty. 1Std. Ctn. Weight (lb) 0.0000Std. Ctn. Volume (cf) 0.0000Std. Pallet Weight (lb) 0.0000Std. Pallet Volume (cf) 0.000000RoHS Compliancy Status Compliant in EMEAPart Description Automatic Cable Tie Installation Tool with Plastic Ergonomic Housing.Product Type Automatic Cable Tie ToolLength (ft.)—Length (m)—Color BlackTool Head for cable ties up to 1.3" (33mm) bundle diameter (P/N's PLT1.5M-XMR andDescriptionBT1.5M-XMR)Pricing Description Automatic Cable Tie Tool Head for PLT1.5M-XMR Cable Ties - Plastic Ergo HousingType Tool HeadUsed with Installation Tool—CE Compliant YesMax. Bundle Diameter33(mm)Max. Bundle Diameter (In.)1.31Weight (lb.) 1.70Weight (g) 770Used With Cable Ties PLT1.5M-XMRMin. Order Qty. 1.0000电动不锈钢扎带枪PBTMT/E型号:PBTMT/E说明PANDUIT CABLE TIE GUN PBTMT/EBattery Powered Installation tool for use with the following stainless steel cross section ties:Type MLT andMLTFC: Heavy, extra-heavy, and super-heavyType MLTC: HeavyType MLTDH: Extra-Heavy andsuper-heavyUsed with custom length banding cross sections:Type MB and MBC: Heavy, extra-heavy, andsuper-heavy2 –12 volt Lithium-Ion batteries and 220 volt, 50 Hz charger included.Product DetailsStd. Pkg. Qty.1Std. Ctn. Weight (lb)0.0000 Std. Ctn. Volume (cf) 0.0000Std. Pallet Weight (lb) 378.0000Std. Pallet Volume (cf)0.000000RoHS Compliancy Status CompliantPart DescriptionBattery Powered Installation tool for use with the following stainless steel cross section ties:Type MLT and MLTFC: Heavy, extra-heavy, and super-heavyType MLTC: HeavyTypeMLTDH: Extra-Heavy and super-heavyUsed with custom length banding cross sections:Type MB and MBC: Heavy, extra-heavy, and super-heavy2 – 12 volt Lithium-Ion batteries and 220 volt, 50 Hz charger included.Product Type Cable Tie and Custom Length Banding ToolColorBlack/RedPricing DescriptionPower MLT Tool CEWeight (lbs.)3.7Weight (g)1800Used With Cable TiesExtra-heavy and super-heavyUsed.MLT TiesMin. Order Qty.1.0000气动扎带枪 PTH型号:PTH说明PANDUIT CABLE TIE GUN PTHErgonomic lightweight design installs Standard, Heavy-Standard, Light-Heavy, or Heavy cross section cable tiesColor identification: Gray Impact Resistant Resin Housing with Red Selector Knob and Red TriggerWeight: 32.0 oz. (907g).Product DetailsStd. Pkg. Qty. 1 Std. Ctn. Weight (lb) 0.0000 Std. Ctn. Volume (cf)0.0000Std. Pallet Weight (lb) 0.0000 Std. Pallet Volume (cf) 0.000000 RoHS CompliancyStatusRoHS directive is not applicablePart DescriptionErgonomic lightweight design installs Standard, Heavy-Standard, Light-Heavy, or Heavy crosssection cable tiesColor identification: Gray Impact Resistant Resin Housing with Red Selector Knob and Red TriggerWeight: 32.0 oz. (907g).Product Type Cable Tie ToolsMaterial Impact resistant resin housing ColorDark Gray/RedPricing Description Pneumatic Cable Tie Tool for Std, Hvy-Std, Lt-Hvy and Hvy Ties - LeasedPart FeaturesErgonomic design with impact resistant resin housing and red knob; replacement parts can bepart of a scheduled maintenance program.CE Compliant YesWeight (oz.) 32.0Weight (g) 907Used With Cable Ties S, HS, LH, HMin. Order Qty. 1.0000扎带枪 ST3EH型号:ST3EH说明PANDUIT CABLE TIE GUN ST3EHInstalls Light-Heavy, Heavy and Extra-Heavy cross section cable ties. Durable all steel construction with comfortable rubberhandles. Color Identification: Blue handles Weight: 9 oz. (256g)Product DetailsStd. Pkg. Qty. 1Std. Ctn. Weight (lb) 0.0000Std. Ctn. Volume (cf) 0.0000Std. Pallet Weight (lb) 518.4000Std. Pallet Volume (cf) 0.000000RoHS Compliancy Status RoHS directive is not applicablePart Description Installs Light-Heavy, Heavy and Extra-Heavy cross section cable ties. Durable all steel construction with comfortable rubber handles. Color Identification: Blue handles Weight: 9 oz. (256g)Pocket catalog part description Installs Light-Heavy, Heavy and Extra-Heavy cross section cable ties, Blue handles, 9.0 oz.; durable all steel constructionMaterial Metal with plastic handles Color Blue/BlackDescription Installs Light-Heavy, Heavy and Extra-Heavy cross section cable ties. Durable all steel construction with comfortable rubber handles. Color identification: blue handle grips Body: all black steel Weight: 9 oz. (256g)Pricing Description Cable Tie Tool, Low Volume, For use with Lt-Hvy, Hvy and Extra-Hvy Ties Part Features Durable, all steel construction with comfortable plastic handles.CE Compliant NoWeight (oz.) 9.0Weight (g) 256Used With Cable Ties LH, H, EHMin. Order Qty. 1.0000不锈钢扎带枪 RT2HT∙型号:RT2HT说明PANDUIT CABLE TIE GUN RT2HTInstallation tool for use with the following stainless steel cross section ties:Type MLT, MLTFC, and MLTD:Extra-heavy and super-heavyUsed with custom length banding cross sections:Type MB and MBC: Extra-heavyand super-heavyWidth of tool nose 2.60" (66.0mm).Product DetailsStd. Pkg. Qty. 1Std. Ctn. Weight (lb) 0.0000Std. Ctn. Volume (cf) 0.0000Std. Pallet Weight (lb) 420.0000Std. Pallet Volume (cf) 0.000000RoHS Compliancy Status CompliantPart Description Installation tool for use with the following stainless steel cross section ties:Type MLT, MLTFC, and MLTD: Extra-heavy and super-heavyUsed with custom length banding cross sections:Type MB and MBC: Extra-heavy and super-heavyWidth of tool nose 2.60" (66.0mm).Product Type Cable Tie and Custom Length Banding ToolColor BlackPricing Description Installation Tool, MLT Ties, Controlled Tension, EH & SH Cross SectionCE Compliant NoWeight (oz.) 40Weight (g) 1134Used With Cable Ties Extra-heavy and super-heavyUsed.MLT TiesMin. Order Qty. 1.0000美国panduit(泛达)不锈钢扎带枪 GS4MT∙型号:GS4MT说明PANDUIT CABLE TIE GUN GS4MTInstallation tool for use with the following stainless steel cross section ties:Type MLT: Standard, light-heavy,and heavyType MLTC, MLTFC, and MLTD: HeavyUsed with custom length banding cross sections:Type MB:Standard and heavyType MBC: HeavyProduct DetailsStd. Pkg. Qty. 1Std. Ctn. Weight (lb) 0.0000Std. Ctn. Volume (cf) 0.0000Std. Pallet Weight (lb) 0.0000Std. Pallet Volume (cf) 0.000000RoHS CompliancyStatusRoHS directive is not applicablePart Description Installation tool for use with the following stainless steel cross section ties:Type MLT: Standard, light-heavy, and heavyType MLTC, MLTFC, and MLTD: HeavyUsed with custom length banding cross sections:Type MB: Standard and heavyType MBC: HeavyProduct Type Cable Tie and Custom Length Banding ToolMaterial Metal tool with powder coat finishColor Light Gray/BlackPricing Description Installation Tool, MLT Ties, Controlled Tension Gun Style, S LH H Cross SectionStandards QPL per Mil. Std. SAE AS81306 and Mil. Spec. SAE AS90387-3CE Compliant NoWeight (oz.) 19.2Weight (g) 544Used With Cable Ties Standard and heavyType MBC: HeavyMin. Order Qty. 1.0000扎带枪GS2BL型号:GS2BL说明PANDUIT CABLE TIE GUN GS2BLSame as GS2B except handle span is reduced 25% - for workers with smaller hands. Qualified Product Listedper Mil. Std. MS90387-1 and Mil. Spec. MIL-T-81306A. Color Identification: Black Trigger Handle and SelectorKnob Body: Maroon Metal Housing Weight: 11.5 oz. (327g).Product DetailsStd. Pkg. Qty. 1Std. Ctn. Weight (lb) 0.0000Std. Ctn. Volume (cf) 0.0000Std. Pallet Weight (lb) 0.0000Std. Pallet Volume (cf) 0.000000RoHS Compliancy Status RoHS directive is not applicablePart Description Same as GS2B except handle span is reduced 25% - for workers with smaller hands. QualifiedProduct Listed per Mil. Std. MS90387-1 and Mil. Spec. MIL-T-81306A. Color Identification:Black Trigger Handle and Selector Knob Body: Maroon Metal Housing Weight: 11.5 oz. (327g)Product Type Cable Tie ToolsMaterial Metal tool with powder coat finishColor BurgundyMil. Std. Part Number MS90387-1Pricing Description Cable Tie Tool for M, I, S ties, Small handle span, Adjustable tensionStandards—Part FeaturesMetal tool with a durable powder coat finish. Shorter handle reach (than GS2B) for users withsmaller hands.CE Compliant NoWeight (oz.) 11.5Weight (g) 327Used With Cable Ties M, I, SMin. Order Qty. 1.0000∙美国panduit(泛达)扎带枪 GTSL∙型号:GTSL说明PANDUIT CABLE TIE GUN GTSLSimilar to GTS except shorter handle reach and stroke. Ergonomic design. Installs Subminiature, Miniature,Intermediate and Standard cross section cable ties. Color Identification: Maroon Trigger Handle and SelectorKnob Body: Gray Impact Resistant Resin Housing Weight: 8.8 oz. (249g) Product DetailsStd. Pkg. Qty. 1Std. Ctn. Weight (lb) 0.0000Std. Ctn. Volume (cf) 0.0000Std. Pallet Weight(lb)0.0000Std. Pallet Volume(cf)0.000000RoHS CompliancyStatusRoHS directive is not applicablePart Description Similar to GTS except shorter handle reach and stroke. Ergonomic design. Installs Subminiature, Miniature, Intermediate and Standard cross section cable ties. Color Identification: Maroon Trigger Handle and Selector Knob Body: Gray Impact Resistant Resin Housing Weight: 8.8 oz. (249g)Product Type Cable Tie ToolsMaterial Impact resistant resin housingColor Dark Gray/BurgundyMil. Std. Part Number MS90387-1Pricing Description Ergonomic Cable Tie Tool for SM, M, I, S ties, Small handle span, Adj tensionStandards QPL per Mil. Std. SAE AS81306 and Mil. Spec. SAE AS90387-5Part FeaturesErgonomic design with impact resistant resin housing, narrow nose, and cushion handle. Shorterhandle reach (than GTS) for users with smaller hands.CE Compliant NoWeight (oz.) 8.8Weight (g) 249Used With CableTiesSM, M, I, SMin. Order Qty. 1.0000∙美国panduit(泛达)扎带枪 GS4EH∙型号:GS4EH说明PANDUIT CABLE TIE GUN GS4EHInstalls Light-Heavy, Heavy and Extra-Heavy cross section cable ties.Color Identification: Blue Trigger Handleand Selector KnobBody: Gray Metal HousingWeight: 16 oz. (454g)Product DetailsStd. Pallet Volume (cf)0.000000Pocket catalog part description Metal Tool; installs Light-Heavy, Heavy and Extra-Heavy cross section cable ties, 16 oz.; blue trigger handleStd. Pkg. Qty. 1Std. Ctn. Weight (lb) 0.0000Std. Ctn. Volume (cf) 0.0000Std. Pallet Weight (lb) 0.0000RoHS Compliancy Status RoHS directive is not applicablePart DescriptionInstalls Light-Heavy, Heavy and Extra-Heavy cross section cable ties.Color Identification: BlueTrigger Handle and Selector KnobBody: Gray Metal HousingWeight: 16 oz. (454g)Product Type Cable Tie ToolsMaterial Metal tool with powder coat finishColor Light Gray/BlueMil. Std. Part Number MS90387-4Pricing Description Cable Tie Tool for LH, H, EH ties, Adjustable tensionStandards QPL per Mil. Std. SAE AS81306 and Mil. Spec. SAE AS90387-4Part Features Metal tool with a durable powder coat finish.CE Compliant NoWeight (oz.) 16.0Weight (g) 454Used With Cable Ties LH, H, EHMin. Order Qty. 1.0000∙美国panduit(泛达)扎带枪 GTH∙型号:GTH说明PANDUIT CABLE TIE GUN GTHErgonomic design. Installs Standard, Heavy-Standard, Light-Heavy and Heavy cross section cable ties. ColorIdentification: Red Trigger Handle, Cushion Sleeve and Selector Knob Body: Gray Impact Resistant ResinHousing Weight: 12.0 oz. (340g)Product DetailsStd. Pkg. Qty. 1Std. Ctn. Weight (lb) 0.0000Std. Ctn. Volume (cf) 0.0000Std. Pallet Weight(lb)0.0000Std. Pallet Volume(cf)0.000000RoHS CompliancyStatusRoHS directive is not applicablePart Description Ergonomic design. Installs Standard, Heavy-Standard, Light-Heavy and Heavy cross section cable ties. Color Identification: Red Trigger Handle, Cushion Sleeve and Selector Knob Body: Gray Impact Resistant Resin Housing Weight: 12.0 oz. (340g)Product Type Cable Tie ToolsMaterial Impact resistant resin housingColor Dark Gray/RedMil. Std. Part Number MS90387-2Pricing Description Ergonomic Cable Tie Tool for S, HS, LH, H ties, Adjustable tensionStandards QPL per Mil. Std. SAE AS81306 and Mil. Spec. SAE AS90387-2Part Features Ergonomic design with impact resistant resin housing, narrow nose, and cushion handle. CE Compliant NoWeight (oz.) 12.0Weight (g) 340Used With CableTiesS, HS, LH, HMin. Order Qty. 1.0000∙ 美国panduit (泛达)不锈钢扎带枪 ST2MT ∙ 型号:ST2MT说明PANDUIT CABLE TIE GUN ST2MTInstallation tool for use with the following stainless steel cross section ties:Type MLT: Standard, light-heavy,heavy and extra-heavyType MLTFC: Standard, heavy and extra-heavyType MLTC and MLT-LPAL: HeavyTypeMLTD: Heavy and extra-heavyUsed with custom length banding cross sections:Type MB: Standard, heavy andextra-heavyType MBC: Heavy and extra-heavyProduct DetailsStd. Pkg. Qty.1 Std. Ctn. Weight (lb)0.0000 Std. Ctn. Volume (cf)0.0000 Std. Pallet Weight (lb)0.0000 Std. Pallet Volume (cf)0.000000RoHS Compliancy Status RoHS directive is not applicablePart DescriptionInstallation tool for use with the following stainless steel cross section ties:Type MLT: Standard,light-heavy, heavy and extra-heavyType MLTFC: Standard, heavy and extra-heavyType MLTCand MLT-LPAL: HeavyType MLTD: Heavy and extra-heavyUsed with custom length bandingcross sections:Type MB: Standard, heavy and extra-heavyType MBC: Heavy and extra-heavyDescriptionUsed with heavy section Pan-Alum™ Type MLT Ties and standard and heavy cross sectionPan-Steel® Type MLT Ties.ColorBlack Pricing DescriptionInstallation Tool, MLT Ties, Twist Cut Off, LH & SH Cross Section Product TypeCable Tie and Custom Length Banding Tool Weight (oz.)16 Weight (g)454 Used With Cable TiesMLT/MLTC/MLTFC/MLTDH Ties. Min. Order Qty. 1.0000∙∙ 气动扎带枪 PTS∙ 型号:PTS说明PANDUIT CABLE TIE GUN PTSErgonomic lightweight design installs Subminiature, Miniature, Intermediate, or Standard cross section cable tiesColor identification: Gray Impact Resistant Resin Housing with Black Selector Knob and TriggerWeight: 17.3 oz. (490g).Product DetailsStd. Pkg. Qty. 1Std. Ctn. Weight (lb) 0.0000Std. Ctn. Volume (cf) 0.0000Std. Pallet Weight (lb) 0.0000Std. Pallet Volume (cf) 0.000000RoHS Compliancy Status RoHS directive is not applicablePart Description Ergonomic lightweight design installs Subminiature, Miniature, Intermediate, or Standard cross section cable tiesColor identification: Gray Impact Resistant Resin Housing with Black Selector Knob and TriggerWeight: 17.3 oz. (490g).Product Type Cable Tie ToolsMaterial Impact resistant resin housingColor Dark Gray/BlackPricing Description Pneumatic Cable Tie Tool for Submin, Min, Int, and Std Ties - LeasedPart FeaturesErgonomic design with impact resistant resin housing and black knob;replacement parts canbe part of a scheduled maintenance program.CE Compliant YesWeight (oz.) 17.3Weight (g) 490Used With Cable Ties SM, M, I, SMin. Order Qty. 1.0000∙全自动扎带枪 PAT2S∙型号:PAT2S说明PANDUIT AUTOMATIC CABLE TIE GUN PAT2SLightweight, ergonomic tool headProduct DetailsStd. Pkg. Qty. 1Std. Ctn. Weight (lb) 0.0000Std. Ctn. Volume (cf) 0.0000Std. Pallet Weight (lb)352.8000Std. Pallet Volume (cf) 0.000000RoHS Compliancy Status Compliant in EMEAPart DescriptionLightweight, ergonomic tool head Product TypeAutomatic Cable Tie Tool Length (ft.)— Length (m)— ColorBlack DescriptionTool Head for cable ties up to 2.00" (51mm) bundle diameter (P/N PLT2S-VMR) Pricing DescriptionAutomatic Cable Tie Tool Head for PLT2S-VMR Cable Ties - Plastic Ergo Housing TypeTool Head Used with Installation Tool— CE CompliantYes Max. Bundle Diameter (mm)49 Max. Bundle Diameter (In.)1.94 Weight (lb.)3.23 Weight (g)1470 Used With Cable TiesPLT1.5M-XMR Min. Order Qty. 1.0000∙ 不锈钢扎带枪 RT2HTN ∙ 型号:RT2HTN说明PANDUIT CABLE TIE GUN RT2HTNNarrow nose installation tool for use with the following stainless steel cross section ties:Type MLT, MLTFC, andMLTD: Extra-heavy and super-heavyUsed with custom length banding cross section:Type MB and MBC:Extra-heavy and super-heavyWidth of tool nose 1.06" (27.0mm).Product DetailsStd. Pkg. Qty.1 Std. Ctn. Weight (lb)0.0000 Std. Ctn. Volume (cf)0.0000 Std. Pallet Weight (lb)460.8000 Std. Pallet Volume (cf)0.000000 RoHS Compliancy Status CompliantPart DescriptionNarrow nose installation tool for use with the following stainless steel cross sectionties:Type MLT, MLTFC, and MLTD: Extra-heavy and super-heavyUsed with customlength banding cross section:Type MB and MBC: Extra-heavy and super-heavyWidth oftool nose 1.06" (27.0mm).Product TypeCable Tie and Custom Length Banding Tool ColorBlack Pricing DescriptionInstallation Tool, MLT Ties, Controlled Tension EH & SH Cross Section CE Compliant NoWeight (oz.) 40Weight (g) 1134Used With Cable Ties Extra-heavy and super-heavyUsed.MLT TiesMin. Order Qty. 1.0000∙美国panduit(泛达)扎带枪 GS4H∙型号:GS4H说明PANDUIT CABLE TIE GUN GS4HInstalls Standard, Heavy-Standard, Light-Heavy and Heavy cross section cable ties. Qualified Product Listed perMil. Std. MS90387-2 and Mil. Spec. MIL-T-81306A.Color Identification: Red Trigger Handle and SelectorKnobBody: Gray Metal Housing Weight: 16 oz. (454g)Product DetailsStd. Pkg. Qty. 1Std. Ctn. Weight (lb) 0.0000Std. Ctn. Volume (cf) 0.0000Std. Pallet Weight (lb) 0.0000Std. Pallet Volume (cf) 0.000000RoHS Compliancy Status RoHS directive is not applicablePart Description Installs Standard, Heavy-Standard, Light-Heavy and Heavy cross section cable ties. Qualified Product Listed per Mil. Std. MS90387-2 and Mil. Spec. MIL-T-81306A.Color Identification: Red Trigger Handle and Selector KnobBody: Gray Metal Housing Weight: 16 oz. (454g)Product Type Cable Tie ToolsMaterial Metal tool with powder coat finishColor Light Gray/RedMil. Std. Part Number MS90387-2Pricing Description Cable Tie Tool for S, HS, LH, H ties, Adjustable tensionStandards QPL per Mil. Std. SAE AS81306 and Mil. Spec. SAE AS90387-2 Part Features Metal tool with a durable powder coat finish.CE Compliant NoWeight (oz.) 16.0Weight (g) 454Used With Cable Ties S, HS, LH, HMin. Order Qty. 1.0000∙扎带枪GTS∙型号:GTS说明PANDUIT CABLE TIE GUN GTSErgonomic design. Installs Subminiature, Miniature, Intermediate and Standard cross section cable ties. Qualified ProductListed per Mil. Std. MS90387-1 and Mil. Spec. MIL-T-81306A.Color Identification: Black Trigger Handle, Cushion Sleeveand Selector KnobBody: Gray Impact Resistant Resin Housing Weight: 9.8 oz. (278g).Product DetailsStd. Pkg. Qty. 1Std. Ctn. Weight (lb) 0.0000Std. Ctn. Volume (cf) 0.0000Std. Pallet Weight (lb) 0.0000Std. Pallet Volume (cf) 0.000000RoHS Compliancy Status RoHS directive is not applicablePart Description Ergonomic design. Installs Subminiature, Miniature, Intermediate and Standard cross section cable ties. Qualified Product Listed per Mil. Std. MS90387-1 and Mil. Spec. MIL-T-81306A.Color Identification: Black Trigger Handle, Cushion Sleeve and Selector KnobBody: Gray Impact Resistant Resin Housing Weight: 9.8 oz. (278g)Product Type Cable Tie ToolsMaterial Impact resistant resin housingColor Dark Gray/BlackMil. Std. Part Number MS90387-1Pricing Description Ergonomic Cable Tie Tool for SM, M, I, S ties, Adjustable tensionStandards QPL per Mil. Std. SAE AS81306 and Mil. Spec. SAE AS90387-1Part Features Ergonomic design with impact resistant resin housing, narrow nose, and cushion handle.CE Compliant NoWeight (oz.) 9.8Weight (g) 278Used With Cable Ties SM, M, I, SMin. Order Qty. 1.0000扎带枪、扎线枪 GS2B∙型号:GS2B说明PANDUIT CABLE TIE GUN GS2BInstalls Miniature, Intermediate and Standard cross section cable ties. Qualified Product Listed per Mil. Std. MS90387-1 andMil. Spec. MIL-T-81306A. Color Identification: Black Trigger Handle and Selector KnobBody: Gray Metal HousingWeight:11.5 oz. (327g).Product Details。

杰尼斯科技产品选购指南说明书

MOST POPULAR MODEL HIGHLIGHTED!Single Junction Reference Electrode, PHE-3111,£35.50Comes with complete operator’s manual.Ordering Examples:ISE-8711,ammonium electrode,£147.ISE-8756,silver/sulfide electrode,£147.C-22PHI-359,£845,bench toppH meter shown smallerthan actual size,see page B-33.C-23CANADA www.omega.ca Laval(Quebec)1-800-TC-OMEGA UNITED KINGDOM Manchester,England0800-488-488GERMANY www.omega.deDeckenpfronn,Germany************FRANCE www.omega.fr 088-466-342BENELUX www.omega.nl 0800-099-33-44UNITED STATES 1-800-TC-OMEGA Stamford,CT.CZECH REPUBLIC www.omegaeng.cz Karviná,Czech Republic596-311-899TemperatureCalibrators, Connectors, General Test and Measurement Instruments, Handheld Instruments for Temperature Measurement, Ice Point References, Indicating Labels,Crayons, Cements and Lacquers, Infrared Temperature Measurement Instruments, Recorders, Relative Humidity Measurement Instruments, PT100 Probes, PT100 Elements,Temperature & Process Meters, Timers and Counters,Temperature and Process Controllers and Power Switching Devices, Thermistor Elements, Probes and Assemblies,Thermocouples, Thermowells and Head and WellAssemblies, Transmitters, Thermocouple Wire, RTD ProbesPressure,Strain and ForceDisplacement Transducers, Dynamic Measurement Force Sensors, Instrumentation for Pressure and StrainMeasurements, Load Cells, Pressure Gauges, PressureReference Section, Pressure Switches, Pressure Transducers,Proximity Transducers, Regulators, Pressure Transmitters,Strain Gauges, Torque Transducers, ValvespH and ConductivityConductivity Instrumentation,Dissolved OxygenInstrumentation,Environmental Instrumentation,pH Electrodes and Instruments,Water and Soil Analysis InstrumentationHeatersBand Heaters,Cartridge Heaters,Circulation Heaters,Comfort Heaters,Controllers,Meters and SwitchingDevices,Flexible Heaters,General Test and Measurement Instruments,Heater Hook-up Wire,Heating Cable Systems,Immersion Heaters,Process Air and Duct,Heaters,Radiant Heaters,Strip Heaters,Tubular HeatersFlow and LevelAir Velocity Indicators,Doppler Flowmeters,LevelMeasurement,Magnetic Flowmeters,Mass Flowmeters,Pitot Tubes,Pumps,Rotameters,Turbine and Paddle Wheel Flowmeters,Ultrasonic Flowmeters,Valves,Variable Area Flowmeters,Vortex Shedding FlowmetersData AcquisitionAuto-Dialers and Alarm Monitoring Systems,Communication Products and Converters,Data Acquisition and Analysis Software,Data LoggersPlug-in Cards,Signal Conditioners,USB,RS232,RS485and Parallel Port Data Acquisition Systems,Wireless Transmitters and Receivers。

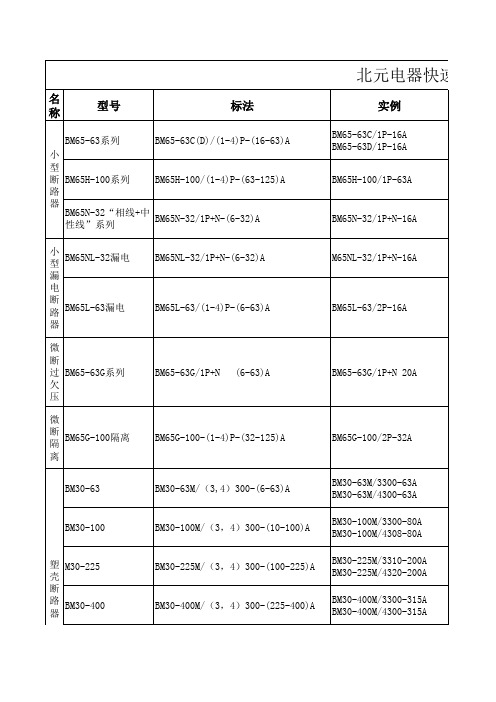

北元电器快速选型表

型号

标法

BM65-63系列

BM65-63C(D)/(1-4)P-(16-63)A

小

型

断 BM65H-100系列 BM65H-100/(1-4)P-(63-125)A

路

器

BM65N-32“相线+中 性线”系列

BM65N-32/1P+N-(6-32)A

北元电器快速选型表

实例

BM65-63C/1P-16A BM65-63D/1P-16A

BM30E-100/3400 -(10-100)A

BM30L-100/3400B-80A

BM30E-225/3400-(100-250)A BM30E-400/3400-(200-400)A BM30E-630/3400-(400-630)A

BM30L-225/3400B-200A BM30L-400/3400B-350A BM30L-630/3400B-500A

过载、短路、漏电 保护

用于交流50Hz线路,230V

6A、10A、16A、20A、 对建筑和类似场所

25A、32A、40A、50A、 有过载,短路,过 用于交流50Hz线路,230V

63A

欠压保护。

32A、63A、80A、100A、 隔离

用于交流50Hz或60Hz线路,400V以下

6A、10A、16A、20A、 25A、32A、40A、50A、 63A

操作和柜外操作

故障危害。

4000A、5000A、6300A

M65NL-32/1P+N-16A BM65L-63/2P-16A BM65-63G/1P+N 20A BM65G-100/2P-32A

BM30-63

BM30-63M/(3,4)300-(6-63)A

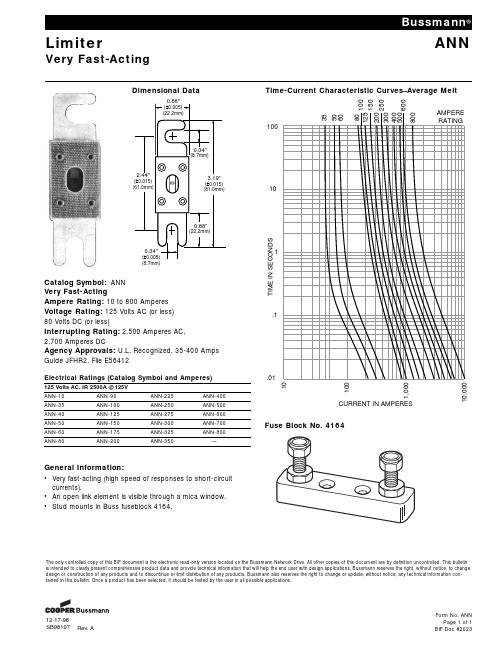

柏斯曼快速断路器产品说明书

Form No. ANN Page 1 of 1BIF Doc #202312-17-98SB98107Rev. ACatalog Symbol:ANN Very Fast-ActingAmpere Rating: 10 to 800 Amperes Voltage Rating: 125 Volts AC (or less)80 Volts DC (or less)Interrupting Rating:2,500 Amperes AC,2,700 Amperes DCAgency Approvals: U.L. Recognized, 35-400 Amps Guide JFHR2, File E56412The only controlled copy of this BIF document is the electronic read-only version located on the Bussmann Network Drive. All other copies of this document are by definition uncontrolled. This bulletin is intended to clearly present comprehensive product data and provide technical information that will help the end user with design applications. Bussmann reserves the right, without notice, to change design or construction of any products and to discontinue or limit distribution of any products. Bussmann also reserves the right to change or update, without notice, any technical information con-tained in this bulletin. Once a product has been selected, it should be tested by the user in all possible applications.Dimensional Data10,000101001,000CURRENT IN AMPERES100101.1.01T I M E I N S E C O N D SAMPERE RATING35506080100125150200300400500250600800Electrical Ratings (Catalog Symbol and Amperes)125 Volts AC, IR 2500A @ 125V ANN-10ANN-90ANN-225ANN-400 ANN-35ANN-100ANN-250ANN-500 ANN-40ANN-125ANN-275ANN-600 ANN-50ANN-150ANN-300ANN-700ANN-60ANN-175ANN-325ANN-800ANN-80ANN-200ANN-350—Time-Current Characteristic Curves–Average MeltGeneral Information:•Very fast-acting (high speed of responses to short-circuit currents).•An open link element is visible through a mica window.•Stud mounts in Buss fuseblock 4164.Fuse Block No. 4164。

ATNS自动电源转换开关产品目录

25

55

10000 10000

10000 10000

6000 6000

6000 6000

b b AC220V 2s

b b AC220V 3s

b b AC220V 3s

b b AC220V 3s

b v b b

b v b b

b b b b

b b b b

b

b

b

b

!"# IEC60947-6

EN60947-6 7

ATNS63

C65

ATNS100

NS100

1~63 440 230/400 N 6 100% AC33B b 2,3,4 H 10 -

16~100 750 690 N 85 25 25 18 18 8 100% AC33B b 3,4 H 100 70 65 50 35 10

(

!"# !

!$%&'()) 25 55

b

b

!"# !"# ! ! ! !"# ( ) !"#$ 5S ! ! $%&

b

b b !" !"

0 30 0 30 b

5

15 5%

0-255

5

15 5%

0-255

b

! b

b v Modbus

AC220V 50/60Hz

AC220V 50/60Hz

v: 8

!

A

!

A

!"#$%&'()*"+, !"#$% !"# !

!"# ! ! !

9

!"

ECN3067中文资料

4.Electrical CharacteristicsUnless otherwise specified, Vcc=15V,VS=325VSuffix T: Top arm B: Bottom ArmTa = 25°CNo.Items Symbols Terminal MIN.TYP.MAX.Unit Condition 1Standby Current IS VS1,VS2--0.25mA Input=“H”2ISB BU-MU,BV-MV,BW-MW -1530m A BU-MU,BV-MV,BW-MW=15V3ICC VCC-1020mA4Output device FVD VFT MU,MV,MW- 2.5 3.5V I=1.5APW<5ms 5VFB MU,MV,MW- 2.5 3.5V I=1.5APW<5ms 6Turn On DelayTimeTdONT MU,MV,MW- 1.0 2.0m s7TdONB MU,MV,MW- 1.0 2.0m s I=1.5A8Turn Off Delay Time TdOFFT MU,MV,MW- 1.0 2.0m s ResistiveLoad9TdOFFB MU,MV,MW- 1.0 2.0m s10Diode FVD VFDT MU,MV,MW- 2.5 3.5V I=1.5A 11VFDB MU,MV,MW- 2.5 3.5V PW<5ms 12Input Voltage VIH UT,VT,WT, 3.5--V13VIL UB,VB,WB-- 1.5V14Input Current IIL UT,VT,WT,UB,VB,WB -100--m A Input=0VNote 115IIH-30--m A Input=5VNote 1 16VB Output Voltage VB CB 6.87.58.2V17VB Output Current IB CB50--mA d VLOAD=0.2V18Over Currentreference VoltageVref RS0.450.50.55V19Fault output onresistanceRonf F-300400W Note 2 20Vcc Under Voltage Negative Going Vuvb VCC9.811.413.0V Note 3 21Reset Hysterisis Vrhb VCC0.10.40.9V22V BU,BV,BW Under Negative Going Vuvt BU-MU,BV-9.811.413.0V Note 4 23Voltage Reset Hysterisis Vrht MV,BW-MW0.10.40.9V24Fault reset delay time tflrs F 6.51020m s25OC shutdown delay toc RS- 2.0 3.0m sNote 1. Pull Up Resistance are typically 200k WNote 2. The equivalent circuit around F terminal is shown below.Note 3. Please see item 5.4.Note 4. Please see item 5.4.CBF5. Function 5.1. Truth TableTerminal Input Output UT,VT,WT,L ON UB,VB,WB H OFF UT,UB UT&UB=L OFF VT,VB VT&VB=L OFF WT,WBWT&WB=LOFF5.2 Timing Chart(Example of Brushless Motor drive)U TV T W TU BV B W BM U O U T P U T M VO U T P U TM W O U T P U T5.3 Over Current OperationThis IC detects over current by checking the Voltage drop at the external resistance RS. When the input voltage at RS terminal exceeds the internal reference voltage (Vref), this IC turns off the output of all arms circuit and F terminal output becomes “L”. After over current detection, reset is done when all six inputs are referenced to high level. In case of not using this function, please connect this terminal to GL terminal (within 100 W ).5pFVreftyp 220k Wtyp 200k Wtyp 300WVBRSRS terminal inner equivalent circuittyp Reset signalLatch SRTop ArmBottom Arm5.4 Undervoltege Detection1) When Vcc supply voltage becomes below Vuvb(11.4V typ.), all of the IGBTs shut off and F terminal output becomes “L”.2) When between BU-MU, BV-MV or BW-MW voltage become below Vuvt(11.4V typ.), top armIGBT of under voltage detected phase shuts off. In this time, F terminal output doesn’t change. Note 1. When VCC supply voltage becomes lower, driving capability of IGBT also becomes lower. Accordingly, power dissipation becomes higher and this causes temperature raise of IC.In case of junction temperature exceeds 135°C, IC may deteriorate or breakdown.5.5 Definition of switching delayInput(UT,UB VT,VB WT,WB) Output Current(MU,MV,MW)Input(UT,UB VT,VB WT,WB) RSFOutput(MU,MV,MW)50%50%20%80%Tdon Tdoff50%50%50%50%tflttoc tflrs50%6.Standard Application No ITEMSSYMBOLS UNIT VALUESTOL.REMARK1VB Smoothing Capacitor Co m F ³ 0.22Stress Voltage 8V 2Boot Strap Capacitor Cb m F ³ 3.3Stress Voltage Vcc 3Boot Strap DiodeDb -Hitachi DFG1C6,DFM1F6 or equivalent Breakdown Voltage : ³ 600V,Current : ³1.0A Trr : £ 200ns4Sensing Resistor Rs W Note15Load resistor for F terminal Rf k W ³ 5.66Resistor of boot strap Rb W Note2Note1. Over-current detection level is determined by the following equation. Io=Vref / Rs (A)Note2. Current limiting resistance Rb is prevention over current protection from operation at initial charge. Rb is about determined by the following equation. ibpeak=Vref / Rs = VCC / Rb Rb > ( VCC * Rs ) / Vref * 2( * 2 shows the margin. Top arms are off state. Ibpeak is one phase only.) ibpeak : Peak current of the initial charge for Cb Vref ; Over Current reference VoltageVB FaultBGH1GL FUT VT WTUB VB WBVccVs2C B SR RfV Mu MvMwMotorVCCControl IC VsMicroprocessorCRS BuBvBwSupplyTop Arm DriverDriverBottom Arm OC protectionInput bufferTo microprocessor power supplyCb Cb CbDb Db DbUV detection Vs1RbGH2Block Diagram(example for boot strap)7. Pin AssignmentPin No.Terminal Name Pin No.Terminal Name 1MV 13VB 2VS214UB 3MW 15WT 4GH216VT 5BW 17UT 6BV 18BU 7VCC 19VS18CB 20Non Connection 9GL 21Non Connection 10F 22MU 11RS 23GH112WB 8. Package OutlineECN3067SLR (SP-23TFA)ECN3067SLV (SP-23TE)9.Package Dimension ( unit: mm ) (1) ECN3067SLV5.0819.81f 3.80±0.052-R1.84±0.194.32±0.051.120.7027.941.2717.50±0.133.80±0.122.7917.78±0.330.404.294.50±0.121.55+0.06-0.04+0.05-0.130.18±0.25231+0.09-0.10.25 M(2) ECN3067SLR6.8±1.09.1±1.0+0.0927.940.717.50±0.131.123.80±0.0510.70±0.121.271.55+0.054.5±0.120.42 t y p2.2±0.316.3±0.50°+10° -0°0°+10° -0°f 3.80±0.0519.8130.18±0.254.32±0.051232.792-R1.84±0.190.25M-0.1-0.1P9/9ECN306710.Note of the design margin under the SOAF ollowing figure Indicates the evaluation as the reference of the SOA (safetyoperation area) under the Tj=135°C ( the junction temperature is equal to 135°C) . Dot mark ( · ) shows the points of the IC destruction.The plural points under the same voltage Indicates the dispersion of the sample.In this figure, IM and VM are the current and the voltage at the terminal of motorwiring at the change of phase (turn on and turn off).Fig. The Safety Operation Area in ECN3067 (reference)0246810100200300400500600VM (V)I M (A )Tj=25'CTj=135'CHITACHI POWER SEMICONDUCTORSFor inquiries relating to the products, please contact nearest overseas representatives which is located “Inquiry” portion on the top page of a home page.Hitachi power semiconductor home page address http://www.hitachi.co.jp/pse。

AT100中文

总体液位,界面液位,以及温度输出的电信号,实际液位值,温

度值, 带有偏移量的实际液位值等, 该装置可在 AT100 上通用,

极易方便用户订备件并减少备件量

2, 极高精度: 满量程的 0.01%

3, 标定极其简单,无需实标,仅仅只需按按钮或者使用 HART 或 DE 通

讯

讯协议

4, 对于重新标定或忘记标定值, 无需重新校验

/i 过程连接

代码 说明 X 无, 用于/SW1,/SW2,/SW3 探杆形式 CF 标准的是 3/4”MNPT 可调的压紧接头

注意: 对于/F1,/F2 探杆形式, 采用的是 1” MNPT 可调的压紧接头 FL 松套法兰或塞头, 与上述压紧接头相配套,

(具体形式,材质,压力等级请看 FLNG-0202-1 法兰设计章节) WP 焊接式过程连接

六 :仪表选型表:

AT100 /a /b /c /d /e /f /g /h /I /j /k /a 传感器杆(探杆)材质

代码 说明 S6 316L 标准不锈钢 A2 20#合金 HC 哈氏合金 C-276 TF 在 316L 不锈钢传感管外带 PFA 特氟隆夹套(厚 1/16”)

最大温度和压力为: 177℃ 和 3.5KG/CM^2

/f 电子装置带有一个模拟量的输出

代码 X M1 M2 M3 M4A M4B M5A

说明 无 一个液位 一个液位, 液晶显示 一个液位, HART 协议或 HONEYWELL DE 协议,DE 协议请加后缀”D” 一个液位, 液晶显示, HART 协议或 DE 协议,DE 协议请加后缀”D” 两个液位, 液晶显示, HART 协议或 DE 协议,DE 协议请加后缀”D” 一个液位,一个温度点, 液晶显示, HART 协议

EPM3064ATC100-10中文资料(Altera)中文数据手册「EasyDatasheet - 矽搜」

行业标准PC和UNIX工作站为基础EDA工具.该 软件基于Windows个人电脑,以及太阳SPARC工作站运行, HP 9000系列700/800工作站.

有关开发工具详细信息,请参阅 可编程逻辑开发系统和软件数据表 Quartus可编程逻辑开发系统和软件数据表.

MAX+PLUS II

速度等级

–5

–6

–7

–10

v

v

v

v

v

v

v

v

v

v

v

对MAX 3000A架构支持100%晶体管到晶体管逻辑(TTL)仿真和高密度小 规模集成(SSI),中等规模集成(MSI),和大规模集成电路( LSI)逻辑功能.最大3000A架构轻松集成多个设备,从好朋友,GAL和22 V10s以MACH和PLSI设备.

SPARCstations和HP 9000系列700/800工作站

■ 通过EDIF提供额外设计输入和仿真支持

2 0 0和3 0 0网表文件,参数化模块库(LPM)

Verilog HDL语言,VHDL等接口,从流行EDA工具

第三方制造商,如Cadence公司,楷模逻辑,导师

显卡,OrCAD,Synopsys公司,Synplicity公司和VeriBest

而

最大3000A架构包括以下内容:

■ 逻辑阵列模块(LAB) ■ 宏单元 ■ 扩展乘产品项(共享和并联) ■ 可编程互连阵列(PIA) ■ I / O控制块

最大3000A架构包括四个专用输入,可作为通用输入或高速,全局控制

信号(时钟,清,和两个输出使能信号),每个宏单元和I / O引脚

.

图1

示出MAX 3000A设备体系结构.

ATX-3064线束测试仪使用说明书,西安安泰电子科技有限公司

线束测试仪ATX-3064使用说明书V1.1目录一、产品简介 (1)1.1产品特点 (1)1.2结构特点 (1)二、使用须知 (1)2.1注意事项 (1)2.2预先检查 (2)三、面板介绍 (2)3.1前面板介绍 (2)3.2后面板介绍 (3)四、产品软件介绍 (3)4.1软件安装 (3)4.2软件主界面 (5)4.2.1系统设置 (6)4.2.2分段测试 (7)4.2.3开始测试 (14)4.2.4自定义配置 (17)五、质保 (20)一、产品简介ATX-3000系列是高压线束测试仪,专用于各种线缆,线束和排线品质及连接可靠性检验的多功能,自动化的线束参数测试系统。

设备可单机操作,亦可连接至电脑操作,基于模块化设计结构,四线制电阻测试,测试精度高。

兼容智能化测试软件及大型数据库,帮助客户进行数据对比分析。

每次开机系统自检,以确保测试系统准确、可靠运行。

1.1产品特点:1、高速的导通测试,自学习通断测试;2、低压电阻测试(<20kΩ),精度±1%;3、直流绝缘电阻测试DC50V~750V,R:10MΩ~1000MΩ(DC精度±5%,R精度±10%);4、交流耐压测试AC50V~500V,I:0.5mA~5mA(AC精度±5%,I精度0.2mA);5、采用板卡式结构,可根据客户需求灵活快速扩展;6、高压放电检测功能,提高检测安全性;7、测试报告自动记录功能;8、RS232,USB等接口可供选择。

1.2结构特点:1、测试板采取模块化结构,方便根据客户需求快速扩展;2、测试板采用64P牛角插座连接器,插拔灵活,可承载较大的电流和测试电压,从而保证了测试的可靠性;3、模块化的测试板设计,方便快速的通道扩展及后期维护。

二、使用须知在使用本仪器前,请务必详细阅读安全注意事项,并遵照执行,避免由于误操作降低仪器的使用寿命或造成不必要损失。

2.1注意事项(1)请勿自行在仪器上安装替代零件,或执行任何未经授权的修改。

MAX306中文资料

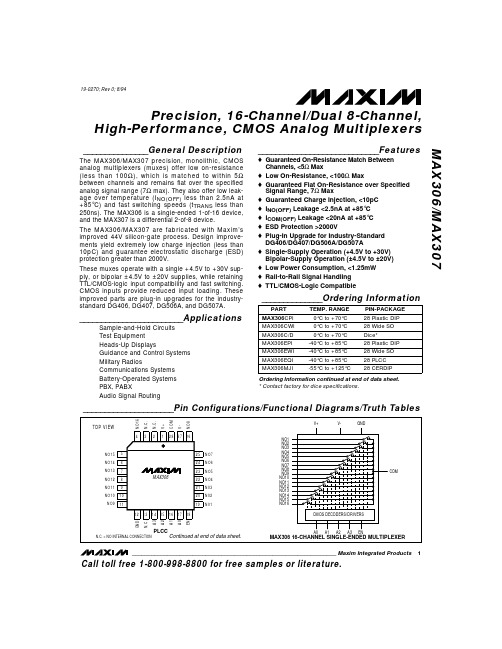

_______________General DescriptionThe MAX306/MAX307 precision, monolithic, CMOS analog multiplexers (muxes) offer low on-resistance (less than 100Ω), which is matched to within 5Ωbetween channels and remains flat over the specified analog signal range (7Ωmax). They also offer low leak-age over temperature (I NO(OFF)less than 2.5nA at +85°C) and fast switching speeds (t TRANS less than 250ns). The MAX306 is a single-ended 1-of-16 device,and the MAX307 is a differential 2-of-8 device.The MAX306/MAX307 are fabricated with Maxim’s improved 44V silicon-gate process. Design improve-ments yield extremely low charge injection (less than 10pC) and guarantee electrostatic discharge (ESD)protection greater than 2000V.These muxes operate with a single +4.5V to +30V sup-ply, or bipolar ±4.5V to ±20V supplies, while retaining TTL/CMOS-logic input compatibility and fast switching.CMOS inputs provide reduced input loading. These improved parts are plug-in upgrades for the industry-standard DG406, DG407, DG506A, and DG507A.________________________ApplicationsSample-and-Hold Circuits Test Equipment Heads-Up DisplaysGuidance and Control Systems Military RadiosCommunications Systems Battery-Operated Systems PBX, PABXAudio Signal Routing____________________________Featureso Guaranteed On-Resistance Match Between Channels, <5ΩMaxo Low On-Resistance, <100ΩMaxo Guaranteed Flat On-Resistance over Specified Signal Range, 7ΩMaxo Guaranteed Charge Injection, <10pC o I NO(OFF)Leakage <2.5nA at +85°C o I COM(OFF)Leakage <20nA at +85°C o ESD Protection >2000Vo Plug-In Upgrade for Industry-Standard DG406/DG407/DG506A/DG507Ao Single-Supply Operation (+4.5V to +30V)Bipolar-Supply Operation (±4.5V to ±20V)o Low Power Consumption, <1.25mW o Rail-to-Rail Signal Handling o TTL/CMOS-Logic CompatibleMAX306/MAX307Precision, 16-Channel/Dual 8-Channel,High-Performance, CMOS Analog Multiplexers________________________________________________________________Maxim Integrated Products 1_____________________Pin Configurations/Functional Diagrams/Truth TablesCall toll free 1-800-998-8800 for free samples or literature.19-0270; Rev 0; 8/94Ordering Information continued at end of data sheet.* Contact factory for dice specifications.M A X 306/M A X 307Precision, 16-Channel/Dual 8-Channel,High-Performance, CMOS Analog Multiplexers 2_______________________________________________________________________________________ABSOLUTE MAXIMUM RATINGSELECTRICAL CHARACTERISTICS—Dual Supplies(V+ = +15V, V- = -15V, GND = 0V, V AH = +2.4V, V AL = +0.8V, T A = T MIN to T MAX , unless otherwise noted.)Stresses beyond those listed under “Absolute Maximum Ratings” may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.Voltage Referenced to V-V+............................................................................-0.3V, 44V GND.........................................................................-0.3V, 25V Digital Inputs, NO, COM (Note 1)...........(V- - 2V) to (V+ + 2V) or30mA (whichever occurs first)Continuous Current (any terminal)......................................30mA Peak Current, NO or COM(pulsed at 1ms, 10% duty cycle max)..........................100mA Continuous Power Dissipation (T A = +70°C)Plastic DIP (derate 9.09mW/°C above +70°C)............727mW Wide SO (derate 12.50mW/°C above +70°C)............1000mW PLCC (derate 10.53mW/°C above +70°C)..................842mW CERDIP (derate 16.67mW/°C above +70°C).............1333mW Operating Temperature RangesMAX30_C_ _.......................................................0°C to +70°C MAX30_E_ _.....................................................-40°C to +85°C MAX30_MJI....................................................-55°C to +125°C Storage Temperature Range.............................-65°C to +150°C Lead Temperature (soldering, 10sec).............................+300°CNote 1:Signals on NO, COM, A0, A1, A2, A3, or EN exceeding V+ or V- are clamped by internal diodes. Limit forward current to maximum current ratings.MAX306/MAX307Precision, 16-Channel/Dual 8-Channel,High-Performance, CMOS Analog Multiplexers_______________________________________________________________________________________3ELECTRICAL CHARACTERISTICS—Dual Supplies (continued)(V+ = +15V, V- = -15V, GND = 0V, V= +2.4V, V = +0.8V, T = T to T , unless otherwise noted.)M A X 306/M A X 307Precision, 16-Channel/Dual 8-Channel,High-Performance, CMOS Analog Multiplexers 4_______________________________________________________________________________________ELECTRICAL CHARACTERISTICS—Single Supply(V+ = +12V, V- = 0V, GND = 0V, V AH = +2.4V, V AL = +0.8V, T A = T MIN to T MAX , unless otherwise noted.)Note 2:The algebraic convention where the most negative value is a minimum and the most positive value a maximum is used inthis data sheet.Note 3:Guaranteed by design.Note 4:∆R ON = R ON(MAX)- R ON(MIN).On-resistance match between channels and flatness are guaranteed only with specifiedvoltages. Flatness is defined as the difference between the maximum and minimum value of on-resistance as measured at the extremes of the specified analog signal range.Note 5:Leakage parameters are 100% tested at the maximum rated hot temperature and guaranteed by correlation at +25°C.Note 6:Off isolation = 20log V COM /V NO , where V COM = output and V NO = input to off switch.MAX306/MAX307Precision, 16-Channel/Dual 8-Channel,High-Performance, CMOS Analog Multiplexers_______________________________________________________________________________________5120140160ON-RESISTANCE vs. V COM(DUAL SUPPLIES)1000204060-2020-1515-1010-5580V COM (V)R O N (Ω)120ON-RESISTANCE vs. V COM AND TEMPERATURE (DUAL SUPPLIES)1000204060-1515-1010-55080V COM (V)R O N (Ω)280320360400ON-RESISTANCE vs. V COM (SINGLE SUPPLY)24040801201601520105200V COM (V)R O N (Ω)120140160ON-RESISTANCE vs. V COM AND TEMPERATURE (SINGLE SUPPLY)10002040601510580V COM (V)R O N (Ω)30CHARGE INJECTION vs. V COM20-30-20-100-1515-1010-55010V COM (V)Q j (p C )100.0001-55125OFF LEAKAGE vs. TEMPERATURE1TEMPERATURE (°C)O F F L E A K A G E (n A )250.010.001-35-15650.1100100045851055100.0001-55125ON LEAKAGE vs. TEMPERATURE1TEMPERATURE (°C)O N L E A K A G E (n A )250.010.001-35-15650.11001000458510551000.001-55125SUPPLY CURRENT vs. TEMPERATURE10TEMPERATURE (°C)I +, I - (µA )250.10.01-35-1565145851055__________________________________________Typical Operating Characteristics(T A = +25°C, unless otherwise noted.)__________Applications InformationOperation with Supply VoltagesOther than ±15VUsing supply voltages other than ±15V will reduce the analog signal range. The MAX306/MAX307 switches operate with ±4.5V to ±20V bipolar supplies or with a +4.5V to +30V single supply; connect V- to GND when operating with a single supply. Also, both device types can operate with unbalanced supplies such as +24V and -5V. The Typical Operating Characteristics graphs show typical on-resistance with 20V, 15V, 10V, and 5V supplies. (Switching times increase by a factor of two or more for operation at 5V.)Overvoltage ProtectionProper power-supply sequencing is recommended for all CMOS devices. Do not exceed the absolute maxi-mum ratings because stresses beyond the listed rat-ings may cause permanent damage to the devices.Always sequence V+ on first, then V-, followed by either the logic inputs, NO, or COM. If power-supply sequencing is not possible, add two small signal diodes in series with supply pins for overvoltage pro-tection (Figure 1). Adding diodes reduces the analogsignal range to 1V above V+ and 1V below V-, but low switch resistance and low leakage characteristics are unaffected. Device operation is unchanged, and the difference between V+ and V- should not exceed +44V.M A X 306/M A X 307Precision, 16-Channel/Dual 8-Channel,High-Performance, CMOS Analog Multiplexers 6_______________________________________________________________________________________Output–bidirectionalCOM28Address Inputs A3–A014–17Enable InputsEN 18Analog Inputs–bidirectional NO1–NO819–26Negative Supply Voltage Input V-27Ground GND 12Analog Inputs–bidirectional NO16–NO94–11MAX306PINNo Internal Connections N.C.2, 3, 13Positive Supply Voltage Input V+1FUNCTIONNAME_____________________________________________________________Pin DescriptionsDiodesMAX306/MAX307Precision, 16-Channel/Dual 8-Channel,High-Performance, CMOS Analog Multiplexers_______________________________________________________________________________________7______________________________________________Test Circuits/Timing DiagramsM A X 306/M A X 307Precision, 16-Channel/Dual 8-Channel,High-Performance, CMOS Analog Multiplexers 8________________________________________________________________________________________________________________________Test Circuits/Timing Diagrams (continued)Figure 5. Charge InjectionMAX306/MAX307Precision, 16-Channel/Dual 8-Channel,High-Performance, CMOS Analog Multiplexers_______________________________________________________________________________________9_________________________________Test Circuits/Timing Diagrams (continued)Figure 8. NO/COM CapacitanceM A X 306/M A X 307Precision, 16-Channel/Dual 8-Channel,High-Performance, CMOS Analog Multiplexers 10______________________________________________________________________________________________Pin Configurations/Functional Diagrams/Truth Tables (continued)A2A1A0EN ON Switch X 0 0 0 0 1 1 1 1 0 0 0 0 1 1 1 1X 0 0 1 1 0 0 1 1 0 0 1 1 0 0 1 1X 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 10 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1None 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16MAX306LOGIC “0” V AL ≤ 0.8V, LOGIC “1” = V AH ≥ 2.4VA3X 0 0 0 0 0 0 0 0 1 1 1 1 1 1 11A2A1A0EN ON Switch X 0 0 0 0 1 1 1 1X 0 0 1 1 0 0 1 1X 0 1 0 1 0 1 0 10 1 1 1 1 1 1 1 1None 1 2 3 4 5 6 7 8MAX307LOGIC “0” V AL ≤ 0.8V, LOGIC “1” = V AH ≥ 2.4VMAX306/MAX307Precision, 16-Channel/Dual 8-Channel,High-Performance, CMOS Analog Multiplexers______________________________________________________________________________________11________Pin Configurations/Functional Diagrams/Truth Tables (continued)_Ordering Information (continued)* Contact factory for dice specifications.Maxim cannot assume responsibility for use of any circuitry other than circuitry entirely embodied in a Maxim product. No circuit patent licenses are implied. Maxim reserves the right to change the circuitry and specifications without notice at any time.12__________________Maxim Integrated Products, 120 San Gabriel Drive, Sunnyvale, CA 94086 (408) 737-7600©1994 Maxim Integrated ProductsPrinted USAis a registered trademark of Maxim Integrated Products.M A X 306/M A X 307Precision, 16-Channel/Dual 8-Channel,High-Performance, CMOS Analog Multiplexers __________________________________________________________Chip TopographiesGNDNO1 NO2 NO3 N04 NO5 NO6 NO7 NO80.184" (4.67mm)0.078" (1.98mm)NO9NO10NO11NO12N013NO14NO15NO16N.C.V-COM V+GND NO1A NO2A NO3A N04A NO5A NO6A NO7A NO8A0.184" (4.67mm)0.078" (1.98mm)NO1B NO2B NO3B NO4B N05B NO6B NO7B NO8B COMBV-COMA V+TRANSISTOR COUNT: 269SUBSTRATE IS INTERNALLY CONNECTED TO V+TRANSISTOR COUNT: 269SUBSTRATE IS INTERNALLY CONNECTED TO V+MAX306MAX307N.C. = NO INTERNAL CONNECTION。

NCV3064资料

180

DFN−8 (Note 5)

Thermal Resistance Junction−to−Air

RqJA

78

Thermal Resistance Junction−to−Case

RqJA

14

Storage temperature range

Maximum junction temperature

Voltage supply Peak Current Sense Input to monitor the voltage drop across an external resistor to limit the peak current through the circuit ON/OFF Pin. Pulling this pin to High level turns the device in Operating. To switch into mode with low current consumption this pin has to be in Low level or floating.

元器件交易网

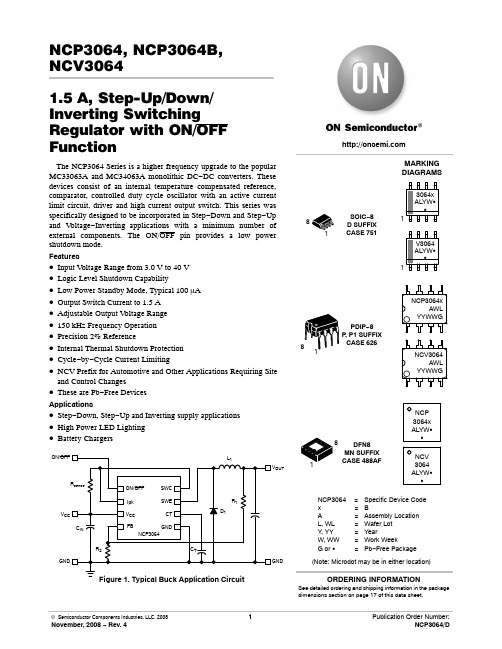

NCP3064, NCP3064B, NCV3064

1.5 A, Step-Up/Down/ Inverting Switching Regulator with ON/OFF Function