IS62WV51216ALL中文资料

IS62WV25616BLL中文资料

IS62WV25616ALL IS62WV25616BLLISSI®Copyright © 2005 Integrated Silicon Solution, Inc. All rights reserved. ISSI reserves the right to make changes to this specification and its products at any time without notice. ISSI assumes no liability arising out of the application or use of any information, products or services described herein. Customers are advised to obtain the latest version of this device specification before relying on any published information and before placing orders for products.256K x 16 LOW VOLTAGE,ULTRA LOW POWER CMOS STATIC SRAMFEATURES•High-speed access time: 55ns, 70ns •CMOS low power operation 36 mW (typical) operating 9 µW (typical) CMOS standby •TTL compatible interface levels •Single power supply1.65V--2.2V V DD (IS62WV25616ALL)2.5V--3.6V V DD (IS62WV25616BLL)•Fully static operation: no clock or refresh required •Three state outputs•Data control for upper and lower bytes •Industrial temperature available •Lead-free availableDESCRIPTIONThe ISSI IS62WV25616ALL/IS62WV25616BLL are high-speed, low power, 4M bit SRAMs organized as 256K words by 16 bits. It is fabricated using ISSI 's high-performance CMOS technology. This highly reliable process coupled with innovative circuit design techniques, yields high-performance and low power consumption devices.When CS1 is HIGH (deselected) or when CS1 is LOW and both LB and UB are HIGH, the device assumes a standby mode at which the power dissipation can be reduced down with CMOS input levels.Easy memory expansion is provided by using Chip Enable and Output Enable inputs. The active LOW Write Enable (WE ) controls both writing and reading of the memory. A data byte allows Upper Byte (UB ) and Lower Byte (LB )access.The IS62WV25616ALL/IS62WV25616BLL are packaged in the JEDEC standard 44-Pin TSOP (TYPE II) and 48-pin mini BGA (6mmx8mm).MAY 20052 Integrated Silicon Solution, Inc. — — 1-800-379-4774Rev.C IS62WV25616ALL, IS62WV25616BLLISSI®PIN DESCRIPTIONSA0-A17Address Inputs I/O0-I/O15Data Inputs/Outputs CS1Chip Enable Input OE Output Enable Input WE Write Enable InputLB Lower-byte Control (I/O0-I/O7)UB Upper-byte Control (I/O8-I/O15)NC No Connection V DD Power GNDGround44-Pin mini TSOP (Type II)(Package Code T)1234567891011121314151617181920212244434241403938373635343332313029282726252423A4A3A2A1A0CS1I/O0I/O1I/O2I/O3V DD GND I/O4I/O5I/O6I/O7WE A16A15A14A13A12A5A6A7OE UB LB I/O15I/O14I/O13I/O12GND V DD I/O11I/O10I/O9I/O8NC A8A9A10A11A17PIN CONFIGURATIONS48- ball mini BGA (6mm x 8mm)(Package Code B)IS62WV25616ALL, IS62WV25616BLL ISSI®TRUTH TABLEI/O PINMode WE CS1OE LB UB I/O0-I/O7I/O8-I/O15V DD Current Not Selected X H X X X High-Z High-Z I SB1, I SB2X X X H H High-Z High-Z I SB1, I SB2 Output Disabled H L H L X High-Z High-Z I CCH L H X L High-Z High-Z I CCRead H L L L H D OUT High-Z I CCH L L H L High-Z D OUTH L L L L D OUT D OUTWrite L L X L H D IN High-Z I CCL L X H L High-Z D INL L X L L D IN D INABSOLUTE MAXIMUM RATINGS(1)Symbol Parameter Value UnitV TERM Terminal Voltage with Respect to GND–0.2 to V DD+0.3VV DD V DD Related to GND–0.2 to V DD+0.3VT STG Storage Temperature–65 to +150°CP T Power Dissipation 1.0WNote:1.Stress greater than those listed under ABSOLUTE MAXIMUM RATINGS may cause permanent damage to the device. Thisis a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect reliability.OPERATING RANGE (V DD)Range Ambient Temperature IS62WV25616ALL IS62WV25616BLLCommercial0°C to +70°C 1.65V - 2.2V 2.5V-3.6VIndustrial–40°C to +85°C 1.65V - 2.2V 2.5V-3.6VDC ELECTRICAL CHARACTERISTICS(Over Operating Range)Symbol Parameter Test Conditions V DD Min.Max.Unit V OH Output HIGH Voltage I OH = -0.1 mA 1.65-2.2V 1.4—VI OH = -1 mA 2.5-3.6V 2.2—VV OL Output LOW Voltage I OL = 0.1 mA 1.65-2.2V—0.2VI OL = 2.1 mA 2.5-3.6V—0.4VV IH Input HIGH Voltage 1.65-2.2V 1.4V DD + 0.2V2.5-3.6V 2.2V DD + 0.3VV IL(1)Input LOW Voltage 1.65-2.2V–0.20.4V2.5-3.6V–0.20.6VI LI Input Leakage GND ≤ V IN≤ V DD–11µAI LO Output Leakage GND ≤ V OUT≤ V DD, Outputs Disabled–11µA Notes: 1. V IL (min.) = –1.0V for pulse width less than 10 ns.IS62WV25616ALL, IS62WV25616BLL ISSI®IS62WV25616ALL, POWER SUPPLY CHARACTERISTICS(1)(Over Operating Range)Symbol Parameter Test Conditions Max.Unit70I C C V DD D ynamic O perating V DD=M ax.,Com.25m ASupply C urrent I OUT = 0 mA, f = f MAX Ind.30I CC1Operating S upply V DD = Max., CS1 = 0.2V Com.10m ACurrent WE=V DD-0.2V Ind.10f=1MHZI SB1TTL Standby Current V DD=M ax.,Com.0.35m A(TTL Inputs)V IN = V IH or V IL Ind.0.35CS1 = V IH , f = 1 MH ZORULB Control V DD = Max., V IN = V IH or V ILCS1 = V IL, f = 0, UB = V IH, LB = V IHI SB2CMOS S tandby V DD=M ax.,Com.15µACurrent (CMOS Inputs)CS1≥V DD – 0.2V,Ind.15V IN≥V DD – 0.2V, orV IN≤ 0.2V, f = 0ORULB Control V DD = Max., CS1 = V IL,V IN≤ 0.2V, f = 0; UB / LB = V DD – 0.2VIS62WV25616BLL, POWER SUPPLY CHARACTERISTICS(1)(Over Operating Range)Symbol Parameter Test Conditions Max.Max.Unit5570I C C V DD D ynamic O perating V DD=M ax.,Com.4035m ASupply C urrent I OUT = 0 mA, f = f MAX Ind.4540I CC1Operating S upply V DD = Max., CS1 = 0.2V Com.1515m ACurrent WE=V DD-0.2V Ind.1515f=1MHZI SB1TTL Standby Current V DD=M ax.,Com.0.350.35m A(TTL Inputs)V IN = V IH or V IL Ind.0.350.35CS1 = V IH, f = 1 MH ZORULB Control V DD = Max., V IN = V IH or V ILCS1 = V IL, f = 0, UB = V IH, LB = V IHI SB2CMOS S tandby V DD=M ax.,Com.1515µACurrent (CMOS Inputs)CS1≥V DD – 0.2V,Ind.1515V IN≥V DD – 0.2V, orV IN≤ 0.2V, f = 0ORULB Control V DD = Max., CS1 = V IL,V IN≤ 0.2V, f = 0; UB / LB = V DD – 0.2V4 Integrated Silicon Solution, Inc. — — 1-800-379-4774Rev.CIS62WV25616ALL, IS62WV25616BLL ISSI®CAPACITANCE(1)Symbol Parameter Conditions Max.UnitC IN Input Capacitance V IN = 0V8pFC OUT Input/Output Capacitance V OUT = 0V10pFNote:1.Tested initially and after any design or process changes that may affect these parameters.AC TEST CONDITIONSIS62WV25616ALL IS62WV25616BLLParameter(Unit)(Unit)Input Pulse Level0.4V to V DD-0.2V0.4V to V DD-0.3VInput Rise and Fall Times 5 ns5nsInput and Output Timing V REF V REFand Reference LevelOutput Load See Figures 1 and 2See Figures 1 and 2IS62WV25616ALL IS62WV25616BLL1.65V-2.2V 2.5V -3.6VR1(Ω)30703070R2(Ω)31503150V REF0.9V 1.5VV TM 1.8V 2.8VFigure 1Figure 2IS62WV25616ALL, IS62WV25616BLL ISSI®READ CYCLE SWITCHING CHARACTERISTICS(1)(Over Operating Range)55 ns70 nsSymbol Parameter Min.Max.Min.Max.Unit t RC Read Cycle Time55—70—ns t AA Address Access Time—55—70ns t OHA Output Hold Time10—10—ns t ACS1CS1 Access Time—55—70ns t DOE OE Access Time—25—35ns t HZOE(2)OE to High-Z Output—20—25ns t LZOE(2)OE to Low-Z Output5—5—ns t HZCS1CS1 to High-Z Output020025ns t LZCS1CS1 to Low-Z Output10—10—ns t BA LB, UB Access Time—55—70ns t HZB LB, UB to High-Z Output020025ns t LZB LB, UB to Low-Z Output0—0—ns Notes:1.Test conditions assume signal transition times of 5 ns or less, timing reference levels of 0.9V/1.5V, input pulse levels of 0.4 toV DD-0.2V/V DD-0.3V and output loading specified in Figure 1.2.Tested with the load in Figure 2. Transition is measured ±500 mV from steady-state voltage. Not 100% tested.6 Integrated Silicon Solution, Inc. — — 1-800-379-4774Rev.CIS62WV25616ALL, IS62WV25616BLL ISSI®AC WAVEFORMSREAD CYCLE NO. 1(1,2) (Address Controlled) (CS1 = OE = V IL, WE = V IH, UB or LB = V IL)READ CYCLE NO. 2(1,3)(CS1, OE, AND UB/LB Controlled)Notes:1.WE is HIGH for a Read Cycle.2.The device is continuously selected. OE, CS1, UB, or LB = V IL. WE=V IH.3.Address is valid prior to or coincident with CS1 LOW transition.IS62WV25616ALL, IS62WV25616BLL ISSI®WRITE CYCLE SWITCHING CHARACTERISTICS(1,2) (Over Operating Range)55 ns70 nsSymbol Parameter Min.Max. Min.Max.Unit t WC Write Cycle Time 55— 70—ns t SCS1CS1 to Write End 45— 60—ns t AW Address Setup Time to Write End45— 60—ns t HA Address Hold from Write End0— 0—ns t SA Address Setup Time 0— 0—ns t PWB LB, UB Valid to End of Write45— 60—ns t PWE WE Pulse Width 40— 50—ns t SD Data Setup to Write End 25— 30—ns t HD Data Hold from Write End0— 0—ns t HZWE(3)WE LOW to High-Z Output—20 —20ns t LZWE(3)WE HIGH to Low-Z Output 5— 5—ns Notes:1.Test conditions assume signal transition times of 5 ns or less, timing reference levels of 0.9V/1.5V, input pulse levels of 0.4V toV DD-0.2V/V DD-0.3V and output loading specified in Figure 1.2.The internal write time is defined by the overlap of CS1 LOW and UB or LB, and WE LOW. All signals must be in valid states to initiate a Write, but any one cango inactive to terminate the Write. The Data Input Setup and Hold timing are referenced to the rising or falling edge of the signal that terminates the write.3.Tested with the load in Figure 2. Transition is measured ±500 mV from steady-state voltage. Not 100% tested.8 Integrated Silicon Solution, Inc. — — 1-800-379-4774Rev.CIS62WV25616ALL, IS62WV25616BLL ISSI®AC WAVEFORMSWRITE CYCLE NO. 1(1,2)(CS1 Controlled, OE = HIGH or LOW)1.WRITE is an internally generated signal asserted during an overlap of the LOW states on the CS1 and WE inputs and atleast one of the LB and UB inputs being in the LOW state.2.WRITE = (CS1) [ (LB) = (UB) ] (WE).WRITE CYCLE NO. 2 (WE Controlled: OE is HIGH During Write Cycle)IS62WV25616ALL, IS62WV25616BLL ISSI®WRITE CYCLE NO. 3 (WE Controlled: OE is LOW During Write Cycle)WRITE CYCLE NO. 4 (UB/LB Controlled)10 Integrated Silicon Solution, Inc. — — 1-800-379-4774Rev.CIS62WV25616ALL, IS62WV25616BLL ISSI®DATA RETENTION SWITCHING CHARACTERISTICSSymbol Parameter Test Condition Min.Max.UnitV DR V DD for Data Retention See Data Retention Waveform 1.2 3.6VI DR Data Retention Current V DD = 1.2V, CS1≥ V DD – 0.2V—15µAt SDR Data Retention Setup Time See Data Retention Waveform0—nst RDR Recovery Time See Data Retention Waveform t RC—nsDATA RETENTION WAVEFORM (CS1 Controlled)IS62WV25616ALL, IS62WV25616BLL ISSI®ORDERING INFORMATIONIS62WV25616ALL (1.65V-2.2V)Commercial Range: 0°C to +70°CSpeed (ns)Order Part No.Package70IS62WV25616ALL-70T TSOPIndustrial Range: –40°C to +85°CSpeed (ns)Order Part No.Package70IS62WV25616ALL-70TI TSOP70IS62WV25616ALL-70BI mini BGA (6mmx8mm)IS62WV25616BLL (2.5V - 3.6V)Commercial Range: 0°C to +70°CSpeed (ns)Order Part No.Package55IS62WV25616BLL-55T TSOP70IS62WV25616BLL-70T TSOPIndustrial Range: –40°C to +85°CSpeed (ns)Order Part No.Package55IS62WV25616BLL-55TI TSOP55IS62WV25616BLL-55TLI TSOP, Lead-free55IS62WV25616BLL-55BI mini BGA (6mmx8mm)55IS62WV25616BLL-55BLI mini BGA (6mmx8mm), Lead-freePACKAGING INFORMATIONISSI®Copyright © 2003 Integrated Silicon Solution, Inc. All rights reserved. ISSI reserves the right to make changes to this specification and its products at any time without notice. ISSI assumes no liability arising out of the application or use of any information, products or services described herein. Customers are advised to Mini Ball Grid ArrayPackage Code: B (48-pin)PACKAGING INFORMATIONISSI®Copyright © 2003 Integrated Silicon Solution, Inc. All rights reserved. ISSI reserves the right to make changes to this specification and its products at any timewithout notice. ISSI assumes no liability arising out of the application or use of any information, products or services described herein. Customers are advised to Plastic TSOPPackage Code: T (Type II)。

BS62LV1600FI55中文资料

BS62LV1600FI55中⽂资料Very Low Power CMOS SRAM 2M X 8 bitBS62LV1600Pb-Free and Green package materials are compliant to RoHSn FEATURESWide V CC operation voltage : 2.4V ~ 5.5V Very low power consumption : V CC = 3.0V Operation current : 46mA (Max.) a t 55ns 2mA (Max.) at 1MHz Standby current : 1.5uA (Typ.) at 25 O C V CC = 5.0V Operation current : 115mA (Max.) a t 55ns 10mA (Max.) a t 1MHz Standby current : 6.0uA (Typ.) at 25O C ? High speed access time : -55 55ns (Max.) at V CC :3.0~5.5V -70 70ns (Max.) at V CC : 2.7~5.5V ? Automatic power down when chip is deselected ? Easy expansion with CE1, CE2 and OE options ? Three state outputs and TTL compatible ? Fully static operation ? Data retention supply voltage as low as 1.5V n DESCRIPTIONThe BS62LV1600 is a high performance, very low power CMOS Static Random Access Memory organized as 2048K by 8 bits and operates form a wide range of 2.4V to 5.5V supply voltage.Advanced CMOS technology and circuit techniques provide both high speed and low power features with typical CMOS standby current of 1.5uA at 3.0V/25O C and maximum access time of 55ns at 3.0V/85O C.Easy memory expansion is provided by an active LOW chip enable (CE1), an active HIGH chip enable (CE2), and active LOW output enable (OE) and three-state output drivers.The BS62LV1600 has an automatic power down feature, reducing the power consumption significantly when chip is deselected. The BS62LV1600 is available in JEDEC standard 44-pin TSOP II and 48-ball BGA package.n POWER CONSUMPTIONPOWER DISSIPATIONSTANDBY(I CCSB1, Max)Operating(I CC , Max)V CC =5.0V V CC =3.0V PRODUCT FAMILYOPERATING TEMPERATUREV CC =5.0V V CC =3.0V1MHz10MHzf Max. 1MHz10MHzf Max.PKG TYPEBS62LV1600EC TSOP II-44 BS62LV1600FC Commercial +0O C to +70O C 50uA 8.0uA 9mA 48mA 113mA 1.5mA 19mA 45mABGA-48-0912 BS62LV1600EITSOP II-44 BS62LV1600FIIndustrial -40O C to +85O C100uA 16uA 10mA 50mA 115mA 2mA 20mA 46mABGA-48-0912n PIN CONFIGURATIONSn BLOCK DIAGRAMBrilliance Semiconductor, Inc. reserves the right to change products and specifications without notice.G H F E D C B A 1 2 3 4 5 6 A9 A11 A10 A19A12 A14 A13 A15 WE NC NC NC DQ7 A17 A16 A7 VSS VCC DQ2 DQ1 DQ6 DQ5 NC A5 OE A3 A0 A6 A4 A1A2CE2 NC NC NCCE1 DQ4 NC 48-ball BGA top view NC NC DQ0 VSS VCC DQ3 NC A18 A20 A8n TRUTH TABLEn ABSOLUTE MAXIMUM RATINGS (1)SYMBOL PARAMETER RATING UNITSV TERM Terminal Voltage withRespect to GND-0.5(2) to 7.0 VT BIAS Temperature UnderBias-40 to +125 O CT STG Storage Temperature -60 to +150 O CP T Power Dissipation 1.0 WI OUT DC Output Current 20 mA1. Stresses greater than those listed under ABSOLUTE MAXIMUM RATINGS may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect reliability.2. –2.0V in case of AC pulse width less than 30 ns. n OPERATING RANGERANGAMBIENTTEMPERATUREV CC Commercial 0O C to + 70O C 2.4V ~ 5.5VIndustrial -40O C to + 85O C 2.4V ~ 5.5Vn CAPACITANCE (1) (T A = 25O C, f = 1.0MHz) SYMBOL PAMAMETER CONDITIONS MAX. UNITS C INInputCapacitanceV IN = 0V 10 pFC IOInput/OutputCapacitanceV I/O = 0V 12 pF1. This parameter is guaranteed and not 100% tested.n DC ELECTRICAL CHARACTERISTICS (T A =-40O C to +85OC)1. Typical characteristics are at T A =25O C and not 100% tested.2. Undershoot: -1.0V in case of pulse width less than 20 ns.3. Overshoot: V CC +1.0V in case of pulse width less than 20 ns.4. F MAX =1/t RC.5. I CC(MAX.) is 45mA/113mA at V CC =3.0V/5.0V and T A =70O C.6. I CCSB1(MAX.) is 8.0uA/50uA at V CC =3.0V/5.0V and T A =70O C.n DATA RETENTION CHARACTERISTICS (T A = -40O C to +85OC)1. V CC =1.5V, T A =25O C and not 100% tested.2. t RC = Read Cycle Time.3. I CCRD(Max.) is4.0uA at T A =70O C.n LOW V CC DATA RETENTION WAVEFORM (1) (CE1 Controlled)Data Retention Mode V CCt CDRV CC t RV IHV IHCE1≧V CC - 0.2V V DR ≧1.5V CE1V CCn LOW V CC DATA RETENTION WAVEFORM (2) (CE2 Controlled)n AC TEST CONDITIONS (Test Load and Input/Output Reference)Input Pulse Levels Vcc / 0V Input Rise and Fall Times 1V/ns Input and Output Timing Reference Level 0.5Vcc t CLZ , t OLZ , t CHZ , t OHZ , t WHZ C L = 5pF+1TTL Output LoadOthersC L = 30pF+1TTL1. Including jig and scope capacitance.n KEY TO SWITCHING WAVEFORMSn AC ELECTRICAL CHARACTERISTICS (T A = -40O C to +85OC)READ CYCLECE2 Data Retention Mode V CC t CDR V CC t R V ILV IL V CCV DR ≧1.5V CE2≦0.2V 1 TTL ALL INPUT PULSES→← 90%V CC GND Rise Time : 1V/ns Fall Time : 1V/ns90%→← 10%10%n SWITCHING WAVEFORMS (READ CYCLE)READ CYCLE 1 (1,2,4)READ CYCLE 2 (1,3,4)READ CYCLE 3 (1, 4)NOTES:1. WE is high in read Cycle.2. Device is continuously selected when CE1 = V IL and CE2= V IH .3. Address valid prior to or coincident with CE1 transition low and/or CE2 transition high.4. OE = V IL .5. Transition is measured ± 500mV from steady state with C L = 5pF. The parameter is guaranteed but not 100% tested. t RC t OHt AA D OUT ADDRESS t OHD OUTCE2 CE1D OUTCE2 CE1 OE ADDRESSn AC ELECTRICAL CHARACTERISTICS (T A = -40OC to +85OC)WRITE CYCLEn SWITCHING WAVEFORMS (WRITE CYCLE)WRITE CYCLE 1 (1)t WCt WR1(3)t CW(11)t CW(11)t WP(2)t AWt OHZ(4,10)t AS t WR2(3)t DHt DWD IND OUTWECE2CE1OEADDRESS(5)(5)WRITE CYCLE 2 (1,6)NOTES:1. WE must be high during address transitions.2. The internal write time of the memory is defined by the overlap of CE1 and CE2 active and WE low. All signals must be active to initiate a write and any one signal can terminate a write by going inactive. The data input setup and hold timing should be referenced to the second transition edge of the signal that terminates the write.3. t WR is measured from the earlier of CE1 or WE going high or CE2 going low at the end of write cycle.4. During this period, DQ pins are in the output state so that the input signals of opposite phase to the outputs must not be applied.5. If the CE1 low transition or the CE2 high transition occurs simultaneously with the WE low transitions or after the WE transition, output remain in a high impedance state.6. OE is continuously low (OE = V IL ).7. D OUT is the same phase of write data of this write cycle. 8. D OUT is the read data of next address.9. If CE1 is low and CE2 is high during this period, DQ pins are in the output state. Then the data input signals of opposite phase to the outputs must not be applied to them. 10. T ransition is measured ± 500mV from steady state with C L = 5pF. The parameter is guaranteed but not 100% tested. 11. t CW is measured from the later of CE1 going low or CE2 going high to the end of write.D IND OUTWE CE2 CE1ADDRESSn ORDERING INFORMATIONBSI (Brilliance Semiconductor Inc.) assumes no responsibility for the application or use of any product or circuit described herein. BSI does not authorize its products for use as critical components in any application in which the failure of the BSI product may be expected to result in significant injury or death, including life-support systems and critical medical instruments.n PACKAGE DIMENSIONSTSOP II-44n PACKAGE DIMENSIONS (continued)3: SYMBOL "N" IS THE NUMBER OF SOLDER BALLS.1: CONTROLLING DIMENSIONS ARE IN MILLIMETERS. 2: PIN#1 DOT MARKING BY LASER OR PAD PRINT.N EDNOTES:4812.09.0E1D1e3.755.250.75 48 mini-BGA (9mm x 12mm)n Revision HistoryRevision No. History Draft Date Remark2.2 Add Icc1 characteristic parameter Jan. 13, 2006Improve Iccsb1 spec.I-grade from 220uA to 100uA at 5.0V20uA to 16uA at 3.0VC-grade from 110uA to 50uA at 5.0V10uA to 8.0uA at 3.0V2.3 Change I-grade operation temperature range May. 25, 2006 - from –25O C to –40O C。

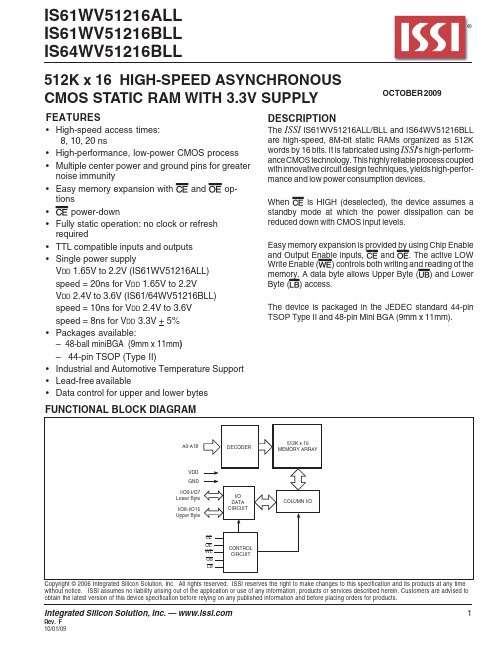

IS61WV51216ALL

PIN DESCRIPTIONS

A0-A18 I/O0-I/O15 CE OE WE LB UB NC VDD GND

Address Inputs Data Inputs/Outputs Chip Enable Input Output Enable Input Write Enable Input Lower-byte Control (I/O0-I/O7) Upper-byte Control (I/O8-I/O15) No Connection Power Ground

The device is packaged in the JEDEC standard 44-pin TSOP Type II and 48-pin Mini BGA (9mm x 11mm).

A0-A18

DECODER

512K x 16 MEMORY ARRAY

VDD GND

I/O0-I/O7 Lower Byte

tions • CE power-down • Fully static operation: no clock or refresh

required • TTL compatible inputs and outputs • Single power supply

VDD 1.65V to 2.2V (IS61WV51216ALL) speed = 20ns for VDD 1.65V to 2.2V VDD 2.4V to 3.6V (IS61/64WV51216BLL) speed = 10ns for VDD 2.4V to 3.6V speed = 8ns for VDD 3.3V + 5% • Packages available: – 48-ball miniBGA (9mm x 11mm) – 44-pin TSOP (Type II) • Industrial and Automotive Temperature Support • Lead-free available • Data control for upper and lower bytes

IS64WV102416BLL中文资料

48 A5 47 A6 46 A7 45 A8 44 OE 43 UB 42 LB 41 I/O15 40 I/O14 39 I/O13 38 I/O12 37 GND 36 VDD 35 I/O11 34 I/O10 33 I/O9 32 I/O8 31 NC 30 A9 29 A10 28 A11 27 A12 26 A13 25 A14

Integrated Silicon Solution, Inc. — — 1-800-379-4774

1

Rev.102416ALL IS61WV102416BLL IS64WV102416BLL

48-pin mini BGA (9mmx11mm)

The device is packaged in the JEDEC standard 48-pin TSOP Type I and 48-pin Mini BGA (9mm x 11mm).

A0-A19

DECODER

1024K x 16 MEMORY ARRAY

VDD GND

I/O0-I/O7 Lower Byte

1 23 45 6

A

LB

OE

A0

A1

A2

NC

B

I/O8

UB

A3

A4

CE

I/O0

C

I/O9 I/O10 A5

数据手册_HR6P72L_Datasheet_C V2.1

海尔 MCU 芯片使用注意事项

关于芯片的上/下电 海尔 MCU 芯片具有独立电源管脚。当 MCU 芯片应用在多电源供电系统时,应先对 MCU 芯片上电,再 对系统其它部件上电;反之,下电时,先对系统其它部件下电,再对 MCU 芯片下电。若操作顺序相反则

可能导致芯片内部元件过压或过流,从而导致芯片故障或元件退化。具体可参照芯片的数据手册说明。

关于芯片的 ESD 防护措施

海尔 MCU 芯片具有满足工业级 ESD 标准保护电路。建议用户根据芯片存储/应用的环境采取适当静电防护 措施。应注意应用环境的湿度;建议避免使用容易产生静电的绝缘体;存放和运输应在抗静电容器、抗静 电屏蔽袋或导电材料容器中;包括工作台在内的所有测试和测量工具必须保证接地;操作者应该佩戴静电 消除手腕环手套,不能用手直接接触芯片等。

关于芯片的初始化

海尔 MCU 芯片具有各种内部和外部复位。对于不同的应用系统,有必要对芯片寄存器、内存、功能模块 等进行初始化,尤其是 I/O 管脚复用功能进行初始化,避免由于芯片上电以后,I/O 管脚状态的不确定情况 发生。

关于芯片的管脚

海尔 MCU 芯片具有宽范围的输入管脚电平,建议用户输入高电平应在 VIHMIN 之上,低电平应在 VILMAX 之 下。避免输入电压介于 VIHMIN 和 VILMAX 之间,以免波动噪声进入芯片。对于未使用的输入管脚,应通过电 阻上拉至电源电平或下拉至地。对于未使用的管脚,建议用户设为输出状态,并通过电阻接至电源或地。 对未使用的管脚处理因应用系统而异,具体遵循应用系统的相关规定和说明。

上海海尔集成电路有限公司

HR6P72L 数据手册

目录

内容目录

第 1 章 芯片简介 .................................................................................................... 10

IS64WV12816BLL中文资料

IS61WV12816BLL®2Integrated Silicon Solution, Inc. — — 1-800-379-4774Rev. C ISSI®IS61WV12816BLL IS64WV12816BLL1234567891011121314151617181920212244434241403938373635343332313029282726252423A4A3A2A1A0CE I/O0I/O1I/O2I/O3V DD GND I/O4I/O5I/O6I/O7WE A16A15A14A13A12A5A6A7OE UB LB I/O15I/O14I/O13I/O12GND V DD I/O11I/O10I/O 9I/O8NC A8A 9A10A11NC44-Pin TSOP (Type II) (T)PIN DESCRIPTIONSA0-A16Address Inputs I/O0-I/O15Data Inputs/Outputs CE Chip Enable Input OE Output Enable Input WE Write Enable InputLB Lower-byte Control (I/O0-I/O7)UB Upper-byte Control (I/O8-I/O15)NC No Connection V DD Power GNDGroundTRUTH TABL EI/O PINModeWE CE OE LB UB I/O0-I/O7I/O8-I/O15V DD Current Not Selected X H X X X High-Z High-Z I SB 1, I SB 2Output Disabled H L H X X High-Z High-Z I CCX L X H H High-Z High-Z ReadH L L L H D OUT High-Z I CCH L L H L High-Z D OUT H L L L L D OUT D OUT Write L L X L H D IN High-Z I CCL L X H L High-Z D IN LLXLLD IND INPIN CONFIGURATIONISSI®IS61WV12816BLL IS64WV12816BLLPIN DESCRIPTIONSA0-A16Address Inputs I/O0-I/O15Data Inputs/Outputs CEChip Enable Input OE Output Enable Input WE Write Enable InputLB Lower-byte Control (I/O0-I/O7)UB Upper-byte Control (I/O8-I/O15)NC No Connection V DD Power GNDGround48-Pin mini BGA (B)PIN CONFIGURATION1 2 3 4 5 6A B C D E F G HLB OE A0A1A2NC I/O 8UB A3A4CE I/O 0I/O 9I/O 10A5A6I/O 1I/O 2GND I/O 11NC A7I/O 3V DD V DD I/O 12NC A16I/O 4GND I/O 14I/O 13A14A15I/O 5I/O 6I/O 15NC A12A13WE I/O 7NCA8A 9A10A11NC4Integrated Silicon Solution, Inc. — — 1-800-379-4774Rev. C ISSI®IS61WV12816BLL IS64WV12816BLLOPERATING RANGE (V DD )Range Ambient TemperatureV DD (15 n S )V DD (12 n S )Industrial –40°C to +85°C 2.5V-3.6V 3.3V + 10%Automotive–40°C to +125°C2.5V-3.6VABSOLUTE MAXIMUM RATINGS (1)Symbol ParameterValue Unit V DD Power Supply Voltage Relative to GND –0.5 to 4.0V V V TERM Terminal Voltage with Respect to GND –0.5 to V DD + 0.5V T STG Storage Temperature –65 to + 150°C P T Power Dissipation1.0WNote:1. Stress greater than those listed under ABSOLUTE MAXIMUM RATINGS may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the opera-tional sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect reliability.DC ELECTRICAL CHARACTERISTICS (Over Operating Range)V DD = 2.5V-3.6VSymbol ParameterTest ConditionsMin.Max.Unit V OH Output HIGH Voltage V DD = Min., I OH = –1.0 mA 1.8—V V OL Output LOW Voltage V DD = Min., I OL = 1.0 mA—0.4V V IH Input HIGH Voltage 2.0V DD + 0.3V V IL Input LOW Voltage (1)–0.30.4V I LI Input Leakage GND ≤ V IN ≤ V DD–11µA I LO Output LeakageGND ≤ V OUT ≤ V DD , Outputs Disabled–11µANote:1.V IL (min.) = –0.3V DC; V IL (min.) = –2.0V AC (pulse width - 2.0 ns). Not 100% tested.V IH (max.) = V DD + 0.3V DC; V IH (max.) = V DD + 2.0V AC (pulse width - 2.0 ns). Not 100% tested.DC ELECTRICAL CHARACTERISTICS (Over Operating Range)V DD = 3.3V + 10%Symbol ParameterTest ConditionsMin.Max.Unit V OH Output HIGH Voltage V DD = Min., I OH = –4.0 mA 2.4—V V OL Output LOW Voltage V DD = Min., I OL = 8.0 mA—0.4V V IH Input HIGH Voltage 2V DD + 0.3V V IL Input LOW Voltage (1)–0.30.8V I LI Input Leakage GND ≤ V IN ≤ V DD–11µA I LO Output LeakageGND ≤ V OUT ≤ V DD , Outputs Disabled–11µANote:1.V IL (min.) = –0.3V DC; V IL (min.) = –2.0V AC (pulse width - 2.0 ns). Not 100% tested.V IH (max.) = V DD + 0.3V DC; V IH (max.) = V DD + 2.0V AC (pulse width - 2.0 ns). Not 100% tested.ISSI®IS61WV12816BLL IS64WV12816BLLPOWER SUPPLY CHARACTERISTICS (1) (Over Operating Range)-12ns -15 ns Symbol Parameter Test Conditions Min.Max.Min.Max.Unit I CCV DD Operating V DD = Max., CE = V IL Com.—35—30mASupply CurrentI OUT = 0 mA, f = Max.Ind.—40—35Auto —40typ.(2)—25—20I SB 1TTL Standby V DD = Max.,Com.—20—20mACurrent V IN = V IH or V IL Ind.—20—20(TTL Inputs)CE ≥ V IH , f = max Auto —30I SB 2CMOS Standby V DD = Max.,Com.—750—750μA CurrentCE ≥ V DD – 0.2V,Ind.—900—900μA (CMOS Inputs)V IN ≥ V DD – 0.2V, or Auto —6mA V IN ≤ 0.2V , f = 0typ.(2)—400—400μANote:1.At f = f MAX , address and data inputs are cycling at the maximum frequency, f = 0 means no input lines change.2.Typical values are measured at V DD =3.3V, T A =250C. Not 100% tested.CAPACITANCE (1)Symbol Parameter Conditions Max.Unit C IN Input Capacitance V IN = 0V 6pF C OUT Input/Output CapacitanceV OUT = 0V8pFNote:1. Tested initially and after any design or process changes that may affect these parameters.6Integrated Silicon Solution, Inc. — — 1-800-379-4774Rev. C ISSI®IS61WV12816BLL IS64WV12816BLLAC TEST LOADSFigure 1.Figure 2.READ CYCLE SWITCHING CHARACTERISTICS (1) (Over Operating Range)-12 ns -15 ns SymbolParameter Min.Max.Min.Max.Unit t RC Read Cycle Time 12—15—ns t AA Address Access Time —12—15ns t OHA Output Hold Time 3—3—ns t ACE CE Access Time —12—15ns t DOE OE Access Time —5—7ns t HZOE (2)OE to High-Z Output —5—6ns t LZOE (2)OE to Low-Z Output 0—0—ns t HZCE (2)CE to High-Z Output 0506ns t LZCE (2)CE to Low-Z Output 3—3—ns t BA LB , UB Access Time —5—7ns t HZB (2)LB , UB to High-Z Output 0506ns t LZB (2)LB , UB to Low-Z Output——nsNotes:1.Test conditions assume signal transition times of 3 ns or less, timing reference levels of 1.5V, input pulse levels of 0V to 3.0V and output loading specified in Figure 1.2.Tested with the load in Figure 2. Transition is measured ±500 mV from steady-state voltage. Not 100% tested.AC TEST CONDITIONSParameterUnit Unit (2.5V-3.6V)(3.3V + 10%)Input Pulse Level0.4V to V DD -0.3V0.4V to V DD -0.3VInput Rise and Fall Times 1.5ns 1.5ns Input and Output Timing V DD /2V DD /2 + 0.05and Reference Level (V Ref )Output LoadSee Figures 1 and 2See Figures 1 and 2ISSI®IS61WV12816BLL IS64WV12816BLLREAD CYCLE NO. 2(1,3)AC WAVEFORMSREAD CYCLE NO. 1(1,2) (Address Controlled) (CE = OE = V IL , UB or LB = V IL )1. WE is HIGH for a Read Cycle.2. The device is continuously selected. OE , CE , UB , or LB = V IL .3. Address is valid prior to or coincident with CE LOW transition.ISSI®IS61WV12816BLLIS64WV12816BLLWRITE CYCLE SWITCHING CHARACTERISTICS(1,3)(Over Operating Range)-12 ns-15 nsSymbol Parameter Min.Max.Min.Max.Unitt WC Write Cycle Time12—15—nst SCE CE to Write End8—10—nst AW Address Setup Time8—10—nsto Write Endt HA Address Hold from Write End0—0—nst SA Address Setup Time0—0—nst PBW LB, UB Valid to End of Write9—10—nst PWE1WE Pulse Width (OE = HIGH)8—10—nst PWE2WE Pulse Width (OE = LOW)10—12—nst SD Data Setup to Write End6—7—nst HD Data Hold from Write End0—0—nst HZWE(3)WE LOW to High-Z Output—5—7nst LZWE(3)WE HIGH to Low-Z Output0—0—nsNotes:1.Test conditions assume signal transition times of 3 ns or less, timing reference levels of 1.5V, input pulse levels of 0V to3.0V and output loading specified in Figure 1.2.The internal write time is defined by the overlap of CE LOW and UB or LB, and WE LOW. All signals must be in valid statesto initiate a Write, but any one can go inactive to terminate the Write. The Data Input Setup and Hold timing are referenced to the rising or falling edge of the signal that terminates the write.3.Tested with the load in Figure 2. Transition is measured ±500 mV from steady-state voltage. Not 100% tested.8Integrated Silicon Solution, Inc. — — 1-800-379-4774Rev. CISSI®IS61WV12816BLL IS64WV12816BLLWRITE CYCLE NO. 1(1,2) (CE Controlled, OE = HIGH or LOW)ISSI®IS61WV12816BLLIS64WV12816BLLWRITE CYCLE NO. 2(1)(WE Controlled, OE = HIGH during Write Cycle)10Integrated Silicon Solution, Inc. — — 1-800-379-4774Rev. CISSI®IS61WV12816BLL IS64WV12816BLLWRITE CYCLE NO. 4 (LB , UB Controlled, Back-to-Back Write) (1,3)1. The internal Write time is defined by the overlap of CE = LOW, UB and/or LB = LOW, and WE = LOW. All signals must be in valid states to initiate a Write, but any can be deasserted to terminate the Write. The t SA , t HA , t SD , and t HD timing is referenced to the rising or falling edge of the signal that terminates the Write.2. Tested with OE HIGH for a minimum of 4 ns before WE = LOW to place the I/O in a HIGH-Z state.3. WE may be held LOW across many address cycles and the LB , UB pins can be used to control the Write function.ISSI®IS61WV12816BLL IS64WV12816BLLDATA RETENTION WAVEFORM (CE Controlled)DATA RETENTION SWITCHING CHARACTERISTICSSymbolParameterTest ConditionOptions Min.Typ.(1)Max.Unit V DRV DD for Data Retention See Data Retention Waveform 1.8— 3.6V I DRData Retention Current V DD = 2.0V, CE ≥ V DD – 0.2V Ind.—0.40.9mA Auto—0.46mA t SDR Data Retention Setup Time See Data Retention Waveform 0——ns t RDRRecovery TimeSee Data Retention Waveformt RC——nsNote 1: Typical values are measured at V DD = 3.3V, T A = 25OC. Not 100% tested.ISSI®IS61WV12816BLL IS64WV12816BLLORDERING INFORMATION:Industrial Range: –40°C to +85°CSpeed (ns)Order Part No.Package12 (151)IS61WV12816BLL-12BI mini BGA (6mm x 8mm)IS61WV12816BLL-12BLI mini BGA (6mm x 8mm), Lead-free IS61WV12816BLL-12TI Plastic TSOP (Type II)IS61WV12816BLL-12TLIPlastic TSOP (Type II), Lead-freeNote:1.Speed = 12ns for V DD = 3.3V + 10%. Speed = 15ns for V DD =2.5V-3.6VAutomotive Range: –40°C to +125°CSpeed (ns)Order Part No.Package15IS64WV12816BLL-15BA3mini BGA (6mm x 8mm)IS64WV12816BLL-15TA3Plastic TSOP (Type II)IS64WV12816BLL-15TLA3Plastic TSOP (Type II), Lead-freePACKAGING INFORMATIONISSI®Copyright © 2003 Integrated Silicon Solution, Inc. All rights reserved. ISSI reserves the right to make changes to this specification and its products at any time without notice. ISSI assumes no liability arising out of the application or use of any information, products or services described herein. Customers are advised to Mini Ball Grid ArrayPackage Code: B (48-pin)PACKAGING INFORMATIONISSI®Copyright © 2003 Integrated Silicon Solution, Inc. All rights reserved. ISSI reserves the right to make changes to this specification and its products at any timewithout notice. ISSI assumes no liability arising out of the application or use of any information, products or services described herein. Customers are advised to Plastic TSOPPackage Code: T (Type II)。

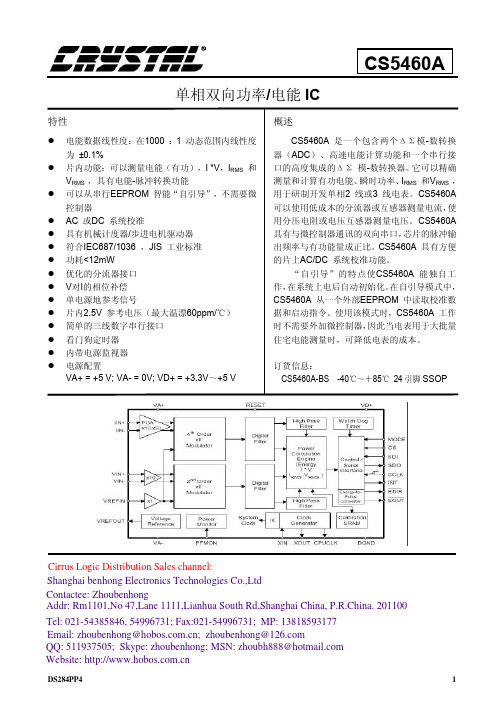

CS5460A中文数据手册

l 片内功能:可以测量电能(有功),I *V,IRMS 和 VRMS ,具有电能-脉冲转换功能

l 可以从串行EEPROM 智能“自引导”,不需要微 控制器

l AC 或DC 系统校准 l 具有机械计度器/步进电机驱动器 l 符合IEC687/1036 ,JIS 工业标准 l 功耗<12mW l 优化的分流器接口 l V对I的相位补偿 l 单电源地参考信号 l 片内2.5V 参考电压(最大温漂60ppm/℃) l 简单的三线数字串行接口 l 看门狗定时器 l 内带电源监视器 l 电源配置

VA+ = +5 V; VA- = 0V; VD+ = +3.3V~+5 V

概述

CS5460A 是一个包含两个ΔΣ模-数转换 器(ADC)、高速电能计算功能和一个串行接 口的高度集成的ΔΣ 模-数转换器。它可以精确 测量和计算有功电能、瞬时功率、IRMS 和VRMS , 用于研制开发单相2 线或3 线电表。CS5460A 可以使用低成本的分流器或互感器测量电流,使 用分压电阻或电压互感器测量电压。CS5460A 具有与微控制器通讯的双向串口,芯片的脉冲输 出频率与有功能量成正比。CS5460A 具有方便 的片上AC/DC 系统校准功能。

cs5460a单相双向功率电能ic特性rms具有电能脉冲转换功能可以从串行eeprom智能自引导不需要微控制器ac或dc系统校准符合iec6871036jis工业标准片内25v参考电压最大温漂60ppm电源配置va0v

IS62WV2568BLL-55HLI中文资料

1 23 45 6

A

A0 A1 CS2 A3 A6 A8

B

I/O4 A2 WE A4 A7 I/O0

C

I/O5

NC A5

I/O1

D

GND

Vcc

E

Vcc

GND

F

I/O6

NC A17

I/O2

G

I/O7 OE CS1 A16 A15 I/O3

H

A9 A10 A11 A12 A13 A14

32-pin TSOP (TYPE I), sTSOP (TYPE I)

GND ≤ VIN ≤ VCC

ILO

Output Leakage

GND ≤ VOUT ≤ VCC, Outputs Disabled

Notes: 1. VIL (min.) = –1.0V for pulse width less than 10 ns.

Min.

Max.

Unit

1.4

—

V

2.2

—

V

—

Rev. B

06/20/05

元器件交易网

ht1621中文资料

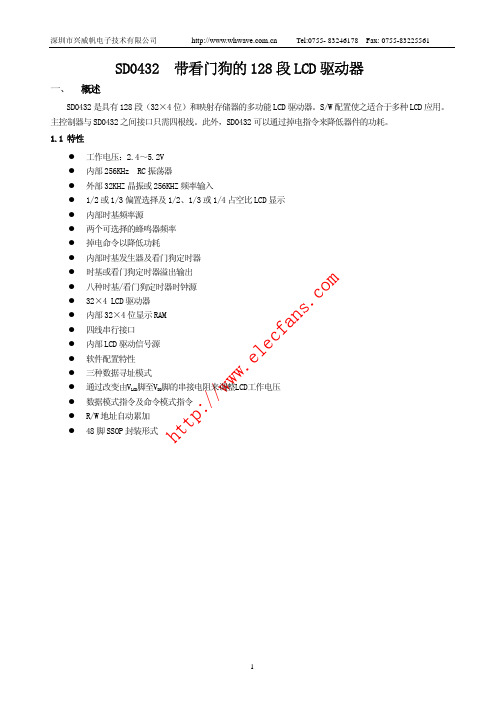

SD0432 中集成了一个简单的声音发生器,此发声器可输出一对不同的驱动信号至 BZ 和 BZ 以产生单音,执 行 TONE 4K 与 TONE 2K 命令,可选择两个不现的音频输出,即 4KHZ 与 2KHZ 这两个频率,TONE ON 及 TONE OFF 命令可打开或关闭语音输出,语音输出 BZ 和 BZ,是一对不同的带驱动蜂鸣器。当系统关闭或语音输出被禁止时, BZ 及 BZ 将处于低电平状态。

命令 LCD OFF 是通过关闭 LCD 偏压发生器来关闭 LCD 显示器。反之,LCD ON 则启动 LCD 显示。BIAS COM 是与

LCD 屏面相关命令。使用 LCD 相关命令,SD0432 可与绝大多数类型的 LCD 屏面兼容。

3. 6 命令格式

SD0432 可由 S/W 设置来配置。有两种命令模式分别用来配置 SD0432 和传送 LCD 显示数据。配置 SD0432 的命

令模式(普通模式)识别码为 100,此命令模式由系统配置命令、LCD 配置命令、音频选择命令、定时器/看门狗

定时器设置命令及操作命令组成。另一方面,数据模式包括 READ、WRITE 及 READ-MODIFY-WRITE 操作。下表为数

据模式及命令模式识别码:

com 操

作

. READ

s WRITE

le RAM 中的数据由 READ、WRITE 以及 READ-MODIFY-WRITE 指令进行存取,下图为由 RAM 控制 LCD 的映象图。

e SEG

COM

COM3

COM2

COM1

COM0

六位地址(A5,A4…A0)

. SEG0

0

ww SEG1

1

w SEG2

IS61WV5128EDBLL-10TLI;中文规格书,Datasheet资料

6

pF

CI/O

Input/Output Capacitance

Vout = 0V

8

pF

5

Notes:

1. Tested initially and after any design or process changes that may affect these parameters.

2. Test conditions: Ta = 25°C, f = 1 MHz, Vdd = 3.3V.

Vdd

Vdd Relates to GND

–0.3 to 4.0

V

Tstg Pt

Storage Temperature Power Dissipation

–65 to +150

°C

1.0

W

2

Notes:

1. Stress greater than those listed under ABSOLUTE MAXIMUM RATINGS may cause permanent damage to

technology. This highly reliable process coupled with innovative circuit design techniques, yields high-performance and low power consumption devices.

36 mini BGA

44-Pin TSOP (Type II)

1

23

45

6

A

A0 A1 NC A3 A6 A8

B

I/O4 A2 WE A4 A7 I/O0

C

I/O5

NC A5

HM62V16256CLTT-5中文资料

Features

• • • Single 2.5 V and 3.0 V supply: 2.2 V to 3.6 V Fast access time: 55 ns/70 ns (max) Power dissipation: Active: 5.0 mW/MHz (typ)(VCC = 2.5 V) : 6.0 mW/MHz (typ) (VCC = 3.0 V) Standby: 2 µW (typ) (VCC = 2.5 V) : 2.4 µW (typ) (V CC = 3.0 V) Completely static memory. No clock or timing strobe required Equal access and cycle times Common data input and output. Three state output Battery backup operation. 2 chip selection for battery backup

1. This parameter is sampled and not 100% tested.

7

HM62V16256C Series

AC Characteristics (Ta = –20 to +70°C, VCC = 2.2 V to 3.6 V, unless otherwise noted.)

Operating current Average operating current

I CC

— —

5 18

20 35

mA mA

HM62V16256C-5 I CC1

HM62V16256C-7 I CC1 I CC2

— —

IS61LV25616AL英文数据手册

订购信息

商业级温度范围 0 +70

速度 ns

器件型号

10

IS61LV25616AL-10T

IS61LV25616AL-10K

ห้องสมุดไป่ตู้

IS61LV25616AL-10LQ

IS61LV25616AL-10B

12

IS61LV25616AL-12T

IS61LV25616AL-12K

IS61LV25616AL-12B

AC 波形

写周期 NO.1 CE 受控 OE 为高或低 (1)

注 1. WRITE 是内部产生的信号 它在 CE 和 WE 输入为低以及 LB 或 UB 输入为低的重叠时间内有效 2. WRITE= ( CE ) [ ( LB ) = ( UB ) ] ( WE ) 写周期 NO.2 WE 受控 写周期内 OE 为高 (1,2)

描述

ISSIIS61LV25616AL 是一个高速 4,194,304 位的静态 RAM 可组成 262,144 个字 16 位 该器件由

ISSI 的高性能 CMOS 技术制造而成 将这种高可靠性的处理技术与创新的电路设计技术相结合 就产生了

高性能和低功耗的 IS61LV25616AL 器件

当 OE 为高电平 不选 时 器件处于等待模式 功耗随着 CMOS 输入电平一起降低

最小 10 8 8 0 0 8 8 10 6 0

2

10 最大

5

6

最小 12 8 8 0 0 8 8 12 6 0

2

12 最大

6

单位

ns ns ns ns ns ns ns ns ns ns ns ns

广州周立功单片机发展有限公司 Tel 020 38730976 38730977 Fax 38730925 http // 注 1. 测试条件 信号跳变时间为 3ns 或更短 1.5V 的时间基准电平 0V 3.0V 的输入脉冲 图 1 所示的输

IS62LV1024L-70QI中文资料

ICSI reserves the right to make changes to its products at any time without notice in order to improve design and supply the best possible product. We assume no responsibility for any errors which may appear in this publication. © Copyright 2000, Integrated Circuit Solution Inc.DESCRIPTIONThe 1+51 IS62LV1024L and IS62LV1024LL are low powerand low Vcc,131,072-word by 8-bit CMOS static RAMs. They are fabricated using 1+51's high-performance CMOS technol-ogy. This highly reliable process coupled with innovative circuit design techniques, yields higher performance and low power consumption devices.When CE1 is HIGH or CE2 is LOW (deselected), the device assumes a standby mode at which the power dissipation can be reduced by using CMOS input levels.Easy memory expansion is provided by using two Chip Enable inputs, CE1 and CE2. The active LOW Write Enable (WE )controls both writing and reading of the memory.The IS62LV1024L and IS62LV1024LL are available in 32-pin 8*20mm TSOP-1, 8*13.4mm TSOP-1, 450mil SOP and 48-pin 6*8mm T.-BGA.CMOS STATIC RAM.EATURESAccess times of 45, 55, and 70 ns Low active power: 60 mW (typical)Low standby power: 15 µW (typical) CMOS standbyLow data retention voltage: 2V (min.) Available in Low Power (-L) and Ultra Low Power (-LL)Output Enable (OE ) and two Chip Enable (CE1 and CE2) inputs for ease in applications TTL compatible inputs and outputs Single 2.7V to 3.6V power supplyIS62LV1024L/LL1234567891011121314151632313029282726252423222120191817NC A16A14A12A7A6A5A4A3A2A1A0I/O0I/O1I/O2GNDVCC A15CE2WE A13A8A9A11OE A10CE1I/O7I/O6I/O5I/O4I/O3PIN CON.IGURATION32-Pin SOPPIN DESCRIPTIONSA0-A16Address Inputs CE1Chip Enable 1 Input CE2Chip Enable 2 Input OE Output Enable Input WE Write Enable Input I/O0-I/O7Input/OutputC o C onnectionVcc Power GNDGroundPIN CON.IGURATION32-Pin 8x20mm TSOP-1 and 8x13.4mm TSOP-1OPERATING RANGERangeAmbient TemperatureV CCCommercial 0°C to +70°C 2.7V to 3.6V Industrial40°C to +85°C2.7V to3.6V48-Pin 6x8mm T.-BGAIS62LV1024L/LLABSOLUTE MAXIMUM RATINGS (1)Symbol ParameterValueUnit V TERM Terminal Voltage with Respect to GND 0.5 to Vcc + 0.5V V CC Vcc related to GND0.3 to +4.6V T BIAS Temperature Under Bias 40 to +85°C T STG Storage Temperature 65 to +150°C P TPower Dissipation0.7WNotes:1.Stress greater than those listed under ABSOLUTE MAXIMUM RATINGS may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect reliability.CAPACITANCE (1,2)Symbol Parameter Conditions Max.Unit C IN Input Capacitance V IN = 0V 6p.C OUTOutput CapacitanceV OUT = 0V8p.Notes:1.Tested initially and after any design or process changes that may affect these parameters.2.Test conditions: T A = 25°C, f = 1 MHz, Vcc =3.0V.DC ELECTRICAL CHARACTERISTICS (Over Operating Range)Symbol ParameterTest ConditionsMin.Max.Unit V OH Output HIGH Voltage V CC = Min., I OH = 1.0 mA 2.2 V V OL Output LOW Voltage V CC = Min., I OL = 2.1 mA0.4V V IH Input HIGH Voltage 2.2V CC + 0.3V V IL Input LOW Voltage 0.30.4V I LI Input Leakage GND ≤ V IN ≤ V CC 11µA I LOOutput LeakageGND ≤ V OUT ≤ V CC11µANotes:1.V IL = 3.0V for pulse width less than 10 ns.TRUTH TABLEModeWE CE1CE2OE I/O Operation Vcc Current Not Selected X H X X High-Z I SB , I SB (Power-down)X X L X High-Z I SB , I SB Output Disabled H L H H High-Z I CC Read H L H L D OUT I CC WriteLLHXD INI CCIS62LV1024L/LLIS62LV1024L POWER SUPPLY CHARACTERISTICS(1)(Over Operating Range)-45L ns-55L ns-70L ns Symbol Parameter Test Conditions Min.Max.Min.Max.Min.Max.Unit I CC Vcc Dynamic Operating V CC = Max., CE = V IL Com. 40 35 30mASupply Current I OUT = 0 mA, f = f MAX Ind. 45 40 35I SB TTL Standby Current V CC = Max.,Com. 0.3 0.3 0.3mA(TTL Inputs)V IN = V IH or V IL, CE1≥ V IH Ind. 0.4 0.4 0.4or CE2 ≤ V IL, f = 0I SB CMOS Standby V CC = Max., f = 0Com. 50 50 50µACurrent (CMOS Inputs)CE1≥ V CC 0.2V,Ind. 75 75 75CE2 ≤ 0.2V,or V IN≥ V CC 0.2V, V IN≤ 0.2VNote:1.At f = f MAX, address and data inputs are cycling at the maximum frequency, f = 0 means no input lines change.IS62LV1024LL POWER SUPPLY CHARACTERISTICS(1)(Over Operating Range)-45LL ns-55LL ns-70LL ns Symbol Parameter Test Conditions Min.Max.Min.Max.Min.Max.Unit I CC Vcc Dynamic Operating V CC = Max., CE = V IL Com. 40 35 30mASupply Current I OUT = 0 mA, f = f MAX Ind. 45 40 35I SB TTL Standby Current V CC = Max.,Com. 0.2 0.2 0.2mA(TTL Inputs)V IN = V IH or V IL, CE1≥ V IH Ind. 0.3 0.3 0.3or CE2 ≤ V IL, f = 0I SB CMOS Standby V CC = Max., f = 0Com. 5 5 5µACurrent (CMOS Inputs)CE1≥ V CC 0.2V,Ind. 10 10 10CE2 ≤ 0.2V,or V IN≥ V CC 0.2V, V IN≤ 0.2VNote:1.At f = f MAX, address and data inputs are cycling at the maximum frequency, f = 0 means no input lines change.IS62LV1024L/LLREAD CYCLE SWITCHING CHARACTERISTICS(1)(Over Operating Range)-45-55-70Symbol Parameter Min.Max.Min.Max.Min.Max.Unit t RC Read Cycle Time45 55 70 ns t AA Address Access Time 45 55 70ns t OHA Output Hold Time10 10 10 ns t ACE CE1 Access Time 45 55 70ns t ACE CE2 Access Time 45 55 70ns t DOE OE Access Time 20 25 35ns t LZOE OE to Low-Z Output0 5 5 ns t HZOE OE to High-Z Output015020025ns t LZCE CE1 to Low-Z Output5 7 10 ns t LZCE CE2 to Low-Z Output5 7 10 ns t HZCE CE1 or CE2 to High-Z Output015020025ns Notes:1.Test conditions assume signal transition times of 5 ns or less, timing reference levels of 1.5V, input pulse levels of 0.4V to2.2Vand output loading specified in .igure 1.2.Tested with the load in .igure 2. Transition is measured ±500 mV from steady-state voltage. Not 100% tested.AC TEST CONDITIONSParameter UnitInput Pulse Level0.4V to 2.2VInput Rise and .all Times 5 nsInput and Output Timing 1.5Vand Reference LevelOutput Load See .igures 1AC TEST LOADS.igure 1..igure 2.IS62LV1024L/LLNotes:1.WE is HIGH for a Read Cycle.2.The device is continuously selected. OE , CE1 = V IL , CE2 = V IH .3.Address is valid prior to or coincident with CE1 LOW and CE2 HIGH transitions.(1,3)AC WAVE.ORMS (1,2)IS62LV1024L/LLWRITE CYCLE SWITCHING CHARACTERISTICS (1,3) (Over Operating Range, Standard and LowPower)-45-55-70SymbolParameter Min.Max.Min.Max.Min.Max.Unit t WC Write Cycle Time 45 55 70 ns t SCE CE1 to Write End 35 50 60 ns t SCE CE2 to Write End35 50 60 ns t AW Address Setup Time to Write End 35 50 60 ns t HA Address Hold from Write End 0 0 0 ns t SA Address Setup Time 0 0 0 ns t PWE " WE Pulse Width 35 40 55 ns t SD Data Setup to Write End 25 25 30 ns t HDData Hold from Write End0 0 0 ns t HZWE WE LOW to High-Z Output 15 20025ns t LZWE WE HIGH to Low-Z Output555nsNotes:1.Test conditions assume signal transition times of 5 ns or less, timing reference levels of 1.5V, input pulse levels of 0.4V to2.2V and output loading specified in .igure 1.2.Tested with the load in .igure 2. Transition is measured ±500 mV from steady-state voltage. Not 100% tested.3.The internal write time is defined by the overlap of CE1 LOW, CE2 HIGH and WE LOW. All signals must be in valid states to initiate a Write, but any one can go inactive to terminate the Write. The Data Input Setup and Hold timing are referenced to the rising or falling edge of the signal that terminates the Write.4.Tested with OE HIGH.AC WAVE.ORMSWRITE CYCLE NO. 1 (9- Controlled)(1,2)IS62LV1024L/LLWRITE CYCLE NO. 2 (+- , CE2 Controlled)(1,2)1.The internal write time is defined by the overlap of CE1 LOW, CE2 HIGH and WE LOW. All signals must be in valid states to initiate a Write, but any one can go inactive to terminate the Write. The Data Input Setup and Hold timing are referenced to the rising or falling edge of the signal that terminates the Write.2.I/O will assume the High-Z state if OE = V IH .DATA RETENTION SWITCHING CHARACTERISTICSSymbolParameterTest ConditionMin.Max.Unit V DRVcc for Data Retention See Data Retention Waveform 2.0 3.6V I DRData Retention CurrentVcc = 2.0V, CE1 ≥ Vcc 0.2VCom. (-L) 30µA Com. (-LL) 5µA Ind. (-L)50µA Ind. (-LL)10µA t SDR Data Retention Setup Time See Data Retention Waveform 0ns t RDRRecovery TimeSee Data Retention Waveformt RCnsDATA RETENTION WAVE.ORM (+- Controlled)IS62LV1024L/LLDATA RETENTION WAVE.ORM (CE2 Controlled)IS62LV1024LORDERING IN.ORMATION Commercial Range: 0°C to +70°C Speed (ns)Order Part No.Package45IS62LV1024L-45Q450mil SOPIS62LV1024L-45T8*20mm TSOP-1IS62LV1024L-45H8*13.4mm TSOP-1IS62LV1024L-45B6*8mm T.-BGA 55IS62LV1024L-55Q450mil SOPIS62LV1024L-55T8*20mm TSOP-1IS62LV1024L-55H8*13.4mm TSOP-1IS62LV1024L-55B6*8mm T.-BGA 70IS62LV1024L-70Q450mil SOPIS62LV1024L-70T8*20mm TSOP-1IS62LV1024L-70H8*13.4mm TSOP-1IS62LV1024L-70B6*8mm T.-BGA IS62LV1024LORDERING IN.ORMATION Industrial Range: 40°C to +85°C Speed (ns)Order Part No.Package45IS62LV1024L-45QI450mil SOPIS62LV1024L-45TI8*20mm TSOP-1IS62LV1024L-45HI8*13.4mm TSOP-1IS62LV1024L-45BI6*8mm T.-BGA 55IS62LV1024L-55QI450mil SOPIS62LV1024L-55TI8*20mm TSOP-1IS62LV1024L-55HI8*13.4mm TSOP-1IS62LV1024L-55BI6*8mm T.-BGA 70IS62LV1024L-70QI450mil SOPIS62LV1024L-70TI8*20mm TSOP-1IS62LV1024L-70HI8*13.4mm TSOP-1IS62LV1024L-70BI6*8mm T.-BGAIS62LV1024L/LLIntegrated Circuit Solution Inc.HEADQUARTER:NO.2, TECHNOLOGY RD. V, SCIENCE-BASED INDUSTRIAL PARK,HSIN-CHU, TAIWAN, R.O.C.TEL: 886-3-5780333.ax: 886-3-5783000BRANCH O..ICE:7., NO. 106, SEC. 1, HSIN-TAI 5TH ROAD,HSICHIH TAIPEI COUNTY, TAIWAN, R.O.C.TEL: 886-2-26962140.AX: 886-2-26962252IS62LV1024LLORDERING IN.ORMATIONCommercial Range: 0°C to +70°CSpeed (ns) Order Part No.Package 45IS62LV1024LL-45Q 450mil SOPIS62LV1024LL-45T 8*20mm TSOP-1IS62LV1024LL-45H 8*13.4mm TSOP-1IS62LV1024LL-45B 6*8mm T.-BGA 55IS62LV1024LL-55Q 450mil SOPIS62LV1024LL-55T 8*20mm TSOP-1IS62LV1024LL-55H 8*13.4mm TSOP-1IS62LV1024LL-55B 6*8mm T.-BGA 70IS62LV1024LL-70Q 450mil SOPIS62LV1024LL-70T 8*20mm TSOP-1IS62LV1024LL-70H 8*13.4mm TSOP-1IS62LV1024LL-70B6*8mm T.-BGAIS62LV1024LLORDERING IN.ORMATIONIndustrial Range: 40°C to +85°CSpeed (ns) Order Part No.Package 45IS62LV1024LL-45QI 450mil SOPIS62LV1024LL-45TI 8*20mm TSOP-1IS62LV1024LL-45HI 8*13.4mm TSOP-1IS62LV1024LL-45BI 6*8mm T.-BGA 55IS62LV1024LL-55QI 450mil SOPIS62LV1024LL-55TI 8*20mm TSOP-1IS62LV1024LL-55HI 8*13.4mm TSOP-1IS62LV1024LL-55BI 6*8mm T.-BGA 70IS62LV1024LL-70QI 450mil SOPIS62LV1024LL-70TI 8*20mm TSOP-1IS62LV1024LL-70HI 8*13.4mm TSOP-1IS62LV1024LL-70BI6*8mm T.-BGA。

IS62WV51216BLL-55TLI中文资料

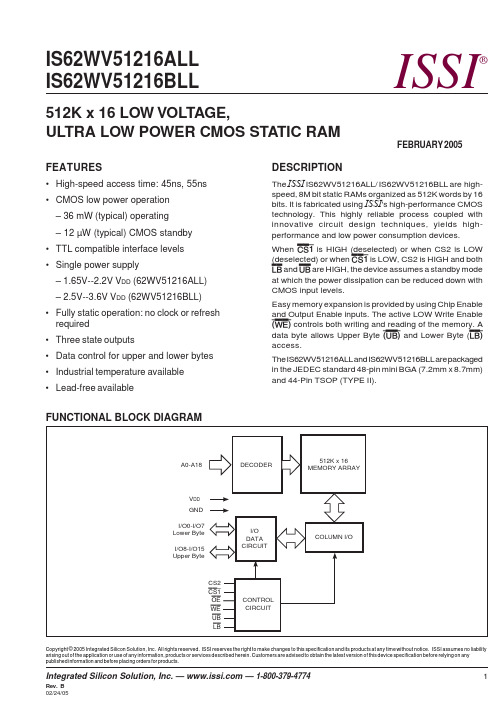

IS62WV51216ALL IS62WV51216BLLISSI®Copyright © 2005 Integrated Silicon Solution, Inc. All rights reserved. ISSI reserves the right to make changes to this specification and its products at any time without notice. ISSI assumes no liability arising out of the application or use of any information, products or services described herein. Customers are advised to obtain the latest version of this device specification before relying on any published information and before placing orders for products.512K x 16 LOW VOLTAGE,ULTRA LOW POWER CMOS STATIC RAMFEATURES•High-speed access time: 45ns, 55ns •CMOS low power operation – 36 mW (typical) operating – 12 µW (typical) CMOS standby •TTL compatible interface levels •Single power supply– 1.65V--2.2V V DD (62WV51216ALL)– 2.5V--3.6V V DD (62WV51216BLL)•Fully static operation: no clock or refresh required •Three state outputs•Data control for upper and lower bytes •Industrial temperature available •Lead-free availableDESCRIPTIONThe ISSI IS62WV51216ALL/ IS62WV51216BLL are high-speed, 8M bit static RAMs organized as 512K words by 16bits. It is fabricated using ISSI 's high-performance CMOS technology. This highly reliable process coupled with innovative circuit design techniques, yields high-performance and low power consumption devices.When CS1 is HIGH (deselected) or when CS2 is LOW (deselected) or when CS1 is LOW, CS2 is HIGH and both LB and UB are HIGH, the device assumes a standby mode at which the power dissipation can be reduced down with CMOS input levels.Easy memory expansion is provided by using Chip Enable and Output Enable inputs. The active LOW Write Enable (WE) controls both writing and reading of the memory. A data byte allows Upper Byte (UB) and Lower Byte (LB)access.The IS62WV51216ALL and IS62WV51216BLL are packaged in the JEDEC standard 48-pin mini BGA (7.2mm x 8.7mm)and 44-Pin TSOP (TYPE II).FUNCTIONAL BLOCK DIAGRAMFEBRUARY 2005IS62WV51216ALL, IS62WV51216BLL ISSI®PIN CONFIGURATIONS48-Pin mini BGA (7.2mm x 8.7mm)PIN DESCRIPTIONSA0-A18Address InputsI/O0-I/O15Data Inputs/OutputsCS1, CS2Chip Enable InputOE Output Enable InputWE Write Enable InputLB Lower-byte Control (I/O0-I/O7) UB Upper-byte Control (I/O8-I/O15) NC No ConnectionV DD PowerGND Ground1 2 3 4 5 6A B C D E F G HLB OE A0A1A2CS2I/O8UB A3A4CS1I/O0I/O9I/O10A5A6I/O1I/O2 GND I/O11A17A7I/O3V DD` V DD I/O12GND A16I/O4GND I/O14I/O13A14A15I/O5I/O6 I/O15NC A12A13WE I/O7A18A8A9A10A11NC1234567891011121314151617181920212244434241403938373635343332313029282726252423A4 A3 A2 A1 A0 CS1 I/O0 I/O1 I/O2 I/O3 V DD GND I/O4 I/O5 I/O6 I/O7 WE A16 A15 A14 A13 A12A5A6A7 OE UB LB I/O15 I/O14 I/O13 I/O12 GND V DD I/O11 I/O10 I/O9 I/O8 A18 A8A9A10 A11 A1744-Pin TSOP (Type II)2Integrated Silicon Solution, Inc. — — 1-800-379-4774Rev.BIS62WV51216ALL, IS62WV51216BLL ISSI®TRUTH TABLEI/O PINMode WE CS1CS2OE LB UB I/O0-I/O7I/O8-I/O15V DD Current Not Selected X H X X X X High-Z High-Z I SB1, I SB2X X L X X X High-Z High-Z I SB1, I SB2X X X X H H High-Z High-Z I SB1, I SB2 Output Disabled H L H H L X High-Z High-Z I CCH L H H X L High-Z High-Z I CCRead H L H L L H D OUT High-Z I CCH L H L H L High-Z D OUTH L H L L L D OUT D OUTWrite L L H X L H D IN High-Z I CCL L H X H L High-Z D INL L H X L L D IN D INOPERATING RANGE (V DD)Range Ambient Temperature IS62WV51216ALL (70ns)IS62WV51216BLL (55ns, 70ns)IS62WV51216BLL (45ns) Commercial0°C to +70°C 1.65V - 2.2V 2.5V - 3.6V 3.0 - 3.6VIndustrial–40°C to +85°C 1.65V - 2.2V 2.5V - 3.6VIS62WV51216ALL, IS62WV51216BLL ISSI®ABSOLUTE MAXIMUM RATINGS(1)Symbol Parameter Value UnitV TERM Terminal Voltage with Respect to GND–0.2 to V DD+0.3VT BIAS Temperature Under Bias–40 to +85°CV DD V DD Related to GND–0.2 to +3.8VT STG Storage Temperature–65 to +150°CP T Power Dissipation 1.0WNote:1.Stress greater than those listed under ABSOLUTE MAXIMUM RATINGS may cause permanent damage to thedevice. This is a stress rating only and functional operation of the device at these or any other conditions abovethose indicated in the operational sections of this specification is not implied. Exposure to absolute maximumrating conditions for extended periods may affect reliability.DC ELECTRICAL CHARACTERISTICS(Over Operating Range)Symbol Parameter Test Conditions V DD Min.Max.Unit V OH Output HIGH Voltage I OH = -0.1 mA 1.65-2.2V 1.4—VI OH = -1 mA 2.5-3.6V 2.2—VV OL Output LOW Voltage I OL = 0.1 mA 1.65-2.2V—0.2VI OL = 2.1 mA 2.5-3.6V—0.4VV IH Input HIGH Voltage 1.65-2.2V 1.4V DD + 0.2V2.5-3.6V 2.2V DD + 0.3VV IL(1)Input LOW Voltage 1.65-2.2V–0.20.4V2.5-3.6V–0.20.6VI LI Input Leakage GND ≤ V IN≤ V DD–11µAI LO Output Leakage GND ≤ V OUT≤ V DD, Outputs Disabled–11µA Notes:1.V IL (min.) = –1.0V for pulse width less than 10 ns.4Integrated Silicon Solution, Inc. — — 1-800-379-4774Rev.BIS62WV51216ALL, IS62WV51216BLL ISSI®CAPACITANCE(1)Symbol Parameter Conditions Max.UnitC IN Input Capacitance V IN = 0V8pFC OUT Input/Output Capacitance V OUT = 0V10pFNote:1.Tested initially and after any design or process changes that may affect these parameters.AC TEST CONDITIONSParameter62WV51216ALL62WV51216BLL(Unit)(Unit)Input Pulse Level0.4V to V DD-0.20.4V to V DD-0.3VInput Rise and Fall Times 5 ns5nsInput and Output Timing V REF V REFand Reference LevelOutput Load See Figures 1 and 2See Figures 1 and 262WV51216ALL62WV51216BLL(1.65V - 2.2V)(2.5V - 3.6V)R1(Ω)30701029R2(Ω)31501728V REF0.9V 1.5VV TM 1.8V 2.8VAC TEST LOADSFigure 1IS62WV51216ALL, IS62WV51216BLL ISSI®IS62WV51216ALL, POWER SUPPLY CHARACTERISTICS(1)(Over Operating Range)Symbol Parameter Test Conditions Max.Unit70I C C V DD D ynamic O perating V DD=M ax.,Com.20m ASupply C urrent I OUT = 0 mA, f = f MAX Ind.25I CC1Operating S upply V DD = Max., CS1 = 0.2V Com.4m ACurrent WE = V DD – 0.2V Ind.4CS2 = V DD – 0.2V, f = 1MHZI SB1TTL Standby Current V DD=M ax.,Com.0.3m A(TTL Inputs)V IN = V IH or V IL Ind.0.3CS1 = V IH , CS2 = V IL,f = 1 MH ZORULB Control V DD = Max., V IN = V IH or V ILCS1 = V IL, f = 0, UB = V IH, LB = V IHI SB2CMOS S tandby V DD=M ax.,Com.15µACurrent (CMOS Inputs)CS1≥V DD – 0.2V,Ind.21CS2 ≤ 0.2V,typ.(1)3V IN≥V DD – 0.2V, orV IN≤0.2V, f = 0ORULB Control V DD = Max., CS1 = V IL, CS2=V IHV IN≥ V DD – 0.2V, or V IN≤ 0.2V, f = 0;UB / LB = V DD – 0.2VNote:.1. Typical values are measured at V DD = 1.8V, T A = 25o C and not 100% tested.6Integrated Silicon Solution, Inc. — — 1-800-379-4774Rev.BIS62WV51216ALL, IS62WV51216BLL ISSI®IS62WV51216BLL, POWER SUPPLY CHARACTERISTICS(1)(Over Operating Range)Symbol Parameter Test Conditions Max.Max.Max.Unit455570I C C V DD D ynamic O perating V DD=M ax.,Com.353025m ASupply C urrent I OUT = 0 mA, f = f MAX Ind.403530I CC1Operating S upply V DD = Max., CS1 = 0.2V Com.555m ACurrent WE = V DD – 0.2V Ind.555CS2 = V DD – 0.2V, f = 1MHZI SB1TTL Standby Current V DD=M ax.,Com.0.30.30.3m A(TTL Inputs)V IN = V IH or V IL Ind.0.30.30.3CS1 = V IH , CS2 = V IL,f = 1 MH ZORULB Control V DD = Max., V IN = V IH or V ILCS1 = V IL, f = 0, UB = V IH, LB = V IHI SB2CMOS S tandby V DD=M ax.,Com.202020µACurrent (CMOS Inputs)CS1≥V DD – 0.2V,Ind.252525CS2 ≤ 0.2V,typ. (2)444V IN≥V DD – 0.2V, orV IN≤0.2V, f = 0ORULB Control V DD = Max., CS1 = V IL, CS2=V IHV IN≥ V DD – 0.2V, or V IN≤ 0.2V, f = 0;UB / LB = V DD – 0.2VNote:1.At f = f MAX, address and data inputs are cycling at the maximum frequency, f = 0 means no input lines change.2. Typical values are measured at V DD =3.0V, T A = 25o C and not 100% tested.IS62WV51216ALL, IS62WV51216BLL ISSI®READ CYCLE SWITCHING CHARACTERISTICS(1)(Over Operating Range)45 ns55 ns70 nsSymbol Parameter Min.Max.Min.Max.Min.Max.Unit t RC Read Cycle Time45—55—70—ns t AA Address Access Time—45—55—70ns t OHA Output Hold Time10—10—10—ns t ACS1/t ACS2CS1/CS2 Access Time—45—55—70ns t DOE OE Access Time—20—25—35ns t HZOE(2)OE to High-Z Output—15—20—25ns t LZOE(2)OE to Low-Z Output5—5—5—ns t HZCS1/t HZCS2(2)CS1/CS2 to High-Z Output015020025ns t LZCS1/t LZCS2(2)CS1/CS2 to Low-Z Output10—10—10—ns t BA LB, UB Access Time—45—55—70ns t HZB LB, UB to High-Z Output015020025ns t LZB LB, UB to Low-Z Output0—0—0—ns Notes:1.Test conditions assume signal transition times of 5 ns or less, timing reference levels of 0.9V/1.5V, input pulse levels of 0.4 toV DD-0.2V/0.4V to V DD-0.3V and output loading specified in Figure 1.2.Tested with the load in Figure 2. Transition is measured ±500 mV from steady-state voltage. Not 100% tested.AC WAVEFORMSREAD CYCLE NO. 1(1,2) (Address Controlled) (CS1 = OE = V IL,CS2 = WE = V IH, UB or LB = V IL)8Integrated Silicon Solution, Inc. — — 1-800-379-4774Rev.BIS62WV51216ALL, IS62WV51216BLL ISSI®AC WAVEFORMSREAD CYCLE NO. 2(1,3)(CS1,CS2, OE, AND UB/LB Controlled)1.WE is HIGH for a Read Cycle.2.The device is continuously selected. OE, CS1, UB, or LB = V IL. CS2=WE=V IH.3.Address is valid prior to or coincident with CS1 LOW transition.IS62WV51216ALL, IS62WV51216BLL ISSI®WRITE CYCLE SWITCHING CHARACTERISTICS(1,2) (Over Operating Range)45ns55 ns70 nsSymbol Parameter Min.Max. Min.Max. Min.Max.Unit t WC Write Cycle Time 45— 55— 70—ns t SCS1/t SCS2CS1/CS2 to Write End 35— 45— 60—ns t AW Address Setup Time to Write End 35— 45— 60—ns t HA Address Hold from Write End 0— 0— 0—ns t SA Address Setup Time 0— 0— 0—ns t PWB LB, UB Valid to End of Write 35— 45— 60—ns t PWE(4)WE Pulse Width 35— 40— 50—ns t SD Data Setup to Write End 20— 25— 30—ns t HD Data Hold from Write End 0— 0— 0—ns t HZWE(3)WE LOW to High-Z Output —20 —20 —30ns t LZWE(3)WE HIGH to Low-Z Output 5— 5— 5—ns Notes:1.Test conditions assume signal transition times of 5 ns or less, timing reference levels of 0.9V/1.5V, input pulse levels of 0.4 toV DD-0.2V/0.4V to V DD-0.3V and output loading specified in Figure 1.2.The internal write time is defined by the overlap of CS1 LOW, CS2 HIGH and UB or LB, and WE LOW. All signals must be in valid states to initiate a Write, butany one can go inactive to terminate the Write. The Data Input Setup and Hold timing are referenced to the rising or falling edge of the signal that terminates the write.3.Tested with the load in Figure 2. Transition is measured ±500 mV from steady-state voltage. Not 100% tested.4. t PWE> t HZWE + t SD when OE is LOW.AC WAVEFORMSWRITE CYCLE NO. 1(1,2)(CS1 Controlled, OE = HIGH or LOW)1.WRITE is an internally generated signal asserted during an overlap of the LOW states on the CS1 , CS2 and WE inputs and atleast one of the LB and UB inputs being in the LOW state.2.WRITE = (CS1) [ (LB) = (UB) ] (WE).10Integrated Silicon Solution, Inc. — — 1-800-379-4774Rev.BIS62WV51216ALL, IS62WV51216BLL ISSI®WRITE CYCLE NO. 2 (WE Controlled: OE is HIGH During Write Cycle)WRITE CYCLE NO. 3 (WE Controlled: OE is LOW During Write Cycle)Integrated Silicon Solution, Inc. — — 1-800-379-477411 Rev.B02/24/05IS62WV51216ALL, IS62WV51216BLL ISSI®WRITE CYCLE NO. 4 (UB/LB Controlled)12Integrated Silicon Solution, Inc. — — 1-800-379-4774Rev.B02/24/05IS62WV51216ALL, IS62WV51216BLL ISSI®DATA RETENTION SWITCHING CHARACTERISTICSSymbol Parameter Test Condition Min.Max.UnitV DR V DD for Data Retention See Data Retention Waveform 1.2 3.6VI DR Data Retention Current V DD = 1.2V, CS1≥ V DD – 0.2V—20µAt SDR Data Retention Setup Time See Data Retention Waveform0—nst RDR Recovery Time See Data Retention Waveform t RC—nsDATA RETENTION WAVEFORM (CS1 Controlled)DATA RETENTION WAVEFORM (CS2 Controlled)Integrated Silicon Solution, Inc. — — 1-800-379-477413 Rev.B02/24/05IS62WV51216ALL, IS62WV51216BLL ISSI®ORDERING INFORMATIONIS62WV51216ALL (1.65V - 2.2V)Industrial Range: –40°C to +85°CSpeed (ns)Order Part No.Package70IS62WV51216ALL-70TI TSOP-IIIS62WV51216ALL-70BI mini BGA (7.2mm x 8.7mm)IS62WV51216ALL-70XI DIEORDERING INFORMATIONIS62WV51216BLL (2.5V - 3.6V)Commercial Range: 0°C to +70°CSpeed (ns)Order Part No.Package45IS62WV51216BLL-45B mini BGA (7.2mm x 8.7mm) Industrial Range: –40°C to +85°CSpeed (ns)Order Part No.Package55IS62WV51216BLL-55TI TSOP-IIIS62WV51216BLL-55TLI TSOP-II, Lead-freeIS62WV51216BLL-55BI mini BGA (7.2mm x 8.7mm)IS62WV51216BLL-55BLI mini BGA (7.2mm x 8.7mm), Lead-free 70IS62WV51216BLL-70XI DIE14Integrated Silicon Solution, Inc. — — 1-800-379-4774Rev.B02/24/05Integrated Silicon Solution, Inc. — — 1-800-379-477415Rev.B 02/24/05IS62WV51216ALL, IS62WV51216BLL ISSI®Mini Ball Grid ArrayPackage Code: B (48-pin)Notes:1. Controlling dimensions are in millimeters.T op View Bottom ViewmBGA - 7.2mm x 8.7mmMILLIMETERSINCHES Sym.Min.Typ.Max.Min.Typ.Max.N0.Leads 48A —— 1.20— —0.047A10 .24—0.300.009 —0.012A20.60——0.024——D 8.608.708.800.3390.3430.346D1 5.25BSC 0.207BSC E 7.107.207.300.2800.2830.287E1 3.75BSC 0.148BSC e 0.75BSC 0.030BSC b0.300.350.400.0120.0140.016PACKAGING INFORMATIONISSI®Integrated Silicon Solution, Inc. — — 1-800-379-4774Rev.F 06/18/03Copyright © 2003 Integrated Silicon Solution, Inc. All rights reserved. ISSI reserves the right to make changes to this specification and its products at any timewithout notice. ISSI assumes no liability arising out of the application or use of any information, products or services described herein. Customers are advised to obtain the latest version of this device specification before relying on any published information and before placing orders for products.Plastic TSOPPackage Code: T (Type II)。

IS62WV51216BLL中文资料

IS62WV51216ALL IS62WV51216BLLISSI®Copyright © 2005 Integrated Silicon Solution, Inc. All rights reserved. ISSI reserves the right to make changes to this specification and its products at any time without notice. ISSI assumes no liability arising out of the application or use of any information, products or services described herein. Customers are advised to obtain the latest version of this device specification before relying on any published information and before placing orders for products.512K x 16 LOW VOLTAGE,ULTRA LOW POWER CMOS STATIC RAMFEATURES•High-speed access time: 45ns, 55ns •CMOS low power operation – 36 mW (typical) operating – 12 µW (typical) CMOS standby •TTL compatible interface levels •Single power supply– 1.65V--2.2V V DD (62WV51216ALL)– 2.5V--3.6V V DD (62WV51216BLL)•Fully static operation: no clock or refresh required •Three state outputs•Data control for upper and lower bytes •Industrial temperature available •Lead-free availableDESCRIPTIONThe ISSI IS62WV51216ALL/ IS62WV51216BLL are high-speed, 8M bit static RAMs organized as 512K words by 16bits. It is fabricated using ISSI 's high-performance CMOS technology. This highly reliable process coupled with innovative circuit design techniques, yields high-performance and low power consumption devices.When CS1 is HIGH (deselected) or when CS2 is LOW (deselected) or when CS1 is LOW, CS2 is HIGH and both LB and UB are HIGH, the device assumes a standby mode at which the power dissipation can be reduced down with CMOS input levels.Easy memory expansion is provided by using Chip Enable and Output Enable inputs. The active LOW Write Enable (WE) controls both writing and reading of the memory. A data byte allows Upper Byte (UB) and Lower Byte (LB)access.The IS62WV51216ALL and IS62WV51216BLL are packaged in the JEDEC standard 48-pin mini BGA (7.2mm x 8.7mm)and 44-Pin TSOP (TYPE II).FUNCTIONAL BLOCK DIAGRAMFEBRUARY 2005IS62WV51216ALL, IS62WV51216BLL ISSI®PIN CONFIGURATIONS48-Pin mini BGA (7.2mm x 8.7mm)PIN DESCRIPTIONSA0-A18Address InputsI/O0-I/O15Data Inputs/OutputsCS1, CS2Chip Enable InputOE Output Enable InputWE Write Enable InputLB Lower-byte Control (I/O0-I/O7) UB Upper-byte Control (I/O8-I/O15) NC No ConnectionV DD PowerGND Ground1 2 3 4 5 6A B C D E F G HLB OE A0A1A2CS2I/O8UB A3A4CS1I/O0I/O9I/O10A5A6I/O1I/O2 GND I/O11A17A7I/O3V DD` V DD I/O12GND A16I/O4GND I/O14I/O13A14A15I/O5I/O6 I/O15NC A12A13WE I/O7A18A8A9A10A11NC1234567891011121314151617181920212244434241403938373635343332313029282726252423A4 A3 A2 A1 A0 CS1 I/O0 I/O1 I/O2 I/O3 V DD GND I/O4 I/O5 I/O6 I/O7 WE A16 A15 A14 A13 A12A5A6A7 OE UB LB I/O15 I/O14 I/O13 I/O12 GND V DD I/O11 I/O10 I/O9 I/O8 A18 A8A9A10 A11 A1744-Pin TSOP (Type II)2Integrated Silicon Solution, Inc. — — 1-800-379-4774Rev.BIS62WV51216ALL, IS62WV51216BLL ISSI®TRUTH TABLEI/O PINMode WE CS1CS2OE LB UB I/O0-I/O7I/O8-I/O15V DD Current Not Selected X H X X X X High-Z High-Z I SB1, I SB2X X L X X X High-Z High-Z I SB1, I SB2X X X X H H High-Z High-Z I SB1, I SB2 Output Disabled H L H H L X High-Z High-Z I CCH L H H X L High-Z High-Z I CCRead H L H L L H D OUT High-Z I CCH L H L H L High-Z D OUTH L H L L L D OUT D OUTWrite L L H X L H D IN High-Z I CCL L H X H L High-Z D INL L H X L L D IN D INOPERATING RANGE (V DD)Range Ambient Temperature IS62WV51216ALL (70ns)IS62WV51216BLL (55ns, 70ns)IS62WV51216BLL (45ns) Commercial0°C to +70°C 1.65V - 2.2V 2.5V - 3.6V 3.0 - 3.6VIndustrial–40°C to +85°C 1.65V - 2.2V 2.5V - 3.6VIS62WV51216ALL, IS62WV51216BLL ISSI®ABSOLUTE MAXIMUM RATINGS(1)Symbol Parameter Value UnitV TERM Terminal Voltage with Respect to GND–0.2 to V DD+0.3VT BIAS Temperature Under Bias–40 to +85°CV DD V DD Related to GND–0.2 to +3.8VT STG Storage Temperature–65 to +150°CP T Power Dissipation 1.0WNote:1.Stress greater than those listed under ABSOLUTE MAXIMUM RATINGS may cause permanent damage to thedevice. This is a stress rating only and functional operation of the device at these or any other conditions abovethose indicated in the operational sections of this specification is not implied. Exposure to absolute maximumrating conditions for extended periods may affect reliability.DC ELECTRICAL CHARACTERISTICS(Over Operating Range)Symbol Parameter Test Conditions V DD Min.Max.Unit V OH Output HIGH Voltage I OH = -0.1 mA 1.65-2.2V 1.4—VI OH = -1 mA 2.5-3.6V 2.2—VV OL Output LOW Voltage I OL = 0.1 mA 1.65-2.2V—0.2VI OL = 2.1 mA 2.5-3.6V—0.4VV IH Input HIGH Voltage 1.65-2.2V 1.4V DD + 0.2V2.5-3.6V 2.2V DD + 0.3VV IL(1)Input LOW Voltage 1.65-2.2V–0.20.4V2.5-3.6V–0.20.6VI LI Input Leakage GND ≤ V IN≤ V DD–11µAI LO Output Leakage GND ≤ V OUT≤ V DD, Outputs Disabled–11µA Notes:1.V IL (min.) = –1.0V for pulse width less than 10 ns.4Integrated Silicon Solution, Inc. — — 1-800-379-4774Rev.BIS62WV51216ALL, IS62WV51216BLL ISSI®CAPACITANCE(1)Symbol Parameter Conditions Max.UnitC IN Input Capacitance V IN = 0V8pFC OUT Input/Output Capacitance V OUT = 0V10pFNote:1.Tested initially and after any design or process changes that may affect these parameters.AC TEST CONDITIONSParameter62WV51216ALL62WV51216BLL(Unit)(Unit)Input Pulse Level0.4V to V DD-0.20.4V to V DD-0.3VInput Rise and Fall Times 5 ns5nsInput and Output Timing V REF V REFand Reference LevelOutput Load See Figures 1 and 2See Figures 1 and 262WV51216ALL62WV51216BLL(1.65V - 2.2V)(2.5V - 3.6V)R1(Ω)30701029R2(Ω)31501728V REF0.9V 1.5VV TM 1.8V 2.8VAC TEST LOADSFigure 1IS62WV51216ALL, IS62WV51216BLL ISSI®IS62WV51216ALL, POWER SUPPLY CHARACTERISTICS(1)(Over Operating Range)Symbol Parameter Test Conditions Max.Unit70I C C V DD D ynamic O perating V DD=M ax.,Com.20m ASupply C urrent I OUT = 0 mA, f = f MAX Ind.25I CC1Operating S upply V DD = Max., CS1 = 0.2V Com.4m ACurrent WE = V DD – 0.2V Ind.4CS2 = V DD – 0.2V, f = 1MHZI SB1TTL Standby Current V DD=M ax.,Com.0.3m A(TTL Inputs)V IN = V IH or V IL Ind.0.3CS1 = V IH , CS2 = V IL,f = 1 MH ZORULB Control V DD = Max., V IN = V IH or V ILCS1 = V IL, f = 0, UB = V IH, LB = V IHI SB2CMOS S tandby V DD=M ax.,Com.15µACurrent (CMOS Inputs)CS1≥V DD – 0.2V,Ind.21CS2 ≤ 0.2V,typ.(1)3V IN≥V DD – 0.2V, orV IN≤0.2V, f = 0ORULB Control V DD = Max., CS1 = V IL, CS2=V IHV IN≥ V DD – 0.2V, or V IN≤ 0.2V, f = 0;UB / LB = V DD – 0.2VNote:.1. Typical values are measured at V DD = 1.8V, T A = 25o C and not 100% tested.6Integrated Silicon Solution, Inc. — — 1-800-379-4774Rev.BIS62WV51216ALL, IS62WV51216BLL ISSI®IS62WV51216BLL, POWER SUPPLY CHARACTERISTICS(1)(Over Operating Range)Symbol Parameter Test Conditions Max.Max.Max.Unit455570I C C V DD D ynamic O perating V DD=M ax.,Com.353025m ASupply C urrent I OUT = 0 mA, f = f MAX Ind.403530I CC1Operating S upply V DD = Max., CS1 = 0.2V Com.555m ACurrent WE = V DD – 0.2V Ind.555CS2 = V DD – 0.2V, f = 1MHZI SB1TTL Standby Current V DD=M ax.,Com.0.30.30.3m A(TTL Inputs)V IN = V IH or V IL Ind.0.30.30.3CS1 = V IH , CS2 = V IL,f = 1 MH ZORULB Control V DD = Max., V IN = V IH or V ILCS1 = V IL, f = 0, UB = V IH, LB = V IHI SB2CMOS S tandby V DD=M ax.,Com.202020µACurrent (CMOS Inputs)CS1≥V DD – 0.2V,Ind.252525CS2 ≤ 0.2V,typ. (2)444V IN≥V DD – 0.2V, orV IN≤0.2V, f = 0ORULB Control V DD = Max., CS1 = V IL, CS2=V IHV IN≥ V DD – 0.2V, or V IN≤ 0.2V, f = 0;UB / LB = V DD – 0.2VNote:1.At f = f MAX, address and data inputs are cycling at the maximum frequency, f = 0 means no input lines change.2. Typical values are measured at V DD =3.0V, T A = 25o C and not 100% tested.IS62WV51216ALL, IS62WV51216BLL ISSI®READ CYCLE SWITCHING CHARACTERISTICS(1)(Over Operating Range)45 ns55 ns70 nsSymbol Parameter Min.Max.Min.Max.Min.Max.Unit t RC Read Cycle Time45—55—70—ns t AA Address Access Time—45—55—70ns t OHA Output Hold Time10—10—10—ns t ACS1/t ACS2CS1/CS2 Access Time—45—55—70ns t DOE OE Access Time—20—25—35ns t HZOE(2)OE to High-Z Output—15—20—25ns t LZOE(2)OE to Low-Z Output5—5—5—ns t HZCS1/t HZCS2(2)CS1/CS2 to High-Z Output015020025ns t LZCS1/t LZCS2(2)CS1/CS2 to Low-Z Output10—10—10—ns t BA LB, UB Access Time—45—55—70ns t HZB LB, UB to High-Z Output015020025ns t LZB LB, UB to Low-Z Output0—0—0—ns Notes:1.Test conditions assume signal transition times of 5 ns or less, timing reference levels of 0.9V/1.5V, input pulse levels of 0.4 toV DD-0.2V/0.4V to V DD-0.3V and output loading specified in Figure 1.2.Tested with the load in Figure 2. Transition is measured ±500 mV from steady-state voltage. Not 100% tested.AC WAVEFORMSREAD CYCLE NO. 1(1,2) (Address Controlled) (CS1 = OE = V IL,CS2 = WE = V IH, UB or LB = V IL)8Integrated Silicon Solution, Inc. — — 1-800-379-4774Rev.BIS62WV51216ALL, IS62WV51216BLL ISSI®AC WAVEFORMSREAD CYCLE NO. 2(1,3)(CS1,CS2, OE, AND UB/LB Controlled)1.WE is HIGH for a Read Cycle.2.The device is continuously selected. OE, CS1, UB, or LB = V IL. CS2=WE=V IH.3.Address is valid prior to or coincident with CS1 LOW transition.IS62WV51216ALL, IS62WV51216BLL ISSI®WRITE CYCLE SWITCHING CHARACTERISTICS(1,2) (Over Operating Range)45ns55 ns70 nsSymbol Parameter Min.Max. Min.Max. Min.Max.Unit t WC Write Cycle Time 45— 55— 70—ns t SCS1/t SCS2CS1/CS2 to Write End 35— 45— 60—ns t AW Address Setup Time to Write End 35— 45— 60—ns t HA Address Hold from Write End 0— 0— 0—ns t SA Address Setup Time 0— 0— 0—ns t PWB LB, UB Valid to End of Write 35— 45— 60—ns t PWE(4)WE Pulse Width 35— 40— 50—ns t SD Data Setup to Write End 20— 25— 30—ns t HD Data Hold from Write End 0— 0— 0—ns t HZWE(3)WE LOW to High-Z Output —20 —20 —30ns t LZWE(3)WE HIGH to Low-Z Output 5— 5— 5—ns Notes:1.Test conditions assume signal transition times of 5 ns or less, timing reference levels of 0.9V/1.5V, input pulse levels of 0.4 toV DD-0.2V/0.4V to V DD-0.3V and output loading specified in Figure 1.2.The internal write time is defined by the overlap of CS1 LOW, CS2 HIGH and UB or LB, and WE LOW. All signals must be in valid states to initiate a Write, butany one can go inactive to terminate the Write. The Data Input Setup and Hold timing are referenced to the rising or falling edge of the signal that terminates the write.3.Tested with the load in Figure 2. Transition is measured ±500 mV from steady-state voltage. Not 100% tested.4. t PWE> t HZWE + t SD when OE is LOW.AC WAVEFORMSWRITE CYCLE NO. 1(1,2)(CS1 Controlled, OE = HIGH or LOW)1.WRITE is an internally generated signal asserted during an overlap of the LOW states on the CS1 , CS2 and WE inputs and atleast one of the LB and UB inputs being in the LOW state.2.WRITE = (CS1) [ (LB) = (UB) ] (WE).10Integrated Silicon Solution, Inc. — — 1-800-379-4774Rev.BIS62WV51216ALL, IS62WV51216BLL ISSI®WRITE CYCLE NO. 2 (WE Controlled: OE is HIGH During Write Cycle)WRITE CYCLE NO. 3 (WE Controlled: OE is LOW During Write Cycle)Integrated Silicon Solution, Inc. — — 1-800-379-477411 Rev.B02/24/05IS62WV51216ALL, IS62WV51216BLL ISSI®WRITE CYCLE NO. 4 (UB/LB Controlled)12Integrated Silicon Solution, Inc. — — 1-800-379-4774Rev.B02/24/05IS62WV51216ALL, IS62WV51216BLL ISSI®DATA RETENTION SWITCHING CHARACTERISTICSSymbol Parameter Test Condition Min.Max.UnitV DR V DD for Data Retention See Data Retention Waveform 1.2 3.6VI DR Data Retention Current V DD = 1.2V, CS1≥ V DD – 0.2V—20µAt SDR Data Retention Setup Time See Data Retention Waveform0—nst RDR Recovery Time See Data Retention Waveform t RC—nsDATA RETENTION WAVEFORM (CS1 Controlled)DATA RETENTION WAVEFORM (CS2 Controlled)Integrated Silicon Solution, Inc. — — 1-800-379-477413 Rev.B02/24/05IS62WV51216ALL, IS62WV51216BLL ISSI®ORDERING INFORMATIONIS62WV51216ALL (1.65V - 2.2V)Industrial Range: –40°C to +85°CSpeed (ns)Order Part No.Package70IS62WV51216ALL-70TI TSOP-IIIS62WV51216ALL-70BI mini BGA (7.2mm x 8.7mm)IS62WV51216ALL-70XI DIEORDERING INFORMATIONIS62WV51216BLL (2.5V - 3.6V)Commercial Range: 0°C to +70°CSpeed (ns)Order Part No.Package45IS62WV51216BLL-45B mini BGA (7.2mm x 8.7mm) Industrial Range: –40°C to +85°CSpeed (ns)Order Part No.Package55IS62WV51216BLL-55TI TSOP-IIIS62WV51216BLL-55TLI TSOP-II, Lead-freeIS62WV51216BLL-55BI mini BGA (7.2mm x 8.7mm)IS62WV51216BLL-55BLI mini BGA (7.2mm x 8.7mm), Lead-free 70IS62WV51216BLL-70XI DIE14Integrated Silicon Solution, Inc. — — 1-800-379-4774Rev.B02/24/05Integrated Silicon Solution, Inc. — — 1-800-379-477415Rev.B 02/24/05IS62WV51216ALL, IS62WV51216BLL ISSI®Mini Ball Grid ArrayPackage Code: B (48-pin)Notes:1. Controlling dimensions are in millimeters.T op View Bottom ViewmBGA - 7.2mm x 8.7mmMILLIMETERSINCHES Sym.Min.Typ.Max.Min.Typ.Max.N0.Leads 48A —— 1.20— —0.047A10 .24—0.300.009 —0.012A20.60——0.024——D 8.608.708.800.3390.3430.346D1 5.25BSC 0.207BSC E 7.107.207.300.2800.2830.287E1 3.75BSC 0.148BSC e 0.75BSC 0.030BSC b0.300.350.400.0120.0140.016PACKAGING INFORMATIONISSI®Integrated Silicon Solution, Inc. — — 1-800-379-4774Rev.F 06/18/03Copyright © 2003 Integrated Silicon Solution, Inc. All rights reserved. ISSI reserves the right to make changes to this specification and its products at any timewithout notice. ISSI assumes no liability arising out of the application or use of any information, products or services described herein. Customers are advised to obtain the latest version of this device specification before relying on any published information and before placing orders for products.Plastic TSOPPackage Code: T (Type II)。

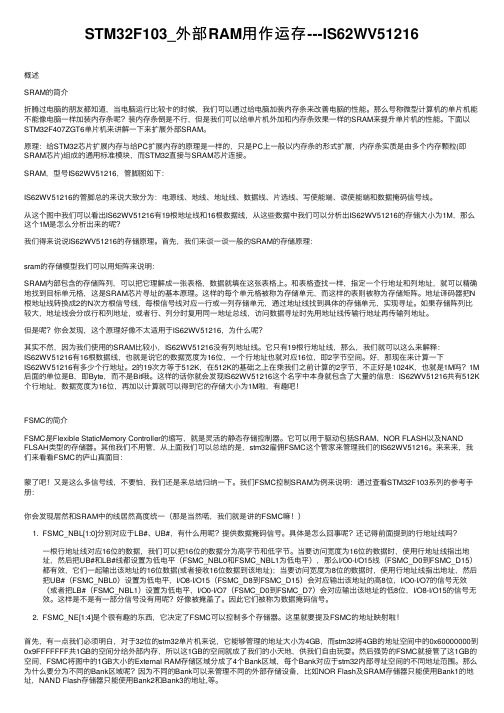

STM32F103_外部RAM用作运存---IS62WV51216

STM32F103_外部RAM⽤作运存---IS62WV51216概述SRAM的简介折腾过电脑的朋友都知道,当电脑运⾏⽐较卡的时候,我们可以通过给电脑加装内存条来改善电脑的性能。

那么号称微型计算机的单⽚机能不能像电脑⼀样加装内存条呢?装内存条倒是不⾏,但是我们可以给单⽚机外加和内存条效果⼀样的SRAM来提升单⽚机的性能。

下⾯以STM32F407ZGT6单⽚机来讲解⼀下来扩展外部SRAM。

原理:给STM32芯⽚扩展内存与给PC扩展内存的原理是⼀样的,只是PC上⼀般以内存条的形式扩展,内存条实质是由多个内存颗粒(即SRAM芯⽚)组成的通⽤标准模块,⽽STM32直接与SRAM芯⽚连接。

SRAM,型号IS62WV51216,管脚图如下:IS62WV51216的管脚总的来说⼤致分为:电源线、地线、地址线、数据线、⽚选线、写使能端、读使能端和数据掩码信号线。

从这个图中我们可以看出IS62WV51216有19根地址线和16根数据线,从这些数据中我们可以分析出IS62WV51216的存储⼤⼩为1M,那么这个1M是怎么分析出来的呢?我们得来说说IS62WV51216的存储原理。

⾸先,我们来谈⼀谈⼀般的SRAM的存储原理:sram的存储模型我们可以⽤矩阵来说明:SRAM内部包含的存储阵列,可以把它理解成⼀张表格,数据就填在这张表格上。

和表格查找⼀样,指定⼀个⾏地址和列地址,就可以精确地找到⽬标单元格,这是SRAM芯⽚寻址的基本原理。

这样的每个单元格被称为存储单元,⽽这样的表则被称为存储矩阵。

地址译码器把N 根地址线转换成2的N次⽅根信号线,每根信号线对应⼀⾏或⼀列存储单元,通过地址线找到具体的存储单元,实现寻址。

如果存储阵列⽐较⼤,地址线会分成⾏和列地址,或者⾏、列分时复⽤同⼀地址总线,访问数据寻址时先⽤地址线传输⾏地址再传输列地址。

但是呢?你会发现,这个原理好像不太适⽤于IS62WV51216,为什么呢?其实不然,因为我们使⽤的SRAM⽐较⼩,IS62WV51216没有列地址线。

频谱仪

手持频谱仪用户手册与操作指南

Spectrum Master

Байду номын сангаас

MS2721 B MS2723 B MS2724 B

9 kHz ~ 7.1 GHz 9 kHz ~ 13 GHz 9 kHz ~ 20 GHz

MS2721B, MS2723B, MS2724B Spectrum Master 手持式频谱仪 用户手册与操作指南

衰 减 器 功 能 ...................................................................................................4-2 前 置 放 大 器 的 操 作 ......................................................................................4-2 第5章 现场测试(单键智能测试) .....................................................................5-1 本章内容介绍 .................................................................................................5-1 占用带宽测量(OBW) ................................................................................5-1 信道功率测量(Channel Power).................................................................5-2 CDMA信 道 功 率 ...........................................................................................5-3 CDMA信 道 功 率 测 量 ..................................................................................5-3 GSM信 道 功 率 测 量 ......................................................................................5-4 临 道 功 率 比 (ACPR) ...............................................................................5-5 临 道 功 率 比 测 量 ...........................................................................................5-5 GSM临 道 功 率 比 测 量 .................................................................................5-6 带 外 杂 散 辐 射 测 量 ......................................................................................5-7 带 内/信 道 外 测 量 .........................................................................................5-8 带 内 杂 散 的 测 量 ...........................................................................................5-8 场 强 测 量 ......................................................................................................5-10 AM/FM/SSB解 调 .......................................................................................5-11 C/I( 载 干 比 ) 测 量 ...................................................................................5-11 第6章 干扰分析测量 .............................................................................................6-1 本章内容介绍 .................................................................................................6-1 Measurements(测量)菜单 ..........................................................................6-2 Spectrum(频谱)菜单 ..................................................................................6-3 Spectrogram( 三 维 频 谱 图 ) 菜 单 ...........................................................6-4 Signal Strength( 信 号 强 度 ) 菜 单 ..........................................................6-5 RSSI( 接 收 信 号 强 度 指 示 ) 菜 单 ...........................................................6-7 Marker(光标)菜单 ..................................................................................6-8 Spectrogram( 三 维 频 谱 图 ) 测 量 步 骤 ................................................6-10 Signal Strength( 信 号 强 度 ) 测 量 步 骤 ................................................6-12 RSSI( 接 收 信 号 强 度 指 示 ) 测 量 步 骤 .................................................6-13 第7章 信道扫描测量 .............................................................................................7-1 本章内容介绍 .................................................................................................7-1 Scanner(扫描)菜单.....................................................................................7-2 幅度(Amplitude)菜单 ................................................................................7-4 用户设置(Custom Setup)菜单...................................................................7-4 测量(Measurements)菜单 ..........................................................................7-5 测量步骤示例 .................................................................................................7-7 用户设置步骤 .................................................................................................7-8 第8章 跟踪信号源 .................................................................................................8-1 本章内容介绍 .................................................................................................8-1 菜单结构 .........................................................................................................8-1

SW6201规格书SW6201中文资料

SW6201的端子定义

引脚定义

详细列出SW6201设备每个引脚的名称和 功能,包括电源引脚、信号输入输出引脚 、控制引脚等。

参数说明

为每个引脚提供详细的参数说明,包括电 压等级、电流承受能力、最大工作频率等 。

典型连接

提供SW6201的典型连接示意图,展示如 何连接电源、输入信号、输出信号、控制 信号等。

输入信号接收 1

SW6201接收来自外部的输入信号

内部处理 2

信号经过内部处理电路的转换和放大

输出信号生成 3

产生最终的输出信号,传递给其他设备

SW6201内部包含一系列复杂的电路,例如放大器、滤波器和逻辑门等,这些电路共同作用,实现信号的接收、处理和输出。

SW6201的主要应用领域

工业自动化

SW6201在工业自动化中扮演着重要角色,可用于控制和监测各 种机器设备。

系统集成

将SW6201集成到项目系统中,进行系统联调,确保系统正常运行。

SW6201的性能测试方法

静态测试

SW6201的静态测试主要包括参数测量 ,如静态电流,静态电压,以及输入 输出特性曲线等,可以通过示波器、 万用表等仪器进行测量。

动态测试

动态测试主要是指测试SW6201在不同 负载情况下,其输出信号的变化情况 ,包括频率响应、失真度等参数测试 ,需要使用专业的测试仪器进行测量 。

SW6201的推荐开发步骤

项目需求分析

仔细分析项目需求,确定SW6201的应用场景和功能需求,确保选择合适的参数配置。

硬件电路设计

根据项目需求,设计合适的硬件电路,选择合适的元器件,确保电路稳定可靠。

软件开发

开发与SW6201接口的软件程序,并进行调试,确保程序运行稳定,功能完整。

IS620PS1R6I-DDR说明书

IS620PS1R6I-DDR说明书IS620PS1R6I-DDR是一个在ISO/IEC802.3标准下的电子数据交换系统,是一个集成在控制器中的数据处理系统,它包含了一个以太网和交换机的网络端口。

它提供了一个高质量(标准为8 bit)、低成本(与传统标准一致)、高质量的通信能力。

它使用安全可靠,快速传输数据和信息的以太网端口,与服务器相连并可在PC机上远程控制。

它能够对网络中不同的电子设备进行访问,而且还可以与服务器互联以获取更多实时信息和更大的带宽。