Programmable cells Interfacing natural and engineered gene networks

高性能CMOS数字电路芯片说明书

Features Array•Full Range of Matrices with up to 480K Gates•0.5 µm Drawn CMOS, 3 Metal Layers, Sea of Gates•RAM and DPRAM Compilers•Library Optimized for Synthesis, Floor Plan and Automatic Test Generation (ATG)• 3 and 5 Volts Operation; Single or Dual Supply Mode•High Speed Performances:–450 ps Max NAND2 Propagation Delay at 4.5V, 720 ps at 2.7V and FO = 5–Min 610 MHz Toggle Frequency at 4.5V, 320 MHz at 2.7V•Programmable PLL Available upon Request•High System Frequency Skew Control through Clock Tree Synthesis Software•Low Power Consumption:–1.96 µW/Gate/MHz at 5V–0.6 µW/Gate/MHz at 3V•Integrated Power On Reset•Matrices with a Max of 484 Fully Programmable Pads•Standard 3, 6, 12 and 24 mA I/Os•Versatile I/O Cell: Input, Output, I/O, Supply, Oscillator•CMOS/TTL/PCI Interface•ESD (2 kV) and Latch-up Protected I/O•High Noise and EMC Immunity:–I/O with Slew Rate Control–Internal Decoupling–Signal Filtering between Periphery and Core–Application Dependent Supply Routing and Several Independant Supply Sources •Wide Selection of MQFPs and MCGA Packages up to 472 Pins•Delivery in Die Form with 94.6 µm Pad Pitch•Advanced CAD Support: Floor Plan, Proprietary Delay Models, Timing Driven Layout, Power Management•Cadence®, Mentor®, Vital® and Synopsys® Reference Platforms•EDIF and VHDL Reference Formats•Available in Military and Space Quality Grades (SCC, MIL-PRF-38535)•No Single Event Latch-up below an LET threshold of 80MeV/mg/cm2•Tested up to a Total Dose of 60 Krad (Si) according to MIL STD 883 Method 1019•QML Q and V with SMD 5962-00B02DescriptionThe MG2RT series is a 0.5 micron, array based, CMOS product family. Several arrays up to 480K gates cover most system integration needs. The MG2RT is manufactured using a 0.5 micron drawn, 3 metal layer CMOS process, called SCMOS 3/2RT.The base cell architecture of the MG2RT series provides high routability of logic with extremely dense compiled memories: RAM and DPRAM. ROM can be generated using synthesis tools.Accurate control of clock distribution can be achieved by PLL hardware and CTS (Clock Tree Synthesis) software. New noise prevention techniques are applied in the array and in the periphery: three or more independent supplies, internal decoupling, customiszation dependent supply routing, noise filtering, skew controlled I/Os, low swing differential I/Os, all contribute to improve the noise immunity and reduce the emission level.The MG2RT is supported by an advanced software environment based on industry standards linking proprietary and commercial tools. Verilog, Modelsym and Design Compiler are the reference front-end tools. Floor planning associated with timing-driven layout provides a short back-end cycle.24115L–AERO–06/05MG2RTThe MG2RT library allows straight forward migration from the MG1RT and MG1 Sea of Gates.A netlist based on this library can be simulated as either MG2RT or MG2RTP. It can also be sim-ulated as MG2 provided there are no SEU hardened cells.Note:Not available for new designs.LibrariesThe MG2RT cell library has been designed to take full advantage of the features offered by both logic and test synthesis tools.Design testability is assured by the full support of SCAN, JTAG (IEEE 1149) and BIST methodologies.More complex macro functions are available in VHDL, such as Two-wire Interface (TWI), UART,Timer.Block GeneratorsBlock generators are used to create a customer specific simulation model and metallisation pat-tern for regular functions like RAM and DPRAM. The basic cell architecture allows one bit per cell for RAM and DPRAM. The main characteristics of these generators are summarised below.Table 1. List of Available MG2RT MatricesType Total Gates Typical UsableGatesTotal PadsMaximum Programmable I/OMG2044E (1)4461631200173150MG2091E 9146464000237214MG2194E (1)193800135600333310MG2265E 264375185000385362MG2360E (1)361680253100445422MG2480E481143336800507484Function Maximum Size (bits)Bits/WordTypical Characteristics (16 Kbits) at 5VAccess Time (ns)Used CellsRAM 32K 1-368.620K DPRAM32K1-369.223K34115L–AERO–06/05MG2RTI/O Buffer InterfacingI/O Flexibility All I/O buffers may be configured as input, output, bi-directional, oscillator or supply. A level translator is located close to each buffer.InputsInput buffers with CMOS or TTL thresholds are non-inverting and feature versions with and with-out hysteresis. The CMOS and TTL input buffers may incorporate pull-up or pull down terminators. For special purposes, a buffer allowing direct input to the matrix core is available. OutputsSeveral kinds of CMOS and TTL output drivers are offered: fast buffers with 3, 6, 12 and 24 mA drive at 5V, low noise buffers with 12 mA drive at 5V.Clock Generation and PLLClock GenerationAtmel offers 6 different types of oscillators: 4 high frequency crystal oscillators and 2 RC oscilla-tors. For all devices, the mark-space ratio is better than 40/60 and the start-up time less than 10ms.PLLContact factory.Oscillators Frequency (MHz)Typical Consumption (mA)Max 5V Max 3V5V 3V Xtal 7M 127 1.20.4Xtal 20M 2817 2.50.8Xtal 50M 704072Xtal 100M 13075165RC 10M 101021RC 32M323231.544115L–AERO–06/05MG2RTPower Supply and Noise ProtectionThe speed and density of the SCMOS3/2RT technology cause large switching current spikes for example when: •either 16 high current output buffers switch simultaneously,•or 10% of the 480,000 gates are switching within a window of 1 ns.Sharp edges and high currents cause some parisitic elements in the packaging to become sig-nificant. In this frequency range, the package inductance and series resistance should be taken into account. It is known that an inductor slows down the settling time of the current and causes voltage drops on the power supply lines. These drops can affect the behavior of the circuit itself or disturb the external application (ground bounce).In order to improve the noise immunity of the MG core matrix, several mechanisms have been implemented inside the MG arrays. Two kinds of protection have been added: one to limit the I/O buffer switching noise and the other to protect the I/O buffers against the switching noise coming from the matrix.I/O Buffers Switching ProtectionThree features are implemented to limit the noise generated by the switching current: •The power supplies of the input and output buffers are separated.•The rise and fall times of the output buffers can be controlled by an internal regulator. •A design rule concerning the number of buffers connected on the same power supply line has been imposed.Matrix Switching Current Protection This noise disturbance is caused by a large number of gates switching simultaneously. To allow this without impacting the functionality of the circuit, three new features have been added:•Decoupling capacitors are integrated directly on the silicon to reduce the power supply drop.•A power supply network has been implemented in the matrix. This solution reduces the number of parasitic elements such as inductance and resistance and constitutes an artificial VDD and Ground plane. One mesh of the network supplies approximately 150 cells. •A low pass filter has been added between the matrix and the input to the output buffer. This limits the transmission of the noise coming from the ground or the VDD supply of the matrix to the external world via the output buffers.54115L–AERO–06/05MG2RTPackagingAtmel offers a wide range of packaging options which are listed below:Note: 1.Contact Atmel local design centers to check the availability of the matrix/package combination.Package Type (1)Pinsmin/max Lead Spacing(mils)MQFP100132196256352252525202064115L–AERO–06/05MG2RTDesign Flows and ToolsDesign Flows and Modes A generic design flow for an MG2RT array is illustrated below.A top down design methodology is proposed which starts with high level system description andis refined in successive design steps. At each step, structural verification is performed whichincludes the following tasks: •Gate level logic simulation and comparison with high level simulation results.•Design and test rules check.•Power consumption analysis.•Timing analysis (only after floor plan).The main design stages are:•System specification, preferably in VHDL form.•Functional description at RTL level.•Logic synthesis.•Floor planning and bonding diagram generation.•Test/Scan insertion, ATG and/or fault simulation.•Physical cell placement, JTAG insertion and clock tree synthesis.•Routing.To meet the various requirements of designers, several interface levels between the customer and Atmel are possible.For each of the possible design modes a review meeting is required for data transfer from the user to Atmel. In all cases the final routing and verifications are performed by Atmel.The design acceptance is formalized by a design review which authorizes Atmel to proceed with sample manufacturing.74115L–AERO–06/05MG2RTFigure 1. MG2RT Design FlowGate Level System SpecificationsRTL SimulationLogic synthesisFloor Plan Bonding diagramScan insertionATG and Fault SimulationJTAG insertion Clock Tree SynthesisRouting + ExtractBackannotated SimulationSign-off Samples Manufacturing and TestPlacementSimulation84115L–AERO–06/05MG2RTDesign Tool and Design Kits (DK)The basic content of a design kit is described in the table below.The interface formats to and from Atmel rely on IEEE or industry standard: •VHDL for functional descriptions •VHDL or EDIF for netlists•Tabular, log or .VCD for simulation results •SDF (VITAL format) and SPF for back annotation •LEF and DEF for physical floor plan informationThe design kits supported for several commercial tools are listed below.Design Kit Support•Cadence/Verilog (RTL and gate), Logic Design Planner•Mentor/Modelsim (RTL and gate), Velocity, BSD Architect, Flex Test •Synopsys, Design Compiler, PrimeTime •VitalTable 2. Design Kit DescriptionDesign Tool or library Atmel Software Name Third Party ToolsDesign manual and libraries (1)Synthesis library(1)Gate level simulation library (1)Design rules analyser STAR Power consumption analyser COMETFloor plan library (1)Timing analyser library (1)Package and bonding software PIMScan path and JTAG insertion (1)ATG and fault simulation library(1)Note: 1.Refer to “Design kits cross reference tables” ATD-TS-WF-R018194115L–AERO–06/05MG2RTElectrical CharacteristicsAbsolute Maximum RatingsDC CharacteristicsAmbient temperature under bias (TA)Military......................................................-55 to +125°C Junction temperature....................................TJ < 175°C Storage temperature.................................-65 to +150°C TTL/CMOS:Supply voltage VDD...................................-0.5V to +7V I/O voltage......................................-0.5V to VDD + 0.5VNote:Stresses above those listed may cause permanent damage to the device. Exposure to absolute maxi-mum rating conditions for extended period may affect device reliability.Table 3. DC Characteristics - Specified at VDD = +5V ± 10%SymbolParameterMinTypMax UnitConditionsVILInput LOW voltage (3)CMOS input TTL input001.50.8VVIHInput HIGH voltage (3)CMOS input TTL input3.52.2VDD VDD V VOL Output LOW voltage 0.4V IOL =24, 12, 6, 3 mA (1)VOHOutput HIGH voltage3.9VIOL =-24, -12, -6, -3 mA (1)VT+Schmitt trigger positive threshold CMOS input TTL input3.61.8VVT-Schmitt trigger negative threshold CMOS input TTL input1.21.0VDelta V CMOS hysteresis 25°C/5V TTL hysteresis 25°C/5V 1.90.6VILInput leakage No pull up/down Pull up Pull down-5-5579-69125+5-120330µA µA µA IOZ3-State Output Leakage current -5+5µAIOSOutput Short circuit currentIOSN IOSP90180270540mABOUT3BOUT6BOUT12BOUT24ICCSB Leakage current per cell 1.010.0nA ICCOPOperating current per cell0.390.58µA/MHz/gateNotes:1.According buffer: Bout24, Bout12, Bout6, Bout3.2.Supplied as a design limit but not guaranteed or tested. No more than one output at a time may be shorted for a maximumduration of 10 seconds.3.Without Schmitt trigger.104115L–AERO–06/05MG2RTTable 4. DC Characteristics - Specified at VDD = +3V ± 0.3VSymbolParameterMinTypMax UnitConditionsVILInput LOW voltage (3)LVCMOS input LVTTL input 000.3 VDD 0.8VVIH Input HIGH voltage (3)LVCMOS input LVTTL input 0.7 VDD 2.0VDD VDDVVOLOutput LOW voltage LVTTL0.4VIOL=12, 6, 3, 1.5 mA (1)VOHOutput high voltage LVTTL2.4VIOH= -8, -4, -2, -1 mA (1)VT+Schmitt trigger positive threshold LVCMOS input LVTTL input2.21.2VVT-Schmitt trigger negative threshold LVCMOS input LVTTL input0.90.8VDelta V CMOS hysteresis 25°C/3V TTL hysteresis 25°C/3V 0.80.2VILInput leakage No pull up/down Pull up Pull down-1-20322442+1-60150µA µA µA IOZ3-State Output Leakage current ±1µAIOSOutput Short circuit currentIOSN IOSP90180270540mABOUT3BOUT6BOUT12BOUT24ICCSB Leakage current per cell 0.65nA ICCOPOperating current per cell0.20.25µA/MHz/gateNotes:1.According buffer: Bout24, Bout12, Bout6, Bout3.2.Supplied as a design limit but not guaranteed or tested. No more than one output at a time may be shorted for a maximumduration of 10 seconds.3.Without Schmitt trigger.114115L–AERO–06/05MG2RTAC CharacteristicsTable 5. AC Characteristics - TJ = 25°C, Process typical (all values in ns)Buffer DescriptionLoad TransitionVDD5V 3V BOUT12Output buffer with 12 mA drive60 pfTplh2.533.91Tphl 2.76 3.64BOUT3Output buffer with 3 mA drive60 pfTplh4.637.22Tphl 4.86 6.36BOUTQLow noise output buffer with 12 mA drive60 pfTplh2.974.48Tphl 4.36 6.24B3STA33-state output buffer with 3 mA drive60 pfTplh4.737.35Tphl 4.89 6.44B3STA123-state output buffer with 12 mA drive60 pfTplh2.644.07Tphl 2.79 3.72B3STAQLow noise 3-state output buffer with 12 mA drive60 pfTplh3.014.61Tphl4.426.34124115L–AERO–06/05MG2RTTable 6. AC Characteristics - TJ = 25°C, Process typical (all values in ns)Cell Description Load TransitionVDD5V 3V BINCMOSCMOS input buffer15 fanTplh0.771.14Tphl 0.75 1.06BINTTLTTL input buffer16 fanTplh0.91.31Tphl 0.7 1.1INVInverter12 fanTplh0.520.8Tphl 0.420.53NAND22 - input NAND12 fanTplh0.731.11Tphl 0.660.9FDFFD flip-flop, Clk to Q8 fanTplh 0.8 1.21Tphl0.681.02Ts 0.330.44Th -0.12-0.24BUF4XHigh drive internal buffer51 fanTplh0.761.1Tphl 0.580.81NOR22-Input NOR gate8 fanTplh0.651.08Tphl 0.370.45OAI224-input OR AND INVERT gate8 fanTplh0.681.14Tphl 0.420.54 OSFFD flip-flop with scan input, Clk to Q8 fanTplh 0.83 1.23Tphl1.001.38Ts 0.560.8Th-0.34-0.64115L–AERO–06/05© Atmel Corporation 2005. All rights reserved. Atmel ®, logo and combinations thereof, are registered trademarks, and Everywhere You Are ®are the trademarks of Atmel Corporation or its subsidiaries. Other terms and product names may be trademarks of others.Disclaimer: The information in this document is provided in connection with Atmel products. No license, express or implied, by estoppel or otherwise,to any intellectual property right is granted by this document or in connection with the sale of Atmel products. EXCEPT AS SET FORTH IN ATMEL’S TERMS AND CONDI-TIONS OF SALE LOCATED ON ATMEL’S WEB SITE, ATMEL ASSUMES NO LIABILITY WHATSOEVER AND DISCLAIMS ANY EXPRESS, IMPLIED OR STATUTORY WARRANTY RELATING TO ITS PRODUCTS INCLUDING, BUT NOT LIMITED TO, THE IMPLIED WARRANTY OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, OR NON-INFRINGEMENT. IN NO EVENT SHALL ATMEL BE LIABLE FOR ANY DIRECT, INDIRECT, CONSEQUENTIAL, PUNITIVE, SPECIAL OR INCIDEN-TAL DAMAGES (INCLUDING, WITHOUT LIMITATION, DAMAGES FOR LOSS OF PROFITS, BUSINESS INTERRUPTION, OR LOSS OF INFORMATION) ARISING OUT OF THE USE OR INABILITY TO USE THIS DOCUMENT, EVEN IF ATMEL HAS BEEN ADVISED OF THE POSSIBILITY OF SUCH DAMAGES. Atmel makes no representations or warranties with respect to the accuracy or completeness of the contents of this document and reserves the right to make changes to specifications and product descriptions at any time without notice. Atmel does not make any commitment to update the information contained herein. Unless specifically provided otherwise, Atmel products are not suitable for, and shall not be used in, automotive applications. Atmel’s products are not intended, authorized, or warranted for use as components in applications intended to support or sustain life.Atmel CorporationAtmel Operations2325 Orchard Parkway San Jose, CA 95131, USA Tel: 1(408) 441-0311Fax: 1(408) 487-2600Regional HeadquartersEuropeAtmel SarlRoute des Arsenaux 41Case Postale 80CH-1705 Fribourg SwitzerlandTel: (41) 26-426-5555Fax: (41) 26-426-5500AsiaRoom 1219Chinachem Golden Plaza 77 Mody Road Tsimshatsui East Kowloon Hong KongTel: (852) 2721-9778Fax: (852) 2722-1369Japan9F, Tonetsu Shinkawa Bldg.1-24-8 ShinkawaChuo-ku, Tokyo 104-0033JapanTel: (81) 3-3523-3551Fax: (81) 3-3523-7581Memory2325 Orchard Parkway San Jose, CA 95131, USA Tel: 1(408) 441-0311Fax: 1(408) 436-4314Microcontrollers2325 Orchard Parkway San Jose, CA 95131, USA Tel: 1(408) 441-0311Fax: 1(408) 436-4314La Chantrerie BP 7060244306 Nantes Cedex 3, France Tel: (33) 2-40-18-18-18Fax: (33) 2-40-18-19-60ASIC/ASSP/Smart CardsZone Industrielle13106 Rousset Cedex, France Tel: (33) 4-42-53-60-00Fax: (33) 4-42-53-60-011150 East Cheyenne Mtn. Blvd.Colorado Springs, CO 80906, USA Tel: 1(719) 576-3300Fax: 1(719) 540-1759Scottish Enterprise Technology Park Maxwell BuildingEast Kilbride G75 0QR, Scotland Tel: (44) 1355-803-000Fax: (44) 1355-242-743RF/AutomotiveTheresienstrasse 2Postfach 353574025 Heilbronn, Germany Tel: (49) 71-31-67-0Fax: (49) 71-31-67-23401150 East Cheyenne Mtn. Blvd.Colorado Springs, CO 80906, USA Tel: 1(719) 576-3300Fax: 1(719) 540-1759Biometrics/Imaging/Hi-Rel MPU/High Speed Converters/RF DatacomAvenue de Rochepleine BP 12338521 Saint-Egreve Cedex, France Tel: (33) 4-76-58-30-00Fax: (33) 4-76-58-34-80Literature Requests/literature。

电子信息工程专业英语专业术语速查表5.0

AA/D abbr. Analog-to-Digital 模数转换16, 17AC abbr. alternating current 交流电5AC analysis 交流分析5 accumulator [ə'kjuːmjʊleɪtə] n.累加器17 accuracy [ˈækjʊrəsi] n.精度6 acquisition time 采集时间16 activate [ˈæktɪveɪt] vt. 激活3active [ˈæktɪv] adj.有源的4, 18 actuator [ˈæktjʊeɪtə] n.激励器4ADC abbr. analog-to-digital converter 模数转换器6, 18 addition [əˈdɪʃən] n. 加法3 address generator 地址产生器17 address latch 地址锁存器3 address pointer 地址指针2 addressing mode 寻址模式26 ADSL abbr. Asymmetrical Digital Subscriber Loop 非对称数字用户线21AFG abbr. Arbitrary Function Generator 任意函数发生器28 algorithm ['ælgərɪðəm] n. 算法27 aliasing ['eɪlɪəsiŋ] n.混叠16ALU abbr. Arithmetic Logic Unit 算术逻辑单元3 amplifier [ˈæmplɪˌfaɪə] n. 放大器4 analog interfacing模拟接口(技术)6 angular [ˈæŋɡjələ] adj.角度的5 angular frequency 角频率5 annotation [ænə'teɪʃən] n.标注15 antenna [ænˈtenə] n.天线10anti-aliasing filter 抗混叠滤波器6, 16 array [ə'reɪ] n.数组26ASIC abbr. Application-Specific Integrated Circuit 专用集成电路13, 14, 15, 16, 25专用集成电路assembler [əˈsemblə] n. 汇编器3 assembly language 汇编语言3 ASSP abbr. Application-Specific Standard Part 专用标准部件14, 25 asynchronous [ə'sɪŋkrənəs] adj.异步的13 attenuator [ə'tenjʊeɪtə] n. 衰减器29 audio [ˈɔːdiəʊ] adj.音频的6 automatic variable 自动变量26AWG abbr. Arbitrary Waveform Generator 任意波形发生器28axis [ˈæksɪs] n. 坐标轴5Bbackplane [ˈbækˌpleɪn] n. 背板;底板9 backward compatible 向下兼容21 bandwidth ['bændˌwɪdθ] n.带宽6第 1 页共15 页bar graph 柱图22base band 基带6base station 基站10, 21battery [ˈbætəri] n. 电池7, 12baud [bɔːd] n.波特21Bessel filter 贝塞耳滤波器19biased [ˈbaɪəst] adj.加偏压的7bill of materials 材料单25binary number 二进制数3BIOS [ˈbaɪɒs] abbr. Basic Input Output System 基本输入输出系统3bipolar [baɪˈpəʊlə] adj.双极性的2bit pattern 位模式3bit vector 位向量26block diagram 方框图6block diagram 框图19BNC abbr. bayonet Neill–Concelman BNC连接器9Bode plot 伯德图5bond [bɒnd] n.接头9boot sector 引导扇区3branch instruction 分支指令26缓存器;;缓存区3, 10 buffer [ˈbʌfə] n. 缓存器bunching ['bʌntʃiŋ] n.聚束19bus interface 总线接口16Ccable ['keɪbl] n.电缆12cache [kæʃ] n.高速缓存2CAD abbr. Computer Aided Design 计算机辅助设计13, 18calculation-intensive algorithm 运算密集型算法17CAM [kæm] abbr. Content Addressable Memory 内容寻址存储器2capacitance [kəˈpæsɪtəns] n. 电容(值)5capacitive [kəˈpæsɪtɪv] adj. 容性的9capacitor [kəˈpæsɪtə] n.电容器2, 5capacity [kə'pæsɪtɪ ] n.容量10capture ['kæptʃə] vt. 输入,记录13carrier wave 载波24carry bit 进位位3cascade [kæsˈkeɪd] n.级联5cathode ['kæθəʊd] n. 阴极29CB abbr. Citizen's Band 民用波段10CCD abbr. Charge Coupled Device 电荷耦合器件18, 23CD abbr. Compact Disc 光盘12, 13cellular [ˈseljʊlə] n.使用蜂窝技术的6channel [ˈtʃænəl] n.信道6第 2 页共15 页characteristic frequency 特征频率5 charge pump 电荷泵8 Chebyshev Type 1 filter 契比雪夫I型滤波器18 chip [tʃɪp] n. 芯片1 chip rate 码片速率21 chrominance [ˈkrəʊmɪnəns] n.色度24 circuit [ˈsɜːkɪt] n. 电路1 circuit board 电路板1 circuitry [ˈsɜːkɪtri] n. 电路2, 4, 6 circular [ˈsɜːkjʊlə] adj. 圆形的5 circular buffer 循环缓冲区17 class [klɑːs] n.类26 clock cycle 时钟周期3 clock generator 时钟发生器8 clock rate 时钟速率9 CMOS abbr. complementary metal-oxide-semiconductor 互补金属氧化物半导体2, 9, 12, 23 coding theory 编码理论11 comparator [kəmˈpærətə] n.比较器2, 6 compatibility [kəmˌpætɪ'bɪlɪtɪ] n. 兼容性16 compiler [kəmˈpaɪlə] n.编译器3, 26 complex plane 复平面5 component [kəmˈpəʊnənt] n. 元器件;组件;部件1 concurrent [kən'kʌrənt] adj.并发的15 concurrent process 并发进程26 conductivity [kɒndʌkˈtɪvɪti] n.导电性7 conjugate [ˈkɒndʒʊɡeɪt] adj.共轭的5 converter [kənˈvɜːtə] n. 整流器7 converter resolution 转换器分辨率6 coordinate [kəʊˈɔːdɪnət] n. 坐标5 cordless phone 无绳电话10 counter [ˈkaʊntə] n. 计数器3 coupling [ˈkʌplɪŋ] n.耦合9 CPU abbr. central processing unit中央处理器1, 12程序))25, 27交叉编译器((程序cross-compiler 交叉编译器crosstalk [ˈkrɒsˌtɔːk] n.串扰9 crowbar [ˈkrəʊˌbɑː] n. 短路器7 CRT abbr. Cathode Ray Tube 阴极射线管29 cryptography [krɪp'tɒgrəfɪ] n. 密码学14 crystal [ˈkrɪstəl] n.晶体8, 18 CT abbr. Computed Tomography 计算机层析成像22 current source 电流源4 cutoff [ˈkʌtɒf] n.截止7 cutoff frequency 截止频率18第 3 页共15 页DD/A abbr. Digital-to-Analog 数模转换16, 17 DAC abbr. Digital-to-Analog Converter 数模转换器18 damping [ˈdæmpɪŋ] n.幅度衰减5 data acquisition 数据采集30 data compression 数据压缩18 data converter 数据转换器6 data processing 数据处理14 data rate 数据率19 data sheet 数据手册4, 6 dB abbr. decibel [ˈdesɪˌbel] 分贝5 DC abbr. direct current 直流电5 DCT abbr. Discrete Cosine Transform 离散余弦变换22 debug [diː'bʌg] vt.调试28 debugger [diː'bʌgə] n. 调试程序27 decimation [desɪ'meɪʃən] n.抽取6 declaration [deklə'reɪʃən] n.声明15 decoder [diːˈkəʊdə] n. 译码器3 delta modulation 增量调制(∆调制)11 denominator [dɪˈnɒmɪˌneɪtə] n.分母5 density [ˈdensəti] n. 密度2 design flow 设计流程13 design specification 设计规格28 desired signal 期望信号28 detector [dɪˈtektə] n.检波器8 deviation [ˌdiːviˈeɪʃən] n. 偏差8 device driver 设备驱动程序27 DG abbr. Data Generator 数据发生器28 dial tone 拨号音10 differentiation [ˌdɪfərenʃiˈeɪʃən] n. 微分4 digital [ˈdɪdʒɪtəl] adj.数字的1 digital cellular phone 数字蜂窝电话6 digital circuit 数字电路2 digital filtering 数字滤波6 digitization [ˌdɪdʒɪtɪ'zeʃən] n. 数字化16 diode [ˈdaɪəʊd] n. 二极管7 discrete [dɪ'skriːt] adj.离散的,分立的1, 13 discrete component 分立元件3 disk drive head 磁盘驱动器磁头18 dissipate [ˈdɪsɪˌpeɪt] vi.耗散7 distortion [dɪ'stɔːʃən] n.畸变28 division [dɪˈvɪʒən] n. 除法3 DMM abbr. digital multimeter 数字多用表28第 4 页共15 页Dolby Stereo 杜比立体声19 don't care 无关项15 downstream ['daʊn'striːm] n.下行比特流11 DRAM abbr. Dynamic Random Access Memory 动态随机存取存储器2 drive [draɪv] n.驱动器2, 12 DSP abbr. Digital Signal Processing 数字信号处理14, 18 DSP abbr. Digital Signal Processor 数字信号处理器16, 17 DSSS abbr. Direct Sequence Spread Spectrum 直序扩频21 duty cycle 占空比7, 8 DVD abbr. Digital Video Disk 数字视盘12 DVI abbr. Digital Video Interactive 交互式数字视频系统12 dynamic range 动态范围16 E合逻辑2, 9 ECL abbr. emitter coupled logic 射极耦射极耦合逻辑EDA abbr. Electronic Design Automation 电子设计自动化13, 15 edge detection 边缘检测22 EEPROM [ˈi:prɒm] abbr. Electrically Erasable Programmable ROM 电可擦除可编程只读存储器2 electrical power 电能7 electricity [ˌilekˈtrɪsəti] n. 电1 electron beam 电子束29 electronics [ˌilekˈtrɒnɪks] n. 电子学, 电子电路1, 7 embedded system 嵌入式系统13 emulation [ˌemjʊ'leɪʃən] n. 仿真16 encoding [ɪn'kəʊdɪŋ] n.编码19 end office 端局10 end product 最终产品16 erasable [ɪˈreɪzəbl] adj.可擦除的2 ethernet[ˈiːθənet] n. 以太网9, 12 even field 偶数场24 execute [ˈeksɪˌkjuːt] vt. 执行3 execution time 执行时间27 exponent [ɪk'spəʊnənt] n.指数17 exponential [ˌekspəˈnenʃəl] adj. 指数的5 expression [ɪk'spreʃən] n. 表达式26 external compensation 外部补偿4 FFCC abbr. Federal Communications Commission 联邦通信委员会10 FDM abbr. Frequency-division multiplexing 频分复用11 feature size 特征尺寸19 feedback [ˈfiːdbæk] n.反馈4 feedback component 反馈元件4 ferroelectric [ˌferəʊɪˈlektrɪk] adj.铁电的2 FFT abbr. Fast Fourier Transform 快速傅里叶变换6, 18第 5 页共15 页field [fiːld] n. 字段26 field operation 现场运行4 filter ['fɪltə] n.滤波器6 filtering [ˈfɪltərɪŋ] n.滤波9, 18 flash memory 闪存23 flip flop 触发器2 floating point processor 浮点处理器3 flux [flʌks] n.通量7 flyback [ˈflaɪbæk] n.回扫7 foundry ['faʊndri] n. 晶圆代工厂16 FPGA abbr. Field Programmable Gate Array 现场可编程门阵列13, 15, 16 frame grabber 帧采集器24 frequency conflict 频率冲突11 frequency masking 频率掩蔽20 frequency response 频率响应9 frequency reuse 频率复用10 frequency synthesizer 频率合成器8full range 满量程28 full scale 满幅度;满量程6full scale range 满量程范围16 functional accelerator 性能加速器16 fundamental frequency 基频29Ggain drift 增益漂移4 GBW abbr. Gain × Bandwidth 增益带宽积4 global data 全局数据26 GPP abbr. General Purpose Processor 通用处理器16 gray scale level 灰度级22 GSM abbr. Global System for Mobile communications 全球移动通信系统6 guided missile 导弹28 gyro ['dʒaɪrəʊ] n.陀螺仪28 handoff [hændɒf] n. 越区切换21 handset ['hænset] n. 手持设备10 Harvard architecture 哈佛结构17 HDL abbr. Hardware Description Language 硬件描述语言13, 15 HDMI abbr. High-Definition Multimedia Interface 高清晰度多媒体接口12 headroom [ˈhedˌruːm] n.净空,活动空间7 heatsink [ˈhiːt ˈsɪŋk] n.散热片7, 12 high impedance 高阻15 high-powered [ˌhaɪ ˈpaʊəd] adj. 大功率的10 histogram ['hɪstəgræm] n.直方图22 histogram equalization 直方图均衡22 Huffman encoding 哈夫曼编码22第 6 页共15 页IIC abbr. integrated circuit 集成电路1, 4 IDE [aɪd] abbr. Integrated Drive Electronics 集成驱动器电路12 IEEE abbr. Institute of Electrical and Electronic Engineers 电气与电子工程师学会15 image contrast 图像对比度22 image sensor 图像传感器23 imaginary part 虚部5 impedance [ɪmˈpiːdəns] n. 阻抗5, 15, 30 inbound ['ɪnbaʊnd] adj.输入的10 inductance [ɪnˈdʌktəns] n. 电感(值)5 inductive [ɪnˈdʌktɪv] adj.感性的9 inductor [ɪnˈdʌktə] n. 电感器5, 7 infinity [ɪnˈfɪnəti] n.无穷大5in-phase 同相28 input offset voltage 输入偏置电压4 instruction [ɪnˈstrʌkʃən] n. 指令3 instruction decoder 地址译码器3 instrumentation [ˌɪnstrʊmen'teɪʃən] n.仪器28 insulate [ˈɪnsjuleɪt] vt.绝缘1 integrated development tool 集成开发工具27集成;;积分4, 7 integration [ˌɪntəˈɡreɪʃən] n. 集成integrator [ˈɪntɪgreɪtə] n. 积分器5 interconnect [ˌɪntəkəˈnekt] n. 互连9 interface [ˈɪntəˌfeɪs] n. 接口电路2, 4 interference [ɪntə'fɪərəns] n. 干扰10 interpolation [ɪntɜːpəʊ'leɪʃən] n.插值6 interrupt latency 中断等待时间27 interval [ˈɪntəvəl] n. 间歇2IP abbr. Intellectual Property 知识产权25 IP abbr. Internet Protocol 互联网协议21 IP packet IP分组21 ISO abbr. International Organization for Standardization 国际标准化组织26 ISP abbr. in-system programmable 在系统可编程14 ISR abbr. Interrupt Service Routine 中断服务程序27Jjack [dʒæk] n.音频插口12 jitter ['dʒɪtə] n.抖动28 jitters [ˈdʒɪtəz] n. 时钟抖动8 JPEG abbr. Joint Photographic Experts Group 联合图象专家组23 JTAG abbr. Joint Test Action Group 联合测试行动组25Kkernel ['kɜːnəl] n.内核程序27 lagging [ˈlæɡɪŋ] adj.滞后的8第7 页共15 页laptop ['læptɒp] n.膝上型轻便电脑12 laser ['leɪzə] abbr. light amplification by stimulated emission of radiation 激光19 latency ['leɪtənsɪ] n. 反应时间27 LLCD abbr. Liquid Crystal Display 液晶显示器23 lead [liːd] n.引线9 leading [ˈliːdɪŋ] adj.超前的8 leakage [ˈli:kɪdʒ] n.泄露2 learning curve 学习曲线15 licensing agreement 专利使用权转让协定17 linear ramp 线性斜坡5 linear regulator 线性稳压器7 linearity [ˌlɪnɪˈærɪtɪ] n. 线性28 lithographic [ˌlɪθəˈɡræfɪk] adj. 平版印刷的2 load [ləʊd] n. 负载7 load current 负载电流7 loading ['ləʊdɪŋ] n.负载30 log [lɒɡ] abbr. logarithm [ˈlɒɡərɪðəm] 对数4 logic [ˈlɒdʒɪk] n. 逻辑1 logic analyzer 逻辑分析仪28 logical channel 逻辑通道21 look-up table 查找表2, 19 loop filter 环路滤波器8 looping scheme 循环机制17 loss [lɒs] n. 损耗7 LP abbr. Long Playing 密纹唱片13 LSI abbr. large-scale integration 大规模集成1 luminance ['luːmɪnəns] n.亮度24 MMAC abbr. Multiplication and Accumulation 乘法累加运算18 machine instruction 机器指令3 magnetic [mæɡˈnetɪk] adj.有磁性的2, 7 magnitude spectrum 幅度谱22 mantissa [mæn'tɪsə ] n.尾数17 m-commerce 移动商务21 memory [ˈmeməri] n.存储器2 memory location 存储器位置3 metallization [ˌmetəlaɪ'zeɪʃən] n.金属化13 microcell [ˈmaɪkrəʊˌsel] n.微蜂窝10 microcontroller [maɪkrəkən'trəʊlə] n.微控器2 micron [ˈmaɪkrɒn] n. 微米;10-6米3 microphone ['maɪkrəfəʊn] n.扩音器18 microprocessor [maɪkrəʊ'prəʊsesə] n. 微处理器1, 3第8 页共15 页miniaturization [ˈmɪnɪətʃəˌraɪˈzeɪʃən] n. 缩微化1 MIPS [mɪps] abbr. Million Instructions Per Second 每秒百万条指令数3, 18 MMX abbr. Multi-Media Extension多媒体增强指令集17 mnemonics [nɪ'mɒnɪks] n. 助记符30 modem ['məʊdem] n.调制解调器12 monotonicity [mɒnətəˈnɪsɪtɪ] n. 单调性28µP abbr. microprocessor 微处理器14 MPEG abbr. Motion Picture Experts Group 运动图象专家组20 MRI abbr. Magnetic Resonance Imaging 核磁共振成像22 MSC abbr. Mobile Switching Center 移动电话交换中心10 MSPS abbr. million samples per second 每秒百万样本数6 MTSO abbr. Mobile Telephone Switching Office 移动电话交换局10 multiframe n.复帧11 multiplexer ['mʌltɪˌpleksə] n.多路复用器28 multiplication [ˌmʌltəplɪˈkeɪʃən] n. 乘法3 multiplier [ˈmʌltɪˌplaɪə] n.乘法器3, 17 Nnetwork operator 网络运营商21 network router 网络路由器2 next state 次态13 noise shaping 噪声整形6 nominal [ˈnɒmɪnəl] adj.标称的8 NRE abbr. nonrecurring engineering 一次性工程14 NTSC abbr. National Television Systems Committee 国家电视系统委员会24 Nyquist theorem 奈奎斯特定理16 Oobject recognition 目标识别22 odd field 奇数场24 one's complement 二进制反码11 op amp abbr. operational amplifier 运算放大器4, 18 opcode [ˈɒpkəʊd] abbr. operation code 操作码3 open loop gain 开环增益4 operand ['ɒpərænd] n.操作数26 operating system 操作系统3 optical [ˈɒptɪkəl] adj.光学的2 order of magnitude 数量级10 OS abbr. Operating System 操作系统12 oscillation [ˌɒsɪˈleɪʃən] n. 振荡4 oscillator [ˈɒsɪˌleɪtə] n.振荡器8 oscilloscope [əˈsɪləˌskəʊp] n.示波器20, 28 OTP abbr. one-time programmable 一次性编程14 outbound ['aʊtbaʊnd] adj.输出的10 outlet ['aʊtlet] n.电源插座12第9 页共15 页overload [ˌəʊvəˈləʊd] n.过载10 overvoltage [ˈəʊvəˈvəʊltɪdʒ] n.过压7Ppackage ['pækɪdʒ] n.封装形式; 程序包4, 15 packet ['pækɪt] n.信息分组21 packet switching 分组交换10 pad [pæd] n.焊盘9 PAL [pæl] abbr. Phase Alternation by Line 逐行倒相24 parallel [ˈpærəlel] adj.并联的8 parallel architecture 并行结构17 parallel resonant 并联谐振8 parallelism ['pærəlelɪzəm] n. 并行度14 passband ['pæsbænd] n.通带5, 18 passive [ˈpæsɪv] adj.无源的4, 7, 18 payload [ˈpeɪˌləʊd] n.有效载荷11 PCB abbr. printed circuit board 印制电路板9, 18 PCM abbr. Pulse Code Modulation 脉冲编码调制11 PCS abbr. Personal Communication Service 个人通信业务11 perceptual coding 知觉编码20 performance specification 性能指标6 peripheral [pə'rɪfərəl] n.外设12 PGA abbr. Programmable Gain Amplifier 可编程增益放大器18 phase spectrum 相位谱22 phone service 电话业务4 piezoelectric [ɪˈlektrɪk] adj.压电的piezoelectric [paɪzəʊɪˈlektrɪk] adj.压电的8, 18 piezoelectric crystal 压电晶体18 pipelining [ˈpaɪpˌlaɪnɪŋ] n. 流水线技术3 pixel ['pɪksəl] n.像素22 PLA abbr. Programmable Logic Array 可编程逻辑阵列13 playback ['pleɪbæk] n.重放19 PLCC abbr. plastic leadless chip carrier 塑料无引线芯片承载封装9 PLD abbr. Programmable Logic Device 可编程逻辑器件13, 14, 15 PLL abbr. phase locked loop 锁相环8 pointer ['pɒɪntə] n.指针26 pole [pəʊl] n. 极点5 pole [pəʊl] n.极点18 POST [pəʊst] abbr. power-on self-test 开机自检12 power [ˈpaʊə] n. 功率1 power consumption 功耗1, 6 power dissipation 功耗16 power loss 功率损耗9 power supply voltage 电源电压4第10 页共15 页power supply 电源12 ppm abbr. parts per million 百万分之一8 predictive encoding 预测编码11 present state 现态13 price/performance ratio 性价比16 probe [prəʊb] n.探头30 processing gain 处理增益6 program call 程序调用26 program counter 程序计数器3, 26 programmable [ˈprəʊɡræməbl] adj.可编程的2 propagate [ˈprɒpəɡeɪt] vi.传播8 propagation delay 传输延迟8, 30 prototype ['prəʊtətaɪp] n. 样机14 PSTN abbr. Public Switched Telephone Network 公共交换电话网10 psychoacoustics [ˌsaɪkəʊə'kuːstɪks] n.心理声学20 PTT abbr. Post Telephone and Telegraph Administration 邮政电话电报管理局10 pulse [pʌls] n.脉冲3 pulse width 脉冲宽度30 QoS abbr. quality-of-service 服务质量21 quality factor 品质因数5 quantization error (noise) 量化误差(噪声)6 quantization level 量化电平16 quartz [kwɒts] n. 石英8 RRAM [ræm] abbr. random-access memory 随机存取存储器3, 12 random noise 随机噪声11 raster ['ræstə] n.光栅29 RC abbr. Reconfigurable Computing 可重配计算14 RC abbr. resistor capacitor 电阻电容5 RCA abbr. Radio Corporation of America 美国无线电公司12 real part 实部5 real time 实时16 rectifier [ˈrektɪfaɪə]n.整流器7 redundancy [rɪ'dʌndənsɪ] n.冗余20 Reed-Solomon coding 里德-索罗蒙编码(RS编码)19 reference voltage 参考电压6 refresh [rɪˈfreʃ] vt.刷新2 register [ˈredʒɪstə] n.寄存器2 regulator [ˈreɡjʊˌleɪtə] n.稳压器7 resistor [rɪˈzɪstə] n. 电阻器6 resolution [rezə'luːʃən] n.分辨率6, 23 resolution function 判决函数26 resonant [ˈrezənənt] adj. 谐振的8第11 页共15 页resonating frequency 谐振频率8 ribbon cable 带状电缆;扁平柔性电缆9 ringing [ˈrɪŋɪŋ] n. 振铃振荡5 ripple ['rɪpl] n.波纹18 RISC abbr. Reduced Instruction-Set Computer 精简指令集计算机25 roll off 滚降18 ROM [rɒm] abbr. read-only memory 只读存储器3 router [ˈruːtə] n. 路由器2 rpm abbr. revolutions per minute 每分钟转数19 RTL abbr. Register Transfer Level 寄存器传输级13 RTOS abbr. Real-Time Operating System 实时操作系统26, 27 run-length encoding 行程编码22Ssample and hold circuit 采样保持电路16 sampling interval 采样间隔16 sampling rate 采样率6 SATA abbr.. Serial Advanced Technology Attachment 串行高级技术附件12 scanning velocity 扫描速度19 scheduler ['ʃedjuːələ] n. 调度程序27 schematic [skiːˈmætɪk] n.原理图7, 13 scientific notation 科学记数法17 SCR abbr. silicon controlled rectifier 可控硅整流器7 SDR abbr. Software-defined Radio 软件无线电14 SECAM ['siːkæm] abbr. SEquential Couleur Avec Memoire 顺序与存储彩色电视系统24 selective [sɪˈlektɪv] adj. 选择性的5 semiconductor [ˌsemɪkənˈdʌktə] n. 半导体1, 7 sequence[ˈsiːkwəns] n. 序列3 sequential [sɪ'kwenʃəl] adj.时序的13 series [ˈsɪəriːz] n. 串联7, 8 series resonant 串联谐振8 shade [ʃeɪd] n.明暗度22 shielding [ˈʃiːldɪŋ] n.屏蔽9 shifter ['ʃɪftə] n. 移位器17 signal conditioning 信号调理4 signal conditioning circuit 信号调理电路18 signal integrity 信号完整性9 signal-to-noise ratio 信噪比16, 20 silicon [ˈsɪlɪkən] n.硅1 simplex ['sɪmpleks] n.单工,单向通信11 simulation [ˌsɪmjʊˈleɪʃən] n.模拟9, 13, 16 sinc correction 抽样函数校正19 sine wave 正弦波6 single-shot 单脉冲29第12 页共15 页skew[skjuː] n.相位偏移8 slew [sluː] n. 摆率8 slope [sləʊp] n. 斜率5 smallest resolvable difference 最小可分辨值17 smoothing ['smu:ðiŋ] n. 平滑(滤波)16 SMS abbr. Short Message Service 短信业务21 SNR abbr. signal to noise ratio 信噪比6 SoC abbr. System-on-Chip 片上系统14 socket [ˈsɒkɪt] n.插座9 soldering [ˈsɒldərɪŋ] n.焊接9 solid state 固态1 sound card 声卡20 source [sɔːs] n. 信号源2 source and load impedances 源阻抗和负载阻抗9 source code 源代码27 spec [spek] abbr. specification 性能指标; 规格8, 12 specification [ˌspesɪfɪˈkeɪʃən] n. 性能指标; 规格4 spectral inversion 频谱反转16 spectral resolution 频率分辨率20 spectrum ['spektrəm] n.频谱6, 16 spread spectrum communication 扩频通信11 SPS abbr. Sample Per Second 每秒样本数18 SRAM abbr. Static Random Access Memory 静态随机存取存储器2 stability [stə'bɪlɪti] n. 稳定性4 stack [stæk] n.堆栈26 startup cost 启动成本27 state machine 状态机14 statement ['steɪtmənt] n.语句15 steady state 稳态8 step function 阶跃函数5 stimuli ['stɪmjʊlaɪ] n.激励源15 stimulus signal 激励信号28 stopband ['stɒpbænd] n.阻带18 strain gage 应力计18 string [strɪŋ] n. 字符串26 structure ['strʌktʃə] n. 结构体26 subassembly [ˌsʌbəˈsembli] n.部件9 subsystem ['sʌbsɪstəm] n.子系统28 subtraction [səbˈtrækʃən] n. 减法3 SUT abbr. System Under Test 被测系统30 switch [swɪtʃ] n. 开关1 switched-capacitor filter 开关电容滤波器5 switching [ˈswɪtʃɪŋ] n.交换,切换7第13 页共15 页synchronization [ˌsɪŋkrənaɪ'zeɪʃən] n.同步11, 21 synchronous ['sɪŋkrənəs] adj.同步的13 synthesis ['sɪnθɪsɪs] n. 综合13 synthesizer [ˈsɪnθəsaɪzə] n.合成器8 system call 系统调用27 TTCXO abbr. temperature compensated crystal oscillator 温度补偿晶体振荡器8 TDM abbr. Time Division Multiplexing 时分复用11 telepresence [ˈtelɪˌprezəns] n. 远程在位21 template ['templeɪt] n. 模板26 temporal masking 暂时掩蔽20 termination [ˌtɜːmɪˈneɪʃən] n.端接9 termination characteristics 端接特性9 test bench 测试台15 test register 测试寄存器3 thermocouple [θɜːməʊˈkʌpəl] n.热电偶18 third party developer 第三方开发商17 thread [θred] n.线程26 TIFF abbr. Tagged Image File Format 标签图像文件格式23 time base 时基30 time constant 时间常数5 time slot 时隙21 time to market 上市时间16 timing [ˈtaɪmɪŋ] n.时序9, 15 timing diagram 时序图30 top-down approach “自顶而下”设计法15 transducer [trænzˈdjuːsə] n. 传感器4, 29 transfer function 传递函数4, 5 transient ['trænzɪənt] n.暂态过程28 transient response 暂态响应5 transistor [trænˈsɪstə] n. 晶体管1 transmission bandwidth 传输带宽20 transmission power 发射功率11 trench capacitor 沟道式电容器2 trigger ['trɪgə] vt.触发13 truth table 真值表26 TTL abbr. transisitor-transisitor logic晶体管晶体管逻辑9 tuning ['tjuːnɪŋ] n.调谐8 type conversion 类型转换15 Uupstream ['ʌpstriːm] n.上行比特流11 USB abbr. Universal Serial Bus 通用串行总线12 UUT abbr. Unit Under Test 被测单元28第14 页共15 页UV abbr. ultraviolet 紫外线2 Vvacuum tube 真空管4 VCO abbr. voltage controlled oscillator 压控振荡器8 vector [ˈvektə] n. 向量5 vertical resolution 垂直分辨率28 VGA abbr. Video Graphics Array 视频图形阵列12 VHS abbr. Video Home System 家用录像系统21 video conference 视频会议21 viewfinder ['vjuːfaɪndə] n. 取景器23 virtual memory 虚拟内存3 VLSI abbr. very large-scale integration 超大规模集成1 vocoder ['vəʊˌkəʊdə ] n.声码器11 volt[vəʊlt] n. 伏特8 voltage [ˈvəʊltɪdʒ] n. 电压;伏特数7 voltage reference 参考电压18 voltage swing 电压摆幅8 volume [ˈvɒljuːm] n. 音量4 Von Neumann architecture 冯·诺依曼结构17 VSWR abbr. voltage standing wave ratio 电压驻波比9 Wwatt [wɒt] n.瓦特10 waveform [ˈweɪvˌfɔːm] n.信号波形7 waveform coding 波形编码20 webcam ['webkæm] n.网络摄像头12 wideband ['waɪd'bænd] adj.宽频带的21 wild card 通配符15 wireless infrastructure 无线基础设施16 XYZzero order hold 零阶保持器16第15 页共15 页。

科技英语外文翻译之英文篇

Microcontroller Based System for theMeasurement of Dielectric Constant inLiquidsCh.V.V.Ramana and K.MalakondaiahDepartment of Instrumentation and University Science InstrumentationCentre,Sri Krishnaevaraya University,Anantapur,IndiaAbstract:A microcontroller based system using 89c51microcontroller for the measurement of dielectric constant in liquids has been designed and developed.It is based on the principle that the change in frequency of an XR–2206function generator,when the liquid forms the dielectric medium of the dielectric cell,is measured with a microcontroller.Atmel’s AT89C51microcontroller is used in the present study.Further,an LCD module is interfaced with the microcontroller in 4-bit mode,which reduces the hardware complexity.Software is developed in C using Ride’s C-cross compiler.The instrument system covers a wide range of dielectric constants for various liquids at various concentrations and at different temperatures.The system is quite successful in the measurement of dielectric constant in liquids with an accuracy of +0.2%.The paper deals with the hardware and software details.Keywords:Dielectric constant,XR-2206Function generator,Frequency measure-ment,C using Ride’s C-cross compiler and 89C51MicrocontrollerINTRODUCTIONThe dielectric constant is a property of major concern in understanding acid-base behaviour in various solvents.A “dielectric”is a substance that can sustain an electric field and acts as an insulator.Some liquids and gases can serve as good dielectric materials,having a special property of storing and dis-sipating electrical energy when subjected to electromagnetic fields.Dry air is Address correspondence to K.Malakondaiah,Department of Instrumentation and University Science Instrumentation Centre,Sri Krishnaevaraya University,Anantapur 515003,India.E-mail:ramana6@Instrumentation Science and Technology ,35:599–608,2007Copyright #Taylor &Francis Group,LLCISSN 1073-9149print /1525-6030onlineDOI:10.1080/10739140701651581599an excellent dielectric.Dielectric measurements are useful for detecting explosives,plastic and metal weapons,drugs,chemical agents,and biological agents.The dielectric constant 1of a liquid is defined as the ratio of the electrical capacitance of a cell when the liquid /solution forms the dielec-tric medium (C s )to the capacitance of the cell when air forms the dielectric medium (C 0)at a given temperature,which is represented by the following equation:1¼ðC s Þ=ðC 0Þð1ÞThe dielectric cell consists of two parallel metallic plates which act as electrodes.The cell acts as a capacitor,while the liquid acts as a dielectric medium.The cell has to be first standardized to measure the dielectric constants of unknown solutions.This is accomplished by considering a pure liquid,such as benzene,as the reference liquid.The dielectric constant of an unknown liquid (1x )can be determined by measuring the capacitance of the cell in air (C 0),the capacitance of cell in the reference liquid (C r ),such as benzene,and the capacitance of the cell in the liquid whose dielectric constant has to be measured (C x ),using the relationship:1x ¼1þ½ðC 0ÀC x Þ=ðC 0ÀC r Þ Âð1r À1Þð2Þwhere 1r is the dielectric constant of the reference liquid.The dielectric constant of a material contains detailed information about the physical and chemical composition and structure.[1]Nowadays,the popularity of microcon-trollers is increasing,due to the fact that they are being used in all types of instruments and in embedded environments.In the present study,the technique utilizes frequency measurement for determination of capacitance using the microcontroller as a tool,while most of the conventional techniques measure the capacitance using bridge methods.PRINCIPLEThe IC XR–2206is a function generator chip.It acts as an RC oscillator.The frequency of oscillations depends on the values of timing resistor R and timing capacitor C.The value of R is kept constant.The dielectric cell acts as a capacitor C that varies with the dielectric medium.Consequently,the frequency of the oscillator also changes.The measurement of the frequency of the oscillator enables one to measure the value of the capacitance of the cell and,thus,the dielectric constant of the medium.In the present study,with suitable interface of the oscillator circuit with a 89C51microcontroller,the frequency of the oscillator is measured.The dielectric constant of the medium is computed using Eq.(2)and is displayed on the LCD.Ch.V.V.Ramana and K.Malakondaiah 600EXPERIMENTALInstrumentationHardware DesignThe block diagram of the microcontroller based system for the measurement of dielectric constant in liquids is shown in Fig.1.A schematic diagram which contains more details is shown in Fig.2.The designed cell is connected between pins 5and 6of THE XR-2206using A BNC connector.The dielectric cell acts as a capacitor C whose capacitance can be measured in terms of frequency.The block A of Fig.2consists of the XR-2206function generator.The output of the RC oscillator (the square wave output (pin 11)is an open collector and,hence,it needs a pull up resistor to V cc .Connecting a 10K resistor between pins 11and V cc ,makes the square wave output to be TTL compatible.In the present study,the XR-2206function generator generally operates at 1MHz frequency.But,the 8051microcontroller can measure the frequency accurately up to a few hundred kilohertz frequency.Hence,the divide counter shown in block B of Fig.2is used.The output of the RC oscillator is given to the clock input of the 74LS90IC [3]decade counter;(which acts as a divide counter (410,412,and a 4-bit binary counter)that divides the RC oscillator output by 10times.The output of the 74LS90is given to the timer 0external input,which is available on the micro-controller (port 3).The microcontroller counts the clock pulses that are given from the 74LS90over an interval of 1sec,which gives the frequency of the oscillator.Block C of Fig.2consists of an LM335[4]which is used as a sensor to measure the temperature of the solution.It also consists ofthe Figure 1.Block diagram of microcontroller based system for the measurement of dielectric constant in liquids.Microcontroller Based System 601hardware that amplifies the signal from the temperature sensor.The output of the temperature unit is given to the analog-to-digital converter (IC 0809)which is shown in block D of Fig.2.The IC 0809is a monolithic CMOS device with an 8-bit analog-to-digital converter,8-channel multiplexer,and microprocessor compatible control logic.[5]The 8-bit A /D converter uses suc-cessive approximation,which can make 100conversions per microsecond at a clock rate 120KHz.The 0809operates 0to 5V input range with single 5V power supply.It is used to convert the analog temperature into digital values.Block E of Fig.2is an AT89C51microcontroller from the Atmel Company.[6]It is a low-power,high-performance CMOS 8-bit microcomputer with 4K bytes of flash programmable and erasable read only memory (PEROM).It has four parallel ports,two 16-bit timers /counters,six interrupt sources,and one programmable serial port,with low powerideal Figure 2.Schematic diagram of microcontroller based system for the measurement of dielectric constant in liquids.(continued )Ch.V.V.Ramana and K.Malakondaiah 602and power down modes;it has the facility of three-program memory lock.The on-chip flash allows the program memory to be reprogrammed in-system or by a conventional nonvolatile memory programmer.All ports are used (port 1is used for LCD display,port 2is for ADC,port 0is used for control signals (that are RS,RW,and EN for LCD display,and SC,ALE and EOC for ADC),port 3(one line is used)is used for frequency measurement.Block F of Fig.2is a two-row 16characters LCD display from ODM;[7]it is interfaced with the microcontroller through port 1to display the measured data and results.The interfacing of the ADC with the microcontroller is shown in Fig.2(a)[continu-ation of Fig.2].Interfacing of the Oscillator with the MicrocontrollerThe frequency of oscillation f 0is determined by the external timing capacitor C (across pins 5and 6)and the timing resistor R (connected to either pin 7or8).The frequency is given by:f 0¼1=R ÃC ð3ÞThe frequency f 0can be adjusted by varying either R or C.In the present study,the timing resistor R is kept constant.Since the timing capacitor C is to be maintained at a minimum of 100pf,a capacitor of value 100pf is connected in parallel with the dielectric cell.TheFigure 2.Continued.Microcontroller Based System 603designed cell is connected between pins5and6of the XR-2206using a BNC connector.The dielectric cell acts as a capacitor C whose capacitance can be measured in terms of frequency using the following equation:C¼1=RÃf0ð4ÞSoftwareSoftware is developed in C using Ride’s(Raisonance Integrated Develop-ment Environment)C-cross compiler to initialize the LCD display and measure the frequency,capacitance,dielectric constant,and temperature. After development,the codes are stored in the program memory(flash EPROM)of the AT89C51microcontroller by using the Atmel programmer and the program is executed.Theflow chart of the program is presentedFig.3.Calibration and MeasurementThe instrument is calibrated and measured following the procedure mentioned below.1.Clean the dielectric cell,dry it,and keep it in a beaker containing air.2.Connect the cell to the circuit as shown in Fig.2.3.Switch on the system and activate the software.4.The system measures and displays the frequency,along with tempera-ture and,in turn,the capacitance of the cell using Eq.(4).Make a note of the values.5.Keep the reference liquid (benzene in the present study)in the cell.6.Repeat the steps from (2)to (4).7.Place the unknown liquid in the cell.8.Repeat the steps from (2)to (4).9.Then,calculate the dielectric constant of the unknown liquid using Eq.(2).10.Note the readings of the dielectric constant of unknown liquids along with temperature.RESULTS AND DISCUSSIONThe performance of the microcontroller-based system for the measurement of dielectric constant in liquids is tested with some liquids at 308C.The samples are selected to cover a wide range.The results are presented in Table 1.The results of the present study are in good agreement with the literature values.The dielectric constant measurements for the binary liquid mixtures(1)benzene þnitrobenzene;(2)nitrobenzene þchlorobenzene;and (3)nitrobenzene þcyclohexanone for various concentrations (mole /L)at 308C were made.The results are graphically represented in Fig.4.Table I.Dielectric constants of pure liquids at 308CSamplePresent work Literature Reference Toulene2.46 2.40[9]Chlorobenzene5.96 5.91[10]5.90[9]Cyclohexanone17.9618.2[9]Acetone20.3020.35[9]Methanol32.5632.6[9]Nitrobenzene 34.8934.81[12]34.80[11]Ch.V.V.Ramana and K.Malakondaiah 606CONCLUSIONThe hardware and software features of a microcontroller based system for the measurement of dielectric constant in liquids are described.The necessary software is developed in C,using Ride’s C-cross compiler.The system is quite successful for the measurement of dielectric constants in liquids with an accuracy of +0.2%.The measurement of dielectric constant,over a wide range,is a special feature of the present study.ACKNOWLEDGMENTSThe authors are thankful to M /S Mittal Enterprises,New Delhi for providing the necessary help to carry out this work.REFERENCES1.Hoppe,W.Bio Physics ;Springer-Verlag:New York,1983.2.XR-2206function generator chip Datasheet,Exar ;the Analog Plus Company,1997.3.IC 74LS90Decade Counter Datasheet ;Motorola,1999.4.Data Acquisition Data Book ;National Semiconductor,1993.5.IC 08098-Bit Analog to Digital Converter Datasheet ;National Semiconductor,1999.6.IC AT89C518-Bit Microcontroller with 4K Bytes Flash Datasheet ;Atmel Company,2000.7.ODM LCD User Manual ;1998.8.Rajendran,A.;Neelamegam,K.An instrument for measurement of dielectric constant of liquids using 8031Microcontroller.Bull.Electrochem.2004,20(2),59–62..This site is for dielectric constanttables.Figure 4.Concentration versus dielectric constant for three binary liquid mixtures.Microcontroller Based System 60710.International Critical Tables of Numerical Data in Physics,Chemistry and Tech-nology ;USA,1933.11.Weissberger,A Ed.,Technique of Organic Chemistry .Vol.III;Interscience:New York,1967.12.Hand Book of Chemistry and Physics ,76th Edn.;The Chemical Rubber Co:Cleveland,Ohio,1995.Received November 17,2006Accepted March 13,2007Manuscript 1605Ch.V.V.Ramana and K.Malakondaiah608。

T8105中文资料

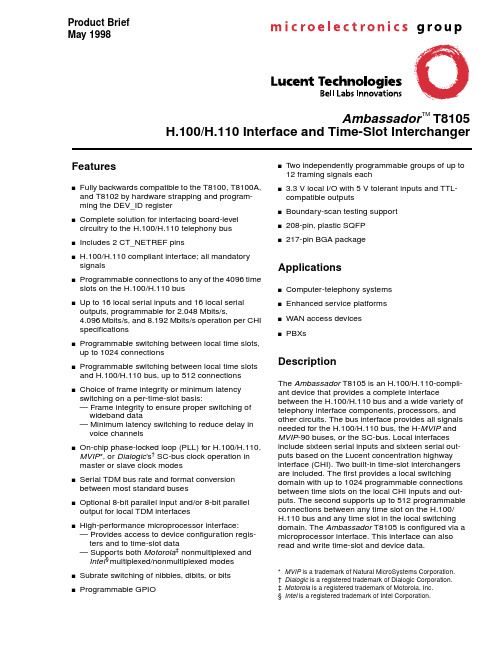

Product BriefMay 1998Ambassador TM T8105H.100/H.110 Interface and Time-Slot InterchangerFeaturess Fully backwards compatible to the T8100, T8100A, and T8102 by hardware strapping and program-ming the DEV_ID registers Complete solution for interfacing board-level circuitry to the H.100/H.110 telephony buss Includes 2 CT_NETREF pinss H.100/H.110 compliant interface; all mandatory signalss Programmable connections to any of the 4096 time slots on the H.100/H.110 buss Up to 16 local serial inputs and 16 local serial outputs, programmable for 2.048 Mbits/s,4.096 Mbits/s, and 8.192 Mbits/s operation per CHI specificationss Programmable switching between local time slots, up to 1024 connectionss Programmable switching between local time slots and H.100/H.110 bus, up to 512 connectionss Choice of frame integrity or minimum latency switching on a per-time-slot basis:— Frame integrity to ensure proper switching of wideband data— Minimum latency switching to reduce delay in voice channelss On-chip phase-locked loop (PLL) for H.100/H.110, MVIP*, or Dialogic’s† SC-bus clock operation in master or slave clock modess Serial TDM bus rate and format conversion between most standard busess Optional 8-bit parallel input and/or 8-bit parallel output for local TDM interfacess High-performance microprocessor interface:— Provides access to device configuration regis-ters and to time-slot data— Supports both Motorola‡ nonmultiplexed and Intel§ multiplexed/nonmultiplexed modess Subrate switching of nibbles, dibits, or bitss Programmable GPIO s T wo independently programmable groups of up to 12 framing signals eachs 3.3 V local I/O with 5 V tolerant inputs and TTL-compatible outputss Boundary-scan testing supports208-pin, plastic SQFPs217-pin BGA packageApplicationss Computer-telephony systemss Enhanced service platformss WAN access devicess PBXsDescriptionThe Ambassador T8105 is an H.100/H.110-compli-ant device that provides a complete interface between the H.100/H.110 bus and a wide variety of telephony interface components, processors, and other circuits. The bus interface provides all signals needed for the H.100/H.110 bus, the H-MVIP and MVIP-90 buses, or the SC-bus. Local interfaces include sixteen serial inputs and sixteen serial out-puts based on the Lucent concentration highway interface (CHI). T wo built-in time-slot interchangers are included. The first provides a local switching domain with up to 1024 programmable connections between time slots on the local CHI inputs and out-puts. The second supports up to 512 programmable connections between any time slot on the H.100/ H.110 bus and any time slot in the local switching domain. The Ambassador T8105 is configured via a microprocessor interface. This interface can also read and write time-slot and device data.*MVIP is a trademark of Natural MicroSystems Corporation.†Dialogic is a registered trademark of Dialogic Corporation.‡Motorola is a registered trademark of Motorola, Inc.§Intel is a registered trademark of Intel Corporation.2Lucent Technologies Inc.Product BriefMay 1998H.100/H.110 Interface and Time-Slot InterchangerAmbassador T8105Description (continued)Onboard clock circuitry , including a digital phase-locked loop, supports all H.100/H.110 clock modes including MVIP and SC-bus compatibility clocks. The local CHI interfaces support PCM rates of 2.048 Mbits/s,4.096 Mbits/s, and 8.192 Mbits/s. The Ambassador T8105 has internal circuitry to support either minimum latency or multi-time-slot frame integrity. Frame integrity is a requisite feature for applications that switch wideband data (ISDN H-channels). Minimum latency is advantageous in voice applications.5-6101(F)cFigure 1. Block Diagram of the Ambassador………H.100, H.110, H-MVIPINTERNAL CLOCKS ANDSTATE COUNTERS/P AND P/S CONVERTERS512LOCATION DATA SRAMTHREE 512LOCATION CONNECTIONCAMs1024LOCATION DATA MEMORY OUTPUT LOGIC AND P/S CONVERTINPUT LOGIC AND S/P CONVERT 1024LOCATION CONNECTION MEMORYTIMING AND CONTROLMICROPROCESSORINTERFACEFRAME GROUP INTERFACE LOGICFRAME GROUPSADDR[1:0]DATA[7:0]µP CONTROLSMISC. I/OCLOCKS AND REFSINTERNAL DATAINTERNAL ADDRESS AND CONTROLLOCAL OUTLOCAL INProduct BriefMay 1998H.100/H.110 Interface and Time-Slot InterchangerAmbassador T8105Application OverviewThe integration of computers and telecommunications has enabled a wide range of new communications applications and has fueled an enormous growth in communications markets. A key element in the devel-opment of computer-based communications equipment has been the addition of an auxiliary telecom bus to existing computer systems. Most manufacturers of high-capacity, computer-based telecommunications equipment have incorporated some such telecom bus in their systems. T ypically, these buses and bus inter-faces are designed to transport and switch Nx64 kbits/s low-latency telecom traffic between boards within the computer, independent of the computer’s I/O and mem-ory buses. At least a half dozen of these PC-based telecom buses emerged in the early 1990s for use within equipment based on ISA/EISA and MCA com-puters.With the advent of the H.100/H.110 bus specification by the Enterprise Computer T elephony Forum, the com-puter-telephony industry has agreed on a single tele-com bus for use with PCI and compact PCI computers.H.100/H.110 facilitates interoperation of components, thus providing maximum flexibility to equipment manu-facturers, value-added resellers, system integrators, and others building computer-based telecommunica-tions applications.Subrate switching is the ability to switch part(s) of one byte from one stream/time slot to another stream/time slot. The parts are the following:s Nibbles (4 bits)—representing a 32 kbits/s subrates Dibits (2 bits)—representing a 16 kbits/s subrates Bits—representing an 8 kbits/s subrateH.100/H.110 data transfers are always bytes. If subrate switching is used, the T8100A constructs a byte con-sisting of the subrate samples. The constructed byte may contain any combination of nibbles, dibits, or bits. In addition, individual data bits can be placed within a byte along with don’t care bits.5-6099FFigure 2. CTI Call Center Application DATABASEETHERNETCTI SERVERUSER EXTENSIONSASRFAXT1/E1ISDNPCIBUSH.100/H.110 BUSTO PSTNT1E1ISDNLucent Technologies Inc.3Lucent T echnologies Inc. reserves the right to make changes to the product(s) or information contained herein without notice. No liability is assumed as a result of their use or application. No rights under any patent accompany the sale of any such product(s) or information. Ambassador is a trademark of Lucent T echnologies Inc.Copyright © 1998 Lucent T echnologies Inc.All Rights Reserved Printed in U.S.A.May 1998PN98-141NTNBPrinted On Recycled PaperFor additional information, contact your Microelectronics Group Account Manager or the following:INTERNET:/micro E-MAIL:docmaster@ N. AMERICA:Microelectronics Group, Lucent T echnologies Inc., 555 Union Boulevard, Room 30L-15P-BA, Allentown, P A 181031-800-372-2447, FAX 610-712-4106 (In CANADA: 1-800-553-2448, FAX 610-712-4106)ASIA P ACIFIC:Microelectronics Group, Lucent T echnologies Singapore Pte. Ltd., 77 Science Park Drive, #03-18 Cintech III, Singapore 118256Tel. (65) 778 8833, FAX (65) 777 7495CHINA:Microelectronics Group, Lucent T echnologies (China) Co., Ltd., A-F2, 23/F , Zao Fong Universe Building, 1800 Zhong Shan Xi Road,Shanghai 200233 P . R. China Tel. (86) 21 6440 0468, ext. 316, FAX (86) 21 6440 0652JAP AN:Microelectronics Group, Lucent T echnologies Japan Ltd., 7-18, Higashi-Gotanda 2-chome, Shinagawa-ku, T okyo 141, JapanTel. (81) 3 5421 1600, FAX (81) 3 5421 1700EUROPE:Data Requests: MICROELECTRONICS GROUP DA T ALINE: Tel. (44) 1189 324 299, FAX (44) 1189 328 148T echnical Inquiries:GERMANY: (49) 89 95086 0 (Munich), UNITED KINGDOM: (44) 1344 865 900 (Bracknell),FRANCE: (33) 1 48 83 68 00 (Paris), SWEDEN: (46) 8 600 7070 (Stockholm), FINLAND: (358) 9 4354 2800 (Helsinki), IT AL Y: (39) 2 6608131 (Milan), SP AIN: (34) 1 807 1441 (Madrid)Product BriefMay 1998H.100/H.110 Interface and Time-Slot InterchangerAmbassador T8105T8105 Selection GuideFeaturesT8100T8100A T8102T8105Subrate switching —√√√Local-to-local connections 1,0241,024—1,024Local-to-H.100 connections256256512512CT_NETREFs1222。

超导磁体电源

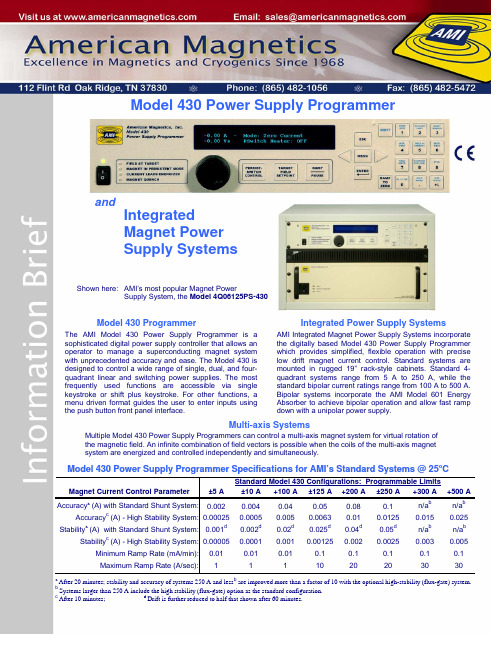

M o d e l 430 P o w e r S u p p l y P r o g r a m m e r S p e c i f i c a t i o n s f o r A M I ’s S t a n d a r d S y s t e m s @ 25o CStandard Model 430 Configurations: Programmable LimitsMagnet Current Control Parameter±5 A±10 A +100 A ±125 A +200 A ±250 A +300 A +500 AAccuracy a (A) with Standard Shunt System: 0.002 0.004 0.04 0.05 0.08 0.1 n/a bn/a bAccuracy c(A) - High Stability System: 0.000250.0005 0.005 0.0063 0.01 0.0125 0.015 0.025Stability a(A) with Standard Shunt System: 0.001d0.002d0.02d0.025d0.04d0.05dn/a bn/a bStability c(A) - High Stability System: 0.000050.0001 0.001 0.001250.002 0.0025 0.003 0.005 Minimum Ramp Rate (mA/min): 0.01 0.01 0.01 0.1 0.1 0.1 0.1 0.1 Maximum Ramp Rate (A/sec):1111020203030aAfter 20 minutes; stability and accuracy of systems 250 A and less bare improved more than a factor of 10 with the optional high-stability (flux-gate) system.bSystems larger than 250 A include the high stability (flux-gate) option as the standard configuration. c After 10 minutes; d Drift is further reduced to half that shown after 60 minutes.Model 430 Power Supply ProgrammerandIntegrated Magnet Power Supply SystemsShown here: AMI’s most popular Magnet Power Supply System, the Model 4Q06125PS-430Model 430 ProgrammerIntegrated Power Supply SystemsThe AMI Model 430 Power Supply Programmer is a sophisticated digital power supply controller that allows an operator to manage a superconducting magnet system with unprecedented accuracy and ease. The Model 430 is designed to control a wide range of single, dual, and four-quadrant linear and switching power supplies. The most frequently used functions are accessible via single keystroke or shift plus keystroke. For other functions, a menu driven format guides the user to enter inputs using the push button front panel interface.AMI Integrated Magnet Power Supply Systems incorporate the digitally based Model 430 Power Supply Programmer which provides simplified, flexible operation with precise low drift magnet current control. Standard systems are mounted in rugged 19” rack-style cabinets. Standard 4-quadrant systems range from 5 A to 250 A, while the standard bipolar current ratings range from 100 A to 500 A. Bipolar systems incorporate the AMI Model 601 Energy Absorber to achieve bipolar operation and allow fast ramp down with a unipolar power supply.Multi-axis SystemsMultiple Model 430 Power Supply Programmers can control a multi-axis magnet system for virtual rotation of the magnetic field. An infinite combination of field vectors is possible when the coils of the multi-axis magnet system are energized and controlled independently and simultaneously.Model 430 Features•Parameter for setting persistent switch cool time1•Ultrahigh resolution and accuracy•Intuitive user operation and comprehensive manual2•Upper current limit and voltage limit settings•Easy to read digital V m/V s (magnet and supply voltage) display meter•Can automatically determine inductance of load•Drivers for LabView•User-adjustable threshold quench detection with detection I/O••Galvanically isolated Program Output signal to prevent ground loops•Multifunction vacuum fluorescent display (VFD)•Menu driven user interface and keypad – logical and intuitive•One touch Ramp/Pause button•Digital readout in Field (kilogauss or Tesla) or Current (Amperes)•Control multiple parallel or series configured supplies•Front panel indication that current is flowing in magnet leads•Velocity sensitive encoder dial for fine adjustments•Programmable piecewise-continuous ramping with 10 current-dependent rates•I ntegrated DB-25 magnetstation connector with wiredDB-25 output signals availablefor other system devices•Built-in Ethernet and RS-2323 communication interfaces•Ethernet port allows access to the Programmer across a local network or via the Internet•Operating software is stored in flash memory and can easily be updated via the Ethernet or RS-232 ports1Important for conduction-cooled magnets (dry switch) when a relatively long time is required to cool as compared with wet switches.2Manual is conveniently available in the Model 430 firmware (pdf format) - just access the instrument’s IP address via a web browser.3An optional external conversion unit is available for interfacing the RS-232 serial port to a GPIB bus.Simplified OperationMost frequently used functions are accessible via single keystroke or shift plus keystroke. The front panel velocity-accelerated rotary encoder dial also allows the operator to make fine adjustments to operating parameters of the magnet system. Magnet system signal wiring, such as magnet voltage/current, helium levels, and temperatures, connect to the rear panel through a single DB-25 connector. Multiple connectors on the rear panel allow the user to route the signals to the appropriate instruments at the control station; the need for complicated wiring between the cryostat and magnet control station is thus eliminated.Digital ControlThe digitally-based Model 430 incorporates very high resolution analog <> digital converters and digital signal processing (DSP) to achieve excellent stability, precise control, and superior current resolution of the programmed magnetic field. An internal microcomputer manages all computations, analog data conversion, display/keypad functions, communications I/O, and analog power supply programming signals.High Resolution and StabilityPrecision instrumentation techniques and potentiometer-free designs are employed throughout the instrument to ensure accurate signal translation for a wide range of conditions. The magnet current is sampled at a resolution of 15.6 µA (for a 125 A supply) and is front-panel programmable in 0.1 mA increments. A further order of magnitude in accuracy and stability can be achieved by choosing the optional fluxgate based current measurement system in place of the standard resistive shunt.Magnet Control and ProtectionThe Model 430 protects the magnet from runaway supply voltage/current or operator error. The quench detect function, with user-adjustable quench sensitivity, is designed to detect a magnet quench and quickly stop power from being delivered to the resistive magnet. The system can optionally incorporate an AMI Liquid Helium (LHe) Level Instrument to prevent magnet quenching due to low LHe level; automatic ramp down of the magnet (even in persistent mode) is initiated if the LHe level drops to a preset level.A system administrator can program the instrument (from the front panel or remotely) with password protected operational limits or any other parameter(s) which can thereafter not be exceeded or changed without the password. During operation of the system, if the operator inadvertently attempts to take the magnet system to an excessive magnetic field strength or excessive voltage, the Programmer will not accept the parameter and will alert the operator that the value exceed the limits.The Model 430 automatically determines and sets the proper persistent switch heater current (range: 0 to 100 mA; compliance 13.5 V). The persistent switch heater circuit is continually monitored and the user is notified of circuit problems. The Model 430 Programmer automatically controls the power supply and persistent switch heater to aid the user in safe and quick transitions in and out of persistent mode.For single quadrant operation (I+, V+) the Model 430Programmer can control various unipolar switching or linearsupplies. Shown here is the AMI Model 08150PS-430 1200 wattswitching supply combination. This system offers great value,small size, and minimum heat generation. The Model 430Programmer has also been tested on older supplies such as theHP6260B linear power supply; it can breathe new life into yoursystem by offering state of the art control capability.Bipolar operation (I+, V-/+) is obtained by adding a Model 601Energy Absorber unit to take full advantage of programmedmagnetic field profiles, and other situations requiring fast rampdown rates.AMI’s lowest-power standard bipolar power supply system, designated 05100PS-430-601, has the Model 08150PS configured at 100 A/ 10 V, and in conjunction with the Model 601, supplies 100 A at 5 V to the load. The system comes mounted in a 19” rack style cabinet. Specifications for this and other standard AMI bipolar systems are outlined below. AMI’s highest-power standard bipolar power supply system, the Model 05500PS-430-601, is pictured on the last page of this brochure. Other ratings and configurations are available.Specifications – Standard Cabinet Mounted Bipolar Power Supply Systems SystemMaximumCurrentMaximumVoltageOutputPowerMaximumInput Power aTypicalNoiseDimensions bh x w x dApproximateWeight c 05100PS-430-601: +100 A ±5 Vdc 500 VA 1500 VA 75 mV p-p 12.5" x 21.0" x 24.5" 70 lb (32 kg)05200PS-430-601: +200 A ±5 Vdc 1000 VA 3000 VA 75 mV p-p 25.0" x 23.6" x 23.6" 165 lb (75 kg) 05300PS-430-601: +300 A ±5 Vdc 1500 VA 4500 VA 75 mV p-p 30.3" x 23.6" x 23.6" 215 lb (98 kg) 05500PS-430-601: +500 A ±5 Vdc 2500 VA 7250 VA 75 mV p-p 47.2" x 21.3" x 24.5" 330 lb (150 kg)a Includes Model 430 and Model 601 bRack/cabinet dimensions; h = height; w = width; d = depth c Includes rack/cabinetFor true high-current four-quadrant operation (I+/-, V+/-) the Model430 is configured with the Model 4Q06125PS Power Supply toprovide smooth, linear sweeps through zero current with constantramp rates across the entire operating range. The magnet systemcan easily be fine tuned by making precise adjustments to the currentthrough the use of the convenient velocity sensitive encoder dial. Thissystem, designated 4Q06125PS-430, comes standard in a 19” rackstyle cabinet, and is depicted on the cover page of this brochure.For higher voltage or current, series and parallel configurations of the4Q06125PS are available (designated 4Q12125PS-430 and4Q06250PS-430). For smaller magnets, four quadrant power supplysystems (designated 4Q1005PS-430 and 4Q1010PS-430)incorporate the smaller Kepco BOP supplies and are offered forsmaller magnet requirements. Specifications for standard AMI fourquadrant systems are outlined below.Other ratings and configurations are available.Specifications – Standard Cabinet Mounted Four Quadrant Power Supply Systems SystemMaximumCurrentMaximumVoltageOutputPowerMaximumInput Power aTypicalNoiseDimensions bh x w x dApproximateWeight c 4Q06125PS-430: ±125 A ±6 Vdc 750 VA 2000 VA 120 mV p-p 12.5" x 21.0" x 24.5" 100 lb (46 kg)4Q06250PS-430: ±250 A ±6 Vdc 1500 VA3800 VA 120 mV p-p 19.5" x 21.0" x 24.5" 200 lb (91 kg)4Q12125PS-430: ±125 A ±12 Vdc 1500 VA3800 VA 240 mV p-p 19.5" x 21.0" x 24.5" 200 lb (91 kg)4Q1005PS-430: ±5 A ±10 Vdc 50 VA 700 VA 10 mV p-p 12.5" x 21.0" x 24.5" 85 lb (39 kg)4Q1010PS-430: ±10 A ±10 Vdc 100 VA 1200 VA 10 mV p-p 12.5" x 21.0" x 24.5" 85 lb (39 kg)a Includes Model 430 bRack/cabinet dimensions; h = height; w = width; d = depth c Includes rack/cabinetThe Internet Protocol Model 430IP Power Supply ProgrammerWith no front panel controls except the power On/Off switch, the Model 430IP is designed for fully functional magnet system control via the rear panel Ethernet connection using TCP/IP with a web browser.Control can be established through a locally connected computer or remotely through a network or even the Internet; the human/machine interface is a web browser depiction of the Model 430. This is especially useful for multi-axis systems where a computer is an inherent part of the system. The IP-capable firmware can also be applied to the standard Model 430 with front panel controls – in this case the computer-displayed Model 430 mirrors and controls all hardware front panel devices with theexception of the ac input power switch. The following is a screen-shot of the Model 430IP being controlled with a web browser.Selecting an AMI Power Supply SystemModel 05500PS-430-601 SystemBipolar (Magnet Voltage -5 V 1to +5 V)05500PS-430-60105300PS-430-60105200PS-430-60105100PS-430-6010 A 100 A 200 A 300 A 400 A 500 A1Available for fast discharge of magnet.Four Quadrant High Current (Magnet Voltage -6 V to +6 V)4Q06250PS-4304Q06125PS-430-300 A -200 A-100 A 0 A 100 A 200 A 300 AFour Quadrant High Current (Magnet Voltage -12 V to +12 V)4Q12125PS-430 4Q12125PS-430-200 A -100 A 0 A 100 A 200 AFour Quadrant Low Current (Magnet Voltage -10 V to +10 V)4Q1010PS-430 4Q06125PS4Q1005PS-430-10 A -5 A 0 A 5 A 10 A。

外泌体之家---笔记

外泌体之家笔记外泌体简介Exosome ,中文名外泌体,是一种能被大多数细胞分泌的微小膜泡,具有脂质双层膜结构,直径大约40-100 nm 。

尽管外泌体最初在1983 年就被发现,但人们一直认为它只是一种细胞的废弃物。

然而最近几年,人们发现这种微小膜泡中含有细胞特异的蛋白、脂质和核酸,能作为信号分子传递给其他细胞从而改变其他细胞的功能。

这些发现点燃了人们对细胞分泌膜泡的兴趣。

最近的研究发现外泌体在很多生理病理上起着重要的作用,如免疫中抗原呈递、肿瘤的生长与迁移、组织损伤的修复等。

不同细胞分泌的外泌体具有不用的组成成分和功能,可作为疾病诊断的生物标志物。

外泌体具有脂质双层膜结构,能很好的保护其包被的物质,且能靶向特定)。

细胞或组织,因此是一种很好靶向给药系统(targeted delivery system2015 年,随着精准医学概念的提出,越来越多的人开始关注如何能做到疾病的精确诊断和治疗。

外泌体作为一个新型的研究热点,由于它在体内存在的广泛性和获取的便捷性,已经成为了疾病诊断治疗的潜在有效方式,在精准医学发展上有着光明的前景。

综述虽然,已有初步研究结果解释外泌体在体内的运输途径。

4)外泌体对肿瘤免疫的影响,以及对肿瘤抗放疗、抗化疗的影响。

Cell :外泌体的研究现状与未来方向--CQ号传导的功能研究仍需要一些实质性的研究来解释。

在这篇综述中,作者以肿瘤细胞及其微 环境为背景,认为癌细胞分泌的外泌体对癌症的发生及恶化起着重要的媒介调控作用。

:as-,。

・』蓄] IMF*tj 趨勰矍:魁趣 EV ZIdT dl 価n 1 niZ pKilitatiDO Dh ml[ nDLIiLvrind'Inhidupodiu Inr —■I'cp -R d ■■ H I M X U I L M■ C 石l-rr.t&J ■■«UJ - 2 lllv IsIMF DP fCU ruiPr>>rTHlActK rwclicifeliiblrVwwnli 一合尹丫AgP 二帀 flf F£i ・[i,z 号flfUiTT'F = ji-Jllff. u- J ui' iJiiJy- ^dbidlunH'al'fairrw Vniliiv e ■ EI J圭 c lU HHI 5 J I 二心ft*____常《(■ kr\.i|yb ・n —“…y一營V”厂百炉L '弦f 盘*莎Hp .!?■ !;;" j “ Ilk Cl*: i-TR. Illi- mi Fl i —I rr : ■:r«・rF*<Kf尸9在这篇Cell 文章中,作者首先总结了目前外泌体最引人注目的功能研究: 1)外泌体携带的 蛋白促进了肿瘤进展和转移;2)外泌体的分泌、运输途径等传递信号通路;3)外泌体中的但关于,其介导的细胞间的信小RNA 具有什么作用;从物理、 生化上区分开, 比如说不同类型的外泌体存在哪些不同的生物标志物, 学功能上区分不同类型的外泌体仍存在很多难题。

PCB专业术语翻译(英语)

PCB专业术语(英语)PCBprinted circuitboard 印刷电路板,指空得线路板PCBA printed circuit boardassembly印刷电路板组件,指完成元件焊接得线路板组件PWA PrintedWire Assembly,Aperturelist Editor:光圈表编辑器。

Aperturelistwindows:光圈表窗口.Annular ring:焊环。

Array:拼版或陈列.Acid trip:蚀刻死角。

Assemby:安装.Bare Bxnel:光板,未进行插件工序得PCB板。

Bad Badsize:工作台,工作台有效尺寸.BlindBuried via:盲孔,埋孔。

Chamfer:倒角。

Circuit:线路。

Circuitlayer:线路层。

Clamshell tester:双面测试机.Coordinates Area:坐标区域.Copy—protect key:软件狗。

Coutour:轮廓。

Draw:一种圆形得光圈,但只就是用于创建线路,不用于创建焊盘。

Drill Rack:铅头表。

Drill Rack Editor:铅头表编辑器。

DrillRackwindow:铅头表窗口。

DCode:Gerber格式中用不着于表达光圈得代码。

Double—sided Biard:双面板。

Endof Block character(EOB):块结束符。

Extract Netlist:提取网络.Firdacial:对位标记.Flash:焊盘,来源于早期矢量光绘机,在矢量光绘机中,焊盘就是光通过光圈“闪出”(Fla sh)而形成得。

Gerber Data:从PCBCAD系统到PCB生产过程中最常用得数据格式.Grid:栅格。

GraphicalEditor:图形编辑器.Incremental Data:增量数据。

Land:接地层。

Layer list window:层列表窗口.Layer setup Area:层设置窗口.Multilayer Board:多层板。

英文翻译——精选推荐

英⽂翻译英⽂翻译(English translation)INTRODUCTION1.0INTRODUCTIONThe AS language reference manual is designed to assist the user whose primary responsibility includes programming and operating Kawasaki industrial robots on a daily basis. AS language is a computer control language designed specifically for use with Kawasaki robot controllers. This text provides information on creating programs, running programs, and editing programs using AS language commands. AS language is relatively easy to learn with many keywords, syntax sequences, and interface commands being intuitive.AS language provides the programmer with the ability to precisely define the task a robot is to perform .Programming the robot with a computer control language (AS) also provides the ability to integrate peripheral components into the program. Typical component interfacing with AS language programs includes: programmable logic controllers (PLCs),lasers, weld controllers, gray scale vision, and remote sensing systems.AS language programs provide outstanding performance in terms of robot trajectory control. Program location points can be stored and played back as either joint angles representing the manipulator (precision points) or geometrically defined locations in the work envelope (transformations). Transformations locations can also be defined based on their relative position to one another (compound transformations).These capabilities allow program locations to be shifted and moved based on parameters and variables and identified in the AS language program.简介1.0简介由于语⾔参考⼿册的⽬睹是帮助⽤户,其主要职责包括编程和操纵川崎⼯业机器⼈的⽇常⼯作。

自动化专业-外文文献-英文文献-外文翻译-plc方面

1、外文原文(复印件)A: Fundamentals of Single-chip MicrocomputerTh e si ng le-ch i p mi cr oc om pu ter is t he c ul mi nat i on o f bo th t h e d ev el op me nt o f th e d ig it al com p ut er an d t he int e gr at ed ci rc ui ta r gu ab ly th e t ow m os t s i gn if ic ant i nv en ti on s o f t h e 20t h c en tu ry[1].Th es e to w t ype s o f a rc hi te ct ur e a re fo un d i n s i ng le—ch ip m i cr oc om pu te r。

S o me em pl oy th e s p li t p ro gr am/d at a me mo ry of t he H a rv ar d ar ch it ect u re, sh ow n in Fi g.3-5A—1,ot he r s fo ll ow t hep h il os op hy, wi del y a da pt ed f or ge n er al—pu rp os e c o mp ut er s an dm i cr op ro ce ss or s, of ma ki ng no lo gi c al di st in ct io n be tw ee n p ro gr am a n d da ta m em or y a s i n th e Pr in cet o n ar ch it ec tu re,sh ow n in F ig。

3-5A-2.In g en er al te r ms a s in gl e—ch i p mi cr oc om pu ter isc h ar ac te ri zed b y the i nc or po ra tio n of al l t he uni t s o f a co mp ut er i n to a s in gl e de v i ce,as s ho wn i n F ig3—5A—3。

毕业设计英文翻译-智能热能表控制器外文翻译-中英文文献对照翻译