74LS161 中文版详细

74LS161和74LS290集成计数器功能说明

74LS161和74LS290集成计数器功能说明1、集成同步计数器同步计数器电路复杂,但计数速度快,多用在计算机电路中。

目前生产的同步计数器芯片分为二进制和十进制两种。

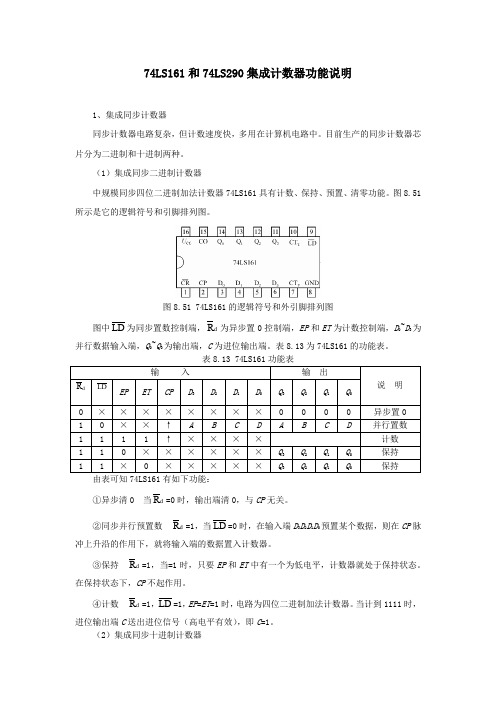

(1)集成同步二进制计数器中规模同步四位二进制加法计数器74LS161具有计数、保持、预置、清零功能。

图8.51所示是它的逻辑符号和引脚排列图。

图8.51 74LS161的逻辑符号和外引脚排列图图中LD为同步置数控制端,d R为异步置0控制端,EP和ET为计数控制端,D0~D3为并行数据输入端,Q0~Q3为输出端,C为进位输出端。

表8.13为74LS161的功能表。

R=0时,输出端清0,与CP无关。

①异步清0 当dR=1,当LD=0时,在输入端D3D2D1D0预置某个数据,则在CP脉②同步并行预置数d冲上升沿的作用下,就将输入端的数据置入计数器。

R=1,当=1时,只要EP和ET中有一个为低电平,计数器就处于保持状态。

③保持d在保持状态下,CP不起作用。

R=1,LD=1,EP=ET=1时,电路为四位二进制加法计数器。

当计到1111时,④计数d进位输出端C送出进位信号(高电平有效),即C=1。

(2)集成同步十进制计数器集成同步十进制加法计数器74LS160的管脚图和功能表与74LS161基本相同,唯一不同的是74LS160是十进制计数器,而74LS161是二进制计数器。

2、集成异步计数器异步计数电路简单,但计数速度慢,多用于仪器、仪表中。

(1)集成计数器74LS290图8.52是二-五-十进制集成计数器74LS290的逻辑结构图。

它兼有二进制、五进制和十进制三种计数功能。

当十进制计数时,又有8421BCD 和5421BCD 码选用功能,表8.14是它的功能表。

95481213131011CP 0CP 1Q 0Q 1Q 3Q 2R O(1)R O(2)S 9(1)S 9(2)图8.52 74LS290的逻辑结构图由表可知,74LS290具有如下功能:①异步置0 当R 0(1)=R 0(2)=1且S 9(1)或S 9(2)中任一端为0,则计数器清零,即Q D Q C Q B Q A =0000。

74ls161引脚图与管脚功能表资料

74ls161引脚图与管脚功能表资料74LS161是常用的四位二进制可预置的同步加法计数器,他可以灵活的运用在各种数字电路,以及单片机系统种实现分频器等很多重要的功能,:<74ls161引脚图>管脚图介绍:时钟CP和四个数据输入端P0~P3清零/MR使能CEP,CET置数PE数据输出端Q0~Q3以及进位输出TC. (TC=Q0·Q1·Q2·Q3·CET)输入输出C R CP LD EP ET D3D2D1D0Q3 Q2Q1Q00 Ф Ф Ф Ф Ф Ф Ф Ф 0 0 0 01 ↑ 0 Ф Ф d c b a d c b a1 ↑ 1 0 Ф Ф Ф Ф Ф Q3 Q2Q1Q01 ↑ 1 Ф 0 Ф Ф Ф Ф Q3 Q2Q1Q01 ↑ 1 1 1 Ф Ф Ф Ф 状态码加1<74LS161功能表〉从74LS161功能表功能表中可以知道,当清零端CR=“0",计数器输出Q3、Q2、Q1、Q0立即为全“0",这个时候为异步复位功能。

当CR=“1”且LD=“0”时,在CP信号上升沿作用后,74LS161输出端Q3、Q2、Q1、Q0的状态分别与并行数据输入端D3,D2,D1,D0的状态一样,为同步置数功能。

而只有当CR=LD=EP=ET=“1"、CP脉冲上升沿作用后,计数器加1。

74LS161还有一个进位输出端CO,其逻辑关系是CO= Q0·Q1·Q2·Q3·CET。

合理应用计数器的清零功能和置数功能,一片74LS161可以组成16进制以下的任意进制分频器。

74ls161引脚图与管脚功能表资料

74ls161引脚图与管脚功能表资料

74LS161是常用的四位二进制可预置的同步加法计数器,他可以灵活的运用在各种数字电路,以及单片机系统种实现分频器等很多重要的功能,:

<74ls161引脚图>

管脚图介绍:

时钟CP和四个数据输入端P0~P3

清零/MR

使能CEP,CET

置数PE

数据输出端Q0~Q3

以及进位输出TC. (TC=Q0·Q1·Q2·Q3·CET)

<74LS161功能表>

从74LS161功能表功能表中可以知道,当清零端CR=“0”,计数器输出Q3、Q2、Q1、Q0立即为全“0”,这个时候为异步复位功能。

当CR=“1”且LD=“0”时,在CP信号上升沿作用后,74LS161输出端Q3、Q2、Q1、Q0的状态分别与并行数据输入端D3,D2,D1,D0的状态一样,为同步置数功能。

而只有当CR=LD=EP=ET=“1”、CP脉冲上升沿作用后,计数器加1。

74LS161还有一个进位输出端CO,其逻辑关系是CO= Q0·Q1·Q2·Q3·CET。

合理应用计数器的清零功能和置数功能,一片74LS161可以组成16进制以下的任意进制分频器。

74ls161引脚图与管脚功能表资料

74ls161引脚图与管脚功能表资料之蔡仲巾千创作创作时间:二零二一年六月三十日74LS161是经常使用的四位二进制可预置的同步加法计数器, 他可以灵活的运用在各种数字电路, 以及单片机系统种实现分频器等很多重要的功能, :<74ls161引脚图>管脚图介绍:时钟CP和四个数据输入端P0~P3清零/MR使能CEP, CET置数PE数据输出端Q0~Q3以及进位输出TC. (TC=Q0·Q1·Q2·Q3·CET)输入输出C R CP LD EP ET D3D2D1D0Q3 Q2Q1Q00 Ф Ф Ф Ф Ф Ф Ф Ф 0 0 0 01 ↑ 0 Ф Ф d c b a d c b a1 ↑ 1 0 Ф Ф Ф Ф Ф Q3 Q2Q1Q01 ↑ 1 Ф 0 Ф Ф Ф Ф Q3 Q2Q1Q01 ↑ 1 1 1 Ф Ф Ф Ф 状态码加1<74LS161功能表>从74LS161功能表功能表中可以知道, 当清零端CR=“0”, 计数器输出Q3、Q2、Q1、Q0立即为全“0”, 这个时候为异步复位功能.当CR=“1”且LD=“0”时, 在CP信号上升沿作用后,74LS161输出端Q3、Q2、Q1、Q0的状态分别与并行数据输入端D3, D2, D1, D0的状态一样, 为同步置数功能.而只有当CR=LD=EP=ET=“1”、CP脉冲上升沿作用后, 计数器加1.74LS161还有一个进位输出端CO, 其逻辑关系是CO= Q0·Q1·Q2·Q3·CET.合理应用计数器的清零功能和置数功能, 一片74LS161可以组成16进制以下的任意进制分频器.。

74ls161引脚图与管脚功能表资料

74LS161是常用的四位二进制可预置的同步加法计数器,他可以灵活的运用在各种数字电路,以及单片机系统种实现分频器等很多重要的功能,:<74ls161引脚图>管脚图介绍:时钟CP和四个数据输入端P0~P3清零/MR使能CEP,CET置数PE数据输出端Q0~Q3以及进位输出TC. (TC=Q0·Q1·Q2·Q3·CET)输入输出C R CP LDEP ET D3D2D1DQ3Q2Q1Q0 Ф Ф Ф Ф Ф Ф Ф Ф 0 0 0 01 ↑ 0 Ф Ф d c b a d c b a1 ↑ 1 0 Ф Ф Ф Ф Ф Q3 Q2Q1Q01 ↑ 1 Ф 0 Ф Ф Ф Ф Q3 Q2Q1Q01 ↑ 1 1 1 Ф Ф Ф Ф 状态码加1<74LS161功能表>从74LS161功能表功能表中可以知道,当清零端CR=“0”,计数器输出Q3、Q2、Q1、Q0立即为全“0”,这个时候为异步复位功能。

当CR=“1”且LD=“0”时,在CP信号上升沿作用后,74LS161输出端Q3、Q2、Q1、Q0的状态分别与并行数据输入端D3,D2,D1,D0的状态一样,为同步置数功能。

而只有当CR=LD=EP=ET=“1”、CP脉冲上升沿作用后,计数器加1。

74LS161还有一个进位输出端CO,其逻辑关系是CO= Q0·Q1·Q2·Q3·CET。

合理应用计数器的清零功能和置数功能,一片74LS161可以组成16进制以下的任意进制分频器。

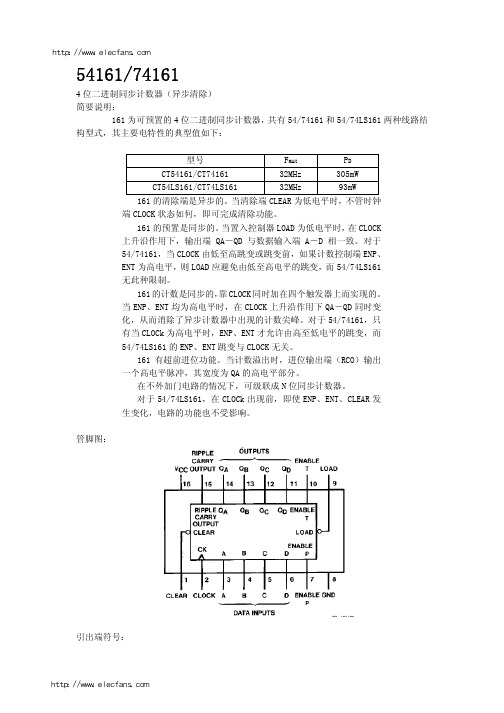

161 的清除端是异步的。

当清除端C LEAR 为低电平时,不管时钟端C LOCK 状态如何,即可完成清除功能。

161 的预置是同步的。

当置入控制器L OAD 为低电平时,在C LOCK 上升沿作用下,输出端QA-QD 与数据输入端A-D 相一致。

对于54/74161,当C LOCK 由低至高跳变或跳变前,如果计数控制端E NP、ENT 为高电平,则L OAD 应避免由低至高电平的跳变,而54/74LS161 无此种限制。

74LS161管脚排列图

74LS161管脚排列图

该计数器能同步并行预置数据,具有清零置数,计数和保持功能,具有进位输出端,可以串接计数器使用。

它的管脚排列如图15-5所示:

图5-5 74LS161管脚排列图

它的功能表如下:

表5-3 74LS161功能表

从逻辑图和功能表可知,该计数器具有清零信号/MR,使能信号CEP,CE T,置数信号PE,时钟信号CP和四个数据输入端P0~P3,四个数据输出端Q0~Q3,以及进位输出TC,且TC=Q0·Q1·Q2·Q3·CET。

5、计数器的级连使用

一个十进制计数器只能显示0~9十个数,为了扩大计数器范围,常用多个十进制计数器级连使用。

同步计数器往往设有进位(或借位)输出端,故可选用其进位(或借位)输出信号来驱动下一级计数器。

下图是由74LS192利用进位输出控制高一位的加计数端构成的加数级连示意图:。

74LS161真值表

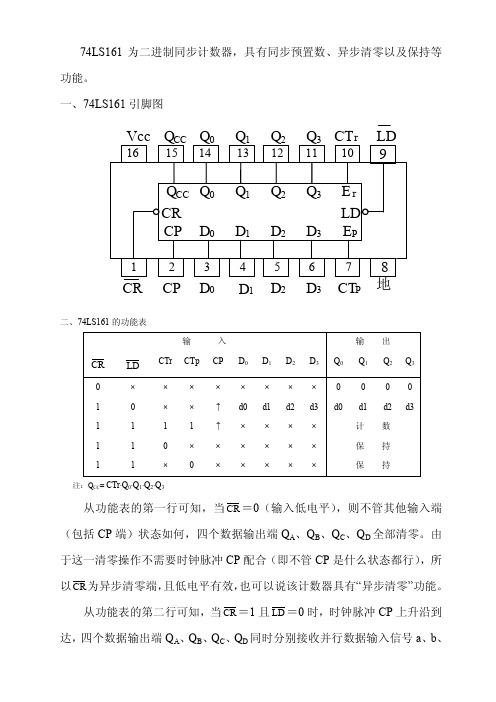

74LS161为二进制同步计数器,具有同步预置数、异步清零以及保持等功能。

一、74LS161引脚图

D 1

D 0

D 2D 3CT P

CR

CP

二、74LS161的功能表

注:Q CC = CTr ·Q 0·Q 1·Q 2·Q 3

从功能表的第一行可知,当CR =0(输入低电平),则不管其他输入端(包括CP 端)状态如何,四个数据输出端Q A 、Q B 、Q C 、Q D 全部清零。

由于这一清零操作不需要时钟脉冲CP 配合(即不管CP 是什么状态都行),所以CR 为异步清零端,且低电平有效,也可以说该计数器具有“异步清零”功能。

从功能表的第二行可知,当CR =1且LD =0时,时钟脉冲CP 上升沿到达,四个数据输出端Q A 、Q B 、Q C 、Q D 同时分别接收并行数据输入信号a 、b 、

c、d。

由于这个置数操作必须有CP上升沿配合,并与CP上升沿同步,所以称那么该芯片具有“同步置数”功能。

从功能表的第三行可知,当LD=CR=1,CTr=CTp=1时,则对计数脉冲CP实现同步十进制加计数;而从功能表的第四行又知道,当CR=LD=1时,只要CTr和ENP中有一个为0,则不管CP状态如何(包括上升沿),计数器所有数据输出都保持原状态不变。

因此,CTr和CTp应该为计数控制端,当它们同时为1时,计数器执行正常同步计数功能;而当它们有一个为0时,计数器执行保持功能。

另外,进位输出Q CC= CTr·Q0·Q1·Q2·Q3表明,进位输出端仅当计数控制端CTr=1且计数器状态为15时它才为1,否则为0。

74LS161中文资料

741S161中文资料介绍741S161是一种四位二进制同步计数器,采用了1S风格的逻辑门实现,能够实现在给定的时钟脉冲下进行递增或递减计数的功能。

该芯片广泛应用于数字逻辑电路和计算机系统中。

功能特点•可以实现二进制计数,递增或递减∙集成了同步和异步清零功能•可以设置最大计数值•支持并行和串行数据输入•适用于高速计数和频率分频应用•可配置的异步复位功能引脚说明741S161芯片一共有16个引脚,其中各引脚的功能如下:1.八进制清零器(C1R):接地信号时,该引脚将计数器清零。

2.CPD:串行数据输入时钟引脚,用于控制串行数据输入。

3.CET:计数器使能输入引脚,控制计数器的启用。

4.PE:并行输入使能引脚,控制并行输入的启用。

5.P0-P3:并行数据输入引脚,用于输入4位二进制数。

6.Q0-Q3:并行输出引脚,输出计数器的当前值。

7.UP/DN:计数器的计数方向选择引脚,接地时计数器减少,未接地时计数器增加。

8.MR:异步复位引脚,接地时计数器清零。

9.TC:计数器溢出弓I脚,当计数器的当前值等于最大计数值时为高电平。

10.GND:接地引脚。

H.TC:计数器溢出弓I脚,当计数器的当前值等于最大计数值时为高电平。

12.CEP:并行输入使能引脚,控制并行输入的启用。

13.CPD:串行数据输入时钟引脚,用于控制串行数据输入。

14.CET:计数器使能输入引脚,控制计数器的启用。

15.CP:时钟输入引脚,接收时钟脉冲输入。

16.VCC:正电源引脚。

741S161应用示例清零器(C1R):接地CPD:接到串行数据输入时钟CET:接地PE:接到并行输入使能P0-P3:接到并行输入数据UP/DN:接地MR:接地TC:接到溢出检测电路GND:接地CEP:接地CPD:接到时钟输入CET:接地CP:接到时钟输入VCC:正电源在上述示例中,我们配置了741S161来实现一个简单的二进制计数器。

并行输入模式被启用,四位并行数据会被输入到P0-P3引脚。

数电作业-用74ls161设计同步加法计数器

H a r b i n I n s t i t u t e o f T e c h n o l o g y设计说明书(论文)课程名称:数字电子技术基础设计题目:同步加法计数器设计院系:航天学院自动化班级:0804101设计者:龚翔宇学号:24设计时间:【问题重述】试用同步加法计数器74LS161(或74LS160)和二4输入与非门74LS20构成百以内任意进制计数器,并采用LED数码管显示计数进制。

采用555定时器构成多谐振荡电路,为同步加法计数器提供时钟输入信号。

【设计思路】同步加法计数器74LS161为16进制计数器,要设计一个60进制的计数器,用555定时器设计多谐振荡电路,为同步加法计数器74LS161提供时钟输入信号并且用LED数码管显示结果。

要用16进制的161计时器设计60进制的,必须将其改装为10进制的。

将2个161联级,低位向高位进位6次,然后置零——即基本设计思路。

【基本元件】74LS161(两片)二4输入与非门74LS20(一片)555定时器【设计方案】555定时器提供时钟信号用555构成的多谐振荡器用555定时器构成的多谐振荡器如图所示。

555定时器可以方便的接成施密特触发器,在其基础上再改接成多谐振荡器。

o u可输出触发脉冲信号。

74LS161接为十进制计数器本方案使用置数法将161改装为十进制的计数器。

用如图所示。

D C B A Q Q Q Q 在经过1000时置数控制端LD =0,74LS161处在置数状态,D C B AQ Q Q Q 重新回到1111, 跳过了中间6个状态,由16进制转换为十进制计数器。

RCO 仍为进位输出。

对于低位芯片,全以0态作为起始状态,经过10-1=9状态后,产生置数控制信号1001。

这样,当第10个时钟的上升沿到达时,计数器置数为0000,每个芯片跳过剩余状态,成为10进制的计数器。

对于高位芯片,以取全0态作为起始状态,经过6个状态后,计数器清零,每个芯片跳过剩余状态,成为6进制的计数器。

74LS161中文资料

0.7

V

74

0.8

0.8

-800

-400 μA

电子器件采购平台: IC资料查询网站: 电子工程技术论坛:/bbs

http://www.elecfans.com

54

输出低电平电流 IOL

74

时钟频率fCP

0

脉冲宽度 tW

25

35

35 24 27 24 27 14 14 28

单位 MHz ns

ns ns ns ns

http://www.elecfans.com

(LOAD=L)

(‘LS161 为 2KΩ)

tPLH CLOCk->RCO tPHL

tPHL CLEAR->Q

【2】:fmax-最大时钟频率

tPLH-输出由低到高电平传输延迟时间

tPHL-输出由高到低电平传输延迟时间

‘161 最小 最大

25

35

35 20 23 25 29 16 16 38

‘LS161 最小 最大

74 -18 -57 -20 -100

Vcc=最大,LOAD 先接高电平,再接低 54

85

IccH 输出高电平时电源电流

电平,其余输入接高电平

74

94

31 mA

31

Vcc=最大,CLOCK 先接高电平,再接低 54

91

IccL 输出低电平时电源电流

电平,其余输入接低电平

74

101

32 mA

32

【1】:测试条件中的“最大”和“最小”用推荐工作条件中的相应值。

VIH=2.4V(‘LS161 为 2.7V)

40

20

40

40 μA

74LS161计数器

74LS161计数器

<74ls161引脚图>

管脚图介绍:

时钟CP和四个数据输⼊端P0~P3

清零/MR

使能CEP,CET

置数PE

数据输出端Q0~Q3

以及进位输出TC.(TC=Q0·Q1·Q2·Q3·CET)

输⼊输出

C R CP L

D EP ET D3D2D1D0Q3Q2Q1Q0

0ФФФФФФФФ0000

1↑0ФФd c b a d c b a

1↑10ФФФФФQ3Q2Q1Q0

1↑1Ф0ФФФФQ3Q2Q1Q0

1↑111ФФФФ状态码加1

<74LS161功能表>

从74LS161功能表功能表中可以知道,当清零端CR=“0”,计数器输出Q3、Q2、Q1、Q0⽴即为全“0”,这个时候为异步复位功能。

当CR=“1”且LD=“0”时,在CP信号上升沿作⽤后,74LS161

输出端Q3、Q2、Q1、Q0的状态分别与并⾏数据输⼊端D3,D2,D1,D0的状态⼀样,为同步置数功能。

⽽只有当

CR=LD=EP=ET=“1”、CP脉冲上升沿作⽤后,计数器加1。

74LS161还有⼀个进位输出端CO,其逻辑关系是

CO=Q0·Q1·Q2·Q3·CET。

合理应⽤计数器的清零功能和置数功能,⼀⽚74LS161可以组成16进制以下的任意进制分频器。

74LS161

图2 集成计数器的级联 (2)用反馈清零法获得任意进制计数器 由于集成计数器一般都设置有清零端和置数端,而且无论是 清零还是置数都有同步和异步之分。例如,4 位二进制同步加法计 数器74LS163的清零和置数均采用同步方式,而有的只有异步清 零功能。获得任意进 制计数器的方法很多,本书只介绍用反馈清 零法获得任意进制计数器。 如用74LS16l构成九进制加法计数器,九进制计数器(N=9) 有9个状态,而74LS161在计数过程中有16个状态(M=[6), 正常循环从0000到1111,要构成九进制加法计数器,此时必须设 法 跳过M-N(16 - 9=7)个状态。74LS161具有异步清零功能, 在其计数过程当中,不管它的输出处于哪 一状态,只要在异步清 零输人端加一低电平电压,使CR=0,74LS161的输出会立即从 那个状态回到0000状 态。清零信号(CR=0)消失后,74LS161 又从0000状态开始重新计数。 如图3(a)所示的九进制计数器,就是借助74LS161的异步 清零功能实现的。如图3(b)所示电路是九进 制计数器的主循环 状态图。

பைடு நூலகம்

计数器的种类很多,按其进制不同分为二进制计数器、十 进制计数器、N进制计数器;按触发器翻转是否 同步分为 异步计数器和同步计数器;按计数时是增还是减分为加法 计数器、减法计数器和加/减法(可逆 )计数器。下面首 先介绍二进制计数器。 1.集成二进制计数器74LS161 74LS161是4位二进制同步加法计数器,除了有二进 制加法计数功能外,还具有异步清零、同步并行置数 、 保持等功能。74LS161的逻辑电路图和引脚排列图如图1 所示,CR是异步清零端,LD是预置数控制端,D0 ,D1, D2,D3是预置数据输人端,P和T是计数使能端,C是进 位输出端,它的设置为多片集成计数器的级 联提供了方 便。 74LS161的功能表如表1所示。由表可知,74LS161 具有以下功能。

74ls161引脚图与管脚功能表资料

74ls161引脚图与管脚功能表资料

74LS161是常用的四位二进制可预置的同步加法计数器,他可以灵活的运用在各种数字电路,以及单片机系统种实现分频器等很多重要的功能,:

<74ls161引脚图>

管脚图介绍:

时钟CP和四个数据输入端P0~P3

清零/MR

使能CEP,CET

置数PE

数据输出端Q0~Q3

以及进位输出TC. (TC=Q0·Q1·Q2·Q3·CET)

输入输出

C R CP L

D EP ET D3D2D1D0Q3 Q2Q1Q0

0 Ф Ф Ф Ф Ф Ф Ф Ф 0 0 0 0

1 ↑ 0 Ф Ф d c b a d c b a

1 ↑ 1 0 Ф Ф Ф Ф Ф Q3 Q2Q1Q0

1 ↑ 1 Ф 0 Ф Ф Ф Ф Q3 Q2Q1Q0

1 ↑ 1 1 1 Ф Ф Ф Ф 状态码加1

<74LS161功能表>

从74LS161功能表功能表中可以知道,当清零端CR=“0”,计数器输出Q3、Q2、Q1、Q0立即为全“0”,这个时候为异步复位功能。

当CR=“1”且LD=“0”时,在CP信号上升沿作用后,74LS161输出端Q3、Q2、Q1、Q0的状态分别与并行数据输入端D3,D2,D1,D0的状态一样,为同步置数功能。

而只有当CR=LD=EP=ET=“1”、CP脉冲上升沿作用后,计数器加1。

74LS161还有一个进位输出端CO,其逻辑关系是CO= Q0·Q1·Q2·Q3·CET。

合理应用计数器的清零功能和置数功能,一片74LS161可以组成16进制以下的任意进制分频器。

74LS161真值表

74LS161为二进制同步计数器,具有同步预置数、异步清零以及保持等

功能。

一、74LS161引脚图

二、74LS161的功能表

输入输出

注:Qcc= CTr∙Q0∙Q∣∙Q2∙Q3

从功能表的第一行可知,当而=0 (输入低电平),则不管其他输入端(包括CP端)状态如何,四个数据输出端Q A、Q B、Q C、Q D全部清零。

由于这一清零操作不需要时钟脉冲CP配合(即不管CP是什么状态都行),所以行为异步清零端,且低电平有效,也可以说该计数器具有“异步清零”功能。

从功能表的第二行可知,当而=1且方=0时•,时钟脉冲CP上升沿到达,四个数据输出端Q A、Q B、Q C、Q D同时分别接收并行数据输入信号a、b、

c、do由于这个置数操作必须有CP上升沿配合,并与CP上升沿同步,所以称那么该芯片具有“同步置数”功能。

从功能表的第三行可知,当说=赤=1, CTr=CTp=l时,则对计数脉冲CP实现同步十进制加计数;而从功能表的第四行又知道,当赤=说= 1时,只要CTr和ENP中有一个为0,则不管CP状态如何(包括上升沿), 计数器所有数据输出都保持原状态不变。

因此,CTr和CTp应该为计数控制端,当它们同时为1时,计数器执行正常同步计数功能;而当它们有一个为。

时,计数器执行保持功能。

另外,进位输出Qcc= CTrQQQ∙Q3表明,进位输出端仅当计数控制端CTr=l且计数器状态为15时它才为1,否则为0。

计数器74LS161功能及其应用PPT课件

灵活的计数模式

74LS161具有异步清零和异步 置数功能,可以在不同的计数 模式下工作,满足多种计数需 求。

易于扩展

74LS161计数器具有多个输出 端和使能端,便于与其他逻辑 器件连接,实现更复杂的计数 系统。

低功耗

74LS161计数器在待机状态下 功耗较低,延长了设备的整体

使用寿命。

缺点

医疗保健

随着医疗保健行业的不断发展,计数器74ls161将在医疗 保健领域发挥重要作用,为医疗设备和仪器的精准控制提 供支持。

市场前景分析

01

市场需求

随着工业自动化、智能家居、医疗保健等领域的不断发展,计数器

74ls161的市场需求将会持续增长。

02 03

竞争格局

目前市场上已经有多家企业涉足计数器74ls161领域,未来市场竞争将 更加激烈。企业需要不断提高技术水平和产品质量,以获得更多的市场 份额。

输入信号抖动敏感

74LS161计数器对输入信号的抖动较 为敏感,需要保证输入信号的稳定性 以避免计数误差。

计数范围有限

74LS161计数器的最大计数值为9, 对于需要更大计数值的应用场景不够 适用。

功耗较高

相对于其他类型的计数器,74LS161 的功耗较高,可能会对设备散热产生 一定压力。

集成度较低

数器单元会被清零。

当异步置数端(LD)输入置数信 号时,74ls161内部的四个计数 器单元会被同时置为数据输入端 (D0-D3)所输入的数据值。

03 计数器74ls161的应用

在数字系统中的应用

数字逻辑设计

74LS161计数器具有2位同步置数、异步清零及同步置数、异步清零、同步置 数及异步清零功能,适用于各种数字逻辑设计,如时序逻辑电路、二进制数计 算等。

74LS161中文资料_数据手册_参数

• POST OFFICE BOX 655303 DALLAS, TEXAS 75265

7

SN54S162, SN74S162 SYNCHRONOUS 4-BIT COUNTERS

SDLS060 – OCTOBER 1976 – REVISED MARCH 1988

8

• POST OFFICE BOX 655303 DALLAS, TEXAS 75265

• POST OFFICE BOX 655303 DALLAS, TEXAS 75265

11

SN54160 THRU SN54163, SN74160 THRU SN74163 SYNCHRONOUS 4-BIT COUNTERS

SDLS060 – OCTOBER 1976 – REVISED MARCH 1988

SDLS060 – OCTOBER 1976 – REVISED MARCH 1988

18

• POST OFFICE BOX 655303 DALLAS, TEXAS 75265

SN54160 THRU SN54163, SN54LS160A THRU SN54LS163A,

SN74160 THRU SN74163, SN74LS160A THRU SN74LS163A, SYNCHRONOUS 4-BIT COUNTERS

• POST OFFICE BOX 655303 DALLAS, TEXAS 75265

3

SN54160, SN54162, SN74160, SN74162 SYNCHRONOUS 4-BIT COUNTERS

SDLS060 – OCTOBER 1976 – REVISED MARCH 1988

D

74ls161引脚图与管脚功能表资料

74ls161引脚图与管脚功能表资料74LS161是常用的四位二进制可预置的同步加法计数器,他可以灵活的运用在各种数字电路,以及单片机系统种实现分频器等很多重要的功能,:<74ls161引脚图>管脚图介绍:时钟CP和四个数据输入端P0~P3清零/MR使能CEP,CET置数PE数据输出端Q0~Q3以及进位输出TC. (TC=Q0·Q1·Q2·Q3·CET)输入输出CRCPLDEP ETD3D2D1D0Q3Q2Q1Q00 Ф Ф Ф Ф Ф Ф Ф Ф 0 0 0 01 ↑ 0 Ф Ф d c b a d c b a 1 ↑ 1 0 Ф Ф Ф Ф ФQ3Q2Q1Q0 1 ↑ 1 Ф 0 Ф Ф Ф Ф Q Q Q Q0<74LS161功能表>从74LS161功能表功能表中可以知道,当清零端CR=“0”,计数器输出Q3、Q2、Q1、Q0立即为全“0”,这个时候为异步复位功能。

当CR=“1”且LD=“0”时,在CP信号上升沿作用后,74LS161输出端Q3、Q2、Q1、Q0的状态分别与并行数据输入端D3,D2,D1,D0的状态一样,为同步置数功能。

而只有当CR=LD=EP=ET=“1”、CP脉冲上升沿作用后,计数器加1。

74LS161还有一个进位输出端CO,其逻辑关系是CO= Q0·Q1·Q2·Q3·CET。

合理应用计数器的清零功能和置数功能,一片74LS161可以组成16进制以下的任意进制分频器。

精品文档word文档可以编辑!谢谢下载!。