通用可编程接口IP核的设计与实现

基于FPGA的USB接口IP核设计

基于FPGA的USB接口IP核设计USB(通用串行总线)作为一种外设连接技术,是计算机外设连接技术的重大变革,USB具有速度快、通用性好、扩展性强、功耗低、稳定、易开发等众多优点,在实践中获得了广泛的应用,逐步成为PC机的一种标准接口。

USB接口控制芯片是实现USB设备与主机建立通信所必须的芯片,目前国内的USB开发者所采用的芯片都是由国外的芯片商所提供,如Cypress、NEC、Motorola等大的IC设计公司,价格较贵。

由于USB的广泛应用,国内外众多科研机构和集成电路设计公司都把目光投向USB这项具有广阔市场前景的技术。

USB内核(USB Core)是USB接口控制芯片的关键模块,设计一个稳定、高速的USB内核更是芯片成功推向市场的前提。

1 USB通信原理USB通信逻辑上分成了3层:信号层、协议层和数据层。

信号层用来实现在USB 设备和主机的物理连接之间传输位信息流的信息。

逻辑层用来实现在USB设备和USB主机端的协议软件之间传输包字节流的信息,它们在信号层被编码成NRZI位信息后传送出去。

数据传输层用来实现在USB主机端的客户端驱动程序和设备端的功能接口之间传输有一定意义的信息,这些信息在协议层被打包成包格式。

1.1 传输的基本单元包(Packet)是USB系统中信息传输的基本单元。

结构,如图1所示,根据USB 规范,包的类型有:令牌包、数据包、握手包和专用包。

USB总线操作(通讯过程)都可以归结为3种包的传输:令牌包、数据包和应答包。

任何操作都是从主机开始的,主机以预先排好的时序,发出一个描述操作类型、方向、外设地址以及端点号,称之为令牌包Foken Packet。

然后由在令牌中指定的数据发送者发出一个数据包Data Packet或者报告它没有数据可以传输。

而数据的目的地一般要以一个应答包Handshake Packet做出响应表明传输是否成功。

1.2 事务处理事务处理(Transaction)是指USB总线上数据信息的一次接收或发送的处理过程。

can总线控制器的接口ip核设计与实现

发送,最高七位不能全为“隐性”。

图2.3仲裁场结构(3)控制场控制场是由保留位和数据长度代码构成。

其中保留位必须是“显性",作为扩展时使用,数据长度代码是待发送数据的字节数量,接收器认可“显性’’与“隐性”的全部组合m】。

仲裁场-●控制场■『效据场陪或CRCⅨaa&D“:1DLcOr'm场保留位数据长度代码图2.4控制场结构数据长度代码是四位,其中d代表显性,r代表隐性。

对其数据字节进行编码后的真值表如图2.5所示。

一…...数据字节的r费眨据长度·代码个数DLC3D●Q亡HC1Dl∞odddd1ddd2ddd3dd4drdd5dd6da7dr8ddd图2.5数据长度代码真值表(4)数据场数据场由数据帧里的发送字节构成,最多可以发送八个字节,字节从最高位开始发送。

(5)CRC场CRC场由CRC序列和CRC界定符构成。

其中CRC序列有15位,是由循环冗余效验模块生成,紧跟其后是隐性的CRC界定符。

10图2.8远程帧结构2.3.3错误帧错误帧是由错误标志和错误界定符两个场构成。

错误标志有两种不同的表现形式:主动错误标志(Activeerrorflag)和被动错误标志(Passiveerrorflag),其中主动错误标志由六个“显性’’位组成,被动错误标志由六个“隐性"位组成嘲【18】【40】。

图2.9错误帧结构错误界定符由八个“隐性”位组成。

当开始传送错误标志后,每个节点都会发送“隐性"位,并监视总线,直到检测到“隐性"位为止,然后发送剩余的“隐性’’位【习。

2.3.4过载帧过载帧是由过载标志和过载定界符构成。

过载帧只能在帧间间隙才产生,因此可以通过这种方式来区分过载帧和错误帧。

图2.10过载帧结构其中过载界定符与错误界定符的工作过程一致,这里就不做介绍。

122.3.5帧间空间帧间空间是由间隙场和总线空闲场构成。

无论是数据帧还是远程帧,要想与其他帧分开,是通过帧间空间来实现的。

当被动错误的节点使用于之前的报文发生器时,帧间空间包括间隙、挂起传送(SUSPENDTRANSMISSIoN)、总线空闲。

uart16550IP核的设计与FPGA的实现

图2.1UART16550基本结构图

下面将介绍整个UART工作原理。

CPU通过CPU接口模块设定整个UART初始状态,如是奇校验还是偶校验、波特率数值和停止位的位数。波特率发生器分频出设定好的波特率并以设定的波特率控制发送和接收模块以达到发送和接收的同步。发送数据时CPU将待发送的并行数据输入发送FIFO,在发送FIFO中有16字节的缓存以减少发送数据时CPU中断次数。发送模块将并行数据转化为串行数据并在数据位前加上起始位后面加上奇偶校验位和停止位,通过串行发送方式发送给外设。接收模块会时刻监视串行输入端口,一旦检测到电平转换(即起始位)接收模块会马上进行状态判断并接收数据,通过奇偶校验和启停位检测有效的排除掉错误数据,然后将启停位和校验位去除,剩余的数据位发送到发送FIFO,并通知CPU在CPU接口模块接收的数据,最后数据就被传输至中央处理区。

3.4波特率发生模块

波特率发生器主要功能就是从输入时钟转换出需要的波特率clk。波特率发生器实际就是一个分频器,通过设计一个计数器,使工作频率很高的系统时钟分频为所需的波特率时钟。之所以需要设定这样一个时钟是因为收发设备间的时钟会积累导致接收数据不正确。而波特率发生器就是专门产生一个远远高于波特率的本地时钟信号对输入RXD不断采样以保证接收器和发送器保持同步。

矩阵式键盘接口通用IP核的设计与实现

化

工

自 动 化

及 仪

表

第 3 8卷

矩 阵 式 键 盘 接 口通 用 l 的设 计 与 实 现 P核

张俊 涛 张 弛

( 西 科 技 大学 电气 与 信 息 工程 学 院 , 安 70 2 ) 陕 西 10 1

摘

要

设 计 并 实现 一 种 基 于 F G 的 矩 阵 式键 盘 接 口 I PA P核 。 与传 统 的 软 件 扫 描 编 程 方 式相 比 。 用 应

o 厂o o ,— _ _ . 】 。I D 。 X

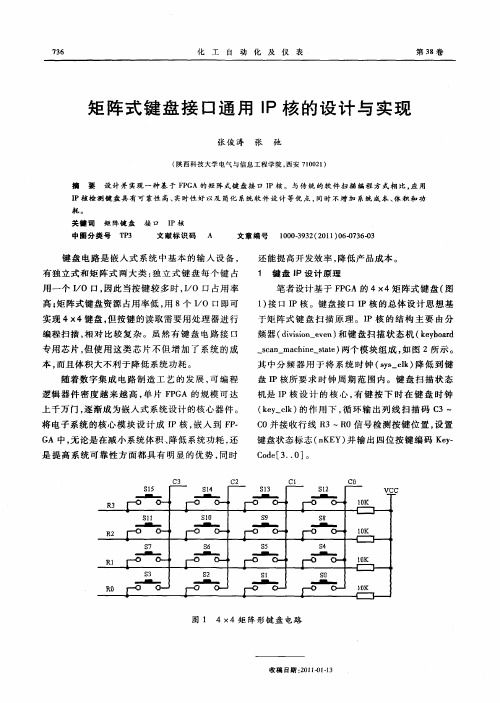

图 1 4×4矩 阵形 键 盘 电路

收 稿 日期 : 0 1 ) .3 2 1 41 1

第 6期

张俊 涛 等 . 阵 式 键 盘 接 口通 用 I 矩 P核 的设 计 与 实 现

; … : … ad sa …c b r c n mah o— — … e— tt a

s 7

■●

S 6

一

S 5

■■

S 4

-

R ro 1 _

S 3 -

ro .

S 2 -

。 厂 。

Sl ・_■ I_ -

’ 厂o o r 1 _ 一 l ’ 0 — K

S0 -_■■・-

R r。 o r。 o l - _

厂 。

上千万 门 , 逐渐 成 为嵌入 式系统设 计 的核心 器件 。

将 电子 系统 的核心 模块 设 计 成 I P核 , 入 到 F . 嵌 P

G 中, 论是在 减小 系统体积 、 低系统 功耗 , A 无 降 还

是 提高 系统 可靠 性 方面 都具 有 明显 的优 势 , 同时

C3 S1 5

XilinxISE软件功能简介与IPCore(IP核)

Xilinx ISE软件功能简介与IP Core(IP核)1 Xilinx ISE软件简要介绍Xilinx是全球领先的可编程逻辑完整解决方案的供应商,研发、制造并销售应用范围广泛的高级集成电路、软件设计工具以及定义系统级功能的IP (Intellectual Property)核长期以来一直推动着FPGA技术的发展。

Xilinx的开发工具也在不断升级,集成了FPGA开发需要的所有功能,其主要特点有:①包含了Xilinx新型Smart Compile技术,可以将实现时间缩减2.5倍,能在最短的时间内提供最高的性能,提供了一个功能强大的设计收敛环境;②全面支持最新FPGA系列器件;③集成式的时序收敛环境有助于快速、轻松地识别FPGA设计的瓶颈;④可以节省一个或多个速度等级的成本,并在逻辑设计中实现最低的总成本。

Foundation Series ISE具有界面友好、操作简单的特点,再加上Xilinx的FPGA芯片占有很大的市场,使其成为非常通用的FPGA工具软件。

ISE作为高效的EDA设计工具集合,与第三方软件扬长避短,使软件功能越来越强大,为用户提供了更加丰富的Xilinx平台[19]。

2 Xilinx ISE软件功能简介ISE 的主要功能包括设计输入、综合、仿真、实现和下载,涵盖了FPGA开发的全过程,从功能上讲,其工作流程无需借助任何第三方EDA软件。

设计输入:ISE提供的设计输入工具包括用于HDL代码输入和查看报告的ISE文本编辑器,用于原理图编辑的工具ECS,用于生成IP Core Generator,用于状态机设计的StateCAD以及用于约束文件编辑的Constraint Editor等。

综合:ISE的综合工具不但包含了Xilinx自身提供的综合工具XST,同时还可以内嵌Mentor Graphics公司的LeonardoSpectrum和Synplicity公司的Synplify,实现无缝链接。

USB 1.1主机控制器IP核设计与实现

文 章 编 号 :0 2 8 3 ( 0 7 2 — 1 9 0 文 献 标 识 码 : 中 图分 类号 :1 O ~ 1 0— 3 12 0 )2 0 0 — 4 A 1P 2 3

l 引 言

U B是 U ie a S r lB s的简 写 , 1 9 S nv r l e a u s i 于 9 4年 底 由 C m. o

ZHANG e- i ZHANG u . sg a d i lm e tto f US 11 h s o tolr I c r . m p t r En i e rn n M |l n, J nDe in n mpe nai n o B . o t c n r l P o eCo ue gn e ig a e d

即插 即用 、 价 、 选 择 的 多 种 速 度 模 式 以及 广 泛 的 软 硬 件 支 廉 可 持 等 特 点 『 日益 成 为 通 用 的 串行 接 口总线 标 准 。 l _ , 基于“ 芯” 龙 1的 3 2位 SC是 一 款 遵循 G , 84 o B I1 2 0系列 标 1

2 rd a nvrt, hns cd m cecsB in 0 0 0 C ia . a ut U iesy C ieeA a e y o S i e ,e ig 10 8 ,hn G e i f n j

E — i :h n me l @g i c n — ma l z a g i n mal o i .

张美林 , 章 军

Z HANG i l 1 HANG J n Me—i , Z n2 u 1中 国科 学 院 计算 技术 研 究 所 , 京 10 8 . 北 000

2中 国科 学 院 研究 生 院 , 京 10 8 . 北 000

ቤተ መጻሕፍቲ ባይዱ

基于SoC可重构密码算法IP核接口电路设计与实现

ba e n So s do C

ZHAN G — u , W ANG in y Lu g o Ja — u

( stt f lcr ncT c n lg , P A nomainE gn eigUnv ri , Z e g h u4 0 0 , Chn ) I tueo e t i e h oo y L I fr t n iern ie sy h n z o 5 0 4 ni E o o t ia

1 微控制器 I . 1 P核

微 控 制 器 是 基 于 网 上 源 码 公 开 的 MC .0 l S85 i P核 改 进 型

cnrl r nt a dcn g rbe ihr loi m oe wi e t rl e n t n , b rvdn eea l b sdo u l o t l i n o f ua l c e ag rh I c r, t t ii e e tdf c o s ypo iigt xmpe ae nd a oeu ) i p t P h h rn r a u i h

SpaceWire总线节点IP核的设计与验证

SpaceWire总线节点IP核的设计与验证SpaceWire总线是一个用于卫星、航天器和卫星地面通信的高速串行通信接口。

它是由欧洲空间总署(ESA)开发的一种通信协议,广泛应用于航天领域。

SpaceWire总线节点IP核是用于实现SpaceWire总线通信功能的重要组成部分。

本文将介绍SpaceWire总线节点IP核的设计与验证。

首先,我们需要了解SpaceWire总线的基本特性。

SpaceWire总线采用的是差分传输方式,具有较高的通信速率,最高可达到200Mbps。

它支持点对点和多点连接,可同时传输双向数据。

此外,SpaceWire总线还具备周期性和非周期性传输的能力,以及错误检测和校正的功能。

这些特性使SpaceWire总线成为航天器和地面设备之间可靠通信的理想选择。

在设计SpaceWire总线节点IP核时,我们需要考虑以下几个方面。

首先,根据具体应用需求,确定IP核的输入输出接口。

通常,SpaceWire总线节点IP核的输入接口包括数据输入、时钟输入和控制信号输入,输出接口包括数据输出和状态输出。

其次,需要设计合适的硬件架构和电路结构来支持高速的差分传输。

这包括差分收发器的设计和实现,以及时钟同步和数据流控制的方式选择等。

最后,需要进行完整性验证和性能测试,确保IP核的正确性和可靠性。

在验证SpaceWire总线节点IP核时,我们可以采用模块级验证和系统级验证相结合的方式。

模块级验证主要是对每个功能模块进行单元测试,确保其功能正常。

例如,可以对差分收发器、时钟同步器和数据流控制模块等进行验证。

系统级验证则是对整个IP核进行集成测试,验证不同模块之间的协同工作和总线通信功能。

在验证过程中,可以使用仿真工具或者实际硬件进行测试。

除了验证IP核的正确性,我们还需要进行性能测试。

性能测试可以评估IP核在运行时的数据传输速率、延迟和吞吐量等指标。

通常,可以通过向IP核输入不同大小的数据包,并记录传输时间和传输成功率来进行性能测试。

USB2.0设备控制器IP核的设计与实现

备 控 制器 的 I P核 ,为高 速 US B设 备 的开 发 打 下 了基 础 。可 以用 于 S C集 成 中 。 O

关键 词 :US B;设 备控 制 器 :I P核 ;协 议层

De i n a d I plm e t to f a Hi h— s e B v c n r le P Co e sg n m e n a in O g pe d US De ie Co t o l r I r

接 外 嗣 设 备 的首 选 接 口 。

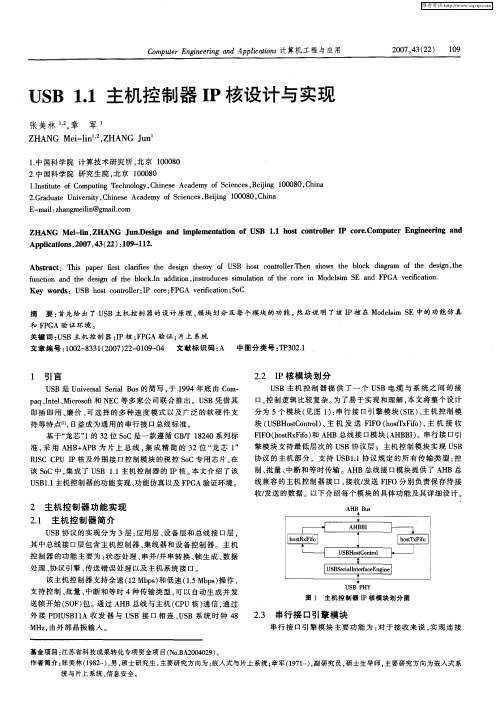

fc )接 口 、协 议 层 ( r tc l a e ,简称 为 P ) ae Pooo L yr L 、存 储 器 管

理单 元 ( mo yMa a e n i) 和 FI 5个 模 块 ,其 系 Me r n g me tUnt FO 统 框 图如 图 1所 示 。

0 引 言

通 用 串行 总 线 ( i ra S r l u , 简称 为 US ) 是 一 Unv sl e i s e aB B

种 快速 、双 向 、 同步 可 动 态监 测 的串 行接 口,从 其 诞 生发 展 到

者 把 设 备要 传 给 主机 的数 据 ( 放 在 F F 区 )组 装 成 协 议 所 已 IO 规 定 的分 组 形 式 ,再通 过 一 个 差 分驱 动 电路 经过 串行 化 、位 填 充 和 N Z 编码 后 输 出 到 US R I B总 线上 。

Ab ta t A e is o o t b e ma s s o a e d v c s a e a ii g d o t fe tv up o tf o US . 0 r c : s re fp ra l s t r g e i e r rsn ue t he e fc i e s p r r m B2 n e f c o t p ca e l r so a y t s u e fe s o u e,h g 一 p e i h一 s e d,lw o r n o d rt e he r q ie e to i h s e d d t r n a to o p we .I r e o me tl e u r m n fh g p e a a ta s c i n,a d v c o t o l rI o e e ie c n r l P c r e b sd o a e n USB2 0 p o o o sde i n d,wh c ke t e se o d v l p h g . r t c li sg e ih ma s i a ir t e eo i h— s e d US e ie Al o,t e I o e c n b n e r t d i p e B d vc . s h P c r a e i t g a e n SOC d sg a i . e i n e sl y Ke r s u i e s ls r lb s d v c o r l r I c r ; p o o o a e y wo d : n v r a e i u ; e ie c nto l ; P o e a e r t c ll y r

fpga中ip核的作用

fpga中ip核的作用FPGA中IP核的作用在FPGA(Field-Programmable Gate Array)设计中,IP (Intellectual Property)核是一种预先设计好的模块,可以在FPGA 中进行复用。

它们是经过验证和优化的硬件功能模块,可以直接集成到FPGA设计中,以提供特定的功能和性能。

IP核在FPGA设计中起到了至关重要的作用。

它们可以加快设计开发过程,提高设计的可靠性和稳定性,同时降低功耗和成本。

下面将介绍IP核在FPGA设计中的几个主要作用。

1.功能扩展:IP核可以为FPGA设计提供各种功能扩展,例如数字信号处理(DSP)、存储控制器、通信接口、图像处理、加密解密等。

通过使用这些现成的IP核,设计者可以快速实现复杂的功能,减少设计周期。

2.性能优化:IP核经过了精心的设计和验证,可以提供高性能的硬件加速功能。

通过使用高效的IP核,设计者可以实现更高的运算速度和吞吐量,满足实时性要求,提高系统性能。

3.资源节约:IP核的复用性使得设计者可以避免重复开发相同的功能模块,节省了宝贵的设计资源和时间。

此外,由于IP核是经过验证和优化的,可以更好地利用FPGA的资源,减少功耗和成本。

4.可靠性保证:IP核经过了严格的验证和测试,可以提供高可靠性的功能模块。

设计者可以信赖这些经过验证的IP核,降低设计中的错误率,提高系统的可靠性。

5.易用性:IP核通常提供了友好的接口和文档,使得设计者可以方便地集成到FPGA设计中。

设计者只需要了解IP核的功能和接口,而无需深入了解底层的硬件实现细节。

然而,在使用IP核时也需要注意一些问题。

首先,IP核的质量和可靠性取决于供应商。

因此,在选择IP核时,设计者应该选择有良好声誉的供应商,并认真评估其性能和可靠性。

此外,由于IP核是现成的模块,可能无法完全满足特定的设计需求。

在这种情况下,设计者可能需要自行定制IP核,以满足特定的性能和功能要求。

基于SOPC的触控屏控制器IP核设计与实现

( 阳理 工 大 学 信 息科 学 与 工 程 学 院 , 宁 沈 阳 10 1 ) 沈 辽 10 5

摘 要 :介 绍 一 款 基 于 S C的 T T— C 触控 屏控 制 器 I OP F LD P核 的设 计 与 实现 。采 用 Vei gHDL作 控 制 器 的模 块 设 计 , ro l

C I uj g MA Pn—un U -n , igq a X i

(c olfI om t nS i c n n ier g S ey gLgn nvr t, hn ag 10 1 , hn ) Sh o o n r ai c neadE gnei , hn a i gU i sy S ey 10 5 C ia f o e n n o ei n

关 键 词 :S C;控 制 器 ;I OP P核 ;触 控 屏 ;Nis oⅡ

中 图分 类 号 : N 7 T 2 6 T 2 ;P 1

文 献标 识 码 : A

文章 编 号 :1 7 — 2 6 2 1 ) 4 0 6 — 4 64 6 3 (02 1— 16 0

De i n a mplm e t to ft P o e us d f r a t u h pa lc n r le s d n sg nd i e n a i n o he I c r e o o c ne o t o l r ba e o S oPC

s se t e in o e d s l y d v ra d c n r lmo u e i o lt d o o r w t h mb d e OP e eo me t y t ma i d s f h ip a r e n o t d l sc mpe e n a b ad i t e e e d d S C d v lp n c g t i o h to s a d p o i e oh te h r w r n ot a ed sn F n l , h oo r l t p ss o do e tu h p n l se p ce . o l , n r v d d b t a d a ea d s f r e i . i al t e c l u f r e h we nt c a e x e t d h w y u si h o a T ec n r l r P c r , c n v ra n o ai l , a c f t a p iain v l ea d c n b s ds e i l. h o t l o e mu h u ie s l d c mp t e h s oeI a b mu h o s p l t a u n a e u e p cf y i c o y

基于FPGA的通用接口总线(GPIB)控制器的IP核设计

19科技创新导报 Science and Technology Innovation Herald I T 技 术引言随着计算机技术、网络技术与通信技术的高速发展与广泛应用,这必将给网络时代的测试仪器和测试技术带来革命性变化,“网络就是仪器”确切的概括了测试和仪器的网络化发展趋势。

组建网络化测试系统不仅能实现更多的资源共享,降低组建系统的费用,还可以提高测试系统的功能,拓宽其应用的范围。

本文采用FPG A芯片实现GPI B控制器的I P 核设计完成芯片TMS 9914的产权自主化。

1 GPIB控制器方案设计GPIB(General Purpose Interface Bus,通用接口总线)使自动化测试仪器的互联有了统一的标准,极大地推动了自动测试技术的发展。

由于GPIB总线为并行外总线,不仅保持了并行总线传送速度快、有效数据速率高的优点,而且增强了驱动能力, 通讯距离可达20m,并有良好的抗干扰能力和通用性,总线上最多可挂接15台设备并且传输速度可以达到8Mbit/s,因此有着良好的应用前景[1][2],其自动测试系统组建图如图1所示。

GPIB控制器IP核设计采用模块化思想进行,设计主要模块包括:与GPIB母线通信的接口功能模块、多线消息译码器以及数据通路模块。

接口功能状态机模块设计包括八个小模块(如源方挂钩、受方挂钩等),并采用VHDL语言对各个小模块进行编程实现,最后调用各个子模块并用原理图的方式进行状态机顶层模块设计,并在Synplify以及Q uartusⅡ平台下进行分析和仿真。

对数据通路的设计也采用同样的方式,先对各个子模块进行设计,然后进行整体设计。

最后调用状态机顶层模块、数据通路顶层模块与多线消息译码电路模块等进行GPIB控制器IP核的顶层设计。

完成整个IPCore设计后,通过J T AG 下载方式将C o r e 下载到选定的F P G A 专用开发套件(ACEX1K30QC208)芯片,从而得到一个实体化的GPIB控制器。

嵌入式系统开发平台——蓝牙基带数据处理IP核的设计与实现的开题报告

嵌入式系统开发平台——蓝牙基带数据处理IP核的设计与实现的开题报告一、研究背景嵌入式系统是指将计算机系统嵌入到其它产品中,为其提供特定的功能。

随着人们对无线通信和蓝牙技术的日益需要,嵌入式系统的发展得到了空前的推进。

嵌入式系统中,芯片的核心是IP核,这是符合一定标准的硬件模块。

IP核的设计和实现直接决定了嵌入式系统的性能和稳定性。

本课题研究的是蓝牙基带数据处理IP核的设计与实现。

蓝牙基带数据处理IP核是蓝牙通信的核心部分,通过高效的数据处理,使蓝牙通信更加快速稳定。

因此,蓝牙基带数据处理IP核的高效设计和实现非常重要。

二、研究内容本课题研究的内容主要包括以下方面:1. 蓝牙基带数据处理IP核的原理与特点研究;2. 蓝牙基带数据处理IP核的设计方法研究;3. 蓝牙基带数据处理IP核的功能测试和性能优化研究。

三、研究目标本课题的研究目标主要包括以下方面:1. 系统地学习蓝牙基带数据处理IP核的原理与特点,掌握蓝牙通信的基本知识;2. 研究蓝牙基带数据处理IP核的设计方法,设计出高效稳定的IP 核;3. 对设计好的蓝牙基带数据处理IP核进行功能测试和性能优化,验证其可行性和优越性。

四、研究意义本课题的研究对于嵌入式系统的发展有重要的意义。

具体包括:1. 推进蓝牙技术在嵌入式系统领域的应用和发展;2. 提高蓝牙基带数据处理IP核的设计和实现水平,进一步提高嵌入式系统的性能和稳定性;3. 为蓝牙产品的研发提供技术支持和参考依据。

五、研究方法本课题主要采用文献资料法和实验验证法。

通过文献资料法,深入了解蓝牙技术和蓝牙基带数据处理IP核的原理及特点,掌握相关设计方法;通过实验验证法,测试蓝牙基带数据处理IP核的功能和性能,进行优化改进。

六、可行性分析本课题的研究方案具有可行性。

首先,蓝牙技术在嵌入式系统领域已经得到广泛应用,需求稳定可靠的蓝牙基带数据处理IP核;其次,本研究所需要的技术和设备都已成熟,能够满足基本需要;最后,本研究旨在设计和优化蓝牙基带数据处理IP核,具有实际应用的意义。

基于FPGA的浮点运算器IP核的设计与实现

基于FPGA的浮点运算器IP核的设计与实现基于现场可编程门阵列(FPGA)的浮点运算器,是一种专门设计用于实现浮点数运算的IP核。

浮点运算器在科学计算、数字信号处理(DSP)、图像处理等领域中具有广泛的应用。

本文将探讨基于FPGA的浮点运算器IP核的设计与实现。

首先,我们需要确定浮点运算器的功能要求和性能指标。

常见的浮点运算器包括加法器、乘法器和除法器,它们能够进行浮点数的加法、乘法和除法运算。

浮点运算器的性能指标包括浮点数位数、运算精度、时钟频率、吞吐量、功耗等。

然后,我们可以选择合适的FPGA芯片进行设计。

不同的FPGA芯片具有不同的资源和性能特点,我们需要根据浮点运算器的功能需求和性能指标,选择具备足够资源和性能的FPGA芯片。

接下来,我们需要进行浮点运算器的架构设计。

浮点运算器的架构通常分为两个主要部分:浮点数运算单元和控制单元。

浮点数运算单元包括加法器、乘法器和除法器,它们实现具体的浮点数运算操作。

控制单元用于控制浮点数运算的流程和时序。

在浮点数运算单元的设计中,我们需要选择合适的浮点数格式。

常见的浮点数格式有IEEE754和自定义浮点数格式。

IEEE754浮点数格式是最常用的浮点数表示方法,它包括单精度浮点数(32位)、双精度浮点数(64位)和扩展精度浮点数(80位)。

自定义浮点数格式可以根据具体应用需求设计,例如定点数格式、定点数加浮点数格式等。

浮点运算器的设计可以采用各种硬件实现方法,如组合逻辑电路、查找表、乘法器阵列和流水线等。

我们需要根据浮点数运算的复杂度和性能要求选择合适的实现方法。

对于较复杂的浮点数运算,可以采用流水线架构来实现并发计算,提高性能和吞吐量。

在控制单元的设计中,我们需要确定浮点数运算的流程和时序。

控制单元可以采用状态机的方式实现,它根据具体的浮点数运算操作,生成相应的控制信号,控制浮点数运算单元的工作状态和时序。

最后,我们需要进行浮点运算器的验证和测试。

验证和测试是设计中非常重要的环节,它可以帮助我们发现并修复设计中的错误和缺陷。

anlogic fpga乘法器ip核的用法

anlogic fpga乘法器ip核的用法FPGA(字段可编程门阵列)是一种灵活的硬件开发平台,它可以通过重构硬件电路来实现不同的应用。

ANLOGIC FPGA乘法器IP核是一种可配置的IP核,用于在FPGA中实现乘法操作。

下面将介绍ANLOGIC FPGA乘法器IP核的用法。

1. 添加IP核:首先,在FPGA开发环境中,添加ANLOGIC FPGA乘法器IP核。

可以通过工具栏或菜单中的选项找到IP核库,并选择乘法器IP核。

2. 配置IP核:一旦添加了乘法器IP核,您可以打开其配置界面。

在配置界面中,您可以设置乘法器的输入和输出位宽,以满足您的应用需求。

3. 连接IP核:接下来,您需要将乘法器IP核与其他模块或信号连接起来。

这可以通过FPGA 开发环境提供的拖放功能来完成。

确保在连接时将乘法器的输入和输出与所需的信号连接起来。

4. 编写顶层设计:在FPGA开发中,您需要编写顶层设计文件来实现所需的功能。

在顶层设计文件中,将乘法器IP核实例化,并将其连接到其他模块或信号。

5. 编译和仿真:在完成顶层设计后,编译整个设计,并进行仿真以验证乘法器的功能。

您可以使用FPGA开发环境中提供的仿真工具来执行仿真。

6. 下载到FPGA:一旦验证通过,您可以将设计下载到FPGA芯片中。

通过FPGA开发环境提供的下载工具,将设计编程到目标FPGA芯片上。

7. 调试和优化:在将设计下载到FPGA后,您可能需要进行调试和优化,以确保乘法器的性能和功能符合预期。

可以使用FPGA开发环境提供的调试工具来完成这些任务。

总结:ANLOGIC FPGA乘法器IP核是一种可配置的IP核,用于在FPGA中实现乘法操作。

通过添加、配置、连接和编程的步骤,可以将乘法器IP核集成到FPGA设计中。

在设计验证、下载和调试过程中,您可以确保乘法器的功能和性能满足预期。

ANLOGIC FPGA乘法器IP核的使用将大大简化乘法操作的实现过程,并提高了硬件设计的灵活性。

PCI Bridge芯片IP核的设计与仿真验证

PCI Bridge芯片IP核的设计与仿真验证PCI Bridge芯片是PCI技术的实现基础,使得不同的PCI设备可以进行完整的互联互通,并通过总线仲裁的方式高效管理总线资源,使整个数据传输系统高效稳定。

在本论文的研究中,对PCI Bridge芯片的实现技术和具体设计做了较为细致的分析和验证。

通过在Testbench中设置各种异常情况的出现来模拟现实情况,进行全面的仿真验证。

完成了PCI总线从接口IP核设计、综合和仿真。

关键字:PCI Bridge芯片IP核,设计,仿真验证第一章绪论1.1引言近年来,计算机技术和电子设备的不断发展,特别是各类CPU速度与效率的高,多核处理器的出现,多级高速缓冲的普遍采用等,这使得需要高速总线传送数据的需求日益增加,与此同时通过多总线结构让不同速度的设备可以挂在不同的总线上,以较低总线竞争,以此使得系统的效率速度大大提高。

在多总线结构中,Local Bus(局部总线)的发展最激动人心。

PCI总线就是目前应用最为广泛的,也是比较领先的高性能局部总线。

在结构上,PCI总线采用地址和数据总线二合一的复用结构、32/64位2种总线带宽、具有多处理器(Multi core processor)功能却又相对独立,同时与其他类别的总线联合工作的结构扩展功能;在电气性能指标上,PCI总线采用33/66MHz 两种主频、5.0/3.3 V两种电压;在通讯协议上,PCI总线采用Burst(猝发传输模式)为缺省模式。

PCI技术具有这么多高端性能,无疑在众多总线中具有压倒性的优势,成为PC 机局部总线和高速设备数据传输的首选。

PCI Bridge芯片是PCI技术的实现基础,使得不同的PCI设备可以进行完整的互联互通,并通过总线仲裁的方式高效管理总线资源,使整个数据传输系统高效稳定。

从应用角度看,PCI技术是计算机系统数据交互的基础,也是嵌入式设备和工业系统与微机系统互联的重要实现方式,研究PCI Bridge规范及其实现具有重要的理论和应用意义。

fpga中ip核的作用

fpga中ip核的作用FPGA(Field Programmable Gate Array)是一种可编程逻辑器件,它可以通过编程来实现不同的功能。

在FPGA中,IP核(Intellectual Property core)是一种可重用的模块,它可以被用来实现特定的功能,例如数字信号处理、图像处理、通信等。

IP核可以被看作是FPGA中的“黑盒子”,它可以被直接使用,而无需了解其内部实现细节。

IP核的作用在于简化FPGA设计的过程。

在FPGA设计中,通常需要实现一些常见的功能,例如乘法器、加法器、存储器等。

这些功能可以通过编写Verilog或VHDL代码来实现,但这需要设计者具备较高的技术水平。

而使用IP核,设计者可以直接将其插入到设计中,从而省去了编写代码的过程。

这不仅可以节省时间,还可以降低设计的难度和错误率。

另外,IP核还可以提高设计的可重用性。

在FPGA设计中,通常需要实现多个功能模块,这些模块可能会在不同的设计中被重复使用。

使用IP核,设计者可以将这些模块封装成IP核,从而方便在不同的设计中重复使用。

这不仅可以提高设计的效率,还可以降低设计的成本。

除了常见的功能模块,IP核还可以实现一些特定的功能。

例如,通信系统中常用的协议(如Ethernet、USB等)可以通过IP核来实现。

这些IP核通常由FPGA厂商或第三方开发商提供,设计者可以直接使用它们,从而简化设计过程。

总之,IP核是FPGA设计中不可或缺的一部分。

它可以简化设计过程,提高设计的可重用性,同时还可以实现一些特定的功能。

在FPGA设计中,设计者应该充分利用IP核,从而提高设计的效率和质量。

基于FPGA的USB接口IP核设计

基于FPGA的USB接口IP核设计USB(通用串行总线)作为一种外设连接技术,是计算机外设连接技术的重大变革,USB具有速度快、通用性好、扩展性强、功耗低、稳定、易开发等众多优点,在实践中获得了广泛的应用,逐步成为PC机的一种标准接口。

USB接口控制芯片是实现USB设备与主机建立通信所必须的芯片,目前国内的USB开发者所采用的芯片都是由国外的芯片商所提供,如Cypress、NEC、Motorola等大的IC设计公司,价格较贵。

由于USB的广泛应用,国内外众多科研机构和集成电路设计公司都把目光投向USB这项具有广阔市场前景的技术。

USB内核(USB Core)是USB接口控制芯片的关键模块,设计一个稳定、高速的USB内核更是芯片成功推向市场的前提。

1 USB通信原理USB通信逻辑上分成了3层:信号层、协议层和数据层。

信号层用来实现在USB设备和主机的物理连接之间传输位信息流的信息。

逻辑层用来实现在USB设备和USB主机端的协议软件之间传输包字节流的信息,它们在信号层被编码成NRZI位信息后传送出去。

数据传输层用来实现在USB主机端的客户端驱动程序和设备端的功能接口之间传输有一定意义的信息,这些信息在协议层被打包成包格式。

1.1 传输的基本单元包(Packet)是USB系统中信息传输的基本单元。

结构,如图1所示,根据USB规范,包的类型有:令牌包、数据包、握手包和专用包。

USB总线操作(通讯过程)都可以归结为3种包的传输:令牌包、数据包和应答包。

任何操作都是从主机开始的,主机以预先排好的时序,发出一个描述操作类型、方向、外设地址以及端点号,称之为令牌包Foken Packet.然后由在令牌中指定的数据发送者发出一个数据包Data Packet或者报告它没有数据可以传输。

而数据的目的地一般要以一个应答包Handshake Packet做出响应表明传输是否成功。

1.2 事务处理事务处理(Transaction)是指USB总线上数据信息的一次接收或发送的处理过程。

IEEE 1394b VersaPHY的IP核设计与实现

IEEE 1394b VersaPHY的IP核设计与实现朱榆涵;邵洪峰;伊小素;龙映雪【摘要】Implementations of VersaPHY IP core is presented. According to VersaPHY protocol, we analyse the VersaPHY labels, packages and register, and complete the design of VersaPHY IP core. In the Altera Quartus II development platform, combining with the Verilog HDL language and its own IP CORE realizes the reception and transmission of packets addressed by VP-Label (read request, read response packet, a write request, write response packets) . Finally we use SignalTap II logic analyzers which is provided by Quartus II integrated development environment to verify , the results show the functions of VersaPHY of IP core is implemented.%文章提出了VersaPHY的IP核的实现方案;根据VersaPHY协议,分析了VersaPHY 的标签、数据包和寄存器,完成了VersaPHY的IP核设计;在A ltera QuartusⅡ开发平台上,结合Verilog HDL语言和其自带的IP CORE实现了VP- Label寻址的数据包(读请求包、读响应包、写请求包、写响应包)的接收和发送;最后借助于QuartusⅡ集成开发环境提供的SignalTapⅡ逻辑分析仪进行验证,结果表明,该系统可以实现不同速度(100Mb/s、200Mb/s、400Mb/s、800Mb/s)的VersaPHY 的数据包的传输,工作稳定可靠,满足实际应用需求.【期刊名称】《计算机测量与控制》【年(卷),期】2012(020)009【总页数】4页(P2525-2528)【关键词】VersaPHY;IP核;Verilog HDL【作者】朱榆涵;邵洪峰;伊小素;龙映雪【作者单位】北京航空航天大学仪器科学与光电工程学院,北京 100191;北京航空航天大学仪器科学与光电工程学院,北京 100191;北京航空航天大学仪器科学与光电工程学院,北京 100191;北京航空航天大学仪器科学与光电工程学院,北京100191【正文语种】中文【中图分类】TP20 引言随着传感器技术的发展和信息化程度的加强,导致现代车载系统日益复杂,传输的数据量不断增大,传统的电总线由于存在带宽有限、体积重量大以及在电磁兼容方面的问题,已经不能很好的满足系统的需求[1]。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

( S o C ) ,a g e n e r a l p r o g r a mm a b l e i n t e f r a c e I P c o r e i s d e s i g n e d b y u s i n g t h e p r o g r a m ma b l e s t a t e m a c h i n e a n d w a v e f o r m d e s c i r p t o r

读入 的数 据 验 证 了设 计 的 正确 性 。

关 键 词 :系 统 芯 片 ; 通 用 可 编程 接 口; I P核 ; 数 据 传 输

中 图 分 类 号 :T P 3 0 2 . 1 文 献 标 识 码 :A 文 章 编 号 :0 2 5 8 — 7 9 9 8 ( 2 0 1 5 ) 0 6 — 0 0 6 6 — 0 3

Hu Xi a o g a n g , Z h a o L i n n a , Yu Z h i g u o , We i J i n g h e , Gu Xi a o f e n g ( 1 . K e y L a b o r a t o r y o f A d v a n c e d P r o c e s s C o n t r o l f o r L i g h t I n d u s t y( r Mi n i s t r y o f E d u c a t i o n ) , D e p a r t m e n t o f E l e c t r o n i c E n g i n e e i r n g ,

Me as u r e me n t Con t r ol Te c h n ol o g y a n d I n s t r u m设计 与实现

胡 小 刚 , 赵 琳 娜 , 虞致 国 , 魏敬 和 。 , 顾 晓 峰

( 1 . 江 南大 学 电子 工程 系 轻 工 过 程 先进 控 制 教 育 部 重 点 实 验 室 , 江苏 无锡 2 1 4 1 2 2; 2 . 中 国 电 子 科 技 集 团公 司 第 五 十 八 研 究 所 , 江 苏 无锡 2 1 4 0 3 5 )

Ab s t r a c t :I n o r d e r t o me e t t h e r e q u i r e me n t s o f h i g h b a n d wi d t h a n d t h e d i v e si r t y o f e x t e r n a l i n t e f r a c e o f S y s t e m -o n— a- Ch i p

摘 要 :为 满 足 S o C 外设 接 1 : 7 高带宽、 外部 电路 接 口多样 性 的 要 求 , 利 用 可 编程 状 态 机 和 波 形 描

述 符存 储 器 , 设 计 了一 种 通 用 可编 程 接 口 I P核 。 分 别 从 接 口硬 件 连 接 设 计 、 固件 程 序 设 计 、 波 形 描 述 符 设 计 和 仿 真 平 台 设 计 等 方 面 对 接 口 的 设 计 流 程 进 行 了详 述 。 以 8 0 5 l C P U核 为 基础 , 利 用 所 设 计 的 接 口I P核 构 建 了 仿 真 验 证 环 境 , 对接 口I P核 编 程 后 实 现 了 对 外 部 存 储 器 的 访 问 , 并 通 过 比 较 写 出 和

me mo r y. T h e d e t a i l e d d e s i g n f l o w o f t h e i n t e fa r c e i s d e s c i r b e d,i n c l u d i n g t h e d e s i g n s o f t h e i n t e f r a c e h a r d w a r e c o n n e c t i o n ,t h e

D0I : 1 0. 1 61 5 7/ i . i s s n. 02 5 8—7 9 9 8. 2 01 5. 0 6. 01 8

De s i g n a n d i mp l e me n t a t i o n o f a g e n e r a l p r o g r a mma b l e i n t e r f a c e I P c o r e

i f r mwa r e d e s i g n,t h e w a v e f o r l T l d e s c i r p t o r a n d t h e s i mu l a t i o n p l a t f o r m .B a s e d o n t h e 8 0 5 1 C P U c o r e ,a v e i r f i c a t i o n s i mu l a t i o n e n v i — r o n me n t i s b u i l t u s i n g t h e d e s i g n e d i n t e f r a c e I P c o r e .T h e i n t e f r a c e I P c o r e i s t e s t e d a n d v e i r i f e d b y c o mp a in r g t h e d a t a b e i n g wr i t -

J i a n g n a n Un i v e r s i t y, Wu x i 21 4 1 2 2, Ch i n a;

2 . T h e 5 8 t h R e s e a r c h I n s t i t u t e o f C h i n a E l e c t r o n i c s T e c h n o l o g y G r o u p C o r p, Wu x i 2 1 4 0 3 5, C h i n a )