FPGA可编程逻辑器件芯片EP2S60F672I5N中文规格书

FPGA可编程逻辑器件芯片EP20K600EFI672中文规格书

Port Connect

0, 1, 2 0, 1, 2 0 0 0 0 0 1 0, 1 0 0 n/a n/a

n/a

ADSP-BF60X BLACKFIN PROCESSOR HARDWARE REFERENCE

PIPELINED VISION PROCESSOR (PVP) PVP FUNCTIONAL DESCRIPTION

ቤተ መጻሕፍቲ ባይዱ

56$7,-,QS,-,QS,-56$7,- 56$7,- 56$7,-

All values outside of the region are defined as zero—InpI,-1 = RSATI,-1 = RSATI,-2 = 0, as shown in the Illustration of RSAT Mode figure.

ADSP-BF60X BLACKFIN PROCESSOR HARDWARE REFERENCE

PIPELINED VISION PROCESSOR (PVP) OPERATING MODES

the signal processing blocks (PVP blocks). You have full flexibility to assign each of the PVP blocks to any pipe. The one exception is the up/down-scaler block (UDS), which can only operate in memory pipe mode. Each PVP block may be assigned only to one pipe at a time. But, there is support for dynamic re-configuration of the pipe assignments. For a graphical overview of all PVP block interconnections, see Configuring Pipe Structure. The PVP blocks are: • Two input formatters (IPFn, x=0, 1) supporting selection of input streams, gating pipeline processing

FPGA可编程逻辑器件芯片EP20K600CF672C8中文规格书

28Link Port (LP)Link ports allow the processor to connect to other processors or peripheral link ports using a simplecommunication protocol for high-speed parallel data transfer. This peripheral allows a variety of I/Operipheral interconnection schemes to I/O peripheral devices as well as co-processing and multiprocessing schemes.The processor’s link ports support 8-bit wide data transfers. The link port pins are multiplexed in the GPIO ports. For information on processor multiplexing, see the processor specific data sheet.Link ports can operate independently and simultaneously, allowing glueless high-speed connectivity of up to four external processors.LP FeaturesAll link ports are identical in their design and have the following common features.•Bidirectional ports with eight data signals (LP_D0 – LP_D7, an acknowledge signal (LP_ACK), and a clock signal (LP_CLK).•Provide high-speed, point-to-point data transfers to other processors, allowing different types of inter-connections between multiple processors.•Pack data into 32-bit words. This data can be directly read by the processor or transferred via DMA to or from on-chip memory.•Support for data buffering through a 2-deep FIFO for transmit and a 4-deep FIFO for receive.•Programmable clock and acknowledge based handshake mechanism for efficient communication.• A dedicated DMA channel.LP Functional DescriptionThis section provides a description of the link port, including a list of its registers and a functional block diagram.ADSP-BF60x LP Register ListThe LP are 8-bit wide ports, which can connect to another processor or peripheral LP. These ports allow a variety of interconnection schemes to I/O peripheral devices as well as co-processing and multiprocessingMissed Event Interrupt Mask RegisterThe ACM_MEVMSK register enables interrupts corresponding to status bits in the ACM_MEVSTAT register. When an ACM_MEVMSK bit is set (=1), an interrupt is generated when the corresponding event missed bit is set (bit in ACM_MEVSTAT is set).3(R/W1C)EV3Event 3 Missed.The ACM_MEVSTAT.EV3 bit indicates when an instance of event 3 hasbeen missed since the last trigger. If set and the corresponding bit inACM_MEVMSK is set (interrupt enabled), the condition generates aninterrupt. This bit is W1C.No Event 3 Missed Status 1Event 3 Missed2(R/W1C)EV2Event 2 Missed.The ACM_MEVSTAT.EV2 bit indicates when an instance of event 2 hasbeen missed since the last trigger. If set and the corresponding bit inACM_MEVMSK is set (interrupt enabled), the condition generates aninterrupt. This bit is W1C.No Event 2 Missed Status 1Event 2 Missed1(R/W1C)EV1Event 1 Missed.The ACM_MEVSTAT.EV1 bit indicates when an instance of event 1 hasbeen missed since the last trigger. If set and the corresponding bit inACM_MEVMSK is set (interrupt enabled), the condition generates aninterrupt. This bit is W1C.No Event 1 Missed Status 1Event 1 Missed(R/W1C)EV0Event 0 Missed.The ACM_MEVSTAT.EV0 bit indicates when an instance of event 0 hasbeen missed since the last trigger. If set and the corresponding bit inACM_MEVMSK is set (interrupt enabled), the condition generates aninterrupt. This bit is W1C.No Event 0 Missed Status 1Event 0 MissedTable 27-12:ACM_MEVSTAT Register Fields (Continued)Bit No.(Access)Bit Name Description/EnumerationEvent N Time RegisterThe ACM_EVTIMEn registers each hold a 32-bit event time value. There are 16 event time registers: 8 are assigned to each ACM timer, if both timers are enabled. If only one timer is enabled, all 16 of the ACM_EVTIMEn registers are assigned to the enabled timer.Note that the ACM_EVTIMEn register should not be programmed when an event is active. The register might give incorrect results. The user should program this register before giving trigger and should re-program the register after all the events are complete (ACM_STAT.ECOM1 or ACM_STAT.ECOM0 bit is set). Also note that even if none of the events are enabled in the ACM_EVTIMEn register (for example, all ACM_EVCTLn.ENAEV =0), the ACM_STAT.ECOM0 or ACM_STAT.ECOM1 bit is set and an interrupt is raised (if unmasked) if a trigger is applied with the Timer enabled.Table 27-14:ACM_EVCTLn Register Fields Bit No.(Access)Bit Name Description/Enumeration5:1(R/W)EPF Event Parameter Field.The ACM_EVCTLn.EPF bits select values for the ADC control pins(ACM_A0, ACM_A1, ACM_A2, and ACM_A3), which are output when theenabled event occurs. Selection of ACM_EVCTLn.EPF values are basedon the type of ADC, usage mode, and other items. For moreinformation, see the operating modes section. Note that all ACM_EVCTLn.EPF bits have the same external pin timing.0(R/W)ENAEVEnable Event.The ACM_EVCTLn.ENAEV bit causes a sampling event to occur to theADC with the ADC controls selected by the ACM_EVCTLn.EPF fieldwhen an event (time comparison match or other external trigger)occurs. If disabled, the corresponding event has no significance, andthe control values is not used.Disable Event 1Enable Event。

FPGA可编程逻辑器件芯片EP20K300EFC672-1X中文规格书

202-Wire Interface (TWI)The processor has a 2-wire interface (TWI), that provides a simple exchange method of control databetween multiple devices. The TWI module is compatible with the widely used I2C bus standard. Addi-tionally, the TWI module is fully compatible with serial camera control bus (SCCB) functionality for easier control of various CMOS camera sensor devices.The TWI module offers the capabilities of simultaneous master and slave operation and support for both 7-bit addressing and multimedia data arbitration. The TWI interface uses two pins for transferring clock (TWI_SCL) and data (TWI_SDA) and supports the protocol at speeds up to 400K bits/sec. The TWI interface pins are compatible with 5 V logic levels.To preserve processor bandwidth, the TWI module can be set up with transfer initiated interrupts to only service FIFO buffer data reads and writes. Protocol related interrupts are optional. The TWI externally moves 8-bit data while maintaining compliance with the I2C bus protocol.TWI FeaturesThe TWI is fully compatible with the widely used I2C bus standard.The TWI controller includes the following features.•Simultaneous master and slave operation on multiple device systems•Support for multi-master bus arbitration•7-bit addressing•100K bits/second and 400K bits/second data rates•General call address support•Master clock synchronization and support for clock low extension•Separate multiple-byte receive and transmit FIFOs•Low interrupt rate•Individual override control of data and clock lines in the event of bus lock-up•Input filter for spike suppression•Serial camera control bus support as specified in the OmniVision Serial Camera Control Bus (SCCB) Functional Specification2-W IRE I NTERFACE (TWI)TWI O PERATING M ODESRepeated StartA repeated start condition is the absence of a stop condition between two transfers. The two transfers canbe of any direction type. Examples include a transmit followed by a receive, or a receive followed by a transmit. The following sections guide the programmer in developing a service routine.Transmit Receive Repeated StartThe following figure shows a repeated start followed by a data receive sequence. The shading in the figure indicates that the slave has control of the bus.Figure 20-7:Repeated Start Followed by Data ReceiveThe following tasks are performed at each interrupt.•Transmit FIFO service (TWI_ISTAT.TXSERV) interrupt. This interrupt is generated due to a FIFO access. Since this is the last byte of this transfer, the TWI_FIFOSTAT register indicates the transmit FIFOis empty. When read, TWI_MSTRCTL.DCNT bit field=0. Set the TWI_MSTRCTL.RSTART bit to indicate arepeated start and set the TWI_MSTRCTL.DIR bit if the following transfer will be a data receive.•Master transfer complete (TWI_ISTAT.MCOMP) interrupt. This interrupt is generated when all data has been transferred (TWI_MSTRCTL.DCNT bit field=0). If no errors are generated, a start condition is initi-ated. Clear the TWI_MSTRCTL.RSTART bit and program the TWI_MSTRCTL.DCNT bits with the desirednumber of bytes to receive.•Receive FIFO service (TWI_ISTAT.RXSERV) interrupt. This interrupt is generated due to the arrival ofa byte in the receive FIFO. Simple data handling is all that is required.•Master transfer complete (TWI_ISTAT.MCOMP) interrupt. The transfer is complete.Receive Transmit Repeated StartThe following figure illustrates a repeated start data receive followed by a data transmit sequence. The shading in the figure indicates that the slave has control of the bus.2-W IRE I NTERFACE (TWI)TWI F UNCTIONAL D ESCRIPTION constant formed by the pull-up resistor and the TWI_SCL capacitance. See the “Register Descrip-tions” section for more details.Serial Data Signal (SDA)This is a bidirectional signal on which serial data is transmitted or received depending on the direction of the transfer.Internal InterfaceThe peripheral bus interface supports the transfer of 16-bit wide data and is used by the processor in the support of register and FIFO buffer reads and writes. The TWI internal interface is comprised of the blocks described below.Register block. Contains all control and status bits and reflects what can be written or read as outlined by the programming model. Status bits can be updated by their respective functional blocks.FIFO buffer. Configured as a1-byte-wide 2-deep transmit FIFO buffer and a 1-byte-wide 2-deep receive FIFO buffer.Transmit shift register. Serially shifts its data out externally off chip. The output can be controlled for generation of acknowledgments or it can be manually overwritten.Receive shift register. Receives its data serially from off chip. The receive shift register is 1 byte wide and data received can either be transferred to the FIFO buffer or used in an address comparison.Address compare block. Supports address comparison in the event the TWI controller module is accessed as a slave.Prescaler block. Must be programmed to generate a 10 MHz time reference relative to the system clock.This time base is used for filtering of data and timing events specified by the electrical data sheet (See the Philips specification), as well as for TWI_SCL clock generation.Clock generation module. Generates an external TWI_SCL clock when in master mode. It includes the logic necessary for synchronization in a multi-master clock configuration and clock stretching whenconfigured in slave mode.TWI Architectural ConceptsThe TWI controller follows the transfer protocol of the Philips I2C Bus Specification version 2.1 dated January 2000.TWI ProtocolThe following figure shows a simple complete transfer.。

FPGA可编程逻辑器件芯片EP2S60F672I4中文规格书

Software Stratix®II devices are supported by the Altera® Quartus®II designsoftware, which provides a comprehensive environment for system-on-a-programmable-chip (SOPC) design. The Quartus II software includesHDL and schematic design entry, compilation and logic synthesis, fullsimulation and advanced timing analysis, SignalTap®II logic analyzer,and device configuration. See the Quartus II Handbook for moreinformation on the Quartus II software features.The Quartus II software supports the Windows XP/2000/NT/98, SunSolaris, Linux Red Hat v7.1 and HP-UX operating systems. It alsosupports seamless integration with industry-leading EDA tools throughthe NativeLink® interface.Duty Cycle DistortionHere is an example for calculating the DCD in percentage for a DDIO output on a row I/O on a -3 device:If the input I/O standard is SSTL-2 and the DDIO output I/O standard is SSTL-2 Class II, the maximum DCD is 60ps (see Table 5–82). If the clock frequency is 267MHz, the clock period T is:T = 1/ f = 1 / 267MHz = 3.745ns = 3745ps Calculate the DCD as a percentage:(T/2 – DCD) / T = (3745ps/2 – 60ps) / 3745ps = 48.4% (for low boundary)(T/2 + DCD) / T = (3745ps/2 + 60ps) / 3745ps = 51.6% (for high boundary)Table 5–82.Maximum DCD for DDIO Output on Row I/O Pins Without PLL in the Clock Path for -3 Devices Notes (1), (2)Row DDIO Output I/OStandardMaximum DCD Based on I/O Standard of Input Feeding the DDIO Clock Port(No PLL in Clock Path)UnitTTL/CMOSSSTL-2SSTL/HSTL LVDS/ HyperTransport Technology3.3 & 2.5 V1.8 & 1.5 V2.5 V1.8 & 1.5 V3.3 V3.3-V LVTTL 260380145145110ps 3.3-V LVCMOS 21033010010065ps 2.5 V 195315858575ps 1.8 V1502658585120ps 1.5-V LVCMOS 255370140140105ps SSTL-2 Class I 175295656570ps SSTL-2 Class II 170290606075ps SSTL-18 Class I 155275555090ps 1.8-V HSTL Class I 150270606095ps 1.5-V HSTL Class I 150270555590ps LVDS/ HyperTransport technology 180180180180180psNotes to Table 5–82:(1)The information in Table 5–82 assumes the input clock has zero DCD.(2)The DCD specification is based on a no logic array noise condition.Table5–84.Maximum DCD for DDIO Output on Column I/O Pins Without PLL in the Clock Path for -3 Devices (Part 1 of 2)Notes (1), (2)DDIO Column Output I/OStandardMaximum DCD Based on I/O Standard of Input Feeding the DDIOClock Port (No PLL in the Clock Path)UnitTTL/CMOS SSTL-2SSTL/HSTL 1.2-V HSTL 3.3/2.5 V1.8/1.5 V2.5 V1.8/1.5 V1.2 V3.3-V LVTTL 260380145145145ps 3.3-V LVCMOS 210330100100100ps 2.5 V195315858585psPLL Timing Specifications Tables5–92 and 5–93 describe the Stratix II PLL specifications when operating in both the commercial junction temperature range (0 to 85°C) and the industrial junction temperature range (–40 to 100 °C).Table5–92.Enhanced PLL Specifications(Part 1 of2)Name Description Min Typ Max Unit f I N Input clock frequency2500MHz f I N P F D Input frequency to thePFD2420MHz f I N D U T Y Input clock duty cycle4060%f E I N D U T Y External feedbackinput clock duty cycle4060%t I N J I T T E R Input or externalfeedback clock inputjitter tolerance interms of period jitter.Bandwidth ≤0.85MHz0.5ns (p-p)Input or externalfeedback clock inputjitter tolerance interms of period jitter.Bandwidth >0.85MHz1.0ns (p-p)t O U T J I T T E R Dedicated clockoutput period jitter 250ps for ≥ 100 MHz outclk25mUI for < 100 MHz outclkps or mUI(p-p)t F C O M P External feedbackcompensation time10nsf O U T Output frequency forinternal global orregional clock 1.5(2)550.0MHzt O U T D U T Y Duty cycle for externalclock output (when setto 50%).455055%f S C A N C L K Scanclk frequency100MHz t C O N F I G P L L Time required toreconfigure scanchains for enhancedPLLs174/f S C A N C L K nsf O U T_E X T PLL external clockoutput frequency 1.5(2)550.0 (1)MHz5Stratix II Device Handbook, Volume PLL Timing Specificationst L O C KTime required for the PLL to lock from the time it is enabled or the end of device configuration 0.031mst D L O C KTime required for the PLL to lockdynamically after automatic clock switchover between two identical clock frequencies 1msf S W I T C H OV E RFrequency range where the clock switchover performs properly 4500MHzf C L B W PLL closed-loop bandwidth0.13 1.2016.90MHz f V C OPLL VCO operating range for –3 and –4 speed grade devices 3001,040MHzPLL VCO operating range for –5 speed grade devices300840MHzf S SSpread-spectrum modulation frequency 30150kHz % spreadPercent down spread for a given clock frequency 0.40.50.6%t P L L _P S E R R Accuracy of PLL phase shift±15ps t A R E S E TMinimum pulse width on areset signal. 10ns t A R E S E T _R E C O N F I GMinimum pulse width on the areset signal when using PLLreconfiguration. Reset the PLL after scandone goes high.500nsNotes to Table 5–92:(1)Limited by I/O f M A X . See Table 5–78 on page 5–69 for the maximum. Cannot exceed f O U T specification.(2)If the counter cascading feature of the PLL is utilized, there is no minimum output clock frequency.Table 5–92.Enhanced PLL Specifications (Part 2 of 2)NameDescriptionMin TypMaxUnit。

FPGA可编程逻辑器件芯片EP2S15F672C6中文规格书

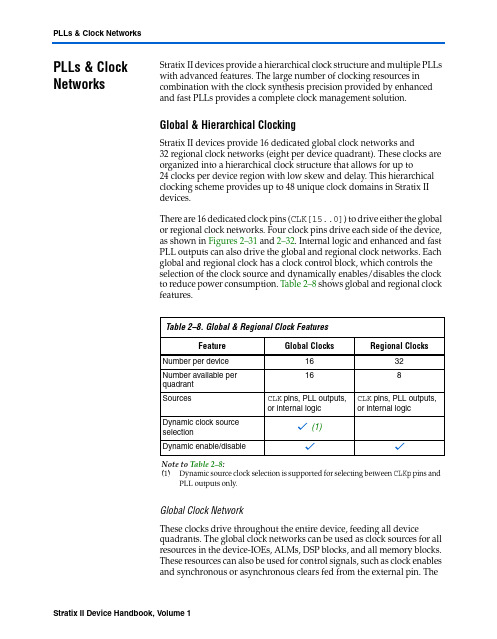

PLLs & Clock NetworksPLLs & Clock Networks Stratix II devices provide a hierarchical clock structure and multiple PLLs with advanced features. The large number of clocking resources in combination with the clock synthesis precision provided by enhanced and fast PLLs provides a complete clock management solution. Global & Hierarchical ClockingStratix II devices provide 16 dedicated global clock networks and32regional clock networks (eight per device quadrant). These clocks are organized into a hierarchical clock structure that allows for up to24clocks per device region with low skew and delay. This hierarchical clocking scheme provides up to 48 unique clock domains in Stratix II devices.There are 16 dedicated clock pins (CLK[15..0]) to drive either the global or regional clock networks. Four clock pins drive each side of the device, as shown in Figures2–31 and 2–32. Internal logic and enhanced and fast PLL outputs can also drive the global and regional clock networks. Each global and regional clock has a clock control block, which controls the selection of the clock source and dynamically enables/disables the clock to reduce power consumption. Table2–8 shows global and regional clock features.Global Clock NetworkThese clocks drive throughout the entire device, feeding all device quadrants. The global clock networks can be used as clock sources for all resources in the device-IOEs, ALMs, DSP blocks, and all memory blocks. These resources can also be used for control signals, such as clock enables and synchronous or asynchronous clears fed from the external pin. The Table2–8.Global & Regional Clock FeaturesFeature Global Clocks Regional Clocks Number per device1632Number available perquadrant168Sources CLK pins, PLL outputs,or internal logicCLK pins, PLL outputs,or internal logic Dynamic clock sourceselectionv (1)Dynamic enable/disable v vNote to Table2–8:(1)Dynamic source clock selection is supported for selecting between CLKp pins andPLL outputs only.Figure2–55.Output TIming Diagram in DDR ModeThe Stratix II IOE operates in bidirectional DDR mode by combining theDDR input and DDR output configurations. The negative-edge-clockedOE register holds the OE signal inactive until the falling edge of the clock.This is done to meet DDR SDRAM timing requirements.External RAM InterfacingIn addition to the six I/O registers in each IOE, Stratix II devices also havededicated phase-shift circuitry for interfacing with external memoryinterfaces. Stratix II devices support DDR and DDR2 SDRAM, QDR IISRAM, RLDRAM II, and SDR SDRAM memory interfaces. In everyStratix II device, the I/O banks at the top (banks 3 and 4) and bottom(banks 7 and 8) of the device support DQ and DQS signals with DQ busmodes of ×4, ×8/×9, ×16/×18, or ×32/×36. Table2–14 shows the numberof DQ and DQS buses that are supported per device.Table2–14.DQS & DQ Bus Mode Support(Part 1 of2)Note(1)Device Package Number of×4GroupsNumber of×8/×9 GroupsNumber of×16/×18 GroupsNumber of×32/×36 GroupsEP2S15484-pin FineLine BGA8400 672-pin FineLine BGA18840 EP2S30484-pin FineLine BGA8400 672-pin FineLine BGA18840 EP2S60484-pin FineLine BGA8400 672-pin FineLine BGA188401,020-pin FineLine BGA361884I/O StructureA compensated delay element on each DQS pin automatically aligns input DQS synchronization signals with the data window of theircorresponding DQ data signals. The DQS signals drive a local DQS bus in the top and bottom I/O banks. This DQS bus is an additional resource to the I/O clocks and is used to clock DQ input registers with the DQS signal.The Stratix II device has two phase-shifting reference circuits, one on the top and one on the bottom of the device. The circuit on the top controls the compensated delay elements for all DQS pins on the top. The circuit on the bottom controls the compensated delay elements for all DQS pins on the bottom.Each phase-shifting reference circuit is driven by a system reference clock, which must have the same frequency as the DQS signal. Clock pins CLK[15..12]p feed the phase circuitry on the top of the device and clock pins CLK[7..4]p feed the phase circuitry on the bottom of the device. In addition, PLL clock outputs can also feed the phase-shifting reference circuits.Figure 2–56 illustrates the phase-shift reference circuit control of each DQS delay shift on the top of the device. This same circuit is duplicated on the bottom of the device.EP2S90484-pin Hybrid FineLine BGA 8400780-pin FineLine BGA 188401,020-pin FineLine BGA 3618841,508-pin FineLine BGA361884EP2S130780-pin FineLine BGA188401,020-pin FineLine BGA 3618841,508-pin FineLine BGA361884EP2S1801,020-pin FineLine BGA3618841,508-pin FineLine BGA361884Notes to Table 2–14:(1)Check the pin table for each DQS/DQ group in the different modes.Table 2–14.DQS & DQ Bus Mode Support (Part 2 of 2)Note (1)DevicePackageNumber of ×4GroupsNumber of ×8/×9 GroupsNumber of ×16/×18 Groups Number of ×32/×36 Groups。

FPGA可编程逻辑器件芯片EP20K600EFI672-2X中文规格书

,175B393B67$7

,175B393B67$7

,5(4 :& ,06. 5:

,5(4 :& ,06. 5:

,/$7 :&

67$7 52VHOIFOHDU

Figure 30-48: PVP Interrupt Flow

The PVP features a single, 32-bit wide event status register, PVP_STAT, as shown in the PVP interrupt flow figure. The PVP_STAT register contains read-only status bits for camera pipe control, memory pipe control, and individual processing blocks. All flags in this register are generated and cleared by hardware. The PVP_ILAT register contains the latched counterparts of the status bits in the PVP_STAT register. If a status bit toggles from 0 to 1 the respective latch bit is set automatically. The latches in the PVP_ILAT register are cleared by software using the W1C method. The PVP_IMSKn registers (one for each processor core) can unmask the interrupt behavior of the latches. If the PVP_STAT.CPRDY bit (camera pipe ready) is set by hardware, the PVP sets the corresponding latch bit, PVP_ILAT.CPRDY. By default, interrupts are not enabled (unmasked). If software sets the PVP_IMSKn. CPRDY bit enabling (unmasking) the interrupt, the latched interrupt status causes an interrupt on the PVP status output to the corresponding processor core.

FPGA可编程逻辑器件芯片EP1S25F672C6中文规格书

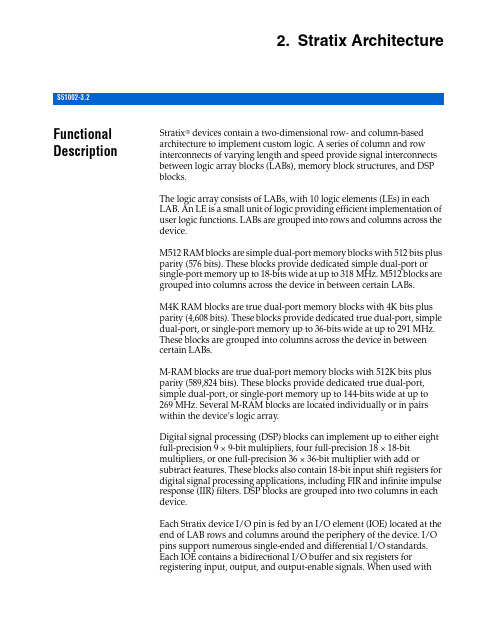

2.Stratix ArchitectureFunctional Description Stratix® devices contain a two-dimensional row- and column-based architecture to implement custom logic. A series of column and row interconnects of varying length and speed provide signal interconnects between logic array blocks (LABs), memory block structures, and DSP blocks.The logic array consists of LABs, with 10 logic elements (LEs) in each LAB. An LE is a small unit of logic providing efficient implementation of user logic functions. LABs are grouped into rows and columns across the device.M512 RAM blocks are simple dual-port memory blocks with 512 bits plus parity (576 bits). These blocks provide dedicated simple dual-port or single-port memory up to 18-bits wide at up to 318MHz. M512 blocks are grouped into columns across the device in between certain LABs.M4K RAM blocks are true dual-port memory blocks with 4K bits plus parity (4,608 bits). These blocks provide dedicated true dual-port, simple dual-port, or single-port memory up to 36-bits wide at up to 291MHz. These blocks are grouped into columns across the device in between certain LABs.M-RAM blocks are true dual-port memory blocks with 512K bits plus parity (589,824bits). These blocks provide dedicated true dual-port, simple dual-port, or single-port memory up to 144-bits wide at up to 269MHz. Several M-RAM blocks are located individually or in pairs within the device’s logic array.Digital signal processing (DSP) blocks can implement up to either eight full-precision 9×9-bit multipliers, four full-precision 18 × 18-bit multipliers, or one full-precision 36×36-bit multiplier with add or subtract features. These blocks also contain 18-bit input shift registers for digital signal processing applications, including FIR and infinite impulse response (IIR) filters. DSP blocks are grouped into two columns in each device.Each Stratix device I/O pin is fed by an I/O element (IOE) located at the end of LAB rows and columns around the periphery of the device. I/O pins support numerous single-ended and differential I/O standards. Each IOE contains a bidirectional I/O buffer and six registers for registering input, output, and output-enable signals. When used withStratix Device Handbook, Volume 1Stratix ArchitectureFigure 2–7.LE in Dynamic Arithmetic ModeStratix Device Handbook, Volume 1MultiTrack InterconnectTable 2–2 shows the Stratix device’s routing scheme.Table 2–2.Stratix Device Routing SchemeSourceDestinationL U T C h a i nR e g i s t e r C h a i nL o c a l I n t e r c o n n e c tD i r e c t L i n k I n t e r c o n n e c tR 4 I n t e r c o n n e c tR 8 I n t e r c o n n e c tR 24 I n t e r c o n n e c tC 4 I n t e r c o n n e c tC 8 I n t e r c o n n e c tC 16 I n t e r c o n n e c tL EM 512 R A M B l o c kM 4K R A M B l o c kM -R A M B l o c kD S P B l o c k sC o l u m n I O E R o w I O ELUT Chain v Register Chain v LocalInterconnect vvvvvvvDirect Link Interconnect v R4 Interconnect v vvvvR8 Interconnect vvvR24Interconnect vvv v C4 Interconnect v vvC8 Interconnect vvvC16Interconnect vvv vLEvvv v v v v v M512 RAM Blockv v v v v v M4K RAM Block v v v v v v M-RAM Block v v DSP Blocks vv vv v v Column IOE v v v v Row IOEvvvvvvStratix Device Handbook, Volume 1Stratix ArchitectureTriMatrix MemoryTriMatrix memory consists of three types of RAM blocks: M512, M4K, and M-RAM blocks. Although these memory blocks are different, they can all implement various types of memory with or without parity,including true dual-port, simple dual-port, and single-port RAM, ROM, and FIFO buffers. Table 2–3 shows the size and features of the different RAM blocks.Table 2–3.TriMatrix Memory Features (Part 1 of 2)Memory FeatureM512 RAM Block (32×18Bits)M4K RAM Block (128×36Bits)M-RAM Block (4K ×144Bits)Maximum performance (1)(1)(1)T rue dual-port memory vv Simple dual-port memoryv v v Single-port memoryvvvStratix Device Handbook, Volume 1TriMatrix MemoryConfigurations512×1256×2128×464×864×932×1632×184K ×12K ×21K ×4512×8512×9256×16256×18128×32128×3664K ×864K ×932K ×1632K ×1816K ×3216K ×368K ×648K ×724K ×1284K ×144Table 2–3.TriMatrix Memory Features (Part 2 of 2)Memory FeatureM512 RAM Block (32×18Bits)M4K RAM Block (128×36Bits)M-RAM Block (4K ×144Bits)。

FPGA可编程逻辑器件芯片EP2S30F672C5中文规格书

Table 6–5 shows the summary of input register modes for the DSP block.Multiplier StageThe multiplier stage supports 9 × 9, 18 × 18, or 36 × 36 multipliers as well as other smaller multipliers in between these configurations. See“Operational Modes” on page 6–21 for details. Depending on the data width of the multiplier, a single DSP block can perform many multiplications in parallel.Each multiplier operand can be a unique signed or unsigned number. Two signals, signa and signb , control the representation of eachoperand respectively. A logic 1 value on the signa signal indicates that data A is a signed number while a logic 0 value indicates an unsigned number. Table 6–6 shows the sign of the multiplication result for the various operand sign representations. The result of the multiplication is signed if any one of the operands is a signed value.There is only one signa and one signb signal for each DSP block.Therefore, all of the data A inputs feeding the same DSP block must have the same sign representation. Similarly, all of the data B inputs feeding the same DSP block must have the same sign representation. The multiplier offers full precision regardless of the sign representation.1When the signa and signb signals are unused, the Quartus ® IIsoftware sets the multiplier to perform unsigned multiplication by default.Table 6–5.Input Register ModesRegister InputMode9 × 918 × 1836 × 36Parallel inputv v vShift register input v v Table 6–6.Multiplier Sign RepresentationData A (signa Value)Data B (signb Value)Result Unsigned (logic 0)Unsigned (logic 0)Unsigned Unsigned (logic 0)Signed (logic 1)Signed Signed (logic 1)Unsigned (logic 0)Signed Signed (logic 1)Signed (logic 1)SignedAccumulatorWhen the adder/subtractor/accumulator is configured as an accumulator, the output of the adder/output block feeds back to the accumulator as shown in Figure6–7. The accumulator can be set up to perform addition only, subtraction only or the addnsub signal can be used to dynamically control the accumulation direction. A logic 1 value on the addnsub signal indicates that the accumulator is performing addition while a logic 0 value indicates subtraction.Each accumulator can be cleared by either clearing the DSP block output register or by using the accum_sload signal. The accumulator clear using the accum_sload signal is independent from the resetting of the output registers so the accumulation can be cleared and a new one can begin without losing any clock cycles. The accum_sload signal controls a feedback multiplexer that specifies that the output of the multiplier should be summed with a zero instead of the accumulator feedback path. The accumulator can also be initialized/preloaded with a non-zero value using the accum_sload signal and the accum_sload_upper_data bus with one clock cycle latency. Preloading the accumulator is done by adding the result of the multiplier with the value specified on the accum_sload_upper_data bus. As in the case of the accumulator clearing, the accum_sload signal specifies to the feedback multiplexer that the accum_sload_upper_data signal should feed the accumulator instead of the accumulator feedback signal. Theaccum_sload_upper_data signal only loads the upper 36-bits of the accumulator. To load the entire accumulator, the value for the lower16-bits must be sent through the multiplier feeding that accumulator with the multiplier set to perform a multiplication by one.The overflow signal will go high on the positive edge of the clock when the accumulator detects an overflow or underflow. The overflow signal will stay high for only one clock cycle after an overflow or underflow is detected even if the overflow or underflow condition is still present. A latch external to the DSP block has to be used to preserve the overflow signal indefinitely or until the latch is cleared.The DSP blocks support Q1.15 input format saturation and rounding in each accumulator. The following signals are available that can control if saturation or rounding or both is performed to the output of the accumulator:■accum_round■accum_saturation■accum_is_saturated outputDSP Blocks in Stratix II and Stratix II GX Devices Each DSP block has two sets of accum_round and accum_saturation signals which control if rounding or saturation is performed on the accumulator output respectively (one set of signals for each accumulator). Rounding and saturation of the accumulator output is only available when implementing an 16 × 16 multiplier-accumulator to conform to the bit widths required for Q1.15 input format computation.A logic 1 value on the accum_round and accum_saturation signal indicates that rounding or saturation is performed while a logic 0 indicates that no rounding or saturation is performed. A logic 1 value on the accum_is_saturated output signal tells you that saturation has occurred to the result of the accumulator.Figure6–10 shows the DSP block configured to perform multiplier-accumulator operations.Adder/SubtractorThe addnsub1 or addnsub3 signals specify whether you are performing addition or subtraction. A logic 1 value on the addnsub1 or addnsub3 signals indicates that the adder/subtractor is performing addition while a logic 0 value indicates subtraction. These signals can be dynamically controlled using logic external to the DSP block. If the first stage is configured as a subtractor, the output is A – B and C – D.The adder/subtractor block share the same signa and signb signals as the multiplier block. The signa and signb signals can be pipelined with a latency of one or two clock cycles or not.The DSP blocks support Q1.15 input format rounding (not saturation) after each adder/subtractor. The addnsub1_round andaddnsub3_round signals determine if rounding is performed to the output of the adder/subtractor.The addnsub1_round signal controls the rounding of the topadder/subtractor and the addnsub3_round signal controls the rounding of the bottom adder/subtractor. Rounding of the adder output is only available when implementing an 16 × 16 multiplier-adder to conform to the bit widths required for Q1.15 input format computation.A logic 1 value on the addnsub_round signal indicates that rounding is performed while a logic 0 indicates that no rounding is performed. Summation BlockThe output of the adder/subtractor block feeds an optional summation block, which is an adder block that sums the outputs of bothadder/subtractor blocks. The summation block is used when more than two multiplier results are summed. This is useful in applications such as FIR filtering.。

FPGA可编程逻辑器件芯片EP20K200EBC672中文规格书

G ENERAL -P URPOSE P ORTS (PORT)PORT P ROGRAMMING M ODELADSP-BF60X B LACKFIN P ROCESSOR H ARDWARE R EFERENCEBecause every PINTx block groups up to 32 pin signals, the PINTx_MASK_SET / PINTx_INVERT_CLEAR register pair can control which of the signals can request an interrupt at the system level. Software may interrogate the PINTx_REQUEST register for signaling pins. The PINTx_REQUEST bits represent a logical AND between the mask and the latch. When any of these bits is set, an interrupt is forwarded to the SIC controller.All MMR registers in the pin interrupt module are 32 bits wide. Individual bits of the PINTx registers repre-sent the associated pins. Nevertheless, the 32 bits can also be seen as four groups of eight pins. Each group can manage up to eight pins out of either the lower or an upper half of any associated port.PORT Programming ModelThe following sections description of the overall program model of the general purpose ports.GPIO Programming Model Flow (Part 1), GPIO Programming Model Flow (Part 2), and GPIO Programming Model Flow (Part 3) show the programming model of the general-purpose ports. This includes the GPIO input and output operation, open-drain mode, and the pin interrupt PINTx modules. NOTE :These process flow diagrams connect where callout letters appear. For example, callout "A" on theGPIO Programming Model Flow (Part 1) diagram connects to callout "A" on the GPIOProgramming Model Flow (Part 2) diagram.The following flow charts describe the processes for setting up pins for different available functionality. Begin the process from the GPIO Programming Model Flow (Part 1) chart. The first decision effect the value of the PORT_FER register, shown at "1", for peripheral functions this should be set. For more infor-mation on setting up for peripheral functions refer to the Port Multiplexing ControlIf the pin is to be a GPIO pin, a series of decisions then need to be made. There are several configuration registers that need to be considered: PORT_DATA , PORT_INV , PORT_DIR , and PORT_INEN . Depending on the type of GPIO pin desired, the configurations may or may not be applicable, and can have different mean-ings. The following paragraphs describe in brief the function of the different settings for each of the pin functions in GPIO mode: Input, Output, and Open-drain. For all registers the SET/CLR versions of the register are recommended to be used. For more detailed descriptions of the configurations, see ADSP-BF60x PORT Register Descriptions .For Output mode, all the pins should always first be made low using PORT_DATA register. The PORT_DIR register is used to define the direction of each pin (output). In this mode, the other registers aren't of any consequence. This flow can be seen starting at label "2" in GPIO Programming Model Flow (Part 1) chart.G ENERAL-P URPOSE P ORTS (PORT)PORT F UNCTIONAL D ESCRIPTIONADSP-BF60x PINT Trigger ListTable 14-4:ADSP-BF60x PINT Trigger List Trigger MastersDescription Trigger ID SensitivityPINT0 Pin Interrupt Block10LEVELPINT1 Pin Interrupt Block11LEVELPINT2 Pin Interrupt Block12LEVELPINT3 Pin Interrupt Block13LEVELPINT4 Pin Interrupt Block14LEVELPINT5 Pin Interrupt Block15LEVELTable 14-5:ADSP-BF60x PINT Trigger List Trigger SlavesDescription Trigger ID SensitivityNoneADSP-BF60x PADS Register ListThe PADS controls signal hysteresis and other system interface signal features for a number of module interfaces.Table 14-6:ADSP-BF60x PADS Register ListName DescriptionPADS_EMAC_PTP_CLKSEL EMAC and PTP Clock Select RegisterPADS_TWI_VSEL TWI Voltage SelectionPADS_PORTS_HYST GPIO Pin Hysteresis Enable RegisterPORT DefinitionsThis section provides definitions relating to the GPIO ports.ADSP-BF60X B LACKFIN P ROCESSOR H ARDWARE R EFERENCEG ENERAL-P URPOSE P ORTS (PORT)PORT F UNCTIONAL D ESCRIPTIONTable 14-7:General-Purpose and Special Function Signals (Continued)Module Signals PortsLP0All A, BData ACLK BACK BLP1All B, CData BCLK CACK CLP2All E, FData FCLK EACK ELP3All E, FData FCLK EACK ETM0All B, D, E, GTimers E, GCLKs B, D, GAlternate Capture Input (ACI)B, D, GSPT0All BSPT1All D, EChannel A Data DMiscellaneous ESPT2All E, GSPT2_ATDV EMiscellaneous GETH0All B, C, DData CETH0_PHYINT DMiscellaneous B, CADSP-BF60X B LACKFIN P ROCESSOR H ARDWARE R EFERENCE。

FPGA可编程逻辑器件芯片XC2VP7-5FFG672I中文规格书

BurstMin RequirementsBurstMin must be less than or equal to half BurstMax and a multiple of the LBUS width. Channel ChangesChannel changes are only permitted after a burst has been fully written to the LBUS.Status/Control InterfaceThe Status/Control interface allows you to set up the Interlaken IP core configuration and monitor the Interlaken IP core status. The following sections describe the various Status and Control signals.Note:Most of the following status signal descriptions assume a good understanding of the Interlaken Protocol. See the Interlaken Protocol Definition Revision 1.2 document for more details.RX Meta Frame StatusThe Interlaken protocol requires that each lane align or synchronize to incoming words using the procedure described in the Interlaken specification. The Interlaken IP core provides status bits to indicate the state of word boundary synchronization and lane alignment. All signals are synchronous with the rising-edge of LBUS_CLK and a detailed description of each signal is included in this section.STAT_RX_SYNCED[11:0]When a bit of this bus is 0, it indicates that word boundary synchronization of the corresponding lane is not complete or that an error has occurred as identified by another status bit.When a bit of this bus is 1, it indicates that the corresponding lane is word boundary synchronized and is receiving Meta Frame Synchronization Words and Scrambler State Control Words as expected.STAT_RX_SYNCED_ERR[11:0]When a bit of this bus is 1, it indicates one of several possible failures on the corresponding lane:•Word boundary synchronization in the lane was not possible using Framing bits [65:64].•After word boundary synchronization in the lane was achieved, errors were detected on Framing bits [65:64].•After word boundary synchronization in the lane was achieved, a valid Meta Frame Synchronization Word was never received.The bits of the bus remain asserted until word boundary synchronization occurs or until some other error or failure is signaled for the corresponding lane.STAT_RX_MF_LEN_ERR[11:0]When a bit of this bus is 1, it indicates that Meta Frame Synchronization Words are being received but not at the expected rate in the corresponding lane. The transmitter and receiver must be re-configured with the same Meta Frame length.The bits of the bus remain asserted until word boundary synchronization occurs or until some other error or failure is signaled for the corresponding lane.STAT_RX_MF_REPEAT_ERR[11:0]After word boundary synchronization is achieved in a lane, if a bit of this bus is a 1, it indicates one of the following:•Four consecutive invalid Meta Frame Synchronization Words were detected in the corresponding lane.•Three consecutive invalid Scrambler State Control Words were detected in the corresponding lane.The bits of the bus remain asserted until word boundary synchronization occurs or until some other error or failure is signaled for the corresponding lane.STAT_RX_DESCRAM_ERR[11:0]When a bit of this bus is 1, it indicates that a Scrambler State Control Word with an unexpected value was received on the corresponding lane. This bit is only asserted after word boundary synchronization is achieved. This output is asserted for one clock period each time a descrambler error is detected.STAT_RX_MF_ERR[11:0]When a bit of this bus is 1, it indicates that an invalid Meta Frame Synchronization Word was received on the corresponding lane. This bit is only asserted after word boundary synchronization is achieved. This output is asserted for one clock period each time an invalid Meta Frame Synchronization Word is detected.STAT_RX_ALIGNEDWhen STAT_RX_ALIGNED is a value of 1, all of the lanes are aligned or de-skewed as explained in the Interlaken specification and the receiver is ready to receive packet data.STAT_RX_ALIGNED_ERRWhen STAT_RX_ALIGNED_ERR is a value of 1, one of the following occurs:•Lane alignment fails after several attempts•Lane alignment is lost (STAT_RX_ALIGNED is asserted and then it is negated)STAT_RX_FRAMING_ERR[11:0]When a bit of this bus is 1, an illegal framing pattern is detected on the corresponding lane after word boundary synchronization. If this error is detected after lane alignment, the error is treated like a CRC24 error.This output is asserted for one clock period each time an illegal framing pattern is detected.RX Error StatusThe Interlaken IP core provides status signals to identify Interlaken data transmission protocol violations in sequences of Control and Data words. These are errors independent of the status of the Meta Frame. Generally, these signals do not indicate a failure on the part of the sending transmitter but some type of corruption during the transmission.All signals are synchronous with the rising-edge of LBUS_CLK and a detailed description of each signal follows.STAT_RX_CRC24_ERRWhen this signal is a value of 1, it indicates that the error detection logic has identified a mismatch between the expected and received value of CRC24 in a Control Word.Every time a CRC24 error is detected, all open packets are marked as containing errors as specified by the Interlaken Protocol specification. By definition, there is no mechanism provided by Interlaken to associate a CRC24 error with individual packets.This signal is asserted for one clock period each time a CRC24 error is detected.。

FPGA可编程逻辑器件芯片EP2S15F672I3N中文规格书

Symbol

Parameter

Conditions

Minimum Maximum Unit

VOL

Low-level output voltage

IOL = 4 mA (2)

0.45

V

Notes to Tables 5–5: (1) Stratix II devices comply to the narrow range for the supply voltage as specified in the EIA/JEDEC Standard,

Figure 2–58. Stratix II Transmitter Channel

Data from R4, R24, C4, or direct link interconnect

10

10

+

Up to 1 Gbps

–

refclk

Local Interconnect

diffioclk

Fast PLL

For more information on multi-volt support, including information on using TDO and nCEO in multi-volt systems, refer to the Stratix II Architecture chapter in volume 1 of the Stratix II Device Handbook.

JESD8-B. (2) This specification is supported across all the programmable drive strength available for this I/O standard as

FPGA可编程逻辑器件芯片EP1S20F672C7中文规格书

Table 1–19. Clock Tree Performance for Stratix III Devices

Device

EP3SL50 EP3SL70 EP3SL110 EP3SL150 EP3SL200 EP3SE260 EP3SL340 EP3SE50 EP3SE80 EP3SE110

C2

Clock Tree Specifications

Table 1–19 lists the clock tree performance specifications for the logic array, DSP blocks, and TriMatrix Memory blocks for Stratix III devices.

Table 1–13 through Table 1–18 list the Stratix III device family I/O standard specifications. Refer to “Glossary” on page 1–326 for an explanation of terms used in the Table 1–14 through Table 1–18.

Switching Characteristics

This section provides performance characteristics of Stratix III core and periphery blocks for commercial grade devices.

These characteБайду номын сангаасistics can be designated as Preliminary and Final and each designation is defined below.

FPGA可编程逻辑器件芯片EP20K300EFI672-2N中文规格书

UART O PERATING M ODESMDB Transmit OperationIn MDB mode, receive and transmit paths operate completely independently from each other, except for sharing bit rate and frame formats for both transfer directions.Transmit operation is initiated by writing the UART_THR or UART_TAIP registers. A write to the UART_THR register transmits the written word with the appending address bit set low, a write to the UART_TAIPregister transmits the written word with the appended address bit set high. The data is moved into the UART_TSR register, where it is shifted out at the bit rate programmed by the UART_CLK register, with start, stop, address, and parity bits appended as required.If DMA is enabled, the DMA engine always writes the data into the UART_THR register, and the written word is transmitted with the appending address bit set low.The polarity of transmit data is selectable, using the UART_CTL.TPOLC bit.MDB Receive OperationReceive operations use the same data format as the transmit configuration, except that the number of stop bits is always assumed to be 1. After detection of the start bit, the received word is shifted into the UART_ RSR register at the programmed bit.Normally, every incoming bit is sampled at exactly the 7th, 8th and 9th sample clock. If, however, the UART_CLK.EDBO bit is set to achieve better bit rate granularity and accuracy as required at high operation speeds, the bits are roughly sampled at 7/16th, 8/16th and 9/16th of their period. Hardware design should ensure that the incoming signal is stable between 6/16th and 10/16th of the nominal bit period.After the appropriate number of bits (including address, parity, and stop bits) is received, the UART_RSR register is transferred to the receive FIFO and accessible through the UART_RBR register.The polarity of receive data is selectable, using the UART_CTL.RPOLC bit.DMA ModeIn DMA mode, separate receive and transmit DMA channels move data between the UART and memory.The software does not have to move data; it just has to set up the appropriate transfers either through the descriptor mechanism or through autobuffer mode.DMA channels provide a 4-deep FIFO, resulting in total buffer capabilities of 6 words at the transmit side and 9 words at the receive side. In DMA mode, the latency is determined by the bus activity and arbitration mechanism and not by the processor loading and interrupt priorities.To enable UART DMA, first set up the system DMA control registers and then enable the UART_IMSK.ERBFI and/or UART_IMSK.ETBEI interrupts. This is necessary because these interrupt request lines double as DMA request lines. With DMA enabled, once these requests are received, the DMA control unit gener-ates a direct memory access. If DMA is not enabled, the UART interrupt is passed on to the system inter-rupt handling unit.ADSP-BF60X UART R EGISTER D ESCRIPTIONSUsing Core TransfersA core transmit operation is accomplished by writing data into the UART_THR register, when the UART_STAT.THRE bit is set. If the UART_STAT.DR bit is set, received data can be read from the UART_RBR register.Using DMA Transfers1.Make sure that the UART_IMSK.ETBEI or the UART_IMSK.ERBFI bits are cleared before configuring theDMA.2.Configure the dedicated DMA channel.3.Set the UART_IMSK.ETBEI or UART_IMSK.ERBFI bits to start the transfer.Using InterruptsEach UART features three interrupt signal outputs.1.Enable individual interrupts in the system event controller (SEC).2.Register IRQ handlers.e the interrupts mask registers to enable specific IRQ events.Setting Up Hardware Flow Control1.Configure automatic or manual hardware flow control for the receiver through the UART_CTL.ARTS bit,and/or the transmitter through the UART_CTL.ACTS bit.2.Configure UART_CTS and UART_RTS polarity through the UART_CTL.FCPOL bit.ADSP-BF60x UART Register DescriptionsUART (UART) contains the following registers.Table 19-9:ADSP-BF60x UART Register ListName DescriptionUART_CTL Control RegisterUART_STAT Status RegisterUART_SCR Scratch RegisterU NIVERSAL A SYNCHRONOUS R ECEIVER/T RANSMITTER (UART)UART E VENT C ONTROL register in the normal manner. Accordingly, the UART_IMSK.ETBEI bit can be cleared through the UART_IMSK_CLR register if the string transmission has completed.The UART_STAT.THRE bit is cleared by hardware when new data is written to the UART_THR register. These writes also clear the transmit interrupt request. However, they also initiate further transmission. Ifcontinued transmission is not desired, the transmit request can alternatively be cleared through the UART_ IMSK_CLR.ETBEI bit register. Transfers of data from the UART_THR register to the UART_TSR register re-set this status flag in the UART_STAT register.The UART_STAT.TEMT bit can be interrogated to discover any ongoing transmission. The UART_STAT.TEMT bit’s sticky counterpart, UART_STAT.TFI, indicates if the transmit buffer has drained and can trigger a status interrupt, if required. When data is pending in either one of these registers, the UART_STAT.TEMT flag is low. As soon as all data has left the UART_TSR register, the UART_STAT.TEMT bit goes high again and indicates that all pending transmit operations (including stop bits) have finished. At that time it is safe to disable the UART_CTL.EN bit or to three-state off-chip line drivers. By this time an interrupt can be gener-ated either through the status interrupt channel when the UART_IMSK.ETFI bit is set, or through the DMA controller when enabled by the UART_IMSK.EDTPTI bit.When enabled by the UART_IMSK.ETBEI bit, the UART_STAT.THRE flag requests data along the peripheral command lines to the DMA controller (hereafter referred to as TXREQ). This signal is routed through the DMA controller. If the associated DMA channel is enabled, the TXREQ signal functions as a DMA request, otherwise the DMA controller simply forwards it to the SEC. Alternatively the UART_IMSK.ETXS bit can redirect the transmit interrupts to the UART status interrupt.With interrupts disabled, these status flags can be polled to determine when data is ready to move. Note that because polling is processor intensive, it is not typically used in real-time signal processing environ-ments. Since read operations from UART_STAT registers have no side effects, different software threads can interrogate these registers without mutual impacts. Polling the SEC_SSTATn register without enabling the interrupts by the SEC_CCTLn register is an alternate method of operation to consider. Software can write up to two words into the UART_THR register before enabling the UART clock. As soon as the UART_CTL.EN bit is set, those two words are sent.Receive InterruptsReceive interrupts are enabled by the UART_IMSK_SET.ERBFI bit. If set, the UART_STAT.DR flag requests an interrupt on the dedicated RXREQ output, indicating that new data is available in the UART_RBR register.This signal is routed through the DMA controller. If the associated DMA channel is enabled, the RXREQ signal functions as a DMA request; otherwise the DMA controller simply forwards it to the SEC. Alterna-tively, if no DMA channel is assigned to the UART, the UART_IMSK.ERXS bit can redirect the receive inter-rupts to the UART status interrupt. When software reads the UART_RBR register, hardware clears the UART_ STAT.DR bit again, which, in turn, clears the receive interrupt request.。

FPGA可编程逻辑器件芯片EP1S25F672I6N中文规格书

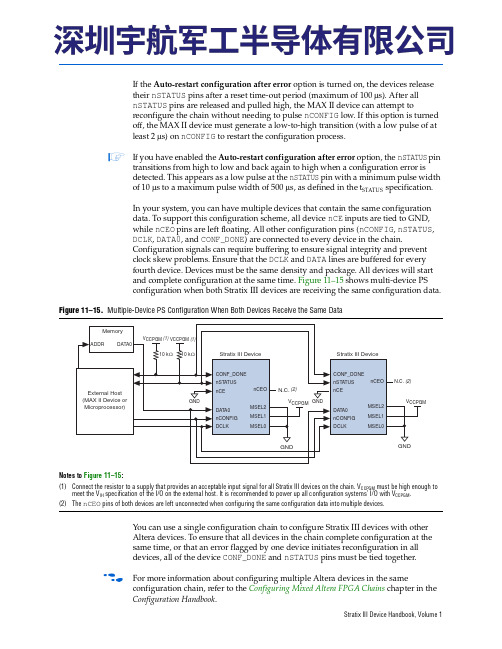

If the Auto-restart configuration after error option is turned on, the devices release their nSTATUS pins after a reset time-out period (maximum of 100μs). After all nSTATUS pins are released and pulled high, the MAX II device can attempt toreconfigure the chain without needing to pulse nCONFIG low. If this option is turned off, the MAX II device must generate a low-to-high transition (with a low pulse of at least 2μs) on nCONFIG to restart the configuration process.1If you have enabled the Auto-restart configuration after error option, the nSTATUS pin transitions from high to low and back again to high when a configuration error is detected. This appears as a low pulse at the nSTATUS pin with a minimum pulse width of 10μs to a maximum pulse width of 500μs, as defined in the t STATUS specification.In your system, you can have multiple devices that contain the same configuration data. To support this configuration scheme, all device nCE inputs are tied to GND, while nCEO pins are left floating. All other configuration pins (nCONFIG , nSTATUS , DCLK , DATA0, and CONF _DONE ) are connected to every device in the chain.Configuration signals can require buffering to ensure signal integrity and prevent clock skew problems. Ensure that the DCLK and DATA lines are buffered for every fourth device. Devices must be the same density and package. All devices will start and complete configuration at the same time. Figure 11–15 shows multi-device PS configuration when both Stratix III devices are receiving the same configuration data.You can use a single configuration chain to configure Stratix III devices with other Altera devices. To ensure that all devices in the chain complete configuration at the same time, or that an error flagged by one device initiates reconfiguration in all devices, all of the device CONF _DONE and nSTATUS pins must be tied together.fFor more information about configuring multiple Altera devices in the sameconfiguration chain, refer to the Configuring Mixed Altera FPGA Chains chapter in the Configuration Handbook .Figure 11–15.Multiple-Device PS Configuration When Both Devices Receive the Same DataNotes to Figure 11–15:(1)Connect the resistor to a supply that provides an acceptable input signal for all Stratix III devices on the chain. V CCPGM must be high enough tomeet the V IH specification of the I/O on the external host. It is recommended to power up all configuration systems’ I/O with V CCPGM .(2)The nCEO pins of both devices are left unconnected when configuring the same configuration data into multiple devices.Chapter 11:Configuring Stratix III DevicesPassive Serial ConfigurationPS Configuration TimingFigure 11–16 shows the timing waveform for PS configuration when using a MAX II device as an external host.Table 11–10 defines the timing parameters for Stratix III devices for PS configuration.Figure 11–16.PS Configuration Timing Waveform (Note 1)Notes to Figure 11–16:(1)The beginning of this waveform shows the device in user-mode. In user-mode, nCONFIG , nSTATUS , and CONF_DONE a re at logic high levels.When nCONFIG is pulled low, a reconfiguration cycle begins.(2)Upon power-up, the Stratix III device holds nSTATUS low for the time of the POR delay.(3)Upon power-up, before and during configuration, CONF_DONE is low .(4)Do not leave DCLK floating after configuration. You should drive it high or low, whichever is more convenient. DATA[0] is available as a userI/O pin after configuration. The state of this pin depends on the dual-purpose pin settings.(5)Two DCLK falling edges are required after CONF_DONE goes high to begin the initialization of the device.nCO N FIGnSTATUS (2)CO N F_DO N E (3)DCLK DATAUser I/OI N IT_DO NEt Table 11–10.PS Timing Parameters for Stratix III Devices (Part 1 of 2)Chapter 11:Configuring Stratix III DevicesPassive Serial ConfigurationTable11–10.PS Timing Parameters for Stratix III Devices (Part 2 of 2)Notes to Table11–10:(1)This value is applicable if you do not delay configuration by extending the nCONFIG or nSTATUS low pulse width.(2)The minimum and maximum numbers apply only if you choose the internal oscillator as the clock source for starting the device.f Device configuration options and how to create configuration files are discussedfurther in the Device Configuration Options and Configuration File Format s chapters involume 2 of the Configuration Handbook.PS Configuration Using a MicroprocessorIn this PS configuration scheme, a microprocessor can control the transfer ofconfiguration data from a storage device, such as flash memory, to the target Stratix IIIdevice.f You can do a PS configuration using MicroBlaster™ Passive Serial Software Driver.For more information, refer to AN423: Configuring the MicroBlaster Passive SerialSoftware Driver.1For all configuration and timing information, refer to “PS Configuration Using a MAX II Device as an External Host” on page11–27. This section is also applicablewhen using a microprocessor as an external host.PS Configuration Using a Download CableIn this section, the generic term download cable includes the Altera USB-Blaster USBport download cable, MasterBlaster™ serial/USB communications cable,ByteBlaster II parallel port download cable, ByteBlasterMV™ parallel port downloadcable, and the EthernetBlaster download cable.In PS configuration with a download cable, an intelligent host (such as a PC) transfersdata from a storage device to the device by using the USB-Blaster, MasterBlaster,ByteBlaster II, EthernetBlaster, or ByteBlasterMV cable.Chapter 11:Configuring Stratix III DevicesPassive Serial ConfigurationChapter 11:Configuring Stratix III DevicesJTAG ConfigurationJTAG ConfigurationThe JTAG has developed a specification for boundary-scan testing. Thisboundary-scan test (BST) architecture offers the capability to efficiently testcomponents on PCBs with tight lead spacing. The BST architecture can test pinconnections without using physical test probes and capture functional data while adevice is operating normally. You can also use the JTAG circuitry to shiftconfiguration data into the device. The Quartus II software automatically generatesSOFs that can be used for JTAG configuration with a download cable in the Quartus IIsoftware programmer.f For more information about JTAG boundary-scan testing and commands availableusing Stratix III devices, refer to the following documents:■IEEE 1149.1 (JTAG) Boundary Scan Testing in Stratix III Device chapter of theStratix III Device Handbook■AN 425: Using the Command-Line Jam STAPL Solution for Device ProgrammingStratix III devices are designed such that JTAG instructions have precedence over anydevice configuration modes. Therefore, JTAG configuration can take place withoutwaiting for other configuration modes to complete. For example, if you attempt JTAGconfiguration of Stratix III devices during PS configuration, PS configuration isterminated and JTAG configuration begins.1You cannot use the Stratix III decompression or design security features if you are configuring your Stratix III device when using JTAG-based configuration.1 A device operating in JTAG mode uses four required pins, TDI, TDO, TMS, and TCK,and one optional pin, TRST. The TCK pin has an internal weak pull-down resistor,while the TDI, TMS, and TRST pins have weak internal pull-up resistors (typically25kΩ). JTAG output pin TDO and all JTAG input pins are powered by thepower supply of I/O bank 1A. All the JTAG pins support2.5V/3.0V/3.3V VCCPDonly LVTTL I/O standard.All user I/O pins are tri-stated during JTAG configuration. Table11–11 explains eachJTAG pin's function.f The TDO output is powered by the Vpower supply of I/O bank 1A. ForCCPDrecommendations on how to connect a JTAG chain with multiple voltages across thedevices in the chain, refer to the IEEE 1149.1 (JTAG) Boundary Scan Testing in Stratix IIIDevices chapter of the Stratix III Device Handbook.。

FPGA可编程逻辑器件芯片EP2S60F672C3N中文规格书

DC & Switching Characteristics

Table 5–78. Maximum Output Toggle Rate on Stratix II Devices (Part 3 of 5) Note (1)

I/O Standard

Drive Strength

Column I/O Pins (MHz)

-

-

- 550 500 500

-

-

- 550 550 550

350

300 300 350 300 300

500

500 450 500 500 450

700

650 600 700 650 600

-

-

- 700 700 650

-

-

- 700 700 700

-

-

- 600 600 550

-

-

- 650 600 600

4 mA 6 mA 8 mA 10 mA 12 mA 8 mA 16 mA 18 mA 20 mA 4 mA 6 mA 8 mA 10 mA 12 mA 16 mA 18 mA 20 mA 4 mA 6 mA 8 mA 10 mA 12 mA 16 mA 18 mA 20 mA 8 mA 12 mA 16 mA 20 mA 24 mA

Column I/O Pins (MHz) Row I/O Pins (MHz)

-3 -4

-5

-3 -4

-5

500 500 450 500 500 450 500 500 450 500 500 450 500 500 450 500 500 450 500 500 450 500 500 450 500 500 450 500 500 450 500 500 500 500 500 500 500 500 500 500 500 500 500 500 500 500 500 500 500 500 500 500 500 500 500 500 500 500 500 500 500 500 500 500 500 500 500 500 500 500 500 500

FPGA可编程逻辑器件芯片EP2S60F672C5中文规格书

Operating ConditionsStratix ®II devices are offered in both commercial and industrial grades. Industrial devices are offered in -4 speed grades and commercial devices are offered in -3 (fastest), -4, -5 speed grades.Tables 5–1 through 5–32 provide information about absolute maximum ratings, recommended operating conditions, DC electrical characteristics, and other specifications for Stratix II devices.Absolute Maximum RatingsTable 5–1 contains the absolute maximum ratings for the Stratix II device family.Table 5–1.StratixII Device Absolute Maximum Ratings Notes (1), (2), (3)SymbolParameterConditionsMinimumMaximumUnitV CCINT Supply voltage With respect to ground –0.5 1.8V V CCIO Supply voltage With respect to ground –0.5 4.6V V CCPD Supply voltageWith respect to ground –0.5 4.6V V CCA Analog power supply for PLLsWith respect to ground–0.5 1.8V V CCD Digital power supply for PLLs With respect to ground –0.5 1.8V V I DC input voltage (4)–0.5 4.6V I OUT DC output current, per pin –2540mA T STG Storage temperature No bias–65150°C T J Junction temperatureBGA packages under bias–55125°CNotes to Tables 5–1(1)See the Operating Requirements for Altera Devices Data Sheet .(2)Conditions beyond those listed in Table 5–1 may cause permanent damage to a device. Additionally, device operation at the absolute maximum ratings for extended periods of time may have adverse affects on the device.(3)Supply voltage specifications apply to voltage readings taken at the device pins, not at the power supply.(4)During transitions, the inputs may overshoot to the voltage shown in Table 5–2 based upon the input duty cycle. The DC case is equivalent to 100% duty cycle. During transitions, the inputs may undershoot to –2.0 V for input currents less than 100mA and periods shorter than 20ns.SII51005-4.5Stratix II Device Handbook, Volume 1DC & Switching Characteristics1.8-V HSTL Class II 1.6600.830 1.6600.831.5-V HSTL Class I1.3750.688 1.3750.68751.5-V HSTL Class II 1.3750.688 1.3750.68751.2-V HSTL with OCT 1.1400.570 1.1400.570Differential SSTL-2 Class I2.3251.1632.3251.1625Table 5–35.Timing Measurement Methodology for Input Pins (Part 2 of 2)Notes (1)–(4)I/O StandardMeasurement Conditions Measurement PointV CCIO (V)V REF (V)Edge Rate (ns)V M E A S (V)Timing Model1The performance numbers in Table5–36 are extracted from theQuartus II software version 5.1 SP1.Table5–36.Stratix II Performance Notes(Part 1 of6)Note(1)ApplicationsResources Used PerformanceALUTsTriMatrixMemoryBlocksDSPBlocks-3SpeedGrade(2)-3SpeedGrade(3)-4SpeedGrade-5SpeedGradeUnitLE16-to-1multiplexer(4)2100654.87625.0523.83460.4MHz32-to-1 multiplexer (4)3800519.21473.26464.25384.17MHz16-bit counter1600566.57538.79489.23421.05MHz64-bit counter6400244.31232.07209.11181.38MHzT riMatrix Memory M512 block Simple dual-port RAM32 × 18 bit010500.00476.19434.02373.13MHz FIFO 32 x 18 bit 2210500.00476.19434.78373.13MHzT riMatrix Memory M4K block Simple dual-port RAM128 x 36 bit (8)010540.54515.46469.48401.60MHzT rue dual-port RAM128 × 18 bit (8)010540.54515.46469.48401.60MHzFIFO128 × 36 bit2210530.22499.00469.48401.60MHzSimple dual-port RAM128 × 36 bit (9)010475.28453.30413.22354.10MHzT rue dual-port RAM128 × 18 bit (9)010475.28453.30413.22354.10MHzStratix II Device Handbook, Volume 1DC & Switching CharacteristicsT riMatrix Memory M-RAM block Single portRAM 4K × 144 bit010349.65333.33303.95261.09MHzSimple dual-portRAM 4K × 144 bit010420.16400.00364.96313.47MHzT rue dual-portRAM 4K × 144 bit010349.65333.33303.95261.09MHzSingle portRAM 8K × 72 bit010354.60337.83307.69263.85MHzSimple dual-portRAM 8K × 72 bit010420.16400.00364.96313.47MHzT rue dual-portRAM 8K × 72 bit010349.65333.33303.95261.09MHzSingle portRAM 16K × 36 bit010364.96347.22317.46271.73MHzSimple dual-portRAM 16K × 36 bit010420.16400.00364.96313.47MHzT rue dual-portRAM 16K × 36 bit010359.71342.46313.47268.09MHzSingle portRAM 32K × 18 bit010364.96347.22317.46271.73MHzSimple dual-portRAM 32K × 18 bit010420.16400.0364.96313.47MHzT rue dual-portRAM 32K × 18 bit010359.71342.46313.47268.09MHzSingle portRAM 64K × 9 bit010364.96347.22317.46271.73MHzSimple dual-portRAM 64K × 9 bit010420.16400.0364.96313.47MHzT rue dual-portRAM 64K × 9 bit010359.71342.46313.47268.09MHzTable5–36.Stratix II Performance Notes(Part 2 of6)Note(1)ApplicationsResources Used PerformanceALUTsTriMatrixMemoryBlocksDSPBlocks-3SpeedGrade(2)-3SpeedGrade(3)-4SpeedGrade-5SpeedGradeUnitStratix II Device Handbook, Volume 1Timing ModelDSP block 9 × 9-bit multiplier(5) 001430.29409.16373.13320.10MHz 18 × 18-bitmultiplier(5)001410.17390.01356.12305.06MHz18 × 18-bitmultiplier(7)001450.04428.08391.23335.12MHz36 × 36-bitmultiplier(5)001250.00238.15217.48186.60MHz36 × 36-bit multiplier(6)001410.17390.01356.12305.06MHz18-bit, four-tap FIRfilter001410.17390.01356.12305.06MHzLarger designs 8-bit,16-tap parallelFIR filter5804259.06240.61217.15185.01MHz8-bit, 1024-point,streaming, threemultipliers and fiveadders FFT function2976229398.72364.03355.23306.37MHz8-bit, 1024-point,streaming, fourmultipliers and twoadders FFT function27812212398.56409.16347.22311.13MHz8-bit, 1024-point,single output, oneparallel FFT engine,burst, three multipliersand five adders FFTfunction98453425.17365.76346.98292.39MHz8-bit, 1024-point,single output, oneparallel FFT engine,burst, four multipliersand two adders FFTfunction91954427.53378.78357.14307.59MHzTable5–36.Stratix II Performance Notes(Part 3 of6)Note(1)ApplicationsResources Used PerformanceALUTsTriMatrixMemoryBlocksDSPBlocks-3SpeedGrade(2)-3SpeedGrade(3)-4SpeedGrade-5SpeedGradeUnitStratix II Device Handbook, Volume 1。

FPGA可编程逻辑器件芯片EP2S30F672I4NN中文规格书

290

462

484

530

618

ps

543

569

898

941

1031

1201 ps

277

290

462

484

530

618

ps

560

587

993

1041

1141

1329 ps

294

308

557

584

640

746

ps

Stratix II Device Handbook, Volume 1

DC & Switching Characteristics

Table 5–75. Stratix II I/O Output Delay for Column Pins (Part 3 of 8)

I/O Standard

Drive Strength

Parameter

1.8 V

2 mA

tO P

tD I P

4 mA

tO P

tD I P

6 mA

tO P

tD I P

Stratix II Device Handbook, Volume 1

Timing Model

Table 5–75. Stratix II I/O Output Delay for Column Pins (Part 6 of 8)

I/O Standard

Drive Strength

Parameter

-5 Speed Grade

Unit

1042

1093

2904 3048 3338 3472 ps

1062

1115

2970 3118 3414 3562 ps

FPGA可编程逻辑器件芯片EP2S15F672I6N中文规格书

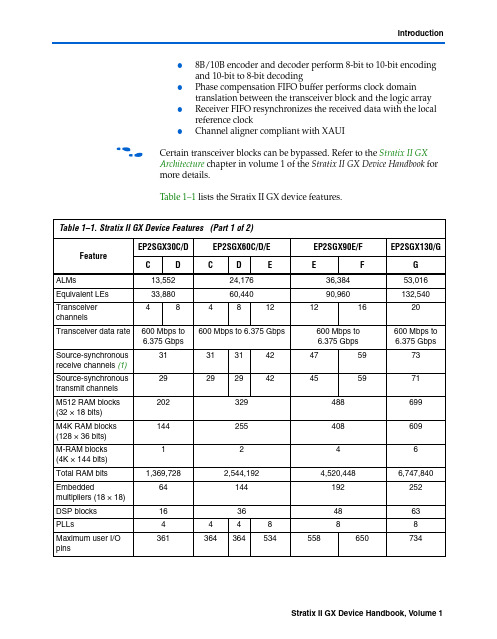

Introduction●8B/10B encoder and decoder perform 8-bit to 10-bit encodingand 10-bit to 8-bit decoding●Phase compensation FIFO buffer performs clock domaintranslation between the transceiver block and the logic array●Receiver FIFO resynchronizes the received data with the localreference clock●Channel aligner compliant with XAUIf Certain transceiver blocks can be bypassed. Refer to the Stratix II GXArchitecture chapter in volume 1 of the Stratix II GX Device Handbook formore details.Table1–1 lists the Stratix II GX device features.Table1–1.Stratix II GX Device Features (Part 1 of2)Feature EP2SGX30C/D EP2SGX60C/D/E EP2SGX90E/F EP2SGX130/G C D C D E E F GALMs13,55224,17636,38453,016 Equivalent LEs33,88060,44090,960132,540 Transceiverchannels484812121620Transceiver data rate600 Mbps to6.375Gbps 600 Mbps to 6.375Gbps600 Mbps to6.375 Gbps600 Mbps to6.375 GbpsSource-synchronousreceive channels (1)31313142475973Source-synchronoustransmit channels29292942455971M512 RAM blocks(32×18bits)202329488699M4K RAM blocks(128×36bits)144255408609M-RAM blocks(4K×144 bits)1246 Total RAM bits1,369,7282,544,1924,520,4486,747,840 Embeddedmultipliers (18×18)64144192252 DSP blocks16364863 PLLs444888 Maximum user I/Opins361364364534558650734Document Revision Historyload acts as a preset when the asynchronous load data input is tied high.When the asynchronous load/preset signal is used, the labclkena0signal is no longer available.The LAB row clocks [5..0] and LAB local interconnect generate theLAB-wide control signals. The MultiTrack™ interconnects haveinherently low skew. This low skew allows the MultiTrack interconnectsto distribute clock and control signals in addition to data.Figure2–34 shows the LAB control signal generation circuit.Figure2–B-Wide Control SignalsAdaptive Logic ModulesAdaptive Logic Modules The basic building block of logic in the Stratix II GX architecture is the ALM. The ALM provides advanced features with efficient logic utilization. Each ALM contains a variety of look-up table (LUT)-based resources that can be divided between two adaptive LUTs (ALUTs). With up to eight inputs to the two ALUTs, one ALM can implement various combinations of two functions. This adaptability allows the ALM to be completely backward-compatible with four-input LUT architectures. One ALM can also implement any function of up to six inputs and certain seven-input functions.In addition to the adaptive LUT-based resources, each ALM contains two programmable registers, two dedicated full adders, a carry chain, a shared arithmetic chain, and a register chain. Through these dedicated resources, the ALM can efficiently implement various arithmetic functions and shift registers. Each ALM drives all types of interconnects: local, row, column, carry chain, shared arithmetic chain, register chain, and direct link interconnects. Figure2–35 shows a high-level block diagram of the Stratix II GX ALM while Figure2–36 shows a detailed view of all the connections in the ALM.Figure2–35.High-Level Block Diagram of the Stratix II GX ALM。

FPGA可编程逻辑器件芯片EP2AGX260FF35I6N中文规格书

P ULSE-W IDTH M ODULATOR (PWM)F UNCTIONAL D ESCRIPTIONSwitching Dead Time (PWM_DT) RegisterThe second important parameter that must be set up in the initial configuration of the PWM Controller is the switching dead time. This is a short delay introduced between turning off one PWM signal (forexample, AH) and turning on the complementary signal (for example, AL). This short time delay permits the power switch being turned off (AH in this case) to completely recover its blocking capability before the complementary switch is turned on. This time delay prevents a potentially destructive short-circuit condi-tion from developing across the dc link capacitor of a typical voltage source inverter.The 10-bit, read/write PWM_DT register controls the dead time. This register controls the dead time inserted into the three pairs of PWM output signals. Dead time (T d) is related to the value in the PWM_DT register by: T d = PWM_DT × 2 × t SCLKTherefore, a PWM_DT value of 0x00A introduces a 200 ns delay (for a SCLK of 100 MHz) between turning off any PWM signal (for example, AH) and then turning on its complementary signal (for example, AL).The length of the dead time can therefore be programmed in increments of 2 × t SCLK (or 20 ns for an SCLK of 100 MHz). The PWM_DT register is a 10-bit register whose maximum value of 0x3FF (1023 decimal) corresponds to a maximum programmed dead time of:T d(max) = 1023 × 2 × t SCLK = 1023 × 2 × 10 × 10-9 = 20.5 μsfor an f SCLK rate of 100 MHz. The dead time can be programmed to be zero by writing 0 to the PWM_DT register.Duty Cycle with Dead-Time Control: Calculations for PULSEMODE 00The duty cycle registers are scaled such that a value of 0 represents a 50% PWM duty, cycle. The switching signals produced are also adjusted to incorporate the programmed dead time value in the PWM_DT register.The unit in this case produces active low signals so that a low level corresponds to a command to turn on the associated power device.A typical pair of PWM outputs, PWM_AH and PWM_AL, is shown in the following figure. The time values inthe figure indicate the integer value in the associated register and can be converted to time by multiplying by the fundamental time increment, t CK. In the example channel A is working off of PWMTMR0.Because PULSEMODE is set to 00, the switching patterns are perfectly symmetrical about the mid-point of the switching period. The dead time is incorporated by moving the switching instants of both PWM signals away from the instant set by the PWM_AH0 register. Both switching edges are moved by an equal amount (PWMDT × t CK) to preserve the symmetrical output patterns. Also shown is the PWM_SYNC_OUT pulse whose rising edge denotes the beginning of the switching period, and the PWM_STAT.TMR0PHASE bit.ADSP-BF60X B LACKFIN P ROCESSOR H ARDWARE R EFERENCEP ULSE -W IDTH M ODULATOR (PWM)E VENT C ONTROLADSP-BF60X B LACKFIN P ROCESSOR H ARDWARE R EFERENCEeven in the event of a loss of the processor clock. In addition to the hardware shutdown features, the PWM system may be shutdown in software by means of the PWM_CTL.SWTRIP bit.Status information about the PWM is available to the user in the PWM_STAT register, which stores all status bits, including raw interrupt status bits. In particular, the period boundary of each timer is available, as well as status bits that indicate whether the operation is in the first half or the second half of the timer. Addi-tionally the TRIP status is also available.The PWM_IMSK and PWM_ILAT registers allow masking and show masked interrupt status bits respectively. The interrupt bits are latched and held on the interrupt event and the software must write a 1 to clear the interrupt bit, usually during the Interrupt Service routine.Trip Control UnitThe PWM Trip unit processes hardware or software fault conditions and shuts down the PWM channel outputs immediately on the occurrence of these conditions. This shut down mechanism can be enabled separately for each channel. The design also allows for a self-restart mechanism to be enabled on a channel. Self-restart re-enables the channel outputs following the fault condition (allowed only on hardware trips) when the PWMTMR-y that the channel is using reaches its period boundary.There are 2 external hardware sources that can indicate a hardware fault condition:1.PWMTRIP0 input pin2.PWMTRIP1 input pinThese are active low inputs where a falling edge on either of these pins indicates a fault condition.To enable the trip unit to shut down a particular channel's output in response to the fault event on either of these PWM_TRIPn pins, program the PWM_TRIPCFG.EN0A bit corresponding to that channel.The PWM_TRIPCFG.MODE0A bits must be programmed to specify the restart mechanism for a channel that has been tripped.1.If PWM_TRIPCFG.MODE0A = 0, once tripped, a trip condition is registered on this channel in the PWM_STAT.FLTTRIPA bit and the outputs of that channel are immediately shut down. This is called a FAULT TRIP condition. To resume channel output when a FAULT TRIP occurs, clear the PWM_STAT.FLTTRIPA bit by writing a 1 to it. Note that the bit cannot be cleared by a processor write if the trip condition is still active. The RAW trip status is available for both the pins in the PWM_STAT.RAWTRIP0register bits.2.If PWM_TRIPCFG.MODE0A = 1, once tripped, a trip condition is registered on this channel in the PWM_STAT.SRTRIPA bit and the outputs of that channel are immediately shut down. This is called a self-restart trip condition. At the next period boundary of the PWMTMR-y that the channel is using, if the tripping condition is not active, the design clears the status register bit and restores the outputs.The trip input pins should have an external pull-down resistor on the chip pin, so that if the pin becomes unconnected the PWM will be disabled.P ULSE-W IDTH M ODULATOR (PWM)F UNCTIONAL D ESCRIPTIONFigure 18-15:XOVR and DISHI/DISLO FunctionalityBrushless DC Motor (Electronically Commutated Motor) ControlIn the control of an electronically commutated motor (ECM), only two inverter legs are switched at any time. Often, the high-side device in one leg must be switched on at the same time as the low-side driver ina second leg. Therefore, by programming identical duty cycles values for two PWM channels (for example,PWM_CHA = PWM_CHB) and setting the PWM_BCTL.XOVR bit to crossover the BH/BL pair if PWM signals, it is possible to turn on the high-side switch of phase A and the low-side switch of phase B at the same time.To control ECM, normally the third inverter leg (phase C in this example) is disabled for a number of PWM cycles. To implement this function, both the PWM_CH and PWM_CL outputs are disabled by setting the PWM_CCTL.DISHI and PWM_CCTL.DISLO bits.In normal ECM operation, each inverter leg is disabled for certain time periods so that the PWM channel registers change based on the position of the rotor shaft (motor commutation).ADSP-BF60X B LACKFIN P ROCESSOR H ARDWARE R EFERENCE。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。