5550LN103K4中文资料

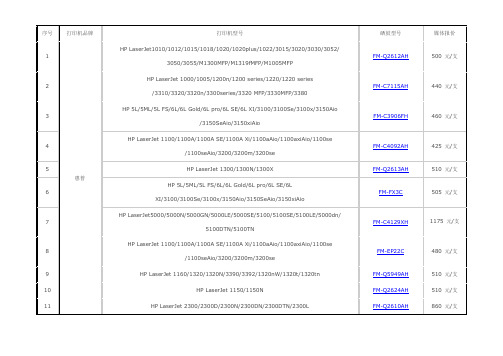

硒鼓型号对照表

1090元/支

20

HP LaserJet 5200/5200L/5200LN/5200dtn/5200n/5200tn/5200Lx

FM-Q7516AH

1150元/支

21

HP LaserJet P2015d/2010/2014/2014n/M2727nfMFP/M2727nfsMFP

FM-C3906FH

460元/支

4

HP LaserJet 1100/1100A/1100ASE/1100AXi/1100aAio/1100axiAio/1100se

/1100seAio/3200/3200m/3200se

FM-C4092AH

425元/支

5

HP LaserJet 1300/1300N/1300X

FM-C972Color LaserJet 4600/4600n/4600dn/4600dtn/4600hdn/4650dn/4650dtn/4650hdn

FM-C9723AH

1505元/支

32

HP Color LaserJet 1500/1500L/2500/2500L/2500n/2500tn/2550/2550L/2550n/

5100DTN/5100TN

FM-C4129XH

1175元/支

8

HP LaserJet 1100/1100A/1100ASE/1100AXi/1100aAio/1100axiAio/1100se

/1100seAio/3200/3200m/3200se

FM-EP22C

480元/支

9

HP LaserJet 1160/1320/1320N/3390/3392/1320nW/1320t/1320tn

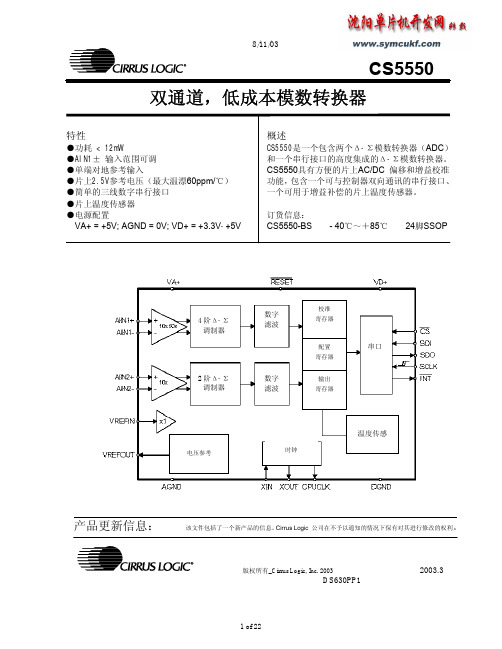

双通道低成本模数转换器cs5550中文

4 寄存器描述…………………………………………………………………………..…………………..18 4.1 配置寄存器………………………………………………………………………………...18 4.2 DC偏移寄存器…………………………………………………………………………...19 4.3 AC/DC增益寄存器……………………………………………………………………..19 4.4 周期计数寄存器…………………………………………………………………………...19 4.5 输出寄存器………………………………………………………………………………...20 4.6 滤波输出寄存器…………………………………………………………………………...20 4.7 状态寄存器和屏蔽寄存器………………………………………………………………...20 4.8 AC偏移寄存器…………………………………………………………………………...21 4.9 温度传感器数据输出寄存器………………………...……………………………………21 4.10 控制寄存器………………………………………………………………………………...21

4 of 22

8/11/03

1. 特性与规格说明 . 最大值和最小值参数是指在所有的操作条件可被保证的值.

. 典型参数是在标准供电和25°C时的测量值. . DGND = 0V.所有电压是指对 0V 的电压值.

模拟特性

参数

符号 最小值

精度(两个通道)

共模抑制比

CMRR

80

偏移漂移

-

模拟输入(AIN1±) 差分输入范围 {(AIN1+) - (AIN1- )}

测量和参考输入

差分模拟输入9,10,15,16 AIN1+, AIN1-, AIN2+, AIN2- —差分模拟输入引脚。

LNSK10中文资料

FEATURESMultilayer structure allows diverse resistance value in the same B constantMultilayer structure allows lower resistance at high B constant.Solder plating with Ni barrier gives high reliability for both flow and reflow soldering.Unified shape and tightly controlled dimension is fit to high mounting speed.APPLICATIONSTemperature compensation for crystal oscillator (TCXO)Temperature compensation for Personal computer Temperature detection for CPU and memory device Temperature detection for battery packTemperature compensation for contrast of LCDLNS V 16 G 103 J PDESCRIPTIONThe LNS series is manganese oxide based NTC thermistor,which shows non-linear resistance-temperature behavior.Multilayered structure has as high reliability as monoblock type,even without protective glass coating, since the active electrode and sensor layer is buried inside the ceramic body.NTC Thermistor SMDSeries B constantZ 3250K K 3435K Y 3670K W 3890K A 3970K V 4150K U 4550K T 4750KChip size (mm)10 1.0 x 0.5 x 0.5 (inches 0402)16 1.6 x 0.8 x 0.8 (inches 0603)202.0 x 1.2 x 0.8 (inches 0805)Resistance at 25 ¡10110 ¡¿101= 100¥10210 ¡¿102= 1 K ¥10310 ¡¿103= 10 K ¥PackageP Paper taping E Emboss taping BBulkResistance deviation rangeF ¡1£¥H ¡3£¥J ¡5£¥K¡10£¥ORDERING INFORMATIONB constant deviation rangeF ¡1%G ¡2%H¡3%SPECIFICATIONS1005(0402) sizeResistance @ 25o CThe zero-power resistance at the standard temperature of 25o C. The zero-power resistance means the value of DC resistance of a thermistor measured at a specified temperature, with electric load being kept so small that there is no noticeable change in the measured resistance by the influence of the applied electric load.Bconstant 25 / 85B = ln(R0/R1) / (1/T- 1/T1) Without special note, B constant is calculated from the resistance values at 25o C and 85o C[B25/85], which is the most common.Dissipation constant (¥‰)Dissipation factor is defined as the ratio at a specified ambient temperature of a change in power dissipation in a thermistor to the resultant body temperature change.¡⁄¥= P/( T1- 25o C) mW/ o C¡⁄P : dissipated power¡⁄T1 : thermistor temp, 85¡0.1o CMaximum power rating PThis is the maximum handling power, keeping its temperature not exceeding the allowed maximum temperature for operation.¡⁄P max = ¥(T max- T a)¡⁄¥:dissipation constant¡⁄T a:25o C¡⁄T max:125o CThermal Time ConstantThe time necessary for an unloaded thermistor to vary its temperature by 63.2%of the difference between its initial and final temperatures. Initial temperature is 85¡0.1o C and final1608(0603) sizeResistance @ 25o CThe zero-power resistance at the standard temperature of 25o C. The zero-power resistance means the value of DC resistance of a thermistor measured at a specified temperature, with electric load being kept so small that there is no noticeable change in the measured resistance by the influence of the applied electric load.Bconstant 25 / 85B = ln(R0/R1) / (1/T- 1/T1) Without special note, B constant is calculated from the resistance values at 25o C and 85o C[B25/85], which is the most common.Dissipation constant (¥‰)Dissipation factor is defined as the ratio at a specified ambient temperature of a change in power dissipation in a thermistor to the resultant body temperature change.¡⁄¥= P/( T1- 25o C) mW/ o C¡⁄P : dissipated power¡⁄T1 : thermistor temp, 85¡0.1o CMaximum power rating PThis is the maximum handling power, keeping its temperature not exceeding the allowed maximum temperature for operation.¡⁄P max = ¥(T max- T a)¡⁄¥:dissipation constant¡⁄T a:25o C¡⁄T max:125o CThermal Time ConstantThe time necessary for an unloaded thermistor to vary its temperature by 63.2%of the difference between its initial and final temperatures. Initial temperature is 85¡0.1o C and final temperature is 47.1¡0.1o C.Resistance @ 25o CThe zero-power resistance at the standard temperature of 25o C . The zero-power resistance means the value of DC resistance of a thermistor measured at a specified temperature,with electric load being kept so small that there is no noticeable change in the measured resistance by the influence of the applied electric load.Bconstant 25 / 85B = ln(R 0/R 1) / (1/T 0- 1/T 1) Without special note, B constant is calculated from the resistance values at 25oC and 85o C [B25/85], which is the most common.Dissipation constant (¥‰)Dissipation factor is defined as the ratio at a specified ambient temperature of a change in power dissipation in a thermistor to the resultant body temperature change. ¡⁄¥= P/( T 1- 25o C ) mW/ o C ¡⁄P : dissipated power ¡⁄T1 : thermistor temp, 85¡0.1o C Maximum power rating PThis is the maximum handling power, keeping its temperature not exceeding the allowed maximum temperature for operation. ¡⁄P max = ¥(T max - T a )¡⁄¥:dissipation constant ¡⁄T a :25o C ¡⁄T max :125o C Thermal Time ConstantThe time necessary for an unloaded thermistor to vary its temperature by 63.2%of the difference between its initial and final temperatures. Initial temperature is 85¡0.1o C and final temperature is 47.1¡0.1o C .2012(0805) sizeRESISTANCE VS. TEMPERATURE TABLERELIABILITY TEST METHODStructure and Dimension CHIP STRUCTURECHIP DIMENSIONSize A B C D E F G H Jtnote 1608 1.0¡0.1 1.9¡0.18.0¡0.1 3.5¡0.05 1.75¡0.1 4.0¡0.1 2.0¡0.05 4.0¡0.1 1.5+0.1-0.00.23¡0.02paper 10050.62¡0.04 1.12¡0.048.0¡0.1 3.5¡0.05 1.75¡0.1 4.0¡0.1 2.0¡0.05 4.0¡0.1 1.5+0.1-0.00.6¡0.05paperTape and Reel Packaging for Paper PackageStructure of TapingTaping must have leader and empty component compartment as shown in the following figure.Size A B W F E P1P2P0D0t1t2note 3216 1.73¡0.1 3.56¡0.18.0+0.3-0.1 3.5¡0.05 1.75¡0.1 4.0¡0.1 2.0¡0.05 4.0¡0.1 1.5+0.1-0.00.23¡0.02 1.14¡0.1emboss 2012 1.45¡0.1 2.25¡0.18.0+0.3-0.1 3.5¡0.05 1.75¡0.1 4.0¡0.1 2.0¡0.05 4.0¡0.1 1.5+0.1-0.00.23¡0.02 1.0¡0.1embossTape and Reel Packaging for Emboss PackagePackage Quantity12,000(pcs/Reel) - 1005 size4,000(pcs/Reel) - 1608, 2012, 3216 sizePackagingRecommended Land PatternSolderingHand soldering : 280o C max., 5sec max.Reflow profileComponent LayoutLocate the product horizontal to the direction at which bending is applied.Component MountingSMT Process CharacteristicsSolder and FluxSolder : Eutetic solder recommended Flux : Rosin based flux recommendedHalogen content 0.2 w% or less recommendedFlow profile。

京瓷零件手册TASKalfa 3050ci 3550ci 4550ci 5550ci零件手册

Part.No.

302LC04031 302LC04051 302LC04063 302LC04071 302LC04191 302LC04200 302LC04212 302LC04250 302LC04260 302LC04280 302LC04290 302LC04410 302LC04720 302LC04651 302LC34050 302LC04271 302LC34010 302LM34010 302LN34010 302LK34010 2FB04270 302FZ04950 302LC04011 302LC94520 302LC04460 302LC04490 302LC04500 302H094300 302LC02710 302LC02720 302LC02730 302LC02760 302LC04240 302LC46230 302LC04730 302LC04751 302LW04260 302LC04740

-1-

FIG. 1 Covers 1

2LK/2LN/2LM/2LC-3

6

101

13

1

101ALeabharlann 5 71013

8

104

35 22 22 34 33 23 18 24

104 104 104 104 102 A 105 104 104 102 101

104

12 11

34 14 32

22

22

15 28 30 27 25 26

Description

COVER TOP TRAY COVER RIGHT LOWER F COVER RIGHT MIDDLE R COVER RIGHT LOWER R COVER EXIT COVER TRAY REAR COVER ISU BOTTOM COVER INNER LEFT COVER INNER FEED F COVER HANDLE COVER MAIN SWITCH MOUNT FRONT COVER LEFT STOPPER ORIGINAL STRAP FRONT COVER LABEL SW CAUTION EN EMBLEM SHEET EMBLEM 5550C SHEET EMBLEM 4550C SHEET EMBLEM 3550C SHEET EMBLEM 3050C PLATE MAGNET SPONGE TRAY WASTE COVER FRONT A PARTS COVER FRONT SP STOPPER CONTAINER PLATE FRONT COVER SPONGE COVER FRONT PARTS,HUMIDITY SENSOR,SP COVER HUMIDITY SENSOR SHEET HUMIDITY SENSOR A SHEET HUMIDITY SENSOR B SHEET COVER HUMIDITY SENSOR COVER FRONT RIGHT LOWER WIRE FRONT LOW SHEET COVER FRONT SPONGE COVER FRONT B SPACER USB SHEET COVER FRONT B

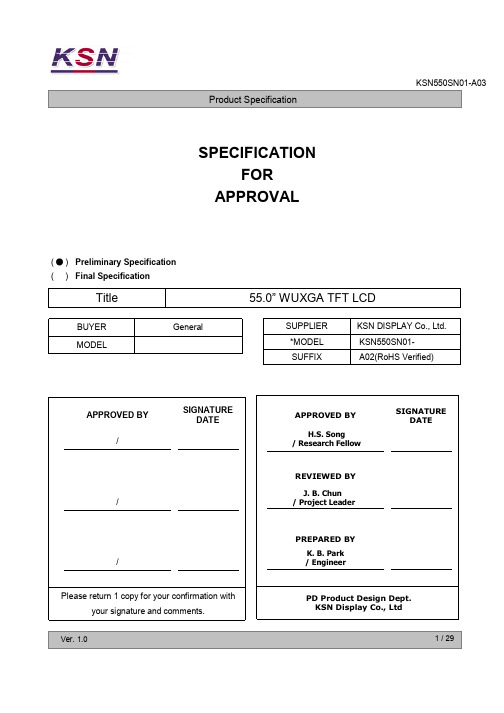

研工(KinSoon)55寸户外高亮液晶显示屏KSN550SN01-A03规格书

Gate Driver Circuit

TFT - LCD Panel

(1920 × RGB × 1080 pixels)

G1080

+12.0V

Power Circuit Block

Power Signals

V : 10Block +24.0V, GND, On/off Ext VBR-B

LED Driver

2000 cd/m2 (Center 1point ,Typ.)

Viewing angle free ( R/L 178 (Min.), U/D 178 (Min.)) Total 241W (Typ.) [Logic=12.9W, Backlight=228.1W(@EXTVBR-B = 100%) 18,100 g (Typ.) Transmissive mode, Normally black Hard coating(3H), Anti-reflection treatment of the front polarizer (Reflectance〈 2%) Landscape and Portrait Enabled

E53NA50中文资料

E53NA50中文资料STE53NA50N -CHANNEL ENHANCEMENT MODEFAST POWER MOS TRANSISTORs TYPICAL R DS(on)=0.075?s HIGH CURRENT POWER MODULE s AVALANCHE RUGGED TECHNOLOGYsVERY LARGE SOA -LARGE PEAK POWER CAPABILITYs EASY TO MOUNTsSAME CURRENT CAPABILITY FOR THE TWO SOURCE TERMINALSs EXTREMELY LOW Rth (Junction to case)sVERY LOW INTERNAL PARASITIC INDUCTANCEsISOLATED PACKAGE UL RECOGNIZEDAPPLICATIONS s SMPS &UPS s MOTOR CONTROL s WELDING EQUIPMENT s OUTPUT STAGE FOR PWM,ULTRASONIC CIRCUITSINTERNAL SCHEMATIC DIAGRAMFebruary 1998ABSOLUTE MAXIMUM RATINGSSymbol ParameterValue Unit V DS Drain-source Voltage (V GS =0)500V V DGR Drain-gate Voltage (R GS =20k ?)500V V GS Gate-source Voltage ±30V I D Drain Current (continuous)at T c =25oC 53A ID Drain Current (continuous)at T c =100o C 33A I DM(?)Drain Current (pulsed)212A P to t Total Dissipation at T c =25oC 460W Derating Factor 3.68W/o CT st g Storage Temperature-55to 150o C T j Max.Operating Junction Temperature 150oCV ISOInsulation Withhstand Voltage (AC-RMS)2500V (?)Pulse width limited by safe operating areaTYPE V DSS R DS(on)I D STE53NA50500V<0.085?53AISOTOP1/7THERMAL DATAR t hj-ca se R thc-h Thermal Resistance Junction-case Max Thermal Resistance Case-heatsink With ConductiveGrease Applied Max0.270.05o C/Wo C/WAVALANCHE CHARACTERISTICSSymbol Parameter Max Value UnitI AR Avalanche Current,Repetitive or Not-Repetitive(pulse width limited by T j max,δ <1%)26AE AS Single Pulse Avalanche Energy(starting T j=25o C,I D=I AR,V DD=50V)1014mJELECTRICAL CHARACTERISTICS(T case=25o C unless otherwise specified)OFFSymbol Parameter Test Conditions Min.Typ.Max.Unit V(BR)DSS Drain-sourceBreakdown VoltageI D=1mA V GS=0500VI DSS Zero Gate VoltageDrain Current(V GS=0)V DS=Max RatingV DS=Max Rating T c=125o C1001000μAμAI GSS Gate-body LeakageCurrent(V DS=0)V GS=±30V±400nA ON(?)Symbol Parameter Test Conditions Min.Typ.Max.Unit V GS(th)Gate ThresholdVoltageV DS=V GS I D=1mA 2.253 3.75VR DS(on)Static Drain-source OnResistanceV GS=10V I D=27A0.0750.085?I D(o n)On State Drain Current V DS>I D(on)x R DS(on)maxV GS=10V53A DYNAMICSymbol Parameter Test Conditions Min.Typ.Max.Unit g fs(?)ForwardTransconductanceV DS>I D(on)X RDS(on)MAX I D=27A25SC iss C oss C rss Input CapacitanceOutput CapacitanceReverse TransferCapacitanceV DS=25V f=1MHz V GS=0131500450162000650nFpFpFSTE53NA50 2/7ELECTRICAL CHARACTERISTICS(continued) SWITCHING ONSymbol Parameter Test Conditions Min.Typ.Max.Unit t d(on) t r Turn-on TimeRise TimeV DD=250V I D=27AR G=4.7 ?V GS=10V(see test circuit,figure1)579280130nsnsQ g Q gs Q gd Total Gate ChargeGate-Source ChargeGate-Drain ChargeV DD=400V I D=53A V GS=10V47054219658nCnCnCSWITCHING OFFSymbol Parameter Test Conditions Min.Typ.Max.Unit t r(Vof f) t ft c Off-voltage Rise TimeFall TimeCross-over TimeV DD=400V I D=53AR G=4.7 ?V GS=10V(see test circuit,figure3)1053614514550205nsnsnsSOURCE DRAIN DIODESymbol Parameter Test Conditions Min.Typ.Max.Unit I SD I SDM(?)Source-drain CurrentSource-drain Current(pulsed)53212AAV SD(?)Forward On Voltage I SD=53A V GS=0 1.6V t rr Q rr I RRM Reverse RecoveryTimeReverse RecoveryChargeReverse RecoveryCurrentI SD=53A di/dt=100A/μsV R=100V T j=150o C(see test circuit,figure3)100031.563nsμCA(?)Pulsed:Pulse duration=300μs,duty cycle1.5% (?)Pulse width limited by safe operating areaSafe Operating Area for Thermal ImpedanceSTE53NA503/7Output Characteristics TransconductanceGate Charge vs Gate-source Voltage Transfer Characteristics Static Drain-source On Resistance Capacitance VariationsSTE53NA50 4/7Normalized Gate Threshold Voltage vs TemperatureSource-drain Diode Forward Characteristics Fig.2:Gate Charge test Circuit Normalized On Resistance vs Temperature Fig.1:Switching Times Test Circuits For Resistive Load Fig.3:Test Circuit For Inductive Load Switching And Diode Recovery TimesSTE53NA505/7DIM.mm inch MIN.TYP.MAX.MIN.TYP.MAX.A 11.812.20.4660.480B 8.99.10.3500.358C 1.95 2.050.0760.080D 0.750.850.0290.033E 12.612.80.4960.503F 25.1525.50.990 1.003G 31.531.71.240 1.248H 40.157J 4.1 4.30.1610.169K 14.915.10.5860.594L 30.130.31.185 1.193M 37.838.21.488 1.503N 40.157O7.88.20.3070.322BEHONJ K L MFACGDISOTOP MECHANICAL DATASTE53NA506/7Information furnished is believed to be accurate and reliable.However,SGS-THOMSON Microelectronics assumes no responsability for the consequences of use of such information nor for any infringement of patents or other rights of third parties which may results from its use.No license is granted by implication or otherwise under any patent or patent rights of SGS-THOMSON Microelectronics.Specifications mentioned in this publication are subject to change without notice.This publication supersedes and replaces all information previously supplied.SGS-THOMSON Microelectronics products are not authorized for use as critical components in life support devices or systems without express written approval of SGS-THOMSON Microelectonics.1998SGS-THOMSON Microelectronics -Printed in Italy -All Rights ReservedSGS-THOMSON Microelectronics GROUP OF COMPANIESAustralia -Brazil -Canada -China -France -Germany -Italy -Japan -Korea -Malaysia -Malta -Morocco -The Netherlands -Singapore -Spain -Sweden -Switzerland -Taiwan -Thailand -United Kingdom -U.S.A...STE53NA50 7/7。

常用三极管参数大全

玉林万顺达电脑芯片级维修资料 2010-07-20整理玉林万顺达电脑芯片级维修资料 2010-07-20整理玉林万顺达电脑芯片级维修资料 2010-07-20整理玉林万顺达电脑芯片级维修资料 2010-07-20整理玉林万顺达电脑芯片级维修资料 2010-07-20整理玉林万顺达电脑芯片级维修资料 2010-07-20整理玉林万顺达电脑芯片级维修资料 2010-07-20整理玉林万顺达电脑芯片级维修资料 2010-07-20整理玉林万顺达电脑芯片级维修资料 2010-07-20整理玉林万顺达电脑芯片级维修资料 2010-07-20整理玉林万顺达电脑芯片级维修资料 2010-07-20整理玉林万顺达电脑芯片级维修资料 2010-07-20整理玉林万顺达电脑芯片级维修资料 2010-07-20整理玉林万顺达电脑芯片级维修资料 2010-07-20整理玉林万顺达电脑芯片级维修资料 2010-07-20整理玉林万顺达电脑芯片级维修资料 2010-07-20整理玉林万顺达电脑芯片级维修资料 2010-07-20整理玉林万顺达电脑芯片级维修资料 2010-07-20整理玉林万顺达电脑芯片级维修资料 2010-07-20整理玉林万顺达电脑芯片级维修资料 2010-07-20整理玉林万顺达电脑芯片级维修资料 2010-07-20整理玉林万顺达电脑芯片级维修资料 2010-07-20整理玉林万顺达电脑芯片级维修资料 2010-07-20整理玉林万顺达电脑芯片级维修资料 2010-07-20整理玉林万顺达电脑芯片级维修资料 2010-07-20整理玉林万顺达电脑芯片级维修资料 2010-07-20整理玉林万顺达电脑芯片级维修资料 2010-07-20整理玉林万顺达电脑芯片级维修资料 2010-07-20整理玉林万顺达电脑芯片级维修资料 2010-07-20整理玉林万顺达电脑芯片级维修资料 2010-07-20整理。

EPM240T100I5N中文资料(Altera)中文数据手册「EasyDatasheet - 矽搜」

256-Pin FineLine

BGA

324-Pin FineLine

BGA

0.5

0.5

1

1

49

121

289

361

7×7

11 × 11 17 × 17 19 × 19

芯片中文手册,看全文,戳

MAX II器件具有内部线性稳压器,它支持3.3 V或2.5 V外接电源电压,调节 供给下降到1.8 V MAX IIG和MAX IIZ器件内部工作电压只接受1.8 V外部电源. MAX IIZ器件引脚兼容100针微型FineLine BGA和256引脚微型FineLine BGA封装 MAX IIG设备.除外部电源电压要求,MAX II和MAX II G设备具有相同引脚 输出和时序规范.

f

有关等效宏单元详细信息,请参阅

宏单元转换方法

白皮书.

MAX II逻辑元素

MAX II和MAX IIG器件有三种速度等级:-3,-4,-5,与

-3是最快.同样,MAX IIZ器件有三种速度等级可供选择:-6,

-7,和-8,以-6是最快.这些速度等级代表总体相对

性能,而不是任何特定时序参数.对于传播延迟定时

由MAX II系列支持.

表1-5 显示外部电源电压

表 1-5. MAX II外接电源电压

设备

多电压内核外部电源电压(V 多电压I / O接口电压电平(V 须知 表 1-5: (1)MAX IIG和MAX IIZ器件只接受1.8 V他们 (2)MAX II器件在1.8 V内部操作

) (2) )

EPM 240 EPM 570 EPM 1270 EPM 2210

3.3 V / 2.5 V或1.8 V ■ 多电压I / O接口,支持3.3 V,2.5 V,1.8 V和1.5 V逻辑电平 ■ 总线型架构,包括可编程摆率,驱动能力,

FPGA可编程逻辑器件芯片EP4CE55F23C8LN中文规格书

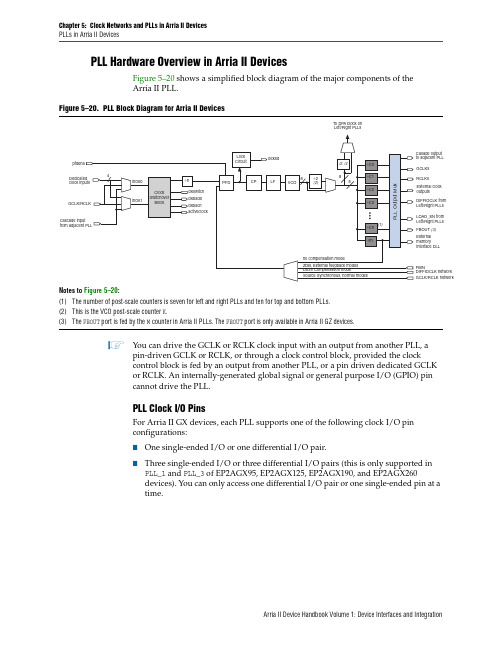

PLLs in Arria II Devices PLL Hardware Overview in Arria II DevicesFigure 5–20 shows a simplified block diagram of the major components of theArria II PLL.1You can drive the GCLK or RCLK clock input with an output from another PLL, apin-driven GCLK or RCLK, or through a clock control block, provided the clockcontrol block is fed by an output from another PLL, or a pin driven dedicated GCLK or RCLK. An internally-generated global signal or general purpose I/O (GPIO) pin cannot drive the PLL.PLL Clock I/O PinsFor Arria II GX devices, each PLL supports one of the following clock I/O pinconfigurations:■One single-ended I/O or one differential I/O pair.■Three single-ended I/O or three differential I/O pairs (this is only supported inPLL _1 and PLL _3 of EP2AGX95, EP2AGX125, EP2AGX190, and EP2AGX260devices). You can only access one differential I/O pair or one single-ended pin at a time.Figure 5–20.PLL Block Diagram for Arria II DevicesNotes to Figure 5–20:(1)The number of post-scale counters is seven for left and right PLLs and ten for top and bottom PLLs.(2)This is the VCO post-scale counter K .(3)The FBOUT port is fed by the M counter in Arria II PLLs. The FBOUT port is only available in Arria II GZ devices.Table5–11.RCLK Outputs From the PLL Clock Outputs for Arria II GZ Device(Part 2 of 2)PLL NumberClock ResourceL2L3B1B2R2R3T1T2 RCLK[32..43]————v v——RCLK[44..63]——————v vClock Control BlockEvery GCLK and RCLK network has its own clock control block. The control blockprovides the following features:■Clock source selection (dynamic selection for GCLKs)■GCLK multiplexing■Clock power down (static or dynamic clock enable or disable)Figure5–12 shows the GCLK select blocks for Arria II devices.Figure5–12.GCLK Control Block for Arria II DevicesNotes to Figure5–12:(1)You can only dynamically control these clock select signals through internal logic when the device is operating in usermode.(2)These clock select signals can only be set through a configuration file (.sof or .pof) and cannot be dynamicallycontrolled during user mode operation.(3)The left side of the Arria II GX device only allows PLL counter outputs as the dynamic clock source selection to theGCLK network.(4)This is only available on the left side of the Arria II GX device.Select the clock source for the GCLK control block either statically with a setting in theQuartus II software or dynamically with an internal logic to drive the multiplexerselect inputs. When selecting the clock source dynamically, you can either select twoPLL outputs (such as C0 or C1), or a combination of clock pins or PLL outputs.Figure5–6.PCLK Networks in (EP2AGX95 and EP2AGX125 Devices)Figure5–7.PCLK Networks in (EP2AGX190 and EP2AGX260 Devices)。

phaser 5550 A3激光打印机 说明书

标准

出纸

自动双面打印 打印 首页输出时间 分辨率(最高) 处理器 内存(标准/最大) 打印接口 打印语言 打印特性

标配 选配

标配

500张 堆叠器: 带500张顶部纸盒的3000张堆叠器 装订器: 带500张顶部纸盒的3000张堆叠器,50张多位打钉和2/4打孔

可选

标准

最快6.5秒

真正1200 x 1200dpi 500MHZ

400-820-5146

富士施乐在华分支机构

北京 上海 广州 深圳 成都 沈阳 天津 长春 青岛 大连 哈尔滨 杭州 武汉 长沙

北京市朝阳区东三环北路霞光里18号佳程广场A座17层 上海市淮海中路300号香港新世界大厦29F/30F/32F 广州市东风中路410-412号健力宝大厦15楼 深圳市福田区益田路4068号卓越时代广场32楼01~08、10室 成都市锦江区滨江东路9号成都香格里拉中心办公楼6层 沈阳市和平区南京北街206号城市广场第二座1406室 天津市南京路75号国际大厦502室 长春市南关区亚泰大街3218号通钢国际大厦A座21层01室 青岛市香港中路59号青岛国际金融中心37层2号 大连市西岗区中山路147号森茂大厦1202E 哈尔滨市南岗区民益街76号网通广场20楼 杭州市潮王路240号银地大厦一层 湖北省武汉市建设大道568号I座21层2105-2107室 长沙市芙蓉区韶山北路159号通程国际大酒店写字楼1208室

郑州 温州 合肥 南京 常州 无锡 苏州 东莞 厦门 福州 西安 重庆 昆明 乌鲁木齐

郑州市中原中路220号裕达国际贸易中心A座22层2212 温州市车站大道高联大厦9B3 合肥市淮河路303号安徽邮电大厦11层D座2号 南京市汉中路89号金鹰国际商城21层B2-C1座 常州市延陵西路23、25、27、29号投资广场17层1706单元 无锡市中山路343号东方广场商务楼11层GH座 苏州工业园区苏华路2号国际大厦1610单元 东莞市南城区胜和路3号胜和广场C座11C 厦门思明区鹭江道8号国际银行大厦12层H室 福州市五四路国贸广场29楼C1 西安市南关正街88号长安国际广场B座1006室 重庆市渝中区邹容路68号大都会商厦2301室 昆明市北京路155号附1号红塔大厦1201室 新疆乌鲁木齐中山路86号中泉广场13楼B室

华硕笔记本

华硕笔记本求助编辑百科名片华硕华硕(ASUS),创立于1989年,一家以技术为核心的公司,至今已经成长为全球性的企业,拥有世界最顶尖的研发队伍,以高品质的产品、创新的技术和令人感动的服务闻名于世。

华硕电脑是全球领先的3C解决方案提供商,致力于为个人和企业用户提供最具创新价值的产品及应用方案。

身为这股改革潮流中的领导者之一,华硕的使命是藉由提供不断创新的IT解决方案,激励华硕的使用者发挥最大潜能。

目录华硕公司简介华硕笔记本简介华硕笔记本售后服务华硕的使命与价值华硕笔记本的特色技术介绍:安全管理专家:更简单易用地安全升级系统信任平台模块TPMRF生物测定指纹扫描器电源管理专家——Power 4 Gear+:网络管理专家——Net4Switch华硕(ASUS)自动升级专家华硕(ASUS)商务笔记本双保险:工业创作的杰作合二为一的电池转轴设计无干扰设计华硕笔记本产品列表(详见参考链接)华硕笔记本5大系列产品介绍客户满意度五强精品机型-华硕X88E667SE-SL全球唯一CPU+GPU超频华硕VX5笔记本基本概况华硕VX5 详细参数华硕与兰博基尼华硕公司简介华硕笔记本简介华硕笔记本售后服务华硕的使命与价值华硕笔记本的特色技术介绍:安全管理专家:更简单易用地安全升级系统信任平台模块TPMRF生物测定指纹扫描器电源管理专家——Power 4 Gear+:网络管理专家——Net4Switch华硕(ASUS)自动升级专家华硕(ASUS)商务笔记本双保险:工业创作的杰作合二为一的电池转轴设计无干扰设计华硕笔记本产品列表(详见参考链接)华硕笔记本5大系列产品介绍客户满意度五强精品机型-华硕X88E667SE-SL全球唯一CPU+GPU超频华硕VX5笔记本基本概况华硕VX5 详细参数华硕与兰博基尼展开编辑本段华硕公司简介华硕(ASUS),创立于1989年,一家以技术为核心的公司,至今已经成长为全球性的企业,拥有世华硕(ASUS)LOGO界最顶尖的研发队伍,以高品质的产品、创新的技术和令人感动的服务闻名于世。

RW1026中文资料

RW1026中文资料RW1026Dot Matrix 48x4 LCD Controller / Driver1FeaturesOperating voltage: 2.4V~5.2V ? External resistor CR oscillator External 256k Hz frequency source inputSelection of 1/2 or 1/3 bias, and selection of 1/2or 1/3 or 1/4 duty LCD applicationsPower down command reduces power consumption ? 48 x 4 LCD driverBuilt-in 48 x 4 bit display RAMIIC serial interface3-line/4-line (type A & type B) serial interface (SPI) ? Internal LCD driving frequency source ? Software configuration feature Data mode and command mode instructions ? R/W address auto incrementVRAB pin for adjusting VLCD operating voltageGeneral DescriptionThe RW1026 is a 192 patterns (48x4), memory mapping, and multi-function LCD driver. The S/W configuration feature of the RW1026 makes it suitable for multiple LCD applications including LCD modules and display subsystems. Only two or three or four lines are required for the serial interface between the host controller and the RW1026. The RW1026 contains a power down command to reduce power consumption.Block DiagramRW1026Dot Matrix 48x4 LCD Controller / Driver2Pad AssignmentChip size: 2463 x 1344 um Pad Size: 89.5 x 88.5 um Pad Pitch: 92.5~231.4 um Chip thickness: 482.6 umz The IC substrate should be connected to VSS in the PCBlayout artwork.RW1026Dot Matrix 48x4 LCD Controller / Driver3CHIP LAYOUT RW1026Dot Matrix 48x4 LCD Controller / Driver4Pad DescriptionPad I/OFunctionCSBI Chip selection input for 3-SPI, 4-SPIwith pull-high resistor.When CSB is login high, the data and command read from or written to the RW1026 are disabled. The serial interface circuit is also reset. But if CSB is at logic low level and isinput to the CSB pad, the data and command transmission between the host controller and the RW1026 are all enabled.XRD(A0)I READ clock input for 4-SPI (type B) with pull-high resistor.Data in the RAM of RW1026 are clocked out on the falling edge of the XRD signal. The clocked out data will appear on the DATA line. The host controller can use the next rising edge to latch the clocked out data.A0 pin for 4-line(type A)serial interface. A0=1: DATA A0=0: CommandXWR(SCLK) I WRITE clock input for 4-SPI (type B) with pull-high resistor.Data on the DATA line are latched into the RW1026 on the rising edge of the XWR signal.Serial clock input (SCLK) pin for 3-line, 4-line (type A), and IIC interface. DATA I/O Serial data input/output with pull-high resistor. VSS - Negative power supply. GroundOSC1 I OSC2 O The OSC1 and OSC2 pads are connected to a external resistor if an RC oscillator is selected. If the system clock comes from an external clock source, the external clocksource should be connected to the OSC1 pad. VLCD I LCD power input. VDD - Positive power supply. COM0-COM3 O LCD common output. SEG0-SEG47O LCD segment output.RSTP I Reset pin with pull-up resistor, Initialized by setting RSTP to "L". Reset operation is performing at RSTP signal level.VRABILCD voltage adjusting pin. Applies voltage between V0 and VSS using a split resistor. IF1,IF0 IInterface selection pins with pull-up resistor IF1,IF0( 0 , 0 ) : IIC Interface ( 0 , 1 ) : 3-line Interface( 1 , 0 ) : 4-line Interface (Type A) ( 1 , 1 ) : 4-line Interface (Type B)。

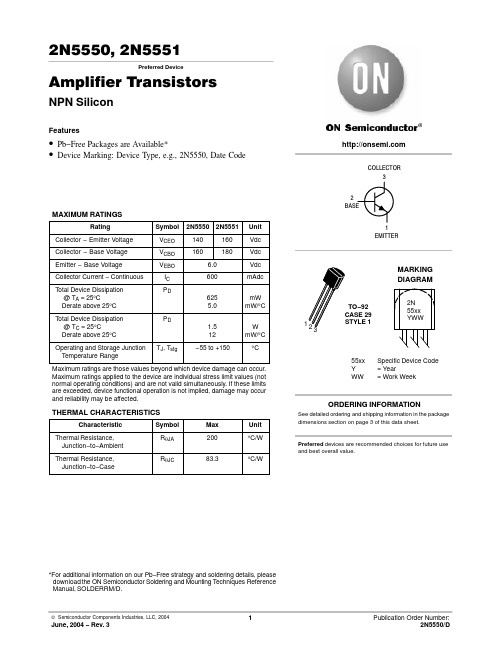

2N5550RLRPG中文资料

2N5550, 2N5551Preferred Device Amplifier Transistors NPN SiliconFeatures•Pb−Free Packages are Available*•Device Marking: Device Type, e.g., 2N5550, Date Code MAXIMUM RATINGSMaximum ratings are those values beyond which device damage can occur. Maximum ratings applied to the device are individual stress limit values (not normal operating conditions) and are not valid simultaneously. If these limits are exceeded, device functional operation is not implied, damage may occur and reliability may be affected.THERMAL CHARACTERISTICS*For additional information on our Pb−Free strategy and soldering details, please download the ON Semiconductor Soldering and Mounting T echniques Reference Manual, SOLDERRM/D.Preferred devices are recommended choices for future use and best overall value.See detailed ordering and shipping information in the package dimensions section on page 3 of this data sheet.ORDERING INFORMATIONELECTRICAL CHARACTERISTICS (T= 25°C unless otherwise noted)ON CHARACTERISTICS (Note 1)SMALL−SIGNAL CHARACTERISTICSORDERING INFORMATION†For information on tape and reel specifications, including part orientation and tape sizes, please refer to our T ape and Reel Packaging Specifica-tions Brochure, BRD8011/D.Figure 1. DC Current GainI C , COLLECTOR CURRENT (mA)500h , D C C U R R E N T G A I NF E 5.0100.10.20.30.50.7 1.02.03.0 5.07.010203050701002003020300100507.0Figure 2. Collector Saturation RegionI B , BASE CURRENT (mA)1.000.30.0050.010.20.5 1.0 2.020500.80.50.40.90.70.60.20.020.050.110V C E , C O L L E C T O R −E M I T T E R V O L T A G E (V O L T S )0.1 5.0I C , COLLECTOR CURRENT (mA)1.0I C , COLLECTOR CURRENT (mA)V , V O L T A G E (V O L T S )1.02.0 5.01020501000.10.20.5Figure 4. “On” Voltages Figure 5. Temperature Coefficients0.80.60.40.20 3.0300.3 1.0 2.0 5.01020501000.10.20.5 3.0300.3C , C A P A C I T A N C E (p F )Figure 6. Switching Time Test Circuit V R , REVERSE VOLTAGE (VOLTS)1001.00.20.5 1.02.05.0102070503020107.05.03.02.00.30.7 3.07.0Figure 7. CapacitancesV outC Values Shown are for I C @ 10 mAFigure 8. Turn−On Time I C , COLLECTOR CURRENT (mA)1000Figure 9. Turn−Off TimeI C , COLLECTOR CURRENT (mA)0.3 1.01020305050000.50.2t , T I M E (n s )t , TI M E (n s )10203050100200300500 2.0100200501002003005003.0 5.03000200010000.3 1.010*******.50.2 2.01002003.0 5.0PACKAGE DIMENSIONSTO−92TO−226AA CASE 29−11ISSUE ALNOTES:1.DIMENSIONING AND TOLERANCING PER ANSI Y14.5M, 1982.2.CONTROLLING DIMENSION: INCH.3.CONTOUR OF PACKAGE BEYOND DIMENSION R IS UNCONTROLLED.4.LEAD DIMENSION IS UNCONTROLLED IN P AND BEYOND DIMENSION K MINIMUM.DIMMIN MAX MIN MAX MILLIMETERSINCHES A 0.1750.205 4.45 5.20B 0.1700.210 4.32 5.33C 0.1250.165 3.18 4.19D 0.0160.0210.4070.533G 0.0450.055 1.15 1.39H 0.0950.105 2.42 2.66J 0.0150.0200.390.50K 0.500−−−12.70−−−L 0.250−−− 6.35−−−N 0.0800.105 2.04 2.66P −−−0.100−−− 2.54R 0.115−−− 2.93−−−V0.135−−−3.43−−−STYLE 1:PIN 1.EMITTER2.BASE3.COLLECTORON Semiconductor and are registered trademarks of Semiconductor Components Industries, LLC (SCILLC). SCILLC reserves the right to make changes without further notice to any products herein. SCILLC makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does SCILLC assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. “Typical” parameters which may be provided in SCILLC data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including “Typicals” must be validated for each customer application by customer’s technical experts. SCILLC does not convey any license under its patent rights nor the rights of others. SCILLC products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body,or other applications intended to support or sustain life, or for any other application in which the failure of the SCILLC product could create a situation where personal injury or death may occur. Should Buyer purchase or use SCILLC products for any such unintended or unauthorized application, Buyer shall indemnify and hold SCILLC and its officers, employees,subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that SCILLC was negligent regarding the design or manufacture of the part.SCILLC is an Equal Opportunity/Affirmative Action Employer. This literature is subject to all applicable copyright laws and is not for resale in any manner.PUBLICATION ORDERING INFORMATION。

zl10355qcf中文资料_数据手册_IC数据表

1Features•Compliant with ETSI 300744DVB-T, Unified Nordig and DTG performance specifications •High performance with fast fully blind acquisition and tracking capability•Low power consumption: less than 0.32W, and eco-friendly standby and sleep modes •Digital filtering of adjacent channels•Single 8MHz SAW filter for 6, 7 & 8 MHz OFDM •Superior single frequency network performance •Fast AGC to track out signal fades •Good Doppler tracking capability•Enhanced frequency capture range to include triple offsets•External 4MHz clock or single low-cost20.48MHz crystal, tolerance up to +/-200 ppm •Automatic mode (2K/8K), guard and spectral inversion detection•Very low driver software overhead due to on-chip state-machine control•Novel RF level detect facility via a separate ADC •Pre and post Viterbi-decoder bit error rates, and uncorrectable block countApplications•Digital terrestrial set-top boxes •Integrated digital televisions •Personal video recorders •PC-TV receivers •Portable applicationsDescriptionThe ZL10355 is a superior fourth generation fully compliant ETSI ETS300 744 COFDM demodulator that exceeds, with margin, the performance requirements of all known DVB-T digital terrestrial television standards, including Unified Nordig and DTG.August 2005Ordering InformationZL10355QCG 64 Pin LQFP Trays, Bake & Drypack ZL10355QCG164 Pin LQFP*Trays, Bake & Drypack ZL10355QCF 64 Pin LQFPTrays, Bake & Drypack ZL10355QCF164 Pin LQFP*Trays, Bake & Drypack*Pb Free Matte Tin-40°C to +85°CZL10355Nordig Unified DVB-T COFDM Terrestrial Demodulator for PC-TV and Hand-held Digital TV (DTV)Data SheetFigure 1 - Block DiagramZL10355Data Sheet A high performance 10 bit on-chip ADC is used to sample the 44 or 36 MHz IF analog signal. Advanced digital filtering of the upper and lower channel enables a single 8 MHz channel SAW filter to be used for 6, 7 and 8 MHz OFDM signal reception. All sampling and other internal clocks are derived from a single 20.48 MHz crystal or a 4 MHz clock input, the tolerance of which may be relaxed as much as 200 ppm.The ZL10355 has a wide frequency capture range able to automatically compensate for the combined offset introduced by the tuner xtal and broadcaster triple frequency offsets.An on-chip state machine controls all acquisition and tracking operations of the ZL10355 as well as controlling the tuner via a 2-wire bus. Any frequency range can be automatically scanned for digital TV channels. This mechanism ensures minimal interaction, maximum flexibility and fast acquisition - very low software overhead.Also included in the design is a 7-bit ADC to detect the RF signal strength and thereby efficiently control the tuner RF AGC.Users have access to all the relevant signal quality information, including input signal power level, signal-to-noise ratio, pre-Viterbi BER, post-Viterbi BER, and the uncorrectable block counts. The error rate monitoring periods are programmable over a wide range.The device is packaged in a 7x7mm 64-pin LQFP and is very low power.ZL10355Data SheetTable of Contents1.0 Pin & Package Details. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .41.1 Pin Outline. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .41.2 Pin Allocation. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .51.3 Pin Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .62.0 Functional Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .82.1 Analog-to-Digital Converter. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .92.2 Automatic Gain Control. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .92.3 IF to Baseband Conversion. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .102.4 Adjacent Channel Filtering . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .102.5 Interpolation and Clock Synchronization. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .102.6 Carrier Frequency Synchronization. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .102.7 Symbol Timing Synchronization . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .102.8 Fast Fourier Transform . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .102.9 Common Phase Error Correction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .112.10 Channel Equalization. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .112.11 Impulse Filtering . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .112.12 Transmission Parameter Signalling (TPS) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .112.13 De-Mapper. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .112.14 Symbol and Bit De-Interleaving. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .112.15 Viterbi Decoder . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .122.16 MPEG Frame Aligner . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .122.17 De-interleaver . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .122.18 Reed-Solomon Decoder . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .122.19 De-scrambler. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .122.20 MPEG Transport Interface. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .123.0 Interfaces . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .133.1 2-Wire Bus. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .133.1.1 Host . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .133.1.2 Tuner . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .133.1.3 Examples of 2-Wire Bus Messages. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .143.1.4 Primary 2-Wire Bus Timing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .143.2 MPEG . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .163.2.1 Data Output Header Format. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .163.2.2 MPEG Data Output Signals. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .173.2.3 MPEG Output Timing. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .173.2.4 MOCLKINV=1 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .183.2.5 MOCLKINV=0 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .184.0 Electrical Characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .194.1 Recommended Operating Conditions. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .194.2 Absolute Maximum Ratings. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .194.3 DC Electrical Characteristics. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .204.4 Crystal Specification and External Clocking . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .204.4.1 Selection of External Components. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .214.4.1.1 Loop Gain Equation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .214.4.1.2 List of Equation Parameters. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .214.4.1.3 Calculating Crystal Power Dissipation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .224.4.1.4 Capacitor Values . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .224.4.1.5 Oscillator/Clock Application Notes . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .235.0 Application Circuit. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .24ZL10355Data Sheet 1.0 Pin & Package Details1.1 Pin OutlineFigure 2 - Pin OutlineZL10355Data Sheet 1.2 Pin AllocationPin Function Pin Function Pin Function Pin Function1Vss17SADD133Vdd49MDO02Vdd18SADD034RFLEV50MDO13Vss19CVdd35CLK2/GPP051MDO24CLK120Vss36DATA2/GPP152MDO35DATA121PLLVdd37CVdd53MDO46IRQ22PLLGND38Vss54Vdd7CVdd23XTI39CVdd55Vss8Vss24XTO40Vss56MDO59RESET25Vss41AGC2/GPP257MDO610SLEEP26PLLTEST42AGC158MDO711STATUS27OSCMODE43GPP359CVdd1228AVdd44SMTEST60Vss13Vdd29AGnd45Vdd61MOCLK14Vss30VIN46Vss62BKERR1531VIN47MOSTRT63MICLK1632AGnd48MOVAL64CVddTable 1 - Pin Names - numericFunction Pin Function Pin Function Pin Function Pin AGC142GPP343PLLTEST26Vdd54 AGC2/GPP241 IRQ6PLLVdd21VIN30 AGnd29MDO049 RESET9VIN31 AGnd32MDO150RFLEV34Vss1 AVdd28MDO251SADD018Vss3BKERR62MDO352SADD117Vss8CLK14MDO453N/C16Vss14 CLK2/GPP035MDO556N/C15Vss20 CVdd7MDO657N/C12Vss25 CVdd19MDO758SLEEP10Vss38 CVdd37MICLK63SMTEST44Vss40 CVdd39MOCLK61STATUS11Vss46Table 2 - Pin Names - alphabetical orderZL10355Data Sheet1.3 Pin DescriptionCVdd 59MOSTRT 47Vdd 2Vss 55CVdd 64MOVAL 48Vdd 13Vss 60DATA15OSCMODE 27Vdd 33 XTI 23DATA2/GPP136PLLGND22Vdd45XTO24Pin Description TablePin NoNamePin DescriptionI/OTypeVmAMPEG pins 47MOSTRT MPEG packet start O CMOS Tristate3.3148MOVALMPEG data valid O 3.3149-53, 56-58MDO(0:4)/MDO(5:7)MPEG data bus O 3.3161MOCLK MPEG clock out O 3.3162BKERR Block error O 3.3163MICLK MPEG clock in ICMOS3.311STATUS Status output O 3.316IRQInterrupt outputOOpen drain 56Control pins 4CLK1Serial clock I CMOS 55DATA1Serial dataI/O Open drain5623XTI Low phase noise oscillatorI CMOS24XTO O 10SLEEP Device power down I 3.312, 15-18SADD(4:0)Serial address setI 3.344SMTEST Production test (only set low)I 3.335CLK2/GPP0Serial clock tuner I/O Open drain 5636DATA2/GPP1Serial data tuner I/O 5642AGC1Primary AGC O 5641AGC2/GPP2Secondary AGC I/O 5643GPP(3)General purpose I/O I/O 569RESET Device resetI CMOS 527OSCMODE Crystal oscillator mode I CMOS 3.326PLLTESTPLL analog test O(tristated)Table 2 - Pin Names - alphabetical order (continued)ZL10355Data SheetAnalog inputs 30VIN positive input I 31VIN negative input I 34RFLEVRF levelISupply pins 21PLLVdd PLL supplyS 1.822PLLGnd S 07, 19, 37, 39, 59, 64CVdd Core logic power S 1.82, 13, 45, 54, Vdd I/O ring power S 3.31, 3, 8, 14, 20, 25, 38, 40, 46, 55, 60Vss Core and I/O ground S 028AVdd ADC analog supply S 1.829, 32AGnd S 033Vdd2nd ADC supply S3.3Pin Description Table (continued)Pin NoNamePin DescriptionI/OTypeV mAZL10355Data Sheet2.0 Functional DescriptionA functional block diagram of the ZL10355 OFDM demodulator is shown in Figure 3. This accepts an IF analog signal and delivers a stream of demodulated soft decision data to the on-chip Viterbi decoder. Clock, timing and frequency synchronization operations are all digital and there are no analog control loops except the AGC. The frequency capture range is large enough for all practical applications. This demodulator has novel algorithms to combat impulse noise as well as co-channel and adjacent channel interference. If the modulation is hierarchical, the OFDM outputs both high and low priority data streams. Only one of these streams is FEC-decoded, but the FEC can be switched from one stream to another with minimal interruption to the transport stream.Figure 3 - OFDM Demodulator DiagramThe FEC module shown in Figure 4 consists of a concatenated convolutional (Viterbi) and Reed-Solomon decoder separated by a depth-12 convolutional de-interleaver. The Viterbi decoder operates on 5-bit soft decisions to provide the best performance over a wide range of channel conditions. The trace-back depth of 128 ensures minimum loss of performance due to inevitable survivor truncation, especially at high code rates. Both the Viterbi and Reed-Solomon decoders are equipped with bit-error monitors. The former provides the bit error rate (BER) at the OFDM output. The latter is the more useful measure as it gives the Viterbi output BER. The error collecting intervals of these are programmable over a very wide range.ZL10355Data SheetFigure 4 - FEC Block DiagramThe FSM controller shown in Figure 3 controls both the demodulator and the FEC. It also drives the 2-wire bus to the tuner. The controller facilitates the automated search of all parameters or any sub-set of parameters of the received signal. It can also be used to scan any defined frequency range searching for OFDM channels. This mechanism provides the fast channel scan and acquisition performance, whilst requiring minimal software overhead in the host driver.The algorithms and architectures used in the ZL10355 have been optimized to minimize power consumption.2.1 Analog-to-Digital ConverterThe ZL10355 has a high performance 10-bit analog-to-digital converter (ADC) which can sample a 6, 7 or 8MHz bandwidth OFDM signal, with its spectrum centred at:•36.17MHz IF•43.75MHz IF•5-10MHz near-zero IFAn on-chip programmable phase locked loop (PLL) is used to generate the ADC sampling clock. The PLL is highly programmable allowing a wide choice of sampling frequencies to suit any IF frequency, and all signal bandwidths.2.2 Automatic Gain ControlAn AGC module compares the absolute value of the digitized signal with a programmable reference. The error signal is filtered and is used to control the gain of the amplifier. A sigma-delta modulated output is provided, which has to be RC low-pass filtered to obtain the voltage to control the amplifier.The programmable AGC reference has been optimized. A large value for the reference leads to excessive ADC clipping and a small value results in excessive quantization noise. Hence the optimum value has been determined assuming the input signal amplitude to be Gaussian distributed. The latter is justified by applying the central limit theorem in statistics to the OFDM signal, which consists of a large number of randomly modulated carriers. This reference or target value may have to be lowered slightly for some applications. Slope control bits have been provided for the AGCs and these have to be set correctly depending on the gain-versus-voltage slope of the gain control amplifiers.ZL10355Data SheetThe bandwidth of the AGC is set to a large value for quick acquisition then reduced to a small value for tracking. The AGC is free running during OFDM channel changes and locks to the new channel while the tuner lock is being established. This is one of the features of ZL10355 used to minimize acquisition time. A robust AGC lock mechanism is provided and the other parts of the ZL10355 begin to acquire only after the AGC has locked.2.3 IF to Baseband ConversionSampling a 36.17MHz IF signal at 45MHz results in a spectrally inverted OFDM signal centred at approximately8.9MHz. The first step of the demodulation process is to convert this signal to a complex (in-phase and quadrature) signal in baseband. A correction for spectral inversion is implemented during this conversion process. Note also that the ZL10355 has control mechanisms to search automatically for an unknown spectral inversion status.2.4 Adjacent Channel FilteringAdjacent channels, in particular the Nicam digital sound signal associated with analog channels, are filtered prior to the FFT.2.5 Interpolation and Clock SynchronizationZL10355 uses digital timing recovery and this eliminates the need for an external VCXO. The ADC samples the signal at a fixed rate, for example, 45.056MHz. Conversion of the 45.056MHz signal to the OFDM sample rate is achieved using the time-varying interpolator. The OFDM sample rate is 64/7MHz for 8MHz and this is scaled by factors 6/8 and 7/8 for 6 and 7MHz channel bandwidths. The nominal ratio of the ADC to OFDM sample rate is programmed in a ZL10355 register (defaults are for 45MHz sampling and 8MHz OFDM). The clock recovery phase locked loop in the ZL10355 compensates for inaccuracies in this ratio due to uncertainties of the frequency of the sampling clock.2.6 Carrier Frequency SynchronizationThere can be frequency offsets in the signal at the input to OFDM, partly due to tuner step size and partly due to broadcast frequency shifts, typically 1/6MHz. These are tracked out digitally, up to 1MHz in 2K and 8K modes, without the need for an analog frequency control (AFC) loop.The default frequency capture range has been set to ±286kHz in the 2K and 8K mode. However, these values can be increased, if necessary, by programming an on-chip register (see 7.4.1). It is recommended that a larger capture range be used for channel scan in order to find channels with broadcast frequency shifts, without having to adjust the tuner. After the OFDM module has locked (the AFC will have been previously disabled), the frequency offset can be read from an on-chip register.2.7 Symbol Timing SynchronizationThis module computes the optimum sample position to trigger the FFT in order to eliminate or minimize inter-symbol interference in the presence of multi-path distortion. Furthermore, this trigger point is continuously updated to dynamically adapt to time-variations in the transmission channel.2.8 Fast Fourier TransformThe FFT module uses the trigger information from the timing synchronization module to set the start point for an FFT. It then uses either a 2K or 8K FFT to transform the data from the time domain to the frequency domain. An extremely hardware-efficient and highly accurate algorithm has been used for this purpose.ZL10355Data Sheet 2.9 Common Phase Error CorrectionThis module subtracts the common phase offset from all the carriers of the OFDM signal to minimize the effect of the tuner phase noise on system performance.2.10 Channel EqualizationThis consists of two parts. The first part involves estimating the channel frequency response from pilot information. Efficient algorithms have been used to track time-varying channels with a minimum of hardware.The second part involves applying a correction to the data carriers based on the estimated frequency response of the channel. This module also generates dynamic channel state information (CSI) for every carrier in every symbol.2.11 Impulse FilteringZL10355 contains several mechanisms to reduce the impact of impulse noise on system performance.2.12 Transmission Parameter Signalling (TPS)An OFDM frame consists of 68 symbols and a superframe is made up of four such frames. There is a set of TPS carriers in every symbol and all these carry one bit of TPS. These bits, when combined, include information about the transmission mode, guard ratio, constellation, hierarchy and code rate, as defined in ETS 300 744. In addition, the first eight bits of the cell identifier are contained in even frames and the second eight bits of the cell identifier are in odd frames. The TPS module extracts all the TPS data, and presents these to the host processor in a structured manner.2.13 De-MapperThis module generates soft decisions for demodulated bits using the channel-equalized in-phase and quadrature components of the data carriers as well as per-carrier channel state information (CSI). The de-mapping algorithm depends on the constellation (QPSK, 16QAM or 64QAM) and the hierarchy (α=0, 1, 2 or 4). Soft decisions for both low- and high-priority data streams are generated.2.14 Symbol and Bit De-InterleavingThe OFDM transmitter interleaves the bits within each carrier and also the carriers within each symbol. The de-interleaver modules consist largely of memory to invert these interleaving functions and present the soft decisions to the FEC in the original order.ZL10355Data Sheet2.15 Viterbi DecoderThe Viterbi decoder accepts the soft decision data from the OFDM demodulator and outputs a decoded bit-stream. The decoder does the de-puncturing of the input data for all code rates other than 1/2. It then evaluates the branch metrics and passes these to a 64-state path-metric updating unit, which in turn outputs a 64-bit word to the survivor memory. The Viterbi decoded bits are obtained by tracing back the survivor paths in this memory. A trace-back depth of 128 is used to minimize any loss in performance, especially at high code rates.The decoder re-encodes the decoded bits and compares these with received data (delayed) to compute bit errors at its input, on the assumption that the Viterbi output BER is significantly lower than its input BER.2.16 MPEG Frame AlignerThe Viterbi decoded bit stream is aligned into 204-byte frames. A robust synchronization algorithm is used to ensure correct lock and to prevent loss of lock due to noise impulses.2.17 De-interleaverErrors at the Viterbi output occur in bursts and the function of the de-interleaver is to spread these errors over a number of 204-byte frames to give the Reed-Solomon decoder a better chance of correcting these. The de-interleaver is a memory unit which implements the inverse of the convolutional interleaving function introduced by the transmitter.2.18 Reed-Solomon DecoderEvery 188-byte transport packet is encoded by the transmitter into a 204-byte frame, using a truncated version of a systematic (255,239) Reed-Solomon code. The corresponding (204,188) Reed-Solomon decoder is capable of correcting up to eight byte errors in a 204-byte frame. It may also detect frames with more than eight byte errors. In addition to efficiently performing this decoding function, the Reed-Solomon decoder in ZL10355 keeps a count of the number of bit errors corrected over a programmable period and the number of uncorrectable blocks. This information can be used to compute the post-Viterbi BER.2.19 De-scramblerThe de-scrambler de-randomizes the Reed-Solomon decoded data by generating the exclusive-OR of this with a pseudo-random bit sequence (PRBS). This outputs 188-byte MPEG transport packets. The TEI bit of the packet header may be set if required to indicate uncorrectable packets.2.20 MPEG Transport InterfaceMPEG data can be output in parallel or serial mode. The output clock frequency is automatically chosen to present the MPEG data as uniformly spaced as possible to the transport processor. This frequency depends on the guard ratio, constellation, hierarchy and code rate. There is also an option for the data to be extracted from the ZL10355 with a clock provided by the user.ZL10355Data Sheet 3.0 Interfaces3.1 2-Wire Bus3.1.1 HostThe primary 2-wire bus serial interface uses pins:•DATA1 (pin 5) serial data, the most significant bit is sent first.•CLK1 (pin 4) serial clock.The 2-wire bus address is determined by applying VDD or VSS to the SADD[4:0] pins.In TNIM evaluation applications, the 2-wire bus address is 0001 111 R/W with the pins connected as follows: ADDR[7]ADDR[6]ADDR[5]ADDR[4]ADDR[3]ADDR[2]ADDR[1]Not programmable SADD[1]SADD[0]VSS VSS VSS VDD VDD VDD VDDWhen the ZL10355 is powered up, the RESET pin9 should be held low for at least 50ms after VDD has reached normal operation levels. As the RESET pin goes high, the logic levels on SADD[4:0] are latched as the 2-wire bus address. ADDR[0] is the R/W bit.The circuit works as a slave transmitter with the lsb set high or as a slave receiver with the lsb set low. In receive mode, the first data byte is written to the RADD virtual register, which forms the register sub-address. The RADD register takes an 8-bit value that determines which of 256 possible register addresses is written to by the following byte. Not all addresses are valid and many are reserved registers that must not be changed from their default values. Multiple byte reads or writes will auto-increment the value in RADD, but care should be taken not to access the reserved registers accidentally.Following a valid chip address, the 2-wire bus STOP command resets the RADD register to 00. If the chip address is not recognized, the ZL10355 will ignore all activity until a valid chip address is received. The 2-wire bus START command does NOT reset the RADD register to 00. This allows a combined 2-wire bus message, to point to a particular read register with a write command, followed immediately with a read data command. If required, this could next be followed with a write command to continue from the latest address. RADD would not be sent in this case. Finally, a STOP command should be sent to free the bus.When the 2-wire bus is addressed (after a recognized STOP command) with the read bit set, the first byte read out is the contents of register 00.3.1.2 TunerThe ZL10355 has a General Purpose Port that can be configured to provide a secondary 2-wire bus. See register GPP_CTL address 0x8C.Master control mode is selected by setting register SCAN_CTL (0x62) [b3]=1.The allocation of the pins is: GPP0 pin 35=CLK2, GPP1 pin 36=DATA2.。

PCA9555DWG4中文资料

PCA9555

......................................................................................................................................................... SCPS131E – AUGUST 2005 – REVISED MAY 2008

The PCA9555 consists of two 8-bit Configuration (input or output selection), Input Port, Output Port, and Polarity Inversion (active high or active low operation) registers. At power on, the I/Os are configured as inputs. The system master can enable the I/Os as either inputs or outputs by writing to the I/O configuration bits. The data for each input or output is kept in the corresponding Input or Output register. The polarity of the Input Port register can be inverted with the Polarity Inversion register. All registers can be read by the system master.

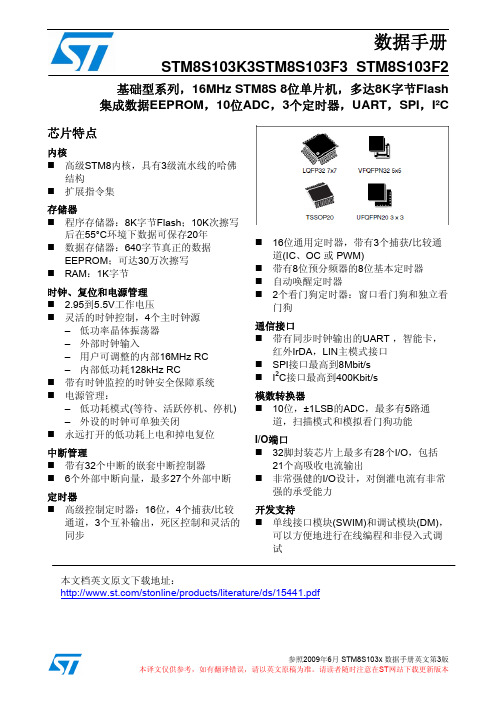

STM8S103中文手册

4.10 TIM1 — 16位高级控制定时器............................................................................................11

4.11

TIM2 — 16位通用定时器...................................................................................................11

4.2

单线接口模块(SWIM)和调试模块(DM) ................................................................................7

4.3

中断控制器 ..........................................................................................................................8

门狗

通信接口 带有同步时钟输出的UART ,智能卡,

红外IrDA,LIN主模式接口 SPI接口最高到8Mbit/s I2C接口最高到400Kbit/s

模数转换器 10位,±1LSB的ADC,最多有5路通

道,扫描模式和模拟看门狗功能

I/O端口 32脚封装芯片上最多有28个I/O,包括

4.6

电源管理............................................................................................................................10

KONICA magicolor 5550 5570 说明书

magicolor 5550/5570®用户指南A011-9562-01N1800825-018B商标KONICA MINOLTA、KONICA MINOL TA 徽标和 PageScope 是 KONICA MINOLTA HOLDINGS, INC.的商标或注册商标。

magicolor 是 KONICA MINOLTA PRINTING SOLUTIONS U.S.A., INC. 的商标或注册商标。

所有其它商标和注册商标归其各自拥有者所有。

版权通告版权所有 © 2006 KONICA MINOLTA BUSINESS TECHNOLOGIES, INC., Marunouchi Center Building, 1-6-1 Marunouchi, Chiyoda-ku, T okyo, 100-0005, Japan。

保留所有权利。

未经 KONICA MINOLTA BUSINESS TECHNOLOGIES, INC. 书面许可,不得复制本文档的全部或部分,也不得将其转换为任何其它媒体或语言。

通告KONICA MINOLTA BUSINESS TECHNOLOGIES, INC. 保留随时修改本指南及指南中所述设备的权利,恕不另行通知。

KONICA MINOLTA BUSINESS TECHNOLOGIES, INC. 已竭力确保本指南中无错误或疏漏之处。

但是,KONICA MINOLTA BUSINESS TECHNOLOGIES, INC. 并不作任何性质的保证,包括但不仅限于对任何与本指南相关的特殊目的的适销性和适用性的暗示性保证。

KONICA MINOLTA BUSINESS TECHNOLOGIES, INC. 不对本指南中所包含的错误或因拥有本指南或使用本指南进行设备操作、或按此操作时因设备性能所造成偶发、特别或随发的损害承担责任或义务。

软件许可协议本软件包由 Konica Minolta Business Technologies, Inc. (KMBT) 提供的如下资料组成:打印软件;采用特殊格式和加密形式并经数字编码的机读式轮廓数据(以下简称“字体程序”);在计算机系统上运行并与打印软件配合使用的其它应用程序(以下简称“主机软件”)以及相关的说明文件(以下简称“文档”)。

Vishay Sfernice TSM4 5mm Square Surface Mount Mini

TSM4YL103KB25TSM4 Vishay Sfernice5 mm Square Surface Mount Miniature Trimmers Multi-TurnCermet SealedDESIGN SUPPORT TOOLSThe TSM4 trimming potentiometer has been designed for surface mount applications and offers volumetric efficiency 5 mm x 5 mm x 3.7 mm with high performance and stability. The TSM4 design is suitable for both manual or automatic operation, and can withstand vapor phase and reflow soldering techniques.FEATURES•0.25 W at 70 °C•Professional and industrial grade•Wide ohmic range (10 Ω to 1 MΩ)•Low contact resistance variation (2 % or 3 Ω)•Small size for optimum packaging density•Tests according to CECC 41000 or IEC 60393-1•Material categorization: for definitions of compliance please see/doc?99912TSM4 Vishay SferniceMECHANICAL SPECIFICATIONSMechanical travel13 turns ± 2Operating torque (max. Ncm)1End stop torque (Ncm)Clutch action (2 turns max.)Unit weight (max. g)0.15Wiper (actual travel)Positioned at approx. 50 %ENVIRONMENTAL SPECIFICATIONSTemperature range-55 °C to +125 °CClimatic category55/125/56Sealing Sealed container IP67MSL level1SOLDERING RECOMMENDATIONSRecommended reflow profile 2, see Application Note /doc?52029TSM4Vishay SferniceNote•Nothing stated herein shall be construed as a guarantee of quality or durabilityPERFORMANCESTESTSCONDITIONSTYPICAL VALUES AND DRIFTS∆R T /R T ∆R 1-2/R 1-2OTHERElectrical endurance1000 h at rated power 90'/30' - ambient temp. 70 °C ± 2 %± 3 %Contact res. variation: ∆ < 1 % Rn Climatic sequence Phase A dry heat 125 °C Phase B damp heat Phase C cold -55 °CPhase D damp heat 5 cycles ± 2 %± 3 %Dielectric strength: 600 V RMS Insulation resistance: > 104 M ΩDamp heat, steady state Temperature 40 °C - RH 93 %56 days± 2 %± 3 %Dielectric strength: 600 V RMS Insulation resistance: > 104 M ΩChange of temperature -55 °C to +125 °C5 cycles ± 1 %∆V 1-2/V 1-3 ≤ ± 2 %Mechanical endurance 100 cycles - rated power ± (3 % + 3 Ω)Shock 50 g - 11 ms3 successive shocks in 3 directions± 1 %∆V 1-2/V 1-3 ≤ ± 1 %Vibration10 Hz to 55 Hz 0.75 mm or 10 g - 6 h± 1 %∆V 1-2/V 1-3 ≤ ± 1 %STANDARD RESISTANCE ELEMENT DATASTANDARD RESISTANCE VALUESLINEAR LAWTYPICAL TCR -55 °C +125 °C MAX. POWER AT 70 °CMAX. WORKINGVOLTAGEMAX. CURRENT THROUGH ELEMENTΩW V mA ppm/°C100.25 1.58158± 100200.25 2.23112500.25 3.53771000.25 5.00502000.257.07355000.2511.2221K 0.2515.815.82K 0.2522.311.25K 0.2535.37.110K 0.2550.0 5.020K 0.2570.7 3.550K 0.25112 2.2100K 0.25158 1.6200K 0.25200 1.0500K 0.082000.41M0.042000.2MARKINGVishay trademark, ohmic value, manufacturing dateThe ohmic value is indicated by a 3 figure code, the first two are significant figures, the third one is the multiplier. Example: 100 = 10 Ω101 = 100 Ω 102 = 1000 Ω 503 = 50 000 ΩTSM4Vishay SferniceORDERING INFORMATION (part number)MODEL STYLE OHMIC VALUE TOLERANCE PACKAGING SPECIAL NUMBER TSM4YJ YL ZJ ZLFrom 10 Ω to 1 M Ω504 = 500 k ΩK = 10 %R10 =reel 500 pieces for ZJ and ZLR05 =reel 250 pieces for YJ and YL On request B25 =box of 50 pieces(If applicable)Given by Vishay for custom designDESCRIPTION (for information only)TSM4YL 500K 10 %TR e3MODELSTYLEVALUETOLERANCESPECIALPACKAGINGLEAD (Pb)-FREERELATED DOCUMENTSAPPLICATION NOTES Potentiometers and Trimmers/doc?51001Guidelines for Vishay Sfernice Resistive and Inductive Components/doc?5202955K4RLM4YSTLegal Disclaimer Notice VishayDisclaimerALL PRODUCT, PRODUCT SPECIFICATIONS AND DATA ARE SUBJECT TO CHANGE WITHOUT NOTICE TO IMPROV E RELIABILITY, FUNCTION OR DESIGN OR OTHERWISE.V ishay Intertechnology, Inc., its affiliates, agents, and employees, and all persons acting on its or their behalf (collectively,“Vishay”), disclaim any and all liability for any errors, inaccuracies or incompleteness contained in any datasheet or in any other disclosure relating to any product.Vishay makes no warranty, representation or guarantee regarding the suitability of the products for any particular purpose or the continuing production of any product. To the maximum extent permitted by applicable law, Vishay disclaims (i) any and all liability arising out of the application or use of any product, (ii) any and all liability, including without limitation special, consequential or incidental damages, and (iii) any and all implied warranties, including warranties of fitness for particular purpose, non-infringement and merchantability.Statements regarding the suitability of products for certain types of applications are based on Vishay's knowledge of typical requirements that are often placed on Vishay products in generic applications. Such statements are not binding statements about the suitability of products for a particular application. It is the customer's responsibility to validate that a particular product with the properties described in the product specification is suitable for use in a particular application. Parameters provided in datasheets and / or specifications may vary in different applications and performance may vary over time. All operating parameters, including typical parameters, must be validated for each customer application by the customer's technical experts. Product specifications do not expand or otherwise modify Vishay's terms and conditions of purchase, including but not limited to the warranty expressed therein.Hyperlinks included in this datasheet may direct users to third-party websites. These links are provided as a convenience and for informational purposes only. Inclusion of these hyperlinks does not constitute an endorsement or an approval by Vishay of any of the products, services or opinions of the corporation, organization or individual associated with the third-party website. Vishay disclaims any and all liability and bears no responsibility for the accuracy, legality or content of the third-party website or for that of subsequent links.Except as expressly indicated in writing, Vishay products are not designed for use in medical, life-saving, or life-sustaining applications or for any other application in which the failure of the Vishay product could result in personal injury or death. Customers using or selling Vishay products not expressly indicated for use in such applications do so at their own risk. Please contact authorized Vishay personnel to obtain written terms and conditions regarding products designed for such applications. No license, express or implied, by estoppel or otherwise, to any intellectual property rights is granted by this document or by any conduct of Vishay. Product names and markings noted herein may be trademarks of their respective owners.© 2022 VISHAY INTERTECHNOLOGY, INC. ALL RIGHTS RESERVEDTSM4YL103KB25。

iC5变频器中文说明书

iC5变频器中文说明书重要说明感谢您选购LG变频调速器~操作防范(1) 维护与安装, 按照产品的重量处理。

, 堆放变频器包装箱数量不要超过规定数目。

, 按照本手册的指令规范安装。

, 交货期间不要打开外壳。

, 不要放置重物在变频器上。

, 检查变频器的装箱方向是否正确。

, 不要使变频器受到摔跌或挤压。

, 对于200V级变频器,使用3类接地方式(接地电阻<100Ω)。

, 检查或安装时,在触摸印刷电路板前注意保护措施(静电放电)。

, 在下列环境条件下使用变频器:环境温度 - 10 ~ 50 ? (无冰冻)湿度 90% RH 或更低 (无凝露)环境储存温度 - 20 ~ 65 ?安装场所无腐蚀性气体,可燃性气体,油雾或灰尘 2海拔, 振动最大海拔高度 1,000m 以下,最大 5.9m/sec (0.6G) 或更低i SV-iC5重要说明(2) 接线, 不要安装电力电容器,浪涌抑制器,或RFI滤波器在变频器的输出侧。

, 连接到电机的输出电缆(U, V, W) 的连接方式将会影响到电机的旋转方向。

, 不正确的端子接线可能引起设备的损坏。

, 端子的正负极接反可能会损坏变频器。

, 只有受过专业培训的人才可以对变频器进行接线和检查。

, 先安装变频器再进行接线,否则,你可能受到电击或人身伤害。

(3) 试运行, 在运行前检查所有参数,根据负载类型修改参数值。

, 始终在本说明书标定的电压范围内使用,否则,可能导致变频器损坏。

(4) 操作防范, 当选择自动重启动功能时,由于电机会在故障停止后突然再启动,所以应远离设备。

, 操作面板上的“STOP”键仅在相应功能设置已经被设定时才有效,特殊情况应准备紧急停止开关。

, 如果故障复位是使用外部端子进行设定,将会发生突然启动。

请预先检查外部端子信号是否处于关断位,否则可能发生意外事故。

, 不要修改或变动变频器内部任何东西。

, 变频器的电子热保护功能可能无法保护电机。

, 在变频器的输入侧不要使用电磁式交流接触器作为变频器频繁启停的开关。