S-24C16A中文资料

FM24C16A-AT24C16中文资料

第 1页

Figure 1. Block Diagram

引脚定义

名称 I/O

SDA I/O

SCL 输入

WP 输入

VDD VSS NC

电源 电源 空脚

描述

串行地址\数据管脚:这个双向引脚用来传送地址和输入输出数据。这是一个开 漏输出,以便与其它器件通过”线或”并接在双线总线上。输入缓冲区集成施密 特触发器用以提高抗干扰性能,输出驱动器具有下降沿斜率控制。此端口必须 外加上拉电阻。 串行时钟:两线制总线的串行时钟输入。数据在时钟的下降沿移出器件,在时 钟的上升沿移入器件,时钟端口同样具有施密特触发器用以提高抗干扰性能。

对器件进行轮循以等待一个就绪状态,因为器

件是以总线速度进行写操作, 一个新的总线

转输将数据移入器件的同时,一个写操作已经

完成,更为详尽的描述将在下面的接口界面章

ห้องสมุดไป่ตู้

节进行描述。

Figure 2. Typical System Configuration

需要指出的是,FM24C16A没有类似内部电源管

图5描述的是单字节和多字节的操作。

第 5页

Figure 5. Single Byte Write

Figure 6. Multiple Byte Write

读操作

四种正确操作方法如下:

有两种基本类型的读操作:当前地址读操作 1、主机在第9个时钟不发应答信号,在第十个时

和随机地址读操作。对当前地址进行读操作

开始

当主机把SDA从高电平拉为低电平,同时SCL 信号为高电平时被认为是开始信号,所有的读 写操作均由开始信号开始。任何时候发布一个 开始信号,一个进行中的操作都会被中止。使 用开始信号中止一个操作的同时,FM24C04A 也会处于开始一个新操作的就绪状态。在操作 过程中,如果电压降低到规定电压的最低值以 下时,FM24C16A执行另外一个的操作之前,会 认为出现了一个开始信号。

FT24C16`FT24C08 资料完整版

F MDCo nf i de n t i al© 2012 Fremont Micro Devices Inc. DS24C04_08_16-A0--page1Two-Wire Serial EEPROM4K, 8K and 16K (8-bit wide)FEATURES❑Low voltage and low power operations:FT24C04A/08A/16A: V CC = 1.8V to 5.5V❑ Maximum Standby current < 1µA (typically 0.02µA and 0.06µA @ 1.8V and 5.5V respectively). ❑ 16 bytes page write mode.❑ Partial page write operation allowed.❑ Internally organized: 512 x 8 (4K), 1024 x 8 (8K), 2048 x 8 (16K). ❑ Standard 2-wire bi-directional serial interface. ❑ Schmitt trigger, filtered inputs for noise protection. ❑ Self-timed Write Cycle (5ms maximum).❑ 1 MHz (5V), 400 kHz (1.8V, 2.5V, 2.7V) Compatibility. ❑ Automatic erase before write operation.❑ Write protect pin for hardware data protection.❑ High reliability: typically 1, 000,000 cycles endurance. ❑ 100 years data retention.❑ Industrial temperature range (-40o C to 85o C).❑Standard 8-lead DIP/SOP/MSOP/TSSOP/DFN and 5-lead SOT-23/TSOT-23 Pb-free packages.DESCRIPTIONThe FT24C04A/08A/16A series are 4,096/8,192/16,384 bits of serial Electrical Erasable andProgrammable Read Only Memory, commonly known as EEPROM. They are organized as 512/1,024/2,048 words of 8 bits (1 byte) each. The devices are fabricated with proprietary advanced CMOS process for low power and low voltage applications. These devices are available in standard 8-lead DIP, 8-lead SOP, 8-lead TSSOP, 8-lead DFN, 8-lead MSOP, and 5-lead SOT-23/TSOT-23 packages. A standard 2-wire serial interface is used to address all read and write functions. Our extended V CC range (1.8V to 5.5V) devices enables wide spectrum of applications.PIN CONFIGURATIONPin Name Pin FunctionA2, A1, A0 Device Address Inputs SDA Serial Data Input / Open Drain Output SCL Serial Clock Input WP Write Protect NC No-ConnectF MDCo nf i de nt i a l© 2012 Fremont Micro Devices Inc. DS24C04_08_16-A0--page2All these packaging types come in conventional or Pb-free certified.VCC W P SCL SDAA2A1A0G 8L DIP 8L SOP8L TSSOP W P VCCG ND FT24C04A/08A/16A 5L SOT-23SCL 8L DFN8L M SOP 5L TSO T-23ABSOLUTE MAXIMUM RATINGSIndustrial operating temperature: -40℃ to 85℃ Storage temperature:-50℃ to 125℃Input voltage on any pin relative to ground: -0.3V to V CC + 0.3V Maximum voltage: 8VESD protection on all pins: >2000V* Stresses exceed those listed under “Absolute Maximum Rating” may cause permanent damage to thedevice. Functional operation of the device at conditions beyond those listed in the specification is not guaranteed. Prolonged exposure to extreme conditions may affect device reliability or functionality .F MDCo nf i de nt i a l© 2012 Fremont Micro Devices Inc. DS24C04_08_16-A0--page3PIN DESCRIPTIONS(A) SERIAL CLOCK (SCL)The rising edge of this SCL input is to latch data into the EEPROM device while the falling edge of this clock is to clock data out of the EEPROM device.(B) DEVICE / CHIP SELECT ADDRESSES (A2, A1, A0)These are the chip select input signals for the serial EEPROM devices. Typically, these signals are hardwired to either V IH or V IL . If left unconnected, they are internally recognized as V IL . FT24C04A has A0 pin as no-connect. FT24C08A has both A0 and A1 pins as no-connect. For FT24C16A, all device address pins (A0-A2) are no-connect.(C) SERIAL DATA LINE (SDA)SDA data line is a bi-directional signal for the serial devices. It is an open drain output signal and can bewired-OR with other open-drain output devices.(D) WRITE PROTECT (WP)The FT24C04A/08A/16A devices have a WP pin to protect the whole EEPROM array from programming. Programming operations are allowed if WP pin is left un-connected or input to V IL . Conversely all programming functions are disabled if WP pin is connected to V IH or V CC . Read operations is not affected by the WP pin’s input level.Table AF MDCo nf i de nt i al© 2012 Fremont Micro Devices Inc. DS24C04_08_16-A0--page4Device Chip Select/DeviceAddress Pins UsedNo-Connect Pins Max number of similardevices on the samebusFT24C04A A2, A1 A0 4FT24C08A A2, A1, A0 2 FT24C16A(None)A2, A1, A01MEMORY ORGANIZATIONThe FT24C04A/08A/16A devices have 32/64/128 pages respectively. Since each page has 16 bytes, random word addressing to FT24C04A/08A/16A will require 9/10/11 bits data word addresses respectively.DEVICE OPERATION(A) SERIAL CLOCK AND DATA TRANSITIONSThe SDA pin is typically pulled to high by an external resistor. Data is allowed to change only whenSerial clock SCL is at V IL . Any SDA signal transition may interpret as either a START or STOP condition as described below. (B) START CONDITIONWith SCL V IH , a SDA transition from high to low is interpreted as a START condition. All valid commands must begin with a START condition.F MDCo nf i de nt i al© 2012 Fremont Micro Devices Inc. DS24C04_08_16-A0--page5(C) STOP CONDITIONWith SCL V IH , a SDA transition from low to high is interpreted as a STOP condition. All valid read or write commands end with a STOP condition. The device goes into the STANDBY mode if it is after a read command. A STOP condition after page or byte write command will trigger the chip into the STANDBY mode after the self-timed internal programming finish. (D) ACKNOWLEDGEThe 2-wire protocol transmits address and data to and from the EEPROM in 8 bit words. The EEPROM acknowledges the data or address by outputting a "0" after receiving each word. The ACKNOWLEDGE signal occurs on the 9th serial clock after each word. (E) STANDBY MODEThe EEPROM goes into low power STANDBY mode after a fresh power up, after receiving a STOP bit in read mode, or after completing a self-time internal programming operation.Figure 1: Timing diagram for START and STOP conditionsFigure 2: Timing diagram for output ACKNOWLEDGESCLSDASTART ConditionSTOP ConditionData Data Valid TransitionSCLData inData out START ConditionACKF MDCo nf i de nt i a l© 2012 Fremont Micro Devices Inc. DS24C04_08_16-A0--page6DEVICE ADDRESSINGThe 2-wire serial bus protocol mandates an 8 bits device address word after a START bit condition to invoke valid read or write command. The first four most significant bits of the device address must be 1010, which is common to all serial EEPROM devices. The next three bits are device address bits. These three device address bits (5th , 6th and 7th ) are to match with the external chip select/address pin states. If a match is made, the EEPROM device outputs an ACKNOWLEDGE signal after the 8th read/write bit, otherwise the chip will go into STANDBY mode. However, matching may not be needed for some or all device address bits (5th , 6th and 7th ) as noted below. The last or 8th bit is a read/write command bit. If the 8th bit is at V IH then the chip goes into read mode. If a “0” is detected, the device enters programming mode.FT24C04A uses A2 (5th ) and A1 (6th ) device address bits. Only four FT24C04A devices can be wired-OR on the same 2-wire bus. Their corresponding chip select address pins A2 and A1 must be hard wired and coded from 00 (b) to 11 (b). Chip select address pin A0 is not used.FT24C08A uses only A2 (5th ) device address bit. Only two FT24C08A devices can be wired-OR on the same 2-wire bus. Their corresponding chip select address pin A2 must be hard-wired and coded from 0 (b) to 1 (b). Chip select address pins A1 and A0 are not used.FT24C16A does not use any device address bit. Only one FT24C16A device can be used on the on 2-wire bus. Chip Select address pins A2, A1, and A0 are not used.WRITE OPERATIONS(A) BYTE WRITEA byte write operation starts when a micro-controller sends a START bit condition, follows by a proper EEPROM device address and then a write command. If the device address bits match the chip select address, the EEPROM device will acknowledge at the 9th clock cycle. The micro-controller will then send the rest of the lower 8 bits word address. At the 18th cycle, the EEPROM will acknowledge the 8-bit address word. The micro-controller will then transmit the 8 bit data. Following an ACKNOWLDEGE signal from the EEPROM at the 27th clock cycle, the micro-controller will issue a STOP bit. After receiving the STOP bit, the EEPROM will go into a self-timed programming mode during which all external inputs will be disabled. After a programming time of T WC , the byte programming will finish and the EEPROM device will return to the STANDBY mode.(B) PAGE WRITEA page write is similar to a byte write with the exception that one to sixteen bytes can be programmed along the same page or memory row. All FT24C04A/08A/16A are organized to have 16 bytes per memory row or page.With the same write command as the byte write, the micro-controller does not issue a STOP bit aftersending the 1st byte data and receiving the ACKNOWLEDGE signal from the EEPROM on the 27th clock cycle. Instead it sends out a second 8-bit data word, with the EEPROM acknowledging at the 36th cycle. This data sending and EEPROM acknowledging cycle repeats until the micro-controller sends a STOP bit after the n 9th clock cycle. After which the EEPROM device will go into a self-timed partial or full page programming mode. After the page programming completes after a time of T WC , the devices will return to the STANDBY mode.F MDCo nf i de nt i a l© 2012 Fremont Micro Devices Inc. DS24C04_08_16-A0--page7The least significant 4 bits of the word address (column address) increments internally by one after receiving each data word. The rest of the word address bits (row address) do not change internally, but pointing to a specific memory row or page to be programmed. The first page write data word can be of any column address. Up to 16 data words can be loaded into a page. If more then 16 data words are loaded, the 17th data word will be loaded to the 1st data word column address. The 18th data word will be loaded to the 2nd data word column address and so on. In other word, data word address (column address) will “roll” over the previously loaded data. (C) ACKNOWLEDGE POLLINGACKNOWLEDGE polling may be used to poll the programming status during a self-timed internal programming. By issuing a valid read or write address command, the EEPROM will not acknowledge at the 9th clock cycle if the device is still in the self-timed programming mode. However, if the programming completes and the chip has returned to the STANDBY mode, the device will return a valid ACKNOWLEDGE signal at the 9th clock cycle.READ OPERATIONSThe read command is similar to the write command except the 8th read/write bit in address word is set to “1”. The three read operation modes are described as follows:(A) CURRENT ADDRESS READThe EEPROM internal address word counter maintains the last read or write address plus one if the power supply to the device has not been cut off. To initiate a current address read operation, the micro-controller issues a START bit and a valid device address word with the read/write bit (8th ) set to “1”. The EEPROM will response with an ACKNOWLEDGE signal on the 9th serial clock cycle. An 8-bit data word will then be serially clocked out. The internal address word counter will then automatically increase by one. For current address read the micro-controller will not issue an ACKNOWLEDGE signal on the 18th clock cycle. The micro-controller issues a valid STOP bit after the 18th clock cycle to terminate the read operation. The device then returns to STANDBY mode.(B) SEQUENTIAL READThe sequential read is very similar to current address read. The micro-controller issues a START bitand a valid device address word with read/write bit (8th ) set to “1”. The EEPROM will response with an ACKNOWLEDGE signal on the 9th serial clock cycle. An 8-bit data word will then be serially clocked out. Meanwhile the internally address word counter will then automatically increase by one. Unlike current address read, the micro-controller sends an ACKNOWLEDGE signal on the 18th clock cycle signaling the EEPROM device that it wants another byte of data. Upon receiving the ACKNOWLEDGE signal, the EEPROM will serially clocked out an 8-bit data word based on the incremented internal address counter. If the micro-controller needs another data, it sends out an ACKNOWLEDGE signal on the 27th clock cycle. Another 8-bit data word will then be serially clocked out. This sequential read continues as long as the micro-controller sends an ACKNOWLEDGE signal after receiving a new data word. When the internal address counter reaches its maximum valid address, it rolls over to the beginning of the memory array address. Similar to current address read, the micro-controller can terminate the sequential read by not acknowledging the last data word received, but sending a STOP bit afterwards instead.(C) RANDOM READRandom read is a two-steps process. The first step is to initialize the internal address counter with a target read address using a “dummy write” instruction. The second step is a current address read.To initialize the internal address counter with a target read address, the micro-controller issues a START bit first, follows by a valid device address with the read/write bit (8th ) set to “0”. The EEPROM will then acknowledge. The micro-controller will then send the address word. Again the EEPROM willacknowledge. Instead of sending a valid written data to the EEPROM, the micro-controller performs a current address readinstruction to read the data. Note that once a START bit is issued, the EEPROM will reset the internal programming process and continue to execute the new instruction - which is to read the current address.laitnedifnoCDMF© 2012 Fremont Micro Devices Inc. DS24C04_08_16-A0--page8F MDCo nf i de nt i al© 2012 Fremont Micro Devices Inc. DS24C04_08_16-A0--page9Figure 8: SCL and SDA Bus TimingAC CHARACTERISTICS1.8 V2.5-5.0 V Symbol ParameterMin Max MinMax Unit f SCLClock frequency, SCL 400 1000 kHz t LOW Clock pulse width low1.20.7µst HIGH Clock pulse width high0.4 0.3 µst I Noise suppression time (1) 180 120 ns t AAClock low to data out valid 0.30.90.20.7µs t BUF Time the bus must be free before a new transmission can start (1)1.3 0.5µs t HD.STA START hold time0.6 0.25 µs t SU.STA START set-up time 0.6 0.25 µs t HD.DAT Data in hold time 0 0 µs t SU.DAT Data in set-up time100100nst R Input rise time (1)0.3 0.3 µst F Input fall time (1) 300 100 nst SU.STO STOP set-up time 0.6 0.25 µs t DH Date out hold time 50 50 ns WRWrite cycle time55msEndurance(1)25o C, Page Mode, 3.3V1,000,000Write CyclesNotes: 1. This Parameter is expected by characterization but are not fully screened by test.2. AC Measurement conditions: R L (Connects to Vcc): 1.3K ΩInput Pulse Voltages: 0.3Vcc to 0.7VccInput and output timing reference Voltages: 0.5VccF MDCo nf i de nt i al© 2012 Fremont Micro Devices Inc. DS24C04_08_16-A0--page10DC CHARACTERISTICSSymbol Parameter Test ConditionsMin Typical Max Units V CC1 24C A supply V CC1.8 5.5 V I CC Supply read currentV CC @ 5.0V SCL = 400 kHz0.5 1.0 mA I CCSupply write current V CC @ 5.0V SCL = 400 kHz2.03.0 mA I SB1 Supply current V CC @ 1.8V, V IN = V CC or V SS 1.0 µA I SB2 Supply current V CC @ 2.5V, V IN = V CC or V SS 1.0 µA I SB3 Supply currentV CC @ 5.0V, V IN = V CC or V SS 0.06 1.0 µA I ILInput leakagecurrentV IN = V CC or V SS 3.0 µA I LOOutput leakagecurrentV IN = V CC or V SS3.0µAV IL Input low level -0.6 V CC x 0.3 V V IHInput high levelV CC x 0.7V CC +0.5 VV OL1 Output low level V CC @ 1.8V, I OL = 0.15 mA0.2 V V OL2 Output low level V CC @ 3.0V, I OL = 2.1 mA0.4VF MDCo nf i de nt i a l© 2012 Fremont Micro Devices Inc. DS24C04_08_16-A0--page11ORDERING INFORMATION:Density PackageTemperatureRangeVcc HSF Packaging Ordering CodeRoHSTube FT24C04A-UDR-BDIP8 -40℃-85℃ 1.8V-5.5VGreen Tube FT24C04A-UDG-B Tube FT24C04A-USR-B RoHSTape and Reel FT24C04A-USR-TTube FT24C04A-USG-B SOP8 -40℃-85℃ 1.8V-5.5VGreen Tape and Reel FT24C04A-USG-TTube FT24C04A-UMR-B RoHS Tape and Reel FT24C04A-UMR-TTube FT24C04A-UMG-B MSOP8 -40℃-85℃ 1.8V-5.5VGreen Tape and Reel FT24C04A-UMG-TTube FT24C04A-UTR-B RoHSTape and Reel FT24C04A-UTR-TTube FT24C04A-UTG-B TSSOP8 -40℃-85℃ 1.8V-5.5VGreen Tape and Reel FT24C04A-UTG-T RoHS Tape and Reel FT24C04A-ULR-T SOT23-5 -40℃-85℃ 1.8V-5.5VGreen Tape and Reel FT24C04A-ULG-T RoHS Tape and Reel FT24C04A-UPR-T TSOT23-5 -40℃-85℃ 1.8V-5.5V Green Tape and Reel FT24C04A-UPG-T RoHS Tape and Reel FT24C04A-UNR-T 4kbitsDFN8 -40℃-85℃ 1.8V-5.5V Green Tape and Reel FT24C04A-UNG-TRoHS Tube FT24C08A-UDR-B DIP8 -40℃-85℃ 1.8V-5.5VGreen Tube FT24C08A-UDG-B Tube FT24C08A-USR-B RoHSTape and Reel FT24C08A-USR-TTube FT24C08A-USG-B 8kbitsSOP8 -40℃-85℃ 1.8V-5.5VGreenTape and Reel FT24C08A-USG-TD: DIP8 S: SOP8 M: MSOP8 T: TSSOP8 L: SOT23-5 P: TSOT23-5 N: DFN8Packaging B: TubeT: Tape and Reel HSF R: RoHS G: GreenU:-40F MDCo nf i de nt i a l© 2012 Fremont Micro Devices Inc. DS24C04_08_16-A0--page12Density Package TemperatureRangeVcc HSF Packaging Ordering CodeTube FT24C08A-UMR-BRoHSTape and Reel FT24C08A-UMR-TTube FT24C08A-UMG-B MSOP8 -40℃-85℃ 1.8V-5.5VGreen Tape and Reel FT24C08A-UMG-TTube FT24C08A-UTR-B RoHSTape and Reel FT24C08A-UTR-TTube FT24C08A-UTG-B TSSOP8 -40℃-85℃ 1.8V-5.5VGreen Tape and Reel FT24C08A-UTG-T RoHSTape and Reel FT24C08A-ULR-T SOT23-5 -40℃-85℃ 1.8V-5.5V Green Tape and Reel FT24C08A-ULG-T RoHS Tape and Reel FT24C08A-UPR-T TSOT23-5 -40℃-85℃ 1.8V-5.5V Green Tape and Reel FT24C08A-UPG-T RoHS Tape and Reel FT24C08A-UNR-T 8kbitsDFN8 -40℃-85℃ 1.8V-5.5V Green Tape and Reel FT24C08A-UNG-TRoHS Tube FT24C16A-UDR-B DIP8 -40℃-85℃ 1.8V-5.5VGreen Tube FT24C16A-UDG-B Tube FT24C16A-USR-B RoHSTape and Reel FT24C16A-USR-TTube FT24C16A-USG-B SOP8 -40℃-85℃ 1.8V-5.5VGreen Tape and Reel FT24C16A-USG-TTube FT24C16A-UMR-B RoHSTape and Reel FT24C16A-UMR-TTube FT24C16A-UMG-B MSOP8 -40℃-85℃ 1.8V-5.5VGreen Tape and Reel FT24C16A-UMG-TTube FT24C16A-UTR-B RoHS Tape and Reel FT24C16A-UTR-TTube FT24C16A-UTG-B TSSOP8 -40℃-85℃ 1.8V-5.5VGreen Tape and Reel FT24C16A-UTG-T RoHSTape and Reel FT24C16A-ULR-T SOT23-5 -40℃-85℃ 1.8V-5.5V Green Tape and Reel FT24C16A-ULG-T RoHS Tape and Reel FT24C16A-UPR-T TSOT23-5 -40℃-85℃ 1.8V-5.5VGreen Tape and Reel FT24C16A-UPG-T RoHS Tape and Reel FT24C16A-UNR-T 16kbitsDFN8 -40℃-85℃ 1.8V-5.5VGreenTape and Reel FT24C16A-UNG-TF MDCo nf i de nt i al© 2012 Fremont Micro Devices Inc. DS24C04_08_16-A0--page13DIP8 PACKAGE OUTLINEDIMENSIONSDimensions In MillimetersDimensions In InchesSymbolMin Max Min MaxA 3.710 4.310 0.146 0.170 A1 0.510 0.020 A2 3.200 3.600 0.126 0.142B 0.380 0.570 0.015 0.022B1 1.524(BSC ) 0.060(BSC )C 0.204 0.360 0.008 0.014D 9.000 9.400 0.354 0.370E 6.200 6.600 0.244 0.260 E1 7.320 7.920 0.288 0.312 e 2.540 (BSC) 0.100(BSC ) L 3.000 3.600 0.118 0.142 E2 8.400 9.000 0.331 0.354F MDCo nf i de nt i al© 2012 Fremont Micro Devices Inc. DS24C04_08_16-A0--page14SOP8 PACKAGE OUTLINE DIMENSIONSDimensions In MillimetersDimensions In InchesSymbolMin Max Min MaxA 1.350 1.750 0.053 0.069A1 0.100 0.250 0.004 0.010A2 1.350 1.550 0.053 0.061 b 0.330 0.510 0.013 0.020 c 0.170 0.250 0.006 0.010D 4.700 5.100 0.185 0.200E 3.800 4.000 0.150 0.157 E1 5.800 6.200 0.228 0.244 e 1.270 (BSC)0.050 (BSC)L 0.400 1.270 0.016 0.050 θ 0° 8° 0° 8°F MDCo nf i de nt i al© 2012 Fremont Micro Devices Inc. DS24C04_08_16-A0--page15MSOP8 PACKAGE OUTLINE DIMENSIONSDimensions In MillimetersDimensions In InchesSymbolMin Max Min MaxA 0.820 1.100 0.320 0.043 A1 0.020 0.150 0.001 0.006 A2 0.750 0.950 0.030 0.037 b 0.250 0.380 0.010 0.015 c 0.090 0.230 0.004 0.009 D 2.900 3.100 0.114 0.122 e 0.65 (BSC) 0.026 (BSC) E 2.900 3.100 0.114 0.122 E1 4.750 5.050 0.187 0.199 L 0.400 0.800 0.016 0.031 θ 0° 6° 0° 6°F MDCo nf i de nt i al© 2012 Fremont Micro Devices Inc. DS24C04_08_16-A0--page16TSSOP8 PACKAGE OUTLINEDIMENSIONSDimensions In MillimetersDimensions In Inches SymbolMinMax Min Max D 2.900 3.100 0.114 0.122 E4.3004.5000.1690.177b 0.190 0.300 0.007 0.012c 0.090 0.200 0.004 0.008 E1 6.250 6.550 0.246 0.258 A 1.100 0.043 A2 0.800 1.000 0.031 0.039 A1 0.020 0.150 0.001 0.006e 0.65 (BSC) 0.026 (BSC) L 0.500 0.700 0.020 0.028H 0.25 (TYP) 0.01 (TYP)θ 1°7° 1° 7°F MDCo n f i de nt i a l© 2012 Fremont Micro Devices Inc. DS24C04_08_16-A0--page17SOT-23-5 PACKAGE OUTLINE DIMENSIONSDimensions In MillimetersDimensions In InchesSymbolMin Max Min MaxA 1.050 1.250 0.041 0.049A1 0.000 0.100 0.000 0.004 A2 1.050 1.150 0.041 0.045 b 0.300 0.500 0.012 0.020 c 0.100 0.200 0.004 0.008 D 2.820 3.020 0.111 0.119 E 1.500 1.700 0.059 0.067 E1 2.650 2.950 0.104 0.116 e 0.95 (BSC) 0.037 (BSC) e1 1.800 2.000 0.071 0.079 L 0.300 0.600 0.012 0.024 θ 0° 8° 0° 6°F MDCo nf i de nt i a l© 2012 Fremont Micro Devices Inc. DS24C04_08_16-A0--page18TSOT-23-5 PACKAGE OUTLINE DIMENSIONSDimensions In MillimetersDimensions In InchesSymbolMin Max Min MaxA 0.700 0.900 0.028 0.035A1 0.000 0.100 0.000 0.004 A2 0.700 0.800 0.028 0.031 b 0.350 0.500 0.014 0.020 c 0.080 0.200 0.003 0.008 D 2.820 3.020 0.111 0.119 E 1.600 1.700 0.063 0.067 E1 2.650 2.950 0.104 0.116 e 0.95 (BSC) 0.037 (BSC) e1 1.90 (BSC) 0.075 (BSC) L 0.300 0.600 0.012 0.024 θ 0° 8° 0° 8°F MDCo nf i de n t i al© 2012 Fremont Micro Devices Inc. DS24C04_08_16-A0--page19DFN8 PACKAGE OUTLINE DIMENSIONSDimensions In MillimetersSymbolMinNomMaxA 0.70 0.75 0.80A1 - 0.02 0.05 b 0.18 0.25 0.03 c 0.18 0.20 0.25 D 1.902.00 2.10D2 1.50REF e 0.50BSC Nd 1.50BSC E 2.90 3.00 3.10 E2 1.60REFL 0.30 0.40 0.50 h 0.20 0.25 0.30F MDCo nf i de n t i al© 2012 Fremont Micro Devices Inc. DS24C04_08_16-A0--page20Fremont Micro Devices (SZ) Limited* Information furnished is believed to be accurate and reliable. However, Fremont Micro Devices, Incorporated (BVI) assumes no responsibility for the consequences of use of such information or for any infringement of patents of other rights of third parties which may result from its use. No license is granted by implication orotherwise under any patent rights of Fremont Micro Devices, Incorporated (BVI). Specifications mentioned in this publication are subject to change without notice. This publication supersedes and replaces all information previously supplied. Fremont Micro Devices, Incorporated (BVI) products are not authorized for use as critical components in life support devices or systems without express written approval of Fremont Micro Devices, Incorporated (BVI). The FMD logo is a registered trademark of Fremont Micro Devices, Incorporated (BVI). All other names are the property of their respective owners.。

S-24C16C

106次 / 字*1(+25°C时) 100年(+25°C时) 16 K位 100%

*1. 每个地址 (字:8 位) *2. 详情请参阅“ 产品型号的构成”。

■ 封装

• 8-Pin SOP(JEDEC) • 8-Pin TSSOP • SNT-8A • TMSOP-8 • WLP

■ 推荐工作条件

项目 电源电压 高电位输入电压 低电位输入电压

符号

VCC VIH VIL

表7 条件 读出 写入

VCC = 1.6 V ~ 5.5 V VCC = 1.6 V ~ 5.5 V

最小值

1.6 1.7 0.7×VCC -0.3

最大值

5.5 5.5 5.5 0.3×VCC

单位

V V V V

■ 端子容量

4

GND

接地

5

SDA*3

串行数据输入输出

6

SCL*3

串行时钟输入

写入保护输入

7

WP

VCC连接:

保护有效

电气开路状态或与GND连接: 保护无效

8

VCC

电源

*1. 请与 GND 或 VCC 相连接。 *2. 请与 GND 相连接。 *3. 请妥善处理,以防被输入高阻抗。

TMSOP-8 Top view

NC

-

1.0

-

1.0

-

1.0

ILO

SDA VOUT = GND ~ VCC

-

1.0

-

1.0

-

1.0

WP

IIL

VIN<0.3×VCC

S-24C01A中文资料

Rev. 2.2_30

CMOS 2-WIRE SERIAL EEPROM

S-24C01A/02A/04A

The S-24C0XA is a series of 2-wired, low power 1K/2K/4K-bit EEPROMs

with a wide operating range. They are organized as 128-word × 8-bit, 256-word × 8-bit, and 512-word × 8-bit, respectively. Each is capable of page write, and sequential read. The time for byte write and page write is the same, i. e., 1 msec. (max.)

during operation at 5 V ± 10%.

Features

• Low power consumption Standby: 1.0 µA Max. Operating: 0.4 mA Max. 0.3 mA Max.

(VCC=5.5 V) (VCC=5.5 V) (VCC=3.3 V)

TEST pin (S-24C01A): Connected to GND.

WP (Write Protection) pin (S-24C02A, S-24C04A):

* Connected to Vcc:

Protection valid

* Connected to GND: Protection invalid

Table 8 Measurement Conditions

Input pulse voltage Input pulse rising/falling time Output judgment voltage Output load

三星S3C2416开发板手册

第四章 结构框图 ..........................................................................................................................26

第五章 电源设计 ..........................................................................................................................27

第二章 硬件特性 ............................................................................................................................4

2.1 参数特性 .......................................................................................................................................4 2.2 核心板外观 ...................................................................................................................................5 2.3 规格尺寸 .......................................................................................................................................5 2.4 底板正面图 ...................................................................................................................................6 2.5 底板结构布局 ...............................................................................................................................6 2.6 底板硬件接口 ...............................................................................................................................7 2.7 液晶屏模块(UT_LCD43C) .....................................................................................................8 2.8 核心板引脚定义 ...........................................................................................................................9

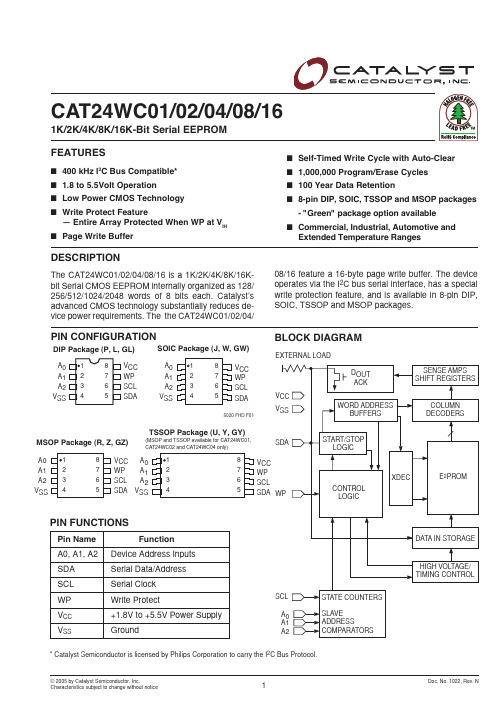

CAT24WC16GYETE13F资料

V A2A0A1CAT24WC01/02/04/08/16ABSOLUTE MAXIMUM RATINGS*Temperature Under Bias .................–55°C to +125°C Storage Temperature.......................–65°C to +150°C Voltage on Any Pin withRespect to Ground (1)...........–2.0V to +V CC + 2.0V V CC with Respect to Ground ...............–2.0V to +7.0V Package Power DissipationCapability (Ta = 25°C)...................................1.0W Lead Soldering Temperature (10 secs)............300°C Output Short Circuit Current (2)........................100mA *COMMENTStresses above those listed under “Absolute Maximum Ratings ” may cause permanent damage to the device.These are stress ratings only, and functional operation of the device at these or any other conditions outside of those listed in the operational sections of this specification is not implied. Exposure to any absolute maximum rating for extended periods may affect device performance and reliability.RELIABILITY CHARACTERISTICS Symbol ParameterMin.Max.Units N END (3)Endurance 1,000,000Cycles/Byte T DR (3)Data Retention 100Years V ZAP (3)ESD Susceptibility 2000Volts I LTH (3)(4)Latch-up100mAD.C. OPERATING CHARACTERISTICSV CC = +1.8V to +5.5V, unless otherwise specified.Limits Symbol ParameterMin.Typ.Max.Units Test Conditions I CC Power Supply Current 3mA f SCL = 100 KHz I SB (5)Standby Current (V CC = 5.0V)1µA V IN = GND or V CC I LI Input Leakage Current 10µA V IN = GND to V CC I LO Output Leakage Current 10µA V OUT = GND to V CCV IL Input Low Voltage –1V CC x 0.3V V IH Input High VoltageV CC x 0.7V CC + 0.5V V OL1Output Low Voltage (V CC = 3.0V)0.4V I OL = 3 mA V OL2Output Low Voltage (V CC = 1.8V)0.5VI OL = 1.5 mA Note:(1)The minimum DC input voltage is –0.5V. During transitions, inputs may undershoot to –2.0V for periods of less than 20 ns. Maximum DCvoltage on output pins is V CC +0.5V, which may overshoot to V CC + 2.0V for periods of less than 20ns.(2)Output shorted for no more than one second. No more than one output shorted at a time.(3)These parameters are tested initially and after a design or process change that affects the parameter according to appropriate AEC-Q100and JEDEC test methods.(4)Latch-up protection is provided for stresses up to 100 mA on address and data pins from –1V to V CC +1V.(5)Maximum standby current (I SB ) = 10µA for the Automotive and Extended Automotive temperature range.CAPACITANCE T A = 25°C, f = 1.0 MHz, V CC = 5V Symbol TestMax.Units Conditions C I/O (3)Input/Output Capacitance (SDA)8pF V I/O = 0V C IN (3)Input Capacitance (A0, A1, A2, SCL, WP)6pFV IN = 0VCAT24WC01/02/04/08/16Note:(1)This parameter is tested initially and after a design or process change that affects the parameter.(2)t PUR and t PUW are the delays required from the time V CC is stable until the specified operation can be initiated.The write cycle time is the time from a valid stop condition of a write sequence to the end of the internal program/erase cycle. During the write cycle, the bus interface circuits are disabled, SDA is allowed to remain high, and the device does not respond to its slave address.Write Cycle Limits Symbol Parameter Min.Typ.Max Units t WRWrite Cycle Time10msPower-Up Timing(1)(2)Symbol ParameterMax.Units t PUR Power-up to Read Operation 1ms t PUWPower-up to Write Operation1msA.C. CHARACTERISTICSV CC = +1.8V to +5.5V, unless otherwise specified.Read & Write Cycle Limitsl o b m y S r e t e m a r a P 8.1-X X C W 42T A C XX C W 42T A C s t i n U V5.5-V 8.1V 5.5-V 5.2V 5.5-V 5.4.n i M .x a M .n i M .x a M .n i M .x a M F L C S yc n e u q e r F k c o l C 001001004z H k T I)1(t a t n a t s n o C e m i T n o i s s e r p p u S e s i o N st u p n I A D S ,L C S 002002002s n t A A K C A d n a t u O a t a D A D S o t w o L L C S tu O 5.35.31µs t FU B )1(e r o f e B e e r F e b t s u M s u B e h t e m i T t r a t S n a C n o i s s i m s n a r T w e N a 7.47.42.1µs t A T S :D H e m i T d l o H n o i t i d n o C t r a t S 446.0µs t W O L d o i r e P w o L k c o l C 7.47.42.1µs t H G I H do i r e P h g i H k c o l C 446.0µs t A T S :U S em i T p u t e S n o i t i d n o C t r a t S )n o i t i d n o C t r a t S d e t a e p e R a r o f (7.47.46.0µs t T A D :D H e m i T d l o H n I a t a D 000s n t T A D :U S e m i T p u t e S n I a t a D 050505s n t R )1(e m i T e s i R L C S d n a A D S 113.0µs t F)1(e m i T l l a F L C S d n a A D S 003003003s n t O T S :U S e m i T p u t e S n o i t i d n o C p o t S 446.0µs t HD em i T d l o H t u O a t a D 001001001snCAT24WC01/02/04/08/16FUNCTIONAL DESCRIPTIONThe CAT24WC01/02/04/08/16 supports the I 2C Bus data transmission protocol. This Inter-Integrated Circuit Bus protocol defines any device that sends data to the bus to be a transmitter and any device receiving data to be a receiver. Data transfer is controlled by the Master device which generates the serial clock and all START and STOP conditions for bus access. The CAT24WC01/02/04/08/16 operates as a Slave device. Both the Mas-ter and Slave devices can operate as either transmitter or receiver, but the Master device controls which mode is activated. A maximum of 8 devices (CAT24WC01 and CAT24WC02), 4 devices (CAT24WC04), 2 devices (CAT24WC08) and 1 device (CAT24WC16) may be connected to the bus as determined by the device address inputs A0, A1, and A2.PIN DESCRIPTIONSSCL: Serial ClockThe CAT24WC01/02/04/08/16 serial clock input pin is used to clock all data transfers into or out of the device.This is an input pin.SDA: Serial Data/AddressThe CAT24WC01/02/04/08/16 bidirectional serial data/address pin is used to transfer data into and out of the device. The SDA pin is an open drain output and can be wire-ORed with other open drain or open collector outputs.A0, A1, A2: Device Address InputsThese inputs set device address when cascading mul-tiple devices. When these pins are left floating the default values are zeros.A maximum of eight devices can be cascaded whenFigure 3. Start/Stop Timing5020 FHD F055020 FHD F03SCLSDA INSDA OUTSTART BITSDASTOP BITSCLCAT24WC01/02/04/08/16using either CAT24WC01 or CAT24WC02 device. All three address pins are used for these densities. If only one CAT24WC01 or CAT24WC02 is addressed on the bus, all three address pins (A0, A1and A2) can be left floating or connected to V SS .A total of four devices can be addressed on a single bus when using CAT24WC04 device. Only A1 and A2address pins are used with this device. The A0 address pin is a no connect pin and can be tied to V SS or left floating. If only one CAT24WC04 is being addressed on the bus, the address pins (A1 and A2) can be left floating or connected to V SS .Only two devices can be cascaded when using CAT24WC08. The only address pin used with this device is A2. The A0 and A1 address pins are no connect pins and can be tied to V SS or left floating. If only one CAT24WC08 is being addressed on the bus, the address pin (A2) can be left floating or connected to V SS .The CAT24WC16 is a stand alone device. In this case,all address pins (A0, A1and A2) are no connect pins and can be tied to V SS or left floating.WP: Write ProtectIf the WP pin is tied to V CC the entire memory array becomes Write Protected (READ only). When the WP pin is tied to V SS or left floating normal read/write operations are allowed to the device.I 2C Bus ProtocolThe following defines the features of the I 2C bus protocol:(1)Data transfer may be initiated only when the bus isnot busy.(2)During a data transfer, the data line must remain stable whenever the clock line is high. Any changes in the data line while the clock line is high will be interpreted as a START or STOP condition.START ConditionThe START Condition precedes all commands to the device, and is defined as a HIGH to LOW transition of SDA when SCL is HIG H. The CAT24WC01/02/04/08/16monitor the SDA and SCL lines and will not respond until this condition is met.STOP ConditionA LOW to HIGH transition of SDA when SCL is HIGH determines the STOP condition. All operations must end with a STOP condition.DEVICE ADDRESSINGThe bus Master begins a transmission by sending a START condition. The Master then sends the address of the particular slave device it is requesting. The four most significant bits of the 8-bit slave address are fixed as 1010 for the CAT24WC01/02/04/08/16 (see Fig. 5).The next three significant bits (A2, A1, A0) are the device address bits and define which device or which part of the device the Master is accessing. Up to eight CAT24WC01/02, four CAT24WC04, two CAT24WC08, and one CAT24WC16 may be individually addressed by the system. The last bit of the slave address specifies whether a Read or Write operation is to be performed.When this bit is set to 1, a Read operation is selected,and when set to 0, a Write operation is selected.After the Master sends a START condition and the slave address byte, the CAT24WC01/02/04/08/16 monitors the bus and responds with an acknowledge (on the SDA line) when its address matches the transmitted slaveFigure 4. Acknowledge Timing5020 FHD F06ACKNOWLEDGESTARTSCL FROM MASTERDATA OUTPUTFROM TRANSMITTERDATA OUTPUT FROM RECEIVERCAT24WC01/02/04/08/16address. The CAT24WC01/02/04/08/16 then performs a Read or Write operation depending on the state of the R/W bit.AcknowledgeAfter a successful data transfer, each receiving device is required to generate an acknowledge. The Acknowledg-ing device pulls down the SDA line during the ninth clock cycle, signaling that it received the 8 bits of data.The CAT24WC01/02/04/08/16 responds with an ac-knowledge after receiving a START condition and its slave address. If the device has been selected along with a write operation, it responds with an acknowledge after receiving each 8-bit byte.When the CAT24WC01/02/04/08/16 is in a READ mode it transmits 8 bits of data, releases the SDA line, and monitors the line for an acknowledge. Once it receives this acknowledge, the CAT24WC01/02/04/08/16 will continue to transmit data. If no acknowledge is sent by the Master, the device terminates data transmission and waits for a STOP condition.WRITE OPERATIONSByte WriteIn the Byte Write mode, the Master device sends the START condition and the slave address information (with the R/W bit set to zero) to the Slave device. After the Slave generates an acknowledge, the Master sends the byte address that is to be written into the address pointer of the CAT24WC01/02/04/08/16. After receiving another acknowledge from the Slave, the Master device transmits the data byte to be written into the addressed memory location. The CAT24WC01/02/04/08/16 ac-knowledge once more and the Master generates the STOP condition, at which time the device begins its internal programming cycle to nonvolatile memory. While this internal cycle is in progress, the device will not respond to any request from the Master device.Page WriteThe CAT24WC01/02/04/08/16 writes up to 16 bytes of data in a single write cycle, using the Page Write operation. The Page Write operation is initiated in the same manner as the Byte Write operation, however instead of terminating after the initial word is transmitted,Figure 5. Slave Address Bits*A0, A1 and A2 correspond to pin 1, pin 2 and pin 3 of the device.**a8, a9 and a10 correspond to the address of the memory array address word.***A0, A1 and A2 must compare to its corresponding hard wired input pins (pins 1, 2 and 3).1010A2 A1 A0R/W1010A2A1a8R/W1010A2a9 a8R/W1010a10a9a8R/WCAT24WC01/02CAT24WC04CAT24WC08CAT24WC16CAT24WC01/02/04/08/1624WCXX F09Figure 7. Page Write Timing5020 FHD F08Figure 6. Byte Write Timing*P=7 for CAT24WC01 and P=15 for CAT24WC02/04/08/16* = Don't care for CAT24WC01BUS ACTIVITY:MASTERSDA LINEBYTE C KC KC KS T O C KC KS T A R SLAVE NOTE: IN THIS EXAMPLE n = XXXX 0000(B); X = 1 or 0WRITE PROTECTIONThe Write Protection feature allows the user to protect against inadvertent programming of the memory array.If the WP pin is tied to V CC , the entire memory array is protected and becomes read only. The CAT24WC01/02/04/08/16 will accept both slave and byte addresses,but the memory location accessed is protected from programming by the device ’s failure to send an acknowledge after the first byte of data is received.READ OPERATIONSThe READ operation for the CAT24WC01/02/04/08/16is initiated in the same manner as the write operation with the one exception that the R/W bit is set to a one.Three different READ operations are possible: Immediate Address READ, Selective READ and Sequential READ.Immediate Address ReadThe CAT24WC01/02/04/08/16’s address counter contains the address of the last byte accessed,incremented by one. In other words, if the last READ or WRITE access was to address N, the READ immediately following would access data from address N+1. If N=E (where E = 255 for 24WC02, 511 for 24WC04, 1023 for 24WC08, and 2047 for 24WC16), then the counter will 'wrap around' to address 0 and continue to clock out data. If N = E (where E = 127 for the CAT24WC01) the counter will not 'wrap around'.BYTE ADDRESSSLAVE ADDRESSSA C KA C KDATAA C K S T O P PBUS ACTIVITY:MASTERSDA LINES T A R T the Master is allowed to send up to fifteen additional bytes. After each byte has been transmitted the CAT24WC01/02/04/08/16 will respond with an acknowledge, and internally increment the low order address bits by one. The high order bits remain unchanged.If the Master transmits more than sixteen bytes prior to sending the STOP condition, the address counter ‘wraps around ’, and previously transmitted data will be overwritten.Once all sixteen bytes are received and the STOP condition has been sent by the Master, the internal programming cycle begins. At this point all received data is written to the CAT24WC01/02/04/08/16 in a single write cycle.Acknowledge PollingThe disabling of the inputs can be used to take advantage of the typical write cycle time. Once the stop condition is issued to indicate the end of the host ’s write operation,the CAT24WC01/02/04/08/16 initiates the internal write cycle. ACK polling can be initiated immediately. This involves issuing the start condition followed by the slave address for a write operation. If the CAT24WC01/02/04/08/16 is still busy with the write operation, no ACK will be returned. If the CAT24WC01/02/04/08/16 has completed the write operation, an ACK will be returned and the host can then proceed with the next read or write operation.CAT24WC01/02/04/08/165020 FHD F10Figure 8. Immediate Address Read TimingSCL SDA 8TH BIT STOPNO ACKDATA OUT89SLAVE ADDRESSSA C KDATAN O A C KS T O P PBUS ACTIVITY:MASTERSDA LINES T A R T Selective ReadSelective READ operations allow the Master device to select at random any memory location for a READ operation. The Master device first performs a ‘dummy ’write operation by sending the START condition, slave address and byte address of the location it wishes to read. After the CAT24WC01/02/04/08/16 acknowledge the word address, the Master device resends the START condition and the slave address, this time with the R/W bit set to one. The CAT24WC01/02/04/08/16 then responds with its acknowledge and sends the 8-bit byte requested. The master device does not send an acknowledge but will generate a STOP condition.Sequential ReadThe Sequential READ operation can be initiated by either the immediate Address READ or Selective READoperations. After the 24WC01/02/04/08/16 sends initial 8-bit byte requested, the Master will respond with an acknowledge which tells the device it requires more data. The CAT24WC01/02/04/08/16 will continue to output an 8-bit byte for each acknowledge sent by the Master. The operation is terminated when the Master fails to respond with an acknowledge, thus sending the STOP condition.The data being transmitted from the CAT24WC01/02/04/08/16 is outputted sequentially with data from address N followed by data from address N+1. The READ operation address counter increments all of the CAT24WC01/02/04/08/16 address bits so that the entire memory array can be read during one operation. If more than the E (where E = 255 for 24WC02, 511 for 24WC04,1023 for 24WC08, and 2047 for 24WC16) bytes are read out, the counter will “wrap around ” and continue to clock out data bytes. If N = E (where E = 127 for the CAT24WC01) the counter will not 'wrap around'.CAT24WC01/02/04/08/165020 FHD F12Figure 10. Sequential Read Timing24WCXX F11Figure 9. Selective Read TimingSLAVE ADDRESSSA C KN O A C K S T O P PBUS ACTIVITY:MASTERSDA LINES T A R T BYTE ADDRESS (n)S A C KDATA nSLAVE ADDRESSA C KS T AR T *BUS ACTIVITY:MASTERSDA LINEDATA n+xDATA nC KC KDATA n+1C KS T O O A C KDATA n+2C KSLAVE ADDRESSCAT24WC01/02/04/08/16Notes:plies with JEDEC Publication 95 MS001 dimensions; however, some of the dimensions may be more stringent.2.All linear dimensions are in inches and parenthetically in millimeters.0.100 (2.54)BSC8-LEAD 300 MIL WIDE PLASTIC DIP (P, L, GL)8-LEAD 150 MIL WIDE SOIC (J, W, GW)Notes:plies with JEDEC publication 95 MS-012 dimensions; however, some dimensions may be more stringent.2.All linear dimensions are in inches and parenthetically in millimeters.CAT24WC01/02/04/08/1611Doc. No. 1022, Rev. N© 2005 by Catalyst Semiconductor, Inc.Characteristics subject to change without noticeSECTION A - ANotes:(1)All dimensions are in mm Angles in degrees.2Does not include Mold Flash, Protrusion or Gate Burrs. Mold Flash, Protrusions or Gate Burrs shall not exceed 0.15 mm. per side. 3Does not include Interlead Flash orProtrusion. Interlead Flash or Protrusion shall not exceed 0.25 mm per side. 4Does not include Dambar Protrusion, allowable Dambar Protrusion shall be 0.08 mm.(5)This part is compliant with JEDEC Specification MO-187 Variations AA.(6) Lead span/stand off height/coplanarity are considered as special characteristics. (S)(7) Controlling dimensions in inches. [mm]CAT24WC01/02/04/08/1612Doc. No. 1022, Rev. N© 2005 by Catalyst Semiconductor, Inc.Characteristics subject to change without notice8-LEAD TSSOP (U, Y, GY)CAT24WC01/02/04/08/1613Doc. No. 1022, Rev. N© 2005 by Catalyst Semiconductor, Inc.Characteristics subject to change without noticeORDERING INFORMATIONNotes:(1) The device used in the above example is a CAT24WC02JI-1.8TE13REV-E (SOIC, Industrial Temperature, 1.8 Volt to 5.5 VoltOperating Voltage, Tape & Reel, Die Revision E)** Available for CAT24WC01, CAT24WC02 and CAT24WC04Catalyst Semiconductor, Inc.Corporate Headquarters 1250 Borregas Avenue Sunnyvale, CA 94089Phone: 408.542.1000Fax: 408.542.1200Publication #:1022Revison:NIssue date:08/12/05Copyrights, Trademarks and PatentsTrademarks and registered trademarks of Catalyst Semiconductor include each of the following:DPP ™AE 2 ™Catalyst Semiconductor has been issued U.S. and foreign patents and has patent applications pending that protect its products. For a complete list of patents issued to Catalyst Semiconductor contact the Company’s corporate office at 408.542.1000.CATALYST SEMICONDUCTOR MAKES NO WARRANTY, REPRESENTATION OR GUARANTEE, EXPRESS OR IMPLIED, REGARDING THE SUITABILITY OF ITS PRODUCTS FOR ANY PARTICULAR PURPOSE, NOR THAT THE USE OF ITS PRODUCTS WILL NOT INFRINGE ITS INTELLECTUAL PROPERTY RIGHTS OR THE RIGHTS OF THIRD PARTIES WITH RESPECT TO ANY PARTICULAR USE OR APPLICATION AND SPECIFICALLY DISCLAIMS ANY AND ALL LIABILITY ARISING OUT OF ANY SUCH USE OR APPLICATION, INCLUDING BUT NOT LIMITED TO, CONSEQUENTIAL OR INCIDENTAL DAMAGES.Catalyst Semiconductor products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the Catalyst Semiconductor product could create a situation where personal injury or death may occur.Catalyst Semiconductor reserves the right to make changes to or discontinue any product or service described herein without notice. Products with data sheets labeled "Advance Information" or "Preliminary" and other products described herein may not be in production or offered for sale.Catalyst Semiconductor advises customers to obtain the current version of the relevant product information before placing orders. Circuit diagrams illustrate typical semiconductor applications and may not be complete.REVISION HISTORYDate Rev.Reason2/3/2004HAdded: CAT24WC01/02/16 not recommended for new designs. See CAT24FC01, CAT24FC02 and CAT24FC16 data sheets5/28/2004I Added Die Revision to ordering information 7/28/2004J Update DC operating characteristics and notes 1/27/2005K Added Die Revision E to ordering information 2/28/2005L Edit Ordering Information 3/18/2005M Edit Features08/12/05NEdit FeaturesEdit Pin FunctionsEdit Reliability CharacteristicsEdit D.C. Operating Characteristics Edit A.C. Characteristics Add Package Dimensions Edit Ordering Information。

AT24C02,AT24C04,AT24C16产品规格书

S P E C I F I C A T I O N24C02/24C04/24C08/24C16Version 1.0Two-wire Serial EEPROM2K bits (256 X 8) / 4K bits (512 X 8) / 8K bits (1024 X 8) / 16K bits (2048 X 8)▉FeaturesThe 24C02/24C04/24C08/24C16 provides 2048/4096/8192/16384 bits of serial electrically erasable and programmable read-only memory (EEPROM) organized as 256/512/1024/2048 words of 8 bits each. The device is optimized for use in many industrial and commercial applications wherelow-power and low-voltage operation are essential. The 24C02/24C04/24C08/24C16 is available in space-saving 8-lead PDIP, 8-lead SOP, and 8-lead TSSOP packages and is accessed via a two-wire serial interface.▉Pin ConfigurationTwo-wire Serial EEPROM2K bits (256 X 8) / 4K bits (512 X 8) / 8K bits (1024 X 8) / 16K bits (2048 X 8)▉Pin DescriptionsTwo-wire Serial EEPROM2K bits (256 X 8) / 4K bits (512 X 8) / 8K bits (1024 X 8) / 16K bits (2048 X 8)▉Pin Descriptions24C02, 2K SERIAL EEPROM: Internally organized with 32 pages of 8 bytes each, the 2K requires an 8-bit data word address for random word addressing.24C04, 4K SERIAL EEPROM: Internally organized with 32 pages of 16 bytes each, the 4K requires a 9-bit data word address for random word addressing.24C08, 8K SERIAL EEPROM: Internally organized with 64 pages of 16 bytes each, the 8K requires a 10-bit data word address for random word addressing.24C16, 16K SERIAL EEPROM: Internally organized with 128 pages of 16 bytes each, the 16K requires an 11-bit data word address for random word addressing.▉Device OperationTwo-wire Serial EEPROM 2K bits (256 X 8) / 4K bits (512 X 8) / 8K bits (1024 X 8) / 16K bits (2048 X 8)Two-wire Serial EEPROM2K bits (256 X 8) / 4K bits (512 X 8) / 8K bits (1024 X 8) / 16K bits (2048 X 8) The 2K, 4K, 8K and 16K EEPROM devices all require an 8-bit device address word following a start condition to enable the chip for a read or write operation (see to Figure 4 on page 7).The device address word consists of a mandatory "1", "0" sequence for the first four most significant bits as shown. This is common to all the Serial EEPROM devices.The next 3 bits are the A2, A1 and A0 device address bits for the 2K EEPROM. These 3 bits must compare to their corresponding hardwired input pins.The 4K EEPROM only uses the A2 and A1 device address bits with the third bit being a memory page address bit. The two device address bits must compare to their corresponding hardwired input pins. The A0 pin is no connect.The 8K EEPROM only uses the A2 device address bit with the next 2 bits being for memory page addressing. The A2 bit must compare to its corresponding hard-wired input pin. The A1 and A0 pins are no connect.The 16K does not use any device address bits but instead the 3 bits are used for memory page addressing. These page addressing bits on the 4K, 8K and 16K devices should be considered the most significant bits of the data word address which follows. The A0, A1 and A2 pins are no connect.The eighth bit of the device address is the read/write operation select bit. A read operation is initiated if this bit is high and a write operation is initiated if this bit is low.Upon a compare of the device address, the EEPROM will output a "0". If a compare is not made, the chip will return to a standby state.▉Write OperationsTwo-wire Serial EEPROM2K bits (256 X 8) / 4K bits (512 X 8) / 8K bits (1024 X 8) / 16K bits (2048 X 8) Read operations are initiated the same way as write operations with the exception that the read/write select bit in the device address word is set to "1". There are three read operations: current address read,random address read and sequential read.CURRENT ADDRESS READ: The internal data word address counter maintains the last address accessed during the last read or write operation, incremented by one. This address stays valid between operations as long as the chip power is maintained. The address "roll over" during read is from the last byte of the last memory page to the first byte of the first page. The address "roll over" during write is from the last byte of the current page to the first byte of the same page.Once the device address with the read/write select bit set to "1" is clocked in and acknowledged by the EEPROM, the current address data word is serially clocked out. The microcontroller does not respond with an input "0" but does generate a following stop condition (see Figure 7 on page 8).RANDOM READ: A random read requires a "dummy" byte write sequence to load in the data word address. Once the device address word and data word address are clocked in and acknowledged by the EEPROM, the microcontroller must generate another start condition. The microcontroller now initiates a current address read by sending a device address with the read/write select bit high. The EEPROM acknowledges the device address and serially clocks out the data word. The microcontroller does not respond with a "0" but does generate a following stop condition (see Figure 8 on page 8). SEQUENTIAL READ: Sequential reads are initiated by either a current address read or a randomTwo-wire Serial EEPROM 2K bits (256 X 8) / 4K bits (512 X 8) / 8K bits (1024 X 8) / 16K bits (2048 X 8)Two-wire Serial EEPROM2K bits (256 X 8) / 4K bits (512 X 8) / 8K bits (1024 X 8) / 16K bits (2048 X 8)l Absolute Maximum Stress RatingsDC Supply Voltage . . . . . . . . . . . . . . . . .-0.3V to +6.5V Input / Output Voltage . . . . . . . .GND-0.3V to V CC+0.3V Operating Ambient Temperature . . . . . -40℃to +85℃Storage Temperature . . . . . . . . . . . . -65℃to +150℃l CommentsStresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to this device. These are stress ratings only. Functional operation of this device at these or any other conditions above those indicated in the operational sections of this specification is not implied or intended. Exposure to the absolute maximum rating conditions for extended periods may affect device reliability.Two-wire Serial EEPROM2K bits (256 X 8) / 4K bits (512 X 8) / 8K bits (1024 X 8) / 16K bits (2048 X 8)▉DC Electrical CharacteristicsApplicable over recommended operating range from TA = 25 ℃, f = 1.0 MHz, VCC = +1.8V Parameter Symbol Min. Typ. Max. Unit ConditionCI/O - - 8 pF VI/O = 0V Input/Output Capacitance(SDA)Input Capacitance (A0, A1,CIN - - 8 pF VIN = 0V A2, SCL)▉AC Electrical CharacteristicsTwo-wire Serial EEPROM2K bits (256 X 8) / 4K bits (512 X 8) / 8K bits (1024 X 8) / 16K bits (2048 X 8) Figure 10: SCL: Serial Clock, SDA: Serial Data I/OTwo-wire Serial EEPROM2K bits (256 X 8) / 4K bits (512 X 8) / 8K bits (1024 X 8) / 16K bits (2048 X 8)▉Write Cycle Timing。

FMD FT24C16A

Two-Wire Serial EEPROM4K, 8K and 16K (8-bit wide)FEATURES❑Low voltage and low power operations:FT24C04A/08A/16A: V CC = 1.8V to 5.5V❑Maximum Standby current < 1µA (typically 0.02µA and 0.06µA @ 1.8V and 5.5V respectively).❑16 bytes page write mode.❑Partial page write operation allowed.❑Internally organized: 512 x 8 (4K), 1024 x 8 (8K), 2048 x 8 (16K).❑Standard 2-wire bi-directional serial interface.❑Schmitt trigger, filtered inputs for noise protection.❑Self-timed Write Cycle (5ms maximum).❑ 1 MHz (5V), 400 kHz (1.8V, 2.5V, 2.7V) Compatibility.❑Automatic erase before write operation.❑Write protect pin for hardware data protection.❑High reliability: typically 1, 000,000 cycles endurance.❑100 years data retention.❑Industrial temperature range (-40o C to 85o C).❑Standard 8-lead DIP/SOP/MSOP/TSSOP/DFN and 5-lead SOT-23/TSOT-23 Pb-free packages. DESCRIPTIONThe FT24C04A/08A/16A series are 4,096/8,192/16,384 bits of serial Electrical Erasable and Programmable Read Only Memory, commonly known as EEPROM. They are organized as 512/1,024/2,048 words of 8 bits (1 byte) each. The devices are fabricated with proprietary advanced CMOS process for low power and low voltage applications. These devices are available in standard 8-lead DIP, 8-lead SOP, 8-lead TSSOP, 8-lead DFN, 8-lead MSOP, and 5-lead SOT-23/TSOT-23packages. A standard 2-wire serial interface is used to address all read and write functions. Our extended V CC range(1.8V to 5.5V)devices enables wide spectrum of applications.PIN CONFIGURATIONPin Name Pin FunctionA2, A1, A0 Device Address InputsSDA Serial Data Input / Open Drain OutputSCL Serial Clock InputWP Write ProtectNo-ConnectNC© 2012 Fremont Micro Devices Inc. DS24C04_08_16-A0--page1© 2012 Fremont Micro Devices Inc. DS24C04_08_16-A0--page2All these packaging types come in conventional or Pb-free certified.VCC W P SCL SDAA2A1A0G 8L DIP 8L SOP8L TSSOP W P VCCG ND FT24C04A/08A/16A 5L SOT-23SCL 8L DFN8L M SOP 5L TSO T-23ABSOLUTE MAXIMUM RATINGSIndustrial operating temperature: -40℃ to 85℃ Storage temperature:-50℃ to 125℃Input voltage on any pin relative to ground: -0.3V to V CC + 0.3V Maximum voltage: 8VESD protection on all pins: >2000V* Stresses exceed those listed under “Absolute Maximum Rating” may cause permanent damage to the device. Functional operation of the device at conditions beyond those listed in the specification is not guaranteed. Prolonged exposure to extreme conditions may affect device reliability or functionality .PIN DESCRIPTIONS(A) SERIAL CLOCK (SCL)The rising edge of this SCL input is to latch data into the EEPROM device while the falling edge of thisclock is to clock data out of the EEPROM device.(B) DEVICE / CHIP SELECT ADDRESSES (A2, A1, A0)These are the chip select input signals for the serial EEPROM devices. Typically, these signals are hardwired to either V IH or V IL. If left unconnected, they are internally recognized as V IL. FT24C04A has A0 pin as no-connect. FT24C08A has both A0 and A1 pins as no-connect. For FT24C16A, all device address pins (A0-A2) are no-connect.(C) SERIAL DATA LINE (SDA)SDA data line is a bi-directional signal for the serial devices. It is an open drain output signal and can be wired-OR with other open-drain output devices.(D) WRITE PROTECT (WP)The FT24C04A/08A/16A devices have a WP pin to protect the whole EEPROM array from programming.Programming operations are allowed if WP pin is left un-connected or input to V IL. Conversely all programming functions are disabled if WP pin is connected to V IH or V CC. Read operations is not affected by the WP pin’s input level.Table A© 2012 Fremont Micro Devices Inc. DS24C04_08_16-A0--page3Device Chip Select/DeviceAddress Pins UsedNo-Connect PinsMax number of similardevices on the samebusFT24C04A A2,A1 A0 4 FT24C08A A2, A1,A0 2 FT24C16A (None) A2, A1, A0 1MEMORY ORGANIZATIONThe FT24C04A/08A/16A devices have 32/64/128 pages respectively. Since each page has 16 bytes, random word addressing to FT24C04A/08A/16A will require 9/10/11 bits data word addresses respectively.DEVICE OPERATION(A) SERIAL CLOCK AND DATA TRANSITIONSThe SDA pin is typically pulled to high by an external resistor. Data is allowed to change only when Serial clock SCL is at V IL. Any SDA signal transition may interpret as either a START or STOP condition as described below.(B) START CONDITIONWith SCL V IH, a SDA transition from high to low is interpreted as a START condition. All valid commands must begin with a START condition.© 2012 Fremont Micro Devices Inc. DS24C04_08_16-A0--page4© 2012 Fremont Micro Devices Inc. DS24C04_08_16-A0--page5(C) STOP CONDITIONWith SCL V IH , a SDA transition from low to high is interpreted as a STOP condition. All valid read or write commands end with a STOP condition. The device goes into the STANDBY mode if it is after a read command. A STOP condition after page or byte write command will trigger the chip into the STANDBY mode after the self-timed internal programming finish. (D) ACKNOWLEDGEThe 2-wire protocol transmits address and data to and from the EEPROM in 8 bit words. The EEPROM acknowledges the data or address by outputting a "0" after receiving each word. The ACKNOWLEDGE signal occurs on the 9th serial clock after each word. (E) STANDBY MODEThe EEPROM goes into low power STANDBY mode after a fresh power up, after receiving a STOP bit in read mode, or after completing a self-time internal programming operation.Figure 1: Timing diagram for START and STOP conditionsFigure 2: Timing diagram for output ACKNOWLEDGESCLSDASTART ConditionSTOP ConditionData Data Valid TransitionSCLData inData out START ConditionACKDEVICE ADDRESSINGThe 2-wire serial bus protocol mandates an 8 bits device address word after a START bit condition to invoke valid read or write command. The first four most significant bits of the device address must be 1010, which is common to all serial EEPROM devices. The next three bits are device address bits. These three device address bits (5th, 6th and 7th) are to match with the external chip select/address pin states. If a match is made, the EEPROM device outputs an ACKNOWLEDGE signal after the 8th read/write bit, otherwise the chip will go into STANDBY mode. However, matching may not be needed for some or all device address bits (5th, 6th and 7th) as noted below. The last or 8th bit is a read/write command bit. If the 8th bit is at V IH then the chip goes into read mode. If a “0” is detected, the device enters programming mode.FT24C04A uses A2 (5th) and A1 (6th) device address bits. Only four FT24C04A devices can be wired-OR on the same 2-wire bus. Their corresponding chip select address pins A2 and A1 must be hard wired and coded from 00 (b) to 11 (b). Chip select address pin A0 is not used.FT24C08A uses only A2 (5th) device address bit. Only two FT24C08A devices can be wired-OR on the same 2-wire bus. Their corresponding chip select address pin A2 must be hard-wired and coded from 0 (b) to 1 (b). Chip select address pins A1 and A0 are not used.FT24C16A does not use any device address bit. Only one FT24C16A device can be used on the on 2-wire bus. Chip Select address pins A2, A1, and A0 are not used.WRITE OPERATIONS(A) BYTE WRITEA byte write operation starts when a micro-controller sends a START bit condition, follows by a properEEPROM device address and then a write command. If the device address bits match the chip select address, the EEPROM device will acknowledge at the 9th clock cycle. The micro-controller will then send the rest of the lower 8 bits word address. At the 18th cycle, the EEPROM will acknowledge the 8-bit address word. The micro-controller will then transmit the 8 bit data. Following an ACKNOWLDEGE signal from the EEPROM at the 27th clock cycle, the micro-controller will issue a STOP bit. After receiving the STOP bit, the EEPROM will go into a self-timed programming mode during which all external inputs will be disabled. After a programming time of T WC, the byte programming will finish and the EEPROM device will return to the STANDBY mode.(B) PAGE WRITEA page write is similar to a byte write with the exception that one to sixteen bytes can be programmedalong the same page or memory row. All FT24C04A/08A/16A are organized to have 16 bytes per memory row or page.With the same write command as the byte write, the micro-controller does not issue a STOP bit after sending the 1st byte data and receiving the ACKNOWLEDGE signal from the EEPROM on the 27th clock cycle. Instead it sends out a second 8-bit data word, with the EEPROM acknowledging at the 36th cycle.This data sending and EEPROM acknowledging cycle repeats until the micro-controller sends a STOP bit after the n 9th clock cycle. After which the EEPROM device will go into a self-timed partial or full page programming mode. After the page programming completes after a time of T WC, the devices will return to the STANDBY mode.© 2012 Fremont Micro Devices Inc. DS24C04_08_16-A0--page6The least significant 4 bits of the word address (column address) increments internally by one afterreceiving each data word. The rest of the word address bits (row address) do not change internally, butpointing to a specific memory row or page to be programmed. The first page write data word can be ofany column address. Up to 16 data words can be loaded into a page. If more then 16 data words areloaded, the 17th data word will be loaded to the 1st data word column address. The 18th data word willbe loaded to the 2nd data word column address and so on. In other word, data word address (columnaddress) will “roll” over the previously loaded data.(C) ACKNOWLEDGE POLLINGACKNOWLEDGE polling may be used to poll the programming status during a self-timed internalprogramming. By issuing a valid read or write address command, the EEPROM will not acknowledge atthe 9th clock cycle if the device is still in the self-timed programming mode. However, if the programmingcompletes and the chip has returned to the STANDBY mode, the device will return a validACKNOWLEDGE signal at the 9th clock cycle.READ OPERATIONSThe read command is similar to the write command except the 8th read/write bit in address word is set to “1”.The three read operation modes are described as follows:(A) CURRENT ADDRESS READThe EEPROM internal address word counter maintains the last read or write address plus one if thepower supply to the device has not been cut off. To initiate a current address read operation, the micro-controller issues a START bit and a valid device address word with the read/write bit (8th) set to “1”. TheEEPROM will response with an ACKNOWLEDGE signal on the 9th serial clock cycle. An 8-bit data wordwill then be serially clocked out. The internal address word counter will then automatically increase byone. For current address read the micro-controller will not issue an ACKNOWLEDGE signal on the 18thclock cycle. The micro-controller issues a valid STOP bit after the 18th clock cycle to terminate the readoperation. The device then returns to STANDBY mode.(B) SEQUENTIAL READThe sequential read is very similar to current address read. The micro-controller issues a START bitand a valid device address word with read/write bit (8th) set to “1”. The EEPROM will response with anACKNOWLEDGE signal on the 9th serial clock cycle. An 8-bit data word will then be serially clocked out.Meanwhile the internally address word counter will then automatically increase by one. Unlike currentaddress read, the micro-controller sends an ACKNOWLEDGE signal on the 18th clock cycle signalingthe EEPROM device that it wants another byte of data. Upon receiving the ACKNOWLEDGE signal, theEEPROM will serially clocked out an 8-bit data word based on the incremented internal address counter.If the micro-controller needs another data, it sends out an ACKNOWLEDGE signal on the 27th clockcycle. Another 8-bit data word will then be serially clocked out. This sequential read continues as longas the micro-controller sends an ACKNOWLEDGE signal after receiving a new data word. When theinternal address counter reaches its maximum valid address, it rolls over to the beginning of the memoryarray address. Similar to current address read, the micro-controller can terminate the sequential read bynot acknowledging the last data word received, but sending a STOP bit afterwards instead.(C) RANDOM READRandom read is a two-steps process. The first step is to initialize the internal address counter with atarget read address using a “dummy write” instruction. The second step is a current address read.To initialize the internal address counter with a target read address, the micro-controller issues a STARTbit first, follows by a valid device address with the read/write bit (8th) set to “0”. The EEPROM will thenacknowledge. The micro-controller will then send the address word. Again the EEPROM willacknowledge. Instead of sending a valid written data to the EEPROM, the micro-controller performs a current address read© 2012 Fremont Micro Devices Inc. DS24C04_08_16-A0--page7instruction to read the data. Note that once a START bit is issued, the EEPROM will reset the internal programming process and continue to execute the new instruction - which is to read the current address.© 2012 Fremont Micro Devices Inc. DS24C04_08_16-A0--page8© 2012 Fremont Micro Devices Inc. DS24C04_08_16-A0--page9Figure 8: SCL and SDA Bus TimingAC CHARACTERISTICS1.8 V2.5-5.0 V Symbol ParameterMin Max Min Max Unit f SCL Clock frequency, SCL 400 1000 kHz t LOW Clock pulse width low 1.20.7µst HIGH Clock pulse width high0.4 0.3 µst I Noise suppression time (1) 180 120 ns t AA Clock low to data out valid 0.3 0.9 0.2 0.7 µs t BUF Time the bus must be free before a new transmission can start (1)1.3 0.5 µs t HD.STA START hold time 0.6 0.25 µs t SU.STA START set-up time 0.6 0.25 µs t HD.DAT Data in hold time 0 0 µs t SU.DAT Data in set-up time 100100nst R Input rise time (1)0.3 0.3 µs t F Input fall time (1) 300 100 nst SU.STO STOP set-up time 0.6 0.25 µs t DH Date out hold time 50 50 ns WRWrite cycle time55msEndurance(1)25o C, Page Mode, 3.3V1,000,000Write CyclesNotes: 1. This Parameter is expected by characterization but are not fully screened by test.2. AC Measurement conditions: R L (Connects to Vcc): 1.3K ΩInput Pulse Voltages: 0.3Vcc to 0.7VccInput and output timing reference Voltages: 0.5VccDC CHARACTERISTICSSymbol Parameter TestConditions MinTypicalMaxUnitsV CC124C A supplyV CC1.8 5.5 VI CC Supply read current V CC@ 5.0V SCL = 400 kHz 0.5 1.0 mA I CC Supply write current V CC@ 5.0V SCL = 400 kHz 2.0 3.0 mA I SB1 Supplycurrent V CC@ 1.8V, V IN = V CC or V SS 1.0 µA I SB2 Supplycurrent V CC@ 2.5V, V IN = V CC or V SS 1.0 µA I SB3 Supplycurrent V CC@ 5.0V, V IN = V CC or V SS0.06 1.0 µAI IL Input leakagecurrentV IN = V CC or V SS 3.0 µAI LO Output leakagecurrentV IN = V CC or V SS 3.0 µAV IL Input low level -0.6 V CC x0.3 V V IH Input high level V CC x0.7V CC+0.5 V V OL1 Outputlowlevel V CC@ 1.8V, I OL = 0.15 mA 0.2 V V OL2 Outputlowlevel V CC@ 3.0V, I OL = 2.1 mA 0.4 V© 2012 Fremont Micro Devices Inc. DS24C04_08_16-A0--page10© 2012 Fremont Micro Devices Inc. DS24C04_08_16-A0--page11ORDERING INFORMATION:Density PackageTemperatureRangeVcc HSF Packaging Ordering CodeRoHSTube FT24C04A-UDR-B DIP8 -40℃-85℃ 1.8V-5.5VGreen Tube FT24C04A-UDG-B Tube FT24C04A-USR-B RoHSTape and Reel FT24C04A-USR-TTube FT24C04A-USG-B SOP8 -40℃-85℃ 1.8V-5.5VGreen Tape and Reel FT24C04A-USG-TTube FT24C04A-UMR-B RoHSTape and Reel FT24C04A-UMR-TTube FT24C04A-UMG-B MSOP8 -40℃-85℃ 1.8V-5.5VGreenTape and Reel FT24C04A-UMG-TTube FT24C04A-UTR-B RoHSTape and Reel FT24C04A-UTR-TTube FT24C04A-UTG-B TSSOP8 -40℃-85℃ 1.8V-5.5VGreenTape and Reel FT24C04A-UTG-T RoHS Tape and Reel FT24C04A-ULR-T SOT23-5 -40℃-85℃ 1.8V-5.5V Green Tape and Reel FT24C04A-ULG-T RoHS Tape and Reel FT24C04A-UPR-T TSOT23-5 -40℃-85℃ 1.8V-5.5V Green Tape and Reel FT24C04A-UPG-T RoHS Tape and Reel FT24C04A-UNR-T 4kbitsDFN8 -40℃-85℃ 1.8V-5.5V Green Tape and Reel FT24C04A-UNG-TRoHS Tube FT24C08A-UDR-B DIP8 -40℃-85℃ 1.8V-5.5VGreen Tube FT24C08A-UDG-B Tube FT24C08A-USR-B RoHSTape and Reel FT24C08A-USR-TTube FT24C08A-USG-B 8kbitsSOP8 -40℃-85℃ 1.8V-5.5VGreenTape and Reel FT24C08A-USG-TD: DIP8 S: SOP8 M: MSOP8 T: TSSOP8 L: SOT23-5 P: TSOT23-5 N: DFN8Packaging B: TubeT: Tape and Reel HSF R: RoHS G: GreenU:-40© 2012 Fremont Micro Devices Inc. DS24C04_08_16-A0--page12Density Package TemperatureRangeVcc HSF Packaging Ordering CodeTube FT24C08A-UMR-BRoHSTape and Reel FT24C08A-UMR-TTube FT24C08A-UMG-B MSOP8 -40℃-85℃ 1.8V-5.5VGreen Tape and Reel FT24C08A-UMG-TTube FT24C08A-UTR-B RoHSTape and Reel FT24C08A-UTR-TTube FT24C08A-UTG-B TSSOP8 -40℃-85℃ 1.8V-5.5VGreen Tape and Reel FT24C08A-UTG-T RoHSTape and Reel FT24C08A-ULR-T SOT23-5 -40℃-85℃ 1.8V-5.5V Green Tape and Reel FT24C08A-ULG-T RoHS Tape and Reel FT24C08A-UPR-T TSOT23-5 -40℃-85℃ 1.8V-5.5V Green Tape and Reel FT24C08A-UPG-T RoHS Tape and Reel FT24C08A-UNR-T 8kbitsDFN8 -40℃-85℃ 1.8V-5.5V Green Tape and Reel FT24C08A-UNG-TRoHS Tube FT24C16A-UDR-B DIP8 -40℃-85℃ 1.8V-5.5VGreen Tube FT24C16A-UDG-B Tube FT24C16A-USR-B RoHSTape and Reel FT24C16A-USR-TTube FT24C16A-USG-B SOP8 -40℃-85℃ 1.8V-5.5VGreen Tape and Reel FT24C16A-USG-TTube FT24C16A-UMR-B RoHSTape and Reel FT24C16A-UMR-TTube FT24C16A-UMG-B MSOP8 -40℃-85℃ 1.8V-5.5VGreenTape and Reel FT24C16A-UMG-TTube FT24C16A-UTR-B RoHSTape and Reel FT24C16A-UTR-TTube FT24C16A-UTG-B TSSOP8 -40℃-85℃ 1.8V-5.5VGreenTape and Reel FT24C16A-UTG-T RoHS Tape and Reel FT24C16A-ULR-T SOT23-5 -40℃-85℃ 1.8V-5.5V Green Tape and Reel FT24C16A-ULG-T RoHS Tape and Reel FT24C16A-UPR-T TSOT23-5 -40℃-85℃ 1.8V-5.5V Green Tape and Reel FT24C16A-UPG-T RoHS Tape and Reel FT24C16A-UNR-T 16kbitsDFN8 -40℃-85℃ 1.8V-5.5VGreenTape and Reel FT24C16A-UNG-TDIP8 PACKAGE OUTLINEDIMENSIONSDimensions In Millimeters Dimensions In InchesSymbolMin Max Min MaxA 3.710 4.310 0.146 0.170A1 0.510 0.020A2 3.200 3.600 0.126 0.142B 0.380 0.570 0.015 0.0221.524(BSC) 0.060(BSC)B1C 0.204 0.360 0.008 0.014D 9.000 9.400 0.354 0.370E 6.200 6.600 0.244 0.260E1 7.320 7.920 0.288 0.312(BSC) 0.100(BSC)e 2.540L 3.000 3.600 0.118 0.142E2 8.400 9.000 0.331 0.354© 2012 Fremont Micro Devices Inc. DS24C04_08_16-A0--page13SOP8 PACKAGE OUTLINE DIMENSIONSDimensions In Millimeters Dimensions In InchesSymbolMin Max Min MaxA 1.350 1.750 0.053 0.069A1 0.100 0.250 0.004 0.010A2 1.350 1.550 0.053 0.061b 0.330 0.510 0.013 0.020c 0.170 0.250 0.006 0.010D 4.700 5.100 0.185 0.200E 3.800 4.000 0.150 0.157E1 5.800 6.200 0.228 0.244(BSC)(BSC) 0.050e 1.270L 0.400 1.270 0.016 0.050θ0° 8° 0° 8°© 2012 Fremont Micro Devices Inc. DS24C04_08_16-A0--page14MSOP8 PACKAGE OUTLINE DIMENSIONSDimensions In Millimeters Dimensions In InchesSymbolMin Max Min MaxA 0.820 1.100 0.320 0.043A1 0.020 0.150 0.001 0.006A2 0.750 0.950 0.030 0.037b 0.250 0.380 0.010 0.015c 0.090 0.230 0.004 0.009D 2.900 3.100 0.114 0.122e 0.65 (BSC) 0.026 (BSC)E 2.900 3.100 0.114 0.122E1 4.750 5.050 0.187 0.199L 0.400 0.800 0.016 0.031θ0° 6° 0° 6°© 2012 Fremont Micro Devices Inc. DS24C04_08_16-A0--page15TSSOP8 PACKAGE OUTLINEDIMENSIONSDimensions In Millimeters Dimensions In InchesSymbolMin Max Min MaxD 2.900 3.100 0.114 0.122E 4.300 4.500 0.169 0.177b 0.190 0.300 0.007 0.012c 0.090 0.200 0.004 0.008E1 6.250 6.550 0.246 0.258A 1.100 0.043A2 0.800 1.000 0.031 0.039A1 0.020 0.150 0.001 0.006e 0.65 (BSC) 0.026 (BSC)L 0.500 0.700 0.020 0.028H 0.25 (TYP) 0.01 (TYP)θ 1° 7° 1° 7°© 2012 Fremont Micro Devices Inc. DS24C04_08_16-A0--page16SOT-23-5 PACKAGE OUTLINE DIMENSIONSDimensions In Millimeters Dimensions In InchesSymbolMin Max Min MaxA 1.050 1.250 0.041 0.049A1 0.000 0.100 0.000 0.004A2 1.050 1.150 0.041 0.045b 0.300 0.500 0.012 0.020c 0.100 0.200 0.004 0.008D 2.820 3.020 0.111 0.119E 1.500 1.700 0.059 0.067E1 2.650 2.950 0.104 0.116e 0.95 (BSC) 0.037 (BSC)e1 1.800 2.000 0.071 0.079L 0.300 0.600 0.012 0.024θ 0° 8° 0° 6°© 2012 Fremont Micro Devices Inc. DS24C04_08_16-A0--page17TSOT-23-5 PACKAGE OUTLINE DIMENSIONSDimensions In Millimeters Dimensions In InchesSymbolMin Max Min MaxA 0.700 0.900 0.028 0.035A1 0.000 0.100 0.000 0.004A2 0.700 0.800 0.028 0.031b 0.350 0.500 0.014 0.020c 0.080 0.200 0.003 0.008D 2.820 3.020 0.111 0.119E 1.600 1.700 0.063 0.067E1 2.650 2.950 0.104 0.116e 0.95 (BSC) 0.037 (BSC)e1 1.90 (BSC) 0.075 (BSC)L 0.300 0.600 0.012 0.024θ 0° 8° 0° 8°© 2012 Fremont Micro Devices Inc. DS24C04_08_16-A0--page18DFN8 PACKAGE OUTLINE DIMENSIONSDimensions In MillimetersSymbolMin Nom Max0.75 0.80A 0.700.02 0.05A1 -0.25 0.03b 0.180.20 0.25c 0.182.00 2.10D 1.90D2 1.50REFe 0.50BSCNd 1.50BSC3.10E 2.903.00E2 1.60REF0.40 0.50L 0.300.25 0.30h 0.20© 2012 Fremont Micro Devices Inc. DS24C04_08_16-A0--page19Fremont Micro Devices (SZ) Limited#5-8, 10/F, Changhong Building, Ke-Ji Nan 12 Road, Nanshan District, ShenzhenTel: (86 755) 86117811Fax: (86 755) 86117810Fremont Micro Devices (Hong Kong) Limited#16, 16/F, Blk B, Veristrong Industrial Centre, 34-36 Au Pui Wan Street, Fotan, Shatin, Hong KongTel: (852) 27811186Fax: (852) 27811144Fremont Micro Devices (USA), Inc.42982 Osgood Road Fremont, CA 94539Tel: (1-510) 668-1321Fax: (1-510) 226-9918Web Site: /* Information furnished is believed to be accurate and reliable. However, Fremont Micro Devices, Incorporated (BVI) assumes no responsibility for the consequences of use of such information or for any infringement of patents of other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent rights of Fremont Micro Devices, Incorporated (BVI). Specifications mentioned in this publication are subject to change without notice. This publication supersedes and replaces all information previously supplied. Fremont Micro Devices, Incorporated (BVI) products are not authorized for use as critical components in life support devices or systems without express written approval of Fremont Micro Devices, Incorporated (BVI). The FMD logo is a registered trademark of Fremont Micro Devices, Incorporated (BVI). All other names are the property of their respective owners.© 2012 Fremont Micro Devices Inc. DS24C04_08_16-A0--page20。

FM24C16B-GTR;FM24C16B-G;中文规格书,Datasheet资料

Ordering Information

FM24C16B-G FM24C16B-GTR “Green”/RoHS 8-pin SOIC “Green”/RoHS 8-pin SOIC, Tape & Reel

This product conforms to specifications per the terms of the Ramtron standard warranty. The product has completed Ramtron’s internal qualification testing and has reached production status. Rev. 3.0 Jan. 2012

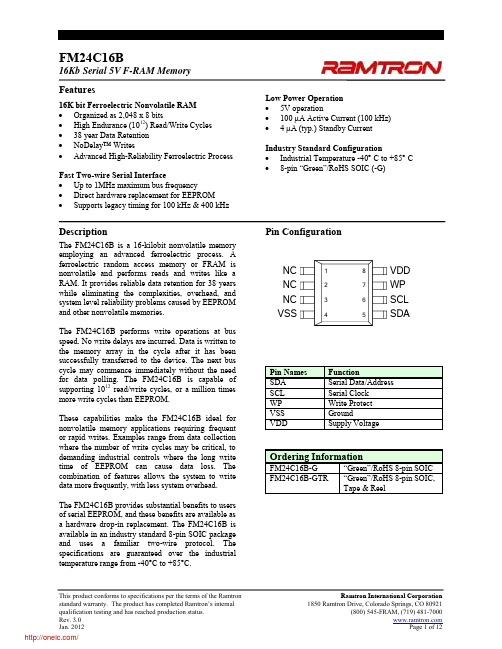

FM24C16B - 16Kb 5V I2C F-RAM

Counter

Address Latch

256 x 64 FRAM Array

8

SDA

`

Serial to Parallel Converter

Data Latch

SCL WP Control Logic

Figure 1. Block Diagram Pin Description Pin Name SDA Type I/O Pin Description Serial Data Address: This is a bi-directional data pin for the two-wire interface. It employs an open-drain output and is intended to be wire-OR’d with other devices on the two-wire bus. The input buffer incorporates a Schmitt trigger for noise immunity and the output driver includes slope control for falling edges. A pull-up resistor is required. Serial Clock: The serial clock input for the two-wire interface. Data is clocked-out on the falling edge and clocked-in on the rising edge. Write Protect: When WP is igh, the entire array is write-protected. When WP is low, all addresses may be written. This pin is internally pulled down. Supply Voltage (5V) Ground No connect

I2CFLASH--24C16芯片手册