Listeningassignment:Deadly superbug infecting hospitals across USA

如何调试 Go 语言代码中的并发问题

如何调试 Go 语言代码中的并发问题调试并发问题是Go语言开发过程中常见的任务,尤其在多线程或多协程的场景中。

并发问题包括了死锁(deadlock)、竞态条件(race condition)和资源争用(resource contention)等。

本文将介绍一些调试并发问题的常用方法和技巧,帮助开发者快速定位和修复问题。

一、日志和调试工具1.使用日志:Go语言内置了log包,可以通过在关键部分使用log.Print()或log.Println()语句,打印自定义的日志信息。

在有并发问题的地方,打印出相关的状态信息,有助于分析问题的根源。

2.使用调试器:Go语言的调试器可以很方便地定位并发问题。

可以通过在关键的代码段设置断点,然后运行程序,当断点触发时,可以查看变量的值和程序的状态,帮助定位问题的源头。

Goland和Delve是常用的Go语言调试工具。

二、锁相关问题的调试方法1.死锁问题-使用工具: Go语言提供了竞态检测工具race,可以通过命令go run -race main.go来启动。

race工具会在运行时检测是否存在竞态条件,帮助开发者快速定位问题。

-观察调用栈:当发生死锁时,使用工具或者使用gdb调试器,在进程中断时查看调用栈,查找是否有锁相互等待的情况。

2.竞态条件问题-使用工具:同样使用go run -race main.go命令来启动Go语言提供的竞态检测工具race。

该工具可以帮助找到数据访问冲突的地方。

-编写基准测试:为了重现竞态条件,可以编写基准测试代码,多运行几次,查看结果是否一致。

如果结果不一致,就可能是竞态条件引起的问题。

三、资源争用问题的调试方法1.分析CPU和内存使用情况:Go语言提供了pprof包,可以用来分析CPU和内存的使用情况。

可以在代码中插入一些收集性能数据的代码,并使用pprof分析工具进行可视化分析,从而定位到资源争用的问题。

2.监控工具:使用第三方的监控工具来监视程序的各项指标。

tms320vc5416数据手册

TMS320VC5416Fixed-Point Digital Signal Processor Data ManualPRODUCTION DATA information is current as of publication date.Products conform to specifications per the terms of the TexasInstruments standard warranty.Production processing does notnecessarily include testing of all parameters.Literature Number:SPRS095PMarch1999–Revised October2008Revision HistoryTMS320VC5416Fixed-Point Digital Signal ProcessorSPRS095P–MARCH 1999–REVISED OCTOBER 2008NOTE:Page numbers for previous revisions may differ from page numbers in the current version.This data sheet revision history highlights the technical changes made to the SPRS095O device-specific data sheet to make it an SPRS095P revision.Scope:This document has been reviewed for technical accuracy;the technical content is up-to-date as of the specified release date with the following corrections.2Revision History Submit Documentation FeedbackContentsTMS320VC5416Fixed-Point Digital Signal ProcessorSPRS095P–MARCH 1999–REVISED OCTOBER 2008Revision History ...........................................................................................................................1TMS320VC5416Features.......................................................................................................2Introduction.......................................................................................................................2.1Description ..................................................................................................................2.2PinAssignments............................................................................................................2.2.1TerminalAssignments forthe GGUPackage...............................................................2.2.2Pin AssignmentsforthePGEPackage......................................................................2.2.3Signal Descriptions ..............................................................................................3Functional Overview ...........................................................................................................3.1Memory ......................................................................................................................3.1.1Data Memory .....................................................................................................3.1.2Program Memory ................................................................................................3.1.3Extended Program Memory ...................................................................................3.2On-Chip ROM With Bootloader ...........................................................................................3.3On-Chip RAM ...............................................................................................................3.4On-Chip Memory Security .................................................................................................3.5Memory Map ................................................................................................................3.5.1Relocatable Interrupt Vector Table ............................................................................3.6On-Chip Peripherals .......................................................................................................3.6.1Software-Programmable Wait-State Generator .............................................................3.6.2Programmable Bank-Switching ................................................................................3.6.3Bus Holders ......................................................................................................3.7Parallel I/O Ports ...........................................................................................................3.7.1Enhanced 8-/16-Bit Host-Port Interface (HPI8/16)..........................................................3.7.2HPI Nonmultiplexed Mode ......................................................................................3.8Multichannel Buffered Serial Ports (McBSPs)..........................................................................3.9Hardware Timer ............................................................................................................3.10Clock Generator ............................................................................................................3.11Enhanced External Parallel Interface (XIO2)...........................................................................3.12DMA Controller .............................................................................................................3.12.1Features ..........................................................................................................3.12.2DMA External Access ...........................................................................................3.12.3DMA Memory Maps .............................................................................................3.12.4DMA Priority Level ...............................................................................................3.12.5DMA Source/Destination Address Modification .............................................................3.12.6DMA in Autoinitialization Mode ................................................................................3.12.7DMA Transfer Counting .........................................................................................3.12.8DMA Transfer in Doubleword Mode ..........................................................................3.12.9DMA Channel Index Registers .................................................................................3.12.10DMA Interrupts ..................................................................................................3.12.11DMA Controller Synchronization Events .....................................................................3.13General-Purpose I/O Pins .................................................................................................3.13.1McBSP Pins as General-Purpose I/O .........................................................................3.13.2HPI Data Pins as General-Purpose I/O ......................................................................3.14Device ID Register .........................................................................................................3.15Memory-Mapped Registers ...............................................................................................3.16McBSP Control Registers and Subaddresses ..........................................................................3.17DMA Subbank Addressed Registers ....................................................................................3.18Interrupts ....................................................................................................................4Support .............................................................................................................................Contents3TMS320VC5416Fixed-Point Digital Signal ProcessorSPRS095P–MARCH1999–REVISED 4.1Documentation Support...................................................................................................4.2Device and Development-Support Tool Nomenclature................................................................5Electrical Specifications......................................................................................................5.1Absolute Maximum Ratings...............................................................................................5.2Recommended Operating Conditions...................................................................................5.3Electrical Characteristics.................................................................................................5.3.1Test Loading.....................................................................................................5.3.2Timing Parameter Symbology............................................................................................5.3.3Internal Oscillator With External Crystal.................................................................................5.4Clock Options...............................................................................................................5.4.1Divide-By-Two and Divide-By-Four Clock Options..........................................................5.4.2Multiply-By-N Clock Option(PLL Enabled)...................................................................5.5Memory and Parallel I/O Interface Timing..............................................................................5.5.1Memory Read....................................................................................................5.5.2Memory Write....................................................................................................5.5.3I/O Read..........................................................................................................5.5.4I/O Write..........................................................................................................5.5.5Ready Timing for Externally Generated Wait States..................................................................5.5.6and Timings...............................................................................................5.5.7Reset,BIO,Interrupt,and MP/MC Timings.............................................................................5.5.8Instruction Acquisition and Interrupt Acknowledge Timings..........................................5.5.9External Flag(XF)and TOUT Timings..................................................................................5.5.10Multichannel Buffered Serial Port(McBSP)Timing...................................................................5.5.10.1McBSP Transmit and Receive Timings....................................................................5.5.10.2McBSP General-Purpose I/O Timing.......................................................................5.5.10.3McBSP as SPI Master or Slave Timing....................................................................5.5.11Host-Port Interface Timing...............................................................................................5.5.11.1HPI8Mode.....................................................................................................5.5.11.2HPI16Mode....................................................................................................6Mechanical Data.................................................................................................................6.1Package Thermal Resistance Characteristics..........................................................................4Contents Submit Documentation FeedbackTMS320VC5416Fixed-Point Digital Signal Processor SPRS095P–MARCH1999–REVISED OCTOBER2008List of Figures2-1144-Ball GGU MicroStar BGA™(Bottom View).............................................................................2-2144-Pin PGE Low-Profile Quad Flatpack(Top View).......................................................................3-1TMS320VC5416Functional Block Diagram..................................................................................3-2Program and Data Memory Map................................................................................................3-3Extended Program Memory Map...............................................................................................3-4Process Mode Status Register..................................................................................................3-5Software Wait-State Register(SWWSR)[Memory-Mapped Register(MMR)Address0028h].........................3-6Software Wait-State Register(SWWSR)[Memory-Mapped Register(MMR)Address0028h].........................3-7Bank-Switching Control Register BSCR)[MMR Address0029h]...........................................................3-8Host-Port Interface—Nonmulltiplexed Mode.................................................................................3-9HPI Memory Map.................................................................................................................3-10Multichannel Control Register(MCR1).........................................................................................3-11Multichannel Control Register(MCR2).........................................................................................3-12Pin Control Register(PCR)......................................................................................................3-13Nonconsecutive Memory Read and I/O Read Bus Sequence.............................................................3-14Consecutive Memory Read Bus Sequence(n=3reads)..................................................................3-15Memory Write and I/O Write Bus Sequence.................................................................................3-16DMA Transfer Mode Control Register(DMMCRn)...........................................................................3-17On-Chip DMA Memory Map for Program Space(DLAXS=0and SLAXS=0).........................................3-18On-Chip DMA Memory Map for Data and IO Space(DLAXS=0and SLAXS=0)....................................3-19DMPREC Register................................................................................................................3-20General-Purpose I/O Control Register(GPIOCR)[MMR Address003Ch]................................................3-21General-Purpose I/O Status Register(GPIOSR)[MMR Address003Dh].................................................3-22Device ID Register(CSIDR)[MMR Address003Eh].........................................................................3-23IFR and IMR Registers...........................................................................................................5-1Tester Pin Electronics............................................................................................................5-2Internal Divide-By-Two Clock Option With External Crystal...............................................................5-3External Divide-By-Two Clock Timing.........................................................................................5-4Multiply-By-One Clock Timing..................................................................................................5-5Nonconsecutive Mode Memory Reads.......................................................................................5-6Consecutive Mode Memory Reads............................................................................................5-7Memory Write(MSTRB=0)....................................................................................................5-8Parallel I/O Port Read(IOSTRB=0).........................................................................................5-9Parallel I/O Port Write(IOSTRB=0)..........................................................................................5-10Memory Read With Externally Generated Wait States.....................................................................5-11Memory Write With Externally Generated Wait States.....................................................................5-12I/O Read With Externally Generated Wait States...........................................................................5-13I/O Write With Externally Generated Wait States...........................................................................5-14HOLD and HOLDA Timings(HM=1).........................................................................................List of Figures5TMS320VC5416Fixed-Point Digital Signal ProcessorSPRS095P–MARCH1999–REVISED 5-15Reset and BIO Timings.........................................................................................................5-16Interrupt Timing..................................................................................................................5-17MP/MC Timing...................................................................................................................5-18Instruction Acquisition(IAQ)and Interrupt Acknowledge(IACK)Timings................................................5-19External Flag(XF)Timing......................................................................................................5-20TOUT Timing.....................................................................................................................5-21McBSP Receive Timings.......................................................................................................5-22McBSP Transmit Timings.......................................................................................................5-23McBSP General-Purpose I/O Timings........................................................................................5-24McBSP Timing as SPI Master or Slave:CLKSTP=10b,CLKXP=0....................................................5-25McBSP Timing as SPI Master or Slave:CLKSTP=11b,CLKXP=0....................................................5-26McBSP Timing as SPI Master or Slave:CLKSTP=10b,CLKXP=1....................................................5-27McBSP Timing as SPI Master or Slave:CLKSTP=11b,CLKXP=1....................................................5-28Using HDS to Control Accesses(HCS Always Low)........................................................................5-29Using HCS to Control Accesses...............................................................................................5-30HINT Timing......................................................................................................................5-31GPIOx Timings...................................................................................................................5-32Nonmultiplexed Read Timings.................................................................................................5-33Nonmultiplexed Write Timings.................................................................................................5-34HRDY Relative to CLKOUT....................................................................................................6List of Figures Submit Documentation FeedbackTMS320VC5416Fixed-Point Digital Signal Processor SPRS095P–MARCH1999–REVISED OCTOBER2008List of Tables2-1Terminal Assignments for the TMS320VC5416GGU(144-Pin BGA Package).........................................2-2Signal Descriptions...............................................................................................................3-1Standard On-Chip ROM Layout...............................................................................................3-2Processor Mode Status(PMST)Register Bit Fields........................................................................3-3Software Wait-State Register(SWWSR)Bit Fields.........................................................................3-4Software Wait-State Control Register(SWCR)Bit Fields..................................................................3-5Bank-Switching Control Register(BSCR)Fields..............................................................................3-6Bus Holder Control Bits..........................................................................................................3-7Sample Rate Input Clock Selection...........................................................................................3-8Clock Mode Settings at Reset.................................................................................................3-9DMD Section of the DMMCRn Register......................................................................................3-10DMA Reload Register Selection...............................................................................................3-11DMA Interrupts...................................................................................................................3-12DMA Synchronization Events..................................................................................................3-13DMA Channel Interrupt Selection..............................................................................................3-14Device ID Register(CSIDR)Bits................................................................................................3-15CPU Memory-Mapped Registers................................................................................................3-16Peripheral Memory-Mapped Registers for Each DSP Subsystem........................................................3-17McBSP Control Registers and Subaddresses.................................................................................3-18DMA Subbank Addressed Registers...........................................................................................3-19Interrupt Locations and Priorities................................................................................................5-1Input Clock Frequency Characteristics.........................................................................................5-2Clock Mode Pin Settings for the Divide-By-2and By Divide-By-4Clock Options.......................................5-3Divide-By-2and Divide-By-4Clock Options Timing Requirements.......................................................5-4Divide-By-2and Divide-By-4Clock Options Switching Characteristics...................................................5-5Multiply-By-N Clock Option Timing Requirements..........................................................................5-6Multiply-By-N Clock Option Switching Characteristics......................................................................5-7Memory Read Timing Requirements..........................................................................................5-8Memory Read Switching Characteristics.....................................................................................5-9Memory Write Switching Characteristics.....................................................................................5-10I/O Read Timing Requirements................................................................................................5-11I/O Read Switching Characteristics...........................................................................................5-12I/O Write Switching Characteristics............................................................................................5-13Ready Timing Requirements for Externally Generated Wait States......................................................5-14Ready Switching Characteristics for Externally Generated Wait States..................................................5-15HOLD and HOLDA Timing Requirements....................................................................................5-16HOLD and HOLDA Switching Characteristics...............................................................................5-17Reset,BIO,Interrupt,and MP/MC Timing Requirements..................................................................5-18Instruction Acquisition(IAQ)and Interrupt Acknowledge(IACK)Switching Characteristics...........................List of Tables7TMS320VC5416Fixed-Point Digital Signal ProcessorSPRS095P–MARCH1999–REVISED 5-19External Flag(XF)and TOUT Switching Characteristics...................................................................5-20McBSP Transmit and Receive Timing Requirements.......................................................................5-21McBSP Transmit and Receive Switching Characteristics..................................................................5-22McBSP General-Purpose I/O Timing Requirements........................................................................5-23McBSP General-Purpose I/O Switching Characteristics...................................................................5-24McBSP as SPI Master or Slave Timing Requirements(CLKSTP=10b,CLKXP=0).................................5-25McBSP as SPI Master or Slave Switching Characteristics(CLKSTP=10b,CLKXP=0).............................5-26McBSP as SPI Master or Slave Timing Requirements(CLKSTP=11b,CLKXP=0).................................5-27McBSP as SPI Master or Slave Switching Characteristics(CLKSTP=11b,CLKXP=0).............................5-28McBSP as SPI Master or Slave Timing Requirements(CLKSTP=10b,CLKXP=1).................................5-29McBSP as SPI Master or Slave Switching Characteristics(CLKSTP=10b,CLKXP=1).............................5-30McBSP as SPI Master or Slave Timing Requirements(CLKSTP=11b,CLKXP=1).................................5-31McBSP as SPI Master or Slave Switching Characteristics(CLKSTP=11b,CLKXP=1).............................5-32HPI8Mode Timing Requirements.............................................................................................5-33HPI8Mode Switching Characteristics..........................................................................................5-34HPI16Mode Timing Requirements............................................................................................5-35HPI16Mode Switching Characteristics.......................................................................................6-1Thermal Resistance Characteristics............................................................................................8Submit Documentation Feedback List of Tables1TMS320VC5416FeaturesTMS320VC5416 Fixed-Point Digital Signal Processor SPRS095P–MARCH1999–REVISED OCTOBER2008Reads•Advanced Multibus Architecture With ThreeSeparate16-Bit Data Memory Buses and One•Arithmetic Instructions With Parallel Store and Program Memory Bus Parallel Load•40-Bit Arithmetic Logic Unit(ALU)Including a•Conditional Store Instructions40-Bit Barrel Shifter and Two Independent•Fast Return From Interrupt 40-Bit Accumulators•On-Chip Peripherals•17-×17-Bit Parallel Multiplier Coupled to a–Software-Programmable Wait-State 40-Bit Dedicated Adder for Non-Pipelined Generator and ProgrammableSingle-Cycle Multiply/Accumulate(MAC)Bank-SwitchingOperation–On-Chip Programmable Phase-Locked •Compare,Select,and Store Unit(CSSU)for the Loop(PLL)Clock Generator With External Add/Compare Selection of the Viterbi Operator Clock Source–One16-Bit Timer•Exponent Encoder to Compute an Exponent–Six-Channel Direct Memory Access(DMA) Value of a40-Bit Accumulator Value in aControllerSingle Cycle–Three Multichannel Buffered Serial Ports •Two Address Generators With Eight Auxiliary(McBSPs)Registers and Two Auxiliary Register–8/16-Bit Enhanced Parallel Host-Port Arithmetic Units(ARAUs)Interface(HPI8/16)•Data Bus With a Bus Holder Feature•Power Consumption Control With IDLE1,•Extended Addressing Mode for8M×16-Bit IDLE2,and IDLE3Instructions With Maximum Addressable External ProgramPower-Down ModesSpace•CLKOUT Off Control to Disable CLKOUT •128K×16-Bit On-Chip RAM Composed of:•On-Chip Scan-Based Emulation Logic,IEEE –Eight Blocks of8K×16-Bit On-ChipStd1149.1(JTAG)Boundary Scan Logic(1) Dual-Access Program/Data RAM•144-Pin Ball Grid Array(BGA)(GGU Suffix)–Eight Blocks of8K×16-Bit On-ChipSingle-Access Program RAM•144-Pin Low-Profile Quad Flatpack(LQFP)(PGE Suffix)•16K×16-Bit On-Chip ROM Configured forProgram Memory• 6.25-ns Single-Cycle Fixed-Point InstructionExecution Time(160MIPS)•Enhanced External Parallel Interface(XIO2)•8.33-ns Single-Cycle Fixed-Point Instruction •Single-Instruction-Repeat and Block-RepeatExecution Time(120MIPS) Operations for Program Code• 3.3-V I/O Supply Voltage(160and120MIPS)•Block-Memory-Move Instructions for BetterProgram and Data Management• 1.6-V Core Supply Voltage(160MIPS)•Instructions With a32-Bit Long Word Operand• 1.5-V Core Supply Voltage(120MIPS)(1)IEEE Standard1149.1-1990Standard-Test-Access Port and •Instructions With Two-or Three-OperandBoundary Scan ArchitectureTMS320C54x,TMS320are trademarks of Texas Instruments.All other trademarks are the property of their respective owners.PRODUCTION DATA information is current as of publication date.Copyright©1999–2008,Texas Instruments Incorporated Products conform to specifications per the terms of the TexasInstruments standard warranty.Production processing does notnecessarily include testing of all parameters.。

Synopsys OptoDesigner 2020.09安装指南说明书

3. Troubleshooting scanning issues........................................................25

Accidental full scan proliferation by folder paths which include build or commit ID............................ 25 Solution......................................................................................................................................25

Contents

Contents

Preface....................................................................................................5

1. Scanning best practices......................................................................... 8

算法面试英文词汇

算法面试英文词汇以下是一些算法面试中可能会遇到的英文词汇:1. 算法分析:Algorithm Analysis2. 时间复杂度:Time Complexity3. 空间复杂度:Space Complexity4. 递归:Recursion5. 动态规划:Dynamic Programming6. 分治法:Divide and Conquer7. 贪心算法:Greedy Algorithm8. 回溯法:Backtracking9. 插入排序:Insertion Sort10. 快速排序:Quick Sort11. 归并排序:Merge Sort12. 堆排序:Heap Sort13. 二分查找:Binary Search14. 深度优先搜索:Depth-First Search (DFS)15. 广度优先搜索:Breadth-First Search (BFS)16. 优先队列:Priority Queue17. 并查集:Disjoint Set18. 线段树:Segment Tree19. 平衡二叉树:Balanced Binary Tree20. 红黑树:Red-Black Tree21. AVL树:AVL Tree22. 图论:Graph Theory23. 最小生成树:Minimum Spanning Tree (MST)24. 最短路径:Shortest Path25. Dijkstra算法:Dijkstra's Algorithm26. Bellman-Ford算法:Bellman-Ford Algorithm27. Floyd-Warshall算法:Floyd-Warshall Algorithm28. 拓扑排序:Topological Sort29. 网络流:Flow in Networks30. 最少生成树:Minimum Cost Spanning Tree (MCTS)31. 二分图匹配:Bipartite Matching32. 并查集操作:Union, Find, Union-by-Rank, Path Compression33. 二叉堆操作:Insert, Delete, Decrease Key, Increase Key, Merge34. 数据结构操作:Insert, Delete, Search, Get Size, Is Empty, Clear35. 链表操作:Create, Delete, Insert Before, Insert After, Print, Find, Merge36. 数组操作:Sort, Reverse, Find Max/Min, Find Index of Max/Min, Rotate, Transpose37. 树操作:Create Root, Insert Node, Delete Node, Find Node, Find Parent of Node, Print Tree38. 图操作:Create Graph, Add Edge, Delete Edge, Find Nodes Connected by Edge, BFS/DFS from Source Node39. 图论问题常见术语:Vertex Cover, Independent Set, Connected Component, Shortest Path, Bipartite Checking, Max Flow/Min Cut 40. 其他常见术语:Big O notation, Amortized analysis, Randomized algorithm, NP-hard problem41. 其他常用算法术语:Divide and Conquer approach, Greedy approach, Dynamic Programming approach42. 动态规划的边界情况处理:Base case/Recursion case。

立即抢占的多级反馈队列调度算法

立即抢占的多级反馈队列调度算法

多级反馈队列调度算法是一种抢占式的调度算法,它将进程划分为多个队列,并为每个队列分配一个时间片大小。

不同队列的时间片大小逐级递减。

具体的多级反馈队列调度算法包括以下步骤:

1. 初始化:为每个队列设置一个时间片大小,通常情况下,较高级别的队列分配较短的时间片。

2. 将所有进程按照优先级或到达时间加入到第一级别队列中。

3. 从当前队列中选取一个进程执行。

4. 如果该进程运行完,结束并从队列中移除。

5. 如果该进程没有运行完,但时间片已经耗尽,则将该进程移到下一个级别的队列中。

6. 重复步骤3-5,直到所有进程执行完毕。

在多级反馈队列调度算法中,较高级别的队列优先级较高,所以当有高优先级的进程到达时,会抢占正在执行的低优先级进程,确保高优先级进程能够尽快得到执行。

同时,低优先级进程也能够得到执行的机会,不至于被一直阻塞。

通过多级反馈队列调度算法,能够实现较短的响应时间和较高的系统吞吐量,能够更好地满足不同进程的执行需求。

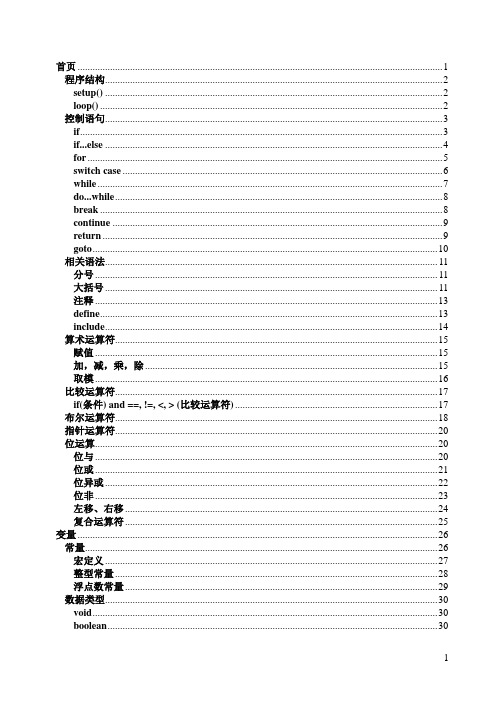

Arduino编程参考手册中文版(带目录适合打印)

! (逻辑非)

指针运算符

* 指针运算符

& 地址运算符

位运算

& (位与)

| (位或)

^ (位异或)

~ (位非)

<< (左移)

>> (右移)

复合运算符

++ (自加)

-- (自减)

+= (复合加)

-= (复合减)

*= (复合乘)

/= (复合除)

&= (复合与)

|= (复合或)

范围

HIGH | LOW

int checkSensor(){

if (analogRead(0) > 400) {

return 1;

else{

return 0;

}

}

return关键字对测试一段代码很方便,不需“注释掉”大段的可能是错误的代码。

void loop(){

//在此测试代码是个好想法

return;

// 这里是功能不正常的代码

for

for语句

描述

for语句用于重复执行被花括号包围的语句块。一个增量计数器通常被用来递增和终止循环。for语句对于任何需要重复的操作是非常有用的。常常用于与数组联合使用以收集数据/引脚。for循环的头部有三个部分:

for (初始化部分; 条件判断部分; 数据递增部分) {

//语句块

。。。

}

初始化部分被第一个执行,且只执行一次。每次通过这个循环,条件判断部分将被测试;如果为真,语句块和数据递增部分就会被执行,然后条件判断部分就会被再次测试,当条件测试为假时,结束循环。

示例:

for (x = 0; x < 255; x ++)

valgrind查内存泄漏的原理

valgrind查内存泄漏的原理Valgrind查内存漏漏的原理Valgrind是一款强大的开源工具,用于检测和调试C/C++程序中的内存错误,其中包括内存泄漏。

本文将从浅入深地解释Valgrind查找内存泄漏的原理。

什么是内存泄漏?内存泄漏是指在程序中动态分配的内存空间没有被正确释放的情况。

这种情况下,程序在运行时会持续地分配新的内存,而不释放旧的内存,最终导致内存耗尽,程序崩溃。

Valgrind的基本原理Valgrind通过内存虚拟化技术来检测和调试程序。

它创建了一个虚拟的执行环境,用于运行目标程序,并捕获程序对内存的读写操作。

Valgrind将目标程序对内存的读写操作转化为自己定义的指令序列,并在内存操作之前和之后插入检测代码。

这些检测代码会记录每次内存操作的详细信息,例如内存的分配和释放,读写操作的位置等。

通过分析这些检测代码,Valgrind能够检测出内存泄漏、非法内存访问、内存重复释放等问题。

Valgrind的工具集Valgrind包含了多个工具,其中最常用的工具是Memcheck。

Memcheck工具Memcheck是Valgrind工具集中最常用的工具,也是用于检测内存泄漏的工具。

它通过跟踪程序中动态分配的内存,并检测是否有未被释放的内存块,来发现内存泄漏的问题。

Memcheck使用了很多高级的技术来提高检测的准确性和效率,例如影子内存和引用计数。

影子内存影子内存是Valgrind中一个重要的概念。

Valgrind为每个字节的内存分配了一个额外的字节,用于存储元数据,比如内存是否已分配、是否已初始化等。

这个额外的字节就是影子内存。

当程序对内存进行读写时,Valgrind会检查对应的影子内存,以确定内存是否被正确使用。

如果发现不合法的操作,Valgrind会报告错误。

引用计数为了提高内存检测的效率,Valgrind使用了引用计数技术。

每个内存块都会记录它被引用的次数。

当程序对内存块进行分配或释放操作时,Valgrind会相应地更新引用计数。

waters质谱masslynx软件使用说明

Copyright Notice

Micromass UK Limited believes that the information in this publication is accurate. However the information is subject to change without notice and should not be construed as a contractual undertaking by Micromass UK Limited. Despite the care that has been given to the preparation of this publication, Micromass UK Limited accepts no responsibility for any loss or any other matter that may arise from any error or inaccuracy that may inadvertently have been included. Copyright 1993-2002 Micromass Ltd. All Rights Reserved. No part of this publication may be copied without the express written permission of Micromass UK Limited.

Page ii

MassLynx NT Users Guide

Contents

MassLynx NT User’s Guide............................................................................

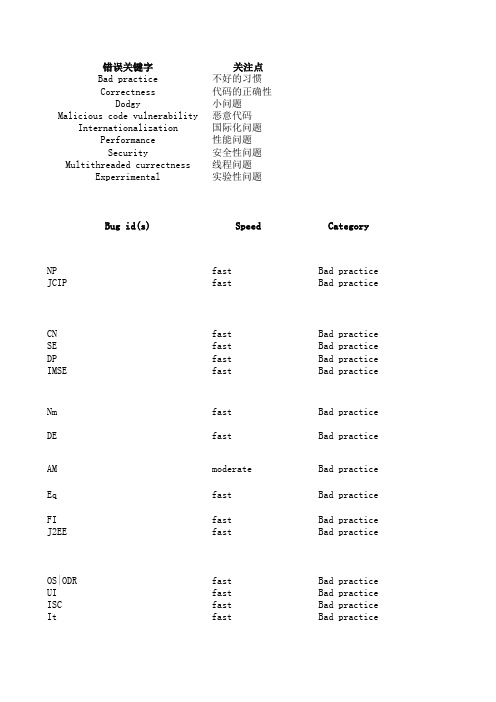

FindBugs错误类型对照表

IMSE_DONT_CATCH_=不良实践- 捕获可疑IllegalMonitorStateExceptionBX_BOXING_IMMEDIATELY_=性能- 基本类型包装之后立刻解包IJU_SETUP_NO_=使用错误- TestCase定义的setUp没有调用super.setUp()TQ_ALWAYS_VALUE_USED_WHERE_NEVER_=使用错误- 某个值使用了注解限制类型,但是这个限制永远不会发生TLW_TWO_LOCK_=多线程错误- 等待两个被持有的锁RV_01_TO_=使用错误- 0至1的随机数被当做整数0NP_PARAMETER_MUST_BE_NONNULL_BUT_MARKED_AS_=高危- 参数必须非null但是标记为可为nullRV_ABSOLUTE_VALUE_OF_RANDOM_=使用错误- 尝试计算32位随机整数的绝对值EC_INCOMPATIBLE_ARRAY_=使用错误- 使用equals()比较不兼容的数组UL_UNRELEASED_LOCK_EXCEPTION_=多线程错误- 方法没有在所有异常路径释放锁SE_NONSTATIC_=不良实践- serialVersionUID不是static的UCF_USELESS_CONTROL_=高危- 无用控制流BC_IMPOSSIBLE_=使用错误- 不可能的转换XSS_REQUEST_PARAMETER_TO_SEND_=安全风险- servlet的反射导致跨站脚本漏洞DM_NEW_FOR_=性能- 仅为了获得一个方法就创建了一个对象OBL_UNSATISFIED_=试验- 方法可能在清理流或资源时失败UW_UNCOND_=多线程错误- 无条件等待DLS_DEAD_LOCAL_STORE_OF_=高危- 把null设置给不会用到的局部变量NM_CLASS_NAMING_=类名应该以大写字母开头RC_REF_COMPARISON_BAD_PRACTICE_=使用错误- 怀疑对两个布尔值的引用进行比较MWN_MISMATCHED_=多线程错误- 不匹配的notify()NM_VERY_=错误- 非常容易迷惑的方法名FI_NULLIFY_=不良实践- 空Finalizer禁用了超类的finalizerMTIA_SUSPECT_STRUTS_INSTANCE_=高危- 继承了struts Action的类使用了实例变量DM_STRING_=性能- 方法调用了效率很低的new String(String)构造方法STCAL_INVOKE_ON_STATIC_DATE_FORMAT_=多线程错误- 调用静态DateFormatNP_NULL_PARAM_DEREF_=使用错误- 非虚拟方法调用向非空参数传入了nullFI_=不良实践- 应该删除空的finalizerCD_CIRCULAR_=试验- 类间存在循环引用EC_UNRELATED_=使用错误- 使用equals()比较不同类型EI_EXPOSE_STATIC_=恶意代码漏洞- 把可变对象保存到静态字段中可能会暴露内部静态状态DMI_INVOKING_TOSTRING_ON_ANONYMOUS_=错误- 对数组执行toStringSIC_INNER_SHOULD_BE_STATIC_=性能- 可以重构成一个静态内部类STI_INTERRUPTED_ON_=错误- 在thread实例上调用了静态Thread.interrupted()方法CN_IDIOM_NO_SUPER_=不良实践- clone方法没有调用super.clone()VA_FORMAT_STRING_BAD_=错误用法- 格式化字符串占位符与传入的参数不匹配EQ_DOESNT_OVERRIDE_=高危- 类没有覆盖父类的equals方法BC_IMPOSSIBLE_DOWNCAST_OF_=错误用法- 集合转换为数组元素时发生的类型转换错误SE_NO_SUITABLE_CONSTRUCTOR_FOR_=不良实践- 类是可扩展的,但是没有提供无参数的构造方法TQ_EXPLICIT_UNKNOWN_SOURCE_VALUE_REACHES_ALWAYS_=错误用法- 数值需要类型标示,但是却标记为未知SIC_INNER_SHOULD_BE_STATIC_NEEDS_=性能- 可以筹够成一个静态内部类EQ_CHECK_FOR_OPERAND_NOT_COMPATIBLE_WITH_=不良实践- equals检测不兼容的参数操作RV_RETURN_VALUE_OF_PUTIFABSENT_=错误用法- 忽略了putIfAbsent的返回值,传递给putIfAbsent的值被重用STCAL_INVOKE_ON_STATIC_CALENDAR_=多线程错误- 调用静态CalendarMS_CANNOT_BE_=恶意代码漏洞- 字段不是final的,不能防止恶意代码的攻击IS_INCONSISTENT_=多线程错误- 不一致的同步SE_NO_=不良实践- 类是可序列化的,但是没有定义serialVersionUIDEI_EXPOSE_=恶意代码漏洞- 可能暴露内部实现,通过与可变对象引用协作NM_METHOD_CONSTRUCTOR_=错误用法- 明显的方法/构造方法混淆ICAST_INTEGER_MULTIPLY_CAST_TO_=高危- 整形乘法的结果转换为long型QF_QUESTIONABLE_FOR_=高危- for循环中存在复杂,微妙或者错误的自增DLS_DEAD_STORE_OF_CLASS_=错误用法- 类中保存了无用字符NM_FUTURE_KEYWORD_USED_AS_MEMBER_=不良实践- 使用了未来java版本中成为关键字的标识BC_VACUOUS_=高危- instanceof会一直返回trueINT_VACUOUS_BIT_=高危- 在整形上进行位操作时有一些位上出现空洞NP_NULL_=错误用法- 一个已知的null值被检测它是否是一个类型的实例SIC_THREADLOCAL_DEADLY_=错误用法- 非静态内部类和ThreadLocal的致命结合EQ_=高危- 罕见的equals方法IJU_NO_=错误用法- TestCase没有任何测试EQ_OVERRIDING_EQUALS_NOT_=错误用法- equals方法覆盖了父类的equals可能功能不符XFB_XML_FACTORY_=高危- 方法直接调用了xml接口的一个具体实现SWL_SLEEP_WITH_LOCK_=多线程错误- 方法在获得锁时调用了Thread.sleep()CN_=不良实践- 类实现了Cloneable ,但是没有定义或使用clone方法WA_AWAIT_NOT_IN_=多线程错误- 未在循环中使用的Condition.await()DM_FP_NUMBER_=性能- 方法调用了低效的浮点书构造方法;应该使用静态的valueOf代替SF_SWITCH_NO_=Switch语句中没有包含defaultNP_NULL_ON_SOME_PATH_FROM_RETURN_=高危- 调用返回返回值可能出现null值NP_CLONE_COULD_RETURN_=不良实践- Clone方法可能返回nullMS_OOI_=恶意代码漏洞- 属性应该从接口中移除并将访问权限设置为包保护DM_BOXED_PRIMITIVE_=性能- 方法使用了装箱的基本类型只为了调用toStringEQ_ABSTRACT_=不良实践- 抽象类定义了协变的equals方法DM_STRING_=性能- 方法调用了String的toString()方法SE_METHOD_MUST_BE_=错误用法- 方法必须是private的为了让序列化正常工作DL_SYNCHRONIZATION_ON_=多线程错误- 在Boolean上使用同步可能导致死锁UWF_UNWRITTEN_=错误用法- 未赋值属性IS2_INCONSISTENT_=多线程错误- 不一致的同步IM_AVERAGE_COMPUTATION_COULD_=高危- 计算平均值可能溢出BIT_SIGNED_CHECK_HIGH_=错误用法- 检查位运算的符号FL_MATH_USING_FLOAT_=错误用法- 方法进行数学运算时使用了浮点数的精度WS_WRITEOBJECT_=多线程错误- 类的writeObject()方法是同步的,但是没有做其他事情RV_RETURN_VALUE_=错误用法- 方法忽略了返回值SQL_NONCONSTANT_STRING_PASSED_TO_=安全风险- 非常量的字符串传递给方法执行SQL语句JCIP_FIELD_ISNT_FINAL_IN_IMMUTABLE_=不良实践- 不可变的类的属性应该是finalAM_CREATES_EMPTY_ZIP_FILE_=不良实践- 创建了一个空的zip文件的入口DM_NEXTINT_VIA_=性能- 使用Random的nextInt方法来获得一个随机整数,而不是nextDouble UI_INHERITANCE_UNSAFE_=不良实践- 如果类被扩展,GetResource的使用可能就是不安全的SIO_SUPERFLUOUS_=错误用法- 不必要的类型检测使用instanceof操作符EQ_OTHER_NO_=错误用法- equals()方法定义,但是没有覆盖equals(Object)USM_USELESS_ABSTRACT_=试验- 抽象方法已经在实现的接口中定义了MTIA_SUSPECT_SERVLET_INSTANCE_=高危- 扩展Servlet的类使用了实例变量DM_USELESS_=多线程错误- 使用默认的空run方法创建了一个线程ML_SYNC_ON_UPDATED_=多线程错误- 方法在一个修改了的属性上进行了同步CO_SELF_NO_=不良实践- 协变的compareTo()定义BC_UNCONFIRMED_=高危- 未检查/未证实的类型转换FI_FINALIZER_NULLS_=不良实践- Finalizer空属性BIT_=错误用法- 不兼容的位掩码(BIT_AND)FE_FLOATING_POINT_=高危- 测试浮点数相等TQ_EXPLICIT_UNKNOWN_SOURCE_VALUE_REACHES_NEVER_=错误用法- 值不要求有类型标示,但是标记为未知NP_NULL_PARAM_=错误用法- 方法调用把null传递给一个非null参数FB_MISSING_EXPECTED_=试验- findbugs丢失了期待或需要的警告DMI_INVOKING_HASHCODE_ON_=错误用法- 在数组上调用了hashCodeQBA_QUESTIONABLE_BOOLEAN_=错误用法- 方法在布尔表达式中分配了boolean文字SA_FIELD_SELF_=错误用法- 属性自己与自己进行了比较UR_UNINIT_READ_CALLED_FROM_SUPER_=错误用法- 父类的构造方法调用未初始化属性的方法ES_COMPARING_PARAMETER_STRING_WITH_EQ.na me=不良实践- 比较字符串参数使用了== 或!=INT_BAD_COMPARISON_WITH_NONNEGATIVE_=错误用法- 错误比较非负值与负数INT_BAD_COMPARISON_WITH_SIGNED_=错误用法- 错误比较带符号的byteIO_APPENDING_TO_OBJECT_OUTPUT_=错误用法- 尝试向一个对象输出流添加信息FI_MISSING_SUPER_=不良实践- Finalizer没有调用父类的finalizerVA_FORMAT_STRING_EXTRA_ARGUMENTS_=错误用法- 传递了多余实际使用的格式化字符串的参数HE_EQUALS_USE_=不良实践- 类定义了equals(),但使用了Object.hashCode()IJU_BAD_SUITE_=错误用法- TestCase声明了一个错误的suite方法DMI_CONSTANT_DB_=安全风险- 硬编码了数据库密码REC_CATCH_=高危- 捕获了没有抛出的异常PS_PUBLIC_=高危- 类在公用接口中暴露了同步和信号EC_UNRELATED_=错误用法- 调用equals()比较不同的接口类型UCF_USELESS_CONTROL_FLOW_NEXT_=错误用法- 执行到下一行的无用流程控制LG_LOST_LOGGER_DUE_TO_WEAK_=试验- OpenJDK中存在潜在的丢失logger的风险,因为弱引用NP_UNWRITTEN_=错误用法- 读取未初始化的属性DMI_UNSUPPORTED_=高危- 调用不支持的方法RCN_REDUNDANT_COMPARISON_OF_NULL_AND_NONNULL_=高危- 重复比较非空值和nullEC_BAD_ARRAY_=错误用法- 调用equals(),与==效果一样EI_EXPOSE_=恶意代码漏洞- 可能通过返回一个可变对象的引用暴露了内部实现NP_DEREFERENCE_OF_READLINE_=高危- 没有判断readLine()的结果是否为空UPM_UNCALLED_PRIVATE_=性能- 从未用到的私有方法NP_NULL_ON_SOME_=错误用法- 可能出现空指针引用NP_EQUALS_SHOULD_HANDLE_NULL_=不良实践- equals()方法没有检测null参数EC_NULL_=错误用法- 使用空参数调用equals()SE_BAD_FIELD_=不良实践- 非序列化值保存在序列化类的实例变量中VO_VOLATILE_REFERENCE_TO_=多线程错误- 数组的volatile引用不会把数组元素也当做volatile来引用NP_SYNC_AND_NULL_CHECK_=多线程错误- 同步和空值检测发生在同一个属性上DM_=不良实践- 方法调用了System.exit(...)RC_REF_=不良实践- 怀疑进行了引用比较SE_NO_SUITABLE_=不良实践- 类是可序列化的,但是父类没有定义无参数构造方法DC_=多线程错误- 可能对属性进行了双重检测DMI_LONG_BITS_TO_DOUBLE_INVOKED_ON_=错误用法- 在int上调用了Double.longBitsToDouble RpC_REPEATED_CONDITIONAL_=错误用法- 重复判断条件WMI_WRONG_MAP_=性能- keySet迭代是低效的,使用entrySet代替DLS_DEAD_LOCAL_=高危- 未用的局部变量INT_BAD_REM_BY_=错误用法- 整数剩余模1RV_RETURN_VALUE_IGNORED_BAD_=不良实践- 方法忽略异常返回值SA_LOCAL_SELF_=高危- 局部变量的自我赋值MS_SHOULD_BE_=恶意代码漏洞- 属性不是final,但是应该设置成finalSIC_INNER_SHOULD_BE_=性能- 应该是一个静态内部类NP_GUARANTEED_=错误用法- null值一定会被调用SE_READ_RESOLVE_MUST_RETURN_=不良实践- readResolve方法必须返回ObjectNP_LOAD_OF_KNOWN_NULL_=高危- 加载了已知的null值BX_BOXING_IMMEDIATELY_UNBOXED_TO_PERFORM_=性能- 基本数据被装箱又被拆箱CN_IMPLEMENTS_CLONE_BUT_NOT_=不良实践- 类定义了clone()但没有实现CloneableCO_ABSTRACT_=不良实践- 抽象类定义了协变的compareTo()方法BAC_BAD_APPLET_=试验- 错误的Applet构造方法依赖未初始化的AppletStubEQ_GETCLASS_AND_CLASS_=不良实践- equals方法因为子类失败DB_DUPLICATE_SWITCH_=高危- 在两个switch语句中使用了相同的代码DB_DUPLICATE_=高危- 在两个分支中使用了相同的代码UOE_USE_OBJECT_=试验- 在final类上调用了equals,但是没有覆盖Object的equals方法FI_=不良实践- Finalizer除了调用父类的finalizer以外什么也没做NP_ALWAYS_=错误用法- 调用了null指针DMI_VACUOUS_SELF_COLLECTION_=错误用法- 集合的调用不能被感知DLS_DEAD_LOCAL_STORE_IN_=错误用法- 返回语句中的无用的赋值IJU_ASSERT_METHOD_INVOKED_FROM_RUN_=错误用法- 在run方法中的JUnit检验不能报告给JUnitDMI_EMPTY_DB_=安全风险- 空的数据库密码DM_BOOLEAN_=性能- 方法调用了低效的Boolean构造方法;使用Boolean.valueOf(...)代替BC_IMPOSSIBLE_=错误用法- 不可能转型BC_EQUALS_METHOD_SHOULD_WORK_FOR_ALL_=不良实践- Equals方法不应该假设任何有关参数类型的事宜RV_EXCEPTION_NOT_=错误用法- 异常创建后就丢弃了,没有抛出VA_PRIMITIVE_ARRAY_PASSED_TO_OBJECT_=错误用法- 基本类型数组传递给一个期待可变对象类型参数的方法LI_LAZY_INIT_UPDATE_=多线程错误- 错误的延迟初始化和更新静态属性SA_FIELD_SELF_=错误用法- 属性自身赋值EQ_ALWAYS_=错误用法- equals方法一直返回falseDMI_RANDOM_USED_ONLY_=不良实践- Random对象创建后只用了一次NM_CLASS_NOT_=不良实践- Class没有继承Exception,虽然名字像一个异常SA_LOCAL_DOUBLE_=高危- 给局部变量双重赋值NP_NULL_PARAM_DEREF_ALL_TARGETS_=错误用法- 方法调用传递null给非空参数(ALL_TARGETS_DANGEROUS)NP_TOSTRING_COULD_RETURN_=不良实践- toString方法可能返回nullBC_BAD_CAST_TO_ABSTRACT_=高危- 转换成抽象集合值得怀疑NM_LCASE_=类定义了hashcode(); 应该是hashCode()吧?RU_INVOKE_=多线程错误- 在线程中调用了run(你的意思是再启动一次么?)DMI_INVOKING_TOSTRING_ON_=错误用法- 调用了数组的toStringNM_METHOD_NAMING_=方法名应该以小写字母开头RCN_REDUNDANT_COMPARISON_TWO_NULL_=高危- 重复比较两个null值SA_LOCAL_SELF_=错误用法- 对一个变量进行无意义的自我计算(比如x & x)MS_MUTABLE_=恶意代码漏洞- 属性是可变的HashtableRV_DONT_JUST_NULL_CHECK_=高危- 方法丢掉了readLine的结果,在检测它是非空之后。

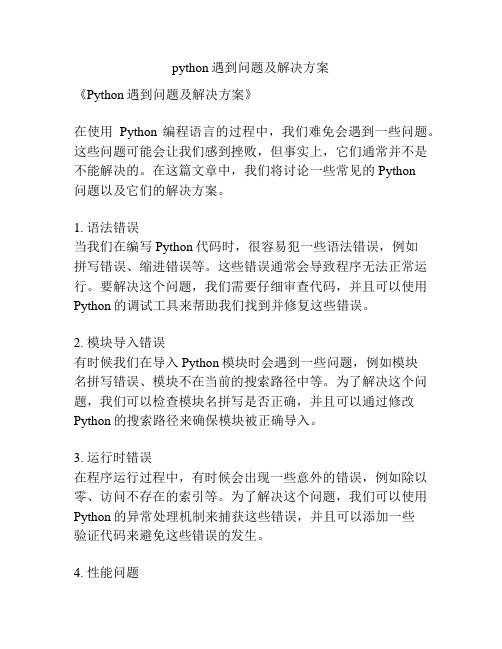

python遇到问题及解决方案

python遇到问题及解决方案

《Python遇到问题及解决方案》

在使用Python编程语言的过程中,我们难免会遇到一些问题。

这些问题可能会让我们感到挫败,但事实上,它们通常并不是不能解决的。

在这篇文章中,我们将讨论一些常见的Python

问题以及它们的解决方案。

1. 语法错误

当我们在编写Python代码时,很容易犯一些语法错误,例如

拼写错误、缩进错误等。

这些错误通常会导致程序无法正常运行。

要解决这个问题,我们需要仔细审查代码,并且可以使用Python的调试工具来帮助我们找到并修复这些错误。

2. 模块导入错误

有时候我们在导入Python模块时会遇到一些问题,例如模块

名拼写错误、模块不在当前的搜索路径中等。

为了解决这个问题,我们可以检查模块名拼写是否正确,并且可以通过修改Python的搜索路径来确保模块被正确导入。

3. 运行时错误

在程序运行过程中,有时候会出现一些意外的错误,例如除以零、访问不存在的索引等。

为了解决这个问题,我们可以使用Python的异常处理机制来捕获这些错误,并且可以添加一些

验证代码来避免这些错误的发生。

4. 性能问题

有时候我们的Python程序会运行的很慢,这可能是因为我们的代码效率不高。

为了解决这个问题,我们可以使用一些优化技巧,例如使用更高效的算法、避免不必要的计算等。

总的来说,遇到问题是不可避免的,但我们并不需要因此感到沮丧。

在编程的过程中,解决问题本身就是一种乐趣,而且通过解决问题我们也会变得更加成熟和有经验。

希望上面提到的解决方案能够帮助你克服在使用Python时遇到的问题。

DS2208数字扫描器产品参考指南说明书

-05 Rev. A

6/2018

Rev. B Software Updates Added: - New Feedback email address. - Grid Matrix parameters - Febraban parameter - USB HID POS (formerly known as Microsoft UWP USB) - Product ID (PID) Type - Product ID (PID) Value - ECLevel

-06 Rev. A

10/2018 - Added Grid Matrix sample bar code. - Moved 123Scan chapter.

-07 Rev. A

11/2019

Added: - SITA and ARINC parameters. - IBM-485 Specification Version.

No part of this publication may be reproduced or used in any form, or by any electrical or mechanical means, without permission in writing from Zebra. This includes electronic or mechanical means, such as photocopying, recording, or information storage and retrieval systems. The material in this manual is subject to change without notice.

Native Instruments MASCHINE MIKRO MK3用户手册说明书

The information in this document is subject to change without notice and does not represent a commitment on the part of Native Instruments GmbH. The software described by this docu-ment is subject to a License Agreement and may not be copied to other media. No part of this publication may be copied, reproduced or otherwise transmitted or recorded, for any purpose, without prior written permission by Native Instruments GmbH, hereinafter referred to as Native Instruments.“Native Instruments”, “NI” and associated logos are (registered) trademarks of Native Instru-ments GmbH.ASIO, VST, HALion and Cubase are registered trademarks of Steinberg Media Technologies GmbH.All other product and company names are trademarks™ or registered® trademarks of their re-spective holders. Use of them does not imply any affiliation with or endorsement by them.Document authored by: David Gover and Nico Sidi.Software version: 2.8 (02/2019)Hardware version: MASCHINE MIKRO MK3Special thanks to the Beta Test Team, who were invaluable not just in tracking down bugs, but in making this a better product.NATIVE INSTRUMENTS GmbH Schlesische Str. 29-30D-10997 Berlin Germanywww.native-instruments.de NATIVE INSTRUMENTS North America, Inc. 6725 Sunset Boulevard5th FloorLos Angeles, CA 90028USANATIVE INSTRUMENTS K.K.YO Building 3FJingumae 6-7-15, Shibuya-ku, Tokyo 150-0001Japanwww.native-instruments.co.jp NATIVE INSTRUMENTS UK Limited 18 Phipp StreetLondon EC2A 4NUUKNATIVE INSTRUMENTS FRANCE SARL 113 Rue Saint-Maur75011 ParisFrance SHENZHEN NATIVE INSTRUMENTS COMPANY Limited 5F, Shenzhen Zimao Center111 Taizi Road, Nanshan District, Shenzhen, GuangdongChina© NATIVE INSTRUMENTS GmbH, 2019. All rights reserved.Table of Contents1Welcome to MASCHINE (23)1.1MASCHINE Documentation (24)1.2Document Conventions (25)1.3New Features in MASCHINE 2.8 (26)1.4New Features in MASCHINE 2.7.10 (28)1.5New Features in MASCHINE 2.7.8 (29)1.6New Features in MASCHINE 2.7.7 (29)1.7New Features in MASCHINE 2.7.4 (31)1.8New Features in MASCHINE 2.7.3 (33)2Quick Reference (35)2.1MASCHINE Project Overview (35)2.1.1Sound Content (35)2.1.2Arrangement (37)2.2MASCHINE Hardware Overview (40)2.2.1MASCHINE MIKRO Hardware Overview (40)2.2.1.1Browser Section (41)2.2.1.2Edit Section (42)2.2.1.3Performance Section (43)2.2.1.4Transport Section (45)2.2.1.5Pad Section (46)2.2.1.6Rear Panel (50)2.3MASCHINE Software Overview (51)2.3.1Header (52)2.3.2Browser (54)2.3.3Arranger (56)2.3.4Control Area (59)2.3.5Pattern Editor (60)3Basic Concepts (62)3.1Important Names and Concepts (62)3.2Adjusting the MASCHINE User Interface (65)3.2.1Adjusting the Size of the Interface (65)3.2.2Switching between Ideas View and Song View (66)3.2.3Showing/Hiding the Browser (67)3.2.4Showing/Hiding the Control Lane (67)3.3Common Operations (68)3.3.1Adjusting Volume, Swing, and Tempo (68)3.3.2Undo/Redo (71)3.3.3Focusing on a Group or a Sound (73)3.3.4Switching Between the Master, Group, and Sound Level (77)3.3.5Navigating Channel Properties, Plug-ins, and Parameter Pages in the Control Area.773.3.6Navigating the Software Using the Controller (82)3.3.7Using Two or More Hardware Controllers (82)3.3.8Loading a Recent Project from the Controller (84)3.4Native Kontrol Standard (85)3.5Stand-Alone and Plug-in Mode (86)3.5.1Differences between Stand-Alone and Plug-in Mode (86)3.5.2Switching Instances (88)3.6Preferences (88)3.6.1Preferences – General Page (89)3.6.2Preferences – Audio Page (93)3.6.3Preferences – MIDI Page (95)3.6.4Preferences – Default Page (97)3.6.5Preferences – Library Page (101)3.6.6Preferences – Plug-ins Page (109)3.6.7Preferences – Hardware Page (114)3.6.8Preferences – Colors Page (114)3.7Integrating MASCHINE into a MIDI Setup (117)3.7.1Connecting External MIDI Equipment (117)3.7.2Sync to External MIDI Clock (117)3.7.3Send MIDI Clock (118)3.7.4Using MIDI Mode (119)3.8Syncing MASCHINE using Ableton Link (120)3.8.1Connecting to a Network (121)3.8.2Joining and Leaving a Link Session (121)4Browser (123)4.1Browser Basics (123)4.1.1The MASCHINE Library (123)4.1.2Browsing the Library vs. Browsing Your Hard Disks (124)4.2Searching and Loading Files from the Library (125)4.2.1Overview of the Library Pane (125)4.2.2Selecting or Loading a Product and Selecting a Bank from the Browser (128)4.2.3Selecting a Product Category, a Product, a Bank, and a Sub-Bank (133)4.2.3.1Selecting a Product Category, a Product, a Bank, and a Sub-Bank on theController (137)4.2.4Selecting a File Type (137)4.2.5Choosing Between Factory and User Content (138)4.2.6Selecting Type and Character Tags (138)4.2.7Performing a Text Search (142)4.2.8Loading a File from the Result List (143)4.3Additional Browsing Tools (148)4.3.1Loading the Selected Files Automatically (148)4.3.2Auditioning Instrument Presets (149)4.3.3Auditioning Samples (150)4.3.4Loading Groups with Patterns (150)4.3.5Loading Groups with Routing (151)4.3.6Displaying File Information (151)4.4Using Favorites in the Browser (152)4.5Editing the Files’ Tags and Properties (155)4.5.1Attribute Editor Basics (155)4.5.2The Bank Page (157)4.5.3The Types and Characters Pages (157)4.5.4The Properties Page (160)4.6Loading and Importing Files from Your File System (161)4.6.1Overview of the FILES Pane (161)4.6.2Using Favorites (163)4.6.3Using the Location Bar (164)4.6.4Navigating to Recent Locations (165)4.6.5Using the Result List (166)4.6.6Importing Files to the MASCHINE Library (169)4.7Locating Missing Samples (171)4.8Using Quick Browse (173)5Managing Sounds, Groups, and Your Project (175)5.1Overview of the Sounds, Groups, and Master (175)5.1.1The Sound, Group, and Master Channels (176)5.1.2Similarities and Differences in Handling Sounds and Groups (177)5.1.3Selecting Multiple Sounds or Groups (178)5.2Managing Sounds (181)5.2.1Loading Sounds (183)5.2.2Pre-listening to Sounds (184)5.2.3Renaming Sound Slots (185)5.2.4Changing the Sound’s Color (186)5.2.5Saving Sounds (187)5.2.6Copying and Pasting Sounds (189)5.2.7Moving Sounds (192)5.2.8Resetting Sound Slots (193)5.3Managing Groups (194)5.3.1Creating Groups (196)5.3.2Loading Groups (197)5.3.3Renaming Groups (198)5.3.4Changing the Group’s Color (199)5.3.5Saving Groups (200)5.3.6Copying and Pasting Groups (202)5.3.7Reordering Groups (206)5.3.8Deleting Groups (207)5.4Exporting MASCHINE Objects and Audio (208)5.4.1Saving a Group with its Samples (208)5.4.2Saving a Project with its Samples (210)5.4.3Exporting Audio (212)5.5Importing Third-Party File Formats (218)5.5.1Loading REX Files into Sound Slots (218)5.5.2Importing MPC Programs to Groups (219)6Playing on the Controller (223)6.1Adjusting the Pads (223)6.1.1The Pad View in the Software (223)6.1.2Choosing a Pad Input Mode (225)6.1.3Adjusting the Base Key (226)6.2Adjusting the Key, Choke, and Link Parameters for Multiple Sounds (227)6.3Playing Tools (229)6.3.1Mute and Solo (229)6.3.2Choke All Notes (233)6.3.3Groove (233)6.3.4Level, Tempo, Tune, and Groove Shortcuts on Your Controller (235)6.3.5Tap Tempo (235)6.4Performance Features (236)6.4.1Overview of the Perform Features (236)6.4.2Selecting a Scale and Creating Chords (239)6.4.3Scale and Chord Parameters (240)6.4.4Creating Arpeggios and Repeated Notes (253)6.4.5Swing on Note Repeat / Arp Output (257)6.5Using Lock Snapshots (257)6.5.1Creating a Lock Snapshot (257)7Working with Plug-ins (259)7.1Plug-in Overview (259)7.1.1Plug-in Basics (259)7.1.2First Plug-in Slot of Sounds: Choosing the Sound’s Role (263)7.1.3Loading, Removing, and Replacing a Plug-in (264)7.1.4Adjusting the Plug-in Parameters (270)7.1.5Bypassing Plug-in Slots (270)7.1.6Using Side-Chain (272)7.1.7Moving Plug-ins (272)7.1.8Alternative: the Plug-in Strip (273)7.1.9Saving and Recalling Plug-in Presets (273)7.1.9.1Saving Plug-in Presets (274)7.1.9.2Recalling Plug-in Presets (275)7.1.9.3Removing a Default Plug-in Preset (276)7.2The Sampler Plug-in (277)7.2.1Page 1: Voice Settings / Engine (279)7.2.2Page 2: Pitch / Envelope (281)7.2.3Page 3: FX / Filter (283)7.2.4Page 4: Modulation (285)7.2.5Page 5: LFO (286)7.2.6Page 6: Velocity / Modwheel (288)7.3Using Native Instruments and External Plug-ins (289)7.3.1Opening/Closing Plug-in Windows (289)7.3.2Using the VST/AU Plug-in Parameters (292)7.3.3Setting Up Your Own Parameter Pages (293)7.3.4Using VST/AU Plug-in Presets (298)7.3.5Multiple-Output Plug-ins and Multitimbral Plug-ins (300)8Using the Audio Plug-in (302)8.1Loading a Loop into the Audio Plug-in (306)8.2Editing Audio in the Audio Plug-in (307)8.3Using Loop Mode (308)8.4Using Gate Mode (310)9Using the Drumsynths (312)9.1Drumsynths – General Handling (313)9.1.1Engines: Many Different Drums per Drumsynth (313)9.1.2Common Parameter Organization (313)9.1.3Shared Parameters (316)9.1.4Various Velocity Responses (316)9.1.5Pitch Range, Tuning, and MIDI Notes (316)9.2The Kicks (317)9.2.1Kick – Sub (319)9.2.2Kick – Tronic (321)9.2.3Kick – Dusty (324)9.2.4Kick – Grit (325)9.2.5Kick – Rasper (328)9.2.6Kick – Snappy (329)9.2.7Kick – Bold (331)9.2.8Kick – Maple (333)9.2.9Kick – Push (334)9.3The Snares (336)9.3.1Snare – Volt (338)9.3.2Snare – Bit (340)9.3.3Snare – Pow (342)9.3.4Snare – Sharp (343)9.3.5Snare – Airy (345)9.3.6Snare – Vintage (347)9.3.7Snare – Chrome (349)9.3.8Snare – Iron (351)9.3.9Snare – Clap (353)9.3.10Snare – Breaker (355)9.4The Hi-hats (357)9.4.1Hi-hat – Silver (358)9.4.2Hi-hat – Circuit (360)9.4.3Hi-hat – Memory (362)9.4.4Hi-hat – Hybrid (364)9.4.5Creating a Pattern with Closed and Open Hi-hats (366)9.5The Toms (367)9.5.1Tom – Tronic (369)9.5.2Tom – Fractal (371)9.5.3Tom – Floor (375)9.5.4Tom – High (377)9.6The Percussions (378)9.6.1Percussion – Fractal (380)9.6.2Percussion – Kettle (383)9.6.3Percussion – Shaker (385)9.7The Cymbals (389)9.7.1Cymbal – Crash (391)9.7.2Cymbal – Ride (393)10Using the Bass Synth (396)10.1Bass Synth – General Handling (397)10.1.1Parameter Organization (397)10.1.2Bass Synth Parameters (399)11Working with Patterns (401)11.1Pattern Basics (401)11.1.1Pattern Editor Overview (402)11.1.2Navigating the Event Area (404)11.1.3Following the Playback Position in the Pattern (406)11.1.4Jumping to Another Playback Position in the Pattern (407)11.1.5Group View and Keyboard View (408)11.1.6Adjusting the Arrange Grid and the Pattern Length (410)11.1.7Adjusting the Step Grid and the Nudge Grid (413)11.2Recording Patterns in Real Time (416)11.2.1Recording Your Patterns Live (417)11.2.2Using the Metronome (419)11.2.3Recording with Count-in (420)11.3Recording Patterns with the Step Sequencer (422)11.3.1Step Mode Basics (422)11.3.2Editing Events in Step Mode (424)11.4Editing Events (425)11.4.1Editing Events with the Mouse: an Overview (425)11.4.2Creating Events/Notes (428)11.4.3Selecting Events/Notes (429)11.4.4Editing Selected Events/Notes (431)11.4.5Deleting Events/Notes (434)11.4.6Cut, Copy, and Paste Events/Notes (436)11.4.7Quantizing Events/Notes (439)11.4.8Quantization While Playing (441)11.4.9Doubling a Pattern (442)11.4.10Adding Variation to Patterns (442)11.5Recording and Editing Modulation (443)11.5.1Which Parameters Are Modulatable? (444)11.5.2Recording Modulation (446)11.5.3Creating and Editing Modulation in the Control Lane (447)11.6Creating MIDI Tracks from Scratch in MASCHINE (452)11.7Managing Patterns (454)11.7.1The Pattern Manager and Pattern Mode (455)11.7.2Selecting Patterns and Pattern Banks (456)11.7.3Creating Patterns (459)11.7.4Deleting Patterns (460)11.7.5Creating and Deleting Pattern Banks (461)11.7.6Naming Patterns (463)11.7.7Changing the Pattern’s Color (465)11.7.8Duplicating, Copying, and Pasting Patterns (466)11.7.9Moving Patterns (469)11.8Importing/Exporting Audio and MIDI to/from Patterns (470)11.8.1Exporting Audio from Patterns (470)11.8.2Exporting MIDI from Patterns (472)11.8.3Importing MIDI to Patterns (474)12Audio Routing, Remote Control, and Macro Controls (483)12.1Audio Routing in MASCHINE (484)12.1.1Sending External Audio to Sounds (485)12.1.2Configuring the Main Output of Sounds and Groups (489)12.1.3Setting Up Auxiliary Outputs for Sounds and Groups (494)12.1.4Configuring the Master and Cue Outputs of MASCHINE (497)12.1.5Mono Audio Inputs (502)12.1.5.1Configuring External Inputs for Sounds in Mix View (503)12.2Using MIDI Control and Host Automation (506)12.2.1Triggering Sounds via MIDI Notes (507)12.2.2Triggering Scenes via MIDI (513)12.2.3Controlling Parameters via MIDI and Host Automation (514)12.2.4Selecting VST/AU Plug-in Presets via MIDI Program Change (522)12.2.5Sending MIDI from Sounds (523)12.3Creating Custom Sets of Parameters with the Macro Controls (527)12.3.1Macro Control Overview (527)12.3.2Assigning Macro Controls Using the Software (528)13Controlling Your Mix (535)13.1Mix View Basics (535)13.1.1Switching between Arrange View and Mix View (535)13.1.2Mix View Elements (536)13.2The Mixer (537)13.2.1Displaying Groups vs. Displaying Sounds (539)13.2.2Adjusting the Mixer Layout (541)13.2.3Selecting Channel Strips (542)13.2.4Managing Your Channels in the Mixer (543)13.2.5Adjusting Settings in the Channel Strips (545)13.2.6Using the Cue Bus (549)13.3The Plug-in Chain (551)13.4The Plug-in Strip (552)13.4.1The Plug-in Header (554)13.4.2Panels for Drumsynths and Internal Effects (556)13.4.3Panel for the Sampler (557)13.4.4Custom Panels for Native Instruments Plug-ins (560)13.4.5Undocking a Plug-in Panel (Native Instruments and External Plug-ins Only) (564)14Using Effects (567)14.1Applying Effects to a Sound, a Group or the Master (567)14.1.1Adding an Effect (567)14.1.2Other Operations on Effects (574)14.1.3Using the Side-Chain Input (575)14.2Applying Effects to External Audio (578)14.2.1Step 1: Configure MASCHINE Audio Inputs (578)14.2.2Step 2: Set up a Sound to Receive the External Input (579)14.2.3Step 3: Load an Effect to Process an Input (579)14.3Creating a Send Effect (580)14.3.1Step 1: Set Up a Sound or Group as Send Effect (581)14.3.2Step 2: Route Audio to the Send Effect (583)14.3.3 A Few Notes on Send Effects (583)14.4Creating Multi-Effects (584)15Effect Reference (587)15.1Dynamics (588)15.1.1Compressor (588)15.1.2Gate (591)15.1.3Transient Master (594)15.1.4Limiter (596)15.1.5Maximizer (600)15.2Filtering Effects (603)15.2.1EQ (603)15.2.2Filter (605)15.2.3Cabinet (609)15.3Modulation Effects (611)15.3.1Chorus (611)15.3.2Flanger (612)15.3.3FM (613)15.3.4Freq Shifter (615)15.3.5Phaser (616)15.4Spatial and Reverb Effects (617)15.4.1Ice (617)15.4.2Metaverb (619)15.4.3Reflex (620)15.4.4Reverb (Legacy) (621)15.4.5Reverb (623)15.4.5.1Reverb Room (623)15.4.5.2Reverb Hall (626)15.4.5.3Plate Reverb (629)15.5Delays (630)15.5.1Beat Delay (630)15.5.2Grain Delay (632)15.5.3Grain Stretch (634)15.5.4Resochord (636)15.6Distortion Effects (638)15.6.1Distortion (638)15.6.2Lofi (640)15.6.3Saturator (641)15.7Perform FX (645)15.7.1Filter (646)15.7.2Flanger (648)15.7.3Burst Echo (650)15.7.4Reso Echo (653)15.7.5Ring (656)15.7.6Stutter (658)15.7.7Tremolo (661)15.7.8Scratcher (664)16Working with the Arranger (667)16.1Arranger Basics (667)16.1.1Navigating Song View (670)16.1.2Following the Playback Position in Your Project (672)16.1.3Performing with Scenes and Sections using the Pads (673)16.2Using Ideas View (677)16.2.1Scene Overview (677)16.2.2Creating Scenes (679)16.2.3Assigning and Removing Patterns (679)16.2.4Selecting Scenes (682)16.2.5Deleting Scenes (684)16.2.6Creating and Deleting Scene Banks (685)16.2.7Clearing Scenes (685)16.2.8Duplicating Scenes (685)16.2.9Reordering Scenes (687)16.2.10Making Scenes Unique (688)16.2.11Appending Scenes to Arrangement (689)16.2.12Naming Scenes (689)16.2.13Changing the Color of a Scene (690)16.3Using Song View (692)16.3.1Section Management Overview (692)16.3.2Creating Sections (694)16.3.3Assigning a Scene to a Section (695)16.3.4Selecting Sections and Section Banks (696)16.3.5Reorganizing Sections (700)16.3.6Adjusting the Length of a Section (702)16.3.6.1Adjusting the Length of a Section Using the Software (703)16.3.6.2Adjusting the Length of a Section Using the Controller (705)16.3.7Clearing a Pattern in Song View (705)16.3.8Duplicating Sections (705)16.3.8.1Making Sections Unique (707)16.3.9Removing Sections (707)16.3.10Renaming Scenes (708)16.3.11Clearing Sections (710)16.3.12Creating and Deleting Section Banks (710)16.3.13Working with Patterns in Song view (710)16.3.13.1Creating a Pattern in Song View (711)16.3.13.2Selecting a Pattern in Song View (711)16.3.13.3Clearing a Pattern in Song View (711)16.3.13.4Renaming a Pattern in Song View (711)16.3.13.5Coloring a Pattern in Song View (712)16.3.13.6Removing a Pattern in Song View (712)16.3.13.7Duplicating a Pattern in Song View (712)16.3.14Enabling Auto Length (713)16.3.15Looping (714)16.3.15.1Setting the Loop Range in the Software (714)16.3.15.2Activating or Deactivating a Loop Using the Controller (715)16.4Playing with Sections (715)16.4.1Jumping to another Playback Position in Your Project (716)16.5Triggering Sections or Scenes via MIDI (717)16.6The Arrange Grid (719)16.7Quick Grid (720)17Sampling and Sample Mapping (722)17.1Opening the Sample Editor (722)17.2Recording Audio (724)17.2.1Opening the Record Page (724)17.2.2Selecting the Source and the Recording Mode (725)17.2.3Arming, Starting, and Stopping the Recording (729)17.2.5Checking Your Recordings (731)17.2.6Location and Name of Your Recorded Samples (734)17.3Editing a Sample (735)17.3.1Using the Edit Page (735)17.3.2Audio Editing Functions (739)17.4Slicing a Sample (743)17.4.1Opening the Slice Page (743)17.4.2Adjusting the Slicing Settings (744)17.4.3Manually Adjusting Your Slices (746)17.4.4Applying the Slicing (750)17.5Mapping Samples to Zones (754)17.5.1Opening the Zone Page (754)17.5.2Zone Page Overview (755)17.5.3Selecting and Managing Zones in the Zone List (756)17.5.4Selecting and Editing Zones in the Map View (761)17.5.5Editing Zones in the Sample View (765)17.5.6Adjusting the Zone Settings (767)17.5.7Adding Samples to the Sample Map (770)18Appendix: Tips for Playing Live (772)18.1Preparations (772)18.1.1Focus on the Hardware (772)18.1.2Customize the Pads of the Hardware (772)18.1.3Check Your CPU Power Before Playing (772)18.1.4Name and Color Your Groups, Patterns, Sounds and Scenes (773)18.1.5Consider Using a Limiter on Your Master (773)18.1.6Hook Up Your Other Gear and Sync It with MIDI Clock (773)18.1.7Improvise (773)18.2Basic Techniques (773)18.2.1Use Mute and Solo (773)18.2.2Create Variations of Your Drum Patterns in the Step Sequencer (774)18.2.3Use Note Repeat (774)18.2.4Set Up Your Own Multi-effect Groups and Automate Them (774)18.3Special Tricks (774)18.3.1Changing Pattern Length for Variation (774)18.3.2Using Loops to Cycle Through Samples (775)18.3.3Load Long Audio Files and Play with the Start Point (775)19Troubleshooting (776)19.1Knowledge Base (776)19.2Technical Support (776)19.3Registration Support (777)19.4User Forum (777)20Glossary (778)Index (786)1Welcome to MASCHINEThank you for buying MASCHINE!MASCHINE is a groove production studio that implements the familiar working style of classi-cal groove boxes along with the advantages of a computer based system. MASCHINE is ideal for making music live, as well as in the studio. It’s the hands-on aspect of a dedicated instru-ment, the MASCHINE hardware controller, united with the advanced editing features of the MASCHINE software.Creating beats is often not very intuitive with a computer, but using the MASCHINE hardware controller to do it makes it easy and fun. You can tap in freely with the pads or use Note Re-peat to jam along. Alternatively, build your beats using the step sequencer just as in classic drum machines.Patterns can be intuitively combined and rearranged on the fly to form larger ideas. You can try out several different versions of a song without ever having to stop the music.Since you can integrate it into any sequencer that supports VST, AU, or AAX plug-ins, you can reap the benefits in almost any software setup, or use it as a stand-alone application. You can sample your own material, slice loops and rearrange them easily.However, MASCHINE is a lot more than an ordinary groovebox or sampler: it comes with an inspiring 7-gigabyte library, and a sophisticated, yet easy to use tag-based Browser to give you instant access to the sounds you are looking for.What’s more, MASCHINE provides lots of options for manipulating your sounds via internal ef-fects and other sound-shaping possibilities. You can also control external MIDI hardware and 3rd-party software with the MASCHINE hardware controller, while customizing the functions of the pads, knobs and buttons according to your needs utilizing the included Controller Editor application. We hope you enjoy this fantastic instrument as much as we do. Now let’s get go-ing!—The MASCHINE team at Native Instruments.MASCHINE Documentation1.1MASCHINE DocumentationNative Instruments provide many information sources regarding MASCHINE. The main docu-ments should be read in the following sequence:1.MASCHINE MIKRO Quick Start Guide: This animated online guide provides a practical ap-proach to help you learn the basic of MASCHINE MIKRO. The guide is available from theNative Instruments website: https:///maschine-mikro-quick-start/2.MASCHINE Manual (this document): The MASCHINE Manual provides you with a compre-hensive description of all MASCHINE software and hardware features.Additional documentation sources provide you with details on more specific topics:►Online Support Videos: You can find a number of support videos on The Official Native In-struments Support Channel under the following URL: https:///NIsupport-EN. We recommend that you follow along with these instructions while the respective ap-plication is running on your computer.Other Online Resources:If you are experiencing problems related to your Native Instruments product that the supplied documentation does not cover, there are several ways of getting help:▪Knowledge Base▪User Forum▪Technical Support▪Registration SupportYou will find more information on these subjects in the chapter Troubleshooting.Document Conventions1.2Document ConventionsThis section introduces you to the signage and text highlighting used in this manual. This man-ual uses particular formatting to point out special facts and to warn you of potential issues.The icons introducing these notes let you see what kind of information is to be expected:This document uses particular formatting to point out special facts and to warn you of poten-tial issues. The icons introducing the following notes let you see what kind of information canbe expected:Furthermore, the following formatting is used:▪Text appearing in (drop-down) menus (such as Open…, Save as… etc.) in the software andpaths to locations on your hard disk or other storage devices is printed in italics.▪Text appearing elsewhere (labels of buttons, controls, text next to checkboxes etc.) in thesoftware is printed in blue. Whenever you see this formatting applied, you will find thesame text appearing somewhere on the screen.▪Text appearing on the displays of the controller is printed in light grey. Whenever you seethis formatting applied, you will find the same text on a controller display.▪Text appearing on labels of the hardware controller is printed in orange. Whenever you seethis formatting applied, you will find the same text on the controller.▪Important names and concepts are printed in bold.▪References to keys on your computer’s keyboard you’ll find put in square brackets (e.g.,“Press [Shift] + [Enter]”).►Single instructions are introduced by this play button type arrow.→Results of actions are introduced by this smaller arrow.Naming ConventionThroughout the documentation we will refer to MASCHINE controller (or just controller) as the hardware controller and MASCHINE software as the software installed on your computer.The term “effect” will sometimes be abbreviated as “FX” when referring to elements in the MA-SCHINE software and hardware. These terms have the same meaning.Button Combinations and Shortcuts on Your ControllerMost instructions will use the “+” sign to indicate buttons (or buttons and pads) that must be pressed simultaneously, starting with the button indicated first. E.g., an instruction such as:“Press SHIFT + PLAY”means:1.Press and hold SHIFT.2.While holding SHIFT, press PLAY and release it.3.Release SHIFT.1.3New Features in MASCHINE2.8The following new features have been added to MASCHINE: Integration▪Browse on , create your own collections of loops and one-shots and send them directly to the MASCHINE browser.Improvements to the Browser▪Samples are now cataloged in separate Loops and One-shots tabs in the Browser.▪Previews of loops selected in the Browser will be played in sync with the current project.When a loop is selected with Prehear turned on, it will begin playing immediately in-sync with the project if transport is running. If a loop preview starts part-way through the loop, the loop will play once more for its full length to ensure you get to hear the entire loop once in context with your project.▪Filters and product selections will be remembered when switching between content types and Factory/User Libraries in the Browser.▪Browser content synchronization between multiple running instances. When running multi-ple instances of MASCHINE, either as Standalone and/or as a plug-in, updates to the Li-brary will be synced across the instances. For example, if you delete a sample from your User Library in one instance, the sample will no longer be present in the other instances.Similarly, if you save a preset in one instance, that preset will then be available in the oth-er instances, too.▪Edits made to samples in the Factory Libraries will be saved to the Standard User Directo-ry.For more information on these new features, refer to the following chapter ↑4, Browser. Improvements to the MASCHINE MIKRO MK3 Controller▪You can now set sample Start and End points using the controller. For more information refer to ↑17.3.1, Using the Edit Page.Improved Support for A-Series Keyboards▪When Browsing with A-Series keyboards, you can now jump quickly to the results list by holding SHIFT and pushing right on the 4D Encoder.▪When Browsing with A-Series keyboards, you can fast scroll through the Browser results list by holding SHIFT and twisting the 4D Encoder.▪Mute and Solo Sounds and Groups from A-Series keyboards. Sounds are muted in TRACK mode while Groups are muted in IDEAS.。

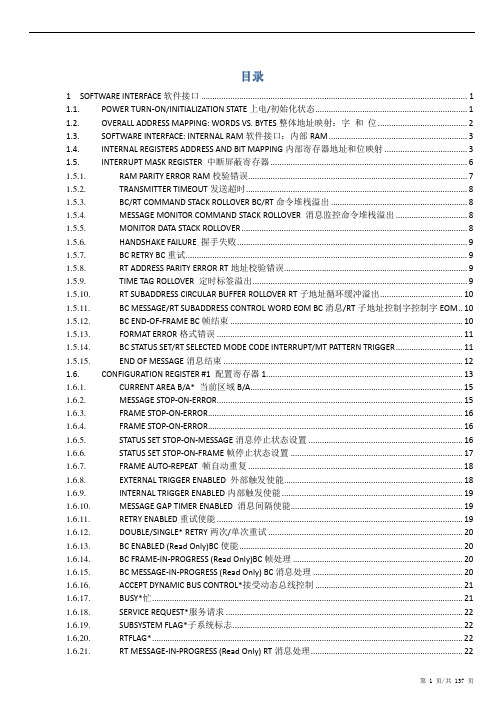

BU_61580寄存器说明中文版

目录

1 SOFTWARE INTERFACE 软件接口 ....................................................................................................................... 1 1.1. POWER TURN-ON/INITIALIZATION STATE 上电/初始化状态 .................................................................... 1 1.2. OVERALL ADDRESS MAPPING: WORDS VS. BYTES 整体地址映射:字 和 位 ........................................ 2 1.3. SOFTWARE INTERFACE: INTERNAL RAM 软件接口:内部 RAM .............................................................. 3 1.4. INTERNAL REGISTERS ADDRESS AND BIT MAPPING 内部寄存器地址和位映射 ..................................... 3 1.5. INTERRUPT MASK REGISTER 中断屏蔽寄存器 ........................................................................................ 6 1.5.1. RAM PARITY ERROR RAM 校验错误..................................

answer