LMH6585VV中文资料

LM2575HV中文资料(上)

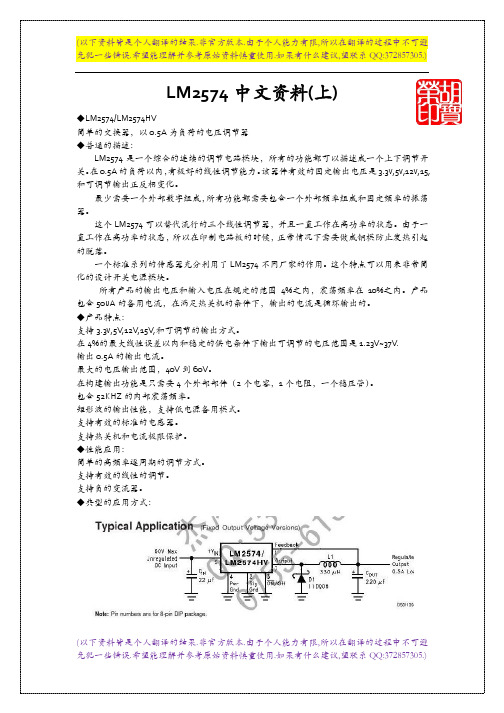

(以下资料皆是个人翻译的结果.非官方版本.由于个人能力有限,所以在翻译的过程中不可避 免犯一些错误.希望能理解并参考原始资料慎重使用.如果有什么建议,望联系 QQ:372857305.)LM2574 中文资料(上)◆LM2574/LM2574HV 简单的交换器,以 0.5A 为负荷的电压调节器 ◆普通的描述: LM2574 是一个综合的连续的调节电路模块,所有的功能都可以描述成一个上下调节开 关。

0.5A 的负荷以内, 在 有极好的线性调节能力。

该器件有效的固定输出电压是 3.3v,5v,12v,15, 和可调节输出正反相变化。

最少需要一个外部数字组成, 所有功能都需要包含一个外部频率组成和固定频率的振荡 器。

这个 LM2574 可以替代流行的三个线性调节器,并且一直工作在高功率的状态。

由于一 直工作在高功率的状态, 所以在印制电路板的时候, 正常情况下需要做成铜模防止发热引起 的脱落。

一个标准系列的传感器充分利用了 LM2574 不同厂家的作用。

这个特点可以用来非常简 化的设计开关电源模块。

所有产品的输出电压和输入电压在规定的范围 4%之内,震荡频率在 10%之内。

产品 包含 50uA 的备用电流,在满足热关机的条件下,输出的电流是循环输出的。

◆产品特点: 支持 3.3v,5V,12V,15V,和可调节的输出方式。

在 4%的最大线性误差以内和稳定的供电条件下输出可调节的电压范围是 1.23V~37V. 输出 0.5A 的输出电流。

最大的电压输出范围,40V 到 60V。

在构建输出功能是只需要 4 个外部部件(2 个电容,1 个电阻,一个稳压管) 。

包含 52KHZ 的内部震荡频率。

矩形波的输出性能,支持低电源备用模式。

支持有效的标准的电感器。

支持热关机和电流极限保护。

◆性能应用: 简单的高频率逐周期的调节方式。

支持有效的线性的调节。

支持负的变流器。

◆典型的应用方式:(以下资料皆是个人翻译的结果.非官方版本.由于个人能力有限,所以在翻译的过程中不可避 免犯一些错误.希望能理解并参考原始资料慎重使用.如果有什么建议,望联系 QQ:372857305.)(以下资料皆是个人翻译的结果.非官方版本.由于个人能力有限,所以在翻译的过程中不可避 免犯一些错误.希望能理解并参考原始资料慎重使用.如果有什么建议,望联系 QQ:372857305.)60V 未校准的 DC 输入◆连接图解:校准的 0.5A 输出◆极限参数: 如果用在军队或者航天上面,则必须用详细的(更好的)设备。

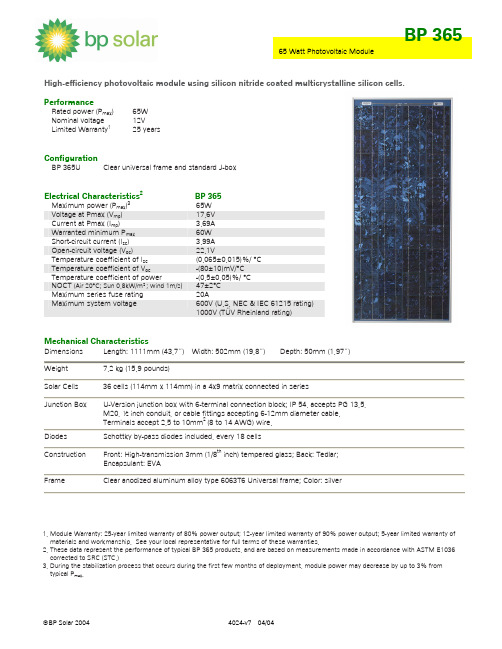

BP365资料

BP 365 I-V Curves

4.5 4.0 3.5 Current (A) 3.0 2.5 2.0 1.5 1.0 0.5 0.0 0 10 20 30 Voltage (V)

t=0C t=25C t=50C t=75C

Listed by Underwriter’s Laboratories for electrical and fire safety (Class C fire rating) Approved by Factory Mutual Research in NEC Class 1, Division 2, Groups C & D hazardous locations (U)

元器件交易网

BP 365

65 Watt Photovoltaic Module

High-efficiency photovoltaic module using silicon nitride coated multicrystalline silicon cells. Performance

Diodes Construction Frame

1. Module Warranty: 25-year limited warranty of 80% power output; 12-year limited warranty of 90% power output; 5-year limited warranty of materials and workmanship. See your local representative for full terms of these warranties. 2. These data represent the performance of typical BP 365 products, and are based on measurements made in accordance with ASTM E1036 corrected to SRC (STC.) 3. During the stabilization process that occurs during the first few months of deployment, module power may decrease by up to 3% from typical Pmax.

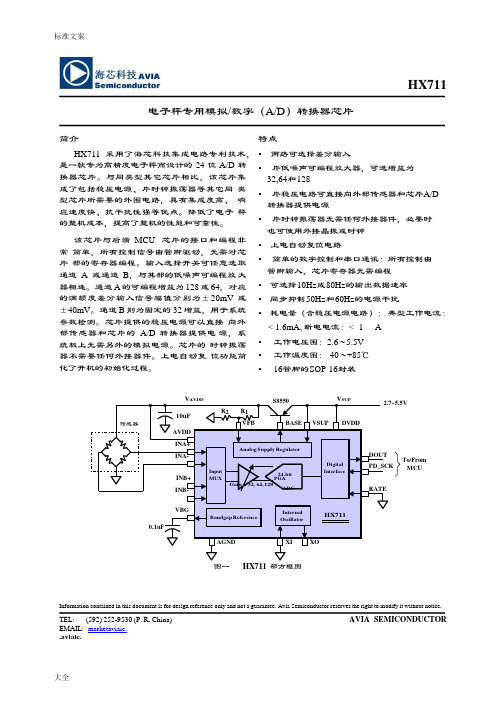

hx711官方资料(海芯)

标准文案大全DigitalInterfaceAnalog Supply RegulatorInputMUXInternalOscillatorBandgap ReferenceHX711电子秤专用模拟/数字(A/D)转换器芯片简介HX711 采用了海芯科技集成电路专利技术,是一款专为高精度电子秤而设计的 24 位 A/D 转换器芯片。

与同类型其它芯片相比,该芯片集成了包括稳压电源、片时钟振荡器等其它同类型芯片所需要的外围电路,具有集成度高、响应速度快、抗干扰性强等优点。

降低了电子秤的整机成本,提高了整机的性能和可靠性。

该芯片与后端MCU 芯片的接口和编程非常简单,所有控制信号由管脚驱动,无需对芯片部的寄存器编程。

输入选择开关可任意选取通道A 或通道B,与其部的低噪声可编程放大器相连。

通道 A 的可编程增益为 128 或 64,对应的满额度差分输入信号幅值分别为±20mV 或±40mV。

通道 B 则为固定的 32 增益,用于系统参数检测。

芯片提供的稳压电源可以直接向外部传感器和芯片的A/D 转换器提供电源,系统板上无需另外的模拟电源。

芯片的时钟振荡器不需要任何外接器件。

上电自动复位功能简化了开机的初始化过程。

特点•两路可选择差分输入•片低噪声可编程放大器,可选增益为32,64 和128•片稳压电路可直接向外部传感器和芯片A/D 转换器提供电源•片时钟振荡器无需任何外接器件,必要时也可使用外接晶振或时钟•上电自动复位电路•简单的数字控制和串口通讯:所有控制由管脚输入,芯片寄存器无需编程•可选择10Hz 或80Hz 的输出数据速率•同步抑制50Hz 和60Hz 的电源干扰•耗电量(含稳压电源电路):典型工作电流:< 1.6mA, 断电电流:< 1 A•工作电压围:2.6 ~ 5.5V•工作温度围:-40 ~ +85℃•16 管脚的S OP-16 封装V AVDD10uF R2 R1S8550V SUP 2.7~5.5V传感器AVDDINA+INA-INB+INB-VFBPGAGain = 32, 64, 128BASE VSUP DVDD24-bitADCDOUTPD_SCKRATETo/FromMCU0.1uF VBGHX711 AGND XI XO图一HX711 部方框图Information contained in this document is for design reference only and not a guarantee. Avia Semiconductor reserves the right to modify it without notice. TEL: (592) 252-9530 (P. R. China) AVIA SEMICONDUCTOR EMAIL: marketaviaic..aviaic.大全管脚说明稳压电路电源 VSUP DVDD 数字电源稳压电路控制输出BASE RATE 输出数据速率控制输入 模拟电源 AVDDXI 外部时钟或晶振输入 稳压电路控制输入VFB XO 晶振输入 模拟地 AGND DOUT 串口数据输出参考电源输出 VBG PD_SCK 断电和串口时钟输入通道A 负输入端 INNA INPB 通道B 正输入端 通道A 正输入端INPAINNB通道B 负输入端SOP-16L 封装表一 管脚描述主要电气参数AA(1)有效位数E NBs(Effective Number of Bits) = ln(FSR/RMS Noise)/ln(2)。

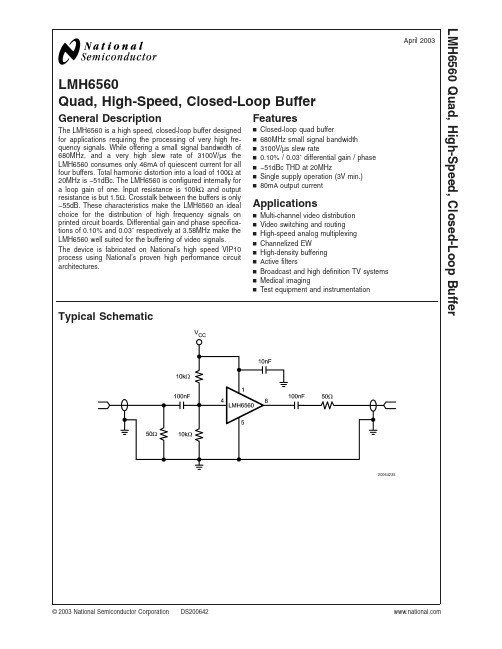

LMH6560中文资料

LMH6560Quad,High-Speed,Closed-Loop BufferGeneral DescriptionThe LMH6560is a high speed,closed-loop buffer designed for applications requiring the processing of very high fre-quency signals.While offering a small signal bandwidth of 680MHz,and a very high slew rate of 3100V/µs the LMH6560consumes only 46mA of quiescent current for all four buffers.Total harmonic distortion into a load of 100Ωat 20MHz is −51dBc.The LMH6560is configured internally for a loop gain of one.Input resistance is 100k Ωand output resistance is but 1.5Ω.Crosstalk between the buffers is only −55dB.These characteristics make the LMH6560an ideal choice for the distribution of high frequency signals on printed circuit boards.Differential gain and phase specifica-tions of 0.10%and 0.03˚respectively at 3.58MHz make the LMH6560well suited for the buffering of video signals.The device is fabricated on National’s high speed VIP10process using National’s proven high performance circuit architectures.Featuresn Closed-loop quad buffern 680MHz small signal bandwidth n 3100V/µs slew raten 0.10%/0.03˚differential gain /phase n −51dBc THD at 20MHzn Single supply operation (3V min.)n80mA output currentApplicationsn Multi-channel video distribution n Video switching and routing n High-speed analog multiplexing n Channelized EWn High-density buffering n Active filtersn Broadcast and high definition TV systems n Medical imagingnTest equipment and instrumentationTypical Schematic20064235April 2003LMH6560Quad,High-Speed,Closed-Loop Buffer©2003National Semiconductor Corporation Absolute Maximum Ratings(Note 1)If Military/Aerospace specified devices are required,please contact the National Semiconductor Sales Office/Distributors for availability and specifications.ESD Tolerance Human Body Model 2000V (Note 2)Machine Model200V (Note 3)Output Short Circuit Duration (Note 4),(Note 5)Supply Voltage (V +–V −)13VVoltage at Input/Output Pins V ++0.8V,V −−0.8VSoldering InformationInfrared or Convection (20sec.)235˚CWave Soldering (10sec.)260˚CStorage Temperature Range −65˚C to +150˚CJunction Temperature (Note 6)+150˚COperating Ratings (Note 1)Supply Voltage (V +–V −)3-10VOperating Temperature Range (Note 6),(Note 7)−40˚C to +85˚CPackage Thermal Resistance (Note 6),(Note 7)14-Pin SOIC 137˚C/W 14-Pin TSSOP160˚C/W±5V Electrical CharacteristicsUnless otherwise specified,all limits guaranteed for T J =25˚C,V +=+5V,V −=−5V,V O =V CM =0V and R L =100Ωto 0V.Boldface limits apply at the temperature extremes.Symbol ParameterConditionsMin (Note 9)Typ (Note 8)Max (Note 9)Units Frequency Domain ResponseSSBW Small Signal Bandwidth V O <0.5V PP 680MHz GFN Gain Flatness <0.1dB V O <0.5V PP375MHz FPBW Full Power Bandwidth (−3dB)V O =2V PP (+10dBm)280MHZ DG Differential Gain R L =150Ωto 0V;f =3.58MHz 0.10%DPDifferential PhaseR L =150Ωto 0V;f =3.58MHz 0.03degTime Domain Response t r Rise Time 3.3V Step (20-80%)0.6ns t f Fall Time0.7ns t s Settling Time to 0.1% 3.3V Step 9ns OS Overshoot 1V Step 4%SR Slew Rate(Note 11)3100V/µs Distortion And Noise PerformanceHD22nd Harmonic Distortion V O =2V PP ;f =20MHz −58dBc HD33rdHarmonic DistortionV O =2V PP ;f =20MHz −52dBc THD Total Harmonic Distortion V O =2V PP ;f =20MHz −51dBc e n Input-Referred Voltage Noise f =1MHz 3nV/CP 1dB Compression Point f =10MHz+23dBm CT Amplifier Crosstalk Receiving Amplifier:R S =50Ωto 0V;f =10MHz −55dB SNR Signal to Noise Ratio f =5MHz;V O =1V PP 120dB AGMAmplifier Gain MatchingR L =2k Ωto 0V;f =5MHz;V O =1V PP0.05dBStatic,DC Performance A CLSmall Signal Voltage GainV O =100mV PP R L =100Ωto 0V 0.970.995V/VV O =100mV PP R L =2k Ωto 0V0.990.998V OS Input Offset Voltage22025mV TC V OSTemperature Coefficient Input Offset Voltage(Note 12)28µV/˚CL M H 6560 2±5V Electrical Characteristics(Continued)Unless otherwise specified,all limits guaranteed for T J=25˚C,V+=+5V,V−=−5V,V O=V CM=0V and R L=100Ωto0V. Boldface limits apply at the temperature extremes.Symbol Parameter ConditionsMin(Note9)Typ(Note8)Max(Note9)UnitsI B Input Bias Current(Note10)−10−14−5µATC I B Temperature Coefficient InputBias Current(Note12)−4.7nA/˚CR OUT Output Resistance R L=100Ωto0V;f=100kHz 1.5ΩR L=100Ωto0V;f=10MHz 1.6PSRR Power Supply Rejection Ratio V S=±5V to V S=±5.25V;V IN=0V 484467dBI S Supply Current,All4Buffers No Load465863mA Miscellaneous PerformanceR IN Input Resistance100kΩC IN Input Capacitance2pFV O Output Swing Positive R L=100Ωto0V 3.103.083.34VR L=2kΩto0V 3.583.553.64Output Swing Negative R L=100Ωto0V−3.34−3.20−3.17VR L=2kΩto0V−3.64−3.58−3.55I SC Output Short Circuit Current Sourcing:V IN=V+;V O=0V−83mASinking:V IN=V−;V O=0V83I O Linear Output Current Sourcing:V IN-V O=0.5V(Note10)−50−42−74mASinking:V IN-V O=−0.5V (Note10)5040745V Electrical CharacteristicsUnless otherwise specified,all limits guaranteed for T J=25˚C,V+=+5V,V−=0V,V O=V CM=V+/2and R L=100Ωto V+/2. Boldface limits apply at the temperature extremes.Symbol Parameter ConditionsMin(Note9)Typ(Note8)Max(Note9)UnitsFrequency Domain ResponseSSBW Small Signal Bandwidth V O<0.5V PP455MHzGFN Gain Flatness<0.1dB V O<0.5V PP75MHzFPBW Full Power Bandwidth(−3dB)V O=2V PP(+10dBm)175MHZDG Differential Gain R L=150Ωto V+/2;f=3.58MHz0.4%DP Differential Phase R L=150Ωto V+/2;f=3.58MHz0.09degTime Domain Responset r Rise Time 2.3V PP Step(20-80%)0.8nst f Fall Time 1.0nst s Settling Time to0.1% 2.3V Step10nsOS Overshoot1V Step0%SR Slew Rate(Note11)1445V/µsLMH656035V Electrical Characteristics(Continued)Unless otherwise specified,all limits guaranteed for T J =25˚C,V +=+5V,V −=0V,V O =V CM =V +/2and R L =100Ωto V +/2.Boldface limits apply at the temperature extremes.Symbol ParameterConditionsMin (Note 9)Typ (Note 8)Max (Note 9)Units Distortion And Noise PerformanceHD22nd Harmonic Distortion V O =2V PP ;f =20MHz −52dBc HD33rd Harmonic Distortion V O =2V PP ;f =20MHz −54dBc THD Total Harmonic Distortion V O =2V PP ;f =20MHz −50dBc e n Input-Referred Voltage Noise f =1MHz 3nV/CP 1dB Compression Point f =10MHz+14dBm CT Amplifier Crosstalk Receiving Amplifier:R S =50Ωto V +/2;f =10MHz −55dB SNR Signal to Noise Ratio V O =1V PP ;f =5MHz 120dB AGMAmplifier Gain MatchingV O =1V PPR L =2k Ωto V +/2;f =5MHz 0.5dBStatic,DC Performance A CLSmall Signal Voltage GainV O =100mV PPR L =100Ωto V +/20.970.994V/VV O =100mV PP R L =2k Ωto V +/20.990.998V OS Input Offset Voltage21315mV TC V OS Temperature Coefficient Input Offset Voltage (Note 12)2µV/˚C I B Input Bias Current(Note 10)−5−5.5−2.5µA TC I B Temperature Coefficient Input Bias Current (Note 12)1.3nA/˚CR OUTOutput ResistanceR L =100Ωto V +/2;f =100kHz 1.7ΩR L =100Ωto V +/2;f =10MHz2.0PSRR Power Supply Rejection Ratio V S =+5V to V S =+5.5V;V IN =V S /2484567dB I SSupply Current All 4BufferNo Load212630mAMiscellaneous Performance R IN Input Resistance 16k ΩC IN Input Capacitance 2pFV OOutput Swing PositiveR L =100Ωto V +/2 3.743.70 3.85V R L =2k Ωto V +/23.923.903.96Output Swing NegativeR L =100Ωto V +/2 1.15 1.221.27VR L =2k Ωto V +/21.04 1.081.10I SC Output Short Circuit Current Sourcing:V IN =V +;V O =V +/2−40mASinking:V IN =V −;V O =V +/222I OLinear Output CurrentSourcing:V IN -V O =0.5V (Note 10)−50−40−64mASinking:V IN -V O =−0.5V (Note 10)302045L M H 6560 43V Electrical CharacteristicsUnless otherwise specified,all limits guaranteed for T J =25˚C,V +=3V,V −=0V,V O =V CM =V +/2and R L =100Ωto V +/2.Boldface limits apply at the temperature extremes.Symbol ParameterConditionsMin (Note 9)Typ (Note 8)Max (Note 9)Units Frequency Domain ResponseSSBW Small Signal Bandwidth V O <0.5V PP 265MHz GFN Gain Flatness <0.1dB V O <0.5V PP40MHz FPBW Full Power Bandwidth (−3dB)V O =1V PP (+4.5dBm)115MHZ Time Domain Responset r Rise Time 1V Step (20-80%) 1.1ns t f Fall Time1.3ns t s Settling Time to 0.1%1V Step 11ns OS Overshoot 0.5V Step 0%SR Slew Rate(Note 11)480V/µs Distortion And Noise PerformanceHD22nd Harmonic Distortion V O =0.5V PP ;f =20MHz −55dBc HD33rdHarmonic DistortionV O =0.5V PP ;f =20MHz −61dBc THD Total Harmonic Distortion V O =0.5V PP ;f =20MHz −54dBc e n Input-Referred Voltage Noise f =1MHz 3nV/CP 1dB Compression Point f =10MHz+4dBm CT Amplifier Crosstalk Receiving Amplifier:R S =50Ωto V +/2;f =10MHz −55dB SNR Signal to Noise Ratio f =5MHz;V O =1V PP 120dB AGMAmplifier Gain MatchingR L =2k Ωto V +/2;f =5MHz;V O =1V PP 0.4dBStatic,DC Performance A CLSmall Signal Voltage GainV O =100mV PPR L =100Ωto V +/20.970.99V/VV O =100mV PP R L =2k Ωto V +/20.990.997V OS Input Offset Voltage1.6810mV TC V OS Temperature Coefficient Input Offset Voltage (Note 12) 2.6µV/˚C I B Input Bias Current(Note 10)−3−3.5−1.4µA TC I B Temperature Coefficient Input Bias Current (Note 12)0.3nA/˚CR OUTOutput ResistanceR L =100Ωto V +/2;f =100kHz 2.1ΩR L =100Ωto V +/2;f =10MHz2.8PSRR Power Supply Rejection Ratio V S =+3V to V S =+3.5V;V IN =V S /2484665dB I SSupply Current,All 4BuffersNo Load111518mAMiscellaneous Performance R IN Input Resistance 17k ΩC INInput Capacitance2pFLMH656053V Electrical Characteristics(Continued)Unless otherwise specified,all limits guaranteed for T J =25˚C,V +=3V,V −=0V,V O =V CM =V +/2and R L =100Ωto V +/2.Boldface limits apply at the temperature extremes.Symbol ParameterConditionsMin (Note 9)Typ (Note 8)Max (Note 9)UnitsV OOutput Swing PositiveR L =100Ωto V +/2 2.01.93 2.05VR L =2k Ωto V +/22.12.02.15Output Swing NegativeR L =100Ωto V +/20.95 1.01.07VR L =2k Ωto V +/20.850.901.0I SC Output Short Circuit Current Sourcing:V IN =V +;V O =V +/2−26mASinking:V IN =V −;V O =V +/214I OLinear Output CurrentSourcing:V IN -V O =0.5V (Note 10)−20−13−30mASinking:V IN -V O =−0.5V (Note 10)12820Note 1:Absolute Maximum Ratings indicate limits beyond which damage to the device may occur.Operating Ratings indicate conditions for which the device is intended to be functional,but specific performance is not guaranteed.For guaranteed specifications and the test conditions,see the Electrical Characteristics.Note 2:Human body model,1.5k Ωin series with 100pF Note 3:Machine Model,0Ωin series with 200pF.Note 4:Applies to both single-supply and split-supply operation.Continuous short circuit operation at elevated ambient temperature can result in exceeding the maximum allowed junction temperature of 150˚C.Note 5:Short circuit test is a momentary test.See next note.Note 6:The maximum power dissipation is a function of T J(MAX),θJA ,and T A .The maximum allowable power dissipation at any ambient temperature is P D =(T J(MAX)-T A )/θJA .All numbers apply for packages soldered directly onto a PC board.Note 7:Electrical Table values apply only for factory testing conditions at the temperature indicated.Factory testing conditions result in very limited self-heating of the device such that T J =T A .There is no guarantee of parametric performance as indicated in the electrical tables under conditions of internal self-heating where T J >T A .See Applications section for information on temperature de-rating of this device.Note 8:Typical Values represent the most likely parametric norm.Note 9:All limits are guaranteed by testing or statistical analysis.Note 10:Positive current corresponds to current flowing into the device.Note 11:Slew rate is the average of the positive and negative slew rate.Average Temperature Coefficient is determined by dividing the change in a parameter at temperature extremes by the total temperature change.Note 12:Average Temperature Coefficient is determined by dividing the change in a parameter at temperature extremes by the total temperature change.L M H 6560 6LMH6560 Connection Diagram14-Pin SOIC/TSSOP Array20064234Top ViewOrdering InformationPackage Part Number Package Marking Transport Media NSC Drawing14-pin SOIC LMH6560MA LMH6560MA55Units/Rail M14ALMH6560MAX 2.5k Units Tape and Reel14-pin TSSOP LMH6560MT LMH6560MT94Units/Rail MTC14LMH6560MTX 2.5k Units Tape and Reel7Typical Performance CharacteristicsAt T J =25˚C,V +=+5V,V −=−5V;unless otherwise speci-fied.Frequency ResponseFrequency Response Over Temperature2006420620064207Gain Flatness 0.1dB Differential Gain and Phase2006420820064204Differential Gain and Phase Transient Response Positive2006420520064228L M H 6560 8Typical Performance Characteristics At T J =25˚C,V +=+5V,V −=−5V;unless otherwisespecified.(Continued)Transient Response NegativeTransient Response Positive for Various V SUPPLY2006422620064227Transient Response Negative for Various V SUPPLY Harmonic Distortion vs.V OUT @5MHz2006422520064211Harmonic Distortion vs.V OUT @10MHz Harmonic Distortion vs.V OUT @20MHz2006420920064210LMH65609Typical Performance Characteristics At T J =25˚C,V +=+5V,V −=−5V;unless otherwisespecified.(Continued)THD vs.V OUT for Various FrequenciesVoltage Noise2006422420064229Linearity V OUT vs.V INCrosstalk vs.Frequency2006422020064202Crosstalk vs.TimeV OS vs.V SUPPLY for 3Units2006420320064230L M H 6560 10Typical Performance Characteristics At TJ=25˚C,V+=+5V,V−=−5V;unless otherwise specified.(Continued)V OS vs.V SUPPLY for Unit1V OS vs.V SUPPLY for Unit22006423120064232 V OS vs.V SUPPLY for Unit3I B vs.V SUPPLY(Note10)2006423320064212 R OUT vs.Frequency PSRR vs.Frequency2006422120064222LMH6560Typical Performance Characteristics At T J =25˚C,V +=+5V,V −=−5V;unless otherwisespecified.(Continued)I SUPPLY vs.V SUPPLYI SUPPLY vs.V IN2006421620064236V OUT vs.I OUT (Sinking)V OUT vs.I OUT (Sourcing)2006421520064201I OUT Sinking vs.V SUPPLY I OUT Sourcing vs.V SUPPLY2006421320064214L M H 6560Typical Performance Characteristics At TJ=25˚C,V+=+5V,V−=−5V;unless otherwise specified.(Continued)Small Signal Pulse Response Large Signal Pulse Response@V S=3V2006422320064219 Large Signal Pulse Response@V S=5V Large Signal Pulse Response@V S=10V2006421820064217LMH6560Application NotesUSING BUFFERSA buffer is an electronic device delivering current gain but no voltage gain.It is used in cases where low impedances need to be driven and more drive current is required.Buffers need a flat frequency response and small propagation delay.Fur-thermore,the buffer needs to be stable under resistive,capacitive and inductive loads.High frequency buffer appli-cations require that the buffer be able to drive transmission lines and cables directly.IN WHAT SITUATION WILL WE USE A BUFFER?In case of a signal source not having a low output impedance one can increase the output drive capability by using a buffer.For example,an oscillator might stop working or have frequency shift which is unacceptably high when loaded heavily.A buffer should be used in that situation.Also in the case of feeding a signal to an A/D converter it is recom-mended that the signal source be isolated from the A/D ing a buffer assures a low output impedance,the delivery of a stable signal to the converter,and accom-modation of the complex and varying capacitive loads that the A/D converter presents to the Op Amp.Optimum value is often found by experimentation for the particular application.The use of buffers is strongly recommended for the handling of high frequency signals,for the distribution of signals through transmission lines or on pcb’s,or for the driving of external equipment.There are several driving options:•Use one buffer to drive one transmission line (see Figure 1)•Use one buffer to drive to multiple points on one trans-mission line (see Figure 2)•Use one buffer to drive several transmission lines each driving a different receiver.(see Figure 3)In these three options it is seen that there is more than one preferred method to reach an (end)point on a transmission line.Until a certain point the designer can make his own choice but the designer should keep in mind never to break the rules about high frequency transport of signals.An ex-planation follows in the text below.TRANSMISSION LINESIntroduction to transmission lines .The following is an over-view of transmission line theory.Transmission lines can be used to send signals from DC to very high frequencies.At all points across the transmission line,Ohm’s law must apply.For very high frequencies,parasitic behavior of the PCB or cable comes into play.The type of cable used must match the application.For example an audio cable looks like a coax cable but is unusable for radar frequencies at 10GHz.In this case one have to use special coax cables with lower attenu-ation and radiation characteristics.Normally a pcb trace is used to connect components on a pcb board together.An important consideration is the amount of current carried by these pcb traces.Wider pcb traces are required for higher current densities and for ap-plications where very low series resistance is needed.When routed over a ground plane,pcb traces have a defined characteristic impedance.In many design situations charac-teristic impedance is not utilized.In the case of high fre-quency transmission,however it is necessary to match the load impedance to the line characteristic impedance (more on this later).Each trace is associated with a certain amount of series resistance and series inductance and also exhibits parallel capacitance to the ground plane.The combination of these parameters defines the line’s characteristic imped-ance.The formula with which we calculate this impedance is as follows:Z 0=√(L/C)In this formula L and C are the value/unit length,and R is assumed to be zero.C and L are unknown in many cases so we have to follow other steps to calculate the Z 0.The char-acteristic impedance is a function of the geometry of the cross section of the line.In (Figure 4)we see three cross sections of commonly used transmission lines.20064237FIGURE 1.20064238FIGURE 2.20064239FIGURE 3.L M H 6560Application Notes(Continued)Z 0can be calculated by knowing some of the physical di-mensions of the pcb line,such as pcb thickness,width of the trace and e r ,relative dielectric constant.The formula given in transmission line theory for calculating Z 0is as follows:(1)e r relative dielectric constant h pcb height W trace widthth thickness of the copperIf we ignore the thickness of the copper in comparison to the width of the trace then we have the following equation:(2)With this formula it is possible to calculate the line imped-ance vs.the trace width.Figure 5shows the impedance associated with a given line ing the same formula it is also possible to calculate what happens when e r varies over a certain range of values.Varying the e r over a range of 1to 10gives a variation for the Characteristic Impedance of about 40Ωfrom 80Ωto 38Ω.Most transmission lines are designed to have 50Ωor 75Ωimpedance.The reason for that is that in many cases the pcb trace has to connect to a cable whose impedance is either 50Ωor 75Ω.As shown e r and the line width influence this value.Next,there will be a discussion of some issues associated with the interaction of the transmission line at the source and at the load.Connecting a Load Using a Transmission LineIn most cases,it is unrealistic to think that we can place a driver or buffer so close to the load that we don’t need a transmission line to transport the signal.The pcb trace length between a driver and the load may affect operation depending upon the operating frequency.Sometimes it is possible to do measurements by connecting the DUT directly to the analyzer.As frequencies become higher the short lines from the DUT to the analyzer become long lines.When this happens there is a need to use transmission lines.The next point to examine is what happens when the load is connected to the transmission line.When driving a load,it is important to match the line and load impedance,otherwise reflections will occur and this phenomena will distort the signal.If a transient is applied at T =0(Figure 6,trace A)the resultant waveform may be observed at the start point of the transmission line.At this point (begin)on the transmission line the voltage increases to (V)and the wave front travels along the transmission line and arrives at the load at T =10.At any point across along the line I =V/Z 0,where Z 0is the impedance of the transmission line.For an applied transient of 2V with Z 0=50Ωthe current from the buffer output stage is 40mA.Many vintage op amps cannot deliver this level of current because of an output current limitation of about 20mA or even less.At T =10the wave front arrives at the load.Since the load is perfectly matched to the transmission line all of the current traveling across the line will be ab-sorbed and there will be no reflections.In this case source and load voltages are exactly the same.When the load and the transmission line have unequal values of impedance a different situation results.Remember there is another basic which says that energy cannot be lost.The power in the transmission line is P =V 2/R.In our example the total power is 22/50=80mW.Assume a load of 75Ω.In that case a power of 80mW arrives at the 75Ωload and causes a voltage of the proper amplitude to maintain the incoming power.20064240FIGURE 4.20064243FIGURE 5.LMH6560Application Notes(Continued)(3)The voltage wavefront of 2.45V will now set about traveling back over the transmission line towards the source,thereby resulting in a reflection caused by the mismatch.On the other hand if the load is less then 50Ωthe backwards traveling wavefront is subtracted from the incoming voltage of 2V.Assume the load is 40Ω.Then the voltage across the load is:(4)This voltage is now traveling backwards through the line toward the start point.In the case of a sinewave interfer-ences develop between the incoming waveform and the backwards-going reflections,thus distorting the signal.If there is no load at all at the end point the complete transient of 2V is reflected and travels backwards to the beginning of the line.In this case the current at the endpoint is zero and the maximum voltage is reflected.In the case of a short at the end of the line the current is at maximum and the voltage is zero.Using Serial and Parallel TerminationMany applications,such as video,use a series resistance between the driver and the transmission line (see Figure 1).In this case the transmission line is terminated with the characteristic impedance at both ends of the line.See Figure 6trace B.The voltage traveling through the transmission lineis half the voltage seen at the output of the buffer,because the series resistor in combination with Z 0forms a two-to-on voltage divider.The result is a loss of 6dB.For video appli-cations,amplifier gain is set to 2in order to realize an overall gain of 1.Many operational amplifiers have a relatively flat frequency response when set to a gain of two compared to unity gain.In trace B it is seen that,if the voltage reaches the end of the transmission line,the line is perfectly matched and no reflections will occur.The end point voltage stays at half the output voltage of the opamp or buffer.Driving More Than One InputAnother transmission line possibility is to route the trace via several points along a transmission line (see Figure 2).This is only possible if care is taken to observe certain restric-tions.Failure to do so will result in impedance discontinuities that will cause distortion of the signal.In the configuration of Figure 2there is a transmission line connected to the buffer output and the end of the line is terminated with Z 0.We have seen in the section ’Connecting a load using a transmission line’that for the condition above,the signal throughout the entire transmission line has the same value,that the value is the nominal value initiated by the opamp output,and no reflections occur at the end point.Because of the lack of reflections no interferences will occur.Consequently the sig-nal has every where on the line the same amplitude.This allows the possibility of feeding this signal to the input port of any device which has high ohmic impedance and low input capacitance.In doing so keep in mind that the transient arrives at different times at the connected points in the transmission line.The speed of light in vacuum,which is about 3*108m/sec,reduces through a transmission line or a cable down to a value of about 2*108m/sec.The distance the signal will travel in 1ns is calculated by solving the following formula:S =V*tWhereS =distanceV =speed in the cableT =timeThis calculation gives the following result:s =2*108*1*10-9=0.2mThat is for each nanosecond the wave front shifts 20cm over the length of the transmission line.Keep in mind that in a distance of just 2cm the time displacement is already ing Serial Termination To More Than One Transmission LineAnother way to reach several points via a transmission line is to start several lines from one buffer output (see Figure 3).This is possible only if the output can deliver the needed current into the sum of all transmission lines.As can be seen in this figure there is a series termination used at the begin-ning of the transmission line and the end of the line has no termination.This means that only the signal at the endpoint is usable because at all other points the reflected signal will cause distortion over the line.Only at the endpoint will the measured signal be the same as at the startpoint.Referring to Figure 6trace C,the signal at the beginning of the line has a value of V/2and at T =0this voltage starts traveling towards the end of the transmission line.Once at the end-point the line has no termination and 100%reflection will occur.At T =10the reflection causes the signal to jump to 2V and to start traveling back along the line to the buffer (see Figure 6trace D).Once the wavefront reaches the series20064246FIGURE 6.L M H 6560Application Notes(Continued)termination resistor,provided the termination value is Z0,thewavefront undergoes total absorption by the termination.This is only true if the output impedance of the buffer/driveris low in comparison to the characteristic impedance Z0.Atthis moment the voltage in the whole transmission line hasthe nominal value of2V(see Figure6trace E).If the threetransmission lines each have a different length the particularpoint in time at which the voltage at the series terminationresistor jumps to2V is different for each case.However,thistransient is not transferred to the other lines because theoutput of the buffer is low and this transient is highly attenu-ated by the combination of the termination resistor and theoutput impedance of the buffer.A simple calculation illus-trates the point.Assume that the output impedance is5Ω.For the frequency of interest the attenuation is V B/V A=55/5=11,where A and B are the points in Figure3.In this casethe voltage caused by the reflection is2/11=0.18V.Thisvoltage is transferred to the remaining transmission lines insequence and following the same rules as before this volt-age is seen at the end points of those lines.The lower theoutput resistance the higher the decoupling between thedifferent lines.Furthermore one can see that at the endpointof these transmission lines there is a normal transient equalto the original transient at the beginning point.However at allother points of the transmission line there is a step voltage atdifferent distances from the startpoint depending at whatpoint this is measured(see trace D).Measuring the Length of a Transmission LineAn open transmission line can be used to measure thelength of a particular transmission line.As can be seen inFigure7.The line of interest has a certain length.A transientis applied at T=0and at that point in time the wavefrontstarts traveling with an amplitude of V/2towards the end ofthe line where it is reflected back to the startpoint.To calculate the length of the line it is necessary to measureimmediately after the series termination resistor.The voltageat that point remains at half nominal voltage,thus V/2,untilthe reflection returns and the voltage jumps to V.During aninterval of5ns the signal travels to the end of the line wherethe wave front is reflected and returns to the measurementpoint.During the time interval when the wavefront is travel-ing to the end of the transmission line and back the voltagehas a value of V/2.This interval is10ns.The length can becalculated with the following formula:S=(V*T)/2(5)As calculated before in the section‘Driving more than oneinput’the signal travels20cm/ns so in5ns this distanceindicated distance is1m.So this example is easily verified.APPLYING A CAPACITIVE LOADThe assumption of pure resistance for the purpose of con-necting the output stage of a buffer or opamp to a load isappropriate as a first approximation.Unfortunately that isonly a part of the truth.Associated with this resistor is acapacitor in parallel and an inductor in series.Any capaci-tance such as C1-1which is connected directly to the outputstage is active in the loop gain as see in Figure8.Outputcapacitance,present also at the minus input in the case of abuffer,causes an increasing phase shift leading to instabilityor even oscillation in the circuit.Unfortunately the leads of the output capacitor also containseries inductors which become more and more important athigh frequencies.At a certain frequency this series capacitorand inductor forms an LC combination which becomes se-ries resonant.At the resonant frequency the reactive com-ponent vanishes leaving only the ohmic resistance(R-1orR-2)of the series L/C combination.(see Figure9).Consider a frequency sweep over the entire spectrum forwhich the LMH6559high frequency buffer is active.In thefirst instance peaking occurs due to the parasitic capaci-tance connected at the load whereas at higher frequenciesthe effects of the series combination of L and C become20064247FIGURE7.20064249FIGURE8.20064250FIGURE9.LMH6560。

MTD658中文资料

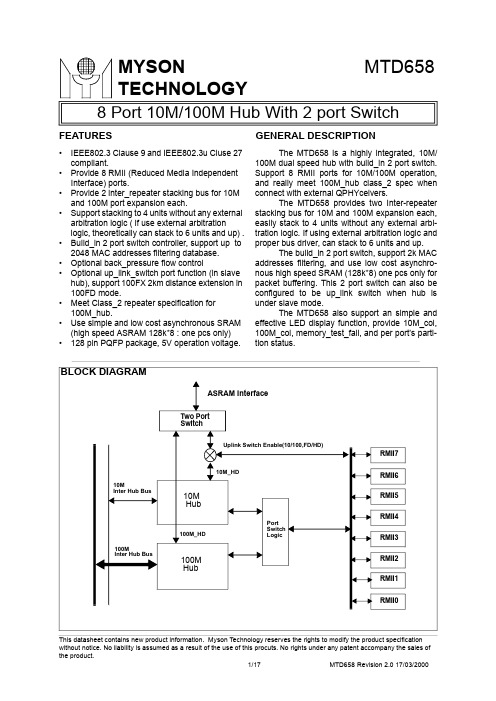

TECHNOLOGYFEATURESGENERAL DESCRIPTIONBLOCK DIAGRAM•IEEE802.3 Clause 9 and IEEE802.3u Cluse 27 compliant.•Provide 8 RMII (Reduced Media Independent Interface) ports.•Provide 2 inter_repeater stacking bus for 10M and 100M port expansion each.•Support stacking to 4 units without any external arbitration logic ( if use external arbitration logic, theoretically can stack to 6 units and up) .•Build_in 2 port switch controller, support up to 2048 MAC addresses filtering database.•Optional back_pressure flow control•Optional up_link_switch port function (in slave hub), support 100FX 2km distance extension in 100FD mode.•Meet Class_2 repeater specification for 100M_hub.•Use simple and low cost asynchronous SRAM (high speed ASRAM 128k*8 : one pcs only) •128 pin PQFP package, 5V operation voltage.8 Port 10M/100M Hub With 2 port SwitchThe MTD658 is a highly integrated, 10M/100M dual speed hub with build_in 2 port switch.Support 8 RMII ports for 10M/100M operation,and really meet 100M_hub class_2 spec when connect with external QPHYceivers.The MTD658 provides two Inter-repeater stacking bus for 10M and 100M expansion each,easily stack to 4 units without any external arbi-tration logic. If using external arbitration logic and proper bus driver, can stack to 6 units and up.The build_in 2 port switch, support 2k MAC addresses filtering, and use low cost asynchro-nous high speed SRAM (128k*8) one pcs only for packet buffering. This 2 port switch can also be configured to be up_link switch when hub is under slave mode.The MTD658 also support an simple and effective LED display function, provide 10M_col,100M_col, memory_test_fail, and per port’s parti-tion status.ASRAM InterfaceRMII7RMII6RMII5RMII4RMII3RMII2RMII1RMII010M Hub100M HubTwo PortSwitchUplink Switch Enable(10/100,FD/HD)10M_HD100M_HDPort Switch Logic10MInter Hub Bus100MInter Hub BusTECHNOLOGY SYSTEM DIAGRAMMTD658MTD658QUAD PHYsceiverQUAD PHYsceiverASRAM (128kx8)10MInter Hub Bus100MInter Hub Bus10MInter Hub Bus100MInter Hub Bus MTD658MTD65810MInter Hub Bus100MInter Hub Bus10MInter Hub Bus100MInter Hub BusRMII0-3RMII4-7DB25 ConnectorQUAD TransformerQUAD TransformerRJ45RJ45TECHNOLOGY1.0 PIN CONNECTION1021011009998979695949392919089888786858483828180797877767574737271706968676665103104105106107108109110111112113114115116117118119120121122123124125126127128A 11A 5A 9A 6A 8A 7A 13A 12W EB A 14G N D A 15A 16I R E Q 10_O U T I R E Q 10_I N 0I R E Q 10_I N 1I R E Q 10_I N 2IC O L B 10I A C K B 10I C L K 10G ND I D A T 10I RE Q 100_O U T I R E Q 100_I N 0I R E Q 100_I N 1I R E Q 100_I N 2I C O L B 100I A C K B 100G N D I C L K 100V C C I D A T 100_0I D A T 100_1I D A T 100_2I D A T 100_3I M A S T E RF D 7U P S W E NVCC A4GND OEB A3A10A2A1D7A0D6D0D5D1GND D4D2D3VCC SYSCLK GND LEDDAT LEDCLK MDC MDIO RSTB0102030405060708091011121314151617181920212223242526272829303132333435363738C R SD V 0T X D 0_1V C C T X D 0_0T XE N 0R X D 0_0R X D 0_1C R S D V 1T X D 1_1T X D 1_0T X E N 1R X D 1_0R X D 1_1G N D C R S D V 2T X D 2_1T X D 2_0T X E N 2R X D 2_0R X D 2_1C R S D V 3T X D 3_1T X D 3_0T X E N 3R X D 3_0R X D 3_1S P D 3S P D 2S P D 1S P D 0V C C G N D C R S D V 4T X D 4_1T X D 4_0T X E N 4R X D 4_0R X D 4_1MTD6586463626160595857565554535251504948474645444342414039SPD4SPD5SPD6SPD7GND VCC RXD7_1RXD7_0TXEN7TXD7_0TXD7_1CRSDV7RXD6_1RXD6_0TXEN6TXD6_0TXD6_1CRSDV6GND VCC RXD5_1RXD5_0TXEN5TXD5_0TXD5_1CRSDV5TECHNOLOGY2.0 PIN DESCRIPTIONSRMII Port Interface PinsName Pin Number I/O DescriptionsCRSDV01I Port0 RMII receive interface signal, CRSDV0 is asserted high whenport0 media is non_idle.RXD0_0 RXD0_167IIPort0 RMII receive data bit_0.Port0 RMII receive data bit_1.TXEN05O Port0 RMII transmit enable signal.TXD0_0 TXD0_142OOPort0 RMII transmit data bit_0.Port0 RMII transmit data bit_1.CRSDV18I Port1 RMII receive interface signal, CRSDV1 is asserted high whenport1 media is non_idle.RXD1_0 RXD1_11213IIPort1 RMII receive data bit_0.Port1 RMII receive data bit_1.TXEN111O Port1 RMII transmit enable signal.TXD1_0 TXD1_1109OOPort1 RMII transmit data bit_0.Port1 RMII transmit data bit_1.CRSDV215I Port2 RMII receive interface signal, CRSDV2 is asserted high whenport2 media is non_idle.RXD2_0 RXD2_11920IIPort2 RMII receive data bit_0.Port2 RMII receive data bit_1.TXEN218O Port2 RMII transmit enable signal.TXD2_0 TXD2_11716OOPort2 RMII transmit data bit_0.Port2 RMII transmit data bit_1.CRSDV321I Port3 RMII receive interface signal, CRSDV3 is asserted high whenport3 media is non_idle.RXD3_0 RXD3_12526IIPort3 RMII receive data bit_0.Port3 RMII receive data bit_1.TXEN324O Port3 RMII transmit enable signal.TXD3_0 TXD3_12322OOPort3 RMII transmit data bit_0.Port3 RMII transmit data bit_1.CRSDV433I Port4 MII receive interface signal, CRSDV4 is asserted high whenport4 media is non_idle.RXD4_0 RXD4_13738IIPort4 RMII receive data bit_0.Port4 RMII receive data bit_1.TXEN436O Port4 RMII transmit enable signal.TXD4_0 TXD4_13534OOPort4 RMII transmit data bit_0.Port4 RMII transmit data bit_1.CRSDV539I Port5 RMII receive interface signal, CRSDV5 is asserted high whenport5 media is non_idle.RXD5_0 RXD5_14344IIPort5 RMII receive data bit_0.Port5 RMII receive data bit_1.TXEN542O Port5 RMII transmit enable signal. TXD5_0O Port5 RMII transmit data bit_0.TECHNOLOGYNote: Asynchronous SRAM acess time: 10/12 ns (max)CRSDV647I Port6 RMII receive interface signal, CRSDV6 is asserted high whenport6 media is non_idle.RXD6_0RXD6_15152I I Port6 RMII receive data bit_0.Port6 RMII receive data bit_1.TXEN650O Port6 RMII transmit enable signal.TXD6_0TXD6_14948O O Port6 RMII transmit data bit_0.Port6 RMII transmit data bit_1.CRSDV753I Port7 RMII receive interface signal, CRSDV7 is asserted high when port7 media is non_idle.RXD7_0RXD7_15758I I Port7 RMII receive data bit_0.Port7 RMII receive data bit_1.TXEN756O Port7 RMII transmit enable signal.TXD7_0TXD7_15554O OPort7 RMII transmit data bit_0.Port7 RMII transmit data bit_1.High Speed Asynchronous SRAM Interface PinsName Pin NumberI/O Descriptions WEB 94O ASRAM control pin for write (low active).OEB 106O ASRAM control pin for read (low active).D[7:0]111,113,115,118,120,119,116,114I/O ASRAM data busA[16:0]90,91,93,96,95,102,108,100,98,97,99,101,104,107,109,110,112O ASRAM address busRMII Port Interface PinsName Pin NumberI/O DescriptionsTECHNOLOGY10M Inter-Bus Interface pinsName Pin Number I/O DescriptionsIMASTER67I Master hub selection:when high: means hub internal inter_bus arbiter is enabled and hub internal two_port switch is well conneted to 10M_hub core and100M_hub core .when low: means hub internal inter_bus arbiter is disabled and hub internal two_port switch is not connected to 10M_hub core and100M_hub core.IACKB1084I/O10M Inter-Bus port access acknowledge signal (low active). For master hub, this pin is output; for slave hub is input, or while EXT_ARBjumper was set to “1”, this pin is input from an external arbitrationdevice.ICOLB1085I/O10M Inter-Bus collision signal (low active). For master hub, this pin can output multi hub collision event to inform all slave hub ; for slave hub, this pin is an input, or while EXT_ARB jumper was set to “1”, this pin is input from an external arbitration device.IREQ10_IN088I10M Inter-Bus port access request input. IREQ10_IN187I10M Inter-Bus port access request input. IREQ10_IN286I10M Inter-Bus port access request input. IREQ10_OUT89O10M Inter-Bus port access request output. ICLK1083I/O10M Inter-Bus port clock.IDAT1081I/O10M Inter-Bus port data bit100M Inter-Bus Interface pins Name Pin Number I/O DescriptionsIACKB10075I/O100M Inter-Bus port access acknowledge signal (low active). For master hub, this pin is output; for slave hub is input, or while EXT_ARBjumper was set to “1”, this pin is input from an external arbitrationdevice.ICOLB10076I/O100M Inter-Bus collision signal (low active). For master hub, this pin can output multi hub collision event to inform all slave hub ; for slave hub, this pin is an input, or while EXT_ARB jumper was set to “1”, this pin is input from an external arbitration device.IREQ100_IN079I100M Inter-Bus port access request input. IREQ100_IN178I100M Inter-Bus port access request input. IREQ100_IN277I100M Inter-Bus port access request input. IREQ100_OUT80O100M Inter-Bus port access request output. ICLK10073I/O100M Inter-Bus port clock.IDAT100_071I/O100M Inter-Bus port data bit 0.IDAT100_170I/O100M Inter-Bus port data bit 1.IDAT100_269I/O100M Inter-Bus port data bit 2.IDAT100_368I/O100M Inter-Bus port data bit 3.TECHNOLOGYLED Interface PinsName Pin Number I/O DescriptionsLEDDAT124I/O LED display serial data out; mapping for LEDCLK signal’s burst clock , its serial out data sequence is : ( first bit be shifted out is from b00, and end of burst bit is b23)b00: port0 partition b08: 10hub_col b16: port0 rx_activityb01: port1 partition b09: 100hub_col b17: port1 rx_activityb02: port2 partition b10: asram_test_fail b18: port2 rx_activityb03: port3 partition b11: port3 partition b19: port3 rx_activityb04: port4 partition b12: port4 partition b20: port4 rx_activityb05: port5 partition b13: port5 partition b21: port5 rx_activityb06: port6 partition b14: port6 partition b22: port6 rx_activityb07: port7 partition b15: port7 partition b23: port7 rx_activityLEDCLK125I/O LED display clock signal, the signal is a discontinued clock for LED data serial shift out. Every clock burst have 24 cycles ( period : 160 ns), and the clock burst will be repeated with every 42ms.Miscellaneous PinsName Pin Number I/O Descriptions RSTB128I System reset input, low active.SYSCLK122I50MHz system clock inputMDC126I/O MII management clock inoutMDIO127I/O MII management data inoutUPSWEN65I Up_link switch port enabling : one of internal two_port switch port willconnect to 100M_hub domain, and another port will redirect to RMII port7.FD766I When up_link switch port enabling, this pin is port7’s full_deplex indi-cator, input from PHY. When hign , indicate port7 in running onfull_duplex mode. When low, indicate on half_duplex mode.SPD030I Port0 speed indicator, input from PHY.SPD0 input low: 100M , input high: 10M.SPD129I Port1 speed indicator, input from PHY.SPD1 input low: 100M , input high: 10M.SPD228I Port2 speed indicator, input from PHY.SPD2 input low: 100M , input high: 10M.SPD327I Port3 speed indicator, input from PHY.SPD3 input low: 100M , input high: 10M.SPD464I Port4 speed indicator, input from PHY.SPD4 input low: 100M , input high: 10M.SPD563I Port5 speed indicator, input from PHY.SPD5 input low: 100M , input high: 10M.TECHNOLOGYSPD662I Port6 speed indicator, input from PHY.SPD6 input low: 100M , input high: 10M.SPD761I Port7 speed indicator, input from PHY.SPD7 input low: 100M , input high: 10M.VCC3,31,45,59,72,103,121PWR Power pinsGND14,32,46,60,74,82,92,105,117,123GND Ground pinsPower On Configuration Set Up Table Name Pin Number I/O DescriptionsTXEN218I/O Back_pressure disable : ( power on external jumper configuration ) - external pull_low (default ) : normal mode (back_pressure enbale) - external pull_high: back_pressure disableTXEN542I/O Auto MII_setting bypass : ( power on external jumper configuration ) - external pull_low (default ) : normal mode ( auto MII_setting); after power_on, MTD658 will auto setup PHY devices be forced in half_ duplex mode for repeater apllication.- external pull_high: auto MII_setting bypassMDC126I/O 1522 bytes packet accept enable : ( power on external jumper configura-tion )- external pull_low (default ) : normal mode ( <=1518 bytes packetaccept)- external pull_high: <= 1522 bytes packet acceptLEDCLK125I/O Hub dealy enhance : ( power on external jumper configuration ) - external pull_low (default ) : nomal hub propagation delay mode.- external pull_high: enhanced hub propagational delay mode, for cov-ering long latency PHY devices).LEDDAT124I/O External arbiter enable : ( power on external jumper configuration ) - external pull_low (default ) : normal mode (inter_repeater bus use internal arbiter)- external pull_high: inter_repeater bus use external arbiter .Miscellaneous PinsName Pin Number I/O DescriptionsTECHNOLOGY3.0 FUNCTIONAL DESCRIPTIONSThe MTD658 is conformed to IEEE802.3 chapter 9 and IEEE802.3u clause 27 specifications. The MTD658 provides 8 Redused MII interfaces and an embedded two port switch to construct a 10M/ 100M dual speed Hub application. Two Inter-Bus are also provided for stackable 10M/100M dual speed Hub application. The MTD658 functions are described as follows:3.1 Repeat and data handling8 independent RMII ports integrated with IEEE802.3 chapter 9 and IEEE802.3u clause 27 repeater functions simultaneously. MTD658 embedded two Hub cores (10M and 100M) ,and each dedicated RMII interface port can get per port’s speed information from per port speed input pin, and thenMTD658 will switch individual port to their appropriated Hub core functions (10M or 100M).The MTD658 receive packets from each RMII ports, and redirect port’s input packet to 10M or 100M Hub core according each port’s speed. The internal IEEE802.3 chapter 9 or IEEE802.3u clause 27 repeater main state machine will starts to repeat the input packet to all ports except the input port. If larger than or equal to two ports have input packet simultaneously, this will be treated as a collision, and MTD658 will assert an arbitrary JAM pattern to all ports’ output until collision event disappear and net-work is idle.3.2 PartitionThe MTD658 provides 10M/100M auto partition/reconnection functions to guarantee the network seg-ment performance by means of dectecting a consecutive collisions. Each dedicated RMII port has implement a individual 10M/100M auto partition/reconnection state machine. If port’s consecutive colli-sion number over or equal to CClimit (10M CClimit default is 32, 100M CClimit default is 64), this port will be partitioned. Reconnection will occurs after a larger than 512 bit time packet was received or transmitted from this partitioned port without any collision.When port is under partition state, MTD658 will not accept any input messages from this port (just mon-itor input message), but will continue output repeated messages to this partition port.Some new partition criterions are also implement, such as long_collision_partition event,jabber_partition event. In 10M/100M partition state machine, longer than 1024 bit time continueous col-lision will force port enter partition state. In 100M partition state machine, if port enter jabber_on state, this port will be partitioned. In 10M, jabber_partition function is not implemented.3.3 JabberThe jabber protect function is used to prevent an illegally long packet reception. After the MTD658 received a longer than 65536 +/- 6.25% bit times packet, this receive port‘s receive/transmit path will be inhibited until carrier is no longer detected.3.4 MII SettingDue to HUB is an half duplex device, the MTD658 need to force all connected phsical devices to work in half duplex environment. The MTD658 will setting all PHY’s SMI register 4’s half/full duplex bit during power on, and than restart auto-negotiation procedure to work in half duplex mode, and the PHY’s device ID should be set by PCB maker from 5’h04 - 5’h0b(port0-7).3.5 Inter-Bus InterfaceTwo Inter-Bus Interface are provided by the MTD658, One is 10M Inter-Bus Interface, the other is 100M Inter-Bus Interface. The Inter-Bus interface is designed for stackable hub application. For each domain, up to 4 MTD658s can be stacked through this Inter-Bus without any external arbitration logic. The Inter-Bus Interface includes IMASTER, IDATA (100M: use IDAT<3:0>, 10M: use only IDAT), REQOUT, REQIN0-2, ICLK, IACKB, ICOLB pins. IMASTER decide which MTD658 can arbitrate the Inter-Bus, and only one MTD658’s IMASTER can be tie high in a stackable Hub. IDATA are synchronous with ICLK. The MTD658 output REQOUT to inform Inter-Bus Interface that it need the Inter-Bus right. WhenTECHNOLOGYREQOUT , but IACKB is asserted, means this MTD658 can get data from IDATA bus. When only one MTD658 output REQOUT to Inter-Bus Interface, IACKB will be asserted by Inter-Bus master device, If larger than two MTD658’s REQOUT were asserted, Inter-Bus master will not assert IACKB , but will assert ICOLB to inform all the connected MTD658s.The Inter-Bus interface can also be programmed to EXT_ARB mode, using LEDDAT pin’s jumper set-ting. In this mode, Inter-Bus interface need an external arbitration logic to arbitrate Inter-Bus operation. And in this mode, the stackable capability is not limitted by the MTD658’s REQIN pins number.3.6 10M/100M packet SwitchThe MTD658 inplements a 10/100M two port switch for 10M/100M packet switching. Total 2K address entrys are provided for packets’ SA learning and DA routing; and alsoprovide automatic aging function ( aging time = 300secs). The input packet from 10MHub ( or 100M Hub) will be stored to external memory first, while packet is good for forward ( CRC chech ok, 64Bytes < length > 1518Bytes, and not local packets ) , than forward this packet to 100M Hub (or 10M Hub).3.7 Uplink Switch PortThe MTD658 can config one switch port as an uplink switch port. When UPSWEN pin is high, and IMASTER pin is low, one of the intenal switch port is connect to 100M HUB, the other is connected to RMII port 7. In uplink switch mode, port 7 can work in 10M/100M(from SPEED7 pin), half/fullduplex(from P7FULL pin) mode.3.8 Memory InterfaceThe MTD658 use asynchronous SRAM as two port switchs’ packet buffers, total has 128K byte exter-nal memory for packet buffering.3.9 MII managementThe MTD658 can be managed through MDC, MDIO pins. The MTD658 implements 3 MII registers for function control and status report (see Section4.0 on page).The management frame format is compliant to IEEE802.3u clause 22, and the device ID is fixed to 5’h1f internally.3.10 LED displayThe MTD658 implements three display modes, port RX activity, 10/100M domain collision, port parti-tion. The LED data pin LEDDAT is high actived.One strobe pin LEDCLK(24 burst clock/per 42ms) is used to latch serial LEDDAT information, and user can shift the latched data into byte aligned shift register to drive LEDs.4.0 RegistersThe MTD658 implements 3 MII registers, define as following tables:TABLE 1. MII registersREGBits Name R/W Descriptions Default NO0CtlReg0R/W CONTROL REGISTER 00Reserved.1’b01DisPar10Set this bit will disable 10M hub core partition function.1’b02DisPar100Set this bit will disable 100M hub core partition function.1’b03DisJab10Set this bit will disable 10M hub core Jabber function.1’b04DisJab100Set this bit will disable 100M hub core Jabber function.1’b05-8Reserved4’b000TECHNOLOGY"R/W" means read/writable.10CClimit10Set "1" will program 10M partition cclimit to 64.1’b0(32)11-15Reserved 2’b001CtlReg1R/W CONTROL REGISTER 116’h00000-7DisPortSet bits "1" disable port 0-7 RMII ports.8’h0008-15Reserved.2Reserved 3Reserved4AgeRegR/W AGE REGISTERTABLE 1. MII registers REG NOBits Name R/WDescriptionsDefaultTECHNOLOGY5.0 Electrical Characteristics5.1 Absolute Maximum Ratings5.2 Recommended Operating Conditions5.3 DC Electrical Characteristics(Under recommended operating conditions and Vcc = 4.75 ~ 5.25V, Tj = 0 to +115 o C)Symbol Parameter RATINGUnit V CC Power Supply Voltage -0.3 to 6.0V V IN Input Voltage -0.3 to Vcc+0.3V V OUT Output Voltage -0.3 to Vcc+0.3VT STGStorage Temperature-55 to 150οCSymbol ParameterMin.Typ.Max.Unit V CC Commercial Power Supply Voltage 4.755 5.25V Industrial Power Supply Voltage 4.55 5.5V V IN Input Voltage0-Vcc VT OPRCommercial Junction Operating Temperature 025115οC Industrial Junction Operating Temperature-4025125οCSymbol Parameter Conditions Min.Typ.Max.Unit I IL Input Leakage Current no pull-up or down-11uA I OZ Tri-state Leakage Current -1010uA C IN Input Capacitance 3pF C OUT Output Capacitance3pF C BID3Bi-direction buffer Capacitance 3pF V IL Input Low Voltage CMOS0.3*Vcc V V IH Input High Voltage CMOS 0.7*VccV V OH Output High Voltage I OL =2,4,8,12,16,24mA 0.4V V OL Output Low VoltageI OH =2,4,8,12,16,24mA 3.5V R IInput Pull-up/down resistanceV IL =0V or V IH =V CC50KOhmTECHNOLOGY5.4 Electrical CharacteristicsSymbol ParameterMin.Typ.Max.Unit NoteT1RMII input setup time 1nS T2RMII input hold time 1nS T3RMII output setup time 3nS T4RMII output hold time 5nSSymbol ParameterMin.Typ.Max.Unit NoteT5WEB pulse width 11.516nS T6OEB pulse width20nS T7Write Address setup time 1018.5nS T8Write Address hold time 1.57nS T9Write Data setup time 1012nS T10Write Data hold time14nS T11Read Address setup time 19.5nS T12Read Address hold timenSFIGURE 1. RMII timingREFCLK CRSDV TXEN TXD[1:0]RXD[1:0]T1T2T3T4Valid ValidFIGURE 2. Memory Interface TimingWEB A[16:0]T9T5T7T8ValidOEB T6ValidD[7:0]ValidValidT10T11T12TECHNOLOGYNote 1 : In 10M/100M Inter-Bus interface, T15-T18 have the same value.Symbol Parameter Min.Typ.Max.Unit NoteT13Inter-Bus output setup time(100M)1520nS Inter-Bus output setup time(10M)50nS T14Inter-Bus output hold time(100M)2025nS Inter-Bus output hold time(10M)50nSSymbol ParameterMin.Typ.Max.Unit Note T15Inter-Bus master REQOUT asserted to IACKB asserted propogation delay 720nS 1T16Inter-Bus master REQOUT deas-serted to IACKB deasserted propo-gation delay15nS1T17Inter-Bus master REQIN asserted to IACKB deasserted(ICOLB asserted) propogation delay(SOJ)517nS 1T18Inter-Bus master REQOUT deas-serted to IACKB asserted(ICOLBde-asserted) propogation delay(EOJ)015nS 1FIGURE 3. Inter-Bus Interface timing IICLK100,T13T14IDATA100,ValidIDAT10ICLK10FIGURE 4. Inter-Bus Interface timing IIIMASTER REQOUT100,REQIN100,IACKB100,ICOLB100,T15T17T16T18REQOUT10REQIN10IACKB10ICOLB10TECHNOLOGYNote 2 : In 10M/100M Inter-Bus interface, T19-T22 have the same value.Symbol ParameterMin.Typ.Max.Unit Note T19Inter-Bus slave REQOUT asserted to IACKB asserted propogation delay 520nS 2T20Inter-Bus slave REQOUT deasserted to IACKB deasserted propogation delay520nS2T21Inter-Bus slave REQIN asserted to IACKB deasserted(ICOLB asserted) propogation delay(SOJ)520nS 2T22Inter-Bus slave REQOUT deasserted to IACKB asserted(ICOLBdeas-serted) propogation delay(EOJ)520nS 2Symbol Parameter Min.Typ.Max.Unit NoteT23MDC clock cycle 400nS T23MDIO input setup time10nSFIGURE 5. Inter-Bus Interface timing IIIIMASTER REQOUT100,REQIN100,IACKB100,ICOLB100,T19T21T20T22REQOUT10REQIN10IACKB10ICOLB10FIGURE 6. MII Management timing MDC T24T25MDIOValidMDC T26T27MDIOValidT23Input TimingOutput TimingTECHNOLOGYT25MDIO input hold time 10nS T26MDIO output setup time 182194nS T27MDIO output hold time206218nSSymbol ParameterMin.Typ.Max.Unit NoteT2824 LED burst clocks duration 3.84uS T29LED burst clock cycle time 42mS T30LED burst clock cycle160nS T31LEDDAT to LEDCLK setup time 80nS T32LEDDAT to LEDCLK setup time80nSSymbol Parameter Min.Typ.Max.Unit NoteFIGURE 7. LED output timingLEDCLKLEDDAT........LEDCLKT28T29T30T31T32TECHNOLOGY6.0 128 pin PQFP Package Data103128138396465102eBD 1DE 1Eper side.. Total in excess of the B dimemsion at maximum material Symbol Dimension in inch Dimension in mm Min Norm Max Min Norm Max A --0.134-- 3.40A10.010--0.25--A20.1070.1120.1172.73 2.85 2.97B 0.0070.0090.0110.170.220.27C 0.004-0.0080.09-0.20D 0.9060.9130.92123.0023.2023.40 D 10.7830.7870.79119.9020.0020.10E0.6690.6770.68517.0017.2017.40 E 10.5470.5510.55513.9014.0014.10e 0.020 BSC 0.50 BSC L0.0290.0350.0410.730.88 1.03L10.063 BSC 1.60 BSCy --0.004--0.10z0o-7o0o -7o。

HM65芯片组所支撑的一切的CPU型号[优质文档]

![HM65芯片组所支撑的一切的CPU型号[优质文档]](https://img.taocdn.com/s3/m/90bd63ceac51f01dc281e53a580216fc700a53a3.png)

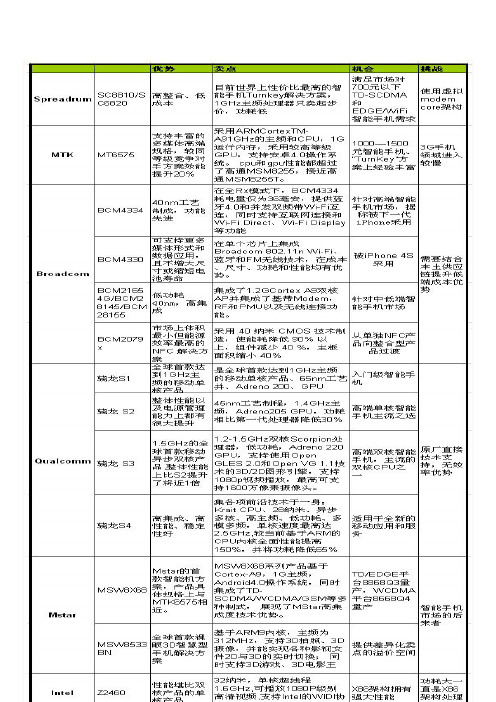

HM65芯片组所支持的所有的CPU型号(HM67 QM67好像也支持)第二代智能英特尔® 酷睿™ i7 处理器第二代智能英特尔® 酷睿™ i5 处理器第二代智能英特尔® 酷睿™ i3 处理器英特尔® 奔腾® 处理器英特尔® 赛扬® 处理器第二代智能英特尔® 酷睿™ i3 移动式处理器处理器号高速缓存时钟速度内核数 / 线程数最大散热设计功耗(TDP)内存类型英特尔® 核芯显卡32 nmi3-2370M 3.0 MB 2.40 GHz 2 / 4 35 W DDR3-1066/1333i3-2367M 3.0 MB 1.40 GHz 2 / 4 17 W DDR3-1066/1333i3-2357M 3.0 MB 1.30 GHz 2 / 4 17 W DDR3-1066/1333i3-2350M 3.0 MB 2.30 GHz 2 / 4 35 W DDR3-1066/1333i3-2330M 3.0 MB 2.20 GHz 2 / 4 35 W DDR3-1066/1333i3-2330E 3.0 MB 2.20 GHz 2 / 4 35 W DDR3-1066/1333i3-2312M 3.0 MB 2.10 GHz 2 / 4 35 W DDR3-1066/1333i3-2310M 3.0 MB 2.10 GHz 2 / 4 35 W DDR3-1066/1333第二代智能英特尔® 酷睿™ i5 移动式处理器处理器号高速缓存时钟速度内核数 / 线程数最大散热设计功耗(TDP)内存类型英特尔® 核芯显卡32 nmi5-2557M 3.0 MB 1.70 GHz 2 / 4 17 W DDR3-1066/1333i5-2540M 3.0 MB 2.60 GHz 2 / 4 35 W DDR3-1066/1333i5-2537M 3.0 MB 1.40 GHz 2 / 4 17 W DDR3-1066/1333i5-2520M 3.0 MB 2.50 GHz 2 / 4 35 W DDR3-1066/1333i5-2510E 3.0 MB 2.50 GHz 2 / 4 35 W DDR3-1066/1333i5-2467M 3.0 MB 1.60 GHz 2 / 4 17 W DDR3-1066/1333i5-2450M 3.0 MB 2.50 GHz 2 / 4 35 W DDR3-1066/1333i5-2435M 3.0 MB 2.40 GHz 2 / 4 35 W DDR3-1066/1333i5-2430M 3.0 MB 2.40 GHz 2 / 4 35 W DDR3-1066/1333i5-2410M 3.0 MB 2.30 GHz 2 / 4 35 W DDR3-1066/1333第二代智能英特尔® 酷睿™ i7 移动式处理器处理器号高速缓存时钟速度内核数 / 线程数最大散热设计功耗(TDP)内存类型英特尔® 核芯显卡32 nmi7-2860QM8.0 MB 2.50 GHz 4 / 8 45 W DDR3-1066/1333/1600i7-2820QM8.0 MB 2.30 GHz 4 / 8 45 W DDR3-1066/1333/1600i7-2760QM 6.0 MB 2.40 GHz 4 / 8 45 W DDR3-1066/1333/1600i7-2720QM 6.0 MB 2.20 GHz 4 / 8 45 W DDR3-1066/1333/1600i7-2710QE 6.0 MB 2.10 GHz 4 / 8 45 W DDR3-1066/1333/1600i7-2677M 4.0 MB 1.80 GHz 2 / 4 17 W DDR3-1066/1333i7-2675QM 6.0 MB 2.20 GHz 4 / 8 45 W DDR3-1066/1333i7-2670QM 6.0 MB 2.20 GHz 4 / 8 45 W DDR3-1066/1333i7-2657M 4.0 MB 1.60 GHz 2 / 4 17 W DDR3-1066/1333i7-2649M 4.0 MB 2.30 GHz 2 / 4 25 W DDR3-1066/1333i7-2640M 4.0 MB 2.80 GHz 2 / 4 35 W DDR3-1066/1333i7-2637M 4.0 MB 1.70 GHz 2 / 4 17 W DDR3-1066/1333i7-2635QM 6.0 MB 2.00 GHz 4 / 8 45 W DDR3-1066/1333i7-2630QM 6.0 MB 2.00 GHz 4 / 8 45 W DDR3-1066/1333i7-2629M 4.0 MB 2.10 GHz 2 / 4 25 W DDR3-1066/1333i7-2620M 4.0 MB 2.70 GHz 2 / 4 35 W DDR3-1066/1333i7-2617M 4.0 MB 1.50 GHz 2 / 4 17 W DDR3-1066/1333。

基于控制器L6585的58W双T8灯管电子镇流器

测 ( C 信号 。 Z D)

控 制器 和 Q1 Q2等 组成 半 桥 式 逆 变 器 电 、

L 、 2 、 9和 L 、 2 、 1 2 C 9 C 4等 分 别组 当 Q3导 通 时 , 2截 止 , 过 L F 路 。 1 C 8 C D 通 P C1

( 1)输 入级 电路 :图 3中 ,电感器 的 电流 通 过 Q 3和 R 2返 回 桥 式 整 流 器 成 串联谐 振式输 出电路, 2 两根灯 管并联连 L F 2和 电容 C1 、 1 、 4 C 0组成输 负端 ; Q3关 断 时 , 2导 通 , PC C C 、 2 O 1 当 D 电流 对 P C 接在镇 流器输 出端。Q2源极连接 的 R 1 F 3

压 和 反馈 开 路 保 护 。

灯 管 , 输 入 功 率 因 数 P > 8 , F 09 5 功 能

表 1 68 L 5 5引 脚 功 能 引脚 号 符 号

1

2 3

4 5

OS C

R F E OI

TH C E P 0L

从该端到地 ( D) 接一 个电容 , GN 连 用作 设置半桥开关频率。

可编程 灯寿终 1引 脚 功 能 L 5 5采 用 2 . 68 O引 脚 S 制和半桥过 电流保护功 能, O 灯 封装 , 引脚 排 列 如 图 1所 示 。 L 5 5的 各 保护与各种镇流器兼容 。在灯 未接入、 68 脱 落 或 灯 失 效 等 情 况 下 , 灯 接 入 或 灯 管 在 个 引 脚 功 能 如 表 1所 示 。

换 模 式 , 乘 法 器 含 有 输 入 电流 总谐 波 失 流 器 电 路 的 交 流 输 出 电 压 范 围 为 其 真最 小化 电路。 P C控制器提供过流 、 F 过 8 ~ 6 V,输 出驱 动 两 个 5 W 的并 联 T 525 8 8

LMV652MM中文资料

45

50

60

mV from

95

110

rail

125

RL = 10 kΩ to V+/2

60

65

75

ISC

Maximum Continuous Output

Sourcing (Note 8)

Current

Sinking (Note 8)

17 mA

25

IS

Supply Current per Amplifier

76

dB

0.3 ≤ VO ≤ 2.7, RL = 10 kΩ to V+/2

86

93

0.4 ≤ VO ≤ 2.6, RL = 10 kΩ to V+/2

83

VO

Output Swing High

RL = 2 kΩ to V+/2

80

95

120

Output Swing Low

RL = 10 kΩ to V+/2 RL = 2 kΩ to V+/2

f = 100 kHz f = 1 kHz f = 1 kHz, AV = 2, RL = 2 kΩ

Min (Note 5)

Typ (Note 4)

0.1 0.15 0.003

Max (Note 5)

Units

pA/ %

5V DC Electrical Characteristics

Unless otherwise specified, all limits are guaranteed for TJ = 25°C, V+ = 5V, V− = 0V,VO = VCM = V+/2, and RL > 1 MΩ. Boldface limits apply at the temperature extremes.

北京大华无线电仪器有限责任公司 2018产品目录说明书

2018PRODUCT CATALOG北京大华无线电仪器有限责任公司(简称:大华电子,原国营768厂),始建于1958年,2018年北京大华电子将迎来60岁华诞。

作为我国最早建成的微波测量仪器大型军工骨干企业,大华人以发展中国测量仪器工业为已任,专注于测试仪器行业,奋勇前行,不断创新。

目前产品已覆盖精密电子测量仪器、自动化测试系统、行业应用解决方案等数百种产品,并广泛应用于军工、科研、高校、通讯、工业控制、汽车电子、新能源等领域。

作为国产测量仪器行业的首创者和领航者,在过去60年间,大华人为客户提供了高质量产品和服务,同时,也为行业的培育、规范、发展做出了自己应有的贡献。

近年来,随着市场需求的不断升级和市场竞争的不断加剧,大华人持续创新,主动求变,引领和推进产业升级。

深入学习贯彻党的十九大精神,“不忘初心,牢记使命”,大华将传承多年的行业经验,通过研发平台升级,致力于高端测量仪器的开发和新行业的测试解决方案的拓展,为新老客户提供全方位的服务。

2018年,将是大华人新的起点,我们将深入持续创新,全面升级迎发展,继续与终端客户、合作伙伴紧密合作,加强军民融合和产学研深度融合,不断推进民用测试仪器的研制开发和高校研究成果的转化,进一步为工业市场提供更具稳定实用的仪器设备及解决方案,为国防建设、电子测量仪器事业的发展做出更大的贡献。

可靠性设计:简化、冗余设计并采用成熟技术方案,MTTF≥5000hrs。

维修性:采用单元模块化设计,便于拆卸、安装,对部件标准化设计,增加产品的互换性。

MTTR≦30min。

保障性:提供全套设备维修手册,并按需为使用及维修人员开展专业培训。

测试性:简化测试及调试设计,提高软件自检功能,提高测试效率。

安全性:确保无害输出,无易碎材质,产品在使用及损坏时不会造成人身伤害。

环境适应性:全部优选合格供应商产品,电子元器件筛选并降额使用。

交、直流分离设计,并采用有效材料增加电磁屏蔽效果。

LMH6715中文资料