从设置、加载、启动看Xilinx FPGA配置流程

FPGA开发基本流程有哪些

FPGA开发基本流程有哪些FPGA(Field-Programmable Gate Array)开发基本流程包括如下步骤:1.系统设计和规划:在FPGA开发之前,需要先进行系统设计和规划。

这一步骤主要包括确定系统需求,定义FPGA的功能和规格。

还需要对应用程序进行综合和分析,以便确定FPGA硬件设计的具体要求。

2. 硬件描述语言编码:在确定FPGA的功能和规格后,接下来需要使用硬件描述语言(例如VHDL或Verilog)编写相应的代码。

这些代码描述了FPGA的逻辑电路结构和功能。

3.仿真验证:编写完硬件描述语言代码后,需要进行仿真验证以确保设计的正确性。

在仿真环境中,可以通过输入测试向量和模拟环境来测试硬件描述语言代码的行为和功能。

这一步骤可以帮助发现设计中的错误和问题,并进行修正和优化。

4. 综合和布局布线:在FPGA开发过程中,综合是将硬件描述语言代码转换为逻辑网表的过程。

综合工具将代码进行逻辑优化和合成,并生成FPGA所需的逻辑网表。

布局布线是将逻辑网表映射到FPGA的物理资源上,包括逻辑单元(Look-Up Tables,LUT)、寄存器、连线等。

5.静态时序分析:在FPGA设计中,对时序要求十分重要。

在静态时序分析过程中,使用时序分析工具来评估FPGA设计是否满足时序要求。

通过对逻辑延迟、时钟频率等进行分析,可以确保FPGA在工作时满足正确的时序要求。

7.优化和迭代:在完成FPGA开发和调试后,可能需要对设计进行进一步的优化和迭代。

通过对性能和资源的分析,可以针对性地优化设计,提高FPGA的性能和效率。

Xilinx-FPGA配置的一些细节

Xilinx-FPGA配置的一些细节Xilinx FPGA配置的一些细节2010年07月03日星期六 14:260 参考资料(1) Xilinx: Development System Reference Guide. dev.pdf, v10.1在Xilinx的doc目录下有。

(2) Xilinx: Virtex FPGA Series Configuration and Readback. XAPP138 (v2.8) March 11, 2005在Xilinx网站上有,链接/bvdocs/appnotes/xap p138.pdf(3)Xilinx: Using a Microprocessor to Configure Xilinx FPGAs via Slave Serial or SelectMAP Mode.XAPP502 (v1.5) December 3, 2007在Xilinx网站上有,链接/bvdocs/appnotes/xap p502.pdf注:此外xapp139和xapp151也是和配置相关的。

(4)Xilinx: Virtex-4 Configuration Guide. UG071 (v1.5) January 12, 2007(5) Tell me about the .BIT file format.链接:/FAQ_Pages/0026_Tell_me_about_bit_files.htm1 Xilinx配置过程主要讲一下Startup Sequence。

Startup Sequence由8个状态组成.除了7是固定的之外,其它几个的顺序是用户可设置的,而且Wait for DCM和DCI是可选的。

其中默认顺序如下:这些在ISE生成bit文件时通过属性页设定。

这几个状态的具体含义如下:Release_DONE : DONE信号变高GWE : 使能CLB和IOB,FPGA的RAMs和FFs可以改变状态GTS : 激活用户IO,之前都是高阻。

fpga的设计流程

fpga的设计流程

随着技术的发展,fpga设计技术也变得越来越成熟,越来越多的产品使用fpga进行控制,它们可以被用来实现很多种复杂的功能,但是在使用之前,需要进行一个系统的设计流程。

本文将对fpga的设计流程进行详细的介绍,帮助用户更好的实现fpga的功能。

首先,在使用fpga之前,用户需要确定fpga的目标功能,也就是要实现什么样的功能,这一步可以粗略的定义出完成的任务,也就是fpga的功能的架构。

其次,编写fpga的硬件结构,这一步要求用户熟悉fpga的硬件结构,以及fpga可以实现的功能结构,确定硬件结构后,可以使用EDA工具进行搭建。

第三,使用 HDL(硬件描述语言)进行编程,这一步是实现fpga 功能的关键,用户需要使用HDL,也就是Verilog或者VHDL来编写代码,使用这些语言来编写硬件电路及对应的功能,以完成fpga功能的部署和调试。

第四,使用仿真工具仿真和调试,完成了上述步骤后,用户可以使用仿真工具,仿真fpga的硬件结构,以及编写好的代码,以便发现硬件和软件的错误,以及调试软件程序以确保功能正常。

第五,烧录fpga,经过仿真和调试,用户需要将fpga烧录成fpga 芯片,这一步需要使用烧录器,将编写的程序烧录到fpga芯片,以实现fpga的功能。

第六,测试功能,最后,用户需要测试实现的功能是否符合预期。

以上就是fpga的设计流程,从fpga的功能定义到实际实现,需要涉及很多步骤,需要用户对fpga充分的了解,以此来确保设计的正确性和合理性。

简述fpga的开发流程

简述fpga的开发流程

简述FPGA的开发流程

FPGA开发流程是由一系列相关步骤组成的。

它可以分为前期设计环境的构建、FPGA及外围电路的设计、FPGA编程、系统烧写和调试等五个主要步骤。

一、构建设计环境

首先,需要构建FPGA的设计环境,安装设计软件,如Xilinx ISE、Quartus等,这些软件可以支持FPGA设计,建立设计环境,提供设计使用。

紧接着,对开发板进行硬件测试,检查硬件是否正常可用,以确保下一步无硬件问题,提高开发效率。

二、FPGA及外围电路设计

接下来进行FPGA及外围电路的设计,设计者可以根据具体需求,使用Verilog HDL或VHDL等语言编写FPGA及外围电路的原理图,经过仿真,验证无误后,进入下一步。

三、FPGA编程

在FPGA及外围电路设计完成后,就可以进行FPGA的编程,即将设计好的原理图编译为FPGA的可烧写文件,如.JED、.BIN等,此时可以使用烧录器进行FPGA编程,将编译加载到目标FPGA芯片中。

四、系统烧录

编程完成后,FPGA芯片可以正常工作,此时需要将系统烧录到FPGA上,使其和外围电路组成完整的系统,以满足应用需求。

五、调试

最后一步是进行系统的调试,这个步骤并不仅仅是测试芯片本身,而是测试整个系统的功能,确保系统能够按照预期工作。

通过以上步骤即可完成FPGA的开发。

FPGA配置方式及过程

1 FPGA器件有三类配置下载方式:主动配置方式(AS)和被动配置方式(PS)和最常用的(JTAG)配置方式。

主动串行(AS)由FPGA器件引导配置操作过程,它控制着外部存储器和初始化过程,EPCS系列.如EPCS1,EPCS4配置器件专供AS模式,目前只支持Stratix II 和Cyclone系列。

使用Altera串行配置器件来完成。

Cyclone器件处于主动地位,配置器件处于从属地位。

配置数据通过DA TA0引脚送入FPGA。

配置数据被同步在DCLK输入上,1个时钟周期传送1位数据。

AS配置器件是一种非易失性、基于flash存储器的存储器,用户可以使用altera的ByteBlaster II 加载电缆、altera的“altera programming unit”或者第三方的编程器来对配置芯片进行编程。

它与FPGA的接口为以下简单的4个信号线:. 串行时钟输入(DCLK):是在配置模式下FPGA内部的振荡器(oscillator)产生的,在配置完成后,该振荡器将被关掉。

工作时钟在20MHz左右,而fast AS方式下(stratix II和cyclone II支持该种配置方式),DCLK时钟工作在40MHz左右,在altera的主动串行配置芯片中,只有EPCS16和EPCS64的DCLK可以支持到40MHz,EPCS1和EPCS4只能支持20MHz。

. AS控制信号输入(ASDI). 片选信号(nCS);. 串行数据输出(DATA)。

多片配置:控制配置芯片的FPGA为“主”,其后面的FPGA为“从”。

主片的nCE需要直接接地,其nCEO输出脚驱动从片的nCE,而从片的nCEO悬空,nCEO脚在FPGA未配置时输出为低。

这样,AS配置芯片中的配置数据首先写到主片的FPGA中,当其接收到它的所有的配置数据以后,随即驱动nCEO信号为高,使能从片的FPGA,这样配置芯片后面的读出的数据将被写入到从片的FPGA中。

fpga基本设计流程

fpga基本设计流程一、概述FPGA(Field Programmable Gate Array)是一种可编程逻辑器件,具有可重构性和灵活性,可以根据设计需求进行编程。

FPGA的设计流程包括设计规划、硬件描述语言编写、综合、实现和验证等步骤。

二、设计规划1.确定设计目标:明确设计的功能需求和性能指标。

2.确定芯片型号:选择适合自己需求的FPGA芯片型号。

3.确定开发平台:选择合适的开发平台,如Vivado、Quartus等。

4.制定设计计划:根据时间和资源情况,制定详细的设计计划。

三、硬件描述语言编写1.选择HDL语言:常用的HDL语言有Verilog和VHDL,根据个人喜好选择一种。

2.编写模块代码:按照模块化思想,将整个系统分为多个模块,并分别进行代码编写。

3.进行仿真测试:通过仿真工具对模块进行测试,确保其功能正确性。

四、综合1.添加约束条件:在综合前需要添加时序约束条件,以保证电路时序正确性。

2.进行综合:使用综合工具将HDL代码转换为门级电路网表,并进行优化处理。

3.查看综合报告:查看综合报告,了解电路资源使用情况和时序等信息。

五、实现1.进行布局:将门级电路网表映射到FPGA芯片的逻辑单元上,并进行布局。

2.进行布线:在逻辑单元之间进行连线,以实现电路功能。

3.生成比特流文件:将电路设计转换为比特流文件,用于后续下载到FPGA芯片上运行。

六、验证1.下载比特流文件:将生成的比特流文件下载到FPGA芯片上运行。

2.进行功能验证:通过工具或外部设备对系统进行功能验证,确保其能够正常工作。

3.进行时序验证:对系统时序进行验证,以确保其满足约束条件和性能指标要求。

七、总结以上就是FPGA基本设计流程的详细步骤。

在实际设计过程中,还需要不断优化和调试,以达到最佳性能和效果。

FPGA基本设计流程

FPGA基本设计流程FPGA(Field-Programmable Gate Array)是一种可编程逻辑设备,提供了一种将数字电路设计和实现的灵活性。

FPGA的设计流程包括以下几个基本步骤。

1.确定需求:在进行FPGA设计之前,首先需要明确设计的需求和目标。

这可能包括功能要求、性能要求、资源限制等。

例如,设计一个图像处理器需要明确需要支持的图像处理算法以及所需的带宽和延迟要求。

2. 设计硬件:设计师需要根据需求来设计硬件电路。

这通常涉及使用硬件描述语言(HDL)如Verilog或VHDL来描述电路的功能和行为。

设计师需要根据需求将整个电路划分为各个模块,并对每个模块进行详细的设计。

3.模块级仿真:在进行整体设计之前,设计师通常会进行模块级的仿真来验证每个模块的功能和正确性。

这可以通过在仿真工具中编写测试向量来模拟不同的输入情况,并验证模块的输出是否符合预期。

4.整体设计:设计师需要将各个模块进行整合,构成整体的FPGA设计。

这通常包括将各个模块连接起来,并添加必要的控制电路和接口电路。

整体设计完成后,设计师需要进行整体仿真来验证整个电路的功能和正确性。

5.综合和约束:综合是将HDL代码转换为FPGA中的逻辑网表的过程。

在综合之前,设计师需要设置约束条件,如时钟频率、时序要求等。

这些约束条件可以帮助综合工具生成更好的逻辑网表。

6.布局和布线:布局是将逻辑网表中的逻辑元素映射到FPGA的可编程逻辑单元(PLD)中的过程。

在布局之后,设计师需要对各个逻辑元素进行布线,即将FPGA中的各个逻辑元素之间进行连线。

布局和布线的目标是尽量减少功耗、延迟和资源占用等指标。

7.物理仿真:在完成布局和布线后,设计师需要进行物理仿真来验证电路的时序和功耗等物理特性。

物理仿真通常使用时序分析工具和功耗分析工具来分析电路的性能和功耗。

FPGA开发流程介绍及实例讲解

FPGA开发流程介绍及实例讲解FPGA(Field Programmable Gate Array)是一种可编程逻辑设备,可以自定义电子电路的功能。

它具有灵活性和可重构性,可用于设计和开发各种电子系统,例如数字信号处理、通信系统、图像处理等。

本文将介绍FPGA开发的流程,并通过一个实例来解释每个步骤。

1.系统设计:在系统设计阶段,项目需求和功能被定义和规划,包括电路的输入输出、算法和处理步骤。

2. 硬件描述语言编程:在FPGA开发中,常用的硬件描述语言包括VHDL(Very high-speed integrated circuit Hardware Description Language)和Verilog。

开发者使用这些语言编写硬件描述代码,定义电路逻辑和内部连接。

3.仿真和验证:在该阶段,开发者利用仿真工具对硬件描述代码进行验证,以确保其正确性和预期功能。

仿真工具可以模拟电路行为并显示输出结果,帮助开发者找到潜在的问题并进行修复。

4.综合和布局布线:在综合阶段,硬件描述代码被综合为逻辑门级别的网表,而在布局布线阶段,逻辑门被映射为FPGA的物理资源。

这两个步骤由综合工具和布局布线工具自动完成。

现在,我们通过一个实例来演示上述FPGA开发流程。

假设我们要设计一个简单的4位计数器,该计数器每秒钟递增一个数字。

1.系统设计:我们定义计数器的输入为时钟信号(用于同步计数器),输出为4位二进制计数值。

2.硬件描述语言编程:我们使用VHDL来编写硬件描述代码。

以下是一个简单的VHDL代码示例:```library ieee;use ieee.std_logic_1164.all;use ieee.numeric_std.all;entity counter isportclk : in std_logic;count_out : out std_logic_vector(3 downto 0)end entity counter;architecture rtl of counter issignal count : unsigned(3 downto 0);beginprocess(clk)beginif rising_edge(clk) thencount <= count + 1;end if;end process;count_out <= std_logic_vector(count);end architecture rtl;```3.仿真和验证:我们使用VHDL仿真器来验证代码。

fpga配置过程(转载)

fpga配置过程(转载)fpga 配置时序图如下1.FPGA器件有三类配置下载⽅式:主动配置⽅式(AS)和被动配置⽅式(PS)和最常⽤的(JTAG)配置⽅式。

AS 由FPGA器件引导配置操作过程,它控制着外部存储器和初始化过程,EPCS系列.如EPCS1,EPCS4配置器件专供AS模式,⽬前只⽀持 Stratix II 和Cyclone系列。

使⽤Altera串⾏配置器件来完成。

Cyclone器件处于主动地位,配置器件处于从属地位。

配置数据通过DATA0引脚送⼊ FPGA。

配置数据被同步在DCLK输⼊上,1个时钟周期传送1位数据。

PS(被动串⾏)则由外部计算机或控制器控制配置过程。

所有altera FPGA都⽀持这种配置模式。

通过altera 的下载电缆、加强型配置器件(EPC16,EPC8,EPC4)等配置器件或智能主机(如微处理器和CPLD)来完成,在PS配置期间,配置数据从外部储存部件(这些存储器可以是altera配置器件或单板上的其他flash器件),通过DATA0引脚送⼊FPGA。

配置数据在DCLK上升沿锁存,1个时钟周期传送1位数据。

FPP(快速被动并⾏):该配置模式只有在stratix系列和APEX II中⽀持;PPA(被动并⾏异步):该配置模式在stratix 系列、APEX II、APEX 20K、mercury、ACEX 1K和FLEX 10K中⽀持;PPS(被动并⾏同步):这种模式只有⼀些较⽼的器件⽀持,APEX II、APEX 20K、mercury、ACEX 1K和FLEX 10K。

PSA(被动串⾏异步):只有在FLEX 6000器件中⽀持。

JTAG接⼝是⼀个业界标准,主要⽤于芯⽚测试等功能,使⽤IEEE Std 1149.1联合边界扫描接⼝引脚,⽀持JAM STAPL标准,可以使⽤Altera下载电缆或主控器来完成。

FPGA配置过程:在FPGA正常⼯作时,配置数据存储在SRAM中,这个SRAM单元也被称为配置存储器(configure RAM)。

Xilinx公司FPGA配置方法分析及实现

电子质量2020年第08期(总第401期)作者简介:王莹莹(1986-),女,中级电子工程师,硕士研究生,从事电子研发工作。

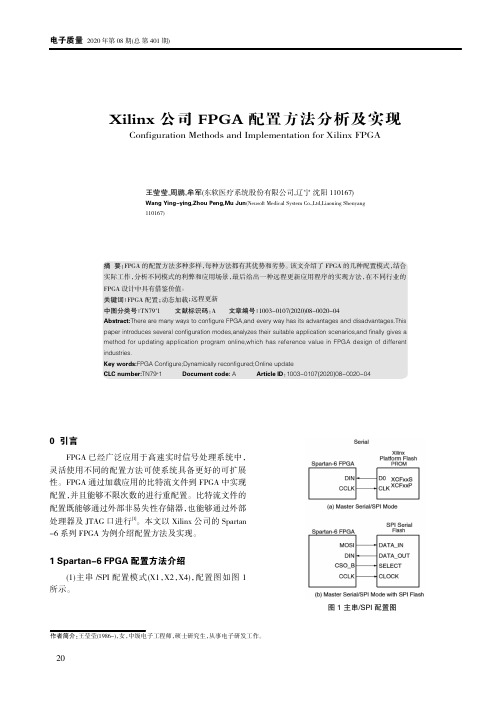

Xilinx 公司FPGA 配置方法分析及实现Configuration Methods and Implementation for Xilinx FPGA王莹莹,周鹏,牟军(东软医疗系统股份有限公司,辽宁沈阳110167)Wang Ying-ying,Zhou Peng,Mu Jun (Neusoft Medical System Co.,Ltd,Liaoning Shenyang 110167)摘要:FPGA 的配置方法多种多样,每种方法都有其优势和劣势。

该文介绍了FPGA 的几种配置模式,结合实际工作,分析不同模式的利弊和应用场景,最后给出一种远程更新应用程序的实现方法,在不同行业的FPGA 设计中具有借鉴价值。

关键词:FPGA 配置;动态加载;远程更新中图分类号:TN79+1文献标识码:A文章编号:1003-0107(2020)08-0020-04Abstract:There are many ways to configure FPGA,and every way has its advantages and disadvantages.This paper introduces several configuration modes,analyzes their suitable application scenarios,and finally gives a method for updating application program online,which has reference value in FPGA design of different industries.Key words:FPGA Configure;Dynamically reconfigured;Online update CLC number:TN79+1Document code:AArticle ID :1003-0107(2020)08-0020-040引言FPGA 已经广泛应用于高速实时信号处理系统中,灵活使用不同的配置方法可使系统具备更好的可扩展性。

xilinx使用步骤

Xilinx软件使用步骤目录基本操作1. 打开xilinx2. open project3. New project4. 创建新的 .vhd文件5. 建立波形文件6. 综合7. 仿真8. 下载程序到电路板中需要注意的问题1.生成顶层原理图2.建立.ucf文件3. implement时出错的原因4.仿真时的问题基本操作1. 打开xilinx图1 打开xilinx界面2. open project图2 open project图3 查找要打开的.ise文件单击打开后,出现在左侧box中。

图4 open project3. New project顶层文件类型,原理图类型选Schematic,否则选择HDL;单击下一步,通过右侧value各项目,配置器件类型,即FPGA 型号。

注意:此处配置错误的话,综合时会出现放不下或者些不进去的错误。

配置完成后,单击下一步,出现创建源文件对话框如下图所示。

不需做设置更改,直接点击下一步,出现添加现有源对话框如下图所示。

不需做任何设置,直接单击下一步,出现New project information对话框,如下图所示。

确认信息无误后,单击完成,创建的新的project即出现在主页面左侧Sources in project中,如下图所示。

4. 创建新的 .vhd文件右击主页面左侧Sources in project中xc2s200-5pq208,在右键菜单中选择New source,如下图所示;出现New source对话框;左侧选择VHDL Module,右侧输入文件名,如下图所示,单击下一步;出现define vhdl source对话框,输入端口名,输入输出类型和MSB,LSB, 如下图所示,然后单击下一步,出现信息对话框,如下图所示,确认无误后,单击完成。

然后主页面如下图所示:5. 建立波形文件在主页面,编程之后保存。

在如下图所示位置右击.vhd文件,选择new source选项。

XilinxFPGA 的power-up配置和 start-up过程

Xilinx FPGA的power-up配置和 start-up过程FPGA的配置分为3步,1.清除配置SRAM2.下载配置数据3. Start-up过程激活逻辑Power-up配置从上图可见,配置在FPGA上电时自动进行。

上电后,FPGA自动开始清楚RAM的内容(此时,外围电路应使/program=1),清除RAM后,FPGA使/INIT变为无效,开始装载配置bit(如果保持/INIT信号有效,则可以延迟装载bit,INIT是双向端口)。

装载bit的过程中,FPGA会做CRC检查,发现错误则把/INIT信号拉低。

配置完成后done变高。

配置时序如下图所示。

也可以通过把/program置低开始(在不重新上电的情况下开始配置FPGA)对Xilinx FPGA的配置有四个主要步骤(不重新上电的情况下开始配置FPGA):(1)配置存储器清空(Clearing Configuration Memory)将PROGRAM管脚拉低300ns以上。

当PROGRAM拉低后,开始配置存储器,将存储器清空。

此时INIT将被拉低,当PROGRAM置高后,FPGA将继续将INIT置低直到完全清除完所有的配置存储器。

当INIT变高时,配置便可以开始了。

(2)加载配置数据(Loading Configuration Data)当INIT变高时,便可以配置FPGA了。

配置时,先将CCLK置低,再将数据发送到DIN上,延时45ns以上,再将CCLK置高,该位数据便写入到了FPGA中(数据是低位在前),然后再准备下一次的输入。

如此反复,将所有数据输入完毕为止。

(3)CRC错误校验(CRC Error Checking)在加载数据过程中,嵌入到配置文件中的CRC值同FPGA计算出来的值比较,若有CRC 校验错误产生,则INIT置低,且FPGA停止加载。

Start-up过程默认的start-up过程在DONE信号变高并延迟一个CCLK后进行,此时global tri-state signal(GTS)信号释放,这样允许器件output打开。

fpga软件的使用流程

FPGA软件的使用流程1. 准备工作在开始使用FPGA软件之前,需要完成以下准备工作:•安装FPGA软件:根据硬件型号和供应商提供的资料,下载并安装相应的FPGA软件。

常见的FPGA软件包括Xilinx ISE、Altera Quartus等。

•学习基础知识:了解FPGA的基本原理,掌握HDL(硬件描述语言)的知识,例如Verilog或VHDL。

同时,理解FPGA的架构和工作流程也是必要的。

2. 创建新工程在使用FPGA软件之前,首先需要创建一个新的工程。

按照以下步骤进行:1.打开FPGA软件:双击桌面上的应用程序图标或通过开始菜单打开相应的应用程序。

2.选择“创建新工程”:在软件界面上找到“新建工程”或类似的选项,点击进入新工程界面。

3.命名工程:为工程命名,选择保存路径,并指定工程的类型(例如Xilinx或Altera)。

4.选择设备型号:根据所使用的FPGA硬件,选择相应的设备型号。

如果不清楚型号,可以参考FPGA供应商的技术手册或官方网站。

3. 设计RTL电路RTL(Register Transfer Level)是描述数字电路的一种方法,FPGA软件可以通过RTL描述用户的电路设计。

在设计RTL电路时,可以按照以下步骤进行:1.打开设计视图:在FPGA软件界面中,找到“设计视图”或类似选项,打开RTL设计界面。

2.添加模块:在设计界面上,选择“添加模块”或类似选项,将所需的模块添加到设计中。

3.连接模块:使用软件提供的连接工具,将各模块按照设计要求连接起来。

4.编写HDL代码:使用HDL语言(如Verilog或VHDL),编写每个模块的逻辑代码。

5.进行仿真:使用软件提供的仿真工具,对设计的RTL电路进行仿真验证。

4. 进行综合在完成RTL电路设计后,需要进行综合(Synthesis)操作,将RTL代码转化为FPGA支持的逻辑元件。

按照以下步骤进行:1.打开综合工具:在FPGA软件界面中,找到“综合”或类似选项,打开综合工具。

Xilinx FPGA开发环境的配置

Xilinx FPGA 开发环境的配置一、配置Modelsim ISE 的Xilinx 的仿真库1、编译仿真库:A、先将Modelsim 安装目录C=Modeltech_6.2b 下面的modelsim.ini 改成存档格式(取消只读模式);B、在DOS 环境中,进入Xilinx 的根目录,然后依次进入bin,nt 目录; C、compxlib -s mti_se -f all -l all -o C:Modeltech_6.2bxilinx_libs。

注意:需要根据你安装的modelsim 目录更改C:Modeltech_6.2b然后就Ok 了,就可以的ISE 中启动Modelsim 进行所有的仿真了。

2、如何在Xilinx ISE 中使用Modelsim ISE,Synplify 进行综合和仿真:A、打开Xilinx ISE,新建一个Project;①、在菜单File 中选择New Project,弹出如下的对话框:②、输入Project 名称,并选择好Project 保存的路径,然后下一步:按照上边的参数进行设置(针对于Spatan 3E 的开发板),然后单击下一步,进入到后面的界面:③、单击New Source 按钮,并按照下面的设置来操作:④、参照下面的参数,进行设置,然后一直选择默认选项,一直到完成。

最后生成的项目界面如下B、输入代码,然后用Synplify 综合:①、参考代码:entity Count iS Port(CLK :in STD_LOGIC; RESET :in STD_LOGIC; LOAD :in STD_LOGIC; DATA IN:in STD_LOGIC_VECTOR(3 downto 0); Qout :out STD_LOGIC_VECTOR(3 downto 0));end Count;architecture Behavioral of Count issignal。

FPGA的设计开发流程主要包括四个步骤设计输入

FPGA的设计开发流程主要包括四个步骤设计输入FPGA的设计开发流程主要包括四个步骤:设计输入(Design Entry)、逻辑综合(Logic Synthesis)、布局布线(Place and Route)和配置生成(Configuration Generation)。

下面将详细介绍每个步骤。

1.系统级设计:在此阶段,设计工程师需要定义系统的功能需求和性能要求,确定设计的输入输出接口,以及设计中需要使用的外设和IP核。

2.架构设计:在此阶段,设计工程师需要将系统级设计转化为硬件描述语言(HDL)的形式。

设计工程师需要使用HDL来描述系统的功能和行为,并将其分解为模块化的子系统。

3.模块级设计:在此阶段,设计工程师需要进一步细化模块的功能和行为,并将其转化为HDL的形式。

设计工程师需要定义每个模块的输入输出接口,并编写相应的HDL代码。

逻辑综合(Logic Synthesis)是将HDL代码转化为逻辑电路网表(logic circuit netlist)的过程。

逻辑综合工具会根据设计工程师的代码描述,将其转化为逻辑门级的电路。

在逻辑综合过程中,设计工程师可以进行优化和约束设置,以达到设计的性能和资源利用率要求。

布局布线(Place and Route)是将逻辑电路网表映射到FPGA芯片上的过程。

在布局布线过程中,设计工程师需要将逻辑电路网表中的逻辑元件(如逻辑门、寄存器等)放置到FPGA芯片的可用资源上,并通过信号线将它们连接起来。

布局布线工具会根据设计工程师的约束和优化目标,自动进行布局和布线的优化。

配置生成(Configuration Generation)是将布局布线后的电路转化为FPGA可执行的配置文件的过程。

配置文件包含了将电路映射到FPGA芯片上的信息,以及FPGA芯片的配置信息。

设计工程师可以使用配置生成工具将布局布线完成的电路转化为配置文件,并将其加载到FPGA芯片中进行验证和测试。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

从设置、加载、启动看Xilinx FPGA 配置流程

尽管FPGA 的配置模式各不相同,但整个配置过程中FPGA 的工作流程是一致的,分为三个部分:设置、加载、启动。

复位结束配置开始

有多种方式使FPGA 的配置进入这一过程。

在上电时,电压达到FPGA 要求之前,FPGA 的上电复位模块将使FPGA 保持在复位状态;外部控制PROG_B 引脚出现一个低脉冲也可以使FPGA 保持在复位状态。

清除配置存储内容

这一步称为初始化,当FPGA 复位结束,配置存储器的内容会被自动清除。

在这个步骤中,除配置专用接口外,FPGA I/O 均被置于高阻态。

在整个初始化过程中,INIT_B 引脚被置低并在初始化结束后恢复高电平。

如果INIT_B 信号在外部被拉低,FPGA 将一直停留在初始化状态。

注意PROG_B 信号的脉宽不能太窄。

采样控制信号

初始化结束后,INIT_B 信号回到高电平。

FPGA 开始采集模式选择引脚M[1:0]和变量选择引脚VS。

如果为主动模式,FPGA 很快就会给出有效的CCLK。

VS 信号只在主动BPI 及其SPI 模式中生效。

此时,FPGA 开始在配置时钟的上升沿对配置数据进行采样。

同步化

每一个FPGA 配置数据流都有一个同步头,它是一段特殊的同步字。

同步字主要用于帮助FPGA 确定正确的数据位置。

同步字之前的配置数据都会被FPGA 忽略,也就是FPGA 仅仅在同步化之后才正式开始接收配置数据。

一般而言,同步字都是由0/1 数目相同的二进制数组成的,如Spartan3 为。