controller设计说明文档

KEYTEC 控制器使用操作说明

1.2 系统产品规格表- KAC- 200 / 400 二 / 四门控制器

项目

操作电压 耗电功率 卡片容量 连结卡片阅读机数量 控制门区 联结卡片阅读机形式

规格

12 Vdc 400 mA 6000 张 8 台 (4 进、4 出) 2 / 4 道门(2 门以上需外接 DO 继电器模块) RS-485 格式

2. KAC- 200 / 400 控制器功能操作说明

2.1 控制器与管理计算机

控制器与管理计算机的联机是透过 RS-485/ USB 接口,使用 KAC-Module 传输接口而直接连接管理 计算机,

一台管理计算机最多可接 99 台控制器,其连接为并联方式(所有同颜色线接在一起)。从管理计算机 延伸出的 RS-485 传输线最长可至 1 公里。 注意:RS-485 传输线线材最好使用 AWG 18~22 # 计算机 RS-485 传输用遮蔽对绞线。

KEYTEC Controller & Operation Manual

KEYTEC

KAC-200 / 400 CONTROLLER

操作使用说明书

-1-

KEYTEC Controller & Operation Manual

目录 1. 概述

1.1 系统架构图 1.2 系统产品规格表 1.3 系统软/硬选 择 Control ID

Control ID=[_ _]

按 CLR 键 2 次回 System 主画面。

再输入欲指 定之控制器 代号(1~99)

D. 将卡片阅读机挂入控制器

设定完卡片阅读机 ID,再把卡片阅读机挂入控制器(卡片阅读机自动侦测加入完成后, 控制器才能接受卡片阅读机传送过来的数据。)

RD-100 感应卡片阅读机特色如下:

系统设计说明书

系统设计说明书系统设计说明书1. 引言本系统设计说明书旨在对系统进行详细的设计描述,包括系统的整体架构、功能模块、数据流程、接口设计等内容,以便开发人员能够理解系统的设计思路,有针对性地进行开发工作。

2. 系统概述本系统为一个基于Web的信息管理系统,旨在帮助用户高效地管理和维护信息。

系统提供了多种功能模块,包括用户管理、数据管理、权限管理等,以满足用户多样化的需求。

3. 系统架构3.1 总体结构本系统采用MVC(Model-View-Controller)架构,将系统分成三层,分别为数据层、业务逻辑层和用户界面层。

- 数据层(Model):负责处理数据的存储和访问,包括数据库的设计和数据操作的实现。

- 业务逻辑层(Controller):负责处理业务逻辑,包括用户请求的处理、数据操作的调用等。

- 用户界面层(View):负责展示系统的用户界面,接收用户的操作请求,并将请求传递给业务逻辑层进行处理。

3.2 模块划分本系统的功能模块主要包括以下几个部分:- 用户管理模块:负责用户登录、注册、个人信息管理等功能。

- 数据管理模块:负责信息的增删查改等功能。

- 权限管理模块:负责对用户的权限进行管理,包括用户角色的设置、权限的分配等功能。

4. 数据流程4.1 用户登录流程1. 用户打开系统首页,点击登录按钮。

2. 系统展示登录页面,用户输入用户名和密码。

3. 用户点击登录按钮,系统检查用户输入的用户名和密码是否正确。

4. 如果用户名和密码正确,系统将用户信息保存到会话中,并跳转到用户首页。

5. 如果用户名和密码不正确,系统提示用户错误信息。

4.2 数据管理流程1. 用户打开数据管理页面,系统展示数据列表。

2. 用户可以通过搜索框输入关键词进行数据搜索。

3. 用户可以点击列表中的数据项,查看数据详情。

4. 用户可以点击新增按钮,添加新的数据项。

5. 用户可以点击编辑按钮,修改数据项的内容。

6. 用户可以点击删除按钮,删除数据项。

PLC控制系统硬件设计说明

PLC控制系统硬件设计说明PLC(Programmable Logic Controller)控制系统是一种常用于工业自动化领域的控制设备,它通过特定的编程语言对输入和输出进行逻辑处理和控制,实现自动化生产和处理过程。

在PLC控制系统中,硬件设计是非常重要的,它关系到系统的可靠性、稳定性以及功能的实现。

本文将对PLC控制系统硬件设计进行详细说明。

首先,在PLC控制系统硬件设计中,核心是选择合适的PLC控制器。

PLC控制器是PLC系统的中央处理器,它负责接收输入信号、进行逻辑运算、控制输出信号等功能。

在选择PLC控制器时,需要考虑以下几个关键因素:1.系统需求:根据实际应用需求确定PLC控制器的性能要求,包括输入输出点数、计算速度、存储容量等。

2.可靠性:选择具有良好可靠性的PLC控制器,能够保证系统的稳定运行和工作寿命。

3.扩展性:考虑到系统可能的扩展和升级需求,选择具有一定扩展能力和模块化设计的PLC控制器。

其次,PLC控制系统的硬件设计还需要考虑输入输出模块的选择。

输入输出模块是与PLC控制器相连接的设备,用于接收或输出信号。

在选择输入输出模块时,需要考虑以下几点:1.输入输出点数:根据实际需求选择合适的输入输出模块,确保能够满足系统的输入输出要求。

2.通信接口:考虑通信方式和协议,选择与PLC控制器兼容的输入输出模块。

3.扩展性:选择具有一定扩展能力的输入输出模块,以便满足系统的扩展需求。

此外,PLC控制系统的硬件设计还需要考虑电源供应和接线方式。

电源供应是保证PLC控制系统稳定运行的基础,应该保证电源的稳定性和可靠性。

接线方式则需要根据实际工作环境和接线布置来确定,通常采用绝缘型接线盒或者由专门承载PLC控制系统的设备柜提供接线空间。

最后,PLC控制系统的硬件设计还需要考虑各种保护和检测电路的设计。

保护电路用于保护PLC控制系统免受电源波动、短路、过载等故障的影响,可以采取电源电压稳压电路、过流保护电路等设计。

dsPIC33C数字信号控制器设计指南说明书

A Leading Provider of Smart, Connected and Secure Embedded Control SolutionsdsPIC33C Digital Signal ControllerDesign GuidelinesdsPIC33C Digital Signal ControllersGeneric Robust GuidelineRobustness features on dsPIC33C DSCs•Internal regulator is Capacitor-less design•No need of an external capacitor, no noise injection from the board•Saves space on the board for routing•Lower component count, lower cost•One extra I/O pin•Virtual Pins for Redundancy and Monitoring : Dual core device feature to cross check/monitor •Flash ECC (Error Correcting Code):Flash Error check with 1-bit detection/correction & 2-bit detection •DMT (Deadman Timer) : Instruction cycle counting and could be used as a SW checkpoint•WDT (Watchdog Timer) : For system recovery•CodeGuard™Security : For code protection schemes•CRC (Cyclic Redundancy Check) : For code validation•Two-Speed Start-up : For slow start up from power on, reduce inrush current•Fail-Safe Clock Monitoring : Clock monitor and switch•Backup FRC (BFRC) : Backup for the FRC clock•AEC-Q100 REVG (Grade 0: -40°C to +150°C) Compliant : Automotive QualDecoupling Capacitor•For wide frequency noise filtering, provide multiple decoupling capacitors (e.g.0.01uF,0.1uF) across supply pins of dsPIC33C DSC •When multiple capacitors are provided, place them in ascending order of their value with lowest value capacitor closest to the dsPIC33C pin •Provide decoupling capacitors between each VDD/GND pair of the dsPIC33C DSC •Place decoupling capacitors close to VDD and GND pin pairs of the dsPIC33C DSC•Connect dsPIC33C DSC pin and capacitor pads using shorter directtraces without any vias between them•Also connect decoupling capacitor between AVDD and AGNDusing shorter tracesDecoupling Caps :AVDD -AGND Decoupling Caps : DVDD -DGNDOscillator and MCLR•Place crystal oscillator close to OSCI/OSCO pins ofthe dsPIC33C DSC and connect it using short directtraces avoiding vias•Provide isolated ground plane under the crystal,connect this ground Isle to Board Ground•Avoid any high-speed signals running near theoscillator circuit•Add series resistor between reset pushbutton andMCLR pin of the dsPIC33C DSCsCurrent feedbacksFrom shunt to amplifier inputs•Use Kelvin sensing –take separate tracesfrom pads of the shunt resistor forconnecting to amplifier input resistors•Take the current feedbacks traces fromshunt resistor as differential pair runningparallel across the board until it isconnected to amplifier input resistors(which are placed closer to amplifierpositive and negative input pins)Ground Connection Analog and Digital Ground•Separate the ground of digital circuits, analog circuits ,high speed circuit, high current circuit etc.•The separated ground must be connected only at supply start point which is closer to the 3.3V LDO (dsPIC33C DSC Supply)•In case of multilayer board, dedicate at least one internal layer for grounds. Try to provide solid ground plane avoiding any cuts •To do this , it is necessary to identify the components that connect to specific ground and place them close to each other in specific area of the boardExample :Solid internal AnalogGround(AGND) planejoining at LDO ground.Digital Ground (DGND) trace Analog Ground (AGND) traceAGND and DGND are joined at one point near the source using net tie.Low Noise GuidelineWeak Spot ADCAnalog-To-Digital Converter Circuit•Increasing CPU speed with shrinking structure sizes result in an increased sensitivity to noise•CPU load transient frequencies stimulate passive/reactive circuits formed by parasitic RLC resonators (PCB)•Digital high-speed peripherals add to noise level•In control applications, the ADC is the most sensitive element and provides the guiding value for noise budget estimations •Power Electronics Control Applications are most sensitive to ADC accuracy•Limited Resolution limits dynamic range of control loop •Noise on feedback signal reproduces on ADC results •Noise on supply lines influences internal references •Faster ADCs generate more noise within the internal, analog circuit DIGITIZEDBLOCK ADC Power Stage(Plant)Error Amplifier +–PWM (Modulator)VoltageDividerREF V ERROR REF OUT V V K V =−⋅EA V D K OUTV INVNoise BudgetHow much noise is acceptable?•Determine maximum acceptable voltage deviation •The most system element influencing the most sensitive parameter of the product determines the acceptance level •In power conversion, this is output voltage / output current accuracy and response characteristic •Both highly depend on reliable ADC results Power ConverterCircuitV IN V OUTADC REF V FBerror+-H C z(Compensator)outputinput Anti-WindupPWMNoise Budget –Potential Noise SourcesHow much noise is acceptable?•Noise can influence the ADC through 3 major ports•(A) Feedback Noise via Input Pin •(B) Ground Noise / Bouncing•(C) Reference Voltage derived from Supply Voltage•Noise can inject•Alias frequencies•Random, erroneous samples•Decrease effective ADC resolution•Maximum acceptable noise levels are application dependent and need to be derived individuallyV FBV F B (t ) ± VTimeFeedbackV o u t [n ]n →InputCLOCKAVSSAVDDV REFABCThree Major Noise PortsADCAlias Frequencies•Random noise on feedback signals are relatively uncritical•Periodic noise components exceeding the minimum ADC granularity may influence ADC results •If these are at around or higher than f SAM /2, alias-frequencies may be injected•High-speed ADCs with very small Sample & Hold (S&H)•Capacitance and short sampling times are getting increasingly sensitive to periodic noise on feedback signals •Once alias frequencies have been injected in the data stream, they may influence the control system.•Recommended to add anti-alias filters to input pins, tuned for the effective sampling frequency of the application while still allowing relevant transients to pass.-1.5-1-0.500.511.504590135180225270315360Waveform Sampled at f NFeedback Sampled InputM a g n i t u d ef SAM 2f SAM70k H z40k H z30k H z 25k H z 10k H z160k H z510k H zI n p u t F r e q u e n c yI n p u t F r e q u e n c yI n p u t F r e q u e n c yAnti-Alias Filter DesignAdjustment of anti-alias cut-off frequencies need to consider the internal ADC architecture to prevent excessive ADC result deviations•Shared ADC CoresADC cores with multiple analog input pins (ANx) connect the single S&H capacitor to the pin via multiplexers. To prevent cross-talkbetween input channels, the S&H capacitor needs to be discharged before connection. When connected, the S&H capacitor needsenough time to charge up to the feedback voltage level to achievean accurate result.•Dedicated ADC CoresDedicated cores continuously keep their S&H connected to the pin, tracking the feedback voltage. The connection is only opened during conversion and closed when conversion has completedADCV FB*V FBCAnti-Alias Filter Design / Shared ADC Core•Step 1: Decoupling Capacity•During sampling using the shared ADC core, the discharged S&H capacitor C HOLD is connected to the feedback circuit. C HOLD is charged through R SS and R IC (~350 W ). The high charging current right after SW SS is closed injects a fast transient into the feedback line. Depending on the distance between the voltage divider and the device input pin, the parasitic trace inductance might prevent to bias this inrush current. Hence, this current is exclusively biased by decoupling capacitor C , eventually forming a capacitive voltage divider with C HOLD . As a result, the final sampling voltage will always settle below the real feedback voltage V FB introducing a measurement error ofError = 1−C HOLD C(first assessment of the static offset)•Software adjustable sampling times allow accounting for and thus minimizing these effects which, however , increases the data acquisitionlatency. For high-speed designs it is therefore recommended to minimize the static error by placing enough capacitance as close as possible at the ADC input pin (recommended value = 30…50 x C HOLD ).V FB *V FBCRV OUTC PINC HOLDV DDR ICR SSSampling Switch I LEAKAGESL TRACEParasitic Trace InductanceC DR BSW SSAnti-Alias Filter Design / Shared ADC Core•Step 2: Filter Resistor•Peak-to-Peak voltage levels of periodic noise should be limited to the voltage equivalent of approx. 3 LSB. At V REF = 3.3V and 12-bit resolution the ADC has a total granularity of 806 µV/tick. 3 LSB therefore have a voltage equivalent of 6.44 mV . The total acceptable level,however , depends on the total feedback signal range and needs to be calculated for every application individually.Example:•A signal is sampled at f SAM = 500 kHz (Nyquist-Shannon limit at f N = 250 kHz). A dominant, periodic noise component f Noise = 1000 kHz with a max. deviation of V Noise pk-pk = 60mV is observed. To prevent alias frequencies being injected into the ADC data stream, this noise needs to be damped to less than 6.44 V @ f N .(-20dB @ f N = 6 mV). The pole introduced by the RC filter therefore needs to be placed one magnitude below f N (=25 kHz) to effectively damp the noise magnitude at f N by factor 10.V FB *V FBCRV OUTC PINC HOLDV DDDistance XR ICR SSSampling SwitchI LEAKAGESL TRACEParasitic Trace InductanceC DR AR BSW SSAnti-Alias Filter Design / Shared ADC Core•Step 3: Recharging Decoupling Capacitor C•After the sampling transient has passed, decoupling capacitor C needs to be recharged up to the feedback level for the next sample. With high resistive voltage divider networks, it is recommended to place an additionaldecoupling capacitor in parallel to the lower voltage divider resistor. This capacitor also helps to compensate the parasitic trace inductance L TRACE . At high sampling frequencies hand high resistive voltage dividers an operational amplifier might be required to recharge C in time for the next sample.V FB *V FBCRV OUTC PINC HOLDV DDDistance XR ICR SSSampling Switch I LEAKAGESL TRACEParasitic Trace Inductance C DR AR BSW SSAnti-Alias Filter Design / Shared ADC Core•Design Tip:•Power electronics designs are commonly noisy as the circuit itself produces noise over a very wide frequency range up to manyGHz. Dominant noise bands in the range of 8-15 MHz caused by Diode ringing as well as harmonics of the switching frequency are sometimes difficult to contain and might be induced in feedback lines. The magnitude of the induced noise is independent from the voltage level present.•Hence, it is recommended to place the voltage divider close to the device, minimizing Distance X as well as the parasitic trace inductance L TRACE . Especially, however, preventing noise from being induced in low voltage signals. Noise induced on high voltage signals will get divided with the feedback signal and will therefore have lower amplitudes requiring less damping and thus expanding the maximum bandwidth of the feedback signal.V FB *V FBCRV OUTC PINC HOLDV DDR ICR SSSampling Switch I LEAKAGESL TRACEParasitic Trace Inductance C DR AR BSW SSNoise Budget –Potential Noise SourcesHow much noise is acceptable?•In addition to adjust noise filtering on feedback signals, it is required to analyze the noise floor on supply and ground lines•The ADC uses a reference voltage, which is derived from the supply voltage•Noise on this supply rail can influence the reference level during a conversion process, equally perturbing ADC results as sampling noisy signals.•Supply rain noise can enter the system through VDD as well as through VSSV FBB (t ) ± VFeedbackV o u t [n ]n →InputCLOCKAVSSAVDDV REFABCADCSymmetrical Layout•The CPU itself is a potential noise hub in the system. Each instruction executed by the CPU will create a load step with low amplitude but high edge speed. These high frequency current pulses are exclusively biased by the decoupling capacitors. The generated AC noise inevitably migrates into supply and ground traces, forward into the device as well as backwards to the voltage regulator (VRM).•Insufficient decoupling can stimulate passive/reactive elements along the way, which, if stimulated in the right frequency, may start to resonate, increasing the noise level.FBVDD/VSSANALOG INPUTSCDLOADVoltage Regulator Module (VRM)Passive/Reactive NetworkActive NetworkVREFC DAB dsPIC33C DSCCCCDigital GroundAnalog GroundOESRC ESLL O A DI LI ESLV DDV SSSymmetrical LayoutFour resonant peaks were found withinthe relevant frequency bandVDD Impedance profile measured at every decoupling capacitor(unpowered and powered)dsPIC33 Target ImpedanceHighly reactive resonance valleysI m p e d a n c e M a g n i t u d eSymmetrical Layout dsPIC33TargetImpedancewindow of interest Stimulus windowTotal VDD Impedance profile measured at PDN Port BCPU Clock Frequencies f CY2f CY f OSCKey Takeaways•Key Takeaways•Sharp valleys in an impedance profile indicate the presence of resonance/anti-resonance frequencies of passive/reactive network elements•The CPU load profile is determined by instruction execution and peripheral activity, which are both software dependent to a high degree•The faster the CPU, the wider the frequency range across potential stimuli can be injected into the passive/reactive network segment•If one or more resonators are stimulated simultaneously, the noise level may inflationary increase (Rouge Wave)•Remedy: Flat Impedance Design•Output impedance of voltage regulator must match target impedance•Decoupling capacitors must be selected to match/cancel excess inductance (traces)•Symmetrical design (equal trace length and width of VDD lines reduce number of resonant peaks)•Using ground planes instead of traces reduce VSS trace impedance, shifting potential resonant peaks into high frequency range beyond the Window Of InterestPlease note:Although passive/reactive network components may still be stimulated by higherfrequencies within the Stimulus Window, the CPU won’t be able to pick them up.Noise Budget –Target ImpedanceFlat Impedance Design•Determining Target Impedance Z TARGET•Determine max. acceptable voltage deviation for the application•ADC being the most sensitive element (ADC sample tolerance, e.g.10mV)•Determine minimum and maximum load current, depending on CPU speed and peripheral usage (e.g.I min= 40mA, I max= 80mA)Example:minmaxarg IIToleranceVZ DDetT−⨯=Z T arg et=3.3V×0.010V0.080A−0.040A=0.825WExcess Impedance Cancellation •Positive supply traces (V DD ) between PDN port (B) anddecoupling ports (C) should be as symmetrical as possible toprevent potential resonant frequencies spreading intomultiple peaks concentrated in a narrow frequency range.•Decoupling capacitance need to be selected to cancel the excess inductance of the supply traces. Too much or less capacitance will inevitably result in resonant tank becomingreactive to stimuli. A symmetrical design will allow to use thesame capacitance at every decoupling point (C)•Analog supply voltage is best taken from the nearest decoupling point (C) being filtered through a ferrite bead (E)FB VDD/VSS ANALOG INPUTSCD C C C D O EExcess Impedance Cancellation •Using ground planes instead of traces lowers the excess inductance, effectively moving potential resonant frequencies to higher ranges and eventually out of the Window Of Interest •Digital and analog ground should always be separated preventing noise produced by the CPU entering sensitive analog circuits •Prevent ground planes from overlapping and accidentally coupling noise between planes •Ground decoupling can be done by•Plane gaps, introducing a slightly increased resistance and inductance between both planes limiting noise from migrating•Putting 0 W resistors in between planes introducing the package inductance as a filter barrier•Replacing 0 W resistors by ferrite beads for a more specific filter characteristicFB VDD/VSS ANALOG INPUTS C D CC C Digital GroundAnalog Ground E 0R 0RAnalog Rail DecouplingVDD-2-AVDD Filtering •Digital noise generated by the CPU on V DD gets contained within the network segment by putting up a barrier between V DD and AV DD :•Ferrite Beads allow selective filtering of frequency bands while ensuring proper balancing of decoupling capacitors on V DD and AV DD (recommended)•Low Resistance Resistors also introduce some small package inductance as well provide resistance adding to lowering the Q resp. increase damping (e.g.4.7 W ) •Gapping of layout traces will have similar effects like the options above, but their effectiveness is questionable (not recommended in general) FB VDD/VSSANALOG INPUTS CD CC C Digital GroundAnalog Ground EV SS AV SSFBV DD AV DD 0RAdditional Design GuidanceDesign Example & DocumentsdsPIC33C DSC Design Reference:dsPIC33CH512MP506 Digital Power Plug-In Module (DP-PIM),Part-No. MA330049Anti-Alias Filter Design Guidance:dsPIC33CH512MP506 DP-PIM User Guide /Appendix C. Characterization Data。

自助终端监控管理软件-系统详细设计说明书

密级:自助终端监控管理软件软件开发详细设计说明书2012 年3月ﻬ目录第一章引言ﻩ错误!未定义书签。

1.1ﻩ项目概况ﻩ错误!未定义书签。

1.2编写目的ﻩ错误!未定义书签。

1。

3主要业务名词和术语定义.............................................................. 错误!未定义书签。

1。

4ﻩ参考文献......................................................................................... 错误!未定义书签。

第二章ﻩ菜单和功能设计...................................................................................错误!未定义书签。

2.1菜单结构一览图.............................................................................. 错误!未定义书签。

第三章包和类设计..........................................................................................错误!未定义书签。

3。

1前台包说明ﻩ错误!未定义书签。

3。

2前台类说明ﻩ错误!未定义书签。

3。

3ﻩ后台包说明ﻩ错误!未定义书签。

3.4ﻩ后台类说明....................................................................................... 错误!未定义书签。

3.4。

1 com。

icom.base。

commons.cache.CommonVarﻩ错误!未定义书签。

3.4.2ﻩcom.icom。

java controller 路径重叠匹配规则

java controller 路径重叠匹配规则1. 引言1.1 背景Java作为一种强大的编程语言,在开发Web应用程序的过程中得到了广泛应用。

Java Controller是Java Web应用程序中的一个重要组件,负责接收和处理客户端请求,并返回相应的响应结果。

在定义Controller路径时,开发人员需要遵循一定的规则,以确保路径可被准确匹配,并且不会出现路径重叠的问题。

然而,在实际开发中,由于各种原因(如团队协作、代码维护等),可能会出现Controller路径重叠的情况。

这种情况下,请求在路由时可能会出现匹配错误、请求处理不准确等问题,导致异常或错误结果的返回。

因此,了解并掌握Java Controller 路径重叠匹配规则是非常重要的。

1.2 目的本文旨在介绍Java Controller 路径重叠匹配规则,并提供解决路径重叠问题的方法。

通过深入分析路径定义、路径重叠问题以及解决方案,读者将能够更好地理解和掌握Controller路径规划与设计,避免或解决日常开发中遇到的路径重叠相关问题。

1.3 结构本文将按照以下结构进行介绍:第2部分将详细探讨Java Controller路径的定义,包括路径格式、通配符使用等内容。

通过了解路径定义规则,读者将能够在编写Controller时准确地定义合适的路径,避免路径重叠的问题。

第3部分将介绍具体的路径重叠问题,并提供解决方法。

以示例案例为基础,详细分析路由匹配原理和常见问题,并提供相应的解决方案,帮助读者更好地理解和解决实际开发中可能遇到的路径重叠问题。

第4部分将从实际应用角度出发,给出一些注意事项和建议。

包括规范化路径设计、多模块集成处理方式以及错误排查和调试技巧等。

通过遵循这些注意事项和建议,开发人员能够更好地设计和处理Controller路径,并迅速排查和解决可能出现的问题。

最后,在第5部分中,本文将总结要点并展望未来发展趋势。

对于Java Controller 路径重叠匹配规则以及相关问题进行一个全面回顾,并对未来可能出现的潜在问题进行一些思考与预测。

flask controller层调用model层方法-概述说明以及解释

flask controller层调用model层方法-概述说明以及解释1.引言1.1 概述在现代Web开发中,Flask框架已经成为了许多开发者的首选工具。

它是一个轻量级的Python Web框架,简单易用,同时功能强大。

在Flask 框架中,Controller层起着控制应用逻辑和处理用户请求的作用,而Model层则负责与数据库交互和数据处理。

在本文中,我们将探讨如何在Flask应用中,Controller层调用Model层的方法,实现数据的传递和处理,从而构建一个完整的Web应用。

通过对这一过程的深入分析,我们可以更好地理解Flask框架的组成和工作原理,为今后的开发实践提供指导和借鉴。

1.2 文章结构文章结构部分应该包括以下内容:1. 引言部分:介绍文章的背景和动机,引出文章要讨论的主题。

2. 正文部分:详细讨论Flask框架的基本概念、Controller层和Model 层的作用,以及它们之间的关系和调用方法。

3. 结论部分:总结文章的主要观点,强调Controller层调用Model 层方法的重要性,并展望未来可能的发展方向。

4. 参考文献:列出文章所涉及的相关文献和参考资料。

1.3 目的:本文旨在探讨在Flask框架中,如何正确地实现Controller层调用Model层方法的操作。

通过深入分析Flask框架的结构和各层的作用,我们将探讨如何合理地将业务逻辑划分到Controller和Model两层中,并且通过实际代码示例演示如何在Controller层中调用Model层的方法。

通过本文的研究,读者可以更好地理解Flask框架的设计原则,提高代码的可维护性和扩展性。

同时,我们也将探讨Controller层调用Model层方法的重要性,以及展望未来在这方面的发展方向。

愿本文能为读者带来启发,促进Flask框架的进一步发展。

2.正文2.1 Flask框架简介Flask框架是一个轻量级的Web应用框架,由Python语言编写而成。

NuMicro M4521微控制器系统设计用户指南说明书

Arm® Cortex®-M32-bit MicrocontrollerNuMicro® FamilyNuTiny-SDK-M4521User ManualThe information described in this document is the exclusive intellectual property of Nuvoton Technology Corporation and shall not be reproduced without permission from Nuvoton. Nuvoton is providing this document only for reference purposes of NuMicro microcontroller based system design. Nuvoton assumes no responsibility for errors or omissions.All data and specifications are subject to change without notice.For additional information or questions, please contact: Nuvoton Technology Corporation.Table of Contents1OVERVIEW (4)2NUTINY-SDK-M4521 INTRODUCTION (5)2.1NuTiny -SDK-M4521 Jumper Description (6)2.1.1Power Setting (6)2.1.2Debug Connector (6)2.1.3USB Connector (6)2.1.4Extended Connector (6)2.1.5Reset Button (6)2.1.6Power Connector (6)2.1.7Virtual COM Port Function Switch (6)Pin Assignment for Extended Connector (8)2.22.3NuTiny-SDK-M4521 PCB Placement (16)3How to Start NuTiny-SDK-M4521 on the Keil μVision® IDE (17)3.1Keil uVision® IDE Software Download and Install (17)Nuvoton Nu-Link Driver Download and Install (17)3.23.3Hardware Setup (17)3.4Example Program (18)4How to Start NuTiny-SDK-M4521 on the IAR Embedded Workbench (19)4.1IAR Embedded Workbench Software Download and Install (19)4.2Nuvoton Nu-Link Driver Download and Install (19)4.3Hardware Setup (19)4.4Example Program (20)5Starting to Use Nu-Link-Me 3.0 VCOM Function (21)Downloading and Installing VCOM Driver (21)5.1VCOM Mode Setting on NuTiny-SDK-M4521 (22)5.25.3Setup on the Development Tool (22)5.3.1Check the Usi ng UART on the Keil μVision® IDE (22)5.3.2Check the Target Device and Debug Setting (23)5.3.3Build and Download Code to NuTiny-SDK-M4521 (25)5.3.4Open the Serial Port Terminal (25)5.3.5Reset Chip (25)6NuTiny-SDK-M4521 Schematic (27)6.1NuTiny-EVB-M4521 Schematic (27)Nu-Link-Me V3.0 Schematic (28)6.27REVISION HISTORY (29)1 OVERVIEWNuTiny-SDK-M4521 is the specific development tool for NuMicro® M4521 series. Users can use NuTiny-SDK-M4521 to develop and verify the application program easily.NuTiny-SDK-M4521 includes two portions. One is NuTiny-EVB-M4521 and the other is Nu-Link-Me. NuTiny-EVB-M4521 is the evaluation board and Nu-Link-Me is its Debug Adaptor. Thus, users do not need other additional ICE or debug equipments.2 NUTINY-SDK-M4521 INTRODUCTIONNuTiny-SDK-M4521 uses the M4521SE6AE as the target microcontroller. Figure 2-1 is NuTiny-SDK-M4521 for M4521 series, the left portion is called NuTiny-EVB-M4521 and the right portion is Debug Adaptor called Nu-Link-Me.NuTiny-EVB-M4521 is similar to other development boards. Users can use it to develop and verify applications to emulate the real behavior. The on board chip covers M4521 series features. The NuTiny-EVB-M4521 can be a real system controller to design users’ target systems.Nu-Link-Me is a Debug Adaptor. The Nu-Link-Me Debug Adaptor connects your PC's USB port to your target system (via Serial Wired Debug Port) and allows you to program and debug embedded programs on the target hardware. The Nu-Link-Me V3.0 also supports VCOM function, which gives users more flexibility when debug. To use Nu-Link-Me Debug adaptor with IAR orKeil, please refer to “Nuvoton NuMicro ® IAR ICE driver user manual “or Nuvoton NuMicro ®Keil ICE driver user manual” in detail. These two documents will be stored in the local hard disk when the user installs each driver. To use Nu-Link-Me 3.0 VCOM function, please refer to Chapter 5.VDD (JP1)Reset Button(SW1)I/O LEDPower LEDTarget ChipVirtual COM Port Function Switch (SW2)ICE Controller USB Connector (J2)ICE ControllerVCC : 3.3V or 5V (JPR1)Extended Connector (JP5, JP7)GND (JP4)Extended Connector (JP6, JP8)USB Connector (J3)Figure 2-1 NuTiny-SDK-M4521 (PCB Board)2.1NuTiny -SDK-M4521 Jumper Description2.1.1 Power Setting●JP1: V DD Voltage connecter in NuTiny-EVB-M4521●J2: USB port in Nu-Link-Me●JPR1: Select 5.0V or 3.3V for system powerX: Unused.Note*: Need to separate NuTiny-EVB-M4521 and Nu-Link-Me.2.1.2 Debug Connector●JP2: Connector in target board (NuTiny-EVB-M4521) for connecting with Nuvoton ICEadaptor (Nu-Link-Me)●JP11: Connector in ICE adaptor (Nu-Link-Me) for connecting with a target board (NuTiny-EVB-M4521)2.1.3 USB Connector●J2: Micro USB Connector in Nu-Link-Me connected to a PC USB port●J3: Micro USB Connector in NuTiny-EVB-M4521 for application use2.1.4 Extended Connector●JP5, JP6, JP7, and JP8: Show all chip pins in NuTiny-EVB-M45212.1.5 Reset Button●SW1: Reset button in NuTiny-EVB-M45212.1.6 Power Connector●JP1: V DD connector in NuTiny-EVB-M4521●JP4: GND connector in NuTiny-EVB-M45212.1.7 Virtual COM Port Function Switch●SW2: Switch SW2 on/off before power on to enable/disable VCOM function.SW2 connects pin 6(PD.0/RXD) and pin 10(PD.1/TXD) in NuTiny-EVB-M4521 with pin 22(PB.1/TXD) and pin 21(PB.0/RXD) in Nuvoton ICE adaptor (Nu-Link-Me V3.0). SW2connects pin 30(VCOM) in Nuvoton ICE adaptor (Nu-Link-Me V3.0) to GND to enable VCOM function.Enable VCOM ModeX: Unused.2.2Pin Assignment for Extended ConnectorNuTiny-EVB-M4521 provides M4521SE6AE on board and the extended connector for LQFP64-pin. Table 2-1 is the pin assignment for M4521SE6AE.NUTINY-SDK-M4521 USER MANUALNUTINY-SDK-M4521 USER MANUALNUTINY-SDK-M4521 USER MANUALNUTINY-SDK-M4521 USER MANUALTable 2-1 Pin Assignment for M45212.3NuTiny-SDK-M4521 PCB PlacementUsers can refer to Figure 2-2 for the NuTiny-SDK-M4521 PCB placement.Figure 2-2 NuTiny-SDK-M4521 PCB Placement3 HOW TO START NUTINY-SDK-M4521 ON THE KEIL ΜVISION® IDE3.1Keil uVision® IDE Software Download and InstallPlease visit the Keil company website () to download the Keil μVision®IDEand install the RVMDK.3.2Nuvoton Nu-Link Driver Download and InstallPlease visit the Nuvoton company NuMicro®website (/NuMicro) todownload “NuMicro®Keil μVision®IDE driver” file. When the Nu-Link driver has been welldownloaded, please unzip t he file and execute the “Nu-Link_Keil_Driver.exe” to install the driv er.Hardware Setup3.3The hardware setup is shown as Figure 3-1.NUTINY-SDK-M4521 USER MANUALFigure 3-1 NuTiny-SDK-M4521 Hardware SetupExample Program3.4This example demonstrates the ease of downloading and debugging an application on a NuTiny-SDK-M4521 board. It can be found on Figure 3-2 list directory and downloaded from Nuvoton NuMicro® website.ProjectFigure 3-2 Example DirectoryTo use this example:This sample code runs some functions about system manager controller and clock controller, and will show messages by Uart. Users can see the messages by following the steps of Chapter 5.⏹Start μVision®⏹Project-OpenOpen the SYS.uvproj project file⏹ Project - BuildCompile and link the SYS application⏹ Flash – DownloadProgram the application code into on-chip Flash ROM⏹Start debug modeUsing the debugger commands, youmay:◆ Review variables in the watchwindow◆ Single step through code◆ Reset the device◆ Run the application4 HOW TO START NUTINY-SDK-M4521 ON THE IAR EMBEDDEDWORKBENCH4.1IAR Embedded Workbench Software Download and InstallPlease connect to IAR company website () to download the IAR EmbeddedWorkbench and install the EWARM.4.2Nuvoton Nu-Link Driver Download and InstallPlease visit the Nuvoton company NuMicro®website (/NuMicro ) todownload the “NuMicro®IAR EWARM Driver” file. When the Nu-Link driver has been welldownloaded, please unzip the file and execute the “Nu-Link_Keil_Driver.exe” to install thedriver.4.3Hardware SetupThe hardware setup is shown as Figure 4-1.NUTINY-SDK-M4521 USER MANUALFigure 4-1 NuTiny-SDK-M4521 Hardware SetupExample Program4.4This example demonstrates the ease of downloading and debugging an application on a NuTiny-SDK-M4521 board. It can be found on Figure 4-2 list directory and downloaded fromNuvoton NuMicro ®website.ProjectFigure 4-2 Example DirectoryTo use this example:This sample code runs some functions about system manager controller and clock controller, and will show messages by Uart. Users can see the messages by following the steps of Chapter 5.⏹ Start IAR Embedded Workbench ⏹Project – Download and DebugProgram the application code into on-chip Flash ROM ⏹ File-Open-WorkspaceOpen the SYS.eww workspace file⏹Single step through code ⏹Project - MakeCompile and link the SYS application⏹ Reset the device⏹Run the application5 STARTING TO USE NU-LINK-ME 3.0 VCOM FUNCTION5.1Downloading and Installing VCOM DriverPlease connect to Nuvoton NuMicro®website (/NuMicro) to downloadthe “NuMicro®ICP Programming Tool” file. After the ICP Programming Tool driver isdownloaded, please unzip the file and execute the “ICP Programming Tool.exe”. Simply followthe installation and optional steps to install ICP Programming Tool and Nu-Link USB Driver,which included VCOM driver.NUTINY-SDK-M4521 USER MANUALFigure 5-1 Optional Step after ICP Programming Tool InstallationFigure 5-2 Install Nuvoton COM&LPT DriverFigure 5-3 Install Nuvoton Universal Serial Bus Controllers5.2VCOM Mode Setting on NuTiny-SDK-M4521Before the NuTiny-SDK-M4521 is connected to the PC, please enable SW2 VCOM function by switching on SW2. The NuTiny-EVB-M4521 transmits through UART0 to VCOM to send outdata. Switch SW2 off when using UART0 function without VCOM function.After connected USB port in Nu-Link-Me to the PC, user can find a “Nuvoton Virtual Com Port”from Device Manager as Figure 5-4.Figure 5-4 Nuvoton Virtual Com Port5.3Setup on the Development ToolThe example is demonstrated on the Keil μVision® IDE.5.3.1 Check the Using UART on the Keil μVision® IDEPlease open the project and find system_M4521.h (which can be found in \\M4521_BSP_CMSIS_V3.00.000\Library\Device\Nuvoton\M4521\Include) to check the using UART in DEBUG_PORT. The setting has to be the same as the using UART in the NuTiny-EVB-M4521.NUTINY-SDK-M4521 USER MANUALFigure 5-5 The Using UART on Keil μVision®IDE5.3.2 Check the Target Device and Debug SettingThe target device has to be the same as the setting in Debug. Please click “Target Option ” to open the Option windows, and find the setting in “Device ”, “Debug ”, and “Utilities ” page. Please follow the steps below to check the setting.5.3.3 Build and Download Code to NuTiny-SDK-M4521Please build the project and download code to NuTiny-SDK-M4521.5.3.4 Open the Serial Port TerminalUser can use serial port terminal, PuTTY for example, to print out debug message.NUTINY-SDK-M4521 USER MANUALFigure 5-6 Set Baud Rate5.3.5 Reset ChipAfter pushing the reset button, the chip will reprogram application and print out debug message.Figure 5-7 Serial Port Terminal WindowsNotice: Please switch SW2 on before the NuTiny-SDK-M4521 connects to the PC. When the NuTiny-SDK-M4521 connects to the PC with SW2 switch on, PC will detect VCOM as a USB device and the detection will only be processed once. VCOM will not function if switch on SW2 after the connection.6 NUTINY-SDK-M4521 SCHEMATIC6.1NuTiny-EVB-M4521 SchematicNUTINY-SDK-M4521 USER MANUALNu-Link-Me V3.0 Schematic 6.27 REVISION HISTORY2018.11.28 1.00 1. Initially issued.Important NoticeNuvoton Products are neither intended nor warranted for usage in systems or equipment, any malfunction or failure of which may cause loss of human life, bodily injury or severe property damage. Such applicat ions are deemed, “Insecure Usage”.Insecure usage includes, but is not limited to: equipment for surgical implementation, atomic energy control instruments, airplane or spaceship instruments, the control or operation of dynamic, brake or safety systems designed for vehicular use, traffic signal instruments, all types of safety devices, and other applications intended to support or sustain life.All Insecure Usage shall be made at customer’s risk, and in the event that third parties lay claims to Nuvoton as a result of customer’s Insecure Usage, customer shall indemnify the damages and liabilities thus incurred by Nuvoton.。

solar controller Manual说明书

■常见故障现象及处理方法:在出现下列现象时,请按照下述方法进行检查:■技术指标:光合太阳能控制器使用说明书■主要特点:1、使用了单片机和专用软件,实现了智能控制;2、利用蓄电池放电率特性修正的准确放电控制。

放电终了电压是由放电率曲线修正的控制点,消除了单纯的电压控制过放的不准确性,符合蓄电池固有的特性,即不同的放电率具有不同的终了电压。

3、具有过充、过放、电子短路、过载保护、独特的防反接保护等全自动控制;以上保护均不损坏任何部件,不烧保险;4、采用了串联式PWM充电主电路,使充电回路的电压损失较使用二极管的充电电路降低近一半,充电效率较非PWM高3%-6%,增加了用电时间;过放恢复的提升充电,正常的直充,浮充自动控制方式使系统有更长的使用寿命;同时具有高精度温度补偿;5、直观的LED发光管指示当前蓄电池状态,让用户了解使用状况;6、所有控制全部采用工业级芯片(仅对带I工业级控制器),能在寒冷、高温、潮湿环境运行自如。

同时使用了晶振定时控制,定时控制精确;7、取消了电位器调整控制设定点,而利用了Flash存储器记录各工作控制点,使设置数字化,消除了因电位器震动偏位、温漂等使控制点出现误差降低准确性、可靠性的因素;8、使用了数字LED显示及设置,一键式操作即可完成所有设置,使用极其方便直观,9、全密封防水型(-S)具有完全的防水防潮性能。

■控制器面板图:到浮充电压,并保持浮充电压。

如果没有发生过放,将不会有提升充电方式,以防蓄电池失水。

这些自动控制过程将使蓄电池达到最佳充电效果并保证或延长其使用寿命。

■系统说明:本控制器专为太阳能直流供电系统、太阳能直流路灯系统设计,并使用了专用电脑芯片的智能化控制器。

采用一键式轻触开关,完成所有操作及设置。

具有短路、过载、独特的防反接保护,充满、过放自动关断、恢复等全功能保护措施,详细的充电指示、蓄电池状态、负载及各种故障指示。

本控制器通过电脑芯片对蓄电池的端电压、放电电流、环境温度等涉及蓄电池容量的参数进行采样,通过专用控制模型计算,实现符合蓄电池特性的放电率、温度补偿修正的高效、高准确率控制,并采用了高效PWM蓄电池的充电模式,保证蓄电池工作在最佳的状态,大大延长蓄电池的使用寿命。

SD Host Controller 2.0设计说明书

SD Host Controller 2.0设计说明书(仅供内部使用)拟制: 张 杰 日期: 2008-8-13审核: 日期:审核: 日期;批准: 日期;创辉电脑深圳代表处香港创辉电脑有限公司深圳代表处研究管理部文档中心 产品版本 密级 V1.0绝密 产品名称: SD Host Controller 2.0修订记录日期修订版本描述作者2008-8-13 1.0 初稿完成张杰目录目录 .................................................................................................................................................. 3第1章总体设计. (5)§1.1 SD卡控制器综述 (5)§1.2 SD卡控制器应用结构图 (5)§1.3 顶层结构图 (6)§1.4 SD卡控制器主要功能点 (6)§1.5 SD卡控制器接口描述 (7)§1.6 SD卡控制器寄存器定义 (8)第2章模块设计与验证 (29)§2.1 命令控制模块(CCL)设计与验证 (29)§2.1.1 模块说明 (29)§2.1.2 模块接口描述 (30)§2.1.3 状态机设计 (32)§2.1.4 功能仿真 (43)§2.2 中断控制/时钟管理模块(Clockgen/INT)设计与验证 (44)§2.2.1 模块说明 (44)§2.2.2 模块接口描述 (44)§2.2.3 模块结构图 (47)§2.2.4 功能仿真 (47)§2.3 数据控制模块(DCL)设计与验证 (50)§2.3.1 模块说明 (50)§2.3.2 详细功能描述 (50)§2.3.3 模块接口描述 (52)§2.3.4 状态机设计 (56)§2.3.5 功能仿真 (56)第3章系统级功能仿真和FPGA验证 (57)§3.1 功能仿真结果表格 (57)§3.2 FPGA验证 (57)第4章LINUX下SD卡驱动程序 (59)§4.1 SDIO驱动程序流程图 (59)§4.2 SD/MMC/SDHC Host 2.0驱动程序流程图 (61)§4.3 相关Card驱动流程图(2.0标准) (67)第5章附录(SD卡控制器验证计划书) (70)§5.1 SD控制器功能验证方案 (70)§5.1.1 验证环境 (70)§5.1.2 验证平台 (70)§5.1.3 验证流程 (71)§5.2 功能点统计 (72)§5.3 详细测试步骤和寄存器设置 (73)§5.4 FPGA验证 (77)§5.4.1 验证目标 (77)§5.4.2 验证方法 (78)§5.4.3 详细验证计划 (78)第6章参与设计人员 (81)第1章总体设计§1.1SD卡控制器综述本设计遵循SD Host Controller Simplified Specification Version2.00版本。

ALTEC CONTROLLER AL830 说明书

ALTEC

MICROCOMPUTER-CONTROLLED

CONTROLLER AL830

INSTRUCTION MANUAL

AL8 3 0温 度 控 制 器

使用说明书

CONTROLLER AL830

R

ALTEC

目录

1 .概 述 … … … … … … … … … … … … … … … … … … … … … … … … … …1 2 .功 能 特 点 … … … … … … … … … … … … … … … … … … … … … … … …1 3 .型 号 定 义 … … … … … … … … … … … … … … … … … … … … … … … …1 4 .仪 器 安 装 … … … … … … … … … … … … … … … … … … … … … … … …2 5 .电 气 连 接 … … … … … … … … … … … … … … … … … … … … … … … …3 6 .面 板 介 绍 … … … … … … … … … … … … … … … … … … … … … … … …5 7 .面 板 显 示 及 操 作 … … … … … … … … … … … … … … … … … … … … …5 8 .软 件 组 态(功 能 参 数 的 设 置)… … … … … … … … … … … … … … …7 9 . PID参 数 整 定 … … … … … … … … … … … … … … … … … … … … …10 1 0 .故 障 显 示 … … … … … … … … … … … … … … … … … … … … … …1 0 1 1 .线 性 过 程 输 入 … … … … … … … … … … … … … … … … … … … …1 1 1 2 .曲 线 程 序 控 制 器 … … … … … … … … … … … … … … … … … … …1 3 1 3 .输 入 信 号 测 量 范 围 … … … … … … … … … … … … … … … … … …1 6

软件详细设计说明-模板

附件A 密级:非密软件CSCI详细设计说明xxxx有限公司二○二一年七月修改历史记录:A.1 授权构件 (5)A.1.1 用户授权认证服务接口AuthController (5)A.1.1.1 功能描述 (5)A.1.1.2 类成员函数设计 (5)A.1.1.2.1 token方法设计 (5)A.2 xxxx模块构件 (5)A.2.1 xxxx接口SchemaController (5)A.2.1.1 功能描述 (5)A.2.1.2 类成员函数设计 (6)A.2.1.2.1 schemaList方法设计 (6)A.2.1.2.2 conceptList方法设计 (6)A.2.1.2.3 attributeList方法设计 (6)A.2.2 检索功能接口SearchController (7)A.2.2.1 功能描述 (7)A.2.2.2 类成员函数设计 (7)A.2.2.2.1 promptList方法设计 (7)A.2.2.2.2 search方法设计 (8)A.2.2.2.3 advancedSearch方法设计 (8)A.2.2.2.4 advancedSearchValue方法设计 (9)A.2.2.2.5 flow方法设计 (9)A.2.3 标签功能接口TagController (9)A.2.3.1 功能描述 (9)A.2.3.2 类成员函数设计 (9)A.2.3.2.1 updateTags方法设计 (10)A.2.3.2.2 getTags方法设计 (10)A.3 WorkArea模块构件 (10)A.3.1 线索管理接口ClueController (10)A.3.1.1 功能描述 (10)A.3.1.2 类成员函数设计 (10)A.3.1.2.1 batchAccess方法设计 (10)A.3.2 分析操作历史接口ClueHistoryController (12)A.3.2.1 功能描述 (12)A.3.2.2 类成员函数设计 (12)A.3.2.2.1 page方法设计 (12)A.3.2.2.2 filterTimes方法设计 (12)A.3.2.2.3 delete方法设计 (13)A.3.2.2.5 updateClue方法设计 (13)A.3.2.2.6 updateStepResult方法设计 (13)A.3.2.2.7 stepDetails方法设计 (13)A.3.3 实体管理接口EntityController (14)A.3.3.1 功能描述 (14)A.3.3.2 类成员函数描述 (14)A.3.3.2.1 addNode方法设计 (14)A.3.3.2.2 deleteNode方法设计 (14)A.3.3.2.3 deleteRelation方法设计 (15)A.3.3.2.4 infobox方法设计 (15)A.3.3.2.5 entityDetails方法设计 (15)A.3.3.2.6 addRelation方法设计 (16)A.3.3.2.7 addUrl方法设计 (16)A.3.4 实体八合一管理接口EntityEightController (16)A.3.4.1 功能描述 (16)A.3.4.2 类成员函数描述 (16)A.3.4.2.1 update方法设计 (16)A.3.4.2.2 addNumericAttrValue方法设计 (17)A.3.4.2.3 deletePrivateData方法设计 (17)A.3.4.2.4 addPrivateData方法设计 (18)A.3.5 图计算接口GraphCalculationController (18)A.3.5.1 功能描述 (18)A.3.5.2 类成员函数描述 (18)A.3.5.2.1 keyPointsAnalysis方法设计 (18)A.3.5.2.2 groupAnalysis方法设计 (20)A.3.5.2.3 groupSummary方法设计 (20)A.3.5.2.4 visualAnalysis方法设计 (21)A.3.6 专题接口TopicController (21)A.3.6.1 功能描述 (21)A.3.6.2 类成员函数描述 (21)A.3.6.2.1 topicList方法设计 (21)A.3.7 工作区接口WorkAreaController (21)A.3.7.1 功能描述 (21)A.3.7.2 类成员函数描述 (22)A.3.7.2.1 search方法设计 (22)A.3.7.2.3 check方法设计 (22)A.3.7.2.4 save方法设计 (23)A.3.7.2.5 batchImport方法设计 (23)A.3.7.2.6 batchDelete方法设计 (24)A.3.7.2.7 createGroup方法设计 (24)A.3.7.2.8 createMask方法设计 (24)A.3.7.2.9 networkPath方法设计 (25)A.3.7.2.10 networkRelation方法设计 (25)软件CSCI详细设计说明A.1 授权构件A.1.1 用户授权认证服务接口AuthControllerA.1.1.1 功能描述用户登录获取token认证A.1.1.2 类成员函数设计表1 用户授权认证服务Controller类成员函数设计token方法设计(1)方法原型:ApiReturn<AuthInfo> token(String grantType,String refreshToken,String account,String password){}(2)方法说明:根据前端传递的用户字段获取或刷新用户token(3)输入/输出数据元素:表2 Token方法设计输入/输出数据元素(5)逻辑流程图图1 token认证逻辑实现图A.2 xxxx模块构件A.2.1 xxxx接口SchemaControllerA.2.1.1 功能描述获取基础库/线索库图谱的Schema列表信息;获取基础库/线索库图谱的Schame概念基础信息列表;获取基础库/线索库图谱指定概念的属性/关系列表。

网站开发详细设计文档

网站开发详细设计文档1. 介绍本文档旨在提供网站开发的详细设计信息。

它包括网站的功能、技术选择、设计模式和数据结构等方面的详细说明。

2. 功能本网站将提供以下主要功能:- 用户注册和登录- 用户个人资料管理- 发布和管理文章- 文章评论和回复- 文章分类和标签- 搜索功能3. 技术选择在开发本网站时,我们将使用以下技术:- 后端开发:Python和Django框架- 数据库:MySQL4. 设计模式本网站将采用MVC(Model-View-Controller)设计模式。

它将分为三个主要部分:- 模型(Model):处理数据和业务逻辑- 视图(View):处理用户界面和交互- 控制器(Controller):协调模型和视图,处理请求和响应5. 数据结构以下是网站中主要数据结构的简要说明:- 用户(User):保存用户的个人信息,包括用户名、密码和电子邮件等- 文章(Article):保存文章的标题、内容、作者和发布日期等- 分类(Category):保存文章的分类信息- 标签(Tag):保存文章的标签信息6. 网站页面布局本网站将采用响应式设计,以适应不同设备和屏幕尺寸。

以下是网站主要页面的布局:- 主页:显示最新发布的文章和热门文章列表- 文章详情页:显示文章的详细内容和相关评论- 用户个人资料页:显示用户的个人信息和发布的文章列表- 登录页:用户可以输入用户名和密码登录- 注册页:用户可以填写注册信息创建新账户7. 总结本文档提供了网站开发的详细设计信息,包括功能、技术选择、设计模式和数据结构等方面的说明。

根据这些设计,我们将开始开发网站的各个模块,并逐步完成整个项目。

ledlightingcontroller控制器说明书

ledlightingcontroller控制器说明书LED灯光控制器使用说明书一、背景介绍在现代社会中,LED灯光的应用越来越广泛。

为了更好地控制和调节LED灯光的亮度、颜色和效果,LED灯光控制器应运而生。

本篇文章将详细介绍LED灯光控制器的使用方法和注意事项,以帮助用户更好地了解和操作该控制器。

二、控制器概述1. 外观设计:本款LED灯光控制器采用简约而时尚的外观设计,采用高级金属材质制作,手感舒适,增加了产品的质感。

2. 功能特点:本款控制器具备多种功能,包括亮度调节、颜色调节、节能模式等,满足用户对不同场景的需求。

三、控制器使用方法1. 连接:将LED灯光控制器与电源和LED灯进行正确的连接,确保电源正常连接,以及灯珠与控制器连接正确。

2. 打开电源:通电后,控制器的指示灯将亮起。

3. 功能选择:一般来说,使用控制器的按钮或旋钮来选择不同的功能。

具体的操作方法需要参照产品说明书进行操作。

四、亮度调节1. 找到亮度调节功能按钮或旋钮,在控制器上找到相应标记。

2. 轻轻旋转或按压亮度调节按钮,LED灯光的亮度将相应发生变化。

3. 根据需要逐渐调节至合适的亮度。

五、颜色调节1. 根据控制器的说明书,找到颜色选择功能按钮或旋钮。

2. 通过旋转或按压颜色调节按钮,改变LED灯的颜色。

此款控制器支持多种颜色模式选择,具体变换效果请参考说明书。

六、节能模式1. 本控制器设计了节能模式,用以提高对LED灯使用寿命的保护和节约能源。

2. 在控制器功能选项中寻找节能模式,并将其打开。

3. 节能模式的具体功能可参考产品说明书。

七、注意事项1. 在使用控制器前,务必仔细阅读产品说明书,了解使用方法和注意事项。

2. 在操作过程中,注意电源的正负极连接,防止反接现象。

3. 避免将控制器和LED灯暴露在过度潮湿或高温的环境下,以免损坏设备。

4. 定期清洁控制器表面,避免灰尘和污垢积累,影响使用效果。

5. 当长时间不使用控制器时,建议将电源切断,以免造成电源浪费和电器故障。

ec controller电导说明书

EC Controller电导说明书

EC Controller的电导说明书包含一些基本的信息,以下是其简要概述:

EC Controller是一个嵌入式控制器,常用于笔记本电脑中,用于键盘控制、触摸板、电源管理、风扇控制、笔记本电池管理等功能。

它实际上是一个单片机,内部包含独立运行的软件,存放在自己(或者与BIOS共用)的非易失性介质中。

EC在笔记本电脑的整个生命周期中都存在,即使笔记本关机,EC也还在工作,除非拔掉电池,EC芯片没有供电,只要有供电,EC就开始工作,并等待按键然后处理电源上电时序并将笔记本上电。

EC Controller在笔记本电脑的便携、智能化、个性化设计中起到了重要的作用。

它内部本身也有一定容量的Flash来存储EC的代码。

EC在系统中的地位绝不次于南北桥,在系统开启的过程中,EC控制着绝大多数重要信号的时序。

在关机状态下,EC一直保持运行,并在等待用户的开机信息。

然而,我无法为您提供完整的EC Controller电导说明书。

为了获得更全面的信息和使用指南,建议您访问生产商的官方网站或者与销售商联系,他们可以提供详细的文档和技术支持。

同时,您也可以在技术论坛或社区中寻找相关的使用经验和教程。

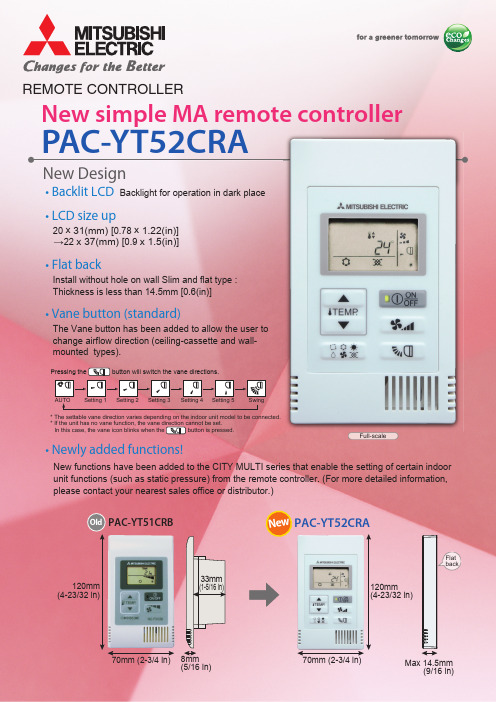

新简易MA遥控器PAC-YT52CRA新设计说明书

New simple MA remote controllerPAC-YT52CRANew Design• Backlit LCD Backlight for operation in dark place• LCD size up20 x 31(mm) [0.78 x 1.22(in)] →22 x 37(mm) [0.9 x 1.5(in)]• Flat backInstall without hole on wall Slim and flat type : Thickness is less than 14.5mm [0.6(in)]• Vane button (standard)The Vane button has been added to allow the user to change airflow direction (ceiling-cassette and wall- mounted types).• Newly added functions!New functions have been added to the CITY MULTI series that enable the setting of certain indoor unit functions (such as static pressure) from the remote controller. (For more detailed information, please contact your nearest sales office or distributor.)120mm (4-23/32 in)120mm (4-23/32 in)PAC-YT51CRBFull-scale33mm (1-5/16 in)8mm (5/16 in)Max 14.5mm (9/16 in)N e w OldFlat backPressing thebutton will switch the vane directions.* The settable vane direction varies depending on the indoor unit model to be connected.* If the unit has no vane function, the vane direction cannot be set.In this case, the vane icon blinks when theAUTO Setting 1Setting 2Setting 3Setting 4Setting 5SwingREMOTE CONTROLLERFunctionsExternal Dimensions14.5[9/16]83.5[3-9/32]120[4-23/32]70[2-3/4]Unit:mm[in.].F F O d n a N O n e e w t e b s e g n a h C F F O /N O Operation mode switching Vane settingBacklightError informationVentilation equipment controlFan speed settingItem DescriptionSetting DisplaySetting Display1. Operations/Display*1Room temp.Setting *1Select from COOL, DRYING, FAN, AUTO, and HEAT.Changes the fan speed.* The settable fan speed varies depending on the indoor unit model to be connected.Switches the vane directions.* The settable vane direction varies depending on the indoor unit model to be connected.Pressing the button lights up a backlight.The light automatically turns off after a certain period of time.(The brightness settings can be selected from Bright, Dark, and Light off.)Displays the current error status with the address.* The address may not be displayed depending on the error status.When the CITY MULTI indoor unit is connected, interlocked setting of the CITY MULTI LOSSNAY unit is possible.When the Mr. SLIM indoor unit (A-control) is connected, interlocked operation of the microcomputer-type LOSSNAY unit is possible. Sets a room temperature.* The preset temperature range varies depending on the indoor unit model to be connected.(The ranges for a standard model are as follows.) • COOL/DRY: 19ºC - 30ºC/67ºF - 87ºF • HEAT: 17ºC - 28ºC/63ºF - 83ºF • AUTO: 19ºC - 28ºC/67ºF - 83ºFAllows/disallows local operationTemperature range restrictionOperation lock By setting a centralized controller, the following local operations are prohibited: ON/OFF; operation mode; preset temperature;* The CENTRAL icon appears while the local operations are prohibited.Locks all buttons.Item Description2. Restriction settings*1 AUTO mode is settable only when those functions are available on the indoor unit.The preset temperature range can be restricted for each operation mode (COOL/HEAT/AUTO).Room temperature detectionVarious settingsThe temperature sensor is built-in on the remote controller.The following settings can be made by setting the dip switches.• Remote controller Main/Sub setting• Temperature display unit setting (Celsius/Fahrenheit)• Cooling/heating display in AUTO mode • Indoor temperature displayItem Description3. MiscellaneousSystem StructureR/C : Remote ControllerSimple MA R/CSimple MA R/CNon-polarized 2-wireNon-polarized 2-wire Connectable ModelsControllable unitsCITY MULTI indoor unit Mr. SLIM indoor unit (A-control)CITY MULTI LOSSNAY unit *1*1 Connected via indoor unit (direct connection not allowed)MEE12K010New publication effective Aug. 2012Specifications subject to change without noticeEco Changes is the Mitsubishi Electric Group’s environmental statement, and expresses the Group’s stance on environmental management. Through a wide range of businesses, we are helping contribute to the realization of a sustainable society.。

自动化控制图例与字母说明表完整

自动化控制图例与字母说明表完整自动化控制图例是一种用来表示自动化系统中各个元件、设备、信号和控制逻辑关系的图形符号和线条组合,它是自动化控制系统设计和分析的重要工具。

字母说明表则是对图例中使用的各个字母和符号进行解释和说明的表格。

以下是一份完整的自动化控制图例与字母说明表,详细描述了各个元件、设备、信号和控制逻辑的含义和功能。

1. 控制器(Controller)- 符号:矩形框- 功能:控制系统的中央处理器,接收输入信号并根据设定的控制算法产生输出信号。

2. 传感器(Sensor)- 符号:圆形- 功能:用于检测和测量物理量,将其转换为电信号并传递给控制器。

3. 执行器(Actuator)- 符号:箭头- 功能:根据控制器的输出信号执行相应的动作,控制系统的执行部份。

4. 信号线(Signal Line)- 符号:直线- 功能:用于传输信号,连接传感器、控制器和执行器。

5. 电源(Power Supply)- 符号:直线和加号- 功能:为控制系统提供电能。

6. 开关(Switch)- 符号:直线和弯曲线- 功能:用于控制电路的通断。

7. 运算器(Operator)- 符号:圆形中带有加号或者乘号- 功能:对输入信号进行数学运算,产生输出信号。

8. 计时器(Timer)- 符号:圆形中带有时钟符号- 功能:根据设定的时间参数,控制输出信号的时间延迟或者持续时间。

9. 计数器(Counter)- 符号:圆形中带有数字- 功能:对输入信号进行计数,根据设定的计数值产生输出信号。

10. 过程变量(Process Variable)- 符号:圆形中带有"P"字母- 功能:表示控制系统中需要被测量或者控制的物理量。

11. 设定值(Setpoint)- 符号:圆形中带有"S"字母- 功能:控制器设定的期望值或者目标值。

12. 输出值(Output)- 符号:圆形中带有"O"字母- 功能:控制器输出的控制信号。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

Controller设计说明书Controller设计说明文档修订表审批记录目录Controller功能简介 (4)模块说明 (4)Controller流程图 (4)函数与结构体说明 (4)模块一 (4)模块二 (5)模块三 (7)模块四 (7)模块五 (8)模块六 (8)调试信息的说明 (8)Controller功能简介Controller是作为服务器程序,它的功能有:(1)对PC(Panel UI/TV UI)发出的控制命令运用网络通信的方式进行接收并对其解析处理,将指令结合硬件协议转化之后写入串口来控制相关设备;(2)对WEB UI进过CGI发送过来的控制命令运用共享内存的方式进行接收,并结合硬件协议转化之后写入串口来控制相关设备;(3)通过读取设备发过来的串口信息,对数据库进行更新设备状态;(4)从数据库读取设备信息。

这里可以看到IGREEN软件系统架构图:IGREEN软件系统架构图.xlsx上面对Controller的功能用图形表现出来,更能够加深理解。

模块说明根据以上的功能说明以及架构图,可以把Controller分为以下六个模块:(1)从数据库读取设备信息;(2)运用网络通信的方式对接收到的控制命令进行解析处理,来唤醒相应的线程;(3)运用共享内存的方式接收控制指令,并根据它来唤醒相应的线程;(4)通过读取设备发过来的串口信息,对数据库进行更新设备状态;(5)将得到的控制指令结合硬件协议转化之后写入串口来控制相关设备;(6)通过发射红外码控制电视、DVD、空调等电器。

Controller流程图以下是Controller设计的流程图,主要是对Controller整个设计过程的纵览,可以对Controller整个设计的思想更好的把握。

点击图标打开Controller设计流程图:Microsoft OfficeWord 文档函数与结构体说明模块一、从数据库读取设备信息(1)init_module_map()函数函数被调用的位置:该函数是在controller_ main()中调用的。

函数意义:读取数据库system表,对device_info[MOD_MAX]这个结构体数组进行初始化,在该函数中,运用了数据库查询语句"select module_name, type from system",得到表的两个属性module_name和type,并将其分别赋值给device_info[i].name和device_info[i].type。

(2)device_info[MOD_MAX]结构体数组struct _module_map{char name[64]; //Device Nameint type; //Device Type}device_info[MOD_MAX];用于存放从数据库读取的Device Name与Device Type。

(3)_reset()函数返回值:返回的是一个int类型的,调用成功时返回0;函数被调用的位置:该函数是在igreen.c的igreen_main()中调用的。

函数意义:对灯信息以及窗帘信息进行初始化设定。

首先,对灯具信息的初始化,运用数据库查询语句"select lighting.id, netid, deviceid, node, level, type from lighting,lighting_igreen where lighting.id = lighting_igreen.id order by deviceid,node",查询lighting及lighting_igreen两个表,将其属性值分别赋值给结构体数组lighting_units[MAX_LIGHTING_NODE]的各成员变量;其次,对窗帘信息的初始化,运用数据库查询语句"select curtain.id, netid, deviceid, node from curtain, curtain_igreen where curtain.id = curtain_igreen.id order by deviceid",查询curtain及curtain_igreen两个表,将其属性值分别赋值给结构体数组curtain_units[MAX_LIGHTING_NODE]的各成员变量;(4)lighting_units[MAX_LIGHTING_NODE]和curtain_units[MAX_LIGHTING_NODE] static struct _igreen_lighting{char id[CE_ID_LEN];// Lighting IDint net_id; // Net IDint device_id; // Device IDint node_id; // Channel IDint level; // Lighting Levelint type; // Lighting Type}lighting_units[MAX_LIGHTING_NODE];用于存放从数据库读取的灯具信息;static struct _igreen_curtain{char id[CE_ID_LEN];// Curtain IDint type; // 3 Lines:0, 2 Lines:1int net_id; // Net IDint device_id; // Device IDint node; // Node ID}curtain_units[MAX_CURTAIN_NODE];用于存放从数据库读取的窗帘信息。

模块二、运用网络通信的方式对接收到的控制命令进行解析处理,来唤醒相应的线程(1)controller_main()函数函数的位置:该函数是在monitor.c中的main函数函数的意义:该函数主要就是运用网络通信的方式接收控制命令,然后对该命令进行解析,获得device type以期唤醒相应的设备线程。

(2)socket(AF_INET, SOCK_DGRAM, 0)返回值:非负的描述字函数的位置:该函数是在monitor.c中的controller_main()函数中出现的函数意义:创建一个UDP套接口,AF_INET表示的是IPv4协议,SOCK_DGRAM表示的是UDP套接口,0表示参数protocol。

具体的介绍参考《Linux环境下的C编程指南》P327。

该函数在这里的实际作用是分别创建server套接口和hbt套接口。

bind(s, (struct sockaddr*)&servaddr, sizeof(struct sockaddr_in))返回值:返回值0表示成功函数意义:绑定套接口函数bind,它的功能是为套接口分配一个本地协议地址,也就是本地IP地址与本地套接口的组合。

具体的介绍参考《Linux环境下的C编程指南》P328。

sendto(hs, &hbt, sizeof(struct _ce_epack), 0, (struct sockaddr *)&hbtaddr, hlen);返回值:函数返回实际写的字节数,如果出错则返回-1函数意义:发送数据包,在这里的实际意义是发送心跳包到所有的用户。

具体的介绍参考《Linux环境下的C编程指南》P355。

recvfrom(s, hdr, sizeof(CEHEADER), MSG_PEEK, (struct sockaddr*)&clntaddr,&socklen)返回值:函数返回实际读的字节数,如果出错则返回-1函数意义:接收数据包,在这里的实际意义是接收控制命令包,具体的介绍参考《Linux环境下的C编程指南》P355。

(3)pack_handle(s, hdr, &clntaddr)函数位置:该函数是在monitor.c中的controller_main()函数中调用的函数意义:对接收到的命令包进行解析并唤醒相应的线程。

将接受的指令包赋值给结构体ce_msg_t msg。

(4)_update_client(ip)函数位置:该函数是在monitor.c中的pack_handle(s, hdr, &clntaddr)函数中调用的函数意义:更新客户的IP记录_chk_client(ip)函数意义:检查客户的IP是否在记录当中_add_client(ip, h->seq)函数意义:将客户的IP保存记录(5)ce_msg_t msgtypedef struct _ce_msg{unsigned int session; /* Especially, session = 0 when this message comesfrom scenario thread. */ unsigned char seq; /* Iddo. */char dev_id[CE_ID_LEN];char cmd[CE_CMD_LEN];}ce_msg_t;该结构体用于存放解析完成后的命令以及运用共享内存接收到的CGI的命令。

(6)get_queue(msg->dev_id)函数位置:该函数是在monitor.c中的pack_handle(s, hdr, &clntaddr)函数中调用的以及在gateway.c中的gateway_main()中被调用。

函数意义:根据msg->dev_id获得device type,在这里将msg->dev_id与device_info[i].name进行比较,然后将device_info[i].type赋值给deviceType作为返回值返回。

(7)ce_put_msg(msg, q)函数位置:该函数是在monitor.c中的pack_handle(s, hdr, &clntaddr)函数中调用的以及在gateway.c中的gateway_main()中被调用。

函数意义:根据获得的deviceType来唤醒相应的线程。

模块三、运用共享内存的方式接收控制指令,并根据它来唤醒相应的线程(1)void *gateway_main(void *arg)函数位置:该函数是gateway.c的main函数函数意义:运用共、共享内存与CGI进行通信,接收命令指令存放在结构体ce_msg_t msg中。

(2)semid=semget(key,3,IPC_CREA T|0666)创建信号量semctl(semid,SERVER,SETV AL,sunion)设置信号量的初始值shmid=shmget(key,SHMDA TASIZE,IPC_CREA T|0666)创建共享内存data=shmat(shmid,0,0)将该共享内存附加到进程的地址空间以上函数都是Linux的系统函数,具体的介绍参考《Linux环境下的C编程指南》第11章进程间通信。