PCM56中文资料

MV56MCM中文手册

MVI56-MCMControlLogix 平台Modbus 通讯模块用户手册August 2003请阅读以下注意事项成功的应用这个模块需要对Allen-Bradley PLC/SLC 硬件知识和现场应用方式有充分的了解。

因此,对于负责完成应用的工作人员,了解应用需求并确保人员和设备不处于不安全或不适当的工作环境是非常重要的。

这本手册是用作帮助用户。

我们力求提供的每个信息都是准确的,而且如实的反映产品的安装要求。

为确保对本产品操作的完全理解,用户必须阅读有关A-B 硬件操作的所有Allen-Bradley应用文档。

在任何条件下,ProSoft Technology, Inc.都不负责间接的或由用户使用或应用本产品而造成的损害。

在没有得到ProSoft Technology 许可的情况下,禁止任何对本手册内容整体或部分性的复制。

本手册内容如有更改,恕不通知。

ProSoft Technology, Inc.并不承担这个义务。

并会随时改进和/或更改此文档或产品。

这些更改会阶段性的进行,以更改技术的不准确和印刷排版错误。

ProSoft Technology, Inc.1675 Chester AvenueFourth FloorBakersfield, CA 93301(661) 716-5100(661) 716-5101 Fax© ProSoft Technology, Inc. 2002August 2003ii目录目录目录 (iii)1 介绍 (1)1.1 基本概念 (1)1.2 设置模块 (1)2 理解结构框架 (3)2.1 主逻辑循环 (4)2.2 ControlLogix处理器未处于运行状态 (4)2.3 背板数据传输 (4)2.4 常规数据传输 (5)2.4.1 读数据块 (6)2.4.2 写数据块 (7)2.5 设置数据传送 (7)2.5.1 模块设置数据 (8)2.6 主站命令数据列表 (9)2.7 从站状态数据块 (10)2.8 命令控制数据块 (12)2.8.1 事件命令 (12)2.8.2 命令控制 (13)2.8.3 写设置 (14)2.8.4 热启动 (15)2.8.5 冷启动 (15)2.9 Pass-Through控制数据块 (15)2.9.1 无格式Pass-Through控制数据块 (15)2.9.2 格式Pass-Through控制数据块 (16)2.9.2.1 功能 5 (16)2.9.2.2 功能 6和16 (16)2.9.2.3 功能 15 (17)MVI56-MCM模块和ControlLogix处理器之间的数据流 (18)2.9.3 从站驱动 (18)2.9.4 主站驱动模式 (20)2.9.4.1 主站命令列表 (21)3 修改模块设置 (23)3.1 上电 (23)3.2 运行中更改参数 (23)3.3 装配模块 (23)3.4 模块数据对象 (MCMModuleDef) (29)3.4.1 设置对象 (30)3.4.1.1 数据传输参数 (MCMModule) (31)iii目录.3.4.1.2 Modbus端口参数 (MCMPort) (32)3.4.1.3 Modbus 主站命令 (MCMCmd) (33)3.4.2 状态对象 (MCMInStat) (34)3.5 用户数据对象 (34)3.6 从站轮询控制和状态 (35)3.7 Modbus 讯息数据 (35)4 修改样例梯形逻辑程序 (37)4.1 上电程序(Power Up) (37)4.2 主程序(MainRoutine) (38)4.3 读数据程序(ReadData) (38)4.4 写数据程序(WriteData) (44)5 诊断和纠错 (51)5.1 从模块读取状态数据 (51)5.1.1 硬件要求 (51)5.1.2 软件要求 (52)5.1.3 端口使用 (52)5.1.4 菜单选项 (53)5.1.4.1 A=数据分析 (53)5.1.4.1.1 1=选择端口 1 (53)5.1.4.1.2 2=选择端口 2 (54)5.1.4.1.3 5=1 mSec 标记 (54)5.1.4.1.4 6=5 mSec标记 (54)5.1.4.1.5 7=10 mSec标记 (54)5.1.4.1.6 8=50 mSec标记 (54)5.1.4.1.7 9=100 mSec标记 (54)5.1.4.1.8 0=No mSec标记 (54)5.1.4.1.9 H=Hex 格式 (54)5.1.4.1.10 A=ASCII 格式 (54)5.1.4.1.11 B=开始 (54)5.1.4.1.12 S=停止 (55)5.1.4.1.13 M = 主菜单 (55)5.1.4.2 B=块传输统计 (55)5.1.4.3 C=模块设置 (55)5.1.4.4 D=查看Modbus数据库 (56)5.1.4.5 0-9 寄存器页码代表 0-9000 (56)5.1.4.6 S=再次显示 (56)5.1.4.6.1 - = 回退 5 页 (57)5.1.4.6.2 P = 前页 (57)5.1.4.6.3 + = 跳过5 页 (57)5.1.4.6.4 N = 下页 (57)5.1.4.6.5 D = 十进制显示 (57)iv目录5.1.4.6.6 H = 十六进制显示 (57)5.1.4.6.7 F = 浮点数显示 (58)5.1.4.6.8 A = ASCII 显示 (58)5.1.4.6.9 M = 主菜单 (58)5.1.4.7 E 和 F=主站命令错误(端口1和2) (58)5.1.4.7.1 S = 再次显示 (58)5.1.4.7.2 - = 回退 2 页 (58)5.1.4.7.3 P = 前页 (58)5.1.4.7.4 + = 跳过2 页 (59)5.1.4.7.5 N = 下页 (59)5.1.4.7.6 D = 十进制显示 (59)5.1.4.7.7 H = 十六进制显示 (59)5.1.4.7.8 M = 主菜单 (59)5.1.4.8 I 和 J=主站命令列表(端口1和2) (59)5.1.4.8.1 S = 再次显示 (59)5.1.4.8.2 - = 回退5页 (59)5.1.4.8.3 P = 前页 (59)5.1.4.8.4 + = 跳过5页 (61)5.1.4.8.5 N = 下页 (61)5.1.4.8.6 M = 主菜单 (61)5.1.4.9 O and P=从站状态列表(端口1和2) (61)5.1.4.10 V=版本信息 (61)5.1.4.11 W=热启动模块 (62)5.1.4.12 Y=传送模块配置到处理器 (62)5.1.4.13 1 and 2=通讯状态(端口1和2) (63)5.1.4.14 6 and 7=端口设置(端口1和2) (63)5.1.4.15 Esc=退出程序 (63)5.2 LED 状态指示 (63)5.2.1 清除故障状态 (66)5.2.2 纠错 (67)6 电缆连接 (69)6.1 Modbus通讯端口 (69)6.1.1 连接电缆到连接器 (69)6.1.1.1 RS-232 (70)6.1.1.2 RS-485 (70)6.1.1.3 RS-422 (70)6.2 RS-232 设置/调试端口 (71)附录 A - MVI56-MCM 数据库定义 (73)附录B – MVI56-MCM 状态数据定义 (75)附录C – MVI56-MCM 设置数据定义 (77)背板设置 (77)v目录.端口1 设置 (78)端口2 设置 (80)端口1 命令 (82)端口2 命令 (82)各种状态 (82)命令控制 (84)附录 D – MVI56-MCM命令控制 (85)附录 E – 产品规格 (87)总体规格 (87)从站功能规格 (88)Modbus主站功能规格 (88)外形 (88)ControlLogix 接口 (88)硬件规格 (88)支持,服务和保证 (91)viIntroduction1 介绍MVI56-MCM (“Modbus通讯模块”) 产品可以让Allen-Bradley ControlLogix I/O 兼容处理器轻松的和其它Modbus协议兼容设备取得通讯。

MPC564MZP40中文资料

MOTOROLA SEMICONDUCTOR PRODUCT BRIEFThis document contains information on a new product. Specifications and information herein are subject to change without notice.MPC561PB/DRev. 1, December 2001MPC561/MPC562 MPC563/MPC564Product BriefMPC561/MPC562 / MPC563/MPC564 RISC MCUIncluding Peripheral Pin Multiplexing withFlash and Code Compression OptionsFeaturesThe MPC561/MPC562 / MPC563/MPC564 are members of the Motorola MPC500 RISC Microcontrollerfamily. As shown in the block diagram, they are composed of:• High performance CPU system— High performance core• Single issue integer core• Compatible with PowerPC instruction set architecture• Precise exception model• Floating point• Extensive system development support— On-chip watchpoints and breakpoints— Program flow tracking— Background debug mode (BDM)— IEEE-ISTO Nexus 5001-1999 Class 3 Debug Interface— MPC500 system interface (USIU, BBC, L2U)— Fully static design— Four major power saving modes• On, doze, sleep, deep-sleep and power-down— 32-Kbyte static RAM (CALRAM)— 512-Kbyte flash (UC3F) on MPC563/MPC564— General-purpose I/O support• On address (24) and data (32) pins• 16 GPIO in MIOS14• Many peripheral pins can be used as GPIO when not used as primary functions• 2.6-V outputs on external bus pins• PPM (peripheral pin multiplexing with parallel-to-serial driver) module• Available in package or die— Plastic ball grid array (PBGA) packagingKey Feature DetailsMPC500 System Interface (USIU)• System configuration and protection features:— Periodic-interrupt timer— Bus monitor— Software watchdog timer— Real-time clock (RTC)元器件交易网— Decrementer— Time base• Clock synthesizer• Power management• Reset controller• External bus interface that tolerates 5-V inputs, provides 2.6-V outputs and supports multiple-mas-ter designs• Enhanced interrupt controller that supports up to eight external and 40 internal interrupts, simpli-fies the interrupt structure and decreases interrupt processing time• USIU supports dual mapping to map part of one internal/external memory to another external memory• USIU supports dual mapping of flash on MPC563 and MPC564 to move part of internal flash mem-ory to external bus for development• External bus, supporting non-wraparound burst for instruction fetches, with up to 8 instructions per memory cycleBurst Buffer Controller (BBC) Module• Support for enhanced interrupt controller (EIC)• Support for enhanced exception table relocation feature• Branch target buffer• Contains 2-Kbytes of decompression RAM (DECRAM) for code compression. This RAM may also be used as general-purpose RAM when code compression feature not used.Flexible Memory Protection Unit• Flexible memory protection units (MPU) in BBC and L2U• Default attributes available in one global entry• Attribute support for speculative accesses• Up to eight memory regions are supported, four for data and four for instructionsMemory Controller• Four flexible chip selects via memory controller• 24-bit address and 32-bit data buses• 4-Kbyte to one 16-Mbyte (data) or four-Gbyte (instruction) region size support• Supports enhanced external burst• Up to eight-beat transfer bursts, two-clock minimum bus transactions• Use with SRAM, EPROM, flash and other peripherals• Byte selects or write enables• 32-bit address decodes with bit masks• Four regions512-Kbytes of CDR3 Flash EEPROM Memory (UC3F) – MPC563 Only• One 512-Kbyte module• Page read mode• Block (64 Kbytes) erasable• External 4.75- to 5.25-V VFLASH power supply for program, erase, and read operations32-Kbyte static RAM (CALRAM)• Composed of one 32-Kbyte CALRAM module— 28-Kbyte static RAM— 4-Kbyte calibration (overlay) RAM feature that allows calibration of flash-based constants • Eight 512-byte overlay regions• One clock fast accesses• Two-clock cycle access option for power saving• Keep-alive power (VDDSRAM) for data retentionGeneral-Purpose I/O Support• 24 Address pins and 32 data pins can be used for general-purpose I/O in single-chip mode • 16 GPIO in MIOS14• Many peripheral pins can be used as GPIO when not used as primary functions• 2.6-V outputs on external bus pins• 5-V outputs with slew rate controlNEXUS Debug Port (Class 3)• Compliant with Class 3 of the IEEE-ISTO Nexus 5001-1999• Program trace via branch trace messaging (BTM)• Data trace via data write messaging (DWM) and data read messaging (DRM)• Ownership trace via ownership trace messaging (OTM)• Run-time access to on-chip memory map and MPC5xx special purpose registers (SPRs) via the READI read/write access protocol• Watchpoint messaging via the auxiliary port• Reduced-port mode (1 MDI, 2 MDO) or full-port mode (2 MDI. 8 MDO)• All features configurable and controllable via the auxiliary port• Security features for production environment• Supports the RCPU debug mode via the auxiliary port• READI module can be reset independent of system resetIntegrated I/O SystemTwo Time Processor Units (TPU3)• True 5-V I/O• Two time processing units (TPU3) with16 channels each• Each TPU3 is a micro-coded timer subsystem• Eight-Kbytes of dual port TPU RAM (DPTRAM) shared by two TPU3 modules for TPU micro-code22-Channel Modular I/O System (MIOS14)• Six modulus counter sub-modules (MCSM)• 10 double-action sub-modules (DASM)• 12 dedicated PWM sub-modules (PWMSM)• One MIOS14 16-bit parallel port I/O sub-modules (MPIOSM)Two Enhanced Queued Analog-to-Digital Converter Modules (QADC64E)• Two queued analog-to-digital converter modules (QADC64_A, QADC64_B) providing a total of 32 analog channels• 16 analog input channels on each QADC64E module using internal multiplexing• Directly supports up to four external multiplexers• Up to 41 total input channels on the two QADC64E modules with external multiplexing• Software configurable to operate in Enhanced or Legacy (MPC555 compatible) mode• Unused analog channels can be used as digital input/output pins— GPIO on all channels in Enhanced mode• 10-bit A/D converter with internal sample/hold• Typical conversion time of less than 5 µs (>200 K samples/second)• Two conversion command queues of variable length• Automated queue modes initiated by:— External edge trigger— Software command— Periodic/interval timer within QADC64E module, that can be assigned to both queue 1 and 2— External Gated trigger (queue 1only)• 64 result registers— Output data is right- or left-justified, signed or unsigned• Alternate reference input (ALTREF), with control in the conversion command word (CCW)Three CAN 2.0B Controller (TouCAN) Modules• Three TouCAN modules (TOUCAN_A, TOUCAN_B, TOUCAN_C)• Each TouCAN provides the following features:— 16 message buffers each, programmable I/O modes— Maskable interrupts— Independent of the transmission medium (external transceiver is assumed)— Open network architecture, multi-master concept— High immunity to EMI— Short latency time for high-priority messages— Low-power sleep mode, with programmable wake-up on bus activity— TOUCAN_C pins are shared with MIOS14 GPIO or QSMCMQueued Serial Multi-Channel Module (QSMCM)• One queued serial module with one queued SPI and two SCIs (QSMCM)• QSMCM matches full MPC555 QSMCM functionality• Queued SPI— Provides full-duplex communication port for peripheral expansion or inter-processor commu-nication— Up to 32 preprogrammed transfers, reducing overhead— Synchronous serial interface with baud rate of up to system clock / 4— Four programmable peripheral-selects pins:— Support up to 16 devices with external decoding— Support up to eight devices with internal decoding— Special wrap-around mode allows continuous sampling of a serial peripheral for efficient inter-facing to serial analog-to-digital (A/D) converters• SCI— UART mode provides NRZ format and half- or full-duplex interface— 16 register receive buffers and 16 register transmit buffers on one SCI— Advanced error detection and optional parity generation and detection— Word-length programmable as eight or nine bits— Separate transmitter and receiver enable bits, and double buffering of data— Wake-up functions allow the CPU to run uninterrupted until either a true idle line is detected, or a new address byte is receivedPeripheral Pin Multiplexing (PPM) PPM• Synchronous serial interface between the microprocessor and an external device• Four internal parallel data sources can be multiplexed through the PPM— TPU3_A: 16 channels— TPU3_B: 16 channels— MIOS14: 12 PWM channels, 4 MDA channels— Internal GPIO: 16 general-purpose inputs, 16 general-purpose outputs• Software configurable stream size• Software configurable clock (TCLK) based on system clock• Software selectable clock modes (SPI mode and TDM mode)• Software selectable operation modes— Continuous mode— Start-transmit-receive (STR) mode• Software configurable internal modules interconnect (shorting)MPC561/MPC562 / MPC563/MPC564 Optional FeaturesThe following are optional features of the MPC561/MPC562 / MPC563/MPC564:• 56-MHz operation (40 MHz is default)• Code compression supported on the MPC562 and the MPC564— Compression reduces instruction memory requirements by 40-50%— Compression optimized for automotive (non-cached) applications • 512 Kbytes flash (available on the MPC563/MPC564 only)— Single array— Page mode read— Block (64 Kbytes) erasable— External 4.75- to 5.25-V VFLASH program, erase, and read power supplyFigure 1 MPC561/MPC562 / MPC563/MPC564 Block DiagramE-BUSMPC5xx Core L-BUSU-BUSIMB3+FPUSIUBuffer Burst Int.L2U I/FUIMB QSMCM MIOS14DPTRAM8-Kbyte READIQADC64JTAGTPU3QADC64TPU332-Kbyte CALRAM 28-Kbyte (No Overlay)4-Kbyte OverlayTou CAN Tou CANPPMSRAM Tou CAN Controller512 Kbytes Flash (on MPC563/MPC564 only)Figure 2 MPC561 / MPC563 Internal Memory Map4-Kbyte Overlay Section0x30 7FFF 0x2F FFFF 0x30 00000x00 00000x38 00000x38 3FFF 0x3F FFFF0x2F C0000x2F BFFF 0x30 80000x37 FFFF 0x38 40000x07 FFFF 0x3F 7FFF 0x3F 80000x08 00000x38 00FF 0x38 01000x2F 80000x2F 7FFF UC3F Flash*512 KbytesReserved for Flash 2,605 KbytesBBC DECRAM 2 Kbytes USIU & Flash Control16 KbytesUIMB I/F & IMB Modules 32 KbytesReserved for IMB 491 Kbytes CALRAM/READI Control 256 bytes Reserved (L-bus Control)~32 KbytesReserved (L-bus Mem)464 KbytesCALRAM 32 Kbytes*NOTE: Only available on MPC563/MPC564.0x3F F0000x30 00000x30 7FFFDPTRAM (8 Kbytes)QSMCM (1 Kbyte)MIOS14 (4 Kbytes)TOUCAN_A (1 Kbyte)TOUCAN_B (1 Kbyte)UIMB Registers (128 bytes)TPU3_A (1 Kbyte)TPU3_B (1 Kbyte)QADC64_A (1 Kbyte)QADC64_B (1 Kbyte)DPTRAM Control (32 bytes)USIU Control Registers0x2F C0000x30 7C000x30 70000x30 60000x30 54000x30 50000x30 4C000x30 48000x30 44000x30 40000x30 20000x30 7400Reserved (8160 bytes)Reserved (2 Kbytes)Reserved (896 bytes)0x30 78000x2F C8000x30 7F80TOUCAN_C (1 Kbyte)0x30 5C00PPM (64 bytes)0x30 5C80Reserved (960 bytes) 0x30 0020UC3F Control Registers*0x2F 8800 Reserved for BBC 0x2F A000 BBC CONTROLFigure 3 MPC561 / MPC563 Ball Map1234567891011121314151617181920212223242526AVDDVSSVSSVSSA_TPUCH3A_TPUCH7A_TPUCH11A_TPUCH15VSSAVRLA_AN3_A NZ_PQB3A_AN51_P QB7A_AN55_PQA3A_AN56_P QA4B_AN0_AN W_PQB0B_AN48_PQB4B_AN52_M A0_PQA0B_AN56_P QA4VSSETRIG2_PCS7MDA13MDA28VSSVSSVDDVSSAB VSS VDD VSS VSS A_TPUCH2A_TPUCH6A_TPUCH10A_TPUCH14VSSA ALTREF A_AN2_A NY_PQB2A_AN50_P QB6A_AN54_MA2_PQ A2A_AN58_P QA6B_AN1_AN X_PQB1B_AN49_PQB5B_AN53_M A1_PQA1B_AN57_P QA5VSSETRIG1_PCS6MDA14MDA29VSSVDDVSSQVDDLBC VSS VSS VDD VSS A_TPUCH1A_TPUCH4A_TPUCH8A_TPUCH12NVDDL VRH A_AN0_A NW_PQB 0A_AN48_P QB4A_AN52_MA0_PQ A0A_AN59_P QA7B_AN2_AN Y_PQB2B_AN50_PQB6B_AN54_M A2_PQA2B_AN58_P QA6VDDH MDA11MDA15VDDH VDD VSS QVDDL VSS CD VSS VSS VSS VDD VSS A_TPUCH5A_TPUCH9A_TPUCH13NVDDL VDDA A_AN1_A NX_PQB1A_AN49_P QB5A_AN53_MA1_PQ A1A_AN57_P QA5B_AN3_AN Z_PQB3B_AN51_PQB7B_AN55_P QA3B_AN59_P QA7VDDH MDA12MDA27VDD VSS QVDDL VSS VSS DE VDDH VSS VSS VSS QVDDL VSS VSS VSS EF B_T2CLK_P CS4A_T2CLK_PCS5A_TPUCH 0QVDDL VDDH MDA30MDA31MPWM0_MDI1F GB_TPUCH12B_TPUCH13B_TPUCH 14B_TPUCH15MPWM1_MDO2MPWM16MPWM3_PP M_RX1MPWM2_PP M_TX1GH B_TPUCH8B_TPUCH9B_TPUCH 10B_TPUCH11MPWM17_M DO3MPWM18_MD O6MPWM19_MDO7MPIO32B5_MDO5HJ B_TPUCH4B_TPUCH5B_TPUCH6B_TPUCH7MPIO32B6_MPWM4_MDO6MPIO32B7_MP WM5MPIO32B8_MPWM20MPIO32B9_MPWM21JK B_TPUCH0B_TPUCH1B_TPUCH2B_TPUCH3MPIO32B12_C_CNTX0MPIO32B11_C _CNRX0MPIO32B10_PPM_TSYNC MPIO32B13_PPM_TCLK KLJCOMP_RS TI_B TCK_DSCK_MCKI B_CNRX0B_CNTX0VSS VSS VSS VSS VSS VSS VF0_MPIO32B0_MDO1VF1_MPIO32B 1_MCKO MPIO32B15_PPM_TX0MPIO32B14_PPM_RX0LM TDI_DSDI_MDI0TMS_EVTI _B VDDSRA MTDO_DSDO_MDO0VSS VSS VSS VSS VSS VSS A_CNTX0VF2_MPIO32B2_MSEI_B VFLS0_MPIO32B3_MSEO_BVFLS1_MPIO 32B4M N IRQ3_B_KR_B_RETRY _B_SGPIO C3IWP0_VFL S0IWP1_VFL S1SGPIOC6_FRZ_PTR_BVSS VSS VSS VSS VSS VSSPCS2_QGPI O2PCS1_QGPIO1PCS0_SS_B_QGPIO0A_CNRX0NP IRQ4_B_AT 2_SGPIOC4IRQ2_B_CR_B_SGPIOC2_MDO5_MTSIRQ0_B_S GPIOC0_MDO4IRQ1_B_RSV_B_SGPIOC1VSS VSS VSS VSS VSS VSSSCK_QGPIO 6MOSI_QGPIO5MISO_QGPIO4PCS3_QGPIO3PR SGPIOC7_IRQOUT_B_LWP0BB_B_VF2_IWP3BG_B_VF 0_LWP1BR_B_VF1_IWP2VSS VSS VSS VSS VSS VSSRXD1_QGPI 1TXD2_QGPO2_C_CNTX0TXD1_QGPO1PULL-SEL RTWE_B_AT0WE_B_AT1WE_B_AT 2WE_B_AT 3VSS VSS VSS VSS VSS VSS EPEE BOEPEE VDDHRXD2_QGPI2_C_CNRX0TU CS0_B CS1_B CS2_BCS3_BCLKOUT VSSF VDDF VFLASH UV RD_WR_B OE_B TEA_B TSIZ0VDD EXTCLK VSS ENGCLK_BUCLK VW TSIZ1TS_B TA_B BDIP_B HRESET_B SRESET_B PORESET_B _TRST_BKAPWRWY BURST_BBI_B_STS_B ADDR_SG PIOA12ADDR_SG PIOA11NVDDLIRQ7_B_MODC K3RSTCONF_B_TEXPVDDSYN YAA VSS VSS VSS QVDDL VSS VSS VSS XFC AA ABVSSVSSQVDDLVSSQVDDLVSSVSSVSSSYNABAC VSS QVDDL VSS NVDDL VSS ADDR_SGP IOA10ADDR_SG PIOA18ADDR_SGPI OA20ADDR_SGPIOA23NVDDL ADDR_S GPIOA26DATA_SG PIOD1DATA_SG PIOD5DATA_SGPIOD7NVDDL DATA_SG PIOD9DATA_SGP IOD11DATA_SGPIOD12NVDDL DATA_SGPIOD14VSS VDD VSS QVDDL VSS EXTAL ACAD QVDDL VSS NVDDL VSS VSS QVDDLADDR_SG PIOA13ADDR_SGPI OA16ADDR_SG PIOA19ADDR_SGP IOA21ADDR_S GPIOA24ADDR_SG PIOA25DATA_SG PIOD0DATA_SG PIOD28DATA_SGP IOD26DATA_SG PIOD24DATA_SGP IOD22DATA_SG PIOD13DATA_SGPI OD15DATA_SGPIOD16IRQ5_B_SGPIOC5_MODCK1VSS VDD VSS QVDDL XTAL ADAE VSS NVDDL VSS VSS VSS QVDDL ADDR_SG PIOA14ADDR_SGPI OA17ADDR_SG PIOA31ADDR_SGP IOA30ADDR_S GPIOA28ADDR_SG PIOA29DATA_SG PIOD30DATA_SG PIOD29DATA_SGP IOD27DATA_SG PIOD25DATA_SGP IOD23DATA_SG PIOD21DATA_SGPI OD19DATA_SGPIOD17IRQ6_B_MODCK2VSS VSS VDD VSS QVDDL AEAF NVDDL VSS VSS VSS VDDH VSS ADDR_SG PIOA15ADDR_SGPI OA9ADDR_SG PIOA8ADDR_SGP IOA22ADDR_S GPIOA27DATA_SG PIOD31DATA_SG PIOD3DATA_SG PIOD2DATA_SGP IOD4DATA_SG PIOD6DATA_SGP IOD8DATA_SG PIOD10DATA_SGPI OD20DATA_S GPIOD18VDDH VSS VSS VSS VDD VSS AF1234567891011121314151617181920212223242526MPC561 / MPC563 Ball Map(As viewed from top, through the package and silicon)NOTE: The flash balls are only available on the MPC563 and MPC564. These are no connect balls onthe MPC561 and MPC562. Flash supplies and inputs are located on the following balls: T23, T24, U24, U25. U26.Ordering InformationTable 2 lists the documents that provide a complete description of the MPC561/563 and are required to design properly with the part. Documentation is available from a local Motorola distributor, a Motorola semiconductor sales office, a Motorola Literature Distribution Center, or through the Motorola Semicon-ductor documentation page on the Internet (the source for the latest information).Table 1 MPC561/562 / MPC563/564Device Name Order Part Number 1NOTES:1. Add R2 suffix for parts shipped in tape and reel media.Package Info Temperature Range Maximum Frequency Code CompressionMPC561MPC561MZP40388 PBGA -40 – 125° C 40 MHz No MPC561MPC561CZP40388 PBGA -40 – 85° C 40 MHz No MPC561MPC561MZP56388 PBGA -40 – 125° C 56 MHz No MPC561MPC561CZP56388 PBGA -40 – 85° C 56 MHz No MPC562MPC562MZP40388 PBGA -40 – 125° C 40 MHz Yes MPC562MPC562CZP40388 PBGA -40 – 85° C 40 MHz Yes MPC562MPC562MZP56388 PBGA -40 – 125° C 56 MHz Yes MPC562MPC562CZP56388 PBGA -40 – 85° C 56 MHz Yes MPC563MPC563MZP40388 PBGA -40 – 125° C 40 MHz No MPC563MPC563CZP40388 PBGA -40 – 85° C 40 MHz No MPC563MPC563MZP56388 PBGA -40 – 125° C 56 MHz No MPC563MPC563CZP56388 PBGA -40 – 85° C 56 MHz No MPC564MPC564MZP40388 PBGA -40 – 125° C 40 MHz Yes MPC564MPC564CZP40388 PBGA -40 – 85° C 40 MHz Yes MPC564MPC564MZP56388 PBGA -40 – 125° C 56 MHz Yes MPC564MPC564CZP56388 PBGA-40 – 85° C56 MHzYesTable 2 Available DocumentationDocument Number TitleMPC561_3RM/ADMPC561/MPC563 Reference ManualAN1821/D Exception Table Relocation and Multi-Processor Address Mapping in the Embedded MPC5XX Family AN2109/D MPC555 Interrupts.AN2127/DEMC Guidelines for MPC500-Based Automotive Powertrain SystemsMPC561/MPC563 PRODUCTBRIEF MOTOROLA11Motorola reserves the right to make changes without further notice to any products herein. Motorola makes no warranty,representation or guarantee regarding the suitability of its products for any particular purpose, nor does Motorola assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation consequential or incidental damages. “Typical” parameters which may be provided in Motorola data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including “Typicals” must be validated for each customer application by customer’s technical experts. Motorola does not convey any license under its patent rights nor the rights of others. Motorola products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support life, or for any other application in which the failure of the Motorola product could create a situation where personal injury or death may occur. Should Buyer purchase or use Motorola products for any such unintended or unauthorized application, Buyer shall indemnify and hold Motorola and its officers,employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that Motorola was negligent regarding the design or manufacture of the part. Motorola and are registered trademarks of Motorola, Inc. Motorola, Inc. is an Equal Opportunity/Affirmative Action Employer.OnCE, DigitalDNA, and the DigitalDNA logo are trademarks of Motorola, Inc.Order Number MPC561PB/DHow to reach us:USA/EUROPEMotorola Literature DistributionP.O. Box 5405Denver, Colorado 802171-303-675-21401-800-441-2447Technical Information Center1-800-521-6274JAPAN Motorola Japan Ltd.SPS, Technical Information Center 3-20-1, Minami-Azabu, Minato-ku Tokyo 106-8573 Japan 81-3-3440-3569ASIA/PACIFICMotorola Semiconductors H.K. Ltd.Silicon Harbour Centre2 Dai King StreetTai Po Industrial EstateTai Po, N.T., Hong Kong852-********Home Page /semiconductors。

PCM-讲解资料

干燥

脱脂 水洗 水洗 干燥 铬酸盐涂布 干燥

铬化处理剂的优点

(3) 节省Energy

: 因处理在常温下,无须加热装置。

(4) 节省劳动力

:几乎无处理液的浓度变化,因此浓度测定频率少。无须特别管理处 理液的温度,喷压,处理时间。不必进行油矿泥处理,打扫喷嘴.

(5) 低公害 ( 减少废水处理工程 )

: 因处理后不必进行水洗,所以无废水,节省废水处理费

2)热镀锌板(Hot Dipped Galvanized -Iron, HDGI, CGI, GI) :

热镀锌槽里浸泡冷轧钢板或热轧钢板以 后钢板表面形成涂锌层. 镀锌层厚,耐腐 蚀性好. 表面的花纹可以按照客户的要 求提供. 在汽车,家电产品等广泛使用。

种类(按照表面的花纹) 1) Regular Spangle 2) Minimized Spangle 3) Zero Spangle 4) Extra Smooth等 锌的涂布量100~500g/㎡, 换算成厚度为 16~70㎛左右. 基本上锌比铁硬, 锌是防腐蚀的. 镀锌层越厚加工性越不好, 耐腐蚀性好.

面漆 面漆

普通聚酯 线形聚酯

加工性及耐候性优 秀的PCM用

建筑 外裝材

加工性优秀的

家电产品

PCM家电产品用 (洗衣棋)

面漆 氟碳树脂 耐候性优秀

建筑 外裝材

背漆 底漆 底漆

环氧树脂 环氧树脂 线形聚酯

附着力及耐腐蚀性, 建筑 外裝材

耐化学性优秀

家电产品

附着力及耐腐蚀性, 耐化学性优秀

建筑 外裝材 底漆

处理.

脱脂过程模式图

钢O 板I

L

钢 板

碱浸透,界面活性剂吸附

OIL OIL

LM56CIM中文资料

LM56Dual Output Low Power ThermostatGeneral DescriptionThe LM56is a precision low power thermostat.Two stable temperature trip points (V T1and V T2)are generated by divid-ing down the LM561.250V bandgap voltage reference using 3external resistors.The LM56has two digital outputs.OUT1goes LOW when the temperature exceeds T1and goes HIGH when the the temperature goes below (T1–T HYST ).Similarly,OUT2goes LOW when the temperature exceeds T2and goes HIGH when the temperature goes below (T2–T HYST ).T HYST is an internally set 5˚C typical hysteresis.The LM56is available in an 8-lead Mini-SO8surface mount package and an 8-lead small outline package.Applicationsn Microprocessor Thermal Management n Appliancesn Portable Battery Powered 3.0V or 5V Systems n Fan Controln Industrial Process Control n HVAC Systemsn Remote Temperature Sensing nElectronic System ProtectionFeaturesn Digital outputs support TTL logic levels n Internal temperature sensorn 2internal comparators with hysteresis n Internal voltage referencen Currently available in 8-pin SO plastic package nFuture availability in the 8-pin Mini-SO8packageKey Specificationsn Power Supply Voltage 2.7V–10V n Power Supply Current 230µA (max)n V REF1.250V ±1%(max)n Hysteresis Temperature 5˚Cn Internal Temperature SensorOutput Voltage (+6.20mV/˚C x T)+395mV n Temperature Trip Point Accuracy:LM56BIMLM56CIM +25˚C±2˚C (max)±3˚C (max)+25˚C to +85˚C ±2˚C (max)±3˚C (max)−40˚C to +125˚C±3˚C (max)±4˚C (max)Simplified Block Diagram and Connection DiagramOrder Number LM56BIM LM56BIMX LM56CIM LM56CIMX LM56BIMM LM56BIMMX LM56CIMM LM56CIMMX NSPackage Number M08A M08A M08A M08A MUA08A MUA08A MUA08A MUA08A SOP-8SOP-8SOP-8SOP-8MSOP-8MSOP-8MSOP-8MSOP-8Transport Media 2500Units2500Units3500Units3500UnitsRail Tape &Reel Rail Tape &Reel Rail Tape &ReelRail Tape &ReelPackage MarkingLM56BIMLM56BIMLM56CIMLM56CIMT02BT02BT02CT02CDS012893-1DS012893-2April 2000LM56Dual Output Low Power Thermostat©2000National Semiconductor Corporation Typical ApplicationDS012893-3V T1=1.250V x (R1)/(R1+R2+R3)V T2=1.250V x (R1+R2)/(R1+R2+R3)where:(R1+R2+R3)=27k ΩandV T1or T2=[6.20mV/˚C x T]+395mV therefore:R1=V T1/(1.25V)x 27k ΩR2=(V T2/(1.25V)x 27k Ω)−R1R3=27k Ω−R1−R2FIGURE 1.Microprocessor Thermal ManagementL M 56 2Absolute Maximum Ratings(Note1)Input Voltage12V Input Current at any pin(Note2)5mA Package Input Current(Note2)20mA Package Dissipation at T A=25˚C(Note3)900mW ESD Susceptibility(Note4)Human Body Model1000V Machine Model200V Soldering InformationSO Package(Note5):Vapor Phase(60seconds)215˚CInfrared(15seconds)220˚C Storage Temperature−65˚C to+150˚COperating Ratings(Note1)Operating Temperature Range T MIN≤T A≤T MAX LM56BIM,LM56CIM−40˚C≤T A≤+125˚C Positive Supply Voltage(V+)+2.7V to+10V Maximum V OUT1and V OUT2+10VLM56Electrical CharacteristicsThe following specifications apply for V+=2.7V DC,and V REF load current=50µA unless otherwise specified.Boldface lim-its apply for T A=T J=T MIN to T MAX;all other limits T A=T J=25˚C unless otherwise specified.Typical LM56BIM LM56CIM UnitsSymbol Parameter Conditions(Note6)Limits Limits(Limits)(Note7)(Note7)Temperature SensorTrip Point Accuracy(Includes±2±3˚C(max)V REF,Comparator Offset,and+25˚C≤T A≤+85˚C±2±3˚C(max)Temperature Sensitivity errors)−40˚C≤T A≤+125˚C±3±4˚C(max)Trip Point Hysteresis T A=−40˚C433˚C(min)66˚C(max)T A=+25˚C5 3.5 3.5˚C(min)6.5 6.5˚C(max)T A=+85˚C6 4.5 4.5˚C(min)7.57.5˚C(max)T A=+125˚C644˚C(min)88˚C(max) Internal Temperature+6.20mV/˚CSensitivityTemperature Sensitivity Error±2±3˚C(max)±3±4˚C(max) Output Impedance−1µA≤I L≤+40µA15001500Ω(max)Line Regulation+3.0V≤V+≤+10V,+25˚C≤T A≤+85˚C±0.36±0.36mV/V(max)+3.0V≤V+≤+10V,−40˚C≤T A<25˚C±0.61±0.61mV/V(max)+2.7V≤V+≤+3.3V±2.3±2.3mV(max)V T1and V T2Analog InputsI BIAS Analog Input Bias Current150300300nA(max)V IN Analog Input Voltage Range V+−1VGND VV OS Comparator Offset288mV(max)V REF OutputV REF V REF Nominal 1.250V V V REF Error±1±1%(max)±12.5±12.5mV(max)∆V REF/∆V+Line Regulation+3.0V≤V+≤+10V0.130.250.25mV/V(max)+2.7V≤V+≤+3.3V0.15 1.1 1.1mV(max)∆V REF/∆I L Load Regulation Sourcing+30µA≤I L≤+50µA0.150.15mV/µA(max)LM563LM56Electrical CharacteristicsThe following specifications apply for V +=2.7V DC ,and V REF load current =50µA unless otherwise specified.Boldface lim-its apply for T A =T J =T MIN to T MAX ;all other limits T A =T J =25˚C unless otherwise specified.Symbol Parameter Conditions Typical Limits Units (Note 6)(Note 7)(Limits)V +Power Supply I SSupply Current V +=+10V 230µA (max)V +=+2.7V 230µA (max)Digital Outputs I OUT(“1”)Logical “1”Output Leakage V +=+5.0V1µA (max)CurrentV OUT(“0”)Logical “0”Output VoltageI OUT =+50µA0.4V (max)Note 1:Absolute Maximum Ratings indicate limits beyond which damage to the device may occur.Operating Ratings indicate conditions for which the device is func-tional,but do not guarantee specific performance limits.For guaranteed specifications and test conditions,see the Electrical Characteristics.The guaranteed speci-fications apply only for the test conditions listed.Some performance characteristics may degrade when the device is not operated under the listed test conditions.Note 2:When the input voltage (V I )at any pin exceeds the power supply (V I <GND or V I >V +),the current at that pin should be limited to 5mA.The 20mA maxi-mum package input current rating limits the number of pins that can safely exceed the power supplies with an input current of 5mA to four.Note 3:The maximum power dissipation must be derated at elevated temperatures and is dictated by T Jmax (maximum junction temperature),θJA (junction to am-bient thermal resistance)and T A (ambient temperature).The maximum allowable power dissipation at any temperature is P D =(T Jmax –T A )/θJA or the number given in the Absolute Maximum Ratings,whichever is lower.For this device,T Jmax =125˚C.For this device the typical thermal resistance (θJA )of the different package types when board mounted follow:Package TypeθJA M08A 110˚C/W MUA08A250˚C/WNote 4:The human body model is a 100pF capacitor discharge through a 1.5k Ωresistor into each pin.The machine model is a 200pF capacitor discharged directly into each pin.Note 5:See AN450“Surface Mounting Methods and Their Effects on Product Reliability”or the section titled “Surface Mount”found in any post 1986National Semi-conductor Linear Data Book for other methods of soldering surface mount devices.Note 6:Typicals are at T J =T A =25˚C and represent most likely parametric norm.Note 7:Limits are guaranteed to National’s AOQL (Average Outgoing Quality Level).L M 56 4Typical Performance CharacteristicsQuiescent Current vs TemperatureDS012893-4V REF Output Voltage vsLoad CurrentDS012893-5OUT1and OUT2VoltageLevels vs Load CurrentDS012893-32Trip Point Hysteresis vs TemperatureDS012893-7Temperature SensorOutput Voltage vsTemperatureDS012893-8Temperature SensorOutput Accuracy vsTemperatureDS012893-9Trip PointAccuracy vs TemperatureDS012893-10Comparator Bias Currentvs TemperatureDS012893-11OUT1and OUT2LeakageCurrent vs TemperatureDS012893-12LM565Typical Performance Characteristics(Continued)V TEMP OutputLine Regulation vs TemperatureDS012893-31V REF Start-Up ResponseDS012893-13V TEMP Start-Up ResponseDS012893-14 LM566Functional Description1.0PIN DESCRIPTIONV+This is the positive supply voltage pin.This pin should be bypassed with0.1µF capacitor toground.GND This is the ground pin.V REF This is the1.250V bandgap voltage reference out-put pin.In order to maintain trip point accuracy thispin should source a50µA load.V TEMP This is the temperature sensor output pin.OUT1This is an open collector digital output.OUT1is ac-tive LOW.It goes LOW when the temperature isgreater than T1and goes HIGH when the tempera-ture drops below T1–5˚C.This output is not in-tended to directly drive a fan motor.OUT2This is an open collector digital output.OUT2is ac-tive LOW.It goes LOW when the temperature isgreater than the T2set point and goes HIGH whenthe temperature is less than T2–5˚C.This output isnot intended to directly drive a fan motor.V T1This is the input pin for the temperature trip point voltage for OUT1.V T2This is the input pin for the low temperature trip point voltage for OUT2.DS012893-15DS012893-16V T1=1.250V x(R1)/(R1+R2+R3)V T2=1.250V x(R1+R2)/(R1+R2+R3)where:(R1+R2+R3)=27kΩandV T1or T2=[6.20mV/˚C x T]+395mV therefore:R1=V T1/(1.25V)x27kΩR2=(V T2/(1.25V)x27k)Ω–R1R3=27kΩ−R1−R2LM567Application Hints2.0LM56TRIP POINT ACCURACY SPECIFICATION For simplicity the following is an analysis of the trip point ac-curacy using the single output configuration show in Figure 2with a set point of 82˚C.Trip Point Error Voltage =V TPE ,Comparator Offset Error for V T1E Temperature Sensor Error =V TSE Reference Output Error =V RE1.V TPE =±V T1E −V TSE +V REWhere:2.V T1E =±8mV (max)3.V TSE =(6.20mV/˚C)x (±3˚C)=±18.6mV4.V RE =1.250V x (±0.01)R2/(R1+R2)Using Equations from page 1of the datasheet.V T1=1.25VxR2/(R1+R2)=(6.20mV/˚C)(82˚C)+395mV Solving for R2/(R1+R2)=0.7227then,5.V RE = 1.250V x (±0.01)R2/(R1+R2)=(0.0125)x (0.7227)=±9.03mVThe individual errors do not add algebraically because,the odds of all the errors being at their extremes are rare.This is proven by the fact the specification for the trip point accuracy stated in the Electrical Characteristic for the temperaturerange of −40˚C to +125˚C,for example,is specified at ±3˚C for the LM56BIM.Note this trip point error specification does not include any error introduced by the tolerance of the ac-tual resistors used,nor any error introduced by power supply variation.If the resistors have a ±0.5%tolerance,an additional error of ±0.4˚C will be introduced.This error will increase to ±0.8˚C when both external resistors have a ±1%tolerance.3.0BIAS CURRENT EFFECT ON TRIP POINT ACCURACYBias current for the comparator inputs is 300nA (max)each,over the specified temperature range and will not introduce considerable error if the sum of the resistor values are kept to about 27k Ωas shown in the typical application of Figure 1.This bias current of one comparator input will not flow if the temperature is well below the trip point level.As the tem-perature approaches trip point level the bias current will start to flow into the resistor network.When the temperature sen-sor output is equal to the trip point level the bias current will be 150nA (max).Once the temperature is well above the trip point level the bias current will be 300nA (max).Therefore,the first trip point will be affected by 150nA of bias current.The leakage current is very small when the comparator input transistor of the different pair is off (see Figure 3).The effect of the bias current on the first trip point can be de-fined by the following equations:where I B =300nA (the maximum specified error).The effect of the bias current on the second trip point can be defined by the following equations:where I B =300nA (the maximum specified error).The closer the two trip points are to each other the more sig-nificant the error is.Worst case would be when V T1=V T2=V REF /2.DS012893-17FIGURE 2.Single Output ConfigurationL M 56 8Application Hints(Continued)4.0MOUNTING CONSIDERATIONSThe majority of the temperature that the LM56is measuring is the temperature of its leads.Therefore,when the LM56is placed on a printed circuit board,it is not sensing the tem-perature of the ambient air.It is actually sensing the tem-perature difference of the air and the lands and printed circuit board that the leads are attached to.The most accurate tem-perature sensing is obtained when the ambient temperature is equivalent to the LM56’s lead temperature.As with any IC,the LM56and accompanying wiring and cir-cuits must be kept insulated and dry,to avoid leakage and corrosion.This is especially true if the cirucit may operate at cold temperatures where condensation can occur. Printed-circuit coatings and varnishes such as Humiseal and epoxy paints or dips are often used to ensure that moisture cannot corrode the LM56or its connections.DS012893-18FIGURE3.Simplified SchematicLM56 9Application Hints(Continued)5.0V REF AND V TEMP CAPACTIVE LOADINGThe LM56V REF and V TEMP outputs handle capacitive load-ing well.Without any special precautions,these outputs can drive any capacitive load as shown in Figure 4.6.0NOISY ENVIRONMENTSOver the specified temperature range the LM56V TEMP out-put has a maximum output impedance of 1500Ω.In an ex-tremely noisy environment it may be necessary to add some filtering to minimize noise pickup.It is recommended that 0.1µF be added from V +to GND to bypass the power supply voltage,as shown in Figure 4.In a noisy environment it may be necessary to add a capacitor from the V TEMP output to ground.A 1µF output capacitor with the 1500Ωoutput im-pedance will form a 106Hz lowpass filter.Since the thermal time constant of the V TEMP output is much slower than the 9.4ms time constant formed by the RC,the overall response time of the V TEMP output will not be significantly affected.For much larger capacitors this additional time lag will increase the overall response time of the LM56.7.0APPLICATIONS CIRCUITSThe circuit shown in Figure 5will reduce the effective bias current error for V T2as discussed in Section 3.0to be equivalent to the error term of V T1.For this circuit the effect of the bias current on the first trip point can be defined by the following equations:where I B =300nA (the maximum specified error).Similarly,bias current affect on V T2can be defined by:where I B =300nA (the maximum specified error).The current shown in Figure 6is a simple overtemperature detector for power devices.In this example,an audio power amplifier IC is bolted to a heat sink and an LM56Celsius temperature sensor is mounted on a PC board that is bolted to the heat sink near the power amplifier.To ensure that the sensing element is at the same temperature as the heat sink,the sensor’s leads are mounted to pads that have feed throughs to the back side of the PC board.Since the LM56is sensing the temperature of the actual PC board the back side of the PC board also has large ground plane to help conduct the heat to the device.The comparator’s output goes low if the heat sink temperature rises above a threshold set by R1,R2,and the voltage reference.This fault detection output from the comparator now can be used to turn on a cooling fan.The circuit as shown in design to turn the fan on when heat sink temperature exceeds about 80˚C,and to turn the fan off when the heat sink temperature falls below ap-proximately 75˚C.DS012893-19FIGURE 4.Loading of V REF and V TEMPDS012893-20FIGURE 5.Reducing Errors Caused by Bias CurrentL M 5610Application Hints(Continued)DS012893-21FIGURE 6.Audio Power Amplifier Overtemperature DetectorDS012893-22FIGURE 7.Simple ThermostatLM5611Physical Dimensionsinches (millimeters)unless otherwise noted8-Lead (0.150"Wide)Molded Small Outline Package,JEDEC Order Number LM56BIM,LM56BIMX,LM56CIM or LM56CIMXNS Package Number M08AL M 56 12Physical Dimensionsinches (millimeters)unless otherwise noted (Continued)LIFE SUPPORT POLICYNATIONAL’S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF THE PRESIDENT AND GENERAL COUNSEL OF NATIONAL SEMICONDUCTOR CORPORATION.As used herein:1.Life support devices or systems are devices or systems which,(a)are intended for surgical implant into the body,or (b)support or sustain life,and whose failure to perform when properly used in accordance with instructions for use provided in the labeling,can be reasonably expected to result in a significant injury to the user.2.A critical component is any component of a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system,or to affect its safety or effectiveness.National Semiconductor Corporation AmericasTel:1-800-272-9959Fax:1-800-737-7018Email:support@National Semiconductor EuropeFax:+49(0)180-5308586Email:europe.support@Deutsch Tel:+49(0)6995086208English Tel:+44(0)8702402171Français Tel:+33(0)141918790National Semiconductor Asia Pacific Customer Response Group Tel:65-2544466Fax:65-2504466Email:ap.support@National Semiconductor Japan Ltd.Tel:81-3-5639-7560Fax:81-3-5639-75078-Lead Molded Mini Small Outline Package (MSOP)(JEDEC REGISTRATION NUMBER M0-187)Order Number LM56BIMM,LM56BIMMX,LM56CIMM,or LM56CIMMXNS Package Number MUA08ALM56Dual Output Low Power ThermostatNational does not assume any responsibility for use of any circuitry described,no circuit patent licenses are implied and National reserves the right at any time without notice to change said circuitry and specifications.。

贴片三极管bcp56最大电流_概述说明以及解释

贴片三极管bcp56最大电流概述说明以及解释1. 引言1.1 概述贴片三极管BCP56是一种常用的电子元件,它具有广泛的应用领域。

在实际应用中,BCP56的最大电流是一个重要参数,它决定了三极管能够承受的最大电流值。

本文旨在对BCP56的最大电流进行全面的概述和解释,并探讨其与其他参数之间的关系。

1.2 文章结构本文将按照以下结构进行论述:首先介绍贴片三极管BCP56的基本特性,包括其构造、材料以及工作原理;接着重点阐述最大电流对BCP56的影响和重要性,包括最大电流参数说明、正确选择最大电流值以及最大电流对性能的影响和限制;随后分析BCP56最大电流与其他参数之间的关系,并给出相应实验结果解释;最后总结研究结果并展望贴片三极管BCP56最大电流在未来的应用前景。

1.3 目的通过本文对贴片三极管BCP56最大电流进行概述说明和解释,我们旨在提供读者对该参数重要性和应用价值的充分认识,并帮助读者正确选择适合的最大电流值。

同时,通过分析BCP56最大电流与其他参数之间的关系,我们希望为进一步研究和应用贴片三极管BCP56提供参考和启示。

注意:以上内容为普通文本格式,请根据需要进行排版和格式调整。

2. 贴片三极管BCP56的基本特性:2.1 构造和材料:贴片三极管BCP56是一种由半导体材料构成的电子元件。

它通常由硅制成,具有三个电极:发射极、基极和集电极。

这些电极之间通过不同材料的层层堆叠和掺杂而形成。

2.2 工作原理:BCP56贴片三极管通过控制基极的信号,调节发射区的电流,从而实现放大和开关功能。

当正向偏置应用到基极时,使得发射结与基结反偏以打开了PNP型晶体管,电流可以从集电结流入拍平的绝缘衬底中。

2.3 典型应用场景:BCP56贴片三极管在很多领域都有广泛的应用。

它可以作为功率放大器、开关、稳压器等组件使用。

在通信设备、音频放大器、自动化系统和移动设备等领域也被广泛采用。

以上就是贴片三极管BCP56的基本特性部分的内容。

MVI56-MCM中文使用说明书

目录

一、使用向导 ........................................................................................................................................4 1.1 系统最低要求 .........................................................................................................................4 1.2 了解你的需求 .........................................................................................................................4 1.3 包装 .........................................................................................................................................6 1.4 跳线设置: .............................................................................................................................6 1.5 安装模块 .................................................................................................................................6 1.6 连接PC机和Rockwell处理器模块...........................................................................................7

nc56 开发手册

nc56 开发手册一、简介NC56是一款基于现代化技术开发的开源网络连接库,旨在为开发者提供高效、稳定和易用的网络连接工具。

该开发手册致力于向开发者介绍NC56的安装、配置和使用方法,以及一些常见的功能和用法示例。

二、安装和配置1.前置要求:在开始使用NC56之前,您需要确保您的开发环境满足以下要求:-操作系统:Windows、Linux或macOS;-编程语言:C/C++;-编译工具:GCC或Clang。

2.下载和安装:您可以从NC56的官方网站或GitHub仓库下载最新版本的安装包。

安装包通常包含库文件和示例代码。

下载完成后,按照相应的操作系统说明进行安装。

3.配置和编译:一般来说,您只需要将NC56的库文件和头文件添加到您的项目中,并在编译时链接NC56的库文件。

根据您的开发环境和构建工具,具体的配置和编译方式可能会有所不同,请参考相应的操作系统说明和示例代码。

三、基本用法1.创建连接:使用NC56,您可以轻松地创建网络连接。

以下是一个简单的示例代码,演示了如何创建一个TCP连接并发送数据:```c#include <nc56.h>int main() {nc56_init();nc56_socket_t socket = nc56_socket_create(AF_INET, SOCK_STREAM, 0);if (socket == NC56_SOCKET_INVALID) {//创建失败}nc56_address_t address;nc56_address_from_ipv4(&address, "127.0.0.1", 1234);if (nc56_socket_connect(socket, &address) != 0) {//连接失败nc56_socket_close(socket);return 1;}const char* message = "Hello, NC56!";if (nc56_socket_send(socket, message, strlen(message)) != strlen(message)) {//发送失败nc56_socket_close(socket);}nc56_socket_close(socket);nc56_cleanup();return 0;}```2.监听连接:您还可以使用NC56创建服务器,并监听传入的连接请求。

nc56 开发手册

NC56开发手册:全面解读与实践指南一、引言NC56,全称Netcool/OMNIbus 5.6,是一款由IBM公司研发的企业级网络管理软件。

它能够实现对网络设备的实时监控和故障预警,提供了一种高效、准确的网络管理和运维方式。

二、系统架构NC56采用的是客户端-服务器模式,包括了事件收集器、事件处理器、数据库服务器以及Web服务器等多个部分。

其中,事件收集器负责从各种网络设备中收集事件信息;事件处理器则负责对这些事件进行处理和分析;数据库服务器用于存储所有的事件信息;而Web服务器则提供了用户界面,使得用户可以通过浏览器来访问和管理NC56。

三、功能特性1. 实时监控:NC56可以实时监控网络设备的状态,并在发现异常时立即发出警报。

2. 故障预警:通过设置阈值,NC56可以在故障发生之前发出预警,从而避免或减少因故障造成的损失。

3. 自动恢复:对于一些常见的故障,NC56还可以自动进行恢复,大大减轻了运维人员的工作负担。

4. 数据分析:NC56还提供了强大的数据分析工具,可以帮助运维人员深入理解网络状态,优化网络配置。

四、安装部署NC56的安装过程相对复杂,需要按照以下步骤进行:1. 确认硬件和软件环境满足NC56的最低要求;2. 下载并解压NC56的安装包;3. 运行安装程序,按照提示进行操作;4. 安装完成后,需要进行一系列的配置,包括但不限于设置事件收集器、事件处理器、数据库服务器以及Web服务器等。

五、使用技巧1. 利用模板快速创建和管理事件规则;2. 利用报告功能对网络状态进行定期分析和总结;3. 利用脚本自动化一些重复性的任务;4. 利用API与其他系统进行集成。

六、常见问题与解决方案在使用NC56的过程中,可能会遇到各种问题,如无法连接到数据库服务器、事件处理器无法启动等。

针对这些问题,NC56提供了详细的错误代码和解决方法,用户可以根据实际情况进行排查和处理。

七、结语NC56作为一款强大且易用的网络管理软件,无论是对于大型企业还是中小型企业来说,都是一个非常好的选择。

56k modem产品知识

调制解调器即Modem能将数字信号转换成模拟信号在电话网上传送,也能将接受到的模拟信号转换成数字信号的设备。

由于目前大部分个人计算机都是通过公用电话网接入计算机网络的,因而需通过调制解调器进行上述转换。

调制解调器是计算机与电话线之间进行信号转换的装置,由调制器和解调器两部分组成,调制器是把计算机的数字信号(如文件等)调制成可在电话线上传输的声音信号的装置,在接收端,解调器再把声音信号转换成计算机能接收的数字信号。

通过调制解调器和电话线就可以实现计算机之间的数据通信。

目前调制解调器主要有两种:内置式和外置式。

内置式调制解调器其实就是一块计算机的扩展卡,插入计算机内的一个扩展槽在安装驱动程序后即可使用,它无需占用计算机的串行端口。

它的连线相当简单,把电话线接头插入卡上的“Line”插口,卡上另一个接口“Phone”则与电话机相连,平时不用调制解调器时,电话机使用一点也不受影响。

外置式调制解调器则是一个放在计算机外部的盒式装置,它需占用电脑的一个串行端口,还需要连接单独的电源才能工作,外置式调制解调器面板上有几盏状态指示灯,可方便您监视Modem的通讯状态,并且外置式调制解调器安装和拆卸容易,设置和维修也很方便,还便于携带。

外置式调制解调器的连接也很方便,phone和line的接法同内置式调制解调器。

但是外置式调制解调器得用一根串行电缆把计算机的一个串行口和调制解调器串行口连起来,这根串行线一般随外置式调制解调器配送。

调制解调器的一个重要性能参数是传输速率,56K的调制解调器是市场上常见的产品。

TEM5632PF 56K内置式DATA/FAX调制解调器......................................................................................................◆ 产品简述:TEM5632PF是一款PCI 56K MODEM,采用Smart Link SL2800芯片,是一款高性能的调制解调器,采用PCI接口,可在Windows98\Windows ME\Windows2000\WindowsXP\WindowsNT等目前流行的操作系统下运行,支持即插即用,数据压缩协议,具有智能记忆存储功能,上传最高可达48K,下载56K。

BX06BK 智能PCM设备 用户手册V1.1(有标)

4.1 组网应用 .................................................................. 53 4.2 组网方式 .................................................................. 53

目录

安全使用须知 .................................................. 1 第一章 基础知识 ............................................... 1

1.1 通信网简介.................................................................. 1 1.1.1 通信网的分类 .......................................................... 1 1.1.2 通信网的基本要素 ...................................................... 1 1.1.3 通信网的发展方向 ...................................................... 1

2.2 系统工作原理................................................................ 8 2.3 硬件结构 ................................................................... 8 2.4 软件结构 ................................................................... 9 2.5 系统特点 ................................................................... 9 2.6 整机配置注意事项........................................................... 10

飞利浦 CRD56 用户手册(中文)说明书

用户手册(中文)ProfessionalDisplay SolutionsCRD56/welcome目录1. 安全注意事项 (1)2. 开箱和安装 (4)2.1. 开箱 (4)2.2. 包装箱内物品 (4)2.3. 安装注意事项 (4)2.4. 输入/输出端子 (5)3. 操作 (6)3.1. Overview(概览) (6)3.2. 设置 (6)3.3. Cloud CMS (10)3.4. 克隆设定 (10)3.5. 文件管理 (11)3.6. 媒体播放器简介 (11)3.7. PDF 播放器 (11)3.8. 日程 (12)4. USB设备兼容性 (13)5. 清洁 (15)6. 技术规格 (16)Philips专业显示器解决方案的保修政策 (17)索引 (19)1. 安全注意事项安全措施与维修警告:使用本文档中未介绍的控制、调整或过程可能导致碰撞、电气危险和/或机械危险。

在连接和使用智能多媒体终端时,请阅读并遵循下列注意事项:操作:• 请勿让智能多媒体终端受阳光直接照射,并使其远离火炉或其他任何热源。

• 移开任何可能掉入通风孔的物品或者会妨碍智能多媒体终端电子器件正常散热的物品。

• 请勿堵塞机壳上的通风孔。

• 放置智能多媒体终端时,确保电源插头和插座便于插拔。

• 如果刚刚通过拔掉电源线关闭了智能多媒体终端,则必须等待6秒钟,方可重新接上电源线,以确保正常运行。

• 务必使用由Philips提供的经过认可的电源线。

如果电源线缺失,请与您当地的服务中心联系。

• 在使用过程中,请勿让智能多媒体终端受到剧烈震动或碰撞。

• 在使用或运输期间,不要敲打智能多媒体终端或使其掉落。

• 若操作员在安装附加设备时需要卸下任何门或盖板,应提供正确卸下和重新安装门的方法。

维护:• 长时间不使用智能多媒体终端时,应拔掉其电源线插头。

• 使用略微蘸湿的布清洁智能多媒体终端时,应拔掉其电源线插头。

电源关闭时,可以使用干布擦拭屏幕。

BCP56;中文规格书,Datasheet资料

TA = 25°C unless otherwise noted

BCP56 80 100 5 1.2 -55 to +150

Units V V V A °C

Operating and Storage Junction Temperature Range

*These ratings are limiting values above which the serviceability of any semiconductor device may be impaired. NOTES: 1) These ratings are based on a maximum junction temperature of 150°C. 2) These are steady state limits. The factory should be consulted on applications involving pulsed or low duty crmal Characteristics

Symbol

TA = 25°C unless otherwise noted

Max Characteristic BCP56 PD RθJA Total Device Dissipation Derate above 25°C Thermal Resistance, Junction to Ambient 1 8 125 W mW/°C °C/W Units

FAIRCHILD SEMICONDUCTOR RESERVES THE RIGHT TO MAKE CHANGES WITHOUT FURTHER NOTICE TO ANY PRODUCTS HEREIN TO IMPROVE RELIABILITY, FUNCTION OR DESIGN. FAIRCHILD DOES NOT ASSUME ANY LIABILITY ARISING OUT OF THE APPLICATION OR USE OF ANY PRODUCT OR CIRCUIT DESCRIBED HEREIN; NEITHER DOES IT CONVEY ANY LICENSE UNDER ITS PATENT RIGHTS, NOR THE RIGHTS OF OTHERS.

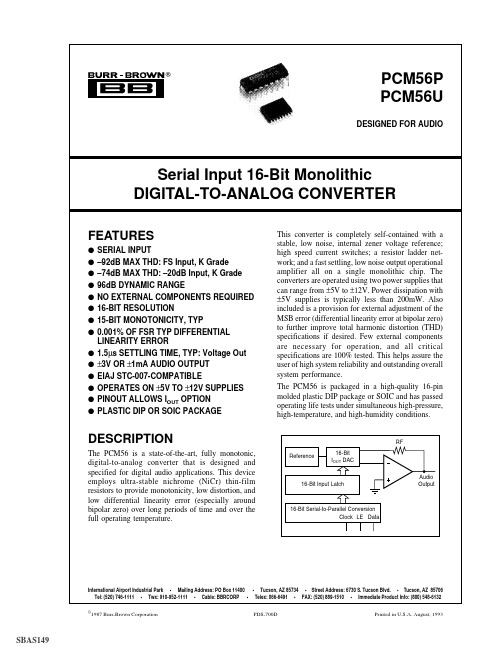

PCM56P-LG4资料

1987 Burr-Brown Corporation

PDS-700D

Printed in U.S.A. August, 1993

SBAS149

元器件交易网

SPECIFICATIONS

ELECTRICAL

Typical at +25°C, and nominal power supply voltages ±5V, unless otherwise noted. PCM56U, PCM56P-J, -K PARAMETER DIGITAL INPUT Resolution Digital Inputs(1): VIH VIL IIH, VIN = +2.7V IIL, VIN = +0.4V Input Clock Frequency TRANSFER CHARACTERISTICS ACCURACY Gain Error Bipolar Zero Error Differential Linearity Error Noise (rms, 20Hz to 20kHz) at Bipolar Zero (VOUT models) TOTAL HARMONIC DISTORTION VO = ±FS at f = 991Hz: PCM56P-K PCM56P-J PCM56P, PCM56U PCM56P-L VO = –20dB at f = 991Hz: PCM56P-K PCM56P-J PCM56P, PCM56U PCM56P-L VO = –60dB at f = 991Hz: PCM56P-K PCM56P-J PCM56P, PCM56U PCM56P-L MONOTONICITY DRIFT (0°C to +70°C) Total Drift(3) Bipolar Zero Drift SETTLING TIME (to ±0.006% of FSR) Voltage Output: 6V Step 1LSB Slew Rate Current Output, 1mA Step: 10Ω to 100Ω Load 1kΩ Load(4) WARM-UP TIME OUTPUT Voltage Output Configuration: Bipolar Range Output Current Output Impedance Short Circuit Duration Current Output Configuration: Bipolar Range (±30%) Output Impedance (±30%) POWER SUPPLY REQUIREMENTS(5) Voltage: +VS and +VL –VS and –VL Supply Drain (No Load): +V (+VS and +VL = +5V) –V (–VS and –VL = –5V) +V (+VS and +VL = +12V) –V (–VS and –VL = –12V) Power Dissipation: VS and VL = ±5V VS and VL = ±12V TEMPERATURE RANGE Specification Operation Storage 1 ±3.0 0.10 Indefinite to Common ±1.0 1.2 +4.75 –4.75 +5.00 –5.00 +10.00 –25.0 +12.0 –27.0 175 468 +13.2 –13.2 +17.0 –35.0 MIN TYP 16 +2.4 0 +VL +0.8 +1.0 –50 MAX UNITS Bits V V µA µA MHz

nc56开发手册

nc56开发手册数据表NC56电容式液位探头1 | 产品和功能描述2/9DB_EN _NC561产品及功能描述1.1性能特点典型应用测量油箱填充液位•淡水•废物、粪便•柴油染料•灭火泡沫应用领域•程序技术•工艺技术•环境技术•车辆技术•船舶技术主要特点•坚固的设计(IP67)•轻松启动•可靠使用•无论罐体材质(金属、塑料或混凝土)和形状如何,都可以使用该探头。

•安装尺寸在 400 至 2000 毫米之间可变,步长为 50 毫米1.2设备版本图 1:产品概要根据介质不同,NC56 可以提供各种版本。

产品和功能描述 | 1DB_EN _NC563/9NC56 2...水废水NC56 3...柴油机取暖油NC56 6...化学品绳探头NC56 系列...NC56 4...粪便FoamNC56 5...图 2:设备版本1探头外壳2管道适配器3垫片4热缩套管绝缘5不锈钢6ECTFE 绝缘材料7重量1.3有可能的使用电容式液位探头 NC56 用于测量装有淡水、废水、粪便、柴油、化学品和灭火泡沫的储罐的液位。

可测量 400 至 2000 毫米之间的液位高度。

无论储罐材质如何(金属、塑料或混凝土),都可以使用该探头。

将此设备用于肮脏或腐蚀性介质之前,请联系制造商,因为该设备需要根据与介质接触的部件进行调整。

该设备仅用于制造商和用户之间约定的用途。

1 | 产品和功能描述4/9DB_EN _NC561.4功能图C:起始容量(探头自由) C:终止容量(探头覆盖)图 3:功能图1.5设计和操作模式将交流电压信号施加到两根相距一定距离的金属棒上。

这意味着金属棒浸入液体中时会变成电容器。

该电容器的电容值主要通过填充液位高度和由此产生的电介质变化来确定。

设备中集成的电子元件将这些电容变化转换成线性均匀的电信号,并与红外遥控器进行比较。

技术数据 | 2DB_EN _NC565/92技术数据2.1一般的一般信息型号说明NC56测量原理连续测量两个/三个探针杆之间的容量变化,取决于流体的填充探针。

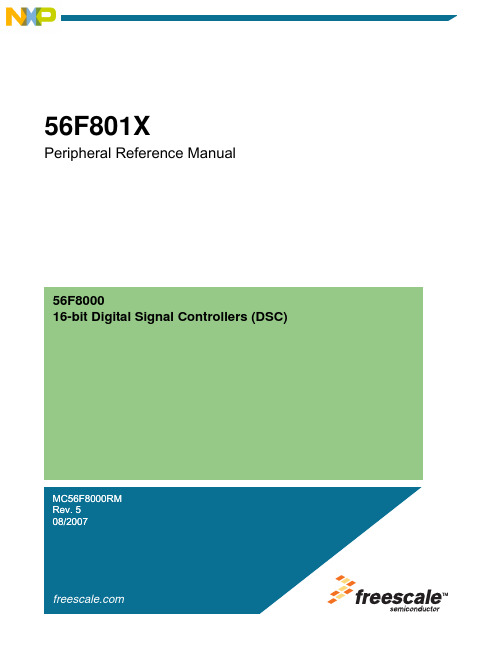

MC56F8000RM 56F801X外设参考手册说明书