DS_BL8509--Voltage Detector,Built-in Delay Circuit(EN,V1.2)

ACS8509T资料

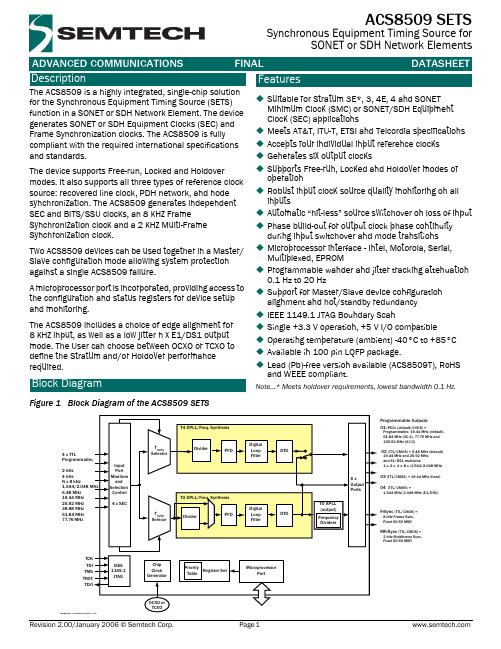

ADVANCED COMMUNICATIONS FINALSynchronous Equipment Timing Source forSONET or SDH Network ElementsDATASHEETThe ACS8509 is a highly integrated, single-chip solution for the Synchronous Equipment Timing Source (SETS) function in a SONET or SDH Network Element. The device generates SONET or SDH Equipment Clocks (SEC) and Frame Synchronization clocks. The ACS8509 is fully compliant with the required international specifications and standards.The device supports Free-run, Locked and Holdovermodes. It also supports all three types of reference clock source: recovered line clock, PDH network, and node synchronization. The ACS8509 generates independent SEC and BITS/SSU clocks, an 8 kHz Frame Synchronization clock and a 2 kHz Multi-Frame Synchronization clock.Two ACS8509 devices can be used together in a Master/ Slave configuration mode allowing system protection against a single ACS8509 failure.A microprocessor port is incorporated, providing access to the configuration and status registers for device setup and monitoring.The ACS8509 includes a choice of edge alignment for 8kHz input, as well as a low jitter n x E1/DS1 output mode. The User can choose between OCXO or TCXO to define the Stratum and/or Holdover performance required.Suitable for Stratum 3E*, 3, 4E, 4 and SONET Minimum Clock (SMC) or SONET/SDH Equipment Clock (SEC) applicationsMeets AT&T, ITU-T, ETSI and Telcordia specifications Accepts four individual input reference clocks Generates six output clocksSupports Free-run, Locked and Holdover modes of operationRobust input clock source quality monitoring on all inputsAutomatic “hit-less” source switchover on loss of input Phase build-out for output clock phase continuity during input switchover and mode transitions Microprocessor interface - Intel, Motorola, Serial, Multiplexed, EPROMProgrammable wander and jitter tracking attenuation 0.1 Hz to 20 HzSupport for Master/Slave device configuration alignment and hot/standby redundancy IEEE 1149.1 JTAG Boundary ScanSingle +3.3 V operation, +5 V I/O compatibleOperating temperature (ambient) -40°C to +85°C Available in 100 pin LQFP package.Lead (Pb)-free version available (ACS8509T), RoHS and WEEE compliant.Note...* Meets holdover requirements, lowest bandwidth 0.1Hz.Block DiagramDescriptionFeaturesADVANCED COMMUNICATIONS FINAL DATASHEET Table of ContentsSection Page Description (1)Block Diagram (1)Features (1)Table of Contents (2)Pin Diagram (4)Pin Description (5)Functional Description (8)Local Oscillator Clock (8)Crystal Frequency Calibration (8)Input Interfaces (9)Over-Voltage Protection (9)Input Reference Clock Ports (9)DivN Examples (10)Input Wander and Jitter Tolerance (10)Frame Sync and Multi-Frame Sync Clocks (Part of T OUT0) (12)Output Clock Ports (12)Low-speed Output Clock (T OUT4) (12)High-speed Output Clock (Part of T OUT0) (12)Low Jitter Multiple E1/DS1 Outputs (13)Output Wander and Jitter (13)Phase Variation (14)Phase Build-Out (17)Microprocessor Interface (17)Motorola Mode (17)Intel Mode (17)Multiplexed Mode (17)Serial Mode (17)EPROM Mode (17)Register Set (18)Configuration Registers (18)Status Registers (18)Register Access (18)Interrupt Enable and Clear (18)Register Map (18)Register Map Description (23)Selection of Input Reference Clock Source (36)Forced Control Selection (36)Automatic Control Selection (36)Ultra Fast Switching (37)Clock Quality Monitoring (37)Activity Monitoring (38)Frequency Monitoring (39)Modes of Operation (39)Free-run mode (39)Pre-Locked mode (39)Locked mode (39)Lost_Phase mode (40)Holdover mode (40)Pre-Locked(2) mode (41)Section Page Protection Facility (41)Alignment of Priority Tables in Master and Slave ACS8509 (42)Alignment of the Selection of Reference Sources for T OUT4 Generation in the Master and Slave ACS8509 (42)Alignment of the Phases of the 8 kHz and 2 kHz Clocks in both Master and Slave ACS8509 (42)JTAG (43)PORB (43)Electrical Specification (45)Operating Conditions (45)DC Characteristics (45)Notes for Tables 24 to 30 (51)Input/Output Timing (52)Motorola Mode (53)Intel Mode (55)Multiplexed Mode (57)Serial Mode (59)EPROM Mode (61)Package Information (62)Thermal Conditions (63)Application Information (64)References (65)Abbreviations (65)Trademark Acknowledgements (66)Revision Status/History (67)Ordering Information (68)Disclaimers (68)Contacts (68)Pin DiagramFigure 2ACS8509 Pin Diagram Synchronous Equipment Timing Source for SONET or SDH Network ElementsNote...I = Input, O = Output, P = Power, TTL U = TTL input with pull-up resistor, TTL D = TTL input with pull-down resistor.Pin DescriptionTable 1Power PinsPin Number SymbolI/O Type Description12, 13, 16VD+P -Supply Voltage: Digital supply to gates in analog section, +3.3 Volts ±10%.33, 39VDD_DIFF P -Supply Voltage: Digital supply for differential ports, +3.3 Volts ±10%.44VDD5P-Digital Supply for +5 Volts Tolerance to Input Pins. Connect to +5Volts (±10%) for clamping to +5 Volts. Connect to VDD for clamping to +3.3 Volts. Leave floating for no clamping, input pins tolerant up to +5.5Volts.50, 61, 85, 86 91VDD P -Supply Voltage: Digital supply to logic, +3.3 Volts ±10%.6VA1+P -Supply Voltage: Analog supply to clock multiplying PLL, +3.3 Volts ±10%.19VA2+P -Supply Voltage: Analog supply to output PLLs, +3.3 Volts ±10%.11, 14, 15, 24, 25, 29, 49, 62, 84, 87,92DGNDP- Supply Ground: Digital ground for logic32, 38GND_DIFF P -Supply Ground: Digital ground for differential ports.1, 5,20AGNDP-Supply Ground: Analog grounds.Table 2Not Connected or Internally Connected PinsPin Number SymbolI/O Type Description4, 17, 26NCNC -Not connected: Leave to Float 3, 18, 22, 27, 28, 34, 35, 40, 41, 42, 43, 46, 47, 52, 53, 55, 57, 89, 93, 94, 96, 97, 98ICIC-Internally Connected: Leave to Float.Table 3Other PinsPin Number Symbol I/O Type Description2TRSTITTL DJTAG Control Reset Input: TRST = 1 to enable JTAG Boundary Scan mode. TRST = 0 for Boundary Scan stand-by mode, still allowing correct device operation. If not used connect to GND or leave floating.7TMS ITTL UJTAG Test Mode Select: Boundary Scan enable. Sampled on rising edge of TCK. If not used connect to VDD or leave floating.8INTREQ O TTL/CMOS Interrupt Request: Active High software Interrupt output.9TCK I TTL D JTAG Clock: Boundary Scan clock input. If not used connect to GND or leavefloating. This pin may require a capacitor placed between the pin and thenearest GND, to reduce noise pickup. A value of 10 pF should be adequate,but the value is dependent on PCB layout.10REFCLK I TTL Reference Clock: 12.800 MHz (refer to “Local Oscillator Clock” on page8). 21TDO O TTL/CMOS JTAG Output: Serial test data output. Updated on falling edge of TCK. If notused leave floating.23TDI I TTL U JTAG Input: Serial test data Input. Sampled on rising edge of TCK. If notused connect to VDD or leave floating.30FrSync O TTL/CMOS Output Reference: 8 kHz Frame Sync output (square wave).31MFrSync O TTL/CMOS Output Reference: 2 kHz Multi-Frame Sync output (square wave).36, 37O1POS, O1NEG O PECL/LVDS Output Reference O1: Programmable, default 19.44 MHz. Also 51.84 MHz,77.76 MHz, 155.52 MHz. MHz, default type PECL.45SYNC2K I TTL D Synchronize 2 kHz: Connect to 2 kHz Multi-Frame Sync output of partnerACS8509 in redundancy system.48SEC1I TTL D Input Reference SEC1: Programmable, default 19.44 MHz(Default Priority 7).51SEC2I TTL D Input Reference SEC2 : Programmable, default 19.44 MHz(Default Priority 8).54SEC3I TTL D Input Reference SEC3: Programmable, default (Master mode)1.544/2.048 MHz, default (Slave mode) 6.48 MHz.(Default Priority 11).56SEC4I TTL D Input Reference SEC4 (Priority 13): Programmable, default1.544/2.048MHz (Default Priority 13).58 - 60UPSEL(2:0)I TTL D Microprocessor Select: Configures the interface for a particularmicroprocessor type at reset.63 - 69A(6:0)I TTL D Microprocessor Interface Address: Address bus for the microprocessorinterface registers. A(0) is SDI in Serial mode - output in EPROM mode only. 70CSB I TTL U Chip Select (Active Low): This pin is asserted Low by the microprocessor toenable the microprocessor interface - output in EPROM mode only.71WRB I TTL U Write (Active Low): This pin is asserted Low by the microprocessor toinitiate a write cycle. In Motorola mode, WRB = 1 for Read.72RDB I TTL U Read (Active Low): This pin is asserted Low by the microprocessor toinitiate a read cycle.73ALE I TTL D Address Latch Enable: This pin becomes the address latch enable from themicroprocessor. When this pin transitions from High to Low, the addressbus inputs are latched into the internal registers. ALE = SCLK in Serialmode.74PORB I TTL U Power-On Reset: Master reset. If PORB is forced Low, all internal states arereset back to default values.Pin Number Symbol I/O Type DescriptionPin Number Symbol I/O Type Description75RDY O TTL/CMOS Ready/Data Acknowledge: This pin is asserted High to indicate the devicehas completed a read or write operation.76 - 83AD(7:0)IO TTL D Address/Data: Multiplexed data/address bus depending on themicroprocessor mode selection. AD(0) is SDO in Serial mode.88O2O TTL/CMOS Output Reference 2: Default 6.48 MHz. Also Dig1 (1.544 MHz/2.048 MHzand 2, 4, 8 x), 19.44 MHz, 25.92 MHz90O3O TTL/CMOS Output Reference 3: 19.44 MHz - fixed.95O4O TTL/CMOS Output Reference 4: 1.544/2.048 MHz, (T4 BITS).99MSTSLVB I TTL U Master/Slave Select: Sets the initial power-up state (or state after a PORB)of the Master/Slave selection register, Reg.34, Bit 1. The register statecan be changed after power up by software.100SONSDHB I TTL D SONET or SDH Frequency Select: Sets the initial power-up state (or stateafter a PORB) of the SONET/SDH frequency selection registers, Reg.34, Bit2 and Reg.38, Bit 5 and Bit 6. When set Low, SDH rates are selected(2.048 MHz etc.) and when set High, SONET rates are selected (1.544 MHzetc.) The register states can be changed after power-up by software.The ACS8509 is a highly integrated, single-chip solution for the SETS function in a SONET/SDH Network Element, for the generation of SEC and frame synchronization pulses.In Free-run mode, the ACS8509 generates a stable, low noise clock signal from an internal oscillator.In Locked mode, the ACS8509 selects the most appropriate input reference source and generates a stable, low-noise clock signal locked to the selected reference.In Holdover mode, the ACS8509 generates a stable, low-noise clock signal from the internal oscillator, adjusted to match the last known good frequency of the last selected reference source.In all modes, the frequency accuracy, jitter and drift performance of the clock meet the requirements of ITU G.812[10], G.813[11], G.823[13], and Telcordia GR-1244-CORE[19].The ACS8509 supports all three types of reference clock source: recovered line clock (T IN1), PDH network synchronization timing (T IN2) and node synchronization (T IN3). The ACS8509 generates independent T OUT0 and T OUT4 clocks, an 8 kHz Frame Synchronization clock and a 2 kHz Multi-Frame Synchronization clock.The ACS8509 has a high tolerance to input jitter and wander. The jitter/wander transfer is programmable (0.1 Hz up to 20 Hz cut-off points).The ACS8509 supports protection. Two ACS8509 devices can be configured to provide protection against a single ACS8509 failure.The protection maintains alignment of the two ACS8509 devices (Master and Slave) and ensures that bothACS8509 devices maintain the same priority table, choose the same reference input and generate the T OUT0 clock, the 8 kHz Frame Synchronization clock and the 2 kHz Multi-Frame Synchronization clock with the same phase.The ACS8509 includes a microprocessor port, providing access to the configuration and status registers for device setup and monitoring.Local Oscillator ClockThe Master system clock on the ACS8509 should be provided by an external clock oscillator of frequency 12.80 MHz. The clock specification is important for meeting the ITU/ETSI and Telcordia performance requirements for Holdover mode. ITU and ETSI specifications permit a combined drift characteristic, at constant temperature, of all non-temperature related parameters, of up to 10 ppb per day. The same specifications allow a drift of 1 ppm over a temperature range of 0 to +70°C.Telcordia specifications are somewhat tighter, requiring a non-temperature-related drift of less than 40 ppb per day and a drift of 280 ppb over the temperature range 0 to +50°C.Please contact Semtech for information on crystal oscillator suppliers.Crystal Frequency CalibrationThe absolute crystal frequency accuracy is less important than the stability since any frequency offset can be compensated by adjustment of register values in the IC. This allows for calibration and compensation of any crystal frequency variation away from its nominal value. ±50 ppm adjustment would be sufficient to cope with most crystals, in fact the range is an order of magnitude larger due to the use of two 8-bit register locations. The setting of the conf_nominal_frequency register allows for this adjustment. An increase in the register value increases the output frequencies by 0.02 ppm for each LSB step. The default value (in decimal) is 39321.Functional DescriptionTable 4ITU and ETSI SpecificationParameter ValueTolerance±4.6 ppm over 20 year lifetimeDrift (Frequency Drift over supply voltage range of +2.7 V to +3.3 V)±0.05 ppm/15 seconds @ constant temp.±0.01 ppm/day @ constant temp.±1 ppm over temp. range 0 to +70°CTable 5Telcordia GR-1244 CORE Specification Parameter Value Tolerance±4.6 ppm over 20 year lifetimeDrift (Frequency Drift over supply voltage range of +2.7 V to +3.3 V)±0.05 ppm/15 seconds @ constant temp.±0.04 ppm/15 seconds @ constant temp.±0.28 ppm/over temp. range 0 to +50°CThe minimum being 0 and the maximum 65535, gives a -700ppm to +500 ppm adjustment range of the output frequencies.For example, if the crystal was oscillating at 12.8 MHz +5ppm, then the calibration value in the register to give a -5 ppm adjustment in output frequencies to compensate for the crystal inaccuracy, would be: 39321 - (5 / 0.02) = 39071 (decimal)Input InterfacesThe ACS8509 supports up to four input reference clock sources from input types T IN1, T IN2 and T IN3 using TTL/ CMOS I/O technologies. These interface technologies support +3.3V and +5 V operation.Over-Voltage ProtectionThe ACS8509 may require Over-Voltage Protection on input reference clock ports according to ITU Recommendation K.41. Semtech protection devices are recommended for this purpose (see separate Semtech data book).Input Reference Clock PortsTable6 gives details of the input reference ports, showing the input technologies and the range of frequencies supported on each port; the default spot frequencies and default priorities assigned to each port on power-up or by reset are also shown. Note that SDH and SONET networks use different default frequencies; the network type is pin-selectable using the SONSDHB pin). Specific frequencies and priorities are set by configuration.Although each input port is shown as belonging to one of the types, T IN1, T IN2 or T IN3, they are fully interchangeable as long as the selected speed is within the maximum operating speed of the input port technology.SDH and SONET networks use different default frequencies; the network type is selectable using the config_mode register 34 Hex, bit 2.For SONET, config_mode register 34 Hex, bit 2 = 1, for SDH config_mode register 34 Hex, bit 2 = 0. On power-up or by reset, the default will be set by the state of the SONSDHB pin (pin 100). Specific frequencies and priorities are set by configuration.TTL ports (compatible also with CMOS signals) support clock speeds up to 100 MHz, with the highest spot frequency being 77.76 MHz. The actual spot frequencies supported are:• 2 kHz,• 4 kHz,• 8 kHz (and N x 8 kHz),• 1.544 MHz (SONET)/2.048 MHz (SDH),• 6.48 MHz,• 19.44 MHz,• 25.92 MHz,• 38.88 MHz,• 51.84 MHz,• 77.76 MHz.The frequency selection is programmed via thecnfg_ref_source_frequency register. The internal DPLL will normally lock to the selected input at the frequency of the input, e.g. 19.44MHz will lock the DPLL phase comparisons at 19.44 MHz. It is, however, possible to utilize an internal pre-divider to the DPLL to divide the input frequency before it is used for phase comparisons in the DPLL. This pre-divider can be used in one of 2 ways: 1.Any of the supported spot frequencies can be dividedto 8 kHz by setting the lock8K bit (bit 6) in theappropriate cnfg_ref_source_frequency registerlocation. For good jitter tolerance for all frequencies and for operation at 19.44 MHz and above, uselock8K. It is possible to choose which edge of the8kHz input to lock to, by setting the appropriate bit of the cnfg_control1 register.2.Any multiple of 8 kHz between 1544 kHz to 100 MHzcan be supported by using the DivN feature (bit 7 of the cnfg_ref_source_frequency register). Anyreference input can be set to use DivN independently of the frequencies and configurations of the otherinputs.Any reference input with the DivN bit set in thecnfg_ref_source_frequency register will employ the internal pre-divider prior to the DPLL locking.The cnfg_freq_divn register contains the divider ratio N where the reference input will get divided by (N+1) where 0<N<214-1. The cnfg_ref_source_frequency register must be set to the closest supported spot frequency to the input frequency, but must be lower than the input frequency. When using the DivN feature the post-dividerNotes: (i)TTL ports (compatible also with CMOS signals) support clock speeds up to 100 MHz, with the highest spot frequency being77.76MHz. The actual spot frequencies are: 2 kHz, 4 kHz, 8 kHz (and N x 8 kHz), 1.544 MHz (SONET)/2.048 MHz (SDH), 6.48 MHz,19.44 MHz, 25.92 MHz, 38.88 MHz, 51.84 MHz, 77.76 MHz. SONET or SDH is selected using the SONSDHB pin. When theSONSDHB pin is High SONET is selected, when the SONSDHB pin is Low SDH is selected.(ii)Input port SEC4 is set at 12 on the Master SETS IC and 1 on the Slave SETS IC, as default on power up (or PORB). The default setup of Master or Slave SEC4 priority is determined by the MSTSLVB pin.frequency must be 8 kHz, which is indicated by setting the lock8k bit high (bit 6 in cnfg_ref_source_frequency register). Any input set to DivN must have the frequency monitors disabled (If the frequency monitors are disabled, they are disabled for all inputs regardless of the input configurations, in this case only activity monitoring will take place). Whilst any number of inputs can be set to use the DivN feature, only one N can be programmed, hence all inputs using the DivN feature must require the same division to get to 8 kHz.DivN ExamplesTo lock to 2.000 MHz:1.The cnfg_ref_source_frequency register is set to11XX0001 (binary) to set the DivN, lock8k bits, and the frequency to E1/DS1. (XX = “leaky bucket” ID for this input).2.The cnfg_mode register (34Hex) bit 2 needs to be setto 1 to select SONET frequencies (DS1).3.The frequency monitors are disabled in cnfg_monitorsregister (48Hex) by writing 00 to bits 0 and 1.4.The DivN register is set to F9 Hex (249 decimal).To lock to 10.000 MHz:1.The cnfg_ref_source_frequency register is set to11XX0010 (binary) to set the DivN, lock8k bits, and the frequency to 6.48 MHz. (XX = “leaky bucket” ID for this input).2.The frequency monitors are disabled in cnfg_monitorsregister (48Hex) by writing 00 to bits 0 and 1.3.The DivN register is set to 4E1 Hex (1249 decimal).Input Wander and Jitter ToleranceThe ACS8509 is compliant to the requirements of all relevant standards, principally ITU Recommendation G.825[15], ANSI T1.101-1999[1] and ETSI ETS 300 462-5 (1996)[4].All reference clock inputs have a tight frequency tolerance but a generous jitter tolerance. Pullin, hold-in and pull-out ranges are specified for each input port in Table7. Minimum jitter tolerance masks are specified in Figures 3 and 4, and Tables 8 and 9, respectively. The ACS8509 will tolerate wander and jitter components greater than those shown in Figure3 and Figure4, up to a limit determined by a combination of the apparent long-term frequency offset caused by wander and the eye-closure caused by jitter (the input source will be rejected if the offset pushesTable 6Input Reference Source Selection and Priority TablePort Number ChannelNumber (Bin)Port Type Input PortTechnologyFrequencies Supported DefaultPrioritySEC10111T IN1TTL/CMOS Up to 100 MHz (see Note (i))Default (SONET): 19.44 MHzDefault (SDH): 19.44 MHz8SEC21000T IN1TTL/CMOS Up to 100 MHz (see Note (i))Default (SONET): 19.44 MHzDefault (SDH): 19.44 MHz9SEC31011T IN2TTL/CMOS Up to 100 MHz (see Note (i))Default (Master) (SONET): 1.544 MHzDefault (Master) (SDH): 2.048 MHzDefault (Slave) 6.48 MHz 12/1 (Note (ii))SEC41101T IN2TTL/CMOS Up to 100 MHz (see Note (i))Default (SONET): 1.544 MHzDefault (SDH): 2.048 MHz14the frequency outside the hold-in range for long enough to be detected, whilst the signal will also be rejected if the eye closes sufficiently to affect the signal purity). The “8klock” mode should be engaged for high jitter tolerance according to these masks. All reference clock ports are monitored for quality, including frequency offset and general activity. Single short-term interruptions in selected reference clocks may not causerearrangements, whilst longer interruptions, or multiple, short-term interruptions, will cause rearrangements, as will frequency offsets which are sufficiently large orsufficiently long to cause loss-of-lock in the phase-locked loop. The failed reference source will be removed from the priority table and declared as unserviceable, until its perceived quality has been restored to an acceptable level.The registers sts_curr_inc_offset (address 0C, 0D, 07) report the frequency of the DPLL with respect to the external TCXO frequency. This is a 19-bit signed number with one LSB representing 0.0003 ppm (range of ±80ppm). Reading this regularly can show how the currently locked source is varying in value e.g. due to wander on its input.The ACS8509 performs automatic frequency monitoring with an acceptable input frequency offset range of ±16.6ppm. The ACS8509 DPLL has a programmablefrequency limit of ±80 ppm. If the range is programmed to be > 16.6 ppm, the frequency monitors should be disabled so the input reference source is not automatically rejected as out of frequency range.Notes: (i)The frequency acceptance and generation range will be ±4.6 ppm around the required frequency when the external crystalfrequency accuracy is within a tolerance of ±4.6 ppm.(ii)The fundamental acceptance range and generation range is ± 9.2 ppm with an exact external crystal frequency of 12.8 MHz. This isthe default DPLL range, the range is also programmable from 0 to 80 ppm in 0.08 ppm steps.Table 7Input Reference Source Jitter ToleranceJitter Tolerance Frequency Monitor Acceptance RangeFrequency AcceptanceRange (Pull-in)Frequency AcceptanceRange (Hold-in)Frequency Acceptance Range (Pull-out)G.703±16.6 ppm ±4.6 ppm (see Note (i))±4.6 ppm (see Note (i))±4.6 ppm (see Note (i))G.783G.823±9.2 ppm (see Note (ii))±9.2 ppm (see Note (ii))±9.2 ppm (see Note (ii))GR-1244-COREFigure 3Minimum Input Jitter Tolerance (OC-3/STM-1)Frame Sync and Multi-Frame Sync Clocks (Part of T OUT0)Frame Sync (8 kHz) and Multi-Frame Sync (2 kHz) clocks are provided on outputs “FrSync” and “MFrSync”. The FrSync and MFrSync clocks have a 50:50 mark space ratio. These are driven from the T OUT0 clock. They are synchronized with their counterparts in a secondACS8509 device (if used), using the technique described later.Output Clock PortsThe device supports a set of main output clocks, T OUT0 and T OUT4, and a pair of secondary output clocks, “Frame Sync” and “Multi-Frame Sync”. The two main output clocks, T OUT0 and T OUT4, are independent of each other and are individually selectable. The two secondary output clocks, Frame Sync and Multi-Frame Sync, are derived from T OUT0. The frequencies of the output clocks are selectable from a range of pre-defined spot frequencies and a variety of output technologies are supported, as defined in Table10.Low-speed Output Clock (T OUT4)The T OUT4 clock is supplied on output port O4. This port will provide a TTL/CMOS signal at either 1.544 MHz or 2.048 MHz, depending on the setting of the SONSDHB pin.High-speed Output Clock (Part of T OUT0)The T OUT0 port has multiple outputs. Output O1 is differential and can support clocks up to 155.52 MHz. Output O2 is a TTL/CMOS output with a choice of 11 different frequencies up to 51.84 MHz. Output O3 is a TTL/CMOS output with fixed frequency of 19.44 MHz. Each output is individually configured to operate at the frequencies shown in Table10 (configuration must be consistent between ACS8509 devices for protection-switching to be effective - output clocks will be phase-aligned between devices). Using thecnfg_differential_outputs register, output O1 can be made to be LVDS or PECL compatible.Low Jitter Multiple E1/DS1 OutputsThis feature is activated using the cnfg_control1 register. This sends a frequency of twice the Dig2 rate (see reg addr 39h, bits 7:6) to the APLL instead of the normal 77.76MHz. For this feature to be used, the Dig2 rate must only be set to 12352kHz/16384kHz using the cnfg_T0_output_frequencies register. The normal OC-3 rate outputs are then replaced with E1/DS1 multiple rates. The E1(SONET)/DS1(SDH) selection is made in the same way as for Dig2 using the cnfg_T0_output_enable register.Table11 shows the relationship between primary output frequencies and the corresponding output in E1/DS1 mode, and from which output they are available. Output Wander and JitterWander and jitter present on the output clocks are dependent on:1.The magnitude of wander and jitter on the selectedinput reference clock (in Locked mode).2.The internal wander and jitter transfer characteristic(in Locked mode).3.The jitter on the local oscillator clock.4.The wander on the local oscillator clock (in Holdovermode).Wander and jitter are treated in different ways to reflect their differing impacts on network design. Jitter is always strongly attenuated, whilst wander attenuation can be varied to suit the application and operating state. Wander and jitter attenuation is performed using a digital phase locked loop (DPLL) with a programmable bandwidth. This gives a transfer characteristic of a low pass filter, with a programmable pole. It is sometimes necessary to change the filter dynamics to suit particular circumstances - one example being when locking to a new source, the filter can be opened up to reduce locking time and can then be gradually tightened again to remove wander. Since wander represents a relatively long-term deviation from the nominal operating frequency, it affects the rate of supply of data to the network element. Strong wander attenuation limits the rate of consumption of data to within a smaller range, so a larger buffer store is required to prevent data loss. But, since any buffer store potentially。

BL8506-30NRM中文资料

TPLH

Parameter Detector Threshold Detector Threshold

Hysteresis Current consumption Maximum operating

voltage Minimum Operating

voltage

Output current

Output Delay Time

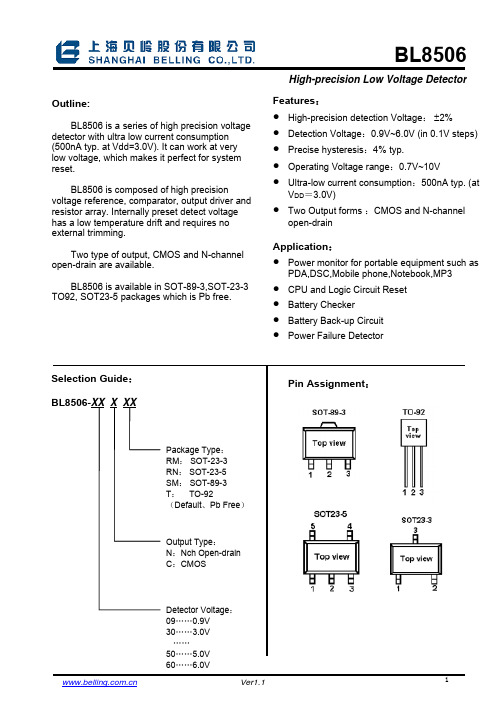

Selection Guide: BL8506-XX X XX

Pin Assignment:

Package Type: RM: SOT-23-3 RN: SOT-23-5 SM: SOT-89-3 T: TO-92 (Default、Pb Free)

Output Type: N:Nch Open-drain C:CMOS

voltage Minimum Operating

voltage

Output current

Output Delay Time

Conditions

VDD=4.7V

Nch VDS=0.05V, VDD=0.70V Pch VDS=-2.1V, VDD=4.50V

Reference data

Min.

Typ.

BL8506 is composed of high precision voltage reference, comparator, output driver and resistor array. Internally preset detect voltage has a low temperature drift and requires no external trimming.

Two type of output, CMOS and N-channel open-drain are available.

in5819中文资料_数据手册_参数

TJ = 75oC TJ = 25oC

1N5819

Reverse Voltage (Volts)

Forward Voltage (Volts)

Reverse Voltage (VR) - Volts Page 7-3

采购电子元器件上万联芯城,只售原装现货,万联芯城专 为终端客户提供电子元器件配单业务,货源均来自原厂及 代理商,客户只需访问官网,联系在线客服提交 BOM 表, 即可获得报价,为客户节省采购成本,满足客户物料需求, 点击进入万联芯城。

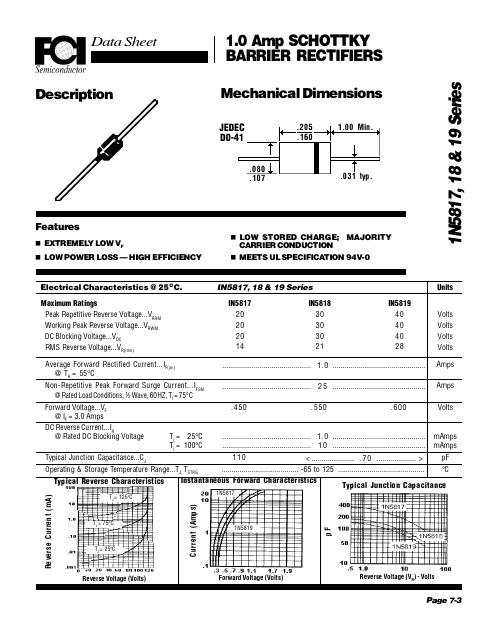

IN5817 20 20 20 14

IN5818 30 30 30 21

IN5819

40

Volts

40

Volts

40

Volts

28

Volts

Average Forward Rectified Current...IF(av) @ TA = 55°C

............................................. 1.0 ............................................... Amps

Typical Junction Capacitance...CJ

110

< ...................... .70 .................... > pF

Operating & Storage Temperature Range...TJ, TSTRG

....................................... -65 to 125 ............................................ °C

BL8506-XX电压检测器选型指南说明书

超低功耗高精度电压检测器BL8506概述: BL8506系列电压检测器,具有高精度,极低功耗(V DD =3.0V 时,I Q =500nA )的特点。

同时,极宽的工作电压范围(0.7V ≦V DD ≦10V ),使得BL8506非常适合用于系统复位的应用中。

BL8506的内部电路由高精度参考源,电压比较器,输出电路和电阻网络等模块组成。

监测电压在芯片内部预先确定,具有高精度,低温漂的特性,无需外部校准。

BL8506电压检测器的输出有CMOS 和N 沟道漏极开路两种形式可供选择。

BL8506可提供SOT-23-3,SOT-23-5, SOT-89-3 ,SC-82AB , TO-92等多种封装形式。

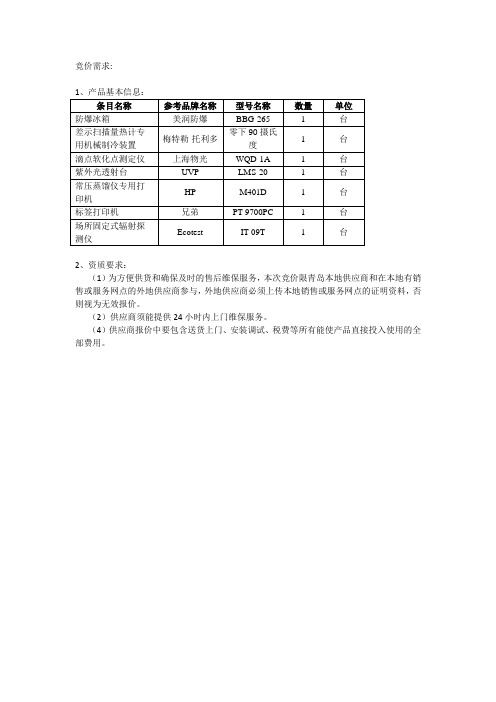

特点:• 检测电压的精度高达±2%• 检测电压范围是0.9V~6V ,每100mV 为间隔(可根据客户需求定制) • 回滞电压典型值为4%• 工作电压范围极宽,为0.7V~10V • 超低功耗,典型值I Q =500nA(V DD =3.0V) • CMOS 和N 沟道漏极开路两种输出形式 •SOT-23-3, SOT-23-5 ,SOT89 -3,SC82AB ,TO-92 等多种封装形式典型应用:• 逻辑电路复位 • 电池电压检测 • 电压窗口比较 • 后备电源管理 •电源故障电路监测上海霖叶微电子有限公司 引脚定义表:引脚号SOT-89-3 TO-92 SOT-23-3SOT-23-5 SC-82AB符号引脚描述1 3 1 1 1 V OUT电压检测输出引脚2 13 2 2 V DD电压输入引脚3 2 2 34 V SS GND引脚--- 4 3 NC 空脚--- 5 -NC 空脚产品命名目录:产品名称检测电压规格输出形式封装形式BL8506-XXARM XXVN沟道开路SOT-23-3BL8506-XXARN XXVN沟道开路SOT-23-5BL8506-XXASM XXVN沟道开路SOT-89-3BL8506-XXASC XXVN沟道开路SC-82ABBL8506-XXAT XXVN沟道开路TO-92BL8506-XXCRM XXVCMOS输出SOT-23-3BL8506-XXCRN XXVCMOS输出SOT-23-5BL8506-XXCSM XXVCMOS输出SOT-89-3BL8506-XXCSC XXVCMOS输出SC-82ABBL8506-XXCT XXVCMOS输出TO-92产品标记信息:系统框图: BL850630A630产品型号符号标记BL8506-09CSM BL8506-09C BL8506-20CT BL8506-20C BL8506-27CSM BL8506-27C BL8506-30CT BL8506-30C …………BL8506-09ARM 609BL8506-21ARN 621BL8506-27CRM 627BL8506-30CRM 630…………N沟道漏极开路输出CMOS输出产品的极限参数:输入电压-----------------------------------------------------------------------------------------0.5V~12V工作温度---------------------------------------------------------------------------------------- -40~+85°C存贮温度---------------------------------------------------------------------------------------- -40~125°C焊接温度和时间-------------------------------------------------------------------------------260°C,10S推荐工作条件:名称最小推荐最大单位输入电压范围0.7 10 V工作环境温度-40 25 70 ℃主要参数和工作特性:• BL8506-09CXX(0.9V)(如非特别注明,测试温度Topt=25℃)数值单位符号定义测试条件最小典型最大V -V DET检测电压 0.8720.9180.9V0.054V HYS回滞电压 0.0180.036I SS功耗电流V DD=2.9V 1 1.5 uAV DDH最大工作电压10V V DDL最小工作电压0.5 V T PLH检测时延100uS • BL8506-27CXX(2.7V) (如非特别注明,测试温度Topt=25℃)数值单位符号定义测试条件最小典型最大2.7-V DET检测电压 2.646V2.754V0.1080.162V HYS回滞电压 0.54I SS功耗电流V DD =4.7V 0.5 1 uAV V DDH最大工作电压10V DDL最小工作电压0.5 VuS T PLH检测时延100• BL8506-30CXX(3.0V)(如非特别注明,测试温度Topt=25℃)数值符号定义测试条件单位最小典型最大V3.063.0-V DET检测电压 2.940.18V0.12V HYS回滞电压 0.60I SS功耗电流V DD =5.0V 0.5 1 uAV V DDH最大工作电压10V DDL最小工作电压0.5 VuS T PLH检测时延100• BL8506-44CXX(4.4V)(如非特别注明,测试温度Topt=25℃)数值单位符号定义测试条件最小典型最大V4.488-V DET检测电压 4.3124.40.264V0.176V HYS回滞电压 0.88I SS功耗电流V DD =6.4V 0.5 1 uAV V DDH最大工作电压10V DDL最小工作电压0.5 V T PLH检测时延100uS 功能说明:V REF 模块产生一个高精度低温度漂移的参考电压,作用于比较器的反向输入端。

DC DC转换器 URB_MT-3WR3系列

3W,Ultra wide input isolated®ulated singleoutput DC/DC converterCB Patent Protection RoHSFEATURES●Ultra wide input voltage rang (4:1)●High efficiency up to 84%●No-load power consumption as low as 0.10W ●Isolation voltage:1.5K VDC●Input Under-voltage Protection ,outputshort-circuit protection ,over-current protection ●Operating temperature range:-40℃to +85℃●International standard pin-out●IEC60950,UL60950,EN60950approvalURB_MT-3WR3series products are of 3W output power,extremely wide range of voltage input of 9-36VDC,18-75VDC,isolation voltage of 1500VDC,Input Under-voltage Protection,output short circuit protection,over-current protection,these products are widely used in fields such as industrial control,electric power,instruments and communication.Selection GuideCertificationPart No.Input Voltage (VDC)OutputEfficiency ②(%,Min./Typ.)@Full LoadMax.Capacitive Load(µF)Nominal (Range)Max.①Output Voltage (VDC)Output Current (mA)(Max./Min.)--URB2403MT-3WR324(9-36)403.3728/073/752200UL /CE/CBURB2405MT-3WR35600/078/802200--URB2409MT-3WR39333/078/801000UL/CE/CBURB2412MT-3WR312250/080/82680URB2415MT-3WR315200/081/83470URB2424MT-3WR324125/080/82100CEURB4803MT-3WR348(18-75)803.3728/073/752200URB4805MT-3WR35600/077/792200URB4812MT-3WR312250/080/82680URB4815MT-3WR315200/082/84470URB4824MT-3WR324125/080/82100Notes:①Exceeding the maximum input voltage may cause permanent damage ;②The efficiency value is measured in the input nominal voltage and output rated load.Input SpecificationsItemOperating Conditions Min.Typ.Max.UnitInput Current (full load /no-load)24VDC input series nominal input voltage3.3V Output --134/4138/7mA Others --154/4161/748VDC input series nominal input voltage3.3V Output --67/469/7Others--77/482/7Reflected Ripple Current Nominal 24VDC input series --120--Nominal 48VDC input series --60--Surge Voltage (1sec.max.)Nominal 24VDC input series -0.7--50VDC Nominal 48VDC input series -0.7--100Starting VoltageNominal 24VDC input series ----9Nominal 48VDC input series ----18Input under-voltage protection Nominal 24VDC input series 5.5 6.5--Nominal 48VDC input series1315.5--Starting Time Nominal input voltage &constant resistance load--10--ms Input FilterC filterCtr l*Module turn-onCtrl pin floating or connected to TTL highlevel(3.5-12VDC)Module turn-offCtrl pin connected to GND or low level(0-1.2VDC)Input current when switched off--610mAHot PlugUnavailableNote:*The voltage of Ctrl pin is relative to input pin GND.Output SpecificationsItemOperating ConditionsMin.Typ.Max.UnitOutput Voltage Accuracy --±1±3%Line Regulation Full load,the input voltage is from low voltage to high voltage --±0.2±0.5Load Regulation 0%-100%load--±0.5±1Transient Recovery Time 25%load step change,nominal input voltage --300500µs Transient Response Deviation --±3±5%Temperature Coefficient Full load----±0.03%/℃Ripple &Noise*20MHz bandwidth ,5%-100%load --30120mV p-p Over-current Protection Input voltage range --150250%Io Short circuit ProtectionHiccup protectionNote:*Ripple and noise are measured by “parallel cable”method,please see DC-DC Converter Application Notes for specific operation.0%-5%load ripple&Noise is no more than 5%Vo.General SpecificationsItemOperating ConditionsMin.Typ.Max.Unit Insulation Voltage Input-output,with the test time of 1minute and the leak current lower than 1mA 1500----VDC Insulation Resistance Input-output,insulation voltage 500VDC 1000----M ΩIsolation Capacitance Input-output,100KHz/0.1V --1000--pFOperating Temperature see Fig.1-40--+85℃Storage Temperature -55--+125Casing Temperature Rise Ta=25℃,nominal input voltage,full load output --+40--Pin Welding Resistance Temperature Welding spot is 1.5mm away from the casing,10seconds ----+300Storage HumidityNon-condensing 5--95%RH Reflow Soldering Temperature Peak temp.≤245℃,maximum duration time ≤60s at 217℃.For actual application,please refer to IPC/JEDEC J-STD-020D.1.Vibration10-55Hz,10G,30Min.along X,Y and ZSwitching Frequency*PWM Mode--350--KHz MTBFMIL-HDBK-217F@25℃1000----K hoursNote:*This series of products using lower frequency technology,the switching frequency value is the test value in full load,when the load is reduced to 50%or less,the switching frequency decreases with decreasing load.Physical SpecificationsCasing Material Black flame-retardant heat-proof plastic Dimensions 19.20*18.10*10.16mm Weight3.5g(Typ.)Cooling MethodFree air convectionEMC SpecificationsEMICECISPR22/EN55022CLASS B (see Fig.3-②for recommended circuit)RE CISPR22/EN55022CLASS B (see Fig.3-②for recommended circuit)EMSESD IEC/EN61000-4-2Contact ±4KV perf.Criteria B RS IEC/EN61000-4-310V/mperf.Criteria A EFT IEC/EN61000-4-4±2KV (see Fig.3-①for recommended circuit)perf.Criteria B Surge IEC/EN61000-4-5line to line ±2KV (see Fig.3-①for recommended circuit)perf.Criteria B CSIEC/EN61000-4-63Vr.m.sperf.Criteria A Immunities of voltage dip,drop and short interruptionIEC/EN61000-4-290%,70%perf.Criteria BProduct Characteristic CurveOperating Temperature()℃Temperature Derating CurveO u t p u t P o w e r P e r c e n t a g e (%)-400407185120806010012040200Safe Operating AreaFig.1Design Reference1.Typical applicationAll the DC/DC converters of this series are tested according to the recommended circuit (see Fig.2)before delivery.If it is required to further reduce input and output ripple,properly increase the input &output of additional capacitors Cin and Cout or select capacitors of low equivalent impedance provided that the capacitance is no larger than the max.capacitive load of the product.VinGND+Vo0VDCCinDC CoutFig.2Vn Cin Cout 24VDC 100µF 10µF 48VDC10µF-47µF10µF2.EMC solution-recommended circuitVi nGND+Vo0VDC/DCLOADC2LDM1②MOVFUSE①C1CY1C3C0+Vi nGNDFig.3Notes:Part ①in the Fig.3is used for EMS test and part ②for EMI filtering;selected based on needs.Parameter descriptionModel Vin:24V Vin:48V FUSE Choose according to actual input currentMOV S20K30S14K60C0680µF/50V 680µF/100V C1,C2 4.7µF/50V4.7µF/100VC3Refer to the Cout in Fig.2LDM112µH CY11nF/2KV3.It is not allowed to connect modules output in parallel to enlarge the power4.For more information about Mornsun EMC Filter products,please visit todownload the Selection Guide of EMC FilterDimensions and Recommended LayoutNC:Pin to be isolated from circuitryNotes:1.Packing information please refer to Product Packing Information which can be downloaded from .TubePacking Bag Number:58010114,Reel Packing Bag Number:58010115;2.The max.capacitive load should be tested within the input voltage range and under full load conditions;3.If the product needs to be cleaned after welding,please wait to completely dried before electrical use it;4.Unless otherwise specified,parameters in this datasheet were measured under the conditions of Ta=25℃,humidity<75%RH with nominalinput voltage and rated output load;5.All index testing methods in this datasheet are based on our Company’s corporate standards;6.We can provide product customization service,please directly contact our technicians for specific information;7.Specifications of this product are subject to changes without prior notice.Mornsun Guangzhou Science&Technology Co.,Ltd.Address:No.5,Kehui St.1,Kehui Development Center,Science Ave.,Guangzhou Science City,Luogang District,Guangzhou,P.R.China Tel:86-20-38601850-8801Fax:86-20-38601272E-mail:***************。

测速雷达主要设备功能及技术参数

测速雷达主要设备功能及技术参数测速雷达型号:KTR-C3(品牌:KITOZER/开拓者)采用高速DSP信号处理芯片、0.1秒快速捕捉。

1)设计小巧轻便、制作精良。

2)纯铸铁结构,坚固耐用。

3)232串口输出。

4)精确度高,捕捉目标速度快。

5)动态时具有同向功能。

6)静态时可分别检测来车、去车。

7)静态测速范围:0~322 KPH。

8)移动测速范围:19~322KPH。

9)环境要求:温度:-30度 ~ +70度;湿度:0 % ~ 90% 。

10)Ka波段窄波雷达,微波频率:34.7GHz(Ka-band),可有效规避探测狗检测。

11)发射角:±4度。

12)规格:重:0.52kg、直径:6.7cm、长:11.8cm。

13)精确度:+/-1KPH。

高清摄像机(品牌:KITOZER/开拓者)高清摄像机功能:CCD成像,200万象素,主要端口有:闪光灯同步口,通过同步线与闪光灯连接;拍照触发口,当收到外部脉冲触发信号时,高清摄像机会抓取一张图片,脉冲信号由独立的拍照触发器发出;网口(100M),与控制主机连接,接收参数配置,上传图片,也可接收带由协议内容的抓拍命令。

产品详细参数表百万像素变焦镜头日本精工本次中煤平朔公司系统百万像素变焦镜头选型为日本精工SE5018MP产品,AVENIR ETOKU(日本精工)十几年来始终专心于监控镜头的市场发展,成为中国安防监控领域用得最多的专业镜头。

本次系统高清摄像机选型为广州莱安智能化系统开发有限公司出品的KTR200A型高清摄像机。

KTR200A是集成一体的高速彩色/单色智能工业相机,采用总像素200万像素的CCD图像传感器,具有处理速度快、分辨率高、图像质量好等特点。

广泛应用于智能交通、电子警察、卡口、高速公路、停车厂等领域的检测和识别。

百万像素网络拍照摄像一体机,将高清图像抓拍、标清视频摄像完美结合,超高清晰度,分辨率达130万~500万像素,专业用于如平安城市建设、机场、银行、道路卡口监控及牌照识别等安全防范领域,能够为客户提供专业的可定制产品及服务,支持后续增值开发。

BL8509中文资料

Reference data

Min.

Typ.

Max.

Unit

2.94

3.0

3.06

V

0.5

1

uA

10

V

0.5

V

mA

0.01

0.05

1.0

2.0

mA

BL8509-340DNRM 3.4V

(Topt 25 ,Unless otherwise specified.)

Symbol -VDET ISS VDDH VDDL

IOUT

Parameter

Detector Threshold Current consumption Maximum operating

voltage Minimum Operating

voltage

Output current

Conditions VDD=5.0V

- 4Total 17 Pages

8/8/2006

元器件交易网

BL8509

BL8509-440DNRM 4.4V

(Topt 25 ,Unless otherwise specified.)

Symbol -VDET ISS VDDH VDDL

IOUT

Parameter

Detector Threshold Current consumption Maximum operating

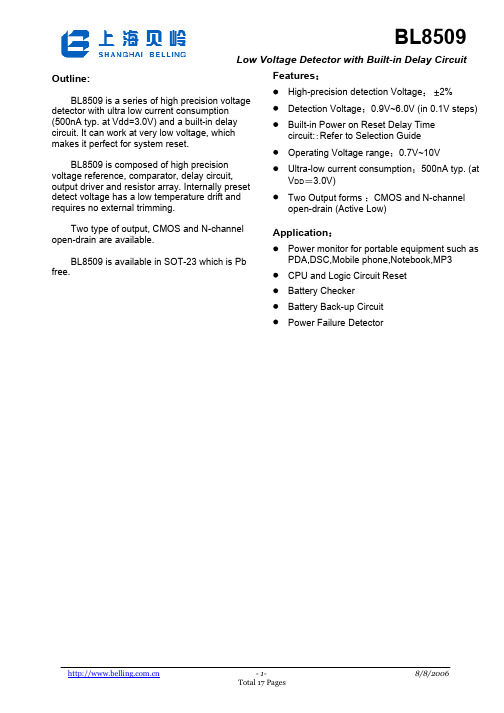

Features

High-precision detection Voltage 2%

Detection Voltage 0.9V~6.0V (in 0.1V steps)

ads8509

REFCAPR1INR2INR3INADS8509 SLAS324C–OCTOBER2004–REVISED APRIL2010 16-BIT250-KSPS SERIAL CMOS SAMPLING ANALOG-TO-DIGITAL CONVERTERCheck for Samples:ADS8509FEATURES DESCRIPTION•250-kHz Sampling Rate The ADS8509is a complete16-bit samplinganalog-to-digital(A/D)converter using state-of-the-art •4-V,5-V,10-V,±3.33-V,±5-V,and±10-V InputCMOS structures.It contains a complete16-bit, Rangescapacitor-based,successive approximation register •±2LSB Max INL(SAR)A/D converter with sample-and-hold,•±1LSB Max DNL,16-Bit No Missing Codes reference,clock,and a serial data interface.Data canbe output using the internal clock or can be •SPI Compatible Serial Output with Daisy-Chainsynchronized to an external data clock.The ADS8509 (TAG)Featurealso provides an output synchronization pulse for •Single5-V Supplyease of use with standard DSP processors.•Pin-Compatible with ADS7809(Low Speed)The ADS8509is specified at a250-kHz sampling rate and12-Bit ADS8508/7808over the full temperature range.Precision resistors •Uses Internal or External Reference provide various input ranges including±10V and0V •70-mW Typ Power Dissipation at250KSPS to5V,while the innovative design allows operationfrom a single+5-V supply with power dissipation •20-Pin SO and28-Pin SSOP Packagesunder100mW.•Simple DSP InterfaceThe ADS8509is available in20-pin SO and28-pinSSOP packages,both fully specified for operation APPLICATIONSover the industrial-40°C to85°C temperature range.•Industrial Process Control•Data Acquisition Systems•Digital Signal Processing•Medical Equipment•InstrumentationPlease be aware that an important notice concerning availability,standard warranty,and use in critical applications of TexasInstruments semiconductor products and disclaimers thereto appears at the end of this data sheet.All trademarks are the property of their respective owners.ADS8509SLAS324C–OCTOBER2004–REVISED This integrated circuit can be damaged by ESD.Texas Instruments recommends that all integrated circuits be handled with appropriate precautions.Failure to observe proper handling and installation procedures can cause damage.ESD damage can range from subtle performance degradation to complete device failure.Precision integrated circuits may be more susceptible to damage because very small parametric changes could cause the device not to meet its published specifications.PACKAGE/ORDERING INFORMATION(1)MINIMUMNO MINIMUM SPECIFICATIONRELATIVE PACKAGE PACKAGE ORDERING TRANSPORT PRODUCT MISSING SINAD TEMPERATUREACCURACY LEAD DESIGNATOR NUMBER MEDIA,QTY CODE(dB)RANGE(LSB)ADS8509IBDW Tube,25SO-20DWADS8509IBDWR Tape and Reel,2000 ADS8509IB±21685–40°C to85°CADS8509IBDB Tube,50SSOP-28DBADS8509IBDBR Tape and Reel,2000ADS8509IDW Tube,25SO-20DWADS8509IDWR Tape and Reel,2000 ADS8509I±31583–40°C to85°CADS8509IDB Tube,50SSOP-28DBADS8509IDBR Tape and Reel,2000 (1)For the most current package and ordering information,see the Package Option Addendum at the end of this document,or visit thedevice product folder on .ABSOLUTE MAXIMUM RATINGSover operating free-air temperature range(unless otherwise noted)(1)UNITR1IN±25VR2IN±25VAnalog inputs R3IN±25VREF+V ANA+0.3V to AGND2–0.3VCAP Indefinite short to AGND2,momentary short to V ANADGND,AGND2±0.3VV ANA6VGround voltage differencesV DIG to V ANA0.3VV DIG6VDigital inputs–0.3V to+V DIG+0.3VMaximum junction temperature165°CStorage temperature range–65°C to150°CInternal power dissipation700mWLead temperature(soldering,1.6mm from case10seconds)260°C(1)All voltage values are with respect to network ground terminal.ADS8509 SLAS324C–OCTOBER2004–REVISED APRIL2010ELECTRICAL CHARACTERISTICSAt T A=–40°C to85°C,f s=250kHz,V DIG=V ANA=5V,using internal reference and0.1%,0.25-W fixed resistors(seeFigure29and Figure30)(unless otherwise specified)ADS8509I ADS8509IB PARAMETER TEST CONDITIONS UNITMIN TYP MAX MIN TYP MAX Resolution1616Bits ANALOG INPUTVoltage range(1)Impedance(1)Capacitance5050pF THROUGHPUT SPEEDConversion cycle Acquire and convert44m s Throughput rate250250kHzDC ACCURACYINL Integral linearity error–33–22LSB(2) DNL Differential linearity error–22–11LSB No missing codes1516Bits Transition noise(3)11LSB±10-V Range Int.ref.with0.1%external fixed–0.50.5–0.50.5 Full-scale%FSRresistorserror(4)(5)All other ranges–0.50.5–0.50.5Full-scale error drift Int.ref.±7±7ppm/°C±10-V Range Ext.ref.with0.1%external–0.50.5–0.50.5 Full-scale%FSRfixed resistorserror(4)(5)All other ranges–0.50.5–0.50.5Full-scale error drift Ext.ref.±2±2ppm/°C Bipolar zero error(4)–1010–55mV Bipolar zero error drift±0.4±0.4ppm/°C10-V Range–55–55 Unipolar zeromV 4-V and5-V–33–33 error(4)RangeUnipolar zero error drift±2±2ppm/°C Recovery to rated accuracy after1-m F Capacitor to CAP11ms power downPower supply sensitivity–88–88+4.75V<V D<+5.25V LSB (V DIG=V ANA=V D)AC ACCURACYSFDR Spurious-free dynamic range f I=20kHz90999599dB(6) THD Total harmonic distortion f I=20kHz–98–90–98–93dBSINAD f I=20kHz83888588dB Signal-to-(noise+distortion)–60-dB Input3032dB SNR Signal-to-noise ratio f I=20kHz83888688dB Full-power bandwidth(7)500500kHz SAMPLING DYNAMICSAperture delay55ns Transient response FS Step22m s Overvoltage recovery(8)150150ns(1)±10V,0V to5V,etc.(see Table2).For normal operation,the analog input should not exceed configured range±20%.(2)LSB means least significant bit.For the±10-V input range,one LSB is305m V.(3)Typical rms noise at worst case transitions and temperatures.(4)As measured with fixed resistors shown in Figure29and Figure30.Adjustable to zero with external potentiometer.Factory calibratedwith0.1%,0.25-W resistors.(5)For bipolar input ranges,full-scale error is the worst case of–full-scale or+full-scale uncalibrated deviation from ideal first and last codetransitions,divided by the transition voltage(not divided by the full-scale range)and includes the effect of offset error.For unipolar input ranges,full-scale error is the deviation of the last code transition divided by the transition voltage.It also includes the effect of offset error.(6)All specifications in dB are referred to a full-scale±10-V input.(7)Full-power bandwidth is defined as the full-scale input frequency at which signal-to-(noise+distortion)degrades to60dB.(8)Recovers to specified performance after2x FS input overvoltage.ADS8509SLAS324C–OCTOBER2004–REVISED ELECTRICAL CHARACTERISTICS(continued)At T A=–40°C to85°C,f s=250kHz,V DIG=V ANA=5V,using internal reference and0.1%,0.25-W fixed resistors(seeFigure29and Figure30)(unless otherwise specified)ADS8509I ADS8509IB PARAMETER TEST CONDITIONS UNITMIN TYP MAX MIN TYP MAX REFERENCEInternal reference voltage No load 2.48 2.5 2.52 2.48 2.5 2.52VInternal reference source current11m A (must use external buffer)Internal reference drift88ppm/°CExternal reference voltage range 2.3 2.5 2.7 2.3 2.5 2.7V for specified linearityExternal reference current drain Ext.2.5-V ref.100100m A DIGITAL INPUTSLogic levelsV IL Low-level input voltage–0.30.8–0.30.8VV IH High-level input voltage 2.0V DIG+0.3V 2.0V DIG+0.3V VI IL Low-level input current V IL=0V±10±10m AI IH High-level input current V IH=5V±10±10m A DIGITAL OUTPUTSData format(serial16-bits)Data coding(binary2'scomplement or straight binary)Pipeline delay(conversion resultsonly available after completedconversion)Data clock(selectable for internalor external data clock)Internal clock(output only when EXT/INT Low99MHz transmitting data)External clock(can run EXT/INT High0.1260.126continually but not recommended MHz for optimum performance)V OL Low-level output voltage I SINK=1.6mA0.40.4VV OH High-level output voltage I SOURCE=500m A44VHi-Z State,±5±5m A Leakage currentV OUT=0V to V DIGOutput capacitance Hi-Z State1515pF POWER SUPPLIESV DIG Digital input voltage 4.755 5.25 4.755 5.25VV ANA Analog input voltage 4.755 5.25 4.755 5.25VMust be≤V ANAI DIG Digital input current44mAI ANA Analog input current1010mA POWER DISSIPATIONPWRD Low f S=250kHz7010070100mW PWRD High5050m W TEMPERATURE RANGESpecified performance–4085–4085°C Derated performance(9)–55125–55125°C Storage–65150–65150°C THERMAL RESISTANCE(q JA)SSOP6262°C/W SO4646°C/W (9)The internal reference may not be started correctly beyond the industrial temperature range(–40°C to85°C),therefore use of anexternal reference is recommended.V DIG V ANA BUSY CS R/C TAG DATA DATACLKSYNCR1IN AGND1REF CAP AGND2R2IN R3IN SB/BTC EXT/INT DGNDPWRD R1IN AGND1REF CAP AGND2R2IN R3IN SB/BTC EXT/INT DGNDNC NC NC NC V DIG V ANA BUSY CS NC NC R/C NCTAG PWRD DATA DATACLK SYNCNC ADS8509SLAS324C –OCTOBER 2004–REVISED APRIL 2010PIN CONFIGURATIONSDW PACKAGESO-20(TOP VIEW)DB PACKAGE SSOP-28(TOP VIEW)ADS8509SLAS324C–OCTOBER2004–REVISED Terminal FunctionsTERMINALDESCRIPTIONNAME DB NO.DW NO.I/OAGND122–Analog ed internally as ground reference point.Minimal current flow.AGND297–Analog groundBUSY2517O Busy output.Falls when a conversion is started and remains low until the conversion is completedand the data is latched into the output shift register.CAP65–Reference buffer capacitor.2.2-m F Tantalum to ground.CS2416–Chip select.Internally ORed with R/C.DATA1713O Serial data output.Data is synchronized to DATACLK with the format determined by the level ofSB/BTC.In the external clock mode,after16bits of data,the ADS8509outputs the level input onTAG as long as CS is low and R/C is high(see Figure8and Figure9).If EXT/INT is low,data isvalid on both the rising and falling edges of DATACLK,and between conversions DATA stays atthe level of the TAG input when the conversion was started.DATACLK1612I/O Either an input or an output depending on the EXT/INT level.Output data is synchronized to thisclock.If EXT/INT is low,DATACLK transmits16pulses after each conversion and then remainslow between conversions.DGND1410–Digital groundEXT/INT139–Selects external or internal clock for transmitting data.If high,data is output synchronized to theclock input on DATACLK.If low,a convert command initiates the transmission of the data from theprevious conversion,along with16-clock pulses output on DATACLK.NC5,8,10,––No connect11,18,20,22,23PWRD2618I Power down input.If high,conversions are inhibited and power consumption is significantlyreduced.Results from the previous conversion are maintained in the output shift register.R/C2115I Read/convert input.With CS low,a falling edge on R/C puts the internal sample-and-hold into thehold state and starts a conversion.When EXT/INT is low,this also initiates the transmission of thedata results from the previous conversion.If EXT/INT is high,a rising edge on R/C with CS low ora falling edge on CS with R/C high transmits a pulse on SYNC and initiates the transmission ofdata from the previous conversion.REF76I/O Reference input/output.Outputs internal2.5-V reference.Can also be driven by external systemreference.In both cases,bypass to ground with a2.2-m F tantalum capacitor.R1IN11I Analog input.See Table2for input range connections.R2IN33I Analog input.See Table2for input range connections.R3IN44I Analog input.See Table2for input range connections.SB/BTC128I Select straight binary or binary2's complement data output format.If high,data is output in astraight binary format.If low,data is output in a binary2's complement format.SYNC1511O Sync output.This pin is used to supply a data synchronization pulse when the EXT level is highand at least one external clock pulse has occurred when not in the read mode.See the externalclock modes desciptions.TAG1914I Tag input for use in the external clock mode.If EXT is high,digital data input from TAG is outputon DATA with a delay that is dependent on the external clock mode.See Figure8and Figure9.V ANA2719I Analog supply input.Nominally+5V.Connect directly to pin20and decouple to ground with0.1-m F ceramic and10-m F tantalum capacitors.V DIG2820I Digital supply input.Nominally+5V.Connect directly to pin19.Must be≤V ANA.CS R/CExternal DATACLKCS Set Low, Discontinuous Ext DATACLKR/C CSExternal DATACLKR/C Set Low, Discontinuous Ext DATACLKCSR/CBUSYExternal DATACLKCS Set Low, Discontinuous Ext DATACLKADS8509SLAS324C –OCTOBER 2004–REVISED APRIL 2010TIMING REQUIREMENTS,T A =–40°C to 85°CPARAMETERMIN TYPMAXUNIT t w1Pulse duration,convert 40ns t d1Delay time,BUSY from R/C low 620ns t w2Pulse duration,BUSY low2.2m s t d2Delay time,BUSY,after end of conversion 5ns t d3Delay time,aperture 5ns t conv Conversion time 2.2m s t acq Acquisition time 1.8m s t conv +t acqCycle time4m s t d4Delay time,R/C low to internal DATACLK output 270ns t c1Cycle time,internal DATACLK110ns t d5Delay time,data valid to internal DATACLK high 1535ns t d6Delay time,data valid after internal DATACLK low 2035ns t c2Cycle time,external DATACLK 35ns t w3Pulse duration,external DATACLK high 15ns t w4Pulse duration,external DATACLK low15ns t su1Setup time,R/C rise/fall to external DATACLK high 15ns t su2Setup time,R/C transition to CS transition 10ns t d7Delay time,SYNC,after external DATACLK high 335ns t d8Delay time,data valid 220ns t d9Delay time,CS to rising edge10ns t d10Delay time,previous data available after CS,R/C low 2m s t su3Setup time,BUSY transition to first external DATACLK 5ns t d11Delay time,final external DATACLK to BUSY falling edge 1m s t su3Setup time,TAG valid 0ns t h1Hold time,TAG valid2nsPARAMETER MEASUREMENT INFORMATIONFigure 1.Critical TimingR/CBUSYSTATUSInternal DATACLKDATA8starts READCS, EXT/INT , and TAG are tied lowBUSYSTATUSExternal DATACLKDATA Nth Data(N+1)th Data TAG = 0No more data to shift outNo more data to shift outTAG = 0TAG = 0TAG = 0TAG = 0R/CEXT/INT tied high, CS and TAG are tied lowt w1 + t su1 starts READt ADS8509SLAS324C –OCTOBER 2004–REVISED APRIL 2010PARAMETER MEASUREMENT INFORMATION (continued)Figure 2.Basic Conversion Timing (Internal DATACLK -Read Previous Data During Conversion)Figure 3.Basic Conversion Timing (External DATACLK)EXT/INT tied high, CS tied lowt w1 + t su1 starts READRising DATACLK change DATA, t w1 + t su1 Starts READTAG is not recommended for this mode. There is not enough time to do so without violating t d11.ADS8509SLAS324C –OCTOBER 2004–REVISED APRIL 2010PARAMETER MEASUREMENT INFORMATION (continued)Figure 4.Read After Conversion (Discontinuous External DATACLK)Figure 5.Read During Conversion (Discontinuous External DATACLK)ADS8509SLAS324C–OCTOBER2004–REVISED PARAMETER MEASUREMENT INFORMATION(continued)EXT/INT tied high, CS tied low t w1 + t su1 starts READFigure6.Read After Conversion With SYNC(Discontinuous External DATACLK)t w1 + t su1 Starts READTAG is not recommended for this mode. There is not enoughtime to do so without violating t d11.Figure7.Read During Conversion With SYNC(Discontinuous External DATACLK)E x t e r n a l D A T A C L KC SR /CB U S YS Y N CD A T AT A GFigure 8.Conversion and Read Timing with Continuous External DATACLK Tied High)ReadAfter Conversions (Not Recommended)Copyright ©2004–2010,Texas Instruments Incorporated 11E D A T A GFigure 9.Conversion and Read Timing with Continous External DATACLK Tied High)ReadPrevious Conversion Results During Conversion (Not Recommended)S F D R − S p u r i o u s F r e e D y n a m i c R a n g e − d BT A − Free-Air Temperature − 5CT H D − T o t a l H a r m o n i c D i s t o r t i o n − d BT A − Free-Air Temperature − 5CS N R −S i g n a l -t o -N o i s e R a t i o − d B707580859095100−402585T A − Free-Air Temperature − 5C−402585S I N A D − S i g n a l -T o -N o i s e a n d D i s t o r t i o n − d BT A − Free-Air Temperature − 5CS I N A D − S i g n a l -T o -N o i s e a n d D i s t o r t i o n − d B657075808590110100f i − Input Frequency − kHz657075808590110100S N R − S i g n a l -t o -N o i s e R a t i o − d Bf i − Input Frequency − kHzTYPICAL CHARACTERISTICSSPURIOUS FREE DYNAMIC RANGETOTAL HARMONIC DISTORTIONvsvsFREE-AIR TEMPERATUREFREE-AIR TEMPERATUREFigure 10.Figure 11.SIGNAL-TO-NOISE RATIOSIGNAL-TO-NOISE AND DISTORTIONvsvsFREE-AIR TEMPERATUREFREE-AIR TEMPERATUREFigure 12.Figure 13.SIGNAL-TO-NOISE RATIOSIGNAL-TO-NOISE AND DISTORTIONvsvsINPUT FREQUENCYINPUT FREQUENCYFigure 14.Figure 15.Copyright ©2004–2010,Texas Instruments Incorporated 13707580859095100105110100S F D R − S p u r i o u s F r e e D y n a m i c R a n g e − d Bf i − Input Frequency − kHz−70−75−80−85−90−95−100−105110100T H D − T o t a l H a r m o n i c D i s t o r t i o n − d Bf i− Input Frequency − kHzI n t e r n a l R e f e r e n c e V o l t a g e − V T A − Free-Air Temperature − 5CB i p o l a r Z e r o S c a l e E r r o r − m VT A − Free-Air Temperature − 5CT A − Free-Air Temperature − 5C F u l l S c a l e E r r o r − %F S R1011121314151617181920−40−25−1052035506580S u p p l y C u r r e n t − m AT A − Free-Air Temperature − 5CSPURIOUS FREE DYNAMIC RANGETOTAL HARMONIC DISTORTIONvsvsINPUT FREQUENCYINPUT FREQUENCYFigure 16.Figure 17.INTERNAL REFERENCE VOLTAGEBIPOLAR ZERO SCALE ERRORvsvsFREE-AIR TEMPERATUREFREE-AIR TEMPERATUREFigure 18.Figure 19.FULL SCALE ERRORSUPPLY CURRENTvsvsFREE-AIR TEMPERATUREFigure 20.Figure 21.P e r f o r m a n c eESR − Resistance − WH i t sCode16384327684915265536I N L − L S B sCode16384327684915265536D N L − L S B sCodePERFORMANCEvsHISTOGRAMFigure 22.Figure 23.INTEGRAL NONLINEARITYFigure 24.DIFFERENTIAL NONLINEARITYFigure 25.Copyright ©2004–2010,Texas Instruments Incorporated 15255075100125A m p l i t u d e − d Bf − Frequency − kHzFFT (20-kHz Input)Figure 26.BASIC OPERATIONTwo signals control conversion in the ADS8509:CS and R/C.These two signals are internally ORed together.To start a conversion the chip must be selected,low,and the conversion signal must be active,low.Either signal can be brought low first.Conversion starts on the falling edge of the second signal.BUSY goes low when conversion starts and returns high after the data from that conversion is shifted into the internal storage register.Sampling begins when BUSY goes high.To reduce the number of control pins can be tied low permanently.The pin now controls conversion and data reading exclusively.In the external clock mode this means that the ADS8509clocks out data whenever R/C is brought high and the external clock is active.In the internal clock mode data is clocked out every convert cycle regardless of the states of CS and R/C.The ADS8509provides a TAG input for cascading multiple converters together.READING DATAThe conversion result is available as soon as BUSY returns to high,therefore data always represents the conversion previously completed even when it is read during a conversion.The ADS8509outputs serial data in either straight binary or binary two’s compliment format.The pin controls the format.Data is shifted out MSB first.The first conversion immediately following a power-up does not produce a valid conversion result.Data can be clocked out with either the internally generated clock or with an external clock.The pin controls this function.If an external clock is used,the TAG input can be used to daisy-chain multiple ADS8509data pins together.INTERNAL DATACLKIn internal clock mode data for the previous conversion is clocked out during each conversion period.The internal data clock is synchronized to the internal conversion clock so that is does not interfere with the conversion process.The DATACLK pin becomes an output when EXT/INT is low.16Clock pulses are generated at the beginning of each conversion after timing t 8is satisfied,i.e.only the previous conversion result can be read during conversion.DATACLK returns to low when it is inactive.The 16bits of serial data are shifted out the DATA pin synchronous to this clock with each bit available on a rising and then a falling edge.The DATA pin returns to the state of the TAG pin input sensed at the start of transmission.EXTERNAL DATACLKThe external clock mode offers several ways to retrieve conversion results.However,since the external clock cannot be synchronized to the internal conversion clock care must be taken to avoid corrupting the data.When is set high,the and signals control the read state.When the read state is initiated,the result from the previously completed conversion is shifted out the DATA pin synchronous to the external clock that is connected to the DATACLK pin.Each bit is available on a falling and then a rising edge.The maximum external clock speed of28.5MHz allows data to be shifted out quickly either at the beginning of conversion or the beginning of sampling.There are several modes of operation available when using an external clock.It is recommended that the external clock run only while reading data.This is discontinuous clock mode.Since the external clock is not synchronized to the internal clock that controls conversion slight changes in the external clock can cause conflicts that can corrupt the conversion process.Specifications with a continuously running external clock cannot be ensured.It is especially important that the external clock does not run during the second half of the conversion cycle(approximately the time period specified by t d11,see the TIMING REQUIREMENTS table).In discontinuous clock mode data can be read during conversion or during sampling,with or without a SYNC pulse.Data read during conversion must meet the t d11timing specification.Data read during sampling must be complete before starting a conversion.Whether reading during sampling or during conversion a SYNC pulse is generated whenever at least one rising edge of the external clock occurs while the part is not in the read state.In the discontinuous external clock with SYNC mode a SYNC pulse follows the first rising edge after the read command.The data is shifted out after the SYNC pulse.The first rising clock edge after the read command generates a SYNC pulse.The SYNC pulse can be detected on the next falling edge and then the next rising edge.Successively,each bit can be read first on the falling edge and then on the next rising edge.Thus17clock pulses after the read command are required to read on the falling edge.18Clock pulses are necessary to read on the rising edge.Table1.DATACLK PulsesDATACLK PULSES REQUIREDDESCRIPTIONWITH SYNC WITHOUT SYNCRead on falling edge of DATACLK1716Read on rising edge of DATACLK1817If the clock is entirely inactive when not in the read state a SYNC pulse is not generated.In this case the first rising clock edge shifts out the MSB.The MSB can be read on the first falling edge or on the next rising edge.In this discontinuous external clock mode with no SYNC,16clocks are necessary to read the data on the falling edge and17clocks for reading on the rising edge.Data always represents the conversion already completed.TAG FEATUREThe TAG feature allows the data from multiple ADS8509converters to be read on a single serial line.The converters are cascaded together using the DATA pins as outputs and the TAG pins as inputs as illustrated in Figure27.The DATA pin of the last converter drives the processor's serial data input.Data is then shifted through each converter,synchronous to the externally supplied data clock,onto the serial data line.The internal clock cannot be used for this configuration.The preferred timing uses the discontinuous external data clock during the sampling period.Data must be read during the sampling period because there is not sufficient time to read data from multiple converters during a conversion period without violating the t d11constraint(see the EXTERNAL DATACLOCK section).The sampling period must be sufficiently long to allow all data words to be read before starting a new conversion.Note,in Figure27,that a NULL bit separates the data word from each converter.The state of the DATA pin at the end of a READ cycle reflects the state of the TAG pin at the start of the cycle.This is true in all READ modes,including the internal clock mode.For example,when a single converter is used in internal clock mode, the state of the TAG pin determines the state of the DATA pin after all16bits have shifted out.When multiple converters are cascaded together,this state forms the NULL bit that separates the words.Thus,with the TAG pin of the first converter grounded as shown in Figure27the NULL bit becomes a zero between each data word.Copyright©2004–2010,Texas Instruments Incorporated17.Figure27.Timing of TAG Feature With Single Conversion(Using External DATACLK)ANALOG INPUTSThe ADS8509has six analog input ranges as shown in Table2.The offset and gain specifications are factory calibrated with0.1%,0.25-W,external resistors as shown in Figure29and Figure30.The external resistors can be omitted if larger gain and offset errors are acceptable or if using software calibration.The hardware trim circuitry shown in Figure29and Figure30can reduce the errors to zero.The analog input pins R1IN,R2IN,and R3IN have±25-V overvoltage protection.The input signal must be referenced to AGND1.This minimizes the ground loop problem typical to analog designs.The analog input should be driven by a low impedance source.A typical driving circuit using OPA627or OPA132is shown in Figure28.The ADS8509can operate with its internal2.5-V reference or an external reference.An external reference connected to pin6(REF)bypasses the internal reference.The external reference must drive the4-kΩresistor that separates pin6from the internal reference(see the illustration on page1).The load varies with the difference between the internal and external reference voltages.The external reference voltage can vary from 2.3V to2.7V.The internal reference is approximately2.5V.The reference,whether internal or external,is buffered internally with a buffer with its output on pin5(CAP).The ADS8509is factory tested with2.2-m F capacitors connected to pins5and6(CAP and REF).Each capacitor should be placed as close as possible to its pin.The capacitor on pin6band limits the internal reference noise.A smaller capacitor can be used but it may degrade SNR and SINAD.The capacitor on pin5stabilizes the reference buffer and provides switching charge to the CDAC during conversion.Capacitors smaller than1m F can cause the buffer to become unstable and may not hold sufficient charge for the CDAC.The parts are tested to specifications with2.2m F so larger capacitors are not necessary.The equivalent series resistor(ESR)of these compensation capacitors is also critical.The total ESR must be kept under3Ω.See the TYPICAL CHARACTERISTICS section concerning how ESR affects performance.Neither the internal reference nor the buffer should be used to drive an external load.Such loading can degrade performance.Any load on the internal reference causes a voltage drop across the4-kΩresistor and affects gain. The internal buffer is capable of driving±2-mA loads but any load can cause perturbations of the reference at the CDAC,degrading performance.It should be pointed out that,unlike other competitor’s parts with similar input structure,the ADS8509does not require a second high-speed amplifier used as a buffer to isolate the CAP pin from the signal dependent current in the R3IN pin but can tolerate it if one does exist.。

DS-TMG022车辆检测器用户手册说明书

DS-TMG022 Vehicle Detector User Manual

Regulatory Information

FCC Information

Please take attention that changes or modification not expressly approved by the party responsible for compliance could void the user’s authority to operate the equipment.

2012/19/EU (WEEE directive): Products marked with this symbol cannot be disposed of as unsorted municipal waste in the European Union. For proper recycling, return this product to your local supplier upon the purchase of equivalent new equipment, or dispose of it at designated collection points. For more information see: 2006/66/EC (battery directive): This product contains a battery that cannot be disposed of as unsorted municipal waste in the European Union. See the product documentation for specific battery information. The battery is marked with this symbol, which may include lettering to indicate cadmium (Cd), lead (Pb), or mercury (Hg). For proper recycling, return the battery to your supplier or to a designated collection point. For more information see: Industry Canada ICES-003 Compliance This device meets the CAN ICES-3 (A)/NMB-3(A) standards requirements.

DS_BL9180--Dual,300mA Ultra-low Noise LDO(EN,V2.1)

VDD

2

5

GND

VDD

2

VOUT2 VOUT2

3

4

EN2 EN2

EN2 EN2

3

Part Number BL9180-XXXRA BL9180-XXXRB BL9180-XXXEP

Top Mark EVYW EVYW BL9180 (Note3) VYWEP

(Note3)

Temp Range -40° C to +85°C -40° C to +85°C -40° C to +85°C

PPMIC BU BL9180 Rev 2.1 8/2010

Belling Proprietary Information. Unauthorized Photocopy and Duplication Prohibited ©2010 Belling All Rights Reserved

Package Information

SOTSOT-2323-6A TOP VIEW VOUT1 VOUT1 1 MARKING 6 EN1 EN1 EN1 EN1 1 MARKING SOTSOT-2323-6B TOP VIEW 6 VOUT1 VOUT1 VOUT1 VOUT1 VIN1 VIN1 5 GND VOUT2 VOUT2 4 VOUT2 VOUT2 VIN2 VIN2 3 4 1 MARKING 2 ESOPESOP-8 TOP VIEW 8 7 6 5 EN1 EN1 GND GND EN2 EN2

Belling Proprietary Information. Unauthorized Photocopy and Duplication Prohibited ©2010 Belling All Rights Reserved

Richtek Technology Corporation RT9807 微型电压检测器说明书