VPR A new packing, placement and routing tool for FPGA research

Eaton 自定义设计的 VPI VPE 干式变压器产品介绍说明书

December 2012Sheet14 General Description014VPI/VPE Dry-TypeTransformersApplication DescriptionEaton’s VPI and VPE transformersare custom-designed dry-type powertransformers, which give environmen-tal protection, for both indoor andoutdoor applications. The transform-ers are explosion-resistant, fire-resistant, non-polluting to theenvironment, and ideally suitable foruse in coordinated unit substations.Typical applications of VPI/VPEtransformers are:■Schools, hospitals, shopping centers■High-rise buildings■Industrial environmentsBenefits■Custom-design flexibility to meet special customer needs andapplications■Computerized loss-evaluated designs for specific customer load and evaluation criteria■Environmental protection■Low maintenance■High short-circuit strength■IEEE short-time overload capability ■Aluminum or copper windings■Available in NEMA 1, 2 and3R enclosures■EconomicalRatings■112.5–3750 kVA■Primary voltages: 600V–35 kV■Primary BIL: up to 150 kV■Secondary voltages: 120V–15 kV■Secondary BIL: up to 75 kV■Temperature rise: 80/115/150°CDry-Type Substation TransformerDesign and TechnologyThe dry-type transformers are customdesigned and manufactured with coilsinsulated with 220°C Class H Nomex®,insulation system. Environmentalprotection is provided by vacuumpressure impregnation with polyesterresin (VPI). Enhanced environmentalprotection is available through the useof silicone resin encapsulation (VPE).The VPE process provides 4-cycleenhanced environmental protection.The entire core and coil assembly isvacuum pressure encapsulated witha silicone resin per MIL-1-24092. Bothsystems are superior to the conven-tional dry-type technology known as“Dip and Bake.” Both resin types, andNomex, insulation system are 220°CClass H rated. Transformers with ClassH insulation are suitable for use up to150°C average rise over a maximumambient temperature of 40°C, not toexceed 30°C average for any 24-hourperiod. Other temperature rise optionsare 80°C and 115°C, which allow thetransformer to be overloaded up to150°C rise.Taps are provided on the central sectionof the HV coil face. Taps are accessed byremoving enclosure panels, and taps arechanged by moving the flexible boltedlinks from one connecting point to theother. T o simplify these changes, theconnection points are clearly identified.Material used for cores is non-aging,cold rolled, high permeability, grain-oriented silicone steel. Cores are con-structed with step lap mitered joints andare rigidly braced to reduce sound levelsand losses in the finished product.To reduce the transfer of noise to thecase, the core is mounted on neoprenerubber vibration dampeners. The coreis electrically grounded by means ofa flexible ground braid.The enclosure has removable panelsfor access to taps and for core and coilinspection. The complete case can beremoved and knocked down to reducesize and weight for rigging into tightlocations.VentilationLouversFan Control/WindingTemperatureIndicatorRemovablePanelFan Motor and BladesCore-CoilAssemblyFor more information, visit: /consultants CA08104001ECA08104001E For more information, visit: /consultantsDecember 2012Sheet14General Description015VPI/VPE Dry-TypeTransformers (Continued)AccessoriesStandard accessories include:■Jacking pads ■Ground pad■Diagrammatic nameplate ■Provisions for rolling ■Ventilation grilles ■Core ground strap■Primary reconnectable taps ■Future fan provisions on units over 500 kVA■Core ground strap ■ANSI 61 paint finish ■Step-lap mitered core ■NEMA 1 enclosureOptional Features■Copper windings/bussing (aluminum is standard)■VPE silicone resin vacuum pressure impregnation and encapsulation ■Fan cooling package, complete with digital winding temperature ■80°C or 115°C rise (150°C rise is standard)■Non-standard ambient temperature (30°C average/24-hour 40°C maximum is standard)■Non-standard altitude (up to 3300 ft (1006m) is standard)■Non-standard BIL level ■NEMA 3R enclosure■Aluminum or copper ground bus ■Lightning arresters■Low loss design (loss evaluation)■Special sound level■Wye-wye connected windings ■UL labelTestsThe following tests are standard:■Induced potential ■Applied potential■Resistance measurement ■Ratio test■Polarity and phase relationship test ■No load loss at rated voltage ■Exciting current at rated voltage ■Impedance and load loss ■Quality control impulseSpecial TestsThe following tests can be provided at additional cost:■Temperature rise ■ANSI impulse ■Sound level ■Witness15 kV 95 kV BIL Aluminum 150˚kVA HeightInches (mm)WidthInches (mm)DepthInches (mm)WeightLbs. (kg)1132253005007501000150020002500300090 (2286)90 (2286)90 (2286)90 (2286)90 (2286)90 (2286)90 (2286)90 (2286)90 (2286)102 (2591)78 (1981)78 (1981)78 (1981)78 (1981)84 (2134)84 (2134)84 (2134)96 (2438)102 (2591)108 (2743)60 (1524)60 (1524)60 (1524)60 (1524)60 (1524)66 (1676)66 (1676)66 (1676)66 (1676)66 (1676)2250 (1022)2850 (1294)3200 (1453)4350 (1975)5450 (2474)6250 (2838)8150 (3700)9350 (4245)11,050 (5017)14,750 (6697)Standard Enclosure Design Dimension & WeightsANSI/IEEE Loading Guide15 kV 95 kV BIL Copper 80˚kVA HeightInches (mm)WidthInches (mm)Depth Inches (mm)WeightLbs. (kg)1132253005007501000150020002500300090 (2286)90 (2286)90 (2286)90 (2286)90 (2286)90 (2286)102 (2591)102 (2591)112 (2845)112 (2845)78 (1981)90 (2286)90 (2286)96 (2438)102 (2591)102 (2591)108 (2743)114 (2896)126 (3200)144 (3658)60 (1524)60 (1524)60 (1524)66 (1676)66 (1676)66 (1676)66 (1676)66 (1676)2950 (1339)4250 (1930)4650 (2111)6350 (2883)8150 (3700)9200 (4177)12,050 (5471)14,850 (6742)18,550 (8422)20,850 (9466)66 (1676)66 (1676)Values listed are typical and should not be used for construction purposes.Retrofit design with minimal enclosure width.1/212341.711.451.301.211.15(210)(196)(181)(165)(155)1.561.371.271.191.141.641.421.291.211.14(220)(206)(186)(169)(158)(217)(203)(185)(169)(156)Times Rated kV A 220˚ Insulation System Following and followed by aconstant load ofPeak Load in Hours90%(1)70%(1)50%(1)Daily loads above rating to give normal life expectancy.(1) Maximum Hottest—spot temperature reached during load cycle.Winding Temperature Indicator provided with isolation barrier for added safety.Low voltage bus arrangement to close couple to low voltage switchgear.5The following tests are made on all transformers unless noted as an exception. The numbers shown do not necessarily indicate the sequence in which the tests will be made. All tests will be made in accordance with the latest revision of ANSI C57.12.91 Test Code for Transformers.1. Resistance measurements of allwindings on the rated tap and on the tap extremes on one unit of a given rating on a multiple unit order2. Ratio Tests on the rated voltage connection and all tap connections3. Polarity and Phase-relation Tests4. No-load loss at rated voltage5. Excitation current at rated voltage6. Impedance and load loss at rated current on the rated voltage connection of each unit and on the tap extremes on one unit of a given rating on a multiple unit order7. Applied Potential Tests8. Double Induced Potential Test.Optional tests which are routinely performed: Temperature Tests will be made when a record of a Temperature Test that has been made in accordance with ANSI standardsis not available on a duplicate or essentially duplicate unit.Temperature Test or tests will be made on one unit only of an order covering one or more units of a given rating. Optional Tests:1. Impulse Tests-full andchopped-wave Tests per ANSIand NEMA standards2. Quality Control Impulse Test(100% full wave)3. Audible Sound Level Test4. Induced Partial Discharge5. Temperature Test6. Insulation Power-factor Test7. Switch and Soak Test8. Short Circuit Test9. Seismic Qualification.ABB’s quality assurance begins withcontract negotiations and continuesthrough design, control of purchasedmaterials, manufacturing and test,and is not complete until thetransformer is installed and operatingsuccessfully in the customer’sapplication for many years.VPE transformers have successfully passedANSI Short Circuit Tests.VPE transformers are manufactured in an ISO9001Certified factory.U L®LISTED93DODISTRIBUTIONTRANSFORMERU L®CLISTED93DODISTRIBUTIONTRANSFORMER®N UCLEAR1E CERTIFICATIONIEEE 323—QUALIFIED LIFEIEEE 344—SEISMIC CERTIFICATIONQuality Assurance 6SpecificationsSelf-Cooled Power RatingkVA PrimaryVoltagekVPrimary BILkVSecondaryVoltagekVSecondary BILkV112.5-10,000Up through 35Up to 150Up through 15Up to 75TemperatureRiseC80/115/150˚Standard VPE Features1.Aluminum windings—copper optional2.Step-lap mitered core3.220˚C insulation system-150˚C average temperaturerise4.Vacuum pressure encapsulated silicone varnish5.Four (4) full-capacity taps on HV winding rated2 1/2% 2-FCAN—2-FCBN on units with voltageabove 601 V6.NEMA 1 heavy-gauge ventilated enclosure withremovable panels front and rear7.ANSI 61 gray paint electrostatically applied usingdry powder8.Vibration isolation pads between core and coil andenclosure9.Base equipped with jacking pads and designed forrolling or skidding enclosure in any direction10.Provisions for lifting core and coil assembly11.Diagrammatic aluminum nameplate12.100% QC Impulse Test13. Short Circuit Design Verification Options & Accessories____ UL listing____ CSA certificationNuclear 1E certification:____ IEEE 323—qualified life____ IEEE 344—seismic certification____ NEMA 3R enclosure____ 80˚C or 115˚C average temperature rise____ Copper windings____ Provisions for future fan cooling (FFA)____ Three-phase electronic temperature monitor____ Forced cooling package with three-phase electronic temperature monitor____ Increased basic impulse levels____ Loss optimized designs____ Air-filled terminal chambers____ Special paint colors____ Retrofit designsTemperatureRise BaseRatedkVA150˚CRisekVAFanCooledkVA150˚C100010001333115˚C 80˚C 100010001150135015301800VPE transformers are constructed with 220˚C class insulation and have a maximum temperature rise of 150˚C.When ordered with 115˚C rise, the VPE transformer (if specified) will have a 115% continuous overload capability (153% with fans). AA/FA/FAVPE transformers, when ordered with a 80˚C rise (if specified), will have a 135% continuous overload capability (180% with fans). AA/FA/FA ANSI C57.12.01ANSI C57.12.91ANSI N45.2-1977ULNRC 10CFR50 Appendix BISO 9001NEMA ST20CSA Z 299.3MIL-I-45208AQualified for manufacture of Nuvlear Class 1-E, Safety Related Transformers including IEEE 344 Certification.Temperature Rise Standards and Certifications7kVA 3-PhaseSelf-Cooled Fan-Cooled VentilatedDry Fan-CooledWeatherResistantVentilated208Y/120240Delta 480Y/277480Delta 112 1/2150225300500750100010001500———400667333346876250937512,50010001333133320002666Secondary Voltage2400 Delta 4160Y /24004160 Delta2000250037505000750010,00012,500——937562504687333326662000133313331000667400————————X X X X XXX XX XX X X X X X X X X X ———XX X X X X X X X X X ————Standard Transformer RatingsPrimary Voltage Class 600V through 34.5 kV 150˚C rise 30˚C average ambientAltitude Derating FactorAltitude (FT)VPE (AA)BIL Correction .894.903.912.921.930.939.948.957.966.985.9941.00kVA Correction Forced Air(FA).823.838.853.868.883.898.914.929.944.959.974.9891.00.67.70.72.77.80.83.86.89.92.95.981.00330040005000600070008000900010,00011,00012,00013,00014,00015,000.975.75NOTE: 3.28 FT = 1 MeterEquivalent Two-Winding(kVA)Ventilated (Class AA Rating)Class FA and AFA RatingSelf-CooledkVA 6968670-910-5051-150151-300301-500501-700701-10001001-15001501-20002001-30003001-40004001-50005001-6000757473716668-83335001-66673334-50002001-33331668-20001168-16670-116772717068666564626050454055Ventilated Forced AirCooled 6001-750075Audible Sound LevelsImpedance ChartkVA ANSI Std.ABB 112.5-500501 & Larger *5.75%5.75%5.75%None Specified* For Units with 60 kV Primaries and below.“X” denotes standard or available.NominalSystemVoltage (kV)1.2S112.55.0S1SBILs in common use (kV crest)10203045609511012515020011SS22S111S111118.715.025.034.5NOTES:S = Standard value.1 = Optional higher levels where exposure to overvoltage occurs and improved protective margins are required.2 = Lower levels where protective characteristics of applied surge arresters have been evaluated and found to provide appropriate surge protection.BIL ’s Associated Voltages8。

国际贸易实务双语Chapter 1

Warming-up Exercise Part A English Tex Part B Bilingual Tex

Chapter One Warming-up Exercise

Answer the following questions.

Chapter One Part A English Tex

Packing of Commodity

Types of Packaging Transport Packaging Transport packing is also called shipping packing, outer packing or big packing. It is classified into unit packing and collective packing. Unit packing is the smallest shippable unit of cargo. In unit packing, goods are put in different forms of containers such as cases, cartons, drums, bales, bags, bundles, etc. Collective packing (also group shipping packing) means a certain number of units of cargo are grouped together to form a large collection. In collective packing, goods are put in flexible container, pallet and container. Sales Packaging Sales packaging is also called inner packaging, small packaging, immediate packaging or marketing packaging. It focuses on the design and beauty of the package, aiming at promoting sales. Sales packaging is divided into carrying packaging, easy-open packaging, hang-up packaging, spraying packaging, gift packaging, etc.

packaging

packagingPackaging: The Key to Product SuccessIntroduction:In today's competitive marketplace, packaging plays a significant role in influencing consumer purchase decisions. A well-designed and attractive packaging can make a positive first impression on consumers, ultimately leading to increased sales. This document explores the importance of packaging, its impact on the success of a product, and the key elements to consider when designing packaging.1. The Purpose of Packaging:Packaging serves multiple purposes beyond the protection and transportation of products. It is the first point of physical contact with consumers and acts as a silent salesman by conveying brand values and product information. Some of the key purposes of packaging include:1.1. Protection: Packaging safeguards products by preventing damage during transportation and storage. It helps to maintain product integrity.1.2. Differentiation: Packaging distinguishes a product from its competitors and attracts consumer attention on crowded store shelves.1.3. Communication: Packaging communicates essential information such as product features, benefits, usage instructions, and ingredients. It also conveys brand values and enhances brand recognition.1.4. Convenience: Packaging should be user-friendly, providing convenience in terms of handling, storage, and usage.2. Impact of Packaging on Consumer Behavior:Packaging can significantly influence consumer behavior and purchasing decisions. A well-packaged product can create strong brand recognition, attract attention, and convey value to consumers. Key ways in which packaging impacts consumer behavior include:2.1. Brand Perception: Packaging provides an opportunity to create a positive brand image and shape consumer perceptions. High-quality and visually appealing packaging can help position a product as premium and trustworthy.2.2. Emotional Connections: Packaging design can evoke emotional responses in consumers, leading to a stronger connection with the product. The use of colors, visuals, and typography can elicit specific emotions and create a memorable experience.2.3. Product Visibility: Packaging design must ensure that the product stands out on store shelves, catching the consumer's eye amidst competitors. Clever use of colors, unique shapes, and strategic placement can enhance product visibility.2.4. Informative Content: Consumers rely on packaging to provide crucial information about the product. Clear communication of product features, benefits, and usage instructions can build consumer trust and influence purchase decisions.3. Key Elements of Effective Packaging Design:When designing packaging, several essential elements should be considered to ensure its effectiveness and appeal to the target audience. These elements include:3.1. Target Audience: Understanding the target audience is crucial in determining the packaging design elements that will resonate with and attract them. Factors such as age, gender, lifestyle, and preferences should be considered.3.2. Branding: Packaging must align with the brand's identity and values. Consistency in terms of color schemes, logos, and typography helps to create brand recognition.3.3. Visual Appeal: Eye-catching packaging design should differentiate the product from competitors. The use of colors, graphics, and fonts should be visually appealing and in line with the brand strategy.3.4. Functional Considerations: Packaging should be practical and user-friendly. It should allow easy product access, provide clear usage instructions, and ensure ease of storage and shipping.3.5. Sustainability: As consumers become more environmentally conscious, sustainable packaging options are gaining importance. Using eco-friendly materials and minimizing waste can enhance a brand's reputation and attract environmentally conscious consumers.Conclusion:Packaging is a vital element in the success of a product. It serves various purposes, including protection, differentiation, communication, and convenience. Effective packaging design can significantly impact consumer behavior, creating brand recognition, emotional connections, and influencing purchase decisions. By considering key elements such as the target audience, branding, visual appeal, functionality, and sustainability, businesses can design packaging that captures the attention and loyalty of consumers, leading to increased sales and brand success.。

【实用文档】达能新包装物和新原材料的评估

NEW PACKING AND NEW RAW MATERIAL EVALUATION达能新包装物和新原材料的评估Agreement ProcedureBefore using a new raw material / a new supplier or a raw material agreed but manufactured in a new supplier plant, it’s necessary to test the compatibility of this new material with your water.It’s necessary to check the organic and inorganic migrations in the water., but also the quality (taste and smell) of the water after bottling and storage in the new packing.The procedure and methods are the followingFIRST STEPSend to the Danone R&D Global Packaging Plateform ( F POULAT*) the following samplesPET: 1 Kg of resin5 lots of preforms (all the cavities)OR50 Kg of PET resinPE/PP for closures : 1Kg of resin 100g resin in a glass containerAbout 100 caps , 20 of them to be packed in aluminium to avoid contamination during transportation对于PE/PP料1.取100克树脂(PE或PP料),装入玻璃容器中2.100个盖子,其中20个用铝制包材包装,避免运输途中的污染On the raw material and on the preforms or caps the total and specificmigration will be evaluated.在原料和半成品,成品盖中总的和精确的迁移量/溶出物将被评估Colour Masterbatch or additives for closures :盖子中色母/色粉或添加剂:If solid masterbatch : 20g in a glass container如果是固体色母:取20克用玻璃容器包装20 closures to be packed in aluminium to avoid contamination duringtransportation取20个盖子,用铝制包材包装,避免运输途中的污染For each raw material (HDPE/PP resin and masterbatch the following informations will be enclosed每种原料必须同时付上以下相关信息•raw material reference including supplier name•提供原料的供应商名称•production plant of the raw material•原料的生产工厂•technical data sheet•技术清单(原料的相关技术说明)-The legal status of this raw material (FDA or European food compliance document and local agreement for your qualitydepartment-政府部门的合法批准文件-To be sent to (邮寄地址)•Danone – R&D BeveragesTo Ms F. POULATPLACE DE LA GAREEVIAN 74500FRANCETel 33 (0)4 50 26 82 90SECOND STEP1)Fill the new packing with treated or untreated water( following yourindustrial process)2)Realize the following organoleptic tests after storage• 1 month at 20°C•10 days at 40°C (abuse test)For each time and each temperature compare the organoleptic characteristics against a sample (glass bottle or PET bottle made with raw material agreed) stored in the same conditions.The quotation scale for the organoleptic tests can be the following* 0 no ‘off taste ‘or bad smell* 1 Very light ‘off taste ‘or bad smell* 2 light ‘off taste’ or bad smell* 3 ‘off taste’ or bad smell* 4 no drinkableIf the results after 10 days at 40°C is less than 2 or equal to 2 and after 1 month at 20°C is less than or equal to 1,5 the new packing or the new material is acceptable,THE NEW RAW MATERIAL OR THE NEW PACKING SHALL BE USABLE IF:-RAW MATERIAL OR NEW PACKING IS APPROVED BY THE WTC ( after migration test)-THE RAW MATERIAL IS IN ACCORDANCE WITH THE REGULATION-THE ORGANOLEPTIC RESULTS ARE CONFORMS0O0SCHEME OF NEW RAW MATERIAL EVALUATIONI study by the WTCII study by the department*The new raw material shall be also conforming to the regulation for the food contact。

Packing外贸函电

· 1. Explosives · 2 . Toxic gas · 3 . Flammable Liquids · 4 . Flammable solids · 5.Radioactive Material · 6.Corrosives

moisture · Keep away from heat · Use no hooks · Keep f l a t · Fragile

Warning marks · Dangerous goods · Inflammable · Explosive · Poison

Warning marks

Packing for Sales

·Packing for sales, or inner packing-- artisti attractive, or small packing, will not only protect, but also prettify commodities.

·suspensible packing transparent packing portable packing window packing gift packing

·Cargoes fall into three groups:

(1) Bulk cargoes or cargoes in bulk: like wheat mineral ore, coal, etc.

(2) Nude cargoes: like vehicles, bronze or stee plates or blocks.

shipment as stipulated in your o f f e r . When making marks, please no the

Unit 13 Packing《外贸英语函电》PPT课件

Notes

2.Products that are packed in such a way as to catch the consumer’s eye will help to sell.用那种足以引起消 费者注目的方法加以包装的产品将有助于销售。

意 • to provide information

about 提供信息 • to provide convenience 提

供方便 • to come to realize 开始认

识到

• undergo v.经受 • rough handling 野蛮装卸 • give attention to 注意 • in a cking is an art.” “Packing or container is part of the product.” “Packing should help identify the product inside.”“包装是一门艺术。”“包装或容器 是产品的一部分。”“包装应该有助于识别里面的商品。”

Text B

(A) Dear Sirs,

Re:Trip Scissors In reply to your letter of August 10 inquiring about the packing of the captioned goods,we wish to state as below. Our exported Trip Scissors are packed in boxes of one dozen each, 100 boxes to a carton.The dimensions are 17 cm high,30 cm wide and 50 cm long with a volume of about 0.026 cubic meter.The gross weight is 23.5 kg.,the net weight being 22.5 kg..As to shipping marks outside the carton,in addition to the gross,net and tare weights,the wording “MADE IN CHINA” is also stenciled on the package.Should you have any special preference in this respect, please let us know and we will meet you to the best of our ability. Taking this opportunity,we would like to inform you that we used to pack our scissors in wooden cases but after several trial shipments in carton packing,we found our cartons just as seaworthy as wooden cases.Besides,cartons are less expensive,lighter to carry and cost lower freight.So nowadays more and more clients are preferring carton packing to wooden case packing.We trust that you will agree to our opinion and accept our carton packing. We thank you in advance for your early reply.

Basic Electronics-- Integrated circuits

Brewer, J.E., Zargham, M.R., Tragoudas, S., Tewksbury, S. “Integrated Circuits”The Electrical Engineering HandbookEd. Richard C. DorfBoca Raton: CRC Press LLC, 2000© 2000 by CRC Press LLC 25Integrated Circuits25.1Integrated Circuit TechnologyTechnology Perspectives •Technology Generations •NationalTechnology Roadmap for Semiconductors25.2Layout, Placement, and Routing What Is Layout?•Floorplanning Techniques •PlacementTechniques •Routing Techniques25.3Application-Specific Integrated Circuits Introduction •Primary Steps of VLSI ASIC Design •Increasing Impact of Interconnection Delays on Design •General Transistor-Level Design of CMOS Circuits •ASIC Technologies •Interconnection Performance Modeling •Clock Distribution •Power Distribution •Analog and Mixed-Signal ASICs Joe E. BrewerIntegrated circuit (IC) technology, the cornerstone of the modern electronics industry, is subject to rapid change.Electronic engineers, especially those engaged in research and development, can benefit from an understanding of the structure and pattern of growth of the technology.Technology PerspectiveA solid state IC is a group of interconnected circuit elements formed on or within a continuous substrate.While an integrated circuit may be based on many different material systems, silicon is by far the dominant material. More than 98% of contemporary electronic devices are based on silicon technology. On the order of 85% of silicon ICs are complementary metal oxide semiconductor (CMOS) devices.From an economic standpoint the most important metric for an IC is the “level of functional integration.”Since the invention of the IC by Jack Kilby in 1958, the level of integration has steadily increased. The pleasant result is that cost and physical size per function reduce continuously, and we enjoy a flow of new, affordable information processing products that pervade all aspects of our day-to-day lives. The historical rate of increase is a doubling of functional content per chip every 18 months.For engineers who work with products that use semiconductor devices, the challenge is to anticipate and make use of these enhanced capabilities in a timely manner. It is not an overstatement to say that survival in the marketplace depends on rapid “design-in” and deployment.For engineers who work in the semiconductor industry, or in its myriad of supporting industries, the challenge is to maintain this relentless growth. The entire industry is marching to a drumbeat. The cost of technology development and the investment in plant and equipment have risen to billions of dollars. Companies that lag behind face a serious loss of market share and, possibly, dire economic consequences.Joe E. BrewerNorthrop Grumman Corporation Medhi R. Zargham andSpyros TragoudasSouthern Illinois University Stuart Tewksbury West Virginia University© 2000 by CRC Press LLCTechnology GenerationsThe concept of a technology generation emerged from analysis of historical records, was clearly defined by Gordon Moore in the 1960s, and codified as Moore’s law. The current version of the law is that succeeding generations will support a four times increase in circuit complexity, and that new generations emerge at approximately 3-year intervals. The associated observations are that linear dimensions of device features change by a factor of 0.7, and the economically viable die size grows by a factor of 1.6.Minimum feature size stated in microns (micrometers) is the term used most frequently to label a technology generation. “Feature” refers to a geometric object in the mask set such as a linewidth or a gate length. The “minimum feature” is the smallest dimension that can be reliably used to form the entity.Figure 25.1 displays the technology evolution sequence. In the diagram succeeding generations are numbered using the current generation as the “0” reference. Because this material was written in 1996, the “0” generation is the 0.35 m m minimum feature size technology that began volume production in 1995.An individual device generation has been observed to have a reasonably well-defined life cycle which covers about 17 years. The first year of volume manufacture is the reference point for a generation, but its lifetime actually extends further in both directions. As shown in Fig. 25.2, one can think of the stages of maturity as ranging over a linear scale which measures years to production in both the plus and minus directions. The 17-year life cycle of a single generation, with new generations being introduced at 3-year intervals, means that at any given time up to six generations are being worked on. This tends to blur the significance of research news and company announcements unless the reader is sensitive to the technology overlap in time.To visualize this situation, consider Fig. 25.3. The top row lists calendar years. The second row shows how the life cycle of the 0.35 m m generation relates to the calendar. The third row shows the life cycle of the 0.25 m m generation vs. the calendar. Looking down any column corresponding to a specific calendar year, one can see which generations are active and identify their respective life cycle year.FIGURE 25.1Semiconductor technology generation time sequence.FIGURE 25.2Life cycle of a semiconductor technology generation.FIGURE 25.3Time overlap of semiconductor technology generations.One should not interpret the 17-year life cycle as meaning that no work is being performed that is relevant to a generation before the 17-year period begins. For example, many organizations are conducting experiments directed at transistors with gate lengths smaller than 0.1 m m. This author’s interpretation is that when basic research efforts have explored technology boundary conditions, the conditions are ripe for a specific generation to begin to coalesce as a unique entity. When a body of research begins to seek compatible materials and processes to enable design and production at the target feature size, the generation life cycle begins. This is a rather diffused activity at first, and it becomes more focused as the cycle proceeds.National Technology Roadmap for SemiconductorsThe National Technology Roadmap for Semiconductors (NTRS) is an almost 200-page volume distributed by the Semiconductor Industry Association (SIA). Focused on mainstream leading edge technology, the roadmap provides a common vision for the industry. It enables a degree of cooperative precompetitive research and development among the fiercely competitive semiconductor device manufacturers. It is a dynamic document which will be revised and reissued to reflect learning on an as-needed basis.The NTRS is compiled by engineers and scientists from all sectors of the U.S. IC technology base. Industry, academia, and government organizations participate in its formulation. Key leaders are the Semiconductor Research Corporation (SRC) and SEMATECH industry consortia. The roadmap effort is directed by the Roadmap Coordinating Group (RCG) of the SIA.The starting assumption of the NTRS is that Moore’s law will continue to describe the growth of the technology. The overall roadmap comprises many individual roadmaps which address defined critical areas of semiconductor research, development, engineering, and manufacturing. In each area, needs and potential solutions for each technology generation are reviewed. Of course, this process is more definitive for the early generations because knowledge is more complete and the range of alternatives is restricted.The NTRS document provides a convenient summary table which presents some of the salient characteristics of the six technology generations ranging from 1995 to 2010. That summary is reproduced (with minor variations in format) as Table 25.1.Year of First DRAM Shipment/Minimum Feature (m m)MemoryBits/chip (DRAM/Flash) 64M 256M 1G 4G 16G 64G Cost/bit @ volume (millicents) 0.017 0.007 0.003 0.001 0.0005 0.0002 Logic (high-volume microprocessor)Logic transistors/cm2 (packed) 4M 7M 13M 25M 50M 90M Bits/cm2 (cache SRAM) 2M 6M 20M 50M 100M 300M Cost/transistor @ volume (millicents) 1 0.5 0.2 0.1 0.05 0.02 Logic (low-volume ASIC)Transistors/cm2 (auto layout) 2M 4M 7M 12M 25M 40M Non-recurring engineering 0.3 0.1 0.05 0.03 0.02 0.01 Cost/transistor (millicents)Number of chip I/OsChip to package (pads) high performance 900 1350 2000 2600 3600 4800 Number of package pins/ballsMicroprocessor/controller 512 512 512 512 800 1024 ASIC (high performance) 750 1100 1700 2200 3000 4000 Package cost (cents/pin) 1.4 1.3 1.1 1.0 0.9 0.8Chip frequency (MHz)On-chip clock, cost performance 150 200 300 400 500 625 On-chip clock, high performance 300 450 600 800 1000 1100 Chip-to-board speed, high performance 150 200 250 300 375 475 Chip size (mm2)DRAM 190 280 420 640 960 1400 Microprocessor 250 300 360 430 520 620© 2000 by CRC Press LLCMax number wiring levels (logic)On-chip4–555–666–77–8 Electrical defect density (d/m2)24016014012010025 Minimum mask count182020222224 Cycle time days (theoretical)91010111112 Maximum substrate diameter (mm)Bulk or epitaxial or SOI wafer200200300300400400 Power supply voltage (V)Desktop 3.3 2.5 1.8 1.5 1.20.9 Battery 2.5 1.8–2.50.9–1.80.90.90.9 Maximum powerHigh performance with heatsink (W)80100120140160180 Logic without heatsink (W)5710101010 Battery (W) 2.5 2.5 3.0 3.5 4.0 4.5 Design and testVolume tester cost/pin ($K) 3.3 1.7 1.30.70.50.4 Number of test vectors (m P/M)16–3216–3216–328–164–84% IC function with BIST/DFT254050709090+Related Topics1.1 Resistors•23.1 ProcessesFurther InformationThe NTRS is available from the SIA, 181 Metro Drive, Suite 450, San Jose, CA 95110, telephone 408-436-6600, fax 408-436-6646. The document can also be accessed via the SEMATECH home page at <>. Information concerning the IC life cycle can be found in Larrabee, G. B. and Chatterjee, P. “DRAM Manu-facturing in the 90’s — Part 1: The History Lesson” and “Part 2: The Roadmap,” Semiconductor International, pp. 84–92, May 1991.Mehdi R. Zargham and Spyros TragoudasVery large scale integrated (VLSI) electronics presents a challenge, not only to those involved in the development of fabrication technology, but also to computer scientists, computer engineers, and electrical engineers. The ways in which digital systems are structured, the procedures used to design them, the trade-offs between hardware and software, and the design of computational algorithms will all be greatly affected by the coming changes in integrated electronics.A VLSI chip can today contain millions of transistors and is expected to contain more than 100 million transistors in the year 2000. One of the main factors contributing to this increase is the effort that has been invested in the development of computer-aided design (CAD) systems for VLSI design. The VLSI CAD systems are able to simplify the design process by hiding the low-level circuit theory and device physics details from the designer, and allowing him or her to concentrate on the functionality of the design and on ways of optimizing it.A VLSI CAD system supports descriptions of hardware at many levels of abstraction, such as system, subsystem, register, gate, circuit, and layout levels. It allows designers to design a hardware device at an abstract level and progressively work down to the layout level. A layout is a complete geometric representation (a set of rectangles) from which the latest fabrication technologies directly produce reliable, working chips. A VLSI © 2000 by CRC Press LLC© 2000 by CRC Press LLC CAD system also supports verification, synthesis, and testing of the design. Using a CAD system, the designer can make sure that all of the parts work before actually implementing the design.A variety of VLSI CAD systems are commercially available that perform all or some of the levels of abstraction of design. Most of these systems support a layout editor for designing a circuit layout . A layout-editor is software that provides commands for drawing lines and boxes, copying objects, moving objects, erasing unwanted objects, and so on. The output of such an editor is a design file that describes the layout. Usually, the design file is represented in a standard format, called Caltech Intermediate Form (CIF), which is accepted by the fabrication industry.What Is Layout?For a specific circuit, a layout specifies the position and dimension of the different layers of materials as they would be laid on the silicon wafer. However, the layout description is only a symbolic representation, which simplifies the description of the actual fabrication process. For example, the layout representation does not explicitly indicate the thickness of the layers, thickness of oxide coating, amount of ionization in the transistors channels, etc., but these factors are implicitly understood in the fabrication process. Some of the main layers used in any layout description are n -diffusion, p -diffusion, poly, metal-1, and metal-2. Each of these layers is represented by a polygon of a particular color or pattern. As an example, Fig. 25.4 presents a specific pattern for each layer that will be used through the rest of this section.As is shown in Fig. 25.5, an n -diffusion layer crossing a poly layer implies an nMOS transistor, and a p -diffusion crossing poly implies a pMOS transistor.Note that the widths of diffusion and poly are represented with a scalable parameter called lambda. These measurements, referred to as design rules, are introduced to prevent errors on the chip, such as preventing thin lines from opening (disconnecting) and short circuiting.FIGURE 25.4Different layers.FIGURE 25.5Layout and fabrication of MOS transistors.© 2000 by CRC Press LLCImplementing the design rules based on lambda makes the design process independent of the fabrication process. This allows the design to be rescaled as the fabrication process improves.Metal layers are used as wires for connections between the components. This is because metal has the lowest propagation delay compared to the other layers. However, sometimes a poly layer is also used for short wires in order to reduce the complexity of the wire routing. Any wire can cross another wire without getting electrically affected as long as they are in different layers. Two different layers can be electrically connected together using contacts. The fabrication process of the contacts depends on types of the layers that are to be connected.Therefore, a layout editor supports different types of contacts by using different patterns.From the circuit layout, the actual chip is fabricated. Based on the layers in the layout, various layers of materials, one on top of the others, are laid down on a silicon wafer. Typically, the processing of laying down each of these materials involves several steps, such as masking, oxide coating, lithography and etching [Mead and Conway, 1980]. For example, as shown in Fig. 25.6(a), for fabricating an nMOS transistor, first two masks,one for poly and one for n -diffusion, are obtained from the circuit layout. Next, the n -diffusion mask is used to create a layer of silicon oxide on the wafer [see Fig. 25.6(b)]. The wafer will be covered with a thin layer of oxide in places where the transistors are supposed to be placed as opposed to a thick layer in other places. The poly mask is used to place a layer of polysilicon on top of the oxide layer to define the gate terminals of the transistor [see Fig. 25.6(c)]. Finally, the n -diffusion regions are made to form the source and drain terminals of the transistor [see Fig. 25.6(d)].To better illustrate the concept of layout design, the design of an inverter in the CMOS technology is shown in Fig. 25.7. An inverter produces an output voltage that is the logical inverse of its input. Considering the circuit diagram of Fig. 25.7(a), when the input is 1, the lower nMOS is on, but the upper pMOS is off. Thus, the output becomes 0 by becoming connected to the ground through the nMOS. On the other hand, if the input is 0, the pMOS is on and the nMOS is off, so the output must find a charge-up path through the pMOS to the supply and therefore becomes 1. Figure 25.7(b) represents a layout for such an inverter. As can be seen from this figure,the problem of a layout design is essentially reduced to drawing and painting a set of polygons. Layout editors provide commands for drawing such polygons. The commands are usually entered at the keyboard or with a mouse and, in some menu-driven packages, can be selected as options from a pull-down menu.FIGURE 25.6Fabrication steps for an nMOS transistor.© 2000 by CRC Press LLCIn addition to the drawing commands, often a layout system provides tools for minimizing the overall area of the layout (i.e., size of the chip). Today a VLSI chip consists of a lot of individual cells, with each one laid out separately. A cell can be an inverter, a NAND gate, a multiplier, a memory unit, etc. The designer can make the layout of a cell and then store it in a file called the cell library. Later, each time the designer wants to design a circuit that requires the stored cell, he or she simply copies the layout from the cell library. A layout may consist of many cells. Most of the layout systems provide routines, called floorplanning, placement and routing routines, for placing the cells and then interconnecting them with wires in such a way that minimizes the layout area. As an example, Fig. 25.8 presents the placement of three cells. The area between the cells is used for routing. The entire routing surface is divided into a set of rectangular routing areas called channels. The sides of each channel consist of a set of terminals. A wire that connects the terminals with the same ID is called a net. The router finds a location for the wire segments of each net within the channel. The following sections classify various types of placement and routing techniques and provide an overview of the main steps of some of these techniques.Floorplanning TechniquesThe floorplanning problem in Computer Aided Design of Integrated Circuits is similar to that in Architecture and the goal is to find a location for each cell based on proximity (layout adjacency) criteria to other cells. We FIGURE 25.7An inverter.FIGURE 25.8Placement and routing.,© 2000 by CRC Press LLCconsider rectangular floorplans whose boundaries are rectangles. It is desirable to obtain a floorplan that minimizes the overall area of the layout.An important goal in floorplanning is the cell sizing problem where the goal is to determine the dimensions of variable cells whose area is invariant. All cells are assumed to be rectangular, and in the cell sizing problem the goal is to determine the width and height of each cell subject to predetermined upper and lower bounds on their ratio, and to their product being equal to its area, so that the final floorplan has optimal area.One of the early approaches in floorplanning is the hierarchical, where recursive bipartition or partition into more than two parts is recursively employed and a floorplan tree is constructed. The tree simply reflects the hierarchical construction of the floorplan. Figure 25.9 shows a hierarchical floorplan and its associated tree.The partitioning problem and related algorithms are discussed extensively later in this section.Many early hierarchical floorplanning tools insist that the floorplan be sliceable. A sliceable floorplan is recursively defined as follows: (a) a cell or (b) a floorplan that can be bipartitioned into two sliceable floorplans with either a horizontal or vertical line. Figure 25.10 shows a sliceable floorplan whose tree is binary.Many tools that produce sliceable floorplans are still in use because of theirsimplicity. In particular, many problems arising in sliceable floorplanning are solv-able optimally in polynomial time [Sarrafzadeh and Wong, 1996]. Unfortunately,sliceable floorplans are rarely optimal (in terms of their area), and they often resultin layouts with very difficult routing phases. (Routing is discussed later in thissection.) Figure 25.11 shows a compact floorplan that is not sliceable.Hierarchical tools that produce nonsliceable floorplans have also been proposed[Sarrafzadeh and Wong, 1996]. The major problem in the development of suchtools is that we are often facing problems that are intractable and thus we have to rely on heuristics in order to obtain fast solutions. For example, the cell sizing problem can be tackled optimally in sliceable floorplans [Otten, 1983 and Stock-meyer, 1983] but the problem is intractable for general nonsliceable floorplans.A second approach to floorplanning is the rectangular dual graph. The idea here is to use duality arguments and express the cell adjacency constraints in terms of a graph, and then use an algorithm to translate the graph into a rectangular floorplan. A rectangular dual graph of a rectangular floorplan is a planar graph G = (V ,E),where V is the set of cells and E is the set of edges, and an edge (C 1,C 2) is in E if and only if cells C 1 and C 2are adjacent in the floorplan. See Fig. 25.12 for a rectangular floorplan and its rectangular dual graph G.FIGURE 25.9 A hierarchical floorplan and its associated tree. The root node has degree 5. The internal node labeled with |indicates a vertical slicing. The internal node labeled with — indicates a horizontal slicing.FIGURE 25.10A sliceable floorplan and its associated binary tree.FIGURE 25.11 A com-pact layout that is notsliceable.© 2000 by CRC Press LLC Let us assume that the floorplan does not contain cross junctions. Figure 25.13 shows a cross junction. This restriction does not significantly increase the area of a floorplan because, as Fig. 25.13 shows, a cross junction can be replaced by two T-junctions by simply adding a short edge e.It has been shown that in the absence of cross junctions the dual graph is planar triangulated (PT), and every T-junction corresponds to a triangulated face of the dual PT graph. Unfortunately, not all PT graphs have a rectangular floorplan. For example, in the graph of Fig. 25.14 we cannot satisfy the adjacency require-ments of edges (a,b), (b,c) and (c,a) at the same time. Note that the later edges form a cycle of length three that is not a face. It has been shown that a PT graph has a rectangular floorplan if and only if it does not contain such cycles of length three. Moreover, a linear time algorithm to obtain such a floorplan has been presented [Sarrafzadeh and Wong, 1996]. The rectangular dual graph approach is a new method for floorplan-ning, and many floorplanning problems, such as the sizing problem, have not been tackled yet.Rectangular floorplans can be obtained using simulated annealing and genetic algorithms. Both techniques are used to solve general optimization problems for which the solution space is not well understood. The approaches are easy to implement, but the algorithms have many parameters which require empirical adjust-ments, and the results are usually unpredictable.A final approach to floorplanning, which unfortunately requires substantial computational resources and results to an intractable problem, is to formulate the problem as a mixed-integer linear programming (LP).Consider the following definitions:W i ,H i ,R i : width, height and area of cell C iX i ,Y i : coordinates of lower left corner of cell C iX,Y : the width and height of the final floorplanA i ,B i : lower and upper bound for the ratio W i /H i of cellC iP ij , Q ij : variables that take 0/1 values for each pair of cells C i and C jThe goal is to find X i ,Y i ,W i , and H i for each cell so that all constraints are satisfied and XY is minimized.The latter is a nonlinear constraint. However, we can fix the width W and minimize the height of the floorplan as follows:FIGURE 25.12 A rectangular floorplan and its associated dual planer graph.FIGURE 25.13 A cross junction can be replaced by 2 T-junctions.FIGURE 25.14For a cycle of size 3 that is not a face we cannot satisfy all constraints.min YX i + W i £ WY ³ Y i + H iThe complete mixed-integer LP formulation is [Sutanthavibul et al., 1991]:min YX i ,Y i ,W i ³ 0P ij ,Q ij = 0 or 1X i + W i £ WY ³ Y i + H iX i + W i £ X j + W(P ij + Q ij )X j + W j £ X i + W(1-P ij + Q ij )Y i + H i £ Y j + H(1 + P ij -Q ij )Y j + H j £ Y i + H(2-P ij -Q ij )When H i appears in the above equations, it must be replaced (using first-order approximation techniques)by H i = D i W i + E i where D i and E i are defined below:W min = W max = H min = H max = D i = (H max – H min )/(W min – W max )E i = H max – D i W minThe unknown variables are X i , Y i , W i , P ij , and Q ij . All other variables are known. The equations can then befed into an LP solver to find a minimum cost solution for the unknowns.Placement TechniquesPlacement is a restricted version of floorplanning where all cells have fixed dimension. The objective of aplacement routine is to determine an optimal position on the chip for a set of cells in a way that the totaloccupied area and total estimated length of connections are minimized. Given that the main cause of delay ina chip is the length of the connections, providing shorter connections becomes an important objective in placinga set of cells. The placement should be such that no cells overlap and enough space is left to complete all theconnections.All exact methods known for determining an optimal solution require a computing effort that increasesexponentially with number of cells. To overcome this problem, many heuristics have been proposed [Preas andLorenzetti, 1988]. There are basically three strategies of heuristics for solving the placement problem, namely,constructive, partitioning, and iterative methods. Constructive methods create placement in an incrementalmanner where a complete placement is only available when the method terminates. They often start by placinga seed (a seed can be a single cell or a group of cells) on the chip and then continuously placing other cellsbased on some heuristics such as size of cells, connectivity between the cells, design condition for connectionlengths, or size of chip. This process continues until all the cells are placed on the chip. Partitioning methodsdivide the cells into two or more partitions so that the number of connections that cross the partition boundariesR i A iR i B iR i B i¤R i A i¤is minimized. The process of dividing is continued until the number of cells per partition becomes less than a certain small number. Iterative methods seek to improve an initial placement by repeatedly modifying it. Improvement might be made by transforming one cell to a new position or switching positions of two or more cells. After a change is made to the current placement configuration based on some cost function, a decision is made to see whether to accept the new configuration. This process continues until an optimal (in most cases a near optimal) solution is obtained. Often the constructive methods are used to create initial placement on which an iterative method subsequently improves.Constructive MethodIn most of the constructive methods, at each step an unplaced cell is selected and then located in the proper area. There are different strategies for selecting a cell from the collection of unplaced cells [Wimer and Koren, 1988]. One strategy is to select the cell that is most strongly connected to already placed cells. For each unplaced cell, we find the total of its connections to all of the already placed cells. Then we select the unplaced cell that has the maximum number of connections. As an example consider the cells in Fig. 25.15. Assume that cells c1 and c2 are already placed on the chip. In Fig. 25.16 we see that cell c5 has been selected as the next cell to be placed. This is because cell c5 has the largest number of connections (i.e., three) to cells c1 and c2.FIGURE 25.15 Initial configuration.FIGURE 25.16 Selection based on the number of connections.。

外贸英语包装packing有关实用词组

1.sale or inner packing 内包装2.the transportation packing or outer packing外包装3.With reference to the packing of our order No.168 for...关于我方第168号有关……货物的包装问题……4. packing method of... 。

的包装方式5.packing arrangement 包装安排6. to your convenience and satisfaction 让你们感到方便和满意7. We look forward to your early reply. 期盼尽早回复8. Please tell us whether the packing requirements could be met.请告诉我们此包装要求能否达到要求?9. ready to accept 打算接受10. We feel regretful to inform you that... 遗憾地告诉贵方……11. meet your request of the special packing material.满足贵方对使用这种特殊包装材料的要求?12. prefer A to B. 宁愿选择A,而不是B13. your confirmation on the issue of packing贵方对包装事宜的确认15. in FCL (Full Container Load) container 用整集装箱装运16.waterproof and airtight 防水且不漏气的17. seaworthy export packing 适于海运的出口包装18. inner/sales packing 内包装19. outer/transportation packing 外包装20. green packing 绿色/环保包装21. shipping mark 运输标志22. indicative mark 指示性标志23. warning mark 警告性标志24. strong enough 足够坚固25. solid and durable 坚固耐用26. suited to the climate/transportation modes 适合气候条件/运输方式27. number of packages 件数28. package number 件号29. pack sth. in... 某商品用……容器来装30. pack... to... 把……装入……31. pack sth. to... and... to... 把某商品装入……容器,再把若干个此种容器装入……32. pack each... in... and... to... 每件……商品用……包装,若干件该商品装入……容器33. Please mark the case with... 请在箱子上刷上……的标记?34. withstand rough handling 经得起粗暴装卸35. strong enough to withstand rough handling 足够牢固,能禁得起野蛮装卸36. be lined with 内衬。

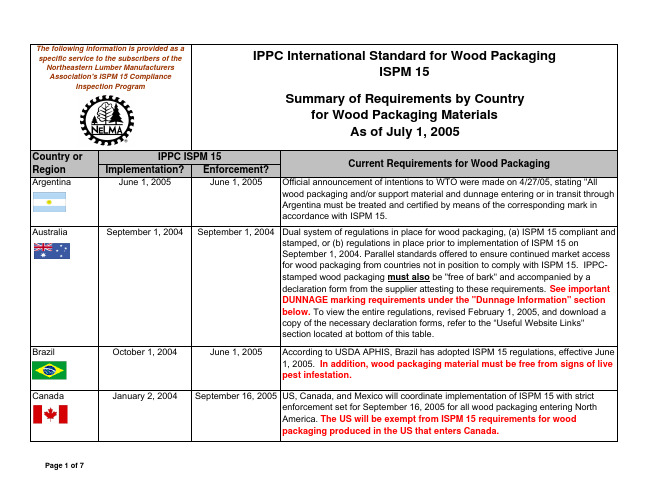

Clearance of ISPM 15 compliant wood packing and …

Compliance Agreement Notice – 2004/13I n t e r n a t i o n a l S t a n d a r d f o r P h y t o s a n i t a r yM e a s u r e s(I S P M)#15Australian Implementation of the International Standard for Phytosanitary Measures (ISPM) # 15: Guidelines for Regulating Wood Packaging Material in International Trade (ISPM 15)On 1 September 2004, Australia will implement the new international standard for solid wood packing1 and dunnage - the International Standard for Phytosanitary Measures (ISPM) # 15: Guidelines for Regulating Wood Packaging Material in International Trade (ISPM 15).This notice is to provide information about facilitated clearance procedures for containerised solid wood packing compliant with ISPM 15.C H A N G E S I N E F F E C T F R O M1S E P T E M B E R2004From 1 September 2004, AQIS will accept solid timber packing and dunnage compliant with ISPM 15 in addition to packing which meets existing AQIS requirements.For AQIS purposes, ISPM 15 treated packing:∙Will not require a treatment certificate (providing that the packing declaration indicates ISPM 15 compliance and freedom from bark).∙Will not need to satisfy the 21 day rule. There is no limitation on time between treatment and shipping (please note this rule is being reviewed for Australia’s existing wood packing import conditions).∙Will be considered acceptable under existing AQIS Compliance Agreement arrangements such as the Containerised Cargo Clearance for FCL/X Scheme.1 Solid wood packing excludes packing made entirely from composite boards, plywood, and medium density fibre board. Please see ICON (.au) for import conditions for these products.P A C K I N G D E C L A R A T I O N SFor AQIS, the packing declaration is an essential quarantine risk management tool as it identifies what has been used as packing within a consignment.The general requirements for packing declarations have not changed; in order for any packing declaration to be acceptable it must contain the following information (as taken from the Containerised Cargo Clearance Manual):∙Letterhead or company stamp∙Date or vessel/voyage reference∙Consignment identifier or numerical ink∙Straw declaration∙Timber declaration and bark declaration where required∙SignatureIn regards to ISPM 15, a packing declaration identifies if ISPM 15 compliant timber packing has been used within a consignment. Attachments 1 and 2 show the revised packing declarations.The revised packing declarations include a new question relating to timber packing. Question 2b asks if all timber packing in the consignment has been marked with ISPM 15 compliant stamps.∙If a yes answer is given, this means that an acceptable treatment has been performed on the timber packing and no further treatment certification isrequired for the timber packing used in the consignment.∙If a no answer is given, consignments must be accompanied either by an acceptable treatment certificate or directed for AQIS inspection (a noresponse means that some or all of the packing is not marked with theISPM15 stamp).The revised packing declaration is only mandatory where timber packing used within a consignment is ISPM 15 compliant.Please note that annual packing declarations will not be accepted for consignments where ISPM 15 compliant timber packing has been used.All other packing is subject to existing AQIS requirements and approved treatments. Further information on these requirements can be found on the AQIS website at .au/cargoqap.For further information regarding ISPM 15 compliant packing, please contact Doug Walsh on 02 6272 4989.C H A N G E S T O T H E C O N T A I N E R I S ED C A R G OC L E A R A N C E M A N U A L–1S E P T E M B E R2004On 1 September 2004, amendments to the Containerised Cargo Clearance Manual will be distributed to industry. Section 4 of the manual defines the requirements for Packing Declarations.The following changes will be made to Section 4:∙Addition of the new question relating to ISPM 15 timber packing under part2.8 Timber Packing Statement∙Amendment of the example packing declaration at the end of the sectionAgain, please note that current clearance procedures for timber packing used within a consignment are still acceptable. The revised packing declarations need only be used by those countries who choose to use ISPM 15 treatments for their timber packing.For further information regarding the changes to the Containerised Cargo Clearance Manual, please contact Rossana Simoncini on 02 6272 4139.Attachment 2。

包装(Packing)常用语句中英文对照

包装(Packing)常用语句中英文对照第一篇:包装(Packing)常用语句中英文对照包装(Packing)常用语句中英文对照We will mark the packages the same as before.我们将在货包上刷上和以前一样的唛头。

Please make an offer indicating the packing.请报价并说明包装情况。

The next thing I'd like to bring up for discussion is packing.下面我想提出包装问题讨论一下。

Packing has a close bearing on sales.包装直接关系到产品的销售。

Packing also effects the reputation of our products.包装也影响产品的声誉。

A packing that catches the eye will help us push the sales.醒目的包装有助于我们推销产品。

Buyers always pay great attention to packing.买方很注意包装的情况。

I'm sure the new packing will give your clients satisfaction.我相信新包装定会使您的客户满意。

Different articles require different packing.不同商品需要不同的包装。

Generally speaking, buyers bear the charges of packing.包装费用一般由买方负担。

Packing charge is about 3% of the total cost of the goods.包装费用占货物总值的百分之三。

Normally, packing charge is included in the contract price.一般地,合同价格中已经包括了包装费用。

IEEE_Spectrum_

/theinstitute

available 5 November

34

40 opiNioN

10 SPECTRAL LINES tech is key to a modern economy, but it’s usually a lousy bet for an investor. By Philip E. Ross

12 FORUM For catching a fibber in the act, a technique called voice stress analysis might be better than functional mrI.

n Engage Students Using Interactive Modeling and Simulation Tools Sponsored by MathWorks http://spectrum.ieee. org/webinar/1686148

n Sponsored white paper: Requirements Engineering for the Automotive Industry Sponsored by IBM http://spectrum.ieee. org/whitepapers

have the most valuable patents in batteries, clean coal, fuel cells, and five other categories. To see where your company ranks, dive deep into our interactive charts, created by the Dutch firm Information Design Studio, and discuss the rankings in our new commenting system.

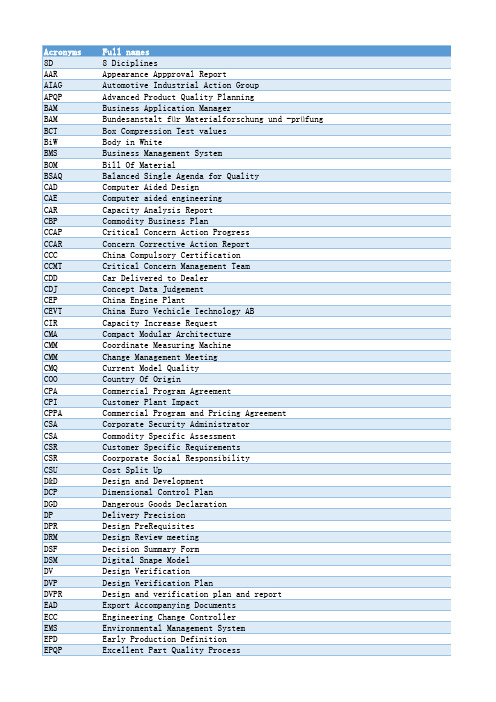

单词缩写 沃尔沃汽车零部件开发项目

SICM SML SOP SP SPA SPC SPFU SPL SQR SREA SRICA SRSA STA TA TCF TE TIE TMS TO TPD TPL TR TS TT UN UP UPL VCCS VCE VCG VCI VCMS VCPA VCT VIR VLD VPDS VQE VRT VSIM VSIM WCR

Emergency Responce Action ElectroStatic Discharge Engineering Sample Evaluation Report Early Supplier Involvement Engineering Statement of Work Engineering Statement Of Work Field Action Board Field Action Stop Shipment Factory Complete Functions Left In Tiko Final Status Report Full Truck Load Global 8 Diciplines Geometry Assurance Engineer Global Dimensioning Tolerancing Geomtry Engineer Global Product Development System Geometry System Utvecklare Global Terms & Conditions Global Terms & Conditions Global Technology Development System Inbound logistics Interim Containment Action ISO Modular Carton International Material Data System Induvidual Moving Range Intellectual Property International Plant Protection Convention International Standard International Standards for Phytosanitary Measures Joined Purchasing Team Knock Down Operations Kontruktions Data Personvagnar Key Performance Indicator Key process Input Variables Key Process Output Variables Lean Deployment Assessment Lean Enterprise Quality Management Logistics Service Provider Ministry of Environmental Protection Materials Management Operations Guideline Logistics Evaluation Multi Party Matrix Milk Run Material Required Date Manufacturing Site Assessment Measurement System Analysis Master Service Agreements Non Disclosure Agreement New Model Launch Normal Weekly Capacity Overall Equipment Effectiveness Operational Management Open To Go Problem Analys

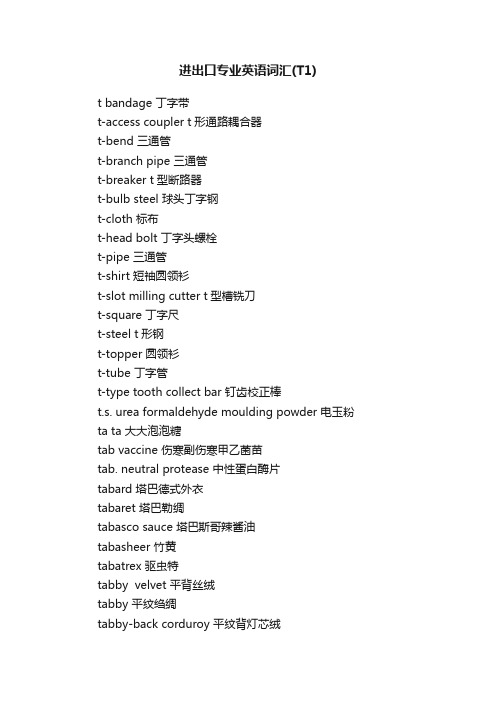

进出口专业英语词汇(T1)