Allegro PCB设计环境介绍

Allegro_Pcb_layout设计流程

• 过孔一般又分为三类:盲孔、埋孔和通孔。

盲孔,指位于印刷线路板的顶层和底层表面,具有一定深

度,用于表层线路和下面的内层线路的连接,孔的深度与孔 径通常不超过一定的比率。

埋孔,指位于印刷线路板内层的连接孔,它不会延伸到线

路板的表面。

盲孔与埋孔两类孔都位于线路板的内层,层压前利用通孔

成型工艺完成,在过孔形成过程中可能还会重叠做好几个内 层。

属连线和通孔的优化布局、电磁保护、热耗 散等各种因素。

Allegro软件

• Allegro PCB软件是美国Cadence公司的 EDA软 件产品,并且大家熟悉的ORCAD也是该公司的产 品。Allegro PCB是全球在High-End PCB Layout系统市场中的领导者。Allegro提供了良好 且交互的工作接口和强大完善的功能,和它前端产 品Capture的结合,为当前高速、高密度、多层的 复杂PCB设计布线提供了最完美解决方案。

• 第一章 Allegro的基本操作

• 控制栏的介绍及注释

• ETCH 导线 • VIA 转换层过孔 • PIN 元件焊接点 • DRC 规则报错

• 鼠标操作指令

在Allegro 系统中,其鼠标三个按键之功能如下:

1. 鼠标左键 – 选取功能 (1) 用来在菜单内选择命令,并执行之。 (2) 用来选取欲动作的对象。

设计软件

• 现在的版图设计需要借助计算机辅助设计 (CAD)实现。以下是业内常用到的软件:

•

Cadence Allegro

•

MentorGraphics PADS

•

MentorGraphics WG,EN

•

Altium designer

•

Zuken CR

AllegroPCB设计

AllegroPCB设计Allegro PCB设计是一款专业的PCB设计软件,它是由Cadence公司开发的。

它提供了完善的PCB设计工具,可以用于各种应用,从单面板到复杂的多层板和高速电路板。

Allegro PCB设计具有许多强大的功能,可以帮助PCB工程师从原型设计到最终生产。

一、基本介绍Allegro PCB设计是一种电路板设计工具。

它可以用于将电路板的原型设计转化为实际的PCB电路板,同时支持各种不同的PCB设计需求。

该软件可以帮助用户轻松地设计电路板,同时还能更好地协作和管理电路板开发流程。

二、主要功能Allegro PCB设计软件拥有许多强大的功能,涵盖了多方面的PCB 设计需求。

下面是几种主要的功能:1. 全局编辑器全局编辑器可以在多个对象之间进行复制和粘贴,可帮助用户快速复制吸纳旋转和移动对象,并应用它们到其它对象和区域。

2. 快速版图编辑速度非常快,支持多层板编辑。

用户可以使用拖放功能将元件从库中拖放到版图图层中。

版图的设置可以通过用户自定义的“属性对话框”实现。

3. 三维可视化Allegro PCB设计软件支持3D可视化,并提供了一种更加直观的方式查看电路板的所有层的信息。

用户可以使用用户界面的本地视图或基于web的3D可视化视图查看其电路板。

4. DFM分析Allegro PCB设计软件还支持平面化、盖层分析、引脚配对和批量编辑等分析功能,以确保电路板可以成功制造。

可以帮助用户检查板设计是否合理,从而避免潜在的生产问题和额外成本。

5. 自动机械CAD转换Allegro PCB设计软件支持自动机械CAD 转换。

可以帮助用户快速生成立体模型和机械图纸,以确保电路板制造符合所需的机械要求。

三、优势与适用范围1. 适用广泛Allegro PCB设计软件可应用于不同规模和类型的电路板,包括单层、双层、多层、高速数字、模拟、射频和混合信号电路板。

2. 高效便利Allegro PCB设计软件极大地提高了电路板设计的效率和便利性。

Allegro PCB设计(二)

五、PCB设计中的规则设置在这节的PCB设计中,规则设置不包括对约束管理器中所进行的规则设置。

在Allegro中,所进行的规则设置包括Spacing Rules和Physical Rules:Spacing Rules 是对元件、网线、引脚、敷铜等之间的间距设定规则;Physical Rules是对线宽、过孔的选择等物理属性设定规则。

选择菜单命令Setup/Constraints或则单击Setup工具栏中的按钮,弹出如图8_38所示对话框。

图中包括3部分的内容:Standard design rules(标准设计规则)、Extended design rules(高级设计规则)、Constraint areas(区域规则设定)。

下面对这3部分进行详细介绍。

8_381、标准设计规则1)设定在线检查规则On-line DRC:设定是否实时检查DRC,On表示在线检查,Off表示关闭此功能,建议选择打开实时检查。

2)标准设计规则检查单击图8_38中的按钮,弹出默认规则设置对话框,如图8_39所示。

8_39在此对话框中,可以设定默认的间距规则如:线到线的最小间距、线到焊盘的最小间距以及焊盘到焊盘的最小间距等。

此处定义的规则是默认的规则,是处于最低优先级的规则设定。

2、高级设计规则——间距规则的设定1)设定间距规则值在图8_38所示的对话框中,单击Spacing rule set中的按钮,打开间距规则设定对话框,如图8_40所示。

在此对话框中,可以对所有走线层(选中ALL ETCH)或单独的一层(选择相应的层)来设定默认的间距规则如:引脚到引脚的最小规则、线到线的最小规则、过孔到过孔之间最小的间距规则。

在此还可以设定相同网名是否执行规则检查(Same Net DRC),其默认值是选择Off表示相同网名不执行规则检查,这里建议大家选择On表示对相同网名同样执行规则检查。

2)添加新的规则对整个印制电路板都使用DEFAULT(默认)的规则有时候不能满足用户的要求,在此可以输入新的规则来使用,以增加一个适合时钟信号的规则CLK为例来介绍添加方法。

Cadence Allegro 中文简易手册说明书

Cadence Allegro简易手册Allegro PCB Layout SystemLab Manual.CHAPTER 1 熟悉环境在开始前请将范例复制到您的工作路径下如:<在安装路径下>\share\pcb\selfstudy\user1 Æ c:\allegroclass\user1启动程序开始Æ程序集ÆCadenceÆPCB systemÆAllegro(电路板工具)开始Æ程序集ÆCadenceÆPCB systemÆPad Designer(焊点编辑)开启旧档选 FILE/OPEN 请开启 C:\AllegroClass\User1\Cds_Routed.brd档如果选了Change Dir 则会将现有路径C:\AllegroClass\User1变成你的内定工作路径认识你的工作窗口有指令区menu bar图标区icon ribbon控制盘control panel工作区design window状态区status window命令区console window.若想自定窗口位置customize 则选View-Customization / Display可设左侧control panel 所放的新位置为浮动式undocked贴左侧Docked_left贴右侧Docked_right(系统值)View / customization / toolbar 则设定控制图标区显示效果项目…显示缩放Zoom by Point Æ显示框选区以左键框二点Zoom fit Æ显示资料全区Zoom in Æ放大比例Zoom out Æ缩小比例Zoom world Æ显示整个工作区Zoom center Æ光标点为下个屏幕中心按Ctrl键配合按着的鼠标右键画w即可Zoom fit.若画Z即可Zoom in画面平移PAN1.利用方向键可平移2.三键鼠标则按中间键即可动态平移.若为二键鼠标则为右键+shift显示项目控制在右侧的控制盘中有visibility 项目来控制显出的对象打勾者代表要显示详细的设定则用指令Setup-color/Visibility而这些对象分成群组 Group级Class次级 Subclass在此可控制图层及各项目的显示与否,我们顺便试一下如何录script1选File-Script指令,键入文件名为colors(勿按Enter键),再点选Record记录2 选Color/Visibility指令,如果要全关选右上角的Global Visibility将值改为All Invisible确定后选套用Apply.这样会关所有显示项目3 选群组中的Components,找到Class里的Ref Des请把它底下的Assembly_top 方框勾选起来表示开启其显示4 选群组中的Geometry把它Board Geometry里的OUTLINE打开, 也把Package Geometry里的Assembly_top 打开5 选群组中的Stack-up,把TOP和BOTTOM的Pin.Via.DRC.Etch打开.而GND及VCC只开DRC.ANTI ETCH如果要设新颜色请在下方色盘Palette中选要用的新颜色,再将它点到要修改项目的色块上就可改过来了6 停止script录制选 File-Script-Stop.先前的层面及颜色设定都会被存在colors.scr中.此colors.scr是一个文字文件,可用一般的文字编辑程序或File-File Viewer加以编辑如果要测试script,请先用All Invisible全关所有显示,再到下方命令列中输入replay colors就会看到程序把先前的设定重跑一次,而显示也回来了标示亮度Highlight将特定对象标示亮度以图形效果显示其特异性如以要找一颗U3的零件为例:1先Zoom in2选标示亮度Display Æ Highlight或其图示3在右侧选高亮度的颜色4选Control panel 中的Find 页面5在Find by name 后net改成symbol (因为是找零件)6点Move键找到U3 (敲入U3 U* 按Tab键)按Apply OK7光标移至右下角全图显示区按右键选Find Next 即可将此对象显示于画面中央控制可被选取对象在编辑对象如:移动复制删除之前须选到所要的对象所以选取对象等的控制会影响后续的动作流程以移动U4的零件及移动U4零件名称RefDes为例1Zoom in到U4附近(在左上角)2选Edit Æ Move指令3选右侧的Find页面4在Find的页面中选全选ALL ON5点 U4的字符串部份你会看到U4会被抓到游标上而你正在移动U4这颗零件(因为symbol有被选取)6选右键中的OOP取消移动U4的动作7在Find页面中选全关ALL OFF 只选Text项目8再选U4字符串部份只有U4字符串被抓起像在调文字面的位置所以跟选择项目很有关系9取消检查数据项利用Display Æ Element 或其图标检查对象内容1先Zoom in2选Display Æ Element或图示3在Find中选ALL ON4随点选对象的不同会显示其相关的资料CHAPTER 2零件的整备本阶段要试建一颗14PIN DIP 零件零件的组成有焊点 PADSACK零件Package symbol每一个接脚PIN及孔Via皆视为一焊点PADSTACK如以60-38为例进入程序开始Æ程序集Æ cadence Æ PCB Systems Æ PAD Designer改种类为贯孔Through单位为mil精确值为1 (小数后1位)焊点在每一铜箔层皆要有一般点regular PAD梅花瓣Thermal-relief PAD挖开点Anti-PAD的三种效果1选Layer 页面2点选Begin Layer3在一般点项目设形状为Circle width为60height为604在梅花瓣设形状为circle值为80Flash项目为TR805在挖开点设形状为circle值为80由于其它层设定相仿可点左侧Bgn按右键copy复制6点internal 的左侧按右键选右键paste即可贴入不须重key in7以同样方法贴到END层8在SOLDERMASK_TOP层的Regular PAD设circle大小为709一样复制到SOLDERMASK_BOTTOM钻孔定义如果定为Through-Hole焊点须定孔径及钻孔符号在Drill Hole 项目中定Plate Type 为Plated (孔壁镀铜)孔径38. Drill symbol的Figure为钻孔符号效果Character为标示字符串Width height为符号的宽及高储存焊点选File Æ Save as 存到 C:\allegroclass \ user1 档名为 60C38d.PAD实体零件的建立建立实体零件的格式不同所以须进入零件建立模式下1File / New 在DRAWING NAME中敲入新零件名如DIP14并在DRAWING TYPE中选PACKAGE SYMBOL2设作图环境选SETUP – DRAWING SIZE在Move Origin项目中的XY各敲入5000使原点调整至适当位置3加入焊点选ADD PIN或其图示并右侧OPTION项目中敲入焊点60S38D后按Tab键状态列会显示出Using ‘ 60S38D.PAD’4光标移至状态列点选后敲入x 0 0会把第一接点放到原点 00的位置上(x须为小写)窗口缩放到PIN1附近5在右侧OPTION中改焊点为60C38D后按Tab键在Y的Qty项目中输入6 6在状态列输x 0 100则会放入向下距100mil的27接点7把Y项目的Qty改7个次序order改up8状态列输入x 300 –600会放入第8PIN到14PIN之焊点但是其脚号仍位于焊点左侧可按右键之OOP取消9将OPTION中的OFFSET值由-100改为100 (表右边100mil处)于状态列输入x 300 -60010完成按右键中的DONE文字面绘制 SILKSCREEN要调整格点大小时请以SETUP /GRIDS将NON-ETCH的X Y值键入25表文字面绘制格点为251选ADD/LINE2将右侧OPTION选为Package Geometry下的SILKSCREEN_TOP设画线角度等3画上文字面的矩形框组装外型绘制Assembly outline (可省略)同文字面之动作但层面为Package Geometry下的Assembly-Top设文字面之零件名称及零件号1选Layout_Label Æ Ref Des或其图示2图面为 refDes下的Assembly_Top3点选放零件名称的好位置(须在Assembly outline中)4键入名称如U* (请先注意右侧的字体基准点角度)5选Layout_Label中Æ Device6选适当的位置后键入 dev type后按右键的DONE绘制零件限制区Package boundary (可省略自动抓)定义零件高度(需要有Package boundary才可定义)1Setup-Area-Package Boundry Height层面为Package Geometry下的Place_Bound_Top2点先前建的Package Boundry 区域3输入高度值如180若没设则以Drawing option下的symbol Height为其内定高度值存零件文件(两者都要存)1选File Æ Create Symbol存成可放到PCB上的.PSM檔2选File Æ SAVE存成供以后修改的图形.DRA檔以自动程序建零件利用Symbol Wizard填入参数自动建零件1、File /New后在Drawing Name键入名称如dip16在Drawing type选PackageSymbol [Wizard] 后选OK2选Package Type为dip后点Next (选零件包装)3套用CADENDCE规划选Default Cadence Supplied template套用其它零件则选Custom template后选.Dra档套入后选Next4设定使用的公英制准确位数及名称前字符串prefix5依不同零件外形设定其参数如脚数Number of Pins脚距LeadPitch行距Terminal row spacing文字面的宽及长Width&Length)6选套用的焊点(一般焊点及第一脚)7定零件原点为中心center of body或第一脚pin1 of symbol及是否另存.PSM檔8选Finish 即OKCHAPTER 3板框绘制板框在Allegro中属于特殊的Mechanical Symbol板框为电路板的外形尺寸,其来源可由手工绘入.,键坐标输入画成.如果有Option 接口的话可由AUTOCAD转入DXF或Pro-Engineer的IDF.键坐标画图框1选File一New,在檔名Drawing Name中敲入如cds_outline.请注意格式务必改成Mechanical Symbol后按OK2设绘图区选Setup一Drawing Size.将图区Size设成A.并把DRAW Extent改设成Left X与Lower Y在设原点偏移量.Width 与Height设工作区大小设工作格点选Setup一Grids.将Non-Etch的格点设为25后按OK画板框选Add一Line.注意层面须改成BOARD GEOMETRY/OUTLINE.请输入x 0 200iy 2300ix 4000iy –2300ix –100iy –200ix –3700iy 200x 0 200 完毕按右键下的Done定工具孔Tooling Hole选指令Add Pin在右侧的Padstack中输入hole109再按Tab键.请在命令列输入x 100 300x 100 2400x 3900 2400 完毕按Done 结束标尺寸Dimension利用Dimension linear指令,层面会自跳到BOARD GEOMETRY下的DIMENSION.点选被测线段就可拖出其尺寸标注线放上.倒角Chamfer如果画的板框有直角要倒角,可用指令Edit一Chamfer.在右侧Options中TrimSegment的First栏设50.表示未倒角的两边线段长为50mil.试着点要倒角的第一段线,再点它的垂直线,就可做出倒角效果来设走线及摆零件区1先Zoom in到图框的左下角,2选Setup一Area一Route Keepin(走线区)在板框内的50mil(二个格点)内画出其布线限制区.(会在ROUTE KEEPIN下的ALL.)3选Setup一Area一Package Keepin(摆零件)画出相同的限制区设禁止摆零件及走线区选Setup一Area一Route Keepout(走线)画上不能走线的范围,其显示为一填满区.试画过后请Edit一Delete删除(在Find中要勾Shape),否则稍后可布线区域可能不够.其它如ViaKeepout则为禁打贯孔区存板框檔1选File一Create Symbol设入档名如cds_outline后选Save会存成cds_outline.bsm的Board Symbol 檔.2再选File一Save存成cds_outline.dra的图形文件.建立环境档Master Design File (.brd)环境档通常是只先放入板框而未含有逻辑数据的作图文件.利用它把大家讨论过认证的Geometry先设好的存在图档上.达到统一作图环境的目的.当成公司内的标准档.1选File一New,在檔名Drawing Name中敲入如cds_master.请注意格式为Layout 后按OK2设绘图区选Setup一Drawing Size.将图区Size设成B.,小数后位数Accuracy设成2.并把DRAW Extent的Left X设成-5000 ,Lower Y设成-5000完成按OK3放入板框零件,选Place一By Symbol一Mechanical,先点Library键才会列出各Mechanical Symbol,选先前建的cds_outline后按OK键准备放到图上4在命令列敲入x 0 0 ,放到图上(0,0)点.完毕按Done加图框Format Symbols如果要加上图框或其它注意事项宣告1Place一By Symbol 一Format, 先点Library键使列出各Format Symbol.如果点选Asizeh.表示要挂上A Size 横向的图框2利用光标把图框放至工作区上(请并确定板框数据含于图框范围内)3按右键选Next选到Note这个Symbol4请放在图框内板框外的适当区域中预放零件如果有特定的零件位置或固定的某几颗零件如connector.switch.等等.可以先摆到板上1选Place一By Symbol一Package.点Library使列出各实体零件.请选其中的conn140后按OK2在命令列输入x 3775 -200后按Done摆到图上设颜色1进到Color/Visibility中设定显示项目或其颜色.如果先前已存有Script 文件请Replay控制图形效果,请在命令列输入 replay colors层数设定Cross SectionAllegro内定的板层为二层板(指二个电气层).您如果是多层板则必须先宣告其层面结构.如层数.材质.用途.Subclass name.正负底片效果等.而其材质的种类及特性定义在<cds ins dir>/share/pcb/text/materials.dat檔中1选Setup一Cross Section点FR-4层名左侧的Edit后选Insert新增,则在原层之上会加入一个新的FR-4层.请总共新加入8层,因为我们待会要宣告此板为六层板,加上五层FR-4介质层及二层原有的空气层全部为13层.2点选第二个FR-4层准备把改设为内层的GND.请点其材质Material项目改设为铜箔Copper,将层面特性Layer Type改选成Plane,而Etch Subclass name取名成GND.最后把其底片效果由念Positive改为Negative表示此层为负片.3最后设定完成如下.表示此板为47.2mil厚的六层板.如果要删层则点选那一层其左侧的Edit键后按右键选删除Delete即可存环境档宣告完毕要存成环境档,请用File-Save As另存新档设入档名为cds_master1.brd 存入.通常Allegro的环境档可统一放在<course inst dir>/allegro/project1/worklib/esdesign/physical路径下CHAPTER 4加载联机关系与设定规范载入联机关系Load the Netlist联机关后档是一个由线路图程序所产生的文字文件netlist目的在交代零件(外型名称)及联机关系(接点及讯号名).要是零件需要作功能互换(gate swap或pin swap)则需另定零件宣告文件device file.如果有同类型但不同名零件可用对应文件map file宣告其对应不需每颗皆定义.以ORCAD为例,再执行完ERC电器检查后.即可执行其Tools-Netlist将线路图档转出联机关系档,其格式请选用others页面里的Allegro.就可把整份图转成一个联机档 .net或.txt零件若是在布线时会做swap的联机交换则须为零件定义其Device file 以宣告其零件之脚数闸数等到时:7400会对应7400.TXT套入宣告如果二者名称不同可以devices.map档宣告其对应性.以下devices.map为例零件7400会对应到74abcd.txt的device檔而非7400.txt如果要零件宣告文件device file,新版的ORCAD 9.x可用指令Accessories-Allergo Netlist自动产生各零件的device file.不需手动以文字编辑程序逐一编写载入联机 Import Logic1. 选File/Import Logic定来源格式Logic Type为Third party.2. 来源档案 Import From 点选后再选Browse键选文字联机文件的3rdparty.txt.3. 是否替换新零件Replace changed component.设Always4. 是否允许拆原有布线Allow etch removed during eco依情况而定5. 设定转联机关系时取代原图上的逻辑数据supersede All logical.6. 要加载联机成为电路板文件选加载Import.设计规范Allegro的设计规范是在定义设计过程中的条件限制,这些条件的设定是用来作为设计时安全检查的标准.例如我们可以定义层数,各层的规范,特殊讯号的限制条件如线宽间距打贯孔数,或特定区域条件等等,以配合电器或机构考量.而且宣告过的规范存在图档上,可避免以后布线时因考量因素众多而疏漏所造成需重修的情况.设定内定设计规则内定设计规则是给图文件中未经特定宣告的任意讯号(一般线)所套用进入Setup-Constraints请点选内定标准值Default Value设定其线到线,线到点,点到点,线宽,套用的贯孔等设定其它的设计规则在一份图档上有些特殊的线有其不同的规则相对于先前定的内定标准值如CLOCK讯号它的间距如为10 mil不同于先前内定的 5 mil.其步骤为定RULE SET请点选SPACING RULE SET下的SET V ALUE.在DELETE后的空白处输入 10 MIL SPACE后点选加入键加入新的RULE SET.随后输入其各间距的值再按OK键确定宣告相关讯号选ATTACH PROPERTY -NET,选右侧的FIND点选下方的FIND BY NAME切换成NET后再输入CLK2.程序跳出其PROPERTY画面请选NET-SPACING-TYPE, 在其V ALUE中输入其组别名称如CLOCK后按APPLY确定讯号套上RULE SET选在SPACING RULE SET中的ASSIGMENT TABLE设定各个RULE SET之间的规范如CLOCK与NO_TYPE指先前订的CLOCK(本例中只有CLK2)与一般讯号NO_TYPE所套用的间距值为10 MIL SPACE设定实体规范在实体规范PHYSICAL RULE SET中选其SET V ALUE键,在DELETE后的空白处输入10 MIL LINE 后点选加入ADD键,建立新的PHYSICAL SET.随后输入其允许最小线宽MIN LINE WIDTH,缩线后最小线宽,最大线宽,是否形走线,套用的贯孔焊点为何等等.,结束按宣告相关讯号选ATTACH PROPERTY-NET,选右侧的FIND点选下方的FIND BY NAME切换成NET后再输入REF.程序跳出其PROPERTY画面请选NET-PHYSICAL_TYPE在其V ALUE中输入其组别名称如ANALOG后按APPLY确定讯号套上RULE SET选在PHYSICAL RULE SET中的ASSIGMENT TABLE套上各个RULE SET的规范如把ANALOG套上先前订的10 MIL LINE,NO_TYPE指一般讯号请套上DEFAULT.第二项为AREA是当有设定特定区域AREA时才有对应的新值可输入STUB LENGTH,允许最多贯孔数MAX VIA等等而AREA则是以特定区域的方式来宣告其特别的设定值如线宽间距等设计规范存盘我们可将前面所设好的规范存成一个技术文件TECH FILE,请选指令FILE-EXPORT-TECHFILE设好文件名再按执行RUN键即可产生下次开新文件时层面只有二层,也没有特殊线宽或间距等设定,这时你可以加载技术档..这样这些设定即不须重设只须要把新讯号重新指定其对应的规则就可了查属性要检查己订属性可用1选EDIT-PROPERTIES配合右侧FIND2 选DISPLAY-PROPERTIES指令后选要查询的值如NET_SPACING_TYPE,再于V ALUE栏输入查询值如 * 表示任意即可查到先前订的CLOCK.在您绘图的过程中Allegro会以先前订的规范持续的检查你的图档当它有违规时则会有DRC的标记在上面.而这个蝴蝶形的标记的两边各有一个英文字母代表它检查的数据种类如L表线段LINE,.V表VIA,P表PAD等等,使我们能很快的知道错误在那儿而侦测到的错误项目又是什么数据间的状况可以马上加以改正.您也可以用SHOW ELEMENT的指令来查看更详细的结果Chaper 5摆放零件在建完零件,传入联机关系,订好规则之后紧接着的就是零件的摆放动作在图示中通常已经挂上了一些有关摆放零件的图标而这些图标就如同指令PLACE下的各个摆放功能请开启位于c:\\allegroclass\user1\ 底下的constrainted.brd手动编名因为置于板上的金手指尚未命名所以我们必须手动的帮它编名请选Logic-Assign RefDes并点选右侧Options下方的RefDes字段中输入J1 点选金手指则会把这颗零件命名为J1设定摆放格点设摆放零件时移动零件的距离请选Setup-Grid下的Non-Etch将其Spacing X:值输入50,Y:值输入50.要不要显示格点则设定左上角的GRID ON以零件名称摆放Placed By RefDes一般摆零件时习惯边看线路图边摆零件,所以我们须将相关的零件逐一叫出这样就会用到此功能请选Place By RefDes指令敲入零件名U5后按OK就可抓出U5到图上准备摆入.如果想要旋转,请按鼠标右键选择Rotate这时零件上就会跑出一根控制杆到光标位置利用鼠标转动即可控制其旋转角度.按左键可停止旋转.移动到要摆的中下图区后按右键选Done放置如果摆上的零件看起来是一个填满的大方块是因为开启了它的限制区.想关闭请至Display-Color/Visibility把Package Geometry/Place_Bound_Top项目勾勾去掉除了此种方法外如果新摆入的零件都须转一个特定角度的话可到Setup-Draw Options选其中的SYMBOL把Angle字段输入或改选成90再点OK键试着抓U7进来摆,你可看到它己是旋转了90度等着您摆入移动零件如果已摆入零件其位置须要挪移请选Edit一Move后再到右侧的Find项中全关只留Symbols.请点选要移动的零件(最好点它的名称字符串)零件就会被抓到光标上,待移到新位置后,点右键按Done即完成移动一群零件同样以Edit一Move指令以鼠标左键框出一个区域,框住要一齐挪移的零件(如果要放弃框选范围可选右键下的Oops).再以左键定其基准点就可一齐移动到时再以右键下的Done确定.再框选时请勿框到 Board Outline,Keepins,keepouts的Board Symbol资料.其它摆放的动作有Place一Component一ICs 摆IC类零件Place一Component一IOs 摆输出入类零件Place一Component一Discrete 摆附属小零件Place一Component一ALL 摆所有零件联机互换的动作有Place一Swap一Component 零件位置互换Place一Swap一Functions 闸联机互换(需有device宣告)Place一Swap一pins 接点联机互换(需有device宣告)联机显示控制联机指点到点间用来表示其电气接续性的表示线.我们会依不同需求开关某些零件或讯号的显示效果来达到评估布线策略的目的显示(关闭)所有联机Display一Show(Blank) Rats一All显示(关闭)单颗零件Display一Show(Blank) Rats一Component显示(关闭)单条联机Display一Show(Blank) Rats一Net产生摆放零件报表您可以产生一份摆放零件报表它可列出图中已摆放及未摆放之零件数据您在摆完零件后可用它来再确认是否有漏网之鱼尚未摆入HAPTER 6 布线布线相关指令设定布线格点随着不同的布线须求.您可为不同层设定不同的布线格点或是设定所谓的不等距格点如8 9 8这样的工作格点.指令为Setup一Grids设定格点,其中左上角的Grids On 为设定是否显示格点.Non-Etch为非电气层格点如摆零件.All Etch为所有电气层之走线格点.Top….为各电气层之走线格点值在布线时我们必须在右侧的Options中设定布线的工作层Act及代换层Alt在走线时首先走在工作层上如果要换层只须连续点二下左键(双击)则您的工作层及代换层会自动互换并打上贯孔试走第一条线1请先关闭所有联机显示,然后选Display一Show Rats一Net按鼠标右键选其中的Net Name输入 clk2使只开此讯号的显示效果2 Zoom in到U15 选择布线图示或Route一Connect将右侧的Options中的Act 层设为Top,Alt层设为IS3,线的角度设45度线宽设5,布线效果RouteType设手动布线Manual.3 试着点线开始布线,一开始走出时是在正面ToP层,如果觉得走得不好请用右键按OoP取消删除布线如果不满意先前所走的布线结果可以用Delete指令予以删除但是请配合右侧Options或Find的选项让使用上更加的便利1.全线删除请选择删除示或指令Edit一Delete在Find下请先选ALL OFF再开Clines请点CLK2的布线,此线会全部高亮请再按右键下的Done就会把它删掉(请救回此线以执行以试作底下其它动作)2.线段删除如果要删掉的只是某些线段非整条布线,请在右侧的下Find关所有项目只留ClineSegs同样点CLK2你会只看到此线段高亮,如果点其它线段则先前的线段即消失被删除了3.二点间线段删除如果要删掉的只是某些线段内的一小段,选Edit一Delete按右键下的Cut,点要删掉线段内的第一点(线段变亮)再点第二点,则剩此区间高亮可删除.布线效果Routing Type在走线的过程中我们有三种效果可以选择,分别是手动布线Manual,循迹布线To Cursor,结点布线To Pick1.手动布线Manual--------在前一光标位置与目前的光标位置间显示出走线’不会自动闪其中的障碍但推线效果明显2.循迹布线To Cursor-----随游标带出布线的走向,可动态的看出将布线的效果,会自动的闪避其中的障碍3.结点布线To Pick--------前后光标点间无法看到动态的布线轨迹,但是会自动闪线且速度比较快走线的过程中按鼠标右键会出现一些选项Done =>布线停止,回到空-状态IdleOops =>取消前线段动作Cancel =>取消前指令Next =>布线暂停,改走其它线Temp Group =>宣告走bus线讯号Complete =>结束bus线讯号选入动作Reject =>放弃现有选取,可改选其它Add Via =>打贯孔Finish =>以同层自动走完未布线段Snap Rat T =>移动讯号T点位置Neck =>窄线布线,须依Physical Rule Set宣告New Target =>改定同讯号的目的点(布线终点)No Target =>尾段讯号不显示Swap Layer =>走线换层(Act层换到Alt层) Toggle =>出线角度切换(先直再斜或先斜再直)打贯孔贯孔是用来导通层到层之间的讯号关系,贯孔必须有焊点的特性在布线的过程若加入贯孔则其工作层与代换层就会自动切换走到对应的布线层面.动作为连续点二下左键(双击)或选右键里的Add Via.移线利用移线指令SLIDE可移动先前所布的线段.你只需要选好指令后用左键点选要移动的线段即可动态的移动此线段,而与此线段相连的线段效果也会自动调整保持整体的完整性1请开启档案CDS_ROUTED.BRD稍为Zoom in到局部区域上.请选图标区上的移线图示或ROUTE一SLIDE2在右侧的Find项目中全清只留Via及Segment3以左键点选线段移动看看,也以左键定其新的落点4可以试着改变调整右边设定如角度CORNER或最大斜线长度Max 45 Len看看它的效果修端点VERTEX要挪动,新增,重迭,删除(选右键下的DELETE VERTEX),请利用EDIT-VERTEX或按F7键.即可修整端点自动整线有Route-Custom Smooth或Route-Gloss可执行SPECCTRA自动布线当您执行ROUTE一SPECCTRA-Auto儿时Allegro会发起SPECCTRA的自动布线程序并建立一个同档名的.dsn檔.在自动布线结束后SPECCTRA会产生一个.ses檔在回到Allegro时转入成已布线档SPECCTRA手动布线执行ROUTE一SPECCTRA-Interactive,可转档到Specctra并以其EditRoute作手动布线产生未布线报表在布线完毕后.我们如果要确定定否有未布线点仍然存在.可以执行TOOLS一Reports选输出的资料为Unconnected pins再点Run键就会产生此报表加以查核CHAPTER 7 内层及铺铜如果您的设计超过二层,那么您就须要设定其内层铜箔的效果包括它的铺铜箔效果,所带的讯号名,避开的间距,内层切割等等的问题通常铜箔分二种,正片铜及负片铜.正片铜显示的是含铜的部分,也就是黑的部分以后就是铜箔.在Allegro中的正片铜您可以看到它所挖开的开孔void 及所接的梅花瓣Thermal 它的缺点是一但铜箔的接续性更改如移零件或贯孔.则铜箔须要重铺以重新连结正确的梅花瓣及挖开不同讯号点负片铜显示的是以后要挖掉铜的部分,反而是白色的部分以后才会有铺铜在Allegro中负片铜只是显示一些点在内层上面.随着所设定的讯号.程序会自动判定那些点该是要改成内层要接的Thermal Relief定义效果,那些不接的点其内层必须是挖开的Anti-Pad定义.Allegro并不会把那些焊点挂在层面上.好处是零件或是贯孔可随意移动不须重铺重算.只有在他产生底片输出时才会将焊点数据并入处理.而它的缺点是您无法在图上即看到真实的底片效果.(尤其是梅花瓣)宣告内层负片铜l.Add一Shape一Solid Fill画内层铺铜范围2.Edit一Change Net(Pick)宣告铜箔的讯号名3.Shape一Fill填铜箔1请开cds_routed.brd檔.设定Setup一Drawing Options在Display项目中勾选Thermal Pads(显示梅花瓣) 及Filled Pads and Cline Endcaps(填满式显示)选项2 选Display一Color/Visibility把Group项目改成Stack再把底下的Etch项全关只留VCC层.其它项的PIN与VIA也是只留VCC后跳出3选Add一Shape一Solid Fill在右侧设Etch及VCC层,在板内的走线区范围内Route Keepin画一个Polygon画完按右键Done结束4宣告内层讯号选Edit一Change Net(Name)在列表中选VCC后跳出5填铜箔.选Shape一Fill这样会灌满并显示出Thermal Pad(单线)及AntiPad的效果宣告内层正片铜l.Add一Shape一Solid Fill画内层铺铜范围2.Edit一Change Net(Pick)宣告铜箔的讯号名3Shape一Parameter设定自动挖开铜箔的效果4V oid一Auto执自动清铜动作(讯号不同者挖开,相同者挖开后架上桥接花辫)5Shape一Fill填满铜箔效果1 选Display一Color/Visibility把Group项目改成Stack再把底下的Etch项全关只留GND层.其它项的PIN与VIA也是只留GND后跳出2选Add一Shape一Solid Fill在右侧设Etch及GND层,在板内的走线区范围内Route Keepin画一个Polygon画完按右键Done结束3宣告内层讯号选Edit一Change Net(Name)在列表中选GND后跳出4选Shape一Parameters设定挖开的项目,间距值,效果等参数5选V oid一Auto在跑了几秒后可看到铜箔该接的变成正片的梅花瓣.不该接的自动避开挖空。

Allegro PCB设计

第八章Allegro PCB设计本章主要讲解如何使用Cadence公司的PCB Editor软件来进行印制电路板(PCB)的设计。

由于前面已经讲述了焊盘以及PCB封装的制作,本章主要讲解如何创建PCB外形框图符号、PCB Editor的使用、PCB设计的规则设置以及PCB设计的布局、布线等几个方面。

对于一个项目的设计,如果把原理图的设计看作设计的前端,那么PCB设计就是这个项目的后端,PCB设计是由原理图设计来约束、决定的,一个项目的PCB设计是从原理图输出到PCB设计环境开始的。

一、PCB Editor软件介绍1、PCB Editor软件的打开在前面的学习过程当中,我们一直是从项目界面中点击“Layout”按钮来启动PCB Editor软件,另一种方法就是直接启动“开始菜单/程序/Allegro SPB 15.5.1/PCB Editor”。

2、Allegro界面Allegro是Cadence公司的PCB设计工具,提供了一个完整、易操作的PCB 设计环境,其用户界面包括、标题栏、菜单栏、工具栏、编辑窗口、控制面板、状态栏、命令栏及视窗栏组成,如图8_1所示。

8_1下面详细介绍一下各栏:1)标题栏标题栏是显示当前打开的界面的位置及所选的模块信息。

2)菜单栏Allegro的菜单栏共由File(文件类)、Edit(编辑类)、View(查看类)、Add (添加类)、Display(显示类)、Setup(设置类)、Shape(敷铜类)、Logic(逻辑类)、Place(布局类)、Route(布线类)、Analyze(分析类)、Manufacture(制造类)、Tools(工具类)以及Help(在线帮助)等14个下拉菜单组成。

(1)File文件类的下拉菜单中的命令主要包括:新建、打开、查看最近的设计及保存文件,输入、输出一些文件信息,查看一些临时文件,打印设置、打印预览、打印、设定文件属性、更改产品模块,录制scr文件及退出命令。

Allegro16.3—PCB设计笔记(详细,实用,图文并茂)介绍

Allegro 16.3 PCB设计笔记看到这篇文章,感觉非常好,分享给大家。

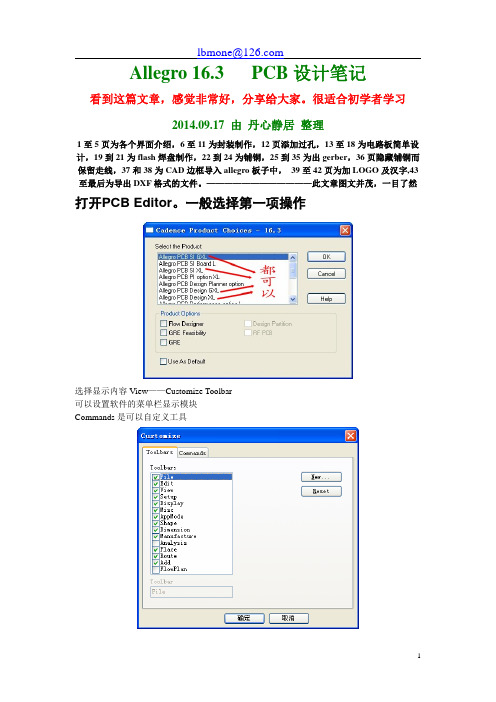

很适合初学者学习2014.09.17 由丹心静居整理1至5页为各个界面介绍,6至11为封装制作,12页添加过孔,13至18为电路板简单设计,19到21为flash焊盘制作,22到24为铺铜,25到35为出gerber,36页隐藏铺铜而保留走线,37和38为CAD边框导入allegro板子中, 39至42页为加LOGO及汉字,43至最后为导出DXF格式的文件。

————————————此文章图文并茂,一目了然打开PCB Editor。

一般选择第一项操作选择显示内容View——Customize Toolbar可以设置软件的菜单栏显示模块Commands是可以自定义工具Display——Color/Visibility封装的制作在Pad Designer中操作此项首先制作贴片式焊盘的做法Candence制作封装需要先制作焊盘打开制作焊盘的软件开始>程序>candence>release 16.3>PCB Editer Utilities>Pad Designer表贴焊盘就不用填写Themal Relief(散热焊盘)和Anti Pad(绝缘层焊盘)了这是建立好的焊盘文件然后打开PCB Editor——File——New——设置图纸大小Setup——Design Parameter Editor——DesignUser Unist(单位)选择 Extents项中Left X和Lower Y为原点的坐标定义,Width和Heigh 为做封装时图纸的大小>Type项不变,仍为Package(封装)。

都改为0.0254(最小步进值)开始加入焊盘>Layout>Pin>>Option中如下设置创建一个零件库必须的几个条件:1至少一个引脚。

2每个零件必须有图形边框,即轮廓线,线路板上丝印层白漆所画的轮廓。

Allegro PCB封装库的设计与规范

这种管理方式的优点是占用的资源比较少,当要批量更新焊盘的时候只要更新PAD库里 的焊盘,再刷新一下电路板就ok,这就是为什么用Allegro打开PCB会比用Protel快的原因,资 源是一点点省下来的。

1 Allegro封装库基本介绍

与Protel封装的区别

Allegro 封装库的 PAD number是唯一的, Protel PCB封装库PAD number可以不唯一。 这就要求我们在设计原理图库的时候Pin number也要和Allegro封装库对应起来,否 则设计的电路图没法导入Allegro里作PCB设计。

例如:bga484_1r00_23x23 表示484 管脚,球间距为1mm,Body size 为23mm 乘以23mm 的BGA 封装。

qfp100_0r50_16x16 表示100 管脚,脚间距为0.5mm,最大外型尺寸为16mm 乘以 16mm 的QFP 封装。 3)SOP、SO、SSOP、TSOP、TSSOP 类封装元件: sop/tsop/ssop/tssop+管脚数_Pitch_Full size 宽度 例如: tssop8_0r65_4r90 表示管脚数为8,管脚间距为0.65mm,Full size 宽度为4.9mm 的 TSSOP封装。

2 Allegro封装库设计规范

PCB 封装名称的命名方法。

1)标准两管脚分立器件: 阻容感等贴装分立器件,根据国际标准命名法则0402、0603、1206、1210、1805…等,以 其实体英制大小进行标准命名。 2)集成芯片类封装元件: 比如:BGA、 QFP、QFN、PLCC、 DFN、SON等等类型芯片,命名规则为: 芯片类型+管脚数_Pitch_Full size

2 Allegro封装库设计规范

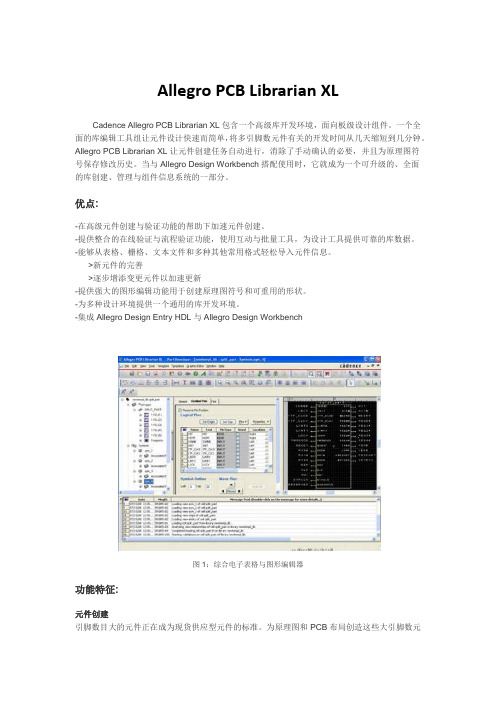

Allegro PCB Librarian XL

Allegro PCB Librarian XLCadence Allegro PCB Librarian XL包含一个高级库开发环境,面向板级设计组件。

一个全面的库编辑工具组让元件设计快速而简单,将多引脚数元件有关的开发时间从几天缩短到几分钟。

Allegro PCB Librarian XL让元件创建任务自动进行,消除了手动确认的必要,并且为原理图符号保存修改历史。

当与Allegro Design Workbench搭配使用时,它就成为一个可升级的、全面的库创建、管理与组件信息系统的一部分。

优点:-在高级元件创建与验证功能的帮助下加速元件创建。

-提供整合的在线验证与流程验证功能,使用互动与批量工具,为设计工具提供可靠的库数据。

-能够从表格、栅格、文本文件和多种其他常用格式轻松导入元件信息。

>新元件的完善>逐步增添变更元件以加速更新-提供强大的图形编辑功能用于创建原理图符号和可重用的形状。

-为多种设计环境提供一个通用的库开发环境。

-集成Allegro Design Entry HDL与Allegro Design Workbench图1:综合电子表格与图形编辑器功能特征:元件创建引脚数目大的元件正在成为现货供应型元件的标准。

为原理图和PCB布局创造这些大引脚数元件,如果不使用特殊工具加快速度,那么可能要花费几个小时甚至几天时间。

Allegro PCB Librarian XL强大的导入与电子表格编辑功能,为操作大引脚数元件数据提供了辅助。

用户可以根据多种符号迅速分离引脚,将引脚名与引脚数一一对应,并指定电源与接地引脚的可见性。

强大的图形编辑器让符号创建简单易上手。

用户不仅可以创建复杂的IEC与IEEE形状代表引脚与功能,还可以将它们保存为可重用的库元素。

Allegro PCB封装向导为多数常用元件提供模板,使得封装创建十分简单。

使用封装向导,用户可以在几分钟的时间内精确创建有数千个引脚的复杂封装。

2 第二章 设定Allegro的工作环境

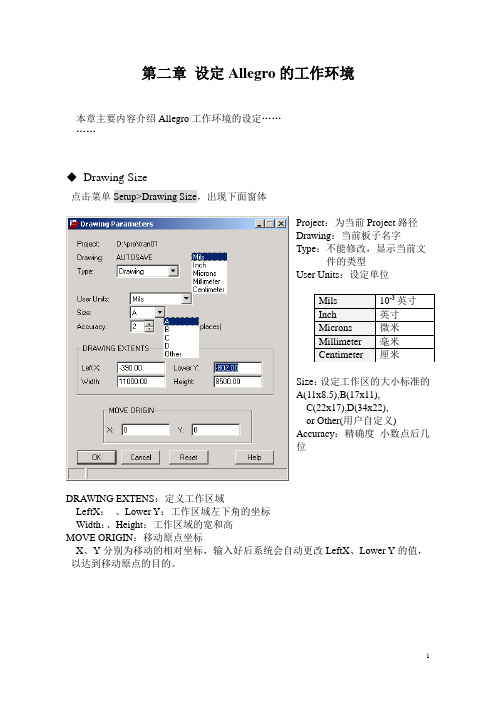

第二章 设定Allegro 的工作环境本章主要内容介绍Allegro 工作环境的设定…… ……Drawing Size点击菜单Setup>Drawing Size ,出现下面窗体Project :为当前Project 路径 Drawing :当前板子名字Type :不能修改,显示当前文件的类型User Units :设定单位Size :设定工作区的大小标准的A(11x8.5),B(17x11), C(22x17),D(34x22), or Other(用户自定义)Accuracy :精确度 小数点后几位DRAWING EXTENS :定义工作区域LeftX : 、Lower Y :工作区域左下角的坐标 Width :、Height :工作区域的宽和高 MOVE ORIGIN :移动原点坐标X 、Y 分别为移动的相对坐标,输入好后系统会自动更改LeftX 、Lower Y 的值, 以达到移动原点的目的。

Drawing Options点击菜单Setup>Drawing OptionsDRC TAB:Status:DRC的状态,后面显示当前有多少DRC状态:UP TO DATE表示当前的OUT OF DATE BATCH表示当前的DRC已经不正确,需要更新On-Line:设置是否要在线式更新DRCMarker size:显示DRC的大小Symbol height:零件的默认高度Update DRC:更新板子上的DRCDisplay TAB:Max rband count:这是设置当移动零件时,零件的pin数大于这个值时,就不显示连到这零件Pin上的net,经过Pin的net还是显示的。

零件Pin156:设500效果:设100效果:Ratsnest geometry:1.Straight:在一直线的pin rats时表现为从pin的中心点到pin的中心点。

2.Jogged:在一直线的pin rats时表现为从pin的中心点拉一个角度出去。

Cadence Allegro SPB简介与安装方法

Cadence Allegro SPB 简介与安装方法Cadence 新一代的Cadence 15.5系统互连设计平台优化并加速了高性能高密度的互连设计。

Cadence Allegro 平台所需的关键技术,以建立从IC 制造、封装和PCB 的一整套完整设计流程。

Cadence Allegro 可提供新一代的协同设计方法,以便建立跨越整个设计链 ——包括I/O 缓冲区、IC 、封装及PCB 设计人员的合作关系。

Cadence 公司著名的软件有:Cadence Allegro ;Cadence LDV ;Cadence IC5.0;Cadence orCAD 等。

功能强大的布局布线设计工具——Allegro PCB ,它是业界领先的PCB 设计系统。

Allegro PCB 是一个交互的环境,用于建立和编辑复杂的、多层印制电路板。

Allegro PCB 丰富的功能将满足当今世界设计和制造的需求。

针对目标按时完成系统协同设计,Cadence Allegro 平台使能协同设计高性能的集成电路、封装和印制电路板的互连,降低成本并加快产品上市时间。

Cadence Allegro 系统互连平台能够跨集成电路、封装和PCB 协同设计高性能互连。

应用平台的协同设计方法,工程师可以迅速优化I/O 缓冲器之间和跨集成电路、封装和PCB 的系统互联。

该方法能避免硬件返工并降低硬件成本和缩短设计周期。

约束驱动的Allegro 流程包括高级功能用于设计捕捉、信号完整性和物理实现。

由于它还得到Cadence Encounter 与Virtuoso 平台的支持,Allegro 协同设计方法使得高效的设计链协同成为现实。

CADENCE PSD 14.1安装方法1. 建立C:\CadenceLM 目录,将光盘Crack 中的所有文件Copy 到该目录;2. 运行Cadence_PSD.exe ,选中“FlexLM Server”,点击“Generate”生成License.dat 文件,在该目录下可以看到;3. 运行光盘setup.exe 安装,选“NetWork Licensing”安装;4. 安装License Manager ,需要license 文件的时候,把路径指到C:\CadenceLM ,5. 安装完成,重新启动6. 打开控制面板,打开FlexLM ,激活服务器,在Status 项可以看到服务是否启动7. 再次运行光盘setup.exe 安装,选“NetWork Licensing”安装;8. Install Products,选择你需要的选项进行安装,询问License 的时候把路径指到C:\CadenceLM ;9. 安装完成,重启动即可使用!!Cadence 14.2 安装方法(详解)1. 在C 盘根目录创建Cadence 文件夹,再在其中创建License_manager 文件夹, 把license.dat 文件拷贝到License_manager 文件夹中,并编辑它的第一行: SERVER your computer name ANY 270012. 打开“控制面板”--“系统”--“高级”--环境变量,新建用户环境变量,变量名LM_LICENSE_FILE ,变量值27001 your computer name3. 运行CD1的Setup.exe4. 选择Network Licensing5. 选择License Manager 安装6. 然后会出现错误窗口,不用管它。

AllegroCB层叠设置

Cade nee Allegro 层叠设置-- 孙海峰对于刚学习Cade nee Allegro ,或者刚从其他 EDA 软件(如Protel )转为 Allegro 使用上的朋友,其颜色设置、层叠意义往往使人望而却步。

如此多的额 叠层,更细致的、更可靠的层叠设置,如何更好的理解和把握,哪些层叠对于我 们设计是常用或必需的呢,我将在以下做详细的介绍。

亠 皿打开Cade nee Allegro ,进入Cade nee PCB 设计环境,点击工具栏的 按钮,或执行菜单Display/Color/Visibility 命令,打开层叠颜色设置的界面,以 此为基础,我来介绍详细的层叠意义。

Cfilftr IH曲 I 啊[三 f 口宅^氓3iffi Lai-ws*OfW=5 I —DEdbb Cu^gmGlnhai Vkjfcbifc ~dQjJLQ I O置分为不同类型层叠,根据个人习惯分别进行设置,要设置好,先必须了解各个 层叠的具体意义。

lj B T»vnr ■ t •_Cl piEjJar , -Ss St Iftclr]5p :■■ L J '■ F 击北MTO P :UXL If 7-n-r p^.-bj点:・N iA-:: Pin vsi. I lun SreT&Jr」L-」Ftf]r4£4 ・・ i7 T>j«riBnl s Hiiiuf act^s IKf WViiig f Mn-iLt AfiL«lTTL3CkLd血葩0,:. 臨带GHSei 弓 LTTFBH .J T 1" 写olif T 3B3 -F^E-jTtDSJ JHI —inI/5fepdrlF4=rinriJ*匚 ■ L ■nnwn □□rm □□□□□ 匚■■■ rar nnr □□□■ n n □ i ■■■■■n.-i-r nnnn - c ■口□口 r uuini r i 在弹出的颜色设置对话框中可以看到, Cade nee Allegro 设计环境将颜色设fLlp*革丄亠二■亠L. tot - q 杠二二LLrl —Lu厂匚□口Plii厂StlrCteJnJ□□1 JRs nzit-_.K1 E J I<i >lZEK / ~3 口Tl ri I|Cu^kn >t»4w.高速PCB 设计经常会用到区域的概念,包括:Constraint Region 高速区域 约束的特殊规则区域、Route Keep Out 禁止布线区域、Via Keep Out 禁止放置 过孔区域、Package Keep Out 禁止布局区域、Package Keep In 允许布局区域、1、PCB 基本叠层Stack-up 设置a) Subclass 子层叠,表示PCB 中具体层叠,包括:Top 层、Bottom 层、 内层(POW/GND )、阻焊层(Soldermask_Top/Soldermask_Bottom )、加焊 层(Pastemak_Top/Pastemask_Bottom ),其他 Subclass 子层叠目前设计中 不需要用到,包括底片应用层(Filmmasktop/Filmmaskbottom )等,这些不常 用的层叠不用花时间去了解的,与目前无关□ My Favori tes rh Di 理1岂 $ £3 SticlrUp-* Cl ConductorFn rimPl Fcn-ConduBoard. G&cwnetry Packige Geoin . _ .Embedded ・-Component EM anuf acturingDrawing F Qrmat區□□□□□□□口 :一出 lirw —-'.: “--==:Tit Si pull ■S -nd ftot-aaSul d E ras sk_T op Sol^trsaxk_&Dtto= Pafit«KiGk_T{>t> Psst ~a;ic_5c-tt:?. F il^asktcp乙庄zcFcCka^_Dctt jnD«nii tr_V*rT_Hithb)子层叠相应的对象 Objects ,与上述的Subclass 一起使用,用以显示不 同子层叠上相应对象,包括子层叠上对应的Pin 引脚、Via 过孔、Etch 走线、DRC 规则错误、Plan 覆铜平面、Anti Etch 隔离走线(用于铜皮分割),这样既 可配合子层叠,设置对应层不同对象的颜色。

Cadence Allegro PCB封装建库规则

Allegro PCB封装建库规则焊盘表贴焊盘方形焊盘命名规则:SPD焊盘长度X焊盘宽度钢网:钢网尺寸与焊盘尺寸相同阻焊:阻焊尺寸比焊盘尺寸大6mil圆形焊盘命名规则: SPD焊盘直径钢网:钢网尺寸与焊盘尺寸相同阻焊:阻焊尺寸比焊盘尺寸大6mil通孔金属化孔命名规则:PAD焊盘直径CIR钻孔直径(圆形焊盘)/PAD焊盘边长SQ钻孔直径(方形焊盘)参数计算:焊盘:分为表层焊盘和内层焊盘,表层焊盘尺寸参考各器件封装参数计算;内层焊盘比钻孔大尺寸10~20milAntipad:各层Antipad至少比焊盘大10mil,具体尺寸大小应该考虑电气安全、传输阻抗、生产可行性等实际情况而定Thermal Relief :与Antipad取相同尺寸阻焊:阻焊尺寸比焊盘尺寸大6mil非金属化孔命名规则:MaDOTb(钻孔直径为a.bmm)/Tooling-Hole,(2004-4-15以前PAD为按照FIaDOTb命名),如果为整数直径,则为Ma即可。

参数计算:焊盘:设置焊盘比钻孔大1milAntipad:各层Antipad至少比焊盘大10mil,具体尺寸大小应该考虑电气安全、生产可行性等实际情况而定Thermal Relief :与Antipad取相同尺寸阻焊:阻焊尺寸比钻孔尺寸大6mil过孔命名规则:VIA钻孔大小,比如VIA10 ,如果为堵孔,命名为VIA钻孔大小-F。

比如VIA12-F。

参数计算:参照下列表封装库封装库的组成封装库主要由Package Symbol, Mechanical Symbol, Format Symbol, Shape Symbol ,Flash symbol五种.他们又可以分为可编辑(*.dra)与不可编辑(Package Symbol→ .psm , MechanicalSymbol→ .bsm , Format Symbol→ .osm , Shape Symbol→ .ssm,flash symbol→*.fsm)其中目前和我们联系比较大的是Package Symbol, Mechanical Symbol, Format Symbol,Flash symbol。

Cadence allegro使用指南

PCB 设计前处理——导网表

• 封装库路径设置

PCB 设计前处理——导网表

• 封装库路径设置

PCB 设计前处理——导网表

• Capture CIS第一方网表导出/导入

PCB 设计前处理——导网表

• Capture CIS第一方网表导出/导入

PCB 设计前处理——导网表

PCB Editor 设计环境和设置——参数设置

• 搜索及My_favorites的使用

PCB Editor 设计环境和设置——参数设置

• 常用项目设置

PCB Editor 设计环境和设置——参数设置

• 库路径设置

PCB Editor 设计环境和设置——参数设置

• 颜色设置(Class和Subclass)

• 美观度

PCB布局思路

• 接口器件及结构定位

– 按引脚定位

PCB布局思路

• 接口器件及结构定位

– 按元件外框或者中线坐标来定位

PCB布局思路

• 主要芯片布局

– PCB区域高度限制

PCB布局思路

• 主要芯片布局

– 散热考虑

PCB布局思路

PCB Editor 设计环境和设置——工作界面

• Allegro SPB 选项面板

– 关闭、打开、重置选项卡

PCB Editor 设计环境和设置——参数设置

• Design Parameter

– Display选项卡

PCB Editor 设计环境和设置——参数设置

• Design Parameter

– Design选项卡

PCB Editor 设计环境和设置——参数设置

• Design Parameter

AllegroPcblayout设计流程概述

目录(mùlù)

• 特性 • 设计软件 • PCB的历史 • PCB设计的展开趋向 • PCB设计流程(liúchéng) • PCB板的概述 • 稀有的PCB工具软件引见 • PCB板设计流程(liúchéng) • PCB板设计趋向

第三页,共94页。

特性(tèxìng)

• 21世纪人类进入了信息化社会,电子产业 失掉(shīdiào)了飞速展开,人们的义务生活 和各种电子产品密不可分。而作为电子产品不 可缺少的重要载体-PCB,也扮演了日益重要的 角色。电子设备出现高功用、高速、庄重的趋 向,PCB作为多学科行业已成为电子设备最关键 技术之一。PCB行业在电子互连技术中占有无 足轻重的位置。

第十七页,共94页。

图1

第十八页,共94页。

图2

第十九页,共94页。

双面板

• 双面板〔Double-Sided Boards〕 这种电路板 的两面都有布线,不过(bùguò)要用上两面的导 线,必需求在两面间有适当的电路衔接才行。这 种电路间的〝桥梁〞叫做导孔〔via〕。导孔是 在PCB上,充溢或涂上金属的小洞,它可以与 两面的导线相衔接。由于双面板的面积比单面板 大了一倍,而且由于布线可以相互交织〔可以绕 到另一面〕,它更适宜用在比单面板更复杂的电 路上。

• 惯例PCB设计包括建库、调网表、规划、 布线、文件输入等几个步骤,但惯例PCB设 计流程(liúchéng)曾经远远不能满足日益复杂 的高速PCB设计要求。

•

由于SI仿真、PI仿真、EMC设计、单板

工艺等都需求严密结合到设计流程(liúchéng)

中,同时为了完成质量控制,要在各节点添

加评审环节,实际的PCB设计流程(liúchéng) 要复杂得多。图中为PCB设计的较典型的 PCB设计流程(liúchéng),能更好地处置高速

AllegroPCB布局

Allegro PCB布局孙海峰完成电路原理图设计绘制、元件封装创建以及原理图网表导入PCB这一系列操作后,就要开始进行PCB的布局布线了,这是PCB板设计的主要工作。

其中PCB布局是EDA设计的重要环节,在PCB设计过程中,正确的电路板元件布局,及正确的布线方向可以有效地防止噪声干扰。

PCB布局主要有两种方式,交互式布局和自动布局,设计者通常时在自动布局的基础上以交互式布局进行调整。

布局的具体流程,是这样的:1、布局准备,包括绘制PCB板框、确定机构件(定位孔、对接孔等)位置、标注重要网络(电源、地等);2、进行布局,根据原理图布局,可以自动布局,也可以手动布局;3、布局后的检查,包括检查元件空间上是否冲突、是否排列整齐等操作。

接下来,就来看看PCB时如何进行布局的。

一、创建电路板进行电路板设计之前,需要首先确定电路板的尺寸、板层、材料等基本要求,而后才能在电路板上进行布局布线等操作。

建立电路板有两种方式,即:手动建立方式和向导建立方式。

下面分别来说明这两种建立方式。

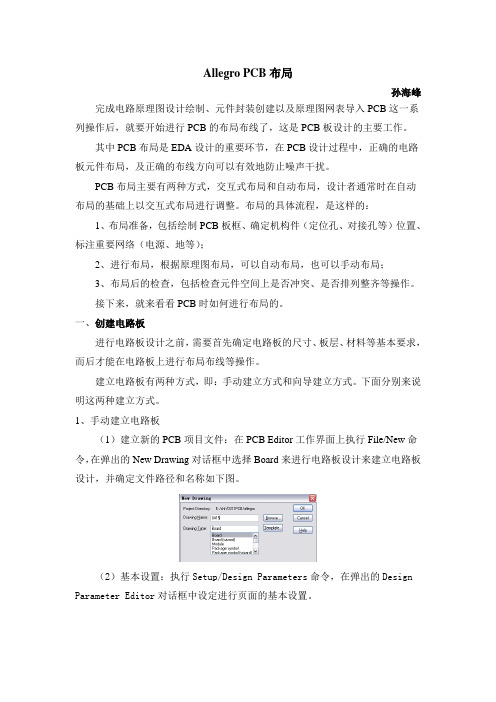

1、手动建立电路板(1)建立新的PCB项目文件:在PCB Editor工作界面上执行File/New命令,在弹出的New Drawing对话框中选择Board来进行电路板设计来建立电路板设计,并确定文件路径和名称如下图。

(2)基本设置:执行Setup/Design Parameters命令,在弹出的Design Parameter Editor对话框中设定进行页面的基本设置。

(3)建立电路板外框:执行Add/Line命令,Options窗口中选择Board Geometry、Outline以及画线方式,则可以进行电路板外框的绘制了。

当然也可以在命令窗口输入命令,来进行外框的精确绘制。

例如下图,通过输入一系列命令后,得到尺寸精确地电路板外框。

(4)安装电路板机构件(安装孔、对接孔等):电路板外框画好后,要放置电路板机构件,执行Place/Manually命令,弹出Placement对话框,在Adanced Settings选项卡中勾选Library,如下图。

Cadence-Allegro-16.5-PCB教程

Visibility控 • 制控面制布板线:层以及每层中元素/对象的显示。

在设置时可如以图整中表体示只设显示置TO,P层布也线走可线以、过单孔、独引脚设和置DRC标。志。

鼠标的

功能:

• 鼠标左键:对象/元素的选取、命令的选择 等

• 鼠标右键:弹出下Z拉oom菜Pre单v • 鼠标中间键:Zoo对m In视窗进行Zoo缩m b放y Po。ints 有两种方

文件类型介绍

• Allegro根据不同性质功能的文件类型保存不 同的文文件件后后缀,主要的文件类类型型 可以参照下表:

缀名

.brd 普通的板子文件 .dra Symbols或Pad的可编辑保存文件 .pad Padstack文件,在做symbols时可以直接调用 .psm Library文件,存package symbols .osm Library文件,存format symbols .bsm Library文件,存mechanical symbols .fsm Library文件,存flash symbols .ssm Library文件,存shape symbols .mdd Library文件,存module definition .tap 输出的包含NC drill数据的文件 .scr Script 和macro 文件 .art 输出的底片文件

• (1)Allegro PCB Designer:是应用最广泛 的一种版本。产品由Base模块和Option附加 模块组成,通过一个完全集成式的设计流 程进行PCB Layout设计。

• (2)OrCAD PCB Designer:分为Professional 和Standard版本,与Allegro PCB Designer相 比,不具有电气约束驱动规则

第11章 Allegro PCB Editor电路板设计

选择Anti Pad,使用的焊盘通过内部敷铜层,但不需要与 该层连接,在该层上;

焊盘类型若为面层上的花焊盘,可将其看作三种类型 的组合,按如图11.7所示的图形类型使用方法,将合适 的尺寸填入3个Geometry框;若用作Flash Pad,点选 Thermal Relief框内的按钮,从中选择用户自己制作的 图形;如用作Shape Pad,使用Regular Pad和Anti Pad各 自框内的按钮,从中选择用户自己制作的图形。

第11章 Allegro PCB Editor电路板设计

(a)Find控制面板 (b)Visibility控制面板 图11.2 Find和Visibility控制面板

第11章 Allegro PCB Editor电路板设计

•Options面板主要显示了执行命令时操作对象的一些属性, 执行具体命令后,Options中会显示当前命令有关的相关参 数。 •在Find面板上,用户可以通过一个过滤器来选择可用的操 作对象。

在Project Manager下,

单击Library Tools—PadStack Editor启动建立和编辑焊盘 Padstack的工作,启动后出现的窗口内有两个标签 Parameters和Layers,分别用于焊盘的参数设定和PCB各层 的参数设定,显示内容分别如图11.6和图11.7所示。

点选其下File-New菜单项,输入焊盘名,用户可根据自 己的开发需求自行设定焊盘参数,建立一个新焊盘文件。 若点选File-Open菜单项,打开已有焊盘文件,用户可修 改此焊盘参数。完成设定后,可单击File菜单下Save或 Save As子项加以保存,得到焊盘文件以备使用。利用 Reports菜单中的各项,可以查看焊盘及钻孔的具体数据。