nt_band_keeper_silicone_DFM

ABB Ability ODM zenon 8.20快速安装指南说明书

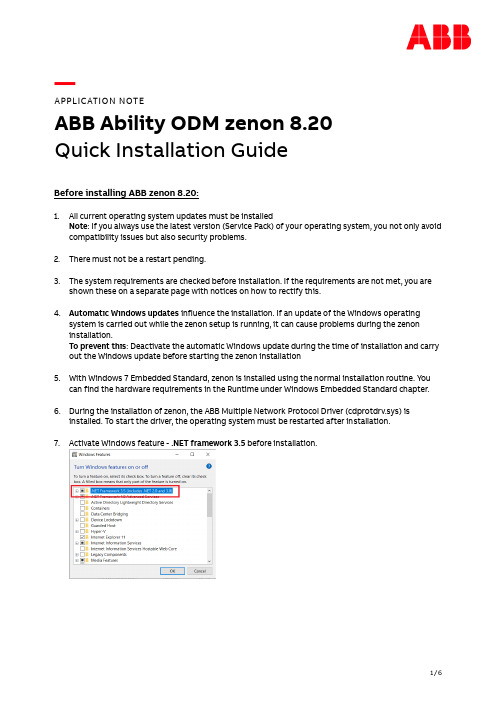

—APPLICATION NOTEABB Ability ODM zenon 8.20Quick Installation GuideBefore installing ABB zenon 8.20:1.All current operating system updates must be installedNote: If you always use the latest version (Service Pack) of your operating system, you not only avoid compatibility issues but also security problems.2.There must not be a restart pending.3.The system requirements are checked before installation. If the requirements are not met, you areshown these on a separate page with notices on how to rectify this.4.Automatic Windows updates influence the installation. If an update of the Windows operatingsystem is carried out while the zenon setup is running, it can cause problems during the zenon installation.To prevent this: Deactivate the automatic Windows update during the time of installation and carry out the Windows update before starting the zenon installation5.With Windows 7 Embedded Standard, zenon is installed using the normal installation routine. Youcan find the hardware requirements in the Runtime under Windows Embedded Standard chapter.6.During the installation of zenon, the ABB Multiple Network Protocol Driver (cdprotdrv.sys) isinstalled. To start the driver, the operating system must be restarted after installation.7.Activate Windows feature - .NET framework 3.5 before installation.Frequent sources of error during installation:1.The virus scanner is active and blocks the installtion because the scanner thinks it´s a virus.Solution: Seperate the system from the network, disable the virus scanner, execute the installation again.2.The firewall was not configured correctly. Solution: Seperate the system from the network, disablethe firewall, execute the installation again.3.Erroneous SQL-installation on the system. Solution: Create project backups; if possible, deinstallSQL server, rename the SQL folder, and restart installation.Get started with download:1.Download ABB zenon 8.20 setup from ABB website (use direct link as mentioned below):ABB zenon 8.20 download link2.Run installer as administrator.3.Select the language for the installation.4.Read and agree to the license terms. Print button will print the EULA and previous button go back tothe language selection page.5.Select options for download:a.Main Release – ABB zenon editor and runtime standard packageb.Zenon PDF Help Files - Besides the Online Help which is installed with zenon software bydefault, the same help content in PDF format can be downloaded and installed.c.ZEE600 - ABB zenon Electrification Edition for seamless integrator of diverse devices such asABB and 3rd party make protection relays, meters, substation equipment condition monitoring units, Programmable Logic Controllers (PLC) and Remote Terminal Units (RTUs),6.Download in progress.7.Downloaded package will be saved in selected target folder.Get started with installation:1.You can start installation on the same machine or download setup can be copied to anothermachine for installation.2.Right click on Start.exe and run as administrator.3.Select language again for installation:4.Also accept license terms again.5.Select options for installation (We suggest youto select all options during download and later youcan choose desired options for installation).a.Zenon 8.20 – You can select Editor (complete development package withruntime), or standalone runtime option. Additionally zenon web sevrer and clientcan be selected for installation.b.Zenon PDF Help Files – in English and German.c.ZEE600 package.6.You will get installation successful message once all selected components are installed properly.7.In case of failed installation please click Show logs link to collect logs and contact us via*********************.。

Switchtec PSX Gen4 程序可配置 PCIe 交换机家族说明书

SummaryThe Switchtec PSX Gen4 Programmable PCIe Switch Family comprises programmable and high-reliability switches that support up to 100 lanes, 52 ports, 26 virtual switch partitions, 48 Non-Transparent Bridges (NTBs), hot- and surprise-plug controllers for each port, advanced error containment, comprehensive diagnostics and debug capabilities, a wide breadth of I/O interfaces and an integrated MIPS processor.T ypical applications for the PSX family include PCIe SSD enclosures, Flash arrays, multi-host archi-tectures, high-density servers, blade servers, pooled storage/compute and applications that require customized, high-reliability PCIe switching.Switchtec TM PSX Gen 4 Programmable PCIe ® Switch FamilyPM41100, PM41084, PM41068, PM41052, PM41036, PM41028FeaturesHigh-Performance Non-Blocking Gen4 Switches• 100-lane, 84-lane, 68-lane, 52-lane, 36-lane and 28-lane variants• Ports bifurcate to x11/x2/x4/x8/x16 lanes • Up to 48 NTBs assignable to any port• Logical Non-Transparent (NT) interconnect allows for larger topologies• Supports 1+1 and N+1 failover mechanismsDMA Controller• High-performance, ultra-low latency DMA engineError Containment• Advanced Error Reporting (AER) on all ports• Downstream Port Containment (DPC) on all downstream ports • Completion Timeout Synthesis (CTS) to prevent an error state in an upstream host due to incomplete non-posted transactions• Upstream Error Containment (UEC), a programmable feature that prevents errors from propagating upstream • Hot- and surprise-plug controllers per port• GPIOs configurable for different cable/connector standardsDiagnostics and Debug• Real-time eye capture• External loopback capability• Errors, statistics and performance countersPCIe Interfaces• Passive, managed and optical cables• SFF-8644, SFF-8643, SFF-8639, OCuLink and other connectors1x1 natively on four lanesThe Microchip name and logo, the Microchip logo and PCIe are registered trademarks and Switchtec is a trademark of Microchip Technology Incorporated in the U.S.A. and other countries. All other trademarks mentioned herein are property of their respective companies.© 2020, Microchip Technology Incorporated. All Rights Reserved. 1/20 DS00003308AHighlights• High-reliability PCIe: robust error containment, hot- and surprise-plug controllers per port, end-to-end data integrity protection, high-quality, low-power SERDES• PSX Software Development Kit (SDK): enables customer-differentiated solutions in areas such as error containment and surprise-plug• Integrated enclosure management processor, I/O interfaces, and SDK for enclosure management firmware development • Comprehensive diagnostics and debugging: PCIe genera-tor and analyzer, per-port performance and error counters, multiple loopback modes and real-time eye capture• Significant power, cost and board space savings with sup -port for:• Up to 52 ports, 48 NTBs, and 26 virtual switch partitions • Flexible x11, x2, x4, x8, and x16 port bifurcation with no restrictions on configuring ports as either upstream or downstream, or on mapping ports to NTBs• NVMe-MI enclosure management:• Integrated NVMe controller• In-band management supporting SES and native NVMe enclosure management stack• Out-of-band management supporting MCTP through I 2C • Secure system solution with boot image authenticationPeripheral I/O Interfaces• Up to 11 Two-Wire Interfaces (TWIs) with SMBus support • Up to 4 SFF-8485-compliant SGPIO ports• 10/100 Ethernet MAC port (MII/RMII) (PSX 100x/84x/68xG4)• 16-bit parallel local bus interface with ECC protection • Up to 4 UARTs•JTAG and EJTAG interfaceHigh-Speed I/O• PCIe Gen4 16 GT/s• Supports PCIe-compliant link training and manual PHY configuration• Manual PHY configuration for opticalPower Management• Active State Power Management (ASPM)• Software-controlled power managementChipLink Diagnostic Tools• Extensive debug, diagnostics, configuration and analysis tools with an intuitive GUI• Access to configuration data, management capabilities and signal integrity analysis tools (such as real-time eye capture)Evaluation KitThe PM42100-KIT Switchtec Gen4 PCIe Switch Evaluation Kit is a device evaluation environment that supports multiple interfaces.Example Application1x1 natively on four lanesFor More Information。

Autodesk Nastran 2022 用户手册说明书

MPA, MPI (design/logo), MPX (design/logo), MPX, Mudbox, Navisworks, ObjectARX, ObjectDBX, Opticore, Pixlr, Pixlr-o-matic, Productstream,

Publisher 360, RasterDWG, RealDWG, ReCap, ReCap 360, Remote, Revit LT, Revit, RiverCAD, Robot, Scaleform, Showcase, Showcase 360,

TrueConvert, DWG TrueView, DWGX, DXF, Ecotect, Ember, ESTmep, Evolver, FABmep, Face Robot, FBX, Fempro, Fire, Flame, Flare, Flint,

ForceEffect, FormIt, Freewheel, Fusion 360, Glue, Green Building Studio, Heidi, Homestyler, HumanIK, i-drop, ImageModeler, Incinerator, Inferno,

Autodesk Nastran 2022

Reference Manual

Nastran Solver Reference Manual

2108 G07 数据路径保护固件与扩展 DDF 内存测试(数据路径保护固件)说明书

2108-G07/R03 Firmware & 2108 G07 Extended DDF Memory Testing(Data Path Protection Firmware)1. BackgroundThe Data Path Protection firmware is intended to provide a method forconfirming the integrity of the data path through the SAN Data Gateway.This test uses pattern data moved through various memory interfaces toinsure that all data paths into and out of command processing memoryand data flow memory (DDF) are correctly functional.Current tests in use are already verifying the integrity of the memories,and are testing the memory interfaces in short transactions. Thisadditional test uses long burst transfers to more completely test thefunction of the interfaces on the data path.The Data Path Protection firmware executes while the SAN Data Gateway is in operation, without affecting on-going transactions. The Data PathProtection firmware can run periodically or be executed on demand.1.1 SAN Data Gateway and SAN Data Gateway RouterThe Data Path Protection Firmware is designed to test data paths to andfrom the DDFM card of the SAN Data Gateway. This card has 2independent data paths, one from the Primary PCI Bus and one from theSecondary PCI bus. The Data Path Protection Firmware executes transfer over both these paths, to explicitly verify integrity on both.The SAN Data Gateway Router has no DDFM card. Data buffer space islocated in the same memory used for the central processor. This memoryis accessed through a single path, regardless of the bus location of thedevice accessing the memory (FC adapters on the Primary PCI Bus, SCSI adapters on the Secondary PCI Bus, or the Central Processor).In both the SAN Data Gateway and the SAN Data Gateway Router, amemory integrity test, called the Memory Scrubber, is executed. In thecase of the SAN Data Gateway, the Memory Scrubber runs on a singleinterface to the DDFM. The Data Path Protection Firmware extended this test to provide a check on the other data path. In the SAN Data Gateway Router, the Memory Scrubber already tests the one and only interface to the memory, so a further Data Path Protection is not needed.In addition to memory testing, the SAN Data Gateway and SAN DataGateway Router periodically test connections between the centralprocessor and the I/O controllers. These tests further assure the integrity of the PCI buses and the PCI interface components.2. Test CoverageThe SAN Data Gateway uses 2 PCI buses to pass data between I/Ocontrollers (Fibre Channel and SCSI), command processing memory,DDF memory and the system processor. The test will write and readpatterned data through the interfaces, to insure proper operation on allmemory interfaces and on both PCI buses. All memory interfaces aretested with both reads and writes.3. On Demand Test for TapeWhen a SAN Data Gateway is used in tape backup applications, theSoftware Data Path Test is used to confirm integrity of the data paths.This test runs on demand as the result of host software issuing one of the commands in the list below immediately after the host issues a WRITEcommand:• WRITE FILE MARK• REWIND• LOAD/UNLOAD• ERASE• SPACE• LOCATEIf an error is found on the data path, the tape command will fail, and there will be a Hardware Error. See “Hardware Error Actions”, below.4. Hardware Error Actions1. Following detection of a hardware error due to aa data pathfault, a message will appear in the SAN Data Gateway Event log,with the following codes:CLASS:CS_EVCLASS_SYSTEM_FAULT0x07CODE:CS_EVCODE_IBF0x0AERROR NUM:DATA FLOW_FAULT0x10102. The SAN Data Gateway will be reset into an un-bootable state.The “RDY” LED will be on, and not blinking.5. Corrective Actions1.Make sure that all I/O is stopped.2.Unplug the ethernet cable, as well as all FC and SCSI cables.3.Connect the null modem cable (and the 9- to 25-pin adapt er if applicable) betweenthe computer serial (COM) port and the SAN Gateway Service Port. If the Service Terminal is already connected, skip to Step 10, below.4.Turn on the service terminal.5.On the service terminal, select the HyperTerminal icon and double-click on it. Thisexample uses HyperTerminal, but other terminal emulation packages are available.Follow instructions that come with the application, if you are not usingHyperTerminal.6.In the New Connection dialog enter SAN Gateway for the name and click OK.7.In the Connect To dialog, for the Connect using field select the COM Port numberthat you have chosen and click OK.8.In the COM Properties dialog select the following:Bits per second:19200Data bits:8Parity:NoneStop bits:1Flow Control:Xon/Xoff9.Click OK.10.Enter the @ command at the VxWorks Boot prompt:[VxWorks Boot]:@11.The SAN Gateway will partially start, and the “RDY” LED will flash rapidly.12.From the service terminal, type the diagBoot command and press Enter:diagBoot13.Wait for the SAN Gateway to reboot.14.At the diagmode> prompt, diagnostic tests may be executed. If the only errorrecorded in the SAN Gateway Event Log is "Data Flow Fault", use the ddfccommand.diagmode>ddfcIf “ddfc” returns a failure status, and no other errors are indicated,replace the DDF memory card.15.If other errors are indicated, follow the instructions in Chapter 3, "MaintenanceAction Plans" and Appendix C, "Diagnostic Command Reference" in the SANGateway Service Guide.6. Returning the SAN Data Gateway to Use1.Type the normalBoot command and press Enter.diagmode>normalBoot2.Wait for the SAN Gateway to begin its reboot.3.The SAN Data Gateway is still unbootable. At the [VxWorksBoot]:prompt, begin editing the boot parameters by entering the ccommand:[VxWorks Boot]:cThe boot parameters will display, line by line. Press Enter to move to thenext field:'.'=clear field;'-'=go to previous field;^D=quitboot device:lnPciprocessor number:0host name:brewmaster2file name:ffs0:vxWorkst.Zinet on ethernet(e):192.168.30.201inet on backplane(b):host inet(h):192.168.30.19gateway inet(g):192.168.30.1user(u):agentftp password(pw)(blank=use rsh):agent99flags(f):0x4target name(tn):MyGatewaystartup script(s):other(o):Write complete[VxWorks Boot]:4.Press Enter to move through all fields that do not need to bechanged. The first field that needs to be changed will be theflags(f) field. Change the flags(f) field to 0x8:flags(f):0x85.Press Enter again to continue moving through fields that do notneed to be changed. Then 4change the startup script(s) field to ffs0:sna.rc:startup script(s):ffs0:sna.rc6.When the [VxWorks Boot]: prompt is seen again, reboot thesystem:[VxWorks Boot]:@7. System should boot normally:[VxWorks Boot]:@boot device:lnPciprocessor number:0host name:brewmaster2file name:ffs0:vxWorkst.Zinet on ethernet(e):192.168.30.201host inet(h):192.168.30.19 gateway inet(g):192.168.30.1user(u):agentftp password(pw):agent99flags(f):0x8target name(tn):MyGatewaystartup script(s):ffs0:sna.rcAttaching network interface lnPci0...done. Attaching network interface lo0...done. Initializing ffs0:AutoSync disabledMounting ffs0:succeeded.done.Loading ffs0:vxWorkst.Z...Inflatingffs0:vxWorkst.Z...Read data into0xc1abf160,len0x000bb586 Inflate to0xc1b7a6f0Inflatedentry=0xc0012bc01639616+380636+293796Starting at0xc0012bc0...Initializing FlashInitializing ffs0:Mounting ffs0:AutoSync disabledsucceeded.ffs0:already initializedAdding6823symbols for standalone.Attached TCP/IP interface to lnPci unit0 Attaching network interface lo0...done.NFS client support not included.-------------------------------------------|SAN Gateway Firmware Version0341|Copyright Pathlight Technology,Inc,1997-1999 ||VxWorks version: 5.3.1|KERNEL:WIND version 2.5|Copyright Wind River Systems,Inc.,1984-1997 ||CPU:Pathlight(i960RD).Processor#0.|Memory Size:0x2000000|BSP version 1.3/0-------------------------------------------ffs0:/-disk check in progress...System clock is set to SUN FEB0606:28:152106instead of THU JAN0100:00:001970ffs0:/-Volume is OKtotal#of clusters:1,784#of free clusters:771#of bad clusters:0total free space:789,504max contigous free space:187,392bytes#of files:18#of folders:5total bytes in files:1,018,121#of lost chains:0total bytes in lost chains:0Executing startup script ffs0:sna.rc...#!/bin/csh-fsna_monitor_initSAN Gateway Version0341.38Built Mar162001, 14:03:12value=-1040893472=0xc1f539e0dbgInitvalue=0=0x0CNFinitvalue=0=0x0csSrvcInitAttempt to add User Name pathlight failed, errno=3538946SAN Gateway Version0341.38Built Mar162001,14:03:12MyGatewayClock set to Up-time countvalue=0=0x0amemInitTesting DDF-PCI0DMA PageX Testing DDF-PCI1DMA PageX Test PASSEDAmem interrupt handler installedvalue=-1041049120=0xc1f2d9e0scsintInitNOTICE:Memory board foundVPS Enabled,License is Valid0xc1f595f0(tShell):VPS:Node name conversion enabled for1nodesData Mover Disabled,License is ValidVPM Enabled,License is ValidSCSI3-DE-TerminatedSCSI1-DE-Terminated-TERM DisabledSCSI4-DE-TerminatedSCSI2-DE-TerminatedUSCSI5-HVD Term EnabledUSCSI2-HVD Term EnabledUSCSI6-LVD Term EnabledUSCSI3-LVD Term Enabled0xc1f595f0(tShell):Disable Terminator for Channel1interrupt:Disable Terminator for Channel1SRS Enabled,License is ValidMyGatewayvalue=-1054014160=0xc12d0530Done executing startup script ffs0:sna.rc -Service Port Reflected Signal Test Starting shellMyGateway>。

Realtek Linux USB PG Tool User Guide

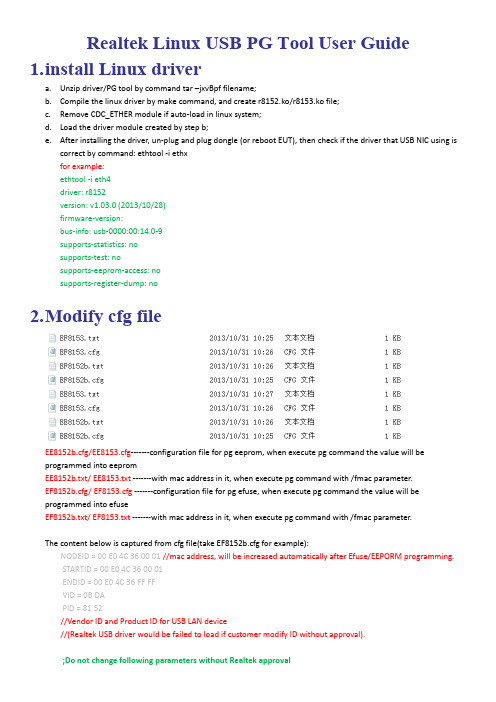

Realtek Linux USB PG Tool User Guide1.i nstall Linux drivera.Unzip driver/PG tool by command tar –jxvBpf filename;pile the linux driver by make command, and create r8152.ko/r8153.ko file;c.Remove CDC_ETHER module if auto-load in linux system;d.Load the driver module created by step b;e.After installing the driver, un-plug and plug dongle (or reboot EUT), then check if the driver that USB NIC using iscorrect by command: ethtool -i ethxfor example:ethtool -i eth4driver: r8152version: v1.03.0 (2013/10/28)firmware-version:bus-info: usb-0000:00:14.0-9supports-statistics: nosupports-test: nosupports-eeprom-access: nosupports-register-dump: no2.M odify cfg fileEE8152b.cfg/EE8153.cfg-------configuration file for pg eeprom, when execute pg command the value will beprogrammed into eepromEE8152b.txt/ EE8153.txt -------with mac address in it, when execute pg command with /fmac parameter.EF8152b.cfg/ EF8153.cfg -------configuration file for pg efuse, when execute pg command the value will beprogrammed into efuseEF8152b.txt/ EF8153.txt -------with mac address in it, when execute pg command with /fmac parameter.The content below is captured from cfg file(take EF8152b.cfg for example):NODEID = 00 E0 4C 36 00 01 //mac address, will be increased automatically after Efuse/EEPORM programming.STARTID = 00 E0 4C 36 00 01ENDID = 00 E0 4C 36 FF FFVID = 0B DAPID = 81 52//Vendor ID and Product ID for USB LAN device//(Realtek USB driver would be failed to load if customer modify ID without approval).;Do not change following parameters without Realtek approval;; 00: disable, 01: enableLPM_BESL_EN = 00SPI_FLASH_EN = 00;EEPROM_EN for 8152BN OnlyEEPROM_EN = 00NO_REMOTE_WAKEUP = 00BOS_DESC_SUPERSPEED = 00;LED_SEL_CFG = Low-Byte High-ByteLED_SEL_CFG = A9 3C;Maximum string length allowed - 17 charactersMANUFACTURE = RealtekPRODUCT = USB 10/100 LANCharacteristics- LPM_BESL_ENRTL8152B(N) supports configuration for Link Power Management (LPM) Capability to be version 1 LPM, known as HIRD (Host Initiated Resume Duration) or advanced LPM, known as BESL (Best Efort Service Latency) - SPI_FLASH_ENIn Windows operating system, it can load Realtek windows driver from SPI Flash(but it is not needed in linux or android OS). Set PG Tool AutoInstall capability (SPI_Flash_EN) to enable if necessary,- EEPROM_ENEEPROM_EN for 8152BN OnlySet EEPROM_EN to enable if external EEPROM is using.- NO_REMOTE_WAKEUPRTL8152(N) will not support remote wake up function when NO_REMOTE_WAKE is enabled.- BOS_DESC_SUPERSPEEDRTL8152B(N) supports BOS_DESC_SUPERSPEED programming for USB-IF test. SuperSpeed USB device capability descriptor will appended to the BOS descriptor tree when BOS_DESC_SUPERSPEED is enabled.- LED_SEL_CFGLED_SEL_CFG = Low-Byte High-ByteCustomized LED configuration. Please refer to RTL8152B(N)_EEPROM_eFuse Datasheet3.ProgramThere are different execute file for different CPU:Make sure execute file and configuration file are in the same path before programing.Choose correct one to program with suitable parameter below:/efuse--- Programming EFUSEExample: /efuse/eeprom--- Programming EEPROM/r--- Read EEPROM or EFuse content to standard output/s--- Search Realtek NIC adapters/# NICnumber--- Select one of Multi_NICIf no NIC number selected, default use all NICsExample: /# 0/nodeid--- Write EEPROM or EFuse NODEID--- NIC number must selectedExapmle: /eeprom /# 0 /nodeid 00E04C360001Exapmle: /efuse /# 1 /nodeid 00E04C360001/dump--- dump Efuse, EEPROM or FLASH to log file/fmac--- Write MAC address from txt file/nchkct--- Bypass Check unknown contentExample: /efuse /r /nchkctExample: /eeprom /r /nchkctFor example1.In programming process, you can run rtunicpg-x86_64 /s first to search all Realtek NIC, if 2 USB NICs found below: root@-desktop:/home/Desktop/linuxpg/new/rtunicpg# ./rtunicpg-x86_64 /s************************************************************************** RTUNicPG - EFUSE/EEPROM/FLASH Programming Utility for* RTL8152/RTL8153 Family USB FE/GBE Network Adapter* Version : v1.0.0.15-1* Copyright (C) Realtek Semiconductor Corp. 2013. All Rights Reserved.*************************************************************************0 eth1 VID:0BDA PID:8153 bcdDevice:3000 00:E0:4C:68:00:A2 path:11 eth4 VID:0BDA PID:8152 bcdDevice:2000 00:E0:4C:36:A0:1A path:22. Then, you can program one of them by command./rtunicpg-x86_64 /# 0 /efuse3. Or read the efuse content by command. /rtunicpg-x86_64 /# 0 /efuse /rIf show un-recognized efuse content, you can read efuse by command./rtunicpg-x86_64 /# 0 /nchkct /efuse /r4. Or program MAC address only by command./rtunicpg-x86_64 /# 0 /efuse /nodeid 00E04C360001 Notes:B Ethernet cannot work fine without programing (mac address is needed at least);B Ethernet can be programmed in windows, linux and android, we provide programming tool for each of the 3 OS;3.In Linux and android operating system, CDC-ECM driver is enough for USB Ethernet to work , but Realtek driver isneeded for programing;4.If you want to program LED_SEL_CFG to efuse only, you can mask all the other line value by adding “;” in the front ofeach line except LED_SEL_CFG line;5.All commands should be executed by root user.The END。

mcpa告警指导书

7600 BCF FAULTY

ESMx System module has lost connection to all modules on

TRX object allocation failed in RF module

TRX object allocation failed in RF module

01 00 00 82 00 00 TRX分配射频模块失败

0C 08 00 83 11 32 RSSI检测接收信号的差超过阈值

(54151) 7601 BCF OPERATION DEGRADED

RF模块检测到的反馈信号丢失的TX

7600 BCF FAULTY

ESMx System module has lost connection to all modules on

(54563) 7607 TRX OPERATION DEGRADED

RSSI detected Rx signal difference exceeding threshold

RF module software updated and waiting restart

00 00 00 84 22 00 射频模块的软件更新,等待重启

15637002189凌敏

7600 BCF FAULTY

7606/7607 ** ESMx System module has lost connection to RF module 系统模块连接射频模块失败

7603 BTS FAULTY

ESMx System module has lost connection to FSEx External Alarm

【企业】塑胶零件DFM检讨报告模板 英文版PPT共22页文档

°C

9 Specific Gravity (density)

10 Color/ transparency

11 Micro-Structure

12 Other character

1st shot

Input

2nd shot (if needed)

C: Visual surfaces’ requirement

E4: Conclusion about current wall thickness design

Proposal agreed by

mold engineer

product designer (MDD)

Proposal properly implemented or not

Name:

OK / NOK Comments

13

5: Output-mold construction study

F1: proposed sequence of surfaces’ released

14

f1.1 (output detail)

15

F2: proposed sequence of surfaces’ closing

16

f2.1: (output detail)

Proposal agreed by

mold engineer

product designer (MDD)

Proposal properly implemented or not

Name:

OK / NOK comments

check by supplier

OK/NOK

File name

Date (yyyymmdd) date

SJA1110 汽车以太网交换机 factsheet说明书

FACT SHEETSJA1110 The SJA1110 automotive Ethernet switchfamily offers innovative and dedicated safetyand security features designed for optimalintegration in auto ECUs. The four switchvariants enable modular ECU design andplatforms and support different automotiveapplications such as gateways, ADAS boxes,and infotainment ECUs.KEY FEATURES• I ntegrated 100BASE-T1 and 100BASE-TX PHYs• Integrated Arm® Cortex®-M7 based core• Best-in class packet inspection and DoS preventioncapabilities• Advanced secure boot capabilities• Purpose built functional safety features• Support for Wake-over-Ethernet (OPEN TC10)• Rich set of Time-Sensitive Networking (TSN) standards• Rich set of NXP original AVB and AUTOSAR® software• System solution with S32G Vehicle Networking Processorand VR5510 power management unitSJA1110 ETHERNET SWITCH BLOCK DIAGRAMENABLEMENT• Production-grade Software Development Kit (SDK)• Native integration with NXP Design Studio IDE• Production grade AUTOSAR drivers• Production grade AVB/802.1AS synchronization protocol middleware• Evaluation board compatible with NXP’s Smart Application Blueprint for Rapid Engineering (SABRE)• Linux® DriversSJA1110 TSN ETHERNET SWITCH/SJA1110NXP and the NXP logo are trademarks of NXP B.V. All other product or service names are the property of their respective owners. Arm and Cortex are trademarks or registered trademarks of Arm Limited (or its subsidiaries) in the US and/or elsewhere. The related technology may be protected by any or all of patents, copyrights, designs and trade secrets. All rights reserved. © 2022 NXP B.V.Document Number: SJA1110AUTESFS REV 1NETWORKING APPLICATIONS • Optimized NXP chipset solution with S32G processor enables unmatched routing, firewalling, intrusion/detection/prevention capabilities • Best-in-class TCAM-based frame inspection for IDPS support, DOS prevention and advanced frames management • BOM optimization features include compatibility with VR5510 PMIC, four pin-compatible variants and optimized cascaded configurationADAS APPLICATIONS• Functional safety-dedicated features improving ECU safety design • Safety manual enable optimized safety design up to ASIL-D ECUs • Automotive Grade 1 (-40 / +125° C) capability for optimized PCB design • High-SGMII count for EMC friendly design • Production-grade AUTOSAR drivers• Compatible with TTTEch ® MotionWise ® middleware INFOTAINMENT/CLUSTER APPLICATIONS• Multi-gigabit SGMII for external Gigabit and Multi-Gigabit PHYs • Autonomous operation support avoids dependency from untrusted external host • Avnu ®-Certified* AVB/gPTP stack for integrated controller• Support for Wake over Ethernet (OPEN TC10)• Integrated controller with programmable GPIOs。

DFM知识点培训教材

DFM 101 Part1 | Dec 2008 Celestica Confidential

DFM Checklist

DFM 101 Part1 | Dec 2008 Celestica Confidential

DFM Checklist Topics

• • • • • • • • • • • Data & History Components Process Flow PTH Assembly SMT Assembly Layout & Spacing Land Patterns Silkscreen Board Outline PCB Fabrication Drawing Mechanical Assembly (not covered in this session)

DFM 101 Part1 | Dec 2008 Celestica Confidential

DFM 101 Outline

After the session, attendees should be ablntify DFM violations in a customer’s design, using the DFM checklist and the PCA DFx Guide

DFM 101 Part1 | Dec 2008 Celestica Confidential

DFM Checklist

• The DFM Checklist is used to ensure that a comprehensive review is done, covering all important areas • Each item on the DFM Checklist should be verified on the design being reviewed, either using Valor automated analysis or by manual checking • The DFM Checklist is a tool to use during the review, it should NOT be included in the DFM Report given to the customer

Bi2Se3未考虑vdw的错误汇总

在没有考虑vdw作用之前,算Bi2Se3材料soc中出现的错误汇总1.I nternal内部的、内在的ERROR RSPHER:running out of buffer缓冲0 013 1 0nonlr.F:Out of buffer RSPHER.....ran an NPAR optimisation最优test and found that if NCPU is too high and NPAR too low the job will quit with ERROR RSPHER. On the other hand if NCPU is too low and NPAR too high the job will hang during iterations迭代次数and cease to停止write any output. There is an optimum value of NCPU/NPAR which can be determined by running a series of 1 or 2 hour jobs with NPAR=1,2,4,8,16,32 for a given number of CPUs. NPAR must always be a factor因子of NCPU and I believe optimum is usually close to NCPU/16, although this is probably cluster集群dependant相关、依赖and possibly also dependant on the type of calculation being performed.得到的CONTCAR是空文件:说明结构优化部分出现了问题。

2.Logscfrunning on 32 total coresdistrk: each k-point on 32 cores, 1 groupsdistr: one band on 32 cores, 1 groupsusing from now: INCARvasp.5.3.3 18Dez12 (build May 19 2015 15:36:57) complexLogbands...vasp.5.3.3 18Dez12 (build May 19 2015 15:36:57) complexPOSCAR found : 0 types and 0 ions对策1:修改KPOINTS 测试771 881 991 10101 11111对策2:修改NPAR=1,测试NPAR=1,2,3,4,5,6验证结果:修改NPAR=2,NPAR=4计算都没有出错,但算出来能带结构与文献不符:在此基础上,调整其他参数,得到正确的结果。

DFMS Presentation (NXPowerLite)

報廢品,不良品

生產能力

執行

Bottom Up(承上啟下)

控制

DFMS 現場管制

生產排配 現場資料收集

製程管控 品質管控 設備管理 WIP庫存管理 零件追蹤 即時監視 包裝出貨管控 資料分析 WEB Query

短期生產計劃 生產分析報表 生產優化運行參數

設備運行參數 物料使用狀態

管理

DB安全管控

1. 數據庫系統權限管控

管控前

管控后

應用範圍

由於程序員或非DBA管理人員 擅自更改數據庫系統結構或 Procedure,Trigger,Table等造 成的DB問題幾乎每月1-2次

管控后的數據庫系統沒有因爲 非管理人員更改或刪除物件引 起異常

應用于 DMD(I) ,DMD(II) ,ASD, EPD, DT2 等單位

堆積停線 一個小時5pcs不良

MSD超時停線

超過管控時間

錫膏靜止超時

錫膏在鋼板上靜止超過30分

PCB開封超過48H(Server專用)

PCB 開封超時管控

回焊爐前超時

到達爐前超過2小時

系統自 動停線

良率低於標準良率停線

NO

停線類型

1 FVS良率過低停線

2 ICT良率過低停線

3 反面API DPPM過高停線

❖維修系統的建置,可以省去維修人員的填表作業 ❖累積過去的維修記錄並予以統計分析 ❖對於新手亦可以最短的時間內維修不良品 ❖將不良原因和零件回饋給上層決策者 ❖可指定維修站之維修人員及線別

❖可新增、刪除不良現象;針對某一不良現象可 新增、刪除、修改維修記錄

元件追蹤系統基本原理

基本原理

先上料

电子论文-DFM在Foundry的解决方案- 通过Calibre LFD工具有效优化库单元设计

DFM在Foundry的解决方案- 通过Calibre LFD工具有效优化库单元设计(1)中芯国际集成电路制造有限公司王谨恒(1),刘庆炜(1)1.引言即使飚升的设计和制造成本也无法阻挡半导体制造向90nm以及更先进工艺进军的步伐,伴随着这一进程的不断加快,可制造性设计(Design for Manufactory)正在成为目前业界最为热门的话题之一。

横亘在生产和设计之间的鸿沟一直都是半导体产业普遍存在的问题。

1.0微米时代,技术人员引入了“设计规则”的概念,随着技术的发展,为了尽可能地利用每一家代工企业的制造能力,开始出现定制化的设计规则。

但这依然无法解决时序(Timing)问题,于是SPICE模型又随之出现。

设计规则和SPICE模型可以看作是晶圆代工企业为了提高良率而向芯片设计者提供的优化信息。

我们同样可以从这个角度来看待DFM。

一直以来,当芯片设计者完成了芯片的设计后,接下来的芯片的实际制造工作是完全由晶圆代工厂来完成,芯片生产者并不会直接参与到芯片的制造过程中。

然而随着半导体制程和工艺复杂度的增加,以前根本无需理会的问题在日趋先进的工艺下变得越来越严重了。

比如在0.25微米时代,一个部位少堆叠100个原子对器件电气特性的影响甚微,但是90nm工艺下,可能该部位本身只有1000个原子的厚度,高达10%的物理尺寸误差对电气特性的影响将是巨大的。

而在芯片设计的过程中,同样也会引入一些问题,最终成为提升芯片良率的限制。

随着这样的问题越来越突出,芯片设计者,芯片制造者以及电子设计自动化工具(EDA)供应商开始致力于合作开发可制造性设计的方法,并以之来构架更为合理和高效的工艺流程和解决方案,以期达到更高更稳定的芯片生产良率。

业界普遍认为,从90nm工艺开始,DFM将会和设计规则、SPICE模型一起成为半导体技术的一部分,如果芯片代工厂无法向芯片设计者提供这些信息,设计师在芯片设计工作中会遇到许多意想不到的问题,从而导致芯片从开发到进入市场的整个周期延长。

苹果塑胶件开发以及DFM模具检讨报告范本(英文)

3 - Parting Line Details

• Main parting line (core to cavity) see picture • Action witness line (slides, lifters etc.) see picture • Any sub-insert line (stationary) see page11&12

817-01080

2015. 09.10

02

2015.0 9.10

02

2015. 09.14

01

1/25/2013

MD Plastic Tooling - Apple Confidential

1 - Project Overview

• Supplier Name and Location XuHong Kunshan

- When saving the DFM please save in format: Program Vendors Part Name APN Stage Cavity DFM Rev (Date).ppt

Example: REAR VENT,INSERTMOLDED,MP INTENT,X577 817-01080-02 EVT1 1-cav DFM01 ( 14 Sep 15 ).ppt

Section

Completed Y/N

Section

Completed Y/N

Section

Completed Y/N

Table Of Contents

Revision History

Project Overview Draft

Canon 打印机维修手册说明书

2.Reconnect the residual-toner feed motor connector J63 and connector J155 on the DC controller PCA.3.Perform the TCU Motor test. Under Diagnostics/Component Test, select TCU Motor and press OK. If this testfails, replace the Residual Toner Feed Motor, part number RM1-5605-000CN.4.If the issue persists, check the gears and ducting of the Waste Toner Paper Feed assembly. If the gears are wornout, replace this component, part number RM1-5584-000CN.top59.C0 ErrorDescriptionDeveloper disengaging (alienation) motor rotation errorRecommended action1.Reconnect intermediate connector J87 of the developing disengagement sensor (SR11), connector J112 on theDC controller PCA, connector J38 of the developing disengagement motor, and the connector J261 on the high-voltage power supply D PCA.2.Run the manual sensor test to verify that the developing disengagement sensor (SR11) is functioning properly.NOTE: SR11 cannot be manually toggled. See Service Manual, Chapter "Manual sensor test (special-modetest)" for instructions.If it is not, replace the main-drive assembly.3.Run the component test for the developing disengagement (alienation) motor (M10) to verify that thedisengagement mechanism is functioning properly. If it is not, replace the developing disengagement motor(M10).top59.F0 ErrorDescriptionA 59.F0 error message is displayed on control panel when the product boots up.CauseThis behavior is primarily caused by a transfer alienation failure in which the ITB is stuck and unable to rotate or because the SR9 sensor (the primary transfer-roller-disengagement sensor aka Sensor K) has gone bad.Recommended actionUpdate to the latest available firmware at .If the issue persists, reseat the ITB, check the connections, perform manual and diagnostic flag and sensor tests, test the fuser motor, and then test the alienation mechanism:1.Reseat the ITB.2.Check the connections to primary transfer-roller-disengagement sensor (SR9 at connector J19) and to the DCcontroller PCA (connector J128).3.If the issue persists, remove the ITB completely from the unit and manually test the ITB gear and flag.1.Rotate the gear and check that the flag actuates when the white gear is turned.Figure 13: Rotate the ITB gear to actuate the ITB flagFigure 14: Flag moving as gear rotatesIf the ITB flag is broken or damaged, or if the flag does not move, replace the ITB.4.If the ITB gear and flag are working properly, test Sensor SR9 by using the MANUAL SENSOR TEST andmanually testing the SR9 flag.1.Remove the ITB if it has been re-installed and locate Sensor SR9 inside the ITB cavity.Figure 15: Primary transfer-roller-disengagement sensor SR9 (Sensor K)2.On the control panel, press the Home button, press the down arrow to highlight the DIAGNOSTICSmenu and press OK, and then select MANUAL SENSOR TEST and press OK.3.From inside the ITB cavity, press up and then release the SR9 flag to actuate the sensor.Figure 16: Manually activating Flag to actuate Sensor SR94.While pressing and releasing the flag, check the control panel display for sensor response (under K) andconfirm that the sensor toggles between 0 and 1 (0 is the normal state).5.If the value does not toggle between 0 and 1, replace the sensor (WG8-5696-000CN).NOTE: To stop the diagnostic, press OK, select EXIT DIAGNOSTICS, and then press OK.5.If Sensor SR9 is working properly, perform a fuser motor (M2) COMPONENT TEST.1.Remove the Fuser.2.Defeat the right door safety switch (upper left area) by inserting a stiff or folded piece of paper anddefeat the right door logic switch (right side below fuser) by using masking tape to hold switch down.3.On the control panel, press the Home button, press the down arrow to highlight the DIAGNOSTICSmenu and press OK, select COMPONENT TEST and press OK, and then select FUSER MOTOR andpress OK.4.During the test, observe the fuser motor gear.5.If the test fails or the fuser motor gear does not rotate, replace the fuser motor (M2).NOTE: To exit the diagnostic, select EXIT DIAGNOSTICS and then press OK.6.If the fuser motor is working properly, perform an ITB Contact/ Alienation Test.NOTE: This test activates the fuser motor (M2) and primary transfer solenoid (SL1) to cycle through the ITBalienation stages.1.Defeat the right door safety switch (upper left area) by inserting a stiff/folded piece of paper and thendefeat right door logic switch (right side below fuser) by use masking tape to hold switch down.2.On the control panel, press the Home button, press the down arrow to highlight the DIAGNOSTICSmenu and press OK, select COMPONENT TEST and press OK, and then select ITB Contact/ AlienationTest and press OK.3.During the test, observe the alienation drive hub located above the cyan cartridge.4.If the test fails or the alienation drive hub does not rotate, replace the fuser-drive assembly.NOTE: To exit the diagnostic, select EXIT DIAGNOSTICS and then press OK.7.Check the connections again to the primary-transfer disengagement sensor J19 and to the connector J128 on theDC controller PCA before reinstalling the ITB.8.Remove any items used to defeat the right door switches, reinstall the ITB and any other components removedduring testing.9.If the error still persists, replace the DC Controller.top60.02 ErrorDescriptionTray 2 is not lifting correctly.。

ZUKEN ADM_DFM讲义

DFM (Design For Manufacturability 可制造性设计)修板和返工因为设计的缺陷而不可避免!大大增加了设计总成本、并无法保证设计时限。

另外,由于产品竞争压力的加大、环境规制、全球化生产的要求,使得设计变得越来越困难。

P l a c e m e n tI m p o r t O u t l i n eW i r i n gS o l d e r R e s i s tA s s i g n C o m p o n e n tI n p u t C i r c u i tOK当前设计流程的问题–为什么必须使用DFMManual CheckManufacture / Assembling因设计不周而引起的加工、装配问题往往在生产环节才能发现!唯一的出路:DFM设计前移PCB 加工与装配缺陷!P l a c e m e n tI m p o r t O u t l i n eW i r i n gS o l d e r R e s i s tA s s i g n C o m p o n e n tI n p u t C i r c u i tOKManual CheckManufacture / Assembling人工检查的低效、知识经验储备不足!当前设计流程的问题–DFM的瓶颈:人工检查的局限性用人的目视方法去检查PCB的设计问题,工作量相当大,缺陷检查的遗漏不可避免信息的传达方法低效(基本用传统纸质方式)信息传达的手段落后也必然造成内容损失和偏差,很难共享企业Know-How,相同的问题可能反复重现“设计完成后再检查” 实在太慢有些缺陷根本没办法到设计完成后来纠正!设计返工不可避免!这样设计时限无法保证。

如何跨越以上DFM 设计的瓶颈呢?DFM 的典型瓶颈:P l a c e m e n tI m p o r t O u t l i n eW i r i n gS o l d e r R e s i s tA s s i g n C o m p o n e n tI n p u t C i r c u i tOKManufacture /AssemblingM a n u a l C h e c kOK !A s s i g n C o m p o n e n tI n p u t C i r c u i tP l a c e m e n tI m p o r t O u t l i n eW i r i n g S o l d e r R e s i s tManufacture / Assembling设计流程的改进–如何有效进行DFM 设计A D MA D MA D MADM System边设计边检查设计检查前移将尽早发现问题、解决问题于前端,避免设计完成再检查出问题是很难纠正。

安特尔AT24C32D 32K Serial EEPROM数据手册说明书

AT24C32DI2C-Compatible (2-Wire) Serial EEPROM32-Kbit (4,096 x 8)DATASHEET Features●Low-voltage and Standard-voltage OperationV CC = 1.7V to 5.5V●Internally Organized as 4,096 x 8 (32K)●I2C-compatible (2-Wire) Serial Interface●Schmitt Trigger, Filtered Inputs for Noise Suppression●Bidirectional Data Transfer Protocol●400kHz (1.7V) and 1MHz (2.5V, 2.7V, 5.0V) Compatibility●Write Protect Pin for Hardware Protection●32-byte Page Write ModePartial Page Writes Allowed●Self-timed Write cycle (5ms Max)●High ReliabilityEndurance: 1,000,000 Write CyclesData Retention: 100 Years●Lead-free/Halogen-free devices Available●Green Package Options (Pb/Halide-free/RoHS Compliant)8-lead JEDEC SOIC, 8-lead TSSOP, 8-pad UDFN, 8-pad XDFN, 5-leadSOT23, 5-ball WLCSP, and 8-ball VFBGA packages●Die Sale Options: Wafer Form, Waffle Pack, and Bumped Wafers DescriptionThe Atmel® AT24C32D provides 32,768 bits of Serial Electrically Erasable and Programmable Read-Only Memory (EEPROM) organized as 4,096 words of 8 bits each. The device’s cascading feature allows up to eight devices to share a common 2-wire bus. The device is optimized for use in many industrial and commercial applications where low-power and low-voltage operation are essential. The devices are available in space-saving 8-lead JEDEC SOIC, 8-lead TSSOP, 8-pad UDFN, 8-pad XDFN, 5-lead SOT23, 5-ball WLCSP, and 8-ball VFBGA packages. In addition, this device operates from 1.7V to 5.5V.AT24C32D [DATASHEET]Atmel-8866D-SEEPROM-AT24C32D-Datasheet_12201621.Pin Configurations and PinoutsTable 1-1.Pin Configuration Note:When using the 5-lead SOT-23 or the 5-ball WLCSP , the software bits A2, A1, and A0 must be set to Logic 0 to properly communicate with the device.2.Absolute Maximum Ratings*8-pad UDFN/XDFNV CC WP SCL SDAA 0A 1A 2GND123487658-ball VFBGABottom View8-lead SOIC8-lead TSSOPTop View12348765A 0A 1A 2GNDV CC WP SCL SDATop View Top ViewA 0A 1A 2GND V CC WP SCL SDA87651234SCL GND SDA123545-lead SOT23WPV CC* Note: Drawings are not to scale5-ball WLCSPBall Side View(1)A 0A 1A 2GNDV CC WP SCL SDA12348765(1)Operating Temperature . . . . . . . . . . .-55°C to +125°C Storage Temperature . . . . . . . . . . . . -65°C to + 150°C Voltage on any pinwith respect to ground . . . . . . . . . . . . . . .-1.0 V +7.0V Maximum Operating Voltage . . . . . . . . . . . . . . . 6.25V DC Output Current. . . . . . . . . . . . . . . . . . . . . . .5.0mA*Notice:Stresses beyond those listed under “AbsoluteMaximum Ratings” may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of this specification are not implied. Exposure to absolute maximum rating conditions forextended periods may affect device reliability.3AT24C32D [DATASHEET]Atmel-8866D-SEEPROM-AT24C32D-Datasheet_1220163.Block Diagram4.Pin DescriptionsSerial Clock (SCL): The SCL input is used to positive-edge clock data into each EEPROM device and negative-edge clock data out of each device.Serial Data (SDA): The SDA pin is bidirectional for serial data transfer. This pin is open drain driven and may be wire-ORed with any number of other open-drain or open-collector devices.Device Addresses (A 2, A 1, A 0): The A 2, A 1, and A 0 pins are device address inputs that are hard wired (directly to GND or to V CC ) for compatibility with other Atmel AT24C devices. When the pins are hard wired, as many as eight 32K devices may be addressed on a single bus system. (Device addressing is discussed in detail in Section 7., “Device Addressing” on page 9). A device is selected when a corresponding hardware and software match is true. If these pins are left floating, the A 2, A 1, and A 0 pins will be internally pulled down to GND. However, due to capacitive coupling that may appear during customer applications, Atmel recommends always connecting the address pins to a known state. When using a pull-up resistor, Atmel recommends using 10k Ω or less.Write Protect (WP): The Write Protect input, when connected to GND, allows normal write operations. When WP is connected directly to V CC , all Write operations to the memory are inhibited. If the pin is left floating, the WP pin will be internally pulled down to GND; however, due to capacitive coupling that may appear during customerapplications, Atmel recommends always connecting the WP pins to a known state. When using a pull-up resistor, Atmel recommends using 10k Ω or less.Table 4-1.Write ProtectV CC GND WP SCL SDAA 2A 1A 0AT24C32D [DATASHEET]Atmel-8866D-SEEPROM-AT24C32D-Datasheet_12201645.Memory OrganizationAT24C32D, 32K Serial EEPROM : The 32K is internally organized as 128 pages of 32-bytes each. Random word addressing requires a 12-bit data word address.5.1Pin CapacitanceTable 5-1.Pin Capacitance (1)Note:1.This parameter is characterized and is not 100% tested.5.2DC CharacteristicsTable 5-2.DC CharacteristicsNote:1.V IL min and V IH max are reference only and are not tested.Applicable over recommended operating range from: T A = 25°C, f = 1.0MHz, V CC = 5.5V.Applicable over recommended operating range from: T AI = -40°C to +85°C, V CC = 1.7V to 5.5V (unless otherwise noted).5AT24C32D [DATASHEET]Atmel-8866D-SEEPROM-AT24C32D-Datasheet_1220165.3AC CharacteristicsTable 5-3.AC Characteristics (Industrial Temperature)Notes:1.This parameter is ensured by characterization and is not 100% tested.2.AC measurement conditions:●R L (connects to V CC ): 1.3k Ω (2.5V, 5.5V), 10k Ω (1.7V)●Input pulse voltages: 0.3V CC to 0.7V CC ●Input rise and fall times: ≤ 50ns ●Input and output timing reference voltages: 0.5 x V CCApplicable over recommended operating range from: T AI = -40°C to +85°C, V CC = 1.7V to 5.5V, CL = 100pF (unless otherwise noted). Test conditions are listed in Note 2.AT24C32D [DATASHEET]Atmel-8866D-SEEPROM-AT24C32D-Datasheet_12201666.Device OperationClock and Data Transitions: The SDA pin is normally pulled high with an external device. Data on the SDA pin may change only during SCL low time periods. Data changes during SCL high periods will indicate a Start or Stop condition as defined below.Figure 6-1.Data ValidityStart Condition : A high-to-low transition of SDA with SCL high is a Start condition that must precede every command.Stop Condition: A low-to-high transition of SDA with SCL high is a Stop condition. After a Read sequence, the Stop condition will place the EEPROM in a standby power mode.Figure 6-2.Start Condition and Stop Condition DefinitionSDASCLData ChangeData StableData StableSDASCLStart Condition Stop Condition7AT24C32D [DATASHEET]Atmel-8866D-SEEPROM-AT24C32D-Datasheet_122016Acknowledge: All addresses and data words are serially transmitted to and from the EEPROM in 8-bit words. The receiving device sends a zero during the ninth clock cycle to acknowledge that it has received each word. This zero response is referred to as an Acknowledge.Figure 6-3.Output AcknowledgeStandby Mode: AT24C32D features a low-power standby mode that is enabled upon power-up and after the receipt of the Stop condition and the completion of any internal operations.Software Reset : After an interruption in protocol, power loss or system reset, any 2-wire part can be protocol reset by following these steps:1.Create a Start condition (if possible).2.Clock nine cycles.3.Create another Start condition followed by Stop condition as shown below.The device should be ready for the next communication after above steps have been completed. In the event that the device is still non-responsive or remains active on the SDA bus, a power cycle must be used to reset the device.Figure 6-4.Software ResetSCLData InData OutStart ConditionAcknowledge981SCLSDAAT24C32D [DATASHEET]Atmel-8866D-SEEPROM-AT24C32D-Datasheet_1220168Figure 6-5.Bus TimingFigure 6-6.Write Cycle TimingNote: 1.The Write cycle time t WR is the time from a valid Stop condition of a Write sequence to the end ofthe internal Clear/Write cycle.SCLSDA InSDA OutSCLSDAStop ConditionStart Condition9AT24C32D [DATASHEET]Atmel-8866D-SEEPROM-AT24C32D-Datasheet_1220167.Device AddressingThe 32K EEPROM requires an 8-bit device address word following a Start condition to enable the chip for a Read or Write operation. The device address word consists of a mandatory ‘1010’ sequence for the first four most significant bits which is known as the device type identifier. These four bits are bit 7, bit 6, bit 5, and bit 4 as seen in Figure 7-1. This is common to all 2-wire Serial EEPROM devices.The next three bits are the A2, A1, and A0 hardware address select bits which allow as many as eight devices on the same bus. These bits must compare to their corresponding hard wired input pins, A 2, A 1, and A 0. The A 2, A 1, and A 0 pins use an internal proprietary circuit that biases them to a logic low condition if the pins are allowed to float.When utilizing the 5-ball WLCSP or the 5-lead SOT-23 packages, the A 2, A 1, and A 0 pins are not available. The A 2, A 1, and A 0 pins are internally pulled to ground and thus the A2, A1, and A0 device address bits must always be set to a Logic 0 to communicate with the device. This condition is depicted in Figure 7-1 below.The eighth bit of the device address is the Read/write operation select bit. A Read operation is initiated if this bit is a Logic 1, and a Write operation is initiated if this bit is a Logic 0.Upon a successful comparison of the device address, the EEPROM will output a zero during the following clock cycle. If a compare is not made, the device will not acknowledge and will instead return to a standby state.Figure 7-1.Device AddressingData Security: The AT24C32D has a hardware data protection scheme that allows the user to write protect the whole memory when the WP pin is at V CC .AT24C32D [DATASHEET]Atmel-8866D-SEEPROM-AT24C32D-Datasheet_122016108.Write OperationsByte Write : A Write operation requires two 8-bit data word addresses following the device address word and acknowledgment. Upon receipt of this address, the EEPROM will again respond with a zero then clock in the first 8-bit data word. Following receipt of the 8-bit data word, the EEPROM will output a zero. The addressing device, such as a microcontroller, must then terminate the write sequence with a Stop condition. At this time, the EEPROM enters an internally-timed Write cycle, t WR , to the nonvolatile memory (See Figure 6-6). All inputs are disabled during this Write cycle and the EEPROM will not respond until the Write is complete.Figure 8-1.Byte WriteNote:* = Don’t care bit.Page Write: The 32K EEPROM is capable of 32-byte Page Writes.A Page Write is initiated the same way as a Byte Write, but the microcontroller does not send a Stop condition after the first data word is clocked in. Instead, after the EEPROM acknowledges receipt of the first data word, the microcontroller can transmit up to 31 more data words. The EEPROM will respond with a zero after each data word received. The microcontroller must terminate the Page Write sequence with a Stop condition.The data word address lower five bits are internally incremented following the receipt of each data word. The higher data word address bits are not incremented, retaining the memory page row location. When the word address, internally generated, reaches the page boundary, the following byte is placed at the beginning of the same page. If more than 32 data words are transmitted to the EEPROM, the data word address will roll-over and the previously loaded data will be altered. The address roll-over during Write is from the last byte of the current page to the first byte of the same page.Figure 8-2.Page WriteNote:* = Don’t care bit.Acknowledge Polling : Once the internally-timed Write cycle has started and the EEPROM inputs are disabled, acknowledge polling can be initiated. This involves sending a Start condition followed by the device address word. The Read/Write bit is representative of the operation desired. Only if the internal Write cycle has completed will the EEPROM respond with a zero, allowing the Read or Write sequence to continue.S T A R TW R I T ES T O PDevice Address FirstWord Address Second Word AddressDataSDA LineM S BA C KR /W A C KA C KA CKSDA LineS T A W R I BK/W KKKKS T9.Read OperationsRead operations are initiated the same way as Write operations with the exception that the Read/Write select bit in the device address word is set to one. There are three Read operations:●Current Address Read ●Random Address Read ●Sequential ReadCurrent Address Read : The internal data word address counter maintains the last address accessed during the last Read or Write operation, incremented by one. This address stays valid between operations as long as the chip power is maintained. The address roll-over during read is from the last byte of the last memory page, to the first byte of the first page.Once the device address with the Read/Write select bit set to one is clocked in and acknowledged by theEEPROM, the current address data word is serially clocked out. The microcontroller does not respond with an zero but does generate a Stop condition.Figure 9-1.Current Address ReadRandom Read: A Random Read requires a dummy Byte Write sequence to load in the data word address. Once the device address word and data word address are clocked in and acknowledged by the EEPROM, the microcontroller must generate another Start condition. The microcontroller now initiates a Current Address Read by sending a device address with the Read/write select bit high. The EEPROM acknowledges the device address and serially clocks out the data word. The microcontroller does not respond with a zero but does generate a Stop condition.Figure 9-2.Random ReadNote:* = Don’t care bit.SDA LineS T A R TDevice AddressR E A DS T O PM S BA C KR /W N O A C KDataSDA LINES T A R TS T A R TR E A DW R I T ES T O PDevice Address Second Word Address Device AddressFirst Word Address Data (n)M S BA C KA C KAC KL S B A C KN O A C KR /W Dummy WriteR /W12Sequential Read: Sequential Reads are initiated by either a Current Address Read or a Random Address Read. After the microcontroller receives a data word, it responds with an acknowledge. As long as the EEPROM receives an acknowledge, it will continue to increment the data word address and serially clock out sequential data words. When the memory address maximum address is reached, the data word address will roll-over and the Sequential Read will continue from the beginning of the array. The Sequential Read operation is terminated when the microcontroller does not respond with a zero but does generate a Stop condition.Figure 9-3.Sequential ReadNote:* = Don’t care bit.SDA LINESTARTSTARTREADWRITESTOP DeviceAddressSecond WordAddressDeviceAddressFirst WordAddressData (n + 1)Data (n + 2)Data (n + x)Data (n)MSBACKACKACKLSBACKACKACKACKNOACKR/WDummy Write. . .. . .R/AT24C32D [DATASHEET]10.Ordering Code DetailAtmel DesignatorProduct FamilyDevice DensityDevice RevisionShipping Carrier OptionOperating VoltagePackage Option32 = 32K24C = Standard I 2C-compatibleSerial EEPROMB = Bulk (Tubes)T = Tape and Reel, Standard Quantity Option E = Tape and Reel, Expanded Quantity OptionM = 1.7V to 5.5VSS = JEDEC SOIC X = TSSOP MA = UDFN ME = XDFN ST = SOT23U = 5-ball, 3x3 Grid Array, WLCSP C = VFBG A WWU = Wafer UnsawnWDT = Die in Tape and ReelPackage Device Grade or Wafer/Die ThicknessH = Green, NiPdAu Lead Finish, Industrial Temperature Range (-40°C to +85°C)U = Green, Matte Sn Lead Finish or SnAgCu Solder Ball Finish, Industrial Temperature Range (-40°C to +85°C)11= 11mil Wafer ThicknessA T 24C 32D -S S H M -TAT24C32D [DATASHEET]1411.Part MarkingsNotes: 1.WLCSP Package: CAUTION: Exposure to ultraviolet (UV) light can degrade the data stored in the EEPROM cells. Therefore, customers who use a WLCSP product must ensure that exposure to ultraviolet lightdoes not occur.2.Contact Atmel Sales for Wafer sales.13.18S1 — 8-lead JEDEC SOICAT24C32D [DATASHEET]1613.28X — 8-lead TSSOP13.38MA2 — 8-pad UDFNAT24C32D [DATASHEET] 1813.48ME1 — 8-pad XDFNAT24C32D [DATASHEET]2013.55TS1 — 5-lead SOT2321AT24C32D [DATASHEET]Atmel-8866D-SEEPROM-AT24C32D-Datasheet_12201613.65U-3 — 5-ball, WLCSPAT24C32D [DATASHEET]Atmel-8866D-SEEPROM-AT24C32D-Datasheet_1220162213.78U2-1 — 8-ball VFBGA23AT24C32D [DATASHEET]Atmel-8866D-SEEPROM-AT24C32D-Datasheet_12201614.Revision HistoryX X X X X XAtmel Corporation1600 Technology Drive, San Jose, CA 95110 USAT: (+1)(408) 441.0311F: (+1)(408) 436.4200|© 2015 Atmel Corporation. / Rev.: Atmel-8866D-SEEPROM-AT24C32D-Datasheet_122016.Atmel ®, Atmel logo and combinations thereof, Enabling Unlimited Possibilities ®, and others are registered trademarks or trademarks of Atmel Corporation in U.S. and other countries. Other terms and product names may be trademarks of others.DISCLAIMER: The information in this document is provided in connection with Atmel products. No license, express or implied, by estoppel or otherwise, to any intellectual property right is granted by this document or in connection with the sale of Atmel products. EXCEPT AS SET FORTH IN THE ATMEL TERMS AND CONDITIONS OF SALES LOCATED ON THE ATMEL WEBSITE, ATMEL ASSUMES NO LIABILITY WHATSOEVER AND DISCLAIMS ANY EXPRESS, IMPLIED OR STATUTORY WARRANTY RELATING TO ITS PRODUCTS INCLUDING, BUT NOT LIMITED TO, THE IMPLIED WARRANTY OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, OR NON-INFRINGEMENT. IN NO EVENT SHALL ATMEL BE LIABLE FOR ANY DIRECT, INDIRECT, CONSEQUENTIAL, PUNITIVE, SPECIAL OR INCIDENTAL DAMAGES (INCLUDING, WITHOUT LIMITATION, DAMAGES FOR LOSS AND PROFITS, BUSINESS INTERRUPTION, OR LOSS OF INFORMATION) ARISING OUT OF THE USE OR INABILITY TO USE THIS DOCUMENT, EVEN IF ATMEL HAS BEEN ADVISED OF THE POSSIBILITY OF SUCH DAMAGES. Atmel makes no representations or warranties with respect to the accuracy or completeness of the contents of this document and reserves the right to make changes to specifications and products descriptions at any time without notice. Atmel does not make any commitment to update the information contained herein. Unless specifically provided otherwise, Atmel products are not suitable for, and shall not be used in, automotive applications. Atmel products are not intended,authorized, or warranted for use as components in applications intended to support or sustain life.SAFETY-CRITICAL, MILITARY, AND AUTOMOTIVE APPLICATIONS DISCLAIMER: Atmel products are not designed for and will not be used in connection with any applications where the failure of such products would reasonably be expected to result in significant personal injury or death (“Safety-Critical Applications”) without an Atmel officer's specific written consent. Safety-Critical Applications include, without limitation, life support devices and systems, equipment or systems for the operation of nuclear facilities and weapons systems.Atmel products are not designed nor intended for use in military or aerospace applications or environments unless specifically designated by Atmel as military-grade. Atmel products are not designed nor intended for use in automotive applications unless specifically designated by Atmel as automotive-grade.。

DFM-B 引导驱动模块说明书

Guided drive module DFM-BFlexible & dynamic!High load capacityAdjustable end positionPneumatic cushioning121.1.PSIProduct Short InformationDFM-BMaximum speed v max.= 1.5 m/s.Pneumatic end position cushion-ing or integrated shock absorbers facilitate almost 100 % greater speed and an endposition accura-cy of less than 0.05 mm.Precision stroke adjustmentin retracted and advanced position with two bearings per guide rod for better guiding accuracy and operating behaviour without the need for expensive in-house con-structions.DFM & DFM-BCompact dimensionsHigh-precision guidance and excellent absorption of torque loads and lateral forces.Sturdy designWith drive and guide unit in one housing, with either plain bearing guide or ball-bearing guide plus a wide variety of mounting options.Alternative air connections For greater flexibility together with standardised proximity sensors of type SM..-8.Incredible load capacities, excellent guidance and all in a modular format – that’s the DFM-B. Reliable, flexible and resilient – even with high torque loading.DFM-B with shock absorber for even heavier loads and higher speedsDFM-B as long-stroke variant up to 400 mmOther variants•Heat-resistant design •X strokes•Customer-specific variants in stainless steel or ascylinder/valve combinationsDFM-B with adjustable end position: •Retracted •Advanced•Retracted and advancedDFM-B with pneumatic:end-position cushioning for heavy loads and high speedsFesto AG &Co.KGRuiter Strasse 82D-73734 EsslingenInternet Tel. ++49 (0)711 347-0 Fax ++49 (0)711 347-2144E-mail service_international@160206S u b j e c t t o c h a n g eGuided drive module DFM-B*Tested representatively and certified for the products ADVU, DGPL and DNC.Overview of series, variants and functionsFFMVariantsCushioning•Pneumatic cushioning •Flexible cushioning•Shock absorber at both endsPosition sensing•Contactless sensing of the piston position using SM..-8 standard proximity sensors •Sensing option on both sides thanks to double slotGuide•Plain bearing guide •Ball-bearing guide。

signaltek nt 用户指南说明书

SignalTEK NT 用户指南

156875 第 3 版 第5页

电源

SignalTEK NT 可采用以下电源:

可充电电源模块。 连接到电源模块内置 DC 插口的直流电源。 电源模块管理

充满电的电源模块将支持最长五小时的高强度、连续使用。为最大限度地延长电源模块的使用寿命,建议每 月至少进行一次完全放电后再完全充电。

弃置

当 SignalTEK NT 已达到使用寿命时,您必须依照当地的环境法规完全弃置这两个设备。

电源模块第一次使用必须完全充电后才能用它

安全信息

使用 SignalTEK NT 时,请务必采取基本的安全防护措施,降低火灾、电击和人员受伤的风险。这些措施包括: 连接到线缆时,必须特别小心,因为线缆上可能存在高压,并且可能存在触电死亡的危险。 避免在暴风雨天气下使用 SignalTEK NT - 存在被闪电击中的风险。 只使用您的 SignalTEK NT 随附的交流电源适配器。 1 类激光产品。来自光纤端口的光输出虽然不可见,但可能会损害视力。切勿直接凝视打开的光链路端口或 光纤末端确认是否有光线射出。 连接器安全性 以下连接器符合 EN60950 SELV 安全规范: RJ-45 以太网端口。 USB 端口。 DC 插口。

用户不可自行维修电源模块。当它达到使用寿命时,请联系您当地的 IDEAL 代表进行更换。

电源模块充电

电源模块可在 SignalTEK NT(任一设备)开启或关闭的情况下在三小时内充满。要对电池模块充电,将随 附的电源适配器连接到 DC 插口。为方便起见,充电时可将电源模块取出或继续连接到设备上。DC 插口旁 的电源 LED 灯发出绿光,表明电池正在充电,绿灯闪烁时表明未充电。

维克ト恩能源生产力系统配置助手说明书

Overview of available AssistantsClick on the thumbnails to see the full screenshot.1. Assistants related to SolarMake sure to read Configuring solar systems with Quattros and Multis when configuring a solar system.ESS AssistantFor Energy Storage Systems (ESS). The Assistant manages the prioritising of Solar Power. Documentation.PV Inverter supportUse this Assistant in Off-grid systems that have AC-Coupled solar power: a grid-tie PV inverter connected to the AC out of a Multi or Quattro inverter/charger.Documentation.DEPRECATED Self-consumption Hub-1 - for dc-coupled systems2022-06-01assistants:overview_of_available_assistants https:///live/assistants:overview_of_available_assistants 13:41Note that Hub-1 is deprecated in favor of ESS.Hub-1 Assistant documentation.Hub-1 is only for hardware with new microprocessor (26 or 27).Hub-1 and Hub-2 Assistant notesDEPRECATED Self-consumption Hub-2 v3 - for ac-coupled systemsTake note of the factor 1.0 rule.Deprecated in favor of ESS.Only for hardware with new microprocessor (26 or 27).Hub-1 and Hub-2 Assistant notesDEPRECATED Self-consumption Hub-2 v2 - for ac-coupled systemsUse only on hardware with old microprocessor (19 or 20). On newer systems, use the version 3 instead, see above.Take note of the factor 1.0 rule.Note that all Hub-2 Assistant versions have been deprecated in favor of ESS.Hub-1 and Hub-2 Assistant notesDEPRECATED Self-consumption Hub-4Do not use Hub-4 for new installs. It is deprecated in favor of ESS.Hub-4 manual.Only for hardware with new microprocessor (26 or 27).2. Functional AssistantsGenerator start and stopAutomatically start and stop a generator based on battery state of charge andactual load of a system. Note that automatic genset start/stop functionality isalso available on the Virtual switch tab in VEConfigure, which is easier to workwith.This is one of the available options to automatically start and stop a generator using Victron equipment. See the auto-generator-start-stop document for an overview of all options. More general information about using a generator in combination with Victron is available here.This Generator start and stop Assistant is also the one to use to configure Ignore AC Input using Assistants.AC Current sensor2022-06-01assistants:overview_of_available_assistants https:///live/assistants:overview_of_available_assistants 13:41Reads PV Inverter current, using an AC Current sensor (CSE000100000),connected to a VE.Bus product. More information available in the AC Currentsensor manual.Silence fanDisable the fans at night with a simple external switch, to ensure a quiet night.Very useful for boats and motorhomes.Input current limit controlAutomatically set the input current limit to a predefined value based on thestate of an aux input or rpm measured with the 1140 interface. Used in thefollowing systems:1.A variable speed generator, flywheel generator or waterturbine, where the available AC powerdepends on the rpm. See the Interface 1140 (ASS030510000) manual for more information.Vehicles or boats that have two different types of shore plugs. One high power plug and one low 2.power plug. Use the assistant to automatically set the input current limiter based on the used plug.And there are more situations that can come to mind, for example a Multi connected behind a 3.transfer switch.Charge current controlSets the charge current to a predefined setpoint, based on the active AC Input(for Quattros) or the state of an aux input.Safety switchUsed to wire an emergency stop button to a VE.Bus system. DEPRECATED VE.Bus BMS supportDeprecated: per VE.Bus firmware version 489, this Assistant is no longer required. When installing a system with VE.Bus BMS, our advice is to first update the firmware of the inverter, using VictronConnect, and thereafter do the configuration. No Assistant needed.Required in combination with a VE.Bus BMS, used with our 12.8 V Lithium batteries. This Assistant communicates with the BMS and controls the Multi based on the BMS measurements.Two-Signal BMS support (previously called Lynx Ion BMS support)Required in combination with a Lynx Ion BMS, used with our 24 V 180 AhLithium system. This Assistant can also be used to control the Multi with a thirdparty Lithium system including BMS. See our PDF Connecting other lithiumbattery systems to Multis and Quattros for more information.3. Advanced AssistantsProgrammable relay2022-06-01assistants:overview_of_available_assistants https:///live/assistants:overview_of_available_assistants 13:41Relay lockerGeneral flag userDISQUSView the discussion thread.。