AD8051_8052_8054

V8A02解决方案用户手册V2.1

V8A02解决方案用户手册V2.1目录1. 文档说明 (6)1.1版本说明 (6)1.2专有名词 (6)2. 方案简介 (8)2.1方案概述 (8)2.2 功能特点 (8)2.2.1 支持DVI数据源输入 (8)2.2.2 支持宽屏等多种DVI输入分辨率 (8)2.2.3 发送卡超大带载 (8)2.2.4 功能强大的配套软件 (8)2.2.5 智能在线检测 (8)2.2.6 高刷新频率 (8)2.2.7 高灰度等级 (9)2.2.8 支持各种像素类型 (9)2.2.9 灵活支持各种模组 (9)2.2.10 多样的端口设置功能 (9)2.2.11箱体色度调整 (9)2.2.12 逐点校正功能 (9)2.2.13 集成测试功能 (9)2.2.14 联机配置数据 (9)2.2.15 智能维修 (10)2.2.16 环路备份功能 (10)2.2.17 在线升级固件安全可靠 (10)2.2.18 支持低电压输入 (10)2.2.19 配备指示灯及控制面板接口 (10)2.2.20 支持远距离传输 (10)2.2.21 支持音频传输及电源控制 (10)2.2.22 提供完整的二次开发接口 (10)2.2.24 支持内建PWM恒流 (10)2.2.25 支持低亮度高保真 (10)2.3产品清单 (11)3. 应用概述 (12)3.1 典型应用 (12)3.2 环路备份 (13)3.3 多发送卡 (14)4. 功能详解 (15)4.1 模组支持能力 (15)4.1.1 模组行、列数1~128以内任意 (16)4.1.2 模组数据类型 (16)4.1.3 模组内每扫描串移长度 (17)4.1.4 虚拟模组LED灯点位置多种排列方式 (17)4.2 箱体连接设置 (17)4.2.1 箱体内模组级联方式 (17)4.2.2 端口扩展 (18)4.2.3 端口对开 (19)4.2.4 端口逆序 (20)4.2.5 端口偏移 (20)4.2.6 箱体带载高度、宽度 (20)4.2.7 箱体显示起始的行、列位置 (21)4.2.8 箱体无信号输入时显示内容设置 (21)4.2.9 箱体级联数量 (21)4.2.10 箱体色度调整 (21)4.2.11 箱体逐点色度校正 (22)4.2.12 箱体测试功能 (22)4.3 屏体参数调节 (23)4.3.1 多个LED屏设置 (23)4.3.3 虚拟LED屏的实效果 (24)4.3.4 LED屏亮度调节 (25)4.3.5 LED屏对比度调节 (26)4.3.6 LED屏色温调节 (26)4.3.7 关闭LED屏显示 (27)4.3.8 锁定LED屏内容 (27)4.3.9 LED屏环境监控 (27)4.4 显示性能参数说明 (30)4.4.1 灰度等级 (30)4.4.2 刷新频率 (31)4.4.3 亮度效率 (31)4.4.4 最小OE (31)4.5 发送卡带载 (31)4.6 在线检测 (34)4.7 系统升级 (34)4.8 智能维修 (36)4.8.1 接收卡更换 (36)4.8.2模组替换 (37)5. 使用说明 (39)5.1 连接硬件 (39)5.1.1 发送卡安装方法 (39)5.1.2 接收卡安装方法 (39)5.1.3 多功能卡安装方法 (39)5.2 安装软件 (40)5.2.1 配置要求 (40)5.2.2 安装步骤 (40)5.3 系统设置 (40)5.3.1 显卡设置 (40)5.3.2系统设置 (43)6. 附录 (55)6.1 设备推荐型号 (55)6.1.1 DVI复制器 (55)6.2 选用线缆清单 (55)6.2.1 HDMI转DVI线缆 (55)6.2.2 音频线 (56)6.2.3 双绞线 (56)6.2.4 光纤 (56)1. 文档说明1.1版本说明版本日期说明V2.0 2013-01-09 升级自1.71版本V2.1 2013-07-15 新增接收卡产品1.2专有名词以下是本文中使用的专用术语及解释,便于读者更好的理解文章内容。●软件一系列按照特定顺序组织的计算机数据和指令的集合,本文中特指在计算机上运行的应用软件。

AD8052_datasheet

REV.BInformation furnished by Analog Devices is believed to be accurate and reliable. However, no responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices.aAD8051/AD8052/AD8054One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A.Tel: 781/329-4700World Wide Web Site: Fax: 781/326-8703© Analog Devices, Inc., 1999Low Cost, High Speed Rail-to-Rail Amplifiers CONNECTION DIAGRAMS(Top Views)FEATURESLow Cost Single (AD8051), Dual (AD8052) and Quad (AD8054)Voltage Feedback ArchitectureFully Specified at +3 V, +5 V and ؎5 V Supplies Single Supply OperationOutput Swings to Within 25 mV of Either Rail Input Voltage Range: –0.2 V to +4 V; V S = +5 V High Speed and Fast Settling on +5 V:110 MHz –3 dB Bandwidth (G = +1) (AD8051/AD8052)150 MHz –3 dB Bandwidth (G = +1) (AD8054)145 V/s Slew Rate50 ns Settling Time to 0.1%Small PackagingAD8051 Available in SOT-23-5AD8052 Available in SOIC-8AD8054 Available in TSSOP-14Good Video Specifications (G = +2)Gain Flatness of 0.1 dB to 20 MHz;R L = 150 ⍀0.03% Differential Gain Error;R L = 1K 0.03؇ Differential Phase Error;R L = 1K Low Distortion–80 dBc Total Harmonic @ 1 MHz, R L = 100⍀Outstanding Load Drive CapabilityDrives 45 mA, 0.5 V from Supply Rails (AD8051/AD8052)Drives 50 pF Capacitive Load (G = +1) (AD8051/AD8052)Low Power of 2.75mA/Amplifier (AD8054)Low Power of 4.4mA/Amplifier (AD8051/AD8052)APPLICATIONS Coax Cable Driver Active Filters Video Switchers A/D DriverProfessional Cameras CCD Imaging Systems CD/DVD ROMPRODUCT DESCRIPTIONThe AD8051 (single), AD8052 (dual) and AD8054 (quad) are low cost, voltage feedback, high speed amplifiers designed to operate on +3 V, +5 V or ±5 V supplies. They have true single supply capability with an input voltage range extending 200␣mV below the negative rail and within 1␣V of the positive rail.Despite their low cost, the AD8051/AD8052/AD8054 provide excellent overall performance and versatility. The output volt-age swing extends to within 25 mV of each rail, providing the maximum output dynamic range with excellent overdrive recov-ery. This makes the AD8051/AD8052/AD8054 useful for video electronics such as cameras, video switchers or any high speedportable equipment. Low distortion and fast settling make them ideal for active filter applications.The AD8051/AD8052/AD8054 offer low power supply cur-rent and can operate on a single +3 V power supply. These features are ideally suited for portable and battery powered applications where size and power are critical.The wide bandwidth and fast slew rate on a single +5 V supply make these amplifiers useful in many general purpose, high speed applications where dual power supplies of up to ±6 V and single supplies from +3 V to +12 V are needed.All of this low cost performance is offered in an 8-lead SOIC,along with a tiny SOT-23-5 package (AD8051), a µSOIC package (AD8052) and a TSSOP-14 (AD8054).FREQUENCY – MHz4.50500.11103.01.51.00.54.03.52.02.55.0P E A K -T O -P E A K O U T P U T V O L T A G E S W I N G(T H D Յ 0.5%) – V o l tsFigure 1.Low Distortion Rail-to-Rail Output SwingSOT-23-5 (RT)R-8, SOIC (RM)R-14, TSSOP-14 (RU-14)SO-8NC +V S V OUT NC–VOUT +V S –IN2–V+IN2–IN+IN SV –VS V++IN B OUT B+IN D V ؊+IN A OUT A ؊IN A ؊IN B IN C IN D–2–REV. BAD8051/AD8052/AD8054–SPECIFICATIONSAD8051A/AD8052A AD8054A ParameterConditionsMin TypMax MinTypMaxUnitsDYNAMIC PERFORMANCE –3 dB Small Signal Bandwidth G = +1, V O = 0.2 V p-p7011080150MHz G = –1, +2, V O = 0.2 V p-p 5060MHzBandwidth for 0.1 dB FlatnessG = +2, V O = 0.2 V p-p,R L = 150 Ω to +2.5 V,R F = 806Ω for AD8051A/AD8052A 20MHz R F = 200Ω for AD8054A12MHz Slew RateG = –1, V O = 2 V Step100145140170V/µs Full Power Response G = +1, V O = 2 V p-p 3545MHz Settling Time to 0.1%G = –1, V O = 2 V Step5040nsNOISE/DISTORTION PERFORMANCE Total Harmonic Distortion 1f C = 5 MHz, V O = 2 V p-p, G = +2–67–68dBInput Voltage Noise f = 10 kHz 1616nV/√Hz Input Current Noisef = 10 kHz850850fA/√Hz Differential Gain Error (NTSC)G = +2, R L = 150 Ω to +2.5 V 0.090.07%R L = 1k Ω to +2.5 V0.030.02%Differential Phase Error (NTSC)G = +2, R L = 150 Ω to +2.5 V 0.190.26Degrees R L = 1k Ω to +2.5 V 0.030.05Degrees Crosstalkf = 5 MHz, G = +2–60–60dBDC PERFORMANCE Input Offset Voltage1.710 1.712mV T MIN –T MAX2530mV Offset Drift1015µV/°C Input Bias Current 1.42.52 4.5µA T MIN –T MAX3.254.5µA Input Offset Current 0.10.750.2 1.2µA Open-Loop GainR L = 2 k Ω to +2.5 V 86988298dB T MIN –T MAX9696dB R L = 150 Ω to +2.5 V 76827482dB T MIN –T MAX7878dBINPUT CHARACTERISTICS Input Resistance 290300k ΩInput Capacitance1.41.5pF Input Common-Mode Voltage Range –0.2 to 4–0.2 to 4V Common-Mode Rejection Ratio V CM = 0 V to +3.5 V 72887086dBOUTPUT CHARACTERISTICS Output Voltage SwingR L = 10␣k Ω to +2.5 V 0.015 to 4.9850.03 to 4.975V R L = 2␣k Ω to +2.5 V 0.1 to 4.90.025 to 4.9750.125 to 4.8750.05 to 4.95V R L = 150 Ω to +2.5 V 0.3 to 4.6250.2 to 4.80.55 to 4.40.25 to 4.65V Output Current V OUT = 0.5 V to +4.5 V 4530mA T MIN –T MAX 4530mA Short Circuit Current Sourcing 8045mA Sinking13085mA Capacitive Load DriveG = +1 (AD8051/AD8052)50pF G = +2 (AD8054)40pFPOWER SUPPLY Operating Range312312V Quiescent Current/Amplifier 4.452.753.275mAPower Supply Rejection Ratio ∆V S = ±1 V70806880dB OPERATING TEMPERATURE RANGE –40+85–40+85°CNOTES 1Refer to Figure 15.Specifications subject to change without notice.(@ T A = +25؇C, V S = +5 V, R L = 2 k ⍀ to +2.5 V,unless otherwise noted)AD8051/AD8052/AD8054 SPECIFICATIONS(@ T A = +25؇C, V S = +3 V, R L = 2 k⍀ to +1.5 V, unless otherwise noted)AD8051A/AD8052A AD8054AParameter Conditions Min Typ Max Min Typ Max Units DYNAMIC PERFORMANCE–3 dB Small Signal Bandwidth G = +1, V O = 0.2 V p-p7011080135MHzG = –1, +2, V O = 0.2 V p-p5065MHzBandwidth for 0.1 dB Flatness G = +2, V O = 0.2 V p-p,R L = 150 Ω to 2.5 V,R F = 402Ω for AD8051A/AD8052A17MHzR F = 200Ω for AD8054A10MHz Slew Rate G = –1, V O = 2 V Step90135110150V/µs Full Power Response G = +1, V O = 1 V p-p6585MHz Settling Time to 0.1%G = –1, V O = 2 V Step5555ns NOISE/DISTORTION PERFORMANCETotal Harmonic Distortion1f C = 5 MHz, V O = 2 V p-p,G = –1, R L = 100 Ω to +1.5 V–47–48dBInput Voltage Noise f = 10 kHz1616nV/√Hz Input Current Noise f = 10 kHz600600fA/√Hz Differential Gain Error (NTSC)G = +2, V CM = +1 VR L = 150 Ω to +1.5 V,0.110.13%R L = 1kΩ to +1.5 V0.090.09% Differential Phase Error (NTSC)G = +2, V CM = +1 VR L = 150 Ω to +1.5 V0.240.3DegreesR L = 1k Ω to +1.5 V0.100.1Degrees Crosstalk f = 5 MHz, G = +2–60–60dBDC PERFORMANCEInput Offset Voltage 1.610 1.612mVT MIN–T MAX2530mV Offset Drift1015µV/°C Input Bias Current 1.3 2.62 4.5µAT MIN–T MAX 3.25 4.5µA Input Offset Current0.150.80.2 1.2µA Open-Loop Gain R L = 2 kΩ80968096dBT MIN–T MAX9494dBR L = 150 Ω74827280dBT MIN–T MAX7676dB INPUT CHARACTERISTICSInput Resistance290300kΩInput Capacitance 1.4 1.5pF Input Common-Mode Voltage Range–0.2 to 2–0.2 to 2V Common-Mode Rejection Ratio V CM = 0 V to 1.5 V72887086dB OUTPUT CHARACTERISTICSOutput Voltage Swing R L = 10␣kΩ to +1.5 V0.01 to 2.990.025 to 2.98VR L = 2␣kΩ to +1.5 V0.075 to 2.90.02 to 2.980.1 to 2.90.35 to 2.965VR L = 150 Ω to +1.5 V0.2 to 2.750.125 to 2.8750.35 to 2.550.15 to 2.75V Output Current V OUT = 0.5 V to +2.5 V4525mAT MIN–T MAX4525mA Short Circuit Current Sourcing6030mASinking9050mA Capacitive Load Drive G = +1 (AD8051/AD8052)45pFG = +2 (AD8054)35pF POWER SUPPLYOperating Range312312V Quiescent Current/Amplifier 4.2 4.8 2.625 3.125mA Power Supply Rejection Ratio∆V S = +0.5 V68806880dB OPERATING TEMPERATURE RANGE–40+85–40+85°C NOTES1Refer to Figure 15.Specifications subject to change without notice.REV. B–3–AD8051/AD8052/AD8054–SPECIFICATIONS(@ T A = +25؇C, V S = ؎5 V, R L = 2 k⍀ to Ground,unless otherwise noted)AD8051A/AD8052A AD8054AParameter Conditions Min Typ Max Min Typ Max Units DYNAMIC PERFORMANCE–3 dB Small Signal Bandwidth G = +1, V O = 0.2 V p-p7011085160MHzG = –1, +2, V O = 0.2 V p-p5065MHz Bandwidth for 0.1 dB Flatness G = +2, V O = 0.2 V p-p,R L = 150 Ω,R F = 1.1kΩ for AD8051A/AD8052A20MHzR F = 200Ω for AD8054A15MHz Slew Rate G = –1, V O = 2 V Step105170150190V/µs Full Power Response G = +1, V O = 2 V p-p4050MHz Settling Time to 0.1%G = –1, V O = 2 V Step5040ns NOISE/DISTORTION PERFORMANCETotal Harmonic Distortion f C = 5 MHz, V O = 2 V p-p, G = +2–71–72dB Input Voltage Noise f = 10 kHz1616nV/√Hz Input Current Noise f = 10 kHz900900fA/√Hz Differential Gain Error (NTSC)G = +2, R L = 150 Ω0.020.06%R L = 1kΩ0.020.02% Differential Phase Error (NTSC)G = +2, R L = 150 Ω0.110.15DegreesR L = 1kΩ0.020.03Degrees Crosstalk f = 5 MHz, G = +2–60–60dBDC PERFORMANCEInput Offset Voltage 1.811 1.813mVT MIN–T MAX2732mV Offset Drift1015µV/°C Input Bias Current 1.4 2.62 4.5µAT MIN–T MAX 3.5 4.5µA Input Offset Current0.10.750.2 1.2µA Open-Loop Gain R L = 2 kΩ88968496dBT MIN–T MAX9696dBR L = 150 Ω78827682dBT MIN–T MAX8080dB INPUT CHARACTERISTICSInput Resistance290300kΩInput Capacitance 1.4 1.5pF Input Common-Mode Voltage Range–5.2 to 4–5.2 to 4V Common-Mode Rejection Ratio V CM = –5 V to +3.5 V72887086dB OUTPUT CHARACTERISTICSOutput Voltage Swing R L = 10␣kΩ–4.98 to +4.98–4.97 to +4.97VR L = 2␣kΩ–4.85 to +4.85–4.97 to +4.97–4.8 to +4.8–4.9 to +4.9VR L = 150 Ω–4.45 to +4.3–4.6 to +4.6–4.0 to +3.8–4.5 to +4.5V Output Current V OUT = –4.5 V to +4.5 V4530mAT MIN–T MAX4530mA Short Circuit Current Sourcing10060mASinking160100mA Capacitive Load Drive G = +1 (AD8051/AD8052)50pFG = +2 (AD8054)40pF POWER SUPPLYOperating Range312312V Quiescent Current/Amplifier 4.8 5.5 2.875 3.4mA Power Supply Rejection Ratio∆V S = ±1V68806880dB OPERATING TEMPERATURE RANGE–40+85–40+85°C Specifications subject to change without notice.–4–REV. B–5–AD8051/AD8052/AD8054REV. B ABSOLUTE MAXIMUM RATINGS 1Supply␣Voltage . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 12.6␣V Internal␣Power␣Dissipation 2Small␣Outline␣Package (R) . . .Observe Power Derating Curves SOT-23-5 Package . . . . . . . . Observe Power Derating Curves µSOIC Package . . . . . . . . . . Observe Power Derating Curves TSSOP-14 Package . . . . . . . Observe Power Derating Curves Input Voltage (Common Mode) . . . . . . . . . . . . . . . . . . . . ±V S Differential␣Input␣Voltage . . . . . . . . . . . . . . . . . . . . . . .±2.5␣V Output Short Circuit Duration. . . . . . . . . . . . . . . . . . . . . .Observe Power Derating Curves Storage Temperature Range (R) . . . . . . . . . –65°C to +125°C Operating Temperature Range (A Grade) . . . –40°C to +85°C Lead Temperature Range (Soldering␣10␣sec) . . . . . . . . +300°CNOTES 1Stresses above those listed under Absolute Maximum Ratings may cause perma-nent damage to the device. This is a stress rating only; functional operation of the device at these or any other conditions above those indicated in the operational section of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.2Specification is for device in free air:8-Lead SOIC: θJA = 155°C/W 5-Lead SOT-23-5: θJA = 240°C/W 8-Lead µSOIC: θJA = 200°C/W 14-Lead SOIC: θJA = 120°C/W 14-Lead TSSOP: θJA = 180°C/WMAXIMUM POWER DISSIPATIONThe maximum power that can be safely dissipated by the AD8051/AD8052/AD8054 is limited by the associated rise in junction temperature. The maximum safe junction temperature forplastic encapsulated devices is determined by the glass transi-tion temperature of the plastic, approximately +150°C. Tempo-rarily exceeding this limit may cause a shift in parametric performance due to a change in the stresses exerted on the die by the package. Exceeding a junction temperature of +175°C for an extended period can result in device failure.While the AD8051/AD8052/AD8054 are internally short circuit protected, this may not be sufficient to guarantee that the maxi-mum junction temperature (+150°C) is not exceeded under all conditions. To ensure proper operation, it is necessary to ob-serve the maximum power derating curves.AMBIENT TEMPERATURE – ؇C–50–40–30–20–100102030405060708090MA X I M U M P O W E R D I S S I P A T I O N – W a t t sFigure 2.Plot of Maximum Power Dissipation vs.Temperature for AD8051/AD8052/AD8054CAUTIONESD (electrostatic discharge) sensitive device. Electrostatic charges as high as 4000V readily accumulate on the human body and test equipment and can discharge without detection.Although the AD8051/AD8052/AD8054 feature proprietary ESD protection circuitry, perma-nent damage may occur on devices subjected to high energy electrostatic discharges. Therefore, proper ESD precautions are recommended to avoid performance degradation or loss of functionality.ORDERING GUIDETemperature PackagePackage Brand ModelRange Descriptions Options*CodeAD8051AR–40°C to +85°C 8-Lead SOICSO-8AD8051AR-REEL –40°C to +85°C 13" Tape and Reel SO-8AD8051AR-REEL7–40°C to +85°C 7" Tape and Reel SO-8AD8051ART-REEL –40°C to +85°C 13" Tape and Reel RT-5H2A AD8051ART-REEL7–40°C to +85°C 7" Tape and Reel RT-5H2AAD8052AR–40°C to +85°C 8-Lead SOICSO-8AD8052AR-REEL –40°C to +85°C 13" Tape and Reel SO-8AD8052AR-REEL7–40°C to +85°C 7" Tape and Reel SO-8AD8052ARM–40°C to +85°C 8-Lead µSOIC RM-8H4A AD8052ARM-REEL –40°C to +85°C 13" Tape and Reel RM-8H4A AD8052ARM-REEL7–40°C to +85°C 7" Tape and Reel RM-8H4AAD8054AR–40°C to +85°C 14-Lead SOIC R-14AD8054AR-REEL –40°C to +85°C 13" Tape and Reel R-14AD8054AR-REEL7–40°C to +85°C 7" Tape and Reel R-14AD8054ARU–40°C to +85°C 14-Lead µSOIC RU-14AD8054ARU-REEL –40°C to +85°C 13" Tape and Reel RU-14AD8054ARU-REEL7–40°C to +85°C7" Tape and ReelRU-14*R = Small Outline; RM = Micro Small Outline; RT = Surface Mount; RU = TSSOP .AD8051/AD8052/AD8054–6–REV. BFREQUENCY – MHz32–7–1–4–5–610–3–2N O R M A L I Z E D G A I N – d BFigure 3.AD8051/AD8052 Normalized Gain vs.Frequency; V S = +5 VFREQUENCY – MHz0.1500110100G A I N – d BFigure 4.AD8051/AD8052 Gain vs. Frequency vs. SupplyFREQUENCY – MHz32–7500110100–1–4–5–610–3–2G A I N – d BFigure 5.AD8051/AD8052 Gain vs. Frequency vs.Temperature1M10M100MFREQUENCY – Hz30100k–5–45421500MN O R M A L I Z E D G A I N – d BFigure 6.AD8054 Normalized Gain vs. Frequency;V S = +5 V62100k5430–2–41M10M100MFREQUENCY – Hz500M G A I N – d BFigure 7.AD8054 Gain vs. Frequency vs. Supply4–4321–1–2–3–5110100FREQUENCY – MHzG A I N – d B500Figure 8.AD8054 Gain vs. Frequency vs. Temperature–7–AD8051/AD8052/AD8054REV. B FREQUENCY – MHz6.36.25.30.11101005.95.65.55.46.16.05.75.8 G A I N F L A T N E S S – d BFigure 9.AD8051/AD8052 0.1 dB Gain Flatness vs.Frequency; G = +2FREQUENCY – MHz0.1500110100G A I N – d BFigure 10.AD8051/AD8052 Large Signal Frequency Response; G = +2FREQUENCY – MHz8070–200.015000.111010040100–10605020300–45–90–135–180O P E N -L O O P G A I N – d BP H A S E – D e g r e e sFigure 11.AD8051/AD8052 Open-Loop Gain and Phase vs. Frequency6.35.95.46.26.16.05.85.75.65.5110010FREQUENCY – MHzG A I N F L A T N E S S – d B5.3Figure 12.AD8054 0.1 dB Gain Flatness vs. Frequency;G = +2FREQUENCY – MHz9876543210–1G A I N – d BFigure 13.AD8054 Large Signal Frequency Response;G = +230k100k1M 10M 100M FREQUENCY – Hz180135500MO P E N -L O O P G A I N – d BP H A S E M A R G I N – D e g r e e sFigure 14.AD8054 Open-Loop Gain and Phase Margin vs. FrequencyAD8051/AD8052/AD8054–8–REV. BFUNDAMENTAL FREQUENCY – MHz؊؊30؊؊70؊؊90؊؊50؊؊T O T A L H A R M O N I CD I S T O R T I O N – d B cFigure 15.Total Harmonic Distortion OUTPUT VOLTAGE – V p-p5.00.51.01.52.0 2.53.0 3.54.04.5؊؊؊؊؊؊؊؊؊؊؊؊W O R S T H A R M O N I C – d B cFigure 16.Worst Harmonic vs. Output Voltage 0.050.00؊0.05؊0.10؊0.15؊0.20؊0.250.10MODULATING RAMP LEVEL – IRE0.10؊0.060.080.060.040.020.00؊0.02؊0.04D I F F E R E N T I A L G A IN E R R O R – %D I F FE R E N T I A L P H A S E E R R O R – D e g r e e sFigure 17.AD8051/AD8052 Differential Gain and Phase Errors100010011010M100V O L T A G E N O I S E – n A H z1k 10k 100k 1M10FREQUENCY – HzFigure 18.Input Voltage Noise vs. Frequency100100.11010M1001k 10k 100k 1M 1FREQUENCY – HzC U R R E N T N O I SE – p H zFigure 19.Input Current Noise vs. Frequency0.10–0.100.050.00–0.050.20.10.0–0.1–0.2–0.30.3D I F F E R E N T I A L G A I N – %D I F FE R E N T I A L P H A S E – D e g r e e sMODULATING RAMP LEVEL – IREFigure 20.AD8054 Differential Gain and Phase Errors–9–AD8051/AD8052/AD8054REV. B FREQUENCY – MHz–10–200.1500110100–50–80–90–100–30–40–70–60C R O S S T A L K – d BFigure 21.AD8052 Crosstalk (Output-to-Output) vs.FrequencyFREQUENCY – MHz0–10–1000.1110100–40–70–80–90–20–30–60–50C M R R – d BFigure 22.CMRR vs. Frequency FREQUENCY – MHz1003.10.10.0310.0131100.311O U T P U T R E S I S T A N C E – ⍀Figure 23.Closed Loop Output Resistance vs. Frequency –10–50–100–20–30–40–60–70–80–90–1100.1110100FREQUENCY – MHz500C R O S S T A L K – d BFigure 24.AD8054 Crosstalk (Output-to-Output) vs.FrequencyFREQUENCY – MHz1500101000.10.01P S R R – d BFigure 25.PSRR vs. FrequencyINPUT STEPS – Volts p-p70S E T T I N G T I M E T O 0.1% ؊ n sFigure 26.Settling Time vs. Input StepAD8051/AD8052/AD8054–10–REV. BLOAD CURRENT – mA655101520253035404550556070758085O U T P U T S A T U R A T I O N V O L T A G E – V o l t sFigure 27.AD8051/AD8052 Output Saturation Voltage vs.Load Current 1009060050.511.522.533.544.58070O P E N -L O O P G A I N – d BOUTPUT VOLTAGE – VoltsFigure 28.Open-Loop Gain vs. Output VoltageLOAD CURRENT – mA0.6250.375030369121518212427O U T P U T S A T U R A T I O N V O L T A G E – V o l t sFigure 29.AD8054 Output Saturation Voltage vs. Load Current1.50V Figure 30.100 mV Step Response, G = +12.502.602.40Figure 31.AD8051/AD8052 200 mV Step Response;V S = +5 V, G = +1V O L T SFigure rge Signal Step Response; V S = +5 V, G = +2Figure 33.Output Swing; G = –1, R L = +2k Ω2.552.502.45V O L T SFigure 34.AD8054 100mV Step Response; VS = +5 V,G = +1Figure rge Signal Step Response; V S = ±5 V, G = +1Overdrive RecoveryOverdrive of an amplifier occurs when the output and/or input range are exceeded. The amplifier must recover from this over-drive condition. As shown in Figure 36, the AD8051/AD8052/AD8054 recovers within 60␣ns from negative overdrive and within 45␣ns from positive overdrive.Figure 36.␣Overdrive RecoveryDriving Capacitive LoadsConsider the AD8051/AD8052 in a closed-loop gain of +1 with +V S = 5V and a load of 2k Ω in parallel with 50pF. Figures 37and 38 show its frequency and time domain responses, respec-tively, to a small-signal excitation. The capacitive load drive of the AD8051/AD8052/AD8054 can be increased by adding a low valued resistor in series with the load. Figures 39 and 40show the effect of a series resistor on capacitive drive for varying voltage gains. As the closed-loop gain is increased, the larger phase margin allows for larger capacitive loads with less peak-ing. Adding a series resistor with lower closed-loop gains ac-complishes the same effect. For large capacitive loads, the frequency response of the amplifier will be dominated by the roll-off of the series resistor and the load capacitance.FREQUENCY – MHz0.111010086420؊2؊4؊6؊8؊10G A I N – d BFigure 37.AD8051/AD8052 Closed-Loop Frequency Response: C L = 50 pF2.602.552.502.452.40Figure 38.AD8051/AD8052 200 mV Step Response:C L = 50 pF1000010001162C A P A C I T I V E L O A D ؊ P F34510010A C L – V/VFigure 39.AD8051/AD8052 Capacitive Load Drive vs.Closed-Loop GainA C L – V/V100010010162345C A P A C I T I V E L O A D – p FFigure 40.AD8054 Capacitive Load Drive vs. Closed-Loop GainCircuit DescriptionThe AD8051/AD8052/AD8054 is fabricated on Analog Devices’proprietary eXtra-Fast Complementary Bipolar (XFCB) pro-cess, which enables the construction of PNP and NPN transis-tors with similar f T s in the 2 GHz–4 GHz region. The process is dielectrically isolated to eliminate the parasitic and latch-upproblems caused by junction isolation. These features allow the construction of high frequency, low distortion amplifiers with low supply currents. This design uses a differential output input stage to maximize bandwidth and headroom (see Figure 1). The smaller signal swings required on the first stage outputs (nodes S1P, S1N)reduce the effect of nonlinear currents due to junction capacitances and improve the distortion performance. With this design har-monic distortion of –80 dBc @ 1 MHz into 100Ω with V OUT =2 V p-p (Gain = +1) on a single 5 V supply is achieved.The inputs of the device can handle voltages from –0.2 V below the negative rail to within 1 V of the positive rail. Exceeding these values will not cause phase reversal; however, the input ESD devices will begin to conduct if the input voltages exceed the rails by greater than 0.5 V. During this overdrive condition,the output stays at the rail.The rail-to-rail output range of the AD8051/AD8052/AD8054is provided by a complementary common-emitter output stage.High output drive capability is provided by injecting all out-put stage predriver currents directly into the bases of the output devices Q8 and Q36. Biasing of Q8 and Q36 is accomplished by I8 and I5, along with a common-mode feedback loop (not shown). This circuit topology allows the AD8051/AD8052 to drive 45 mA of output current and the AD8054 to drive 30mA of out-put current with the outputs within 0.5␣V of the supply rails.V V IN V IN VFigure 41.AD8051/AD8052 Simplified Schematic APPLICATIONSLayout ConsiderationsThe specified high speed performance of the AD8051/AD8052/AD8054 requires careful attention to board layout and compo-nent selection. Proper RF design techniques and low-parasitic component selection are necessary.The PCB should have a ground plane covering all unused por-tions of the component side of the board to provide a low im-pedance path. The ground plane should be removed from the area near the input pins to reduce the parasitic capacitance.Chip capacitors should be used for the supply bypassing. One end should be connected to the ground plane and the other within 3mm of each power pin. An additional large (4.7␣µF to 10 µF) tantalum electrolytic capacitor should be connected in parallel, but not necessarily so close, to supply current for fast,large signal changes at the output.The feedback resistor should be located close to the inverting input pin in order to keep the parasitic capacitance at this node to a minimum. Parasitic capacitance of less than 1 pF at the inverting input can significantly affect high speed performance.Stripline design techniques should be used for long signal traces (greater than about 25mm). These should be designed with a characteristic impedance of 50 Ω or 75 Ω and be properly termi-nated at each end.Active FiltersActive filters at higher frequencies require wider bandwidth op amps to work effectively. Excessive phase shift produced by lower frequency op amps can significantly impact active filter performance.Figure 42 shows an example of a 2␣MHz biquad bandwidth filter that uses three op amps of an AD8054. Such circuits are sometimes used in medical ultrasound systems to lower the noise bandwidth of the analog signal before A/D conversion.Please note that the unused amplifiers’ inputs should be tied to ground.V R6Figure 42.2␣MHz Biquad Bandpass Filter Using AD8054The frequency response of the circuit is shown in Figure 43.FREQUENCY – Hz10k100M100k1M10M؊10؊20؊30؊40G A I N – d BFigure 43.Frequency Response of 2␣MHz Bandpass Biquad FilterA/D and D/A ApplicationsFigure 44 is a schematic showing the AD8051 used as a driver for an AD9201, a 10-bit 20 MSPS dual A/D converter. This converter is designed to convert I and Q signals in communica-tion systems. In this application, only the I channel is being driven. The I channel is enabled by applying a logic HIGH to SELECT, Pin 27.The AD8051 is running from a dual supply and is configured for a gain of +2. The input signal is terminated in 50 Ω andFigure 44.AD8051 Driving an AD9201, a 10-Bit 20 MSPS A/D Converterapplied to the noninverting input of the AD8051. The amplifieroutput is 2 V p-p, which is the maximum input range of theAD9201. The 22 Ω series resistor limits the maximum currentthat flows and helps to lower the distortion of the A/D.The AD9201 has differential inputs for each channel. These aredesignated the A and B inputs. The B inputs of each channel areconnected to VREF (Pin 8) which supplies a positive referenceof 2.5 V. Each of the B inputs has a small low pass filter thatalso helps to reduce distortion.The output of the op amp is ac coupled into INA-I (Pin 2) viatwo parallel capacitors to provide good high frequency and lowfrequency coupling. The 1 kΩ resistor references the signal toVREF that is applied to INB-I. Thus, INA-I will swing bothpositive and negative with respect to the bias voltage applied toINB-I.With the sampling clock running at 20 MSPS, the A/D outputwas analyzed with a digital analyzer. Two input frequencieswere used, 1 MHz and 9.5 MHz, which is just short of theNyquist frequency. These signals were well filtered to minimizeany harmonics.Figure 45 shows the FFT response of the A/D for the case of1 MHz analog input. The SFDR is 71.66 dB and the A/D isproducing 8.8 ENOB (effective number of bits). When theanalog frequency was raised to 9.5 MHz, the SFDR was re-duced to 60.18 dB and the A/D operated with 8.46 ENOBs asshown in Figure 46. The inclusion of the AD8051 in the circuithad no worsening of the distortion performance of the AD9201.Figure 45.FFT Plot for AD8051 Driving the AD9201 at1 MHzFigure 46.FFT Plot for AD8051 Driving the AD9201 at9.5 MHz。

Silicon Laboratories C8051F380 1 2 3 4 5 6 7 C USB

-10 位 ADC(仅 C8051F380/1/2/3/C)•高达 500ksps•内建模拟多路复用器,单端和差分模式•VREF 来自外部引脚、内部参考或 V DD•内建温度传感器•外部转换启动输入选项-两个比较器-内部参考电压(仅 C8051F380/1/2/3/C)-掉电检测器和上电复位电路USB 功能控制器-符合 USB 规格 2.0-全速 (12Mbps) 或低速 (1.5Mbps) 运行-集成时钟恢复;全速或低速无需外部晶体-支持八个灵活的终端-1kB USB 缓冲存储器-集成收发器;无需外部电阻片上调试-片上调试电路提供全速、非侵入式的系统内调试(无需仿真器)-提供断点、单步执行、检查/修改内存和寄存器-比使用 ICE 芯片、目标仿真头和仿真插座的仿真系统有更优越的性能电源电压输入: 2.7 至 5.25V-使用片内稳压器时,支持的电压范围为 2.7~5.25V -流水线指令体系结构;70% 指令的执行时间为 1 个或2个系统时钟-高达 48 MIPS 的操作-扩展的中断处理程序内存-4352 或 2304字节 RAM-64、32 或 16kB 闪存;可在系统内编程的 512 字节扇区数字外围设备-40/25 个端口 I/O;全部能承受 5V 高灌电流-硬件增强型SPI™、两个 I2C/SMBus™ 和两个增强型UART 串口-六个通用 16 位计数器/定时器-16 位可编程计数器阵列 (PCA),有五个采集/比较模块-外部存储器接口 (EMIF)时钟源-内部振荡器:启用时钟恢复时精度为 ±0.25%。

支持所有USB 和 UART 模式-外部振荡器:晶体、RC、C 或时钟(1 或 2 引脚模式)-低频 (80kHz) 内部振荡器-在运行中可切换时钟源封装-48 引脚 TQFP (C8051F380/2/4/6)-32 引脚 LQFP (C8051F381/3/5/7/C)-5x5mm 32 引脚 QFN (C8051F381/3/5/7/C)温度范围: –40 至 +85°CC8051F380/1/2/3/4/5/6/7/CC8051F380/1/2/3/4/5/6/7/CTable of Contents1. System Overview (16)2. C8051F34x Compatibility (20)2.1. Hardware Incompatibilities (21)3. Pinout and Package Definitions (22)4. Typical Connection Diagrams (34)4.1. Power (34)4.2. USB (36)4.3. Voltage Reference (VREF) (36)5. Electrical Characteristics (37)5.1. Absolute Maximum Specifications (37)5.2. Electrical Characteristics (38)6. 10-Bit ADC (ADC0, C8051F380/1/2/3/C only) (46)6.1. Output Code Formatting (47)6.3. Modes of Operation (50)6.3.1. Starting a Conversion (50)6.3.2. Tracking Modes (51)6.3.3. Settling Time Requirements (52)6.4. Programmable Window Detector (56)6.4.1. Window Detector Example (58)6.5. ADC0 Analog Multiplexer (C8051F380/1/2/3/C only) (59)7. Voltage Reference Options (62)8. Comparator0 and Comparator1 (64)8.1. Comparator Multiplexers (71)9. Voltage Regulators (REG0 and REG1) (74)9.1. Voltage Regulator (REG0) (74)9.1.1. Regulator Mode Selection (74)9.1.2. VBUS Detection (74)9.2. Voltage Regulator (REG1) (74)10. Power Management Modes (76)10.1. Idle Mode (76)10.2. Stop Mode (77)10.3. Suspend Mode (77)11. CIP-51 Microcontroller (79)11.1. Instruction Set (80)11.1.1. Instruction and CPU Timing (80)11.2. CIP-51 Register Descriptions (85)12. Prefetch Engine (88)13. Memory Organization (89)13.1. Program Memory (91)13.2. Data Memory (91)13.3. General Purpose Registers (92)13.4. Bit Addressable Locations (92)13.5. Stack (92)C8051F380/1/2/3/4/5/6/7/C14. External Data Memory Interface and On-Chip XRAM (93)14.1. Accessing XRAM (93)14.1.1. 16-Bit MOVX Example (93)14.1.2. 8-Bit MOVX Example (93)14.2. Accessing USB FIFO Space (94)14.3. Configuring the External Memory Interface (95)14.4. Port Configuration (95)14.5. Multiplexed and Non-multiplexed Selection (98)14.5.1. Multiplexed Configuration (98)14.5.2. Non-multiplexed Configuration (98)14.6. Memory Mode Selection (100)14.6.1. Internal XRAM Only (100)14.6.2. Split Mode without Bank Select (100)14.6.3. Split Mode with Bank Select (101)14.6.4. External Only (101)14.7. Timing (102)14.7.1. Non-multiplexed Mode (104)14.7.1.1. 16-bit MOVX: EMI0CF[4:2] = 101, 110, or 111 (104)14.7.1.2. 8-bit MOVX without Bank Select: EMI0CF[4:2] = 101 or 111 (105)14.7.1.3. 8-bit MOVX with Bank Select: EMI0CF[4:2] = 110 (106)14.7.2. Multiplexed Mode (107)14.7.2.1. 16-bit MOVX: EMI0CF[4:2] = 001, 010, or 011 (107)14.7.2.2. 8-bit MOVX without Bank Select: EMI0CF[4:2] = 001 or 011 (108)14.7.2.3. 8-bit MOVX with Bank Select: EMI0CF[4:2] = 010 (109)15. Special Function Registers (111)15.1. 13.1. SFR Paging (111)16. Interrupts (118)16.1. MCU Interrupt Sources and Vectors (119)16.1.1. Interrupt Priorities (119)16.1.2. Interrupt Latency (119)16.2. Interrupt Register Descriptions (119)16.3. INT0 and INT1 External Interrupt Sources (127)17. Reset Sources (129)17.1. Power-On Reset (130)17.2. Power-Fail Reset / VDD Monitor (131)17.3. External Reset (132)17.4. Missing Clock Detector Reset (132)17.5. Comparator0 Reset (132)17.6. PCA Watchdog Timer Reset (133)17.7. Flash Error Reset (133)17.8. Software Reset (133)17.9. USB Reset (133)18. Flash Memory (135)18.1. Programming The Flash Memory (135)18.1.1. Flash Lock and Key Functions (135)C8051F380/1/2/3/4/5/6/7/C18.1.2. Flash Erase Procedure (135)18.1.3. Flash Write Procedure (136)18.2. Non-Volatile Data Storage (137)18.3. Security Options (137)19. Oscillators and Clock Selection (142)19.1. System Clock Selection (143)19.2. USB Clock Selection (143)19.3. Programmable Internal High-Frequency (H-F) Oscillator (145)19.3.1. Internal Oscillator Suspend Mode (145)19.4. Clock Multiplier (147)19.5. Programmable Internal Low-Frequency (L-F) Oscillator (148)19.5.1. Calibrating the Internal L-F Oscillator (148)19.6. External Oscillator Drive Circuit (149)19.6.1. External Crystal Mode (149)19.6.2. External RC Example (151)19.6.3. External Capacitor Example (151)20. Port Input/Output (153)20.1. Priority Crossbar Decoder (154)20.2. Port I/O Initialization (158)20.3. General Purpose Port I/O (161)21. Universal Serial Bus Controller (USB0) (172)21.1. Endpoint Addressing (172)21.2. USB Transceiver (173)21.3. USB Register Access (175)21.4. USB Clock Configuration (179)21.5. FIFO Management (181)21.5.1. FIFO Split Mode (181)21.5.2. FIFO Double Buffering (182)21.5.1. FIFO Access (182)21.6. Function Addressing (183)21.7. Function Configuration and Control (183)21.8. Interrupts (186)21.9. The Serial Interface Engine (193)21.10. Endpoint0 (193)21.10.1. Endpoint0 SETUP Transactions (193)21.10.2. Endpoint0 IN Transactions (193)21.10.3. Endpoint0 OUT Transactions (194)21.11. Configuring Endpoints1-3 (196)21.12. Controlling Endpoints1-3 IN (197)21.12.1. Endpoints1-3 IN Interrupt or Bulk Mode (197)21.12.2. Endpoints1-3 IN Isochronous Mode (198)21.13. Controlling Endpoints1-3 OUT (201)21.13.1. Endpoints1-3 OUT Interrupt or Bulk Mode (201)21.13.2. Endpoints1-3 OUT Isochronous Mode (201)22. SMBus0 and SMBus1 (I2C Compatible) (205)C8051F380/1/2/3/4/5/6/7/C22.1. Supporting Documents (206)22.2. SMBus Configuration (206)22.3. SMBus Operation (206)22.3.1. Transmitter Vs. Receiver (207)22.3.2. Arbitration (207)22.3.3. Clock Low Extension (207)22.3.4. SCL Low Timeout (207)22.3.5. SCL High (SMBus Free) Timeout (208)22.4. Using the SMBus (208)22.4.1. SMBus Configuration Register (208)22.4.2. SMBus Timing Control Register (210)22.4.3. SMBnCN Control Register (214)22.4.3.1. Software ACK Generation (214)22.4.3.2. Hardware ACK Generation (214)22.4.4. Hardware Slave Address Recognition (217)22.4.5. Data Register (221)22.5. SMBus Transfer Modes (223)22.5.1. Write Sequence (Master) (223)22.5.2. Read Sequence (Master) (224)22.5.3. Write Sequence (Slave) (225)22.5.4. Read Sequence (Slave) (226)22.6. SMBus Status Decoding (226)23. UART0 (232)23.1. Enhanced Baud Rate Generation (233)23.2. Operational Modes (234)23.2.1. 8-Bit UART (234)23.2.2. 9-Bit UART (235)23.3. Multiprocessor Communications (236)24. UART1 (240)24.1. Baud Rate Generator (241)24.2. Data Format (242)24.3. Configuration and Operation (243)24.3.1. Data Transmission (243)24.3.2. Data Reception (243)24.3.3. Multiprocessor Communications (244)25. Enhanced Serial Peripheral Interface (SPI0) (250)25.1. Signal Descriptions (251)25.1.1. Master Out, Slave In (MOSI) (251)25.1.2. Master In, Slave Out (MISO) (251)25.1.3. Serial Clock (SCK) (251)25.1.4. Slave Select (NSS) (251)25.2. SPI0 Master Mode Operation (251)25.3. SPI0 Slave Mode Operation (253)25.4. SPI0 Interrupt Sources (254)25.5. Serial Clock Phase and Polarity (254)25.6. SPI Special Function Registers (256)26. Timers (263)26.1. Timer 0 and Timer 1 (266)26.1.1. Mode 0: 13-bit Counter/Timer (266)26.1.2. Mode 1: 16-bit Counter/Timer (267)26.1.3. Mode 2: 8-bit Counter/Timer with Auto-Reload (267)26.1.4. Mode 3: Two 8-bit Counter/Timers (Timer 0 Only) (268)26.2. Timer 2 (274)26.2.1. 16-bit Timer with Auto-Reload (274)26.2.2. 8-bit Timers with Auto-Reload (275)26.2.3. Timer 2 Capture Modes: USB Start-of-Frame or LFO Falling Edge (275)26.3. Timer 3 (281)26.3.1. 16-bit Timer with Auto-Reload (281)26.3.2. 8-bit Timers with Auto-Reload (282)26.3.3. Timer 3 Capture Modes: USB Start-of-Frame or LFO Falling Edge (282)26.4. Timer 4 (288)26.4.1. 16-bit Timer with Auto-Reload (288)26.4.2. 8-bit Timers with Auto-Reload (289)26.5. Timer 5 (293)26.5.1. 16-bit Timer with Auto-Reload (293)26.5.2. 8-bit Timers with Auto-Reload (294)27. Programmable Counter Array (298)27.1. PCA Counter/Timer (299)27.2. PCA0 Interrupt Sources (300)27.3. Capture/Compare Modules (301)27.3.1. Edge-triggered Capture Mode (302)27.3.2. Software Timer (Compare) Mode (303)27.3.3. High-Speed Output Mode (304)27.3.4. Frequency Output Mode (305)27.3.5. 8-bit Pulse Width Modulator Mode (306)27.3.6. 16-Bit Pulse Width Modulator Mode (307)27.4. Watchdog Timer Mode (308)27.4.1. Watchdog Timer Operation (308)27.4.2. Watchdog Timer Usage (309)27.5. Register Descriptions for PCA0 (311)28. C2 Interface (316)28.1. C2 Interface Registers (316)28.2. C2 Pin Sharing (319)Document Change List (320)Contact Information (321)List of FiguresFigure1.1. C8051F380/2/4/6 Block Diagram (18)Figure1.2. C8051F381/3/5/7/C Block Diagram (19)Figure3.1. TQFP-48 Pinout Diagram (Top View) (25)Figure3.2. TQFP-48 Package Diagram (26)Figure3.3. TQFP-48 Recommended PCB Land Pattern (27)Figure3.4. LQFP-32 Pinout Diagram (Top View) (28)Figure3.5. LQFP-32 Package Diagram (29)Figure3.6. LQFP-32 Recommended PCB Land Pattern (30)Figure3.7. QFN-32 Pinout Diagram (Top View) (31)Figure3.8. QFN-32 Package Drawing (32)Figure3.9. QFN-32 Recommended PCB Land Pattern (33)Figure4.1. Connection Diagram with Voltage Regulator Used and No USB (34)Figure4.2. Connection Diagram with Voltage Regulator Not Used and No USB (34)Figure4.3. Connection Diagram with Voltage Regulator Used and USB Connected (Bus-Powered) (35)Figure4.4. Connection Diagram with Voltage Regulator Used and USB Connected (Self-Powered) (35)Figure4.5. Connection Diagram for USB Pins (36)Figure4.6. Connection Diagram for Internal Voltage Reference (36)Figure6.1. ADC0 Functional Block Diagram (46)Figure6.2. Typical Temperature Sensor Transfer Function (48)Figure6.3. Temperature Sensor Error with 1-Point Calibration (49)Figure6.4. 10-Bit ADC Track and Conversion Example Timing (51)Figure6.5. ADC0 Equivalent Input Circuits (52)Figure6.6. ADC Window Compare Example: Right-Justified Data (58)Figure6.7. ADC Window Compare Example: Left-Justified Data (58)Figure7.1. Voltage Reference Functional Block Diagram (62)Figure8.1. Comparator0 Functional Block Diagram (64)Figure8.2. Comparator1 Functional Block Diagram (65)Figure8.3. Comparator Hysteresis Plot (66)Figure8.4. Comparator Input Multiplexer Block Diagram (71)Figure11.1. CIP-51 Block Diagram (79)Figure13.1. On-Chip Memory Map for 64kB Devices (C8051F380/1/4/5) (89)Figure13.2. On-Chip Memory Map for 32kB Devices (C8051F382/3/6/7) (90)Figure13.3. On-Chip Memory Map for 16kB Devices (C8051F38C) (91)Figure14.1. USB FIFO Space and XRAM Memory Map with USBFAE set to ‘1’ (94)Figure14.2. Multiplexed Configuration Example (98)Figure14.3. Non-multiplexed Configuration Example (99)Figure14.4. EMIF Operating Modes (100)Figure14.5. Non-Multiplexed 16-bit MOVX Timing (104)Figure14.6. Non-multiplexed 8-bit MOVX without Bank Select Timing (105)Figure14.7. Non-multiplexed 8-bit MOVX with Bank Select Timing (106)Figure14.8. Multiplexed 16-bit MOVX Timing (107)C8051F380/1/2/3/4/5/6/7/CFigure14.9. Multiplexed 8-bit MOVX without Bank Select Timing (108)Figure14.10. Multiplexed 8-bit MOVX with Bank Select Timing (109)Figure17.1. Reset Sources (129)Figure17.2. Power-On and VDD Monitor Reset Timing (130)Figure18.1. Flash Program Memory Map and Security Byte (137)Figure19.1. Oscillator Options (142)Figure19.2. External Crystal Example (150)Figure20.1. Port I/O Functional Block Diagram (Port 0 through Port 3) (153)Figure20.2. Port I/O Cell Block Diagram (154)Figure20.3. Peripheral Availability on Port I/O Pins (155)Figure20.4. Crossbar Priority Decoder in Example Configuration(No Pins Skipped) (156)Figure20.5. Crossbar Priority Decoder in Example Configuration (3 Pins Skipped) (157)Figure21.1. USB0 Block Diagram (172)Figure21.2. USB0 Register Access Scheme (175)Figure21.3. USB FIFO Allocation (181)Figure22.1. SMBus Block Diagram (205)Figure22.2. Typical SMBus Configuration (206)Figure22.3. SMBus Transaction (207)Figure22.4. Typical SMBus SCL Generation (209)Figure22.5. Typical Master Write Sequence (223)Figure22.6. Typical Master Read Sequence (224)Figure22.7. Typical Slave Write Sequence (225)Figure22.8. Typical Slave Read Sequence (226)Figure23.1. UART0 Block Diagram (232)Figure23.2. UART0 Baud Rate Logic (233)Figure23.3. UART Interconnect Diagram (234)Figure23.4. 8-Bit UART Timing Diagram (234)Figure23.5. 9-Bit UART Timing Diagram (235)Figure23.6. UART Multi-Processor Mode Interconnect Diagram (236)Figure24.1. UART1 Block Diagram (240)Figure24.2. UART1 Timing Without Parity or Extra Bit (242)Figure24.3. UART1 Timing With Parity (242)Figure24.4. UART1 Timing With Extra Bit (242)Figure24.5. Typical UART Interconnect Diagram (243)Figure24.6. UART Multi-Processor Mode Interconnect Diagram (244)Figure25.1. SPI Block Diagram (250)Figure25.2. Multiple-Master Mode Connection Diagram (252)Figure25.3. 3-Wire Single Master and 3-Wire Single Slave Mode Connection Diagram (252)Figure25.4. 4-Wire Single Master Mode and 4-Wire Slave Mode Connection Diagram (253)Figure25.5. Master Mode Data/Clock Timing (255)Figure25.6. Slave Mode Data/Clock Timing (CKPHA = 0) (255)C8051F380/1/2/3/4/5/6/7/C Figure25.7. Slave Mode Data/Clock Timing (CKPHA = 1) (256)Figure25.8. SPI Master Timing (CKPHA = 0) (260)Figure25.9. SPI Master Timing (CKPHA = 1) (260)Figure25.10. SPI Slave Timing (CKPHA = 0) (261)Figure25.11. SPI Slave Timing (CKPHA = 1) (261)Figure26.1. T0 Mode 0 Block Diagram (267)Figure26.2. T0 Mode 2 Block Diagram (268)Figure26.3. T0 Mode 3 Block Diagram (269)Figure26.4. Timer 2 16-Bit Mode Block Diagram (274)Figure26.5. Timer 2 8-Bit Mode Block Diagram (275)Figure26.6. Timer2 Capture Mode (T2SPLIT = 0) (276)Figure26.7. Timer2 Capture Mode (T2SPLIT = 0) (277)Figure26.8. Timer 3 16-Bit Mode Block Diagram (281)Figure26.9. Timer 3 8-Bit Mode Block Diagram (282)Figure26.10. Timer3 Capture Mode (T3SPLIT = 0) (283)Figure26.11. Timer3 Capture Mode (T3SPLIT = 0) (284)Figure26.12. Timer 4 16-Bit Mode Block Diagram (288)Figure26.13. Timer 4 8-Bit Mode Block Diagram (289)Figure26.14. Timer 5 16-Bit Mode Block Diagram (293)Figure26.15. Timer 5 8-Bit Mode Block Diagram (294)Figure27.1. PCA Block Diagram (298)Figure27.2. PCA Counter/Timer Block Diagram (299)Figure27.3. PCA Interrupt Block Diagram (300)Figure27.4. PCA Capture Mode Diagram (302)Figure27.5. PCA Software Timer Mode Diagram (303)Figure27.6. PCA High-Speed Output Mode Diagram (304)Figure27.7. PCA Frequency Output Mode (305)Figure27.8. PCA 8-Bit PWM Mode Diagram (306)Figure27.9. PCA 16-Bit PWM Mode (307)Figure27.10. PCA Module 4 with Watchdog Timer Enabled (308)Figure28.1. Typical C2 Pin Sharing (319)List of TablesTable1.1. Product Selection Guide (17)Table2.1. C8051F38x Replacement Part Numbers (20)Table3.1. Pin Definitions for the C8051F380/1/2/3/4/5/6/7/C (22)Table3.2. TQFP-48 Package Dimensions (26)Table3.3. TQFP-48 PCB Land Pattern Dimensions (27)Table3.4. LQFP-32 Package Dimensions (29)Table3.5. LQFP-32 PCB Land Pattern Dimensions (30)Table3.6. QFN-32 Package Dimensions (32)Table3.7. QFN-32 PCB Land Pattern Dimensions (33)Table5.1. Absolute Maximum Ratings (37)Table5.2. Global Electrical Characteristics (38)Table5.3. Port I/O DC Electrical Characteristics (39)Table5.4. Reset Electrical Characteristics (39)Table5.5. Internal Voltage Regulator Electrical Characteristics (40)Table5.6. Flash Electrical Characteristics (40)Table5.7. Internal High-Frequency Oscillator Electrical Characteristics (41)Table5.8. Internal Low-Frequency Oscillator Electrical Characteristics (41)Table5.9. External Oscillator Electrical Characteristics (41)Table5.10. ADC0 Electrical Characteristics (42)Table5.11. Temperature Sensor Electrical Characteristics (43)Table5.12. Voltage Reference Electrical Characteristics (43)Table5.13. Comparator Electrical Characteristics (44)Table5.14. USB Transceiver Electrical Characteristics (45)Table11.1. CIP-51 Instruction Set Summary (81)Table14.1. AC Parameters for External Memory Interface (110)Table15.1. Special Function Register (SFR) Memory Map (112)Table15.2. Special Function Registers (113)Table16.1. Interrupt Summary (120)Table21.1. Endpoint Addressing Scheme (173)Table21.2. USB0 Controller Registers (178)Table21.3. FIFO Configurations (182)Table22.1. SMBus Clock Source Selection (209)Table22.2. Minimum SDA Setup and Hold Times (210)Table22.3. Sources for Hardware Changes to SMBnCN (217)Table22.4. Hardware Address Recognition Examples (EHACK = 1) (218)Table22.5. SMBus Status Decoding: Hardware ACK Disabled (EHACK = 0) (227)Table22.6. SMBus Status Decoding: Hardware ACK Enabled (EHACK = 1) (229)Table23.1. Timer Settings for Standard Baud Rates Using Internal Oscillator (238)Table24.1. Baud Rate Generator Settings for Standard Baud Rates (241)Table25.1. SPI Slave Timing Parameters (262)Table27.1. PCA Timebase Input Options (299)Table27.2. PCA0CPM Bit Settings for PCA Capture/Compare Modules (301)Table27.3. Watchdog Timer Timeout Intervals1 (310)List of RegistersSFR Definition6.1. ADC0CF: ADC0 Configuration (53)SFR Definition6.2. ADC0H: ADC0 Data Word MSB (54)SFR Definition6.3. ADC0L: ADC0 Data Word LSB (54)SFR Definition6.4. ADC0CN: ADC0 Control (55)SFR Definition6.5. ADC0GTH: ADC0 Greater-Than Data High Byte (56)SFR Definition6.6. ADC0GTL: ADC0 Greater-Than Data Low Byte (56)SFR Definition6.7. ADC0LTH: ADC0 Less-Than Data High Byte (57)SFR Definition6.8. ADC0LTL: ADC0 Less-Than Data Low Byte (57)SFR Definition6.9. AMX0P: AMUX0 Positive Channel Select (60)SFR Definition6.10. AMX0N: AMUX0 Negative Channel Select (61)SFR Definition7.1. REF0CN: Reference Control (63)SFR Definition8.1. CPT0CN: Comparator0 Control (67)SFR Definition8.2. CPT0MD: Comparator0 Mode Selection (68)SFR Definition8.3. CPT1CN: Comparator1 Control (69)SFR Definition8.4. CPT1MD: Comparator1 Mode Selection (70)SFR Definition8.5. CPT0MX: Comparator0 MUX Selection (72)SFR Definition8.6. CPT1MX: Comparator1 MUX Selection (73)SFR Definition9.1. REG01CN: Voltage Regulator Control (75)SFR Definition10.1. PCON: Power Control (78)SFR Definition11.1. DPL: Data Pointer Low Byte (85)SFR Definition11.2. DPH: Data Pointer High Byte (85)SFR Definition11.3. SP: Stack Pointer (86)SFR Definition11.4. ACC: Accumulator (86)SFR Definition11.5. B: B Register (86)SFR Definition11.6. PSW: Program Status Word (87)SFR Definition12.1. PFE0CN: Prefetch Engine Control (88)SFR Definition14.1. EMI0CN: External Memory Interface Control (96)SFR Definition14.2. EMI0CF: External Memory Interface Configuration (97)SFR Definition14.3. EMI0TC: External Memory TIming Control (103)SFR Definition15.1. SFRPAGE: SFR Page (111)SFR Definition16.1. IE: Interrupt Enable (121)SFR Definition16.2. IP: Interrupt Priority (122)SFR Definition16.3. EIE1: Extended Interrupt Enable 1 (123)SFR Definition16.4. EIP1: Extended Interrupt Priority 1 (124)SFR Definition16.5. EIE2: Extended Interrupt Enable 2 (125)SFR Definition16.6. EIP2: Extended Interrupt Priority 2 (126)SFR Definition16.7. IT01CF: INT0/INT1 ConfigurationO (128)SFR Definition17.1. VDM0CN: VDD Monitor Control (132)SFR Definition17.2. RSTSRC: Reset Source (134)SFR Definition18.1. PSCTL: Program Store R/W Control (139)SFR Definition18.2. FLKEY: Flash Lock and Key (140)SFR Definition18.3. FLSCL: Flash Scale (141)SFR Definition19.1. CLKSEL: Clock Select (144)C8051F380/1/2/3/4/5/6/7/CSFR Definition19.2. OSCICL: Internal H-F Oscillator Calibration (145)SFR Definition19.3. OSCICN: Internal H-F Oscillator Control (146)SFR Definition19.4. CLKMUL: Clock Multiplier Control (147)SFR Definition19.5. OSCLCN: Internal L-F Oscillator Control (148)SFR Definition19.6. OSCXCN: External Oscillator Control (152)SFR Definition20.1. XBR0: Port I/O Crossbar Register 0 (159)SFR Definition20.2. XBR1: Port I/O Crossbar Register 1 (160)SFR Definition20.3. XBR2: Port I/O Crossbar Register 2 (161)SFR Definition20.4. P0: Port 0 (162)SFR Definition20.5. P0MDIN: Port 0 Input Mode (162)SFR Definition20.6. P0MDOUT: Port 0 Output Mode (163)SFR Definition20.7. P0SKIP: Port 0 Skip (163)SFR Definition20.8. P1: Port 1 (164)SFR Definition20.9. P1MDIN: Port 1 Input Mode (164)SFR Definition20.10. P1MDOUT: Port 1 Output Mode (165)SFR Definition20.11. P1SKIP: Port 1 Skip (165)SFR Definition20.12. P2: Port 2 (166)SFR Definition20.13. P2MDIN: Port 2 Input Mode (166)SFR Definition20.14. P2MDOUT: Port 2 Output Mode (167)SFR Definition20.15. P2SKIP: Port 2 Skip (167)SFR Definition20.16. P3: Port 3 (168)SFR Definition20.17. P3MDIN: Port 3 Input Mode (168)SFR Definition20.18. P3MDOUT: Port 3 Output Mode (169)SFR Definition20.19. P3SKIP: Port 3 Skip (169)SFR Definition20.20. P4: Port 4 (170)SFR Definition20.21. P4MDIN: Port 4 Input Mode (170)SFR Definition20.22. P4MDOUT: Port 4 Output Mode (171)SFR Definition21.1. USB0XCN: USB0 Transceiver Control (174)SFR Definition21.2. USB0ADR: USB0 Indirect Address (176)SFR Definition21.3. USB0DAT: USB0 Data (177)USB Register Definition21.4. INDEX: USB0 Endpoint Index (179)USB Register Definition21.5. CLKREC: Clock Recovery Control (180)USB Register Definition21.6. FIFOn: USB0 Endpoint FIFO Access (182)USB Register Definition21.7. FADDR: USB0 Function Address (183)USB Register Definition21.8. POWER: USB0 Power (185)USB Register Definition21.9. FRAMEL: USB0 Frame Number Low (186)USB Register Definition21.10. FRAMEH: USB0 Frame Number High (186)USB Register Definition21.11. IN1INT: USB0 IN Endpoint Interrupt (187)USB Register Definition21.12. OUT1INT: USB0 OUT Endpoint Interrupt (188)USB Register Definition21.13. CMINT: USB0 Common Interrupt (189)USB Register Definition21.14. IN1IE: USB0 IN Endpoint Interrupt Enable (190)USB Register Definition21.15. OUT1IE: USB0 OUT Endpoint Interrupt Enable (191)USB Register Definition21.16. CMIE: USB0 Common Interrupt Enable (192)USB Register Definition21.17. E0CSR: USB0 Endpoint0 Control (195)USB Register Definition21.18. E0CNT: USB0 Endpoint0 Data Count (196)C8051F380/1/2/3/4/5/6/7/C USB Register Definition21.19. EENABLE: USB0 Endpoint Enable (197)USB Register Definition21.20. EINCSRL: USB0 IN Endpoint Control Low (199)USB Register Definition21.21. EINCSRH: USB0 IN Endpoint Control High (200)USB Register Definition21.22. EOUTCSRL: USB0 OUT Endpoint Control Low Byte 202 USB Register Definition21.23. EOUTCSRH: USB0 OUT Endpoint Control High Byte (203)USB Register Definition21.24. EOUTCNTL: USB0 OUT Endpoint Count Low (203)USB Register Definition21.25. EOUTCNTH: USB0 OUT Endpoint Count High (204)SFR Definition22.1. SMB0CF: SMBus Clock/Configuration (211)SFR Definition22.2. SMB1CF: SMBus Clock/Configuration (212)SFR Definition22.3. SMBTC: SMBus Timing Control (213)SFR Definition22.4. SMB0CN: SMBus Control (215)SFR Definition22.5. SMB1CN: SMBus Control (216)SFR Definition22.6. SMB0ADR: SMBus0 Slave Address (218)SFR Definition22.7. SMB0ADM: SMBus0 Slave Address Mask (219)SFR Definition22.8. SMB1ADR: SMBus1 Slave Address (219)SFR Definition22.9. SMB1ADM: SMBus1 Slave Address Mask (220)SFR Definition22.10. SMB0DAT: SMBus Data (221)SFR Definition22.11. SMB1DAT: SMBus Data (222)SFR Definition23.1. SCON0: Serial Port 0 Control (237)SFR Definition23.2. SBUF0: Serial (UART0) Port Data Buffer (238)SFR Definition24.1. SCON1: UART1 Control (245)SFR Definition24.2. SMOD1: UART1 Mode (246)SFR Definition24.3. SBUF1: UART1 Data Buffer (247)SFR Definition24.4. SBCON1: UART1 Baud Rate Generator Control (248)SFR Definition24.5. SBRLH1: UART1 Baud Rate Generator High Byte (248)SFR Definition24.6. SBRLL1: UART1 Baud Rate Generator Low Byte (249)SFR Definition25.1. SPI0CFG: SPI0 Configuration (257)SFR Definition25.2. SPI0CN: SPI0 Control (258)SFR Definition25.3. SPI0CKR: SPI0 Clock Rate (259)SFR Definition25.4. SPI0DAT: SPI0 Data (259)SFR Definition26.1. CKCON: Clock Control (264)SFR Definition26.2. CKCON1: Clock Control 1 (265)SFR Definition26.3. TCON: Timer Control (270)SFR Definition26.4. TMOD: Timer Mode (271)SFR Definition26.5. TL0: Timer 0 Low Byte (272)SFR Definition26.6. TL1: Timer 1 Low Byte (272)SFR Definition26.7. TH0: Timer 0 High Byte (273)SFR Definition26.8. TH1: Timer 1 High Byte (273)SFR Definition26.9. TMR2CN: Timer 2 Control (278)SFR Definition26.10. TMR2RLL: Timer 2 Reload Register Low Byte (279)SFR Definition26.11. TMR2RLH: Timer 2 Reload Register High Byte (279)SFR Definition26.12. TMR2L: Timer 2 Low Byte (279)SFR Definition26.13. TMR2H Timer 2 High Byte (280)SFR Definition26.14. TMR3CN: Timer 3 Control (285)C8051F380/1/2/3/4/5/6/7/CSFR Definition26.15. TMR3RLL: Timer 3 Reload Register Low Byte (286)SFR Definition26.16. TMR3RLH: Timer 3 Reload Register High Byte (286)SFR Definition26.17. TMR3L: Timer 3 Low Byte (286)SFR Definition26.18. TMR3H Timer 3 High Byte (287)SFR Definition26.19. TMR4CN: Timer 4 Control (290)SFR Definition26.20. TMR4RLL: Timer 4 Reload Register Low Byte (291)SFR Definition26.21. TMR4RLH: Timer 4 Reload Register High Byte (291)SFR Definition26.22. TMR4L: Timer 4 Low Byte (291)SFR Definition26.23. TMR4H Timer 4 High Byte (292)SFR Definition26.24. TMR5CN: Timer 5 Control (295)SFR Definition26.25. TMR5RLL: Timer 5 Reload Register Low Byte (296)SFR Definition26.26. TMR5RLH: Timer 5 Reload Register High Byte (296)SFR Definition26.27. TMR5L: Timer 5 Low Byte (296)SFR Definition26.28. TMR5H Timer 5 High Byte (297)SFR Definition27.1. PCA0CN: PCA Control (311)SFR Definition27.2. PCA0MD: PCA Mode (312)SFR Definition27.3. PCA0CPMn: PCA Capture/Compare Mode (313)SFR Definition27.4. PCA0L: PCA Counter/Timer Low Byte (314)SFR Definition27.5. PCA0H: PCA Counter/Timer High Byte (314)SFR Definition27.6. PCA0CPLn: PCA Capture Module Low Byte (315)SFR Definition27.7. PCA0CPHn: PCA Capture Module High Byte (315)C2 Register Definition28.1. C2ADD: C2 Address (316)C2 Register Definition28.2. DEVICEID: C2 Device ID (317)C2 Register Definition28.3. REVID: C2 Revision ID (317)C2 Register Definition28.4. FPCTL: C2 Flash Programming Control (318)C2 Register Definition28.5. FPDAT: C2 Flash Programming Data (318)。

C8051F_全线产品选型手册

选型请启用筛选

Part Number C8051F000 C8051F001 C8051F002 C8051F005 C8051F006 C8051F007 C8051F010 C8051F011 C8051F012 C8051F015 C8051F016 C8051F017 C8051F018 C8051F019 C8051F020 C8051F021 C8051F022 C8051F023 C8051F040 C8051F041 C8051F042 C8051F043 C8051F044 C8051F045 C8051F046 C8051F047 C8051F060 C8051F061 C8051F062 C8051F063 C8051F064 C8051F065 C8051F066 C8051F067 C8051F120 C8051F121 C8051F122 C8051F123 C8051F124 C8051F125 C8051F126 C8051F127 C8051F130 C8051F131 C8051F132 C8051F133 C8051F206 C8051F220 C8051F221 C8051F226 C8051F230 C8051F231 C8051F236 C8051F300-GM C8051F300-GS C8051F301-GM C8051F301-GS C8051F302-GM C8051F302-GS C8051F303-GM C8051F303-GS C8051F304-GM C8051F304-GS C8051F305-GM C8051F305-GS C8051F310 C8051F311 C8051F312 C8051

C8051F单片机

5、系统复位

复位电路将控制器置于一个预定的缺省状态。 1)CIP-51 停止程序执行 2) 特殊功能寄存器(SFR)被初始化为所定义的复位值 3)外部端口引脚被置于一个已知状态 4)中断和定时器被禁止。 5)所有的SFR 都被初始化为预定值 6)I/O 端口锁存器的复位值为0xFF,全部为逻辑‘1’,内部 弱上拉有效,使外部I/O 引脚处于高电平状态。 7) MCU 使用内部振荡器运行在2MHz 作为默认的系统时钟。 8) 看门狗定时器被使能,使用其最长的超时时间。

13

1、概述

4、可编程数字I/O •C8051F310有29个I/O引脚(3个8位口和一个5位口) •C8051F31x端口的工作情况与标准8051相似,但有一些 改进。每个端口引脚都可以被配置为模拟输入或数字I/O 。 •被选择作为数字I/O的引脚还可以被配置为推挽或漏极 开路输出。 •在标准8051中固定的“弱上拉”可以被总体禁止,为低 功耗应用提供了进一步节电的能力。

18

3、优先权交叉开关配置

也称为“交叉开关”,按优先权顺序将端口0 – 3 的 引脚分配给器件上的数字外设(UART、SMBus、 PCA、定时器等)。 端口引脚的分配顺序是从P0.0 开始,可以一直分配 到P3.7。为数字外设分配端口引脚的优先权顺序为 UART0具有最高优先权,而CNVSTR具有最低优先 权。 优先权交叉开关的配置是通过3个特殊功能寄存器 XBR0、XBR1、XBR2来实现的,对应使能位被设置 为逻辑‘1’时,交叉开关将端口引脚分配给外设。

◆16K 字节可在系统编程的FLASH 存储器

◆1280字节的片内RAM ◆可寻址64K字节地址空间的外部数据存储器接口

◆硬件实现的SPI、SMBus/ I2C 和两个UART 串行接口

奥伟斯科技为您提供GS8051_GS8052_GS8054系列聚洵高速运算放大器

GS8051/GS8052/GS8054描述:GS8051 / 1N(单),GS8052 / 2N(双),GS8054(四)是轨到轨输出电压反馈放大器,具有易用性和低成本。

它们具有通常在电流反馈放大器中发现的带宽和压摆率。

GS8051系列均具有宽的输入共模电压范围和输出电压摆幅,因此易于在低至2.5V的单电源上使用。

尽管成本较低,但GS8051系列仍具有出色的整体性能。

它们提供250MHz(G = +1)的宽带宽,以及高达52MHz(G = +2)的0.1dB平坦度,并提供典型的2.8mA /放大器低功耗。

GS8051系列具有低失真和快速建立的特点,非常适合于缓冲高速A / D或D / A转换器。

GS8051 / 2N具有掉电禁用功能,可将电源电流降至50µA。

这些功能使GS8051 / 2N成为尺寸和功耗至关重要的便携式和电池供电应用的理想选择。

所有参数均在-40至+125扩展温度范围内指定。

特点:+ 2.5V〜+ 5.5V单电源供电GS8051提供SOT23-5和SC70-5封装•轨到轨输出GS8052提供SOP-8和MSOP-8封装•-3dB带宽(G = + 1):250MHz(典型值)GS8054提供SOP-14和TSSOP-14封装•低输入偏置电流:1pA(典型值)GS8051N提供SOT23-6和SC70-6封装•静态电流:2.8mA /放大器(典型值)GS8052N采用MSOP-10封装•工作温度:-40°C〜+ 125°C•小包装:Features•+ 2.5V〜+ 5.5V单电源供电轨到轨输出-3dB带宽(G = + 1):250MHz(Typ。

)低输入偏置电流:1pA(典型值)静态电流:2.8mA /放大器(典型值)工作温度:-40°C〜+ 125°C 小包装:GS8051提供SOT23-5和SC70-5封装GS8052提供SOP-8和MSOP-8封装GS8054提供SOP-14和TSSOP-14封装GS8051N提供SOT23-6和SC70-6封装GS8052N采用MSOP-10封装:General DescriptionGS8051 / 1N(单),GS8052 / 2N(双),GS8054(四)是轨到轨输出电压反馈放大器,具有易用性和低成本。

聚洵半导体,运放ic,模拟芯片

27

Y/Y

TSSOP14

Cross Reference

LMV321 SGM321

LMV321 SGM321

LMV358 SGM358

LMV324 SGM324

应用领域:

血压计,血糖仪 电波钟 低功耗设备 传感器接口 便携式系统 移动通信 可穿戴设备

该文档是极速PDF编辑器生成,

如果想去掉该提示,请访问并下载: /

Cross Reference

MCP6001 TS1871 MCP6001 TS1871 MCP6002TS18

72

MCP6004 TS1874

低噪声运放GS631/8632/8634/8721/8722/8724

产品特性

Product No.

GS8631 GS8632 GS8634

Channel

产品Roadmap

GS321/321Y/358/324

GS8541/8542/8544

低功耗运放

GS6001/6001Y/6002/6004

低压低功耗运放

GS8631/8632/8634 GS8721/8722/8724

低噪声运放

GS8051/8052/8054 GS8091/8092/8094

GS8061/8062/8064 高速运放

-

Rail to Rail Input /Output

N/Y N/Y N/Y N/Y N/Y N/Y

Package

SOT23-5 SC70-5 SOP8 MSOP8 SOP14 TSSOP14 SOT23-5 SC70-5 SOP8 MSOP8 SOP14 TSSOP14

Cross Reference

应用领域:

DAC8562_485模块电路详解及使用说明

目录1、模块功能: (2)2、模块简介:(详细看资料说明) (3)3、电路详解 (6)3.1电源部分 (6)3.2 DAC芯片部分 (7)3.3单片机部分 (8)3.4 RS485部分 (9)4、模块接线和注意事项 (10)6、modbus协议解释 (12)7、模块尺寸 (12)8、模块测试 (13)9、编程器使用 (14)DAC8562_485模块电路详解及使用说明1、模块功能:●使用TI原装DAC8562芯片,2路16位精度独立输出,相当于两块DA芯片并行工作,互不影响。

●发货时模块输出电压范围0-2.5V、0-5V、-5--+5V、-10---+10V、0-10V、0-20V可选,也可以定制其他电压范围。

●模块自带5-36V转-12V、5-36V转5V电源电路,也就是说模块只需要单电源供电就可以使模块正常工作,输出正负电压信号。

●模块自带STC15F408AD工业级单片机,具有8路10位AD采集功能,DAC自动控制功能等。

●标准RS485接口,支持Modbus协议。

●提供完整C语言源程序,所有功能都封装成函数,可以轻松移植到其他任何单片机。

●DAC芯片控制IO全部引出,可以使用模块自带的STC芯片对DAC芯片控制,也可以使用外接的单片机对DAC进行控制。

外接单片机支持3.3V、5V电平。

●送STC下载仿真器一个,USB转TTL,可对模块进行编程、仿真调试,看下图。

●工业级抗干扰设计。

模块全部使用原装芯片,固态电容、钽电容一应俱全,绝不吝啬。

已在工业产品中应用,效果很好。

2、模块简介:(详细看资料说明)1、模块供电12V,本模块可以供电6-36V,但是由于设计模块的DA输出范围为正负10V,所以为了模块正常工作请供电12V。

2、RS485接口,该接口为标准485接口,由于模块使用的是单电源供电,所以没有加光耦隔离(需要完全隔离的双电源,光耦隔离才起作用)。

3、4个0欧电阻,焊接上4个电阻后,DA芯片与单片机连接,可用模块上的单片机控制DA,以实现自动控制。

SILICON LABORATORIES C8051F340 数据手册

C8051F340USB, 48 MIPS, 64 kB Flash, 10-Bit ADC, 48-Pin Mixed-Signal MCUAnalog Peripherals10-Bit ADC-±1 LSB INL; no missing codes-Programmable throughput up to 200 ksps-Up to 17 external inputs; programmable as single-ended or differential -Built-in temperature sensor (±3 °C)Two ComparatorsInternal Voltage Reference: 2.4 V POR/Brown-out DetectorUSB Function Controller-USB specification 2.0 compliant-Full-speed (12 Mbps) or low-speed (1.5 Mbps) operation-Integrated clock recovery; no external crystal required for either full-speed or low-speed operation -Supports eight flexible endpoints -Dedicated 1 kB USB buffer memory-Integrated transceiver; no external resistors requiredOn-Chip Debug-On-chip debug circuitry facilitates full speed, non-intrusive in-system debug (no emulator required)-Provides breakpoints, single stepping-Inspect/modify memory, registers, and USB memory-Superior performance to emulation systems using ICE-chips, target pods, and socketsTemperature Range: –40 to +85 °CHigh-Speed 8051 µC Core-Pipelined instruction architecture; executes 70% of instructions in 1 or 2 system clocks-Up to 48 MIPS throughput with 48 MHz Clock -Expanded interrupt handlerMemory-4352 bytes data RAM (256 + 4 kB)-64 kB Flash; in-system programmable in 512-byte sectors (512 bytes are reserved)-External parallel data memory interfaceDigital Peripherals-40 port I/O; all are 5 V tolerant-Hardware SMBus™ (I 2C™ compatible), SPI™, and 2 UART serial ports available concurrently- 4 general-purpose 16-bit counter/timers-Programmable 16-bit counter array with 5 capture/compare modules Clock Sources-Internal oscillator: 0.25% accuracy with clock recovery enabled; supports all USB and UART modes-External oscillator: Crystal, RC, C, or Clock -On-chip clock multiplier: up to 48 MHzVoltage Regulator-On-chip voltage regulator supports USB bus-powered operation -Regulator bypass mode supports USB self-powered operationOperating Voltage: 2.7 to 5.25 V Package-48-Pin TQFP (lead-free package)Ordering Part Number-C8051F340-GQUC8051F340DK Development KitPackage Information。

AD9952 Evaluation Board Datasheet说明书

功能框图图1.DC/PHASE CORRECTION DC/PHASE CORRECTIONC SS C L KS D I OSERIAL PORT INTERFACE15141323892325262838VPOS_3P3DECL1TO DECL4211119303136273340101VPOS_5VLDO VCOLDO 2.5VRFIN0RFIN12922POLYPHASE FILTERLOIN–REFINLOIN+I+I–Q–Q+QUAD DIVIDERPLL343935547611990-001Rev. ADocument FeedbackInformation furnished by Analog Devices is believed to be accurate and reliable. However , no responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other rights of third parties that may result from its use. Speci cations subject to change without notice. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices. T rademarks and registered trademarks are the property of their respective owners.One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A. Tel: 781.329.4700 ©2013–2014 Analog Devices, Inc. All rights reserved. Technical Support 695 MHz 至2700 MHz 正交解调器,集成小数N 分频PLL 和VCOADRF6820产品特性集成小数N 分频PLL 的I/Q 解调器RF 输入频率范围:695 MHz 至2700 MHz 内部LO 频率范围:356.25 MHz 至2850 MHz 输入P1dB :14.5 dBm (1900 MHz RF) 输入IP3:35 dBm (1900 MHz RF) 可编程HD3/IP3调整单刀双掷(SPDT) RF 输入开关RF 数字步进衰减范围:0 dB 至15 dB集成式RF 可调谐巴伦,支持单端50 Ω输入 多核集成式VCO解调1 dB 带宽:600 MHz 4个可选基带增益和带宽模式数字可编程LO 相位失调和直流零点可通过三线式串行端口接口(SPI)进行编程 40引脚、6 mm x 6 mm LFCSP 封装应用蜂窝W-CDMA/GSM/LTE 数字预失真(DPD)接收器 微波点对点无线电概述ADRF6820是一款高度集成的解调器和频率合成器,非常适合用于下一代通信系统中。

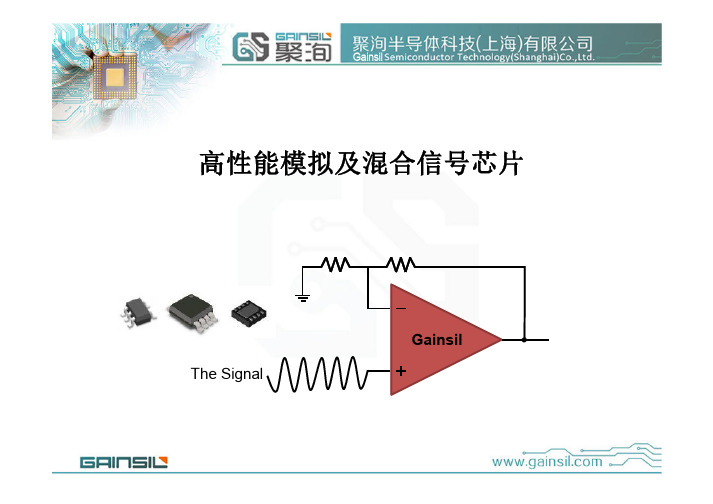

MS8051、MS8052、MS8054资料完整版

MS805x 系列的低失真和快速建立使得它成为 A/D 和 D/A 缓冲器的理想选择。所有的特性工作温度范围为-40℃到 125℃。

产品规格分类

产品 MS8051 MS8052 MS8054

封装形式 SOT23-5/SO-8 SO-8/MSOP-8 TSSOP-14/SO-14

打印名称 MS8051 MS8052 MS8054

应用

图像 光电二极管前置放大器 专业视频设备和照相设备 手持设备 DVD/CD 基站 有源滤波器 模数转换

参

数

符号

测试条件

最小值 典型值 最大值

动态特性

-3dB 小信号带宽

BW G = +1, VO = 0.1Vp-p, RF = 24Ω, RL

180

= 150Ω

G = +1, VO = 0.1Vp-p, RF = 24Ω, RL

250

= 1kΩ

G = +2, VO = 0.1Vp-p, RL = 50Ω

版本号:1.0 2013.2.25 共17页 第1页

瑞盟科技

极限参数

参数

电源电压,V+到 V-

共模电压输入范围

存储温度

结温

工作温度

封装热阻 @TA =25℃

SOT23-5 SO-8

MSOP-8

ESD 敏感度(人体模式)

ESD 敏感度(机器模式)

符号 VDD VCM

TA θJA θJA θJA

80X01和80X02电气采样模块扩展器说明书

80X01and80X02Electrical Sampling Module Extender InstructionsWarrantyWarranty Tektronix warrants that the parts and modules(“parts”)that it manufactures andsells will be free from defects in materials and workmanship for a period of three(3)months from the date of shipment.If any such part proves defective duringthis warranty period,Tektronix,at its option,either will repair the defective partwithout charge,or will provide a replacement in exchange for the defectivepart.Parts and modules used by Tektronix for warranty work may be new orreconditioned to like new performance.All replaced parts and modules becomethe property of Tektronix.In order to obtain service under this warranty,Customer must notify Tektronixof the defect before the expiration of the warranty period and make suitablearrangements for the performance of service.Customer shall be responsible forpackaging and shipping the defective part to the service center designated byTektronix,with shipping charges prepaid.Tektronix shall pay for the return ofthe part to Customer if the shipment is to a location within the country in whichthe Tektronix service center is located.Customer shall be responsible for payingall shipping charges,duties,taxes,and any other charges for parts returned toany other locations.This warranty shall not apply to any defect,failure or damage caused by improperuse or improper or inadequate maintenance and care.Tektronix shall not beobligated to furnish service under this warranty a)to repair damage resulting fromattempts by personnel other than Tektronix representatives to install,repair orservice the part;b)to repair damage resulting from improper use or connection toincompatible equipment;c)to repair any damage or malfunction caused by theuse of non-Tektronix supplies;or d)to service a part that has been modified orintegrated with other products or parts when the effect of such modification orintegration increases the time or difficulty of servicing the part.THIS WARRANTY IS GIVEN BY TEKTRONIX WITH RESPECTTO THE PART IN LIEU OF ANY OTHER WARRANTIES,EXPRESSOR IMPLIED.TEKTRONIX AND ITS VENDORS DISCLAIM ANYIMPLIED WARRANTIES OF MERCHANTABILITY OR FITNESS FOR APARTICULAR PURPOSE.TEKTRONIX'RESPONSIBILITY TO REPAIR ORREPLACE DEFECTIVE PARTS IS THE SOLE AND EXCLUSIVE REMEDYPROVIDED TO THE CUSTOMER FOR BREACH OF THIS WARRANTY.TEKTRONIX AND ITS VENDORS WILL NOT BE LIABLE FOR ANYINDIRECT,SPECIAL,INCIDENTAL,OR CONSEQUENTIAL DAMAGESIRRESPECTIVE OF WHETHER TEKTRONIX OR THE VENDOR HASADV ANCE NOTICE OF THE POSSIBILITY OF SUCH DAMAGES.Copyright©Tektronix*P071320600*Important safety informationImportant safety informationThis manual contains information and warnings that must be followed by the userfor safe operation and to keep the product in a safe condition.To safely perform service on this product,additional information is provided atthe end of this section.(See page2,Service safety summary.)General safety summaryUse the product only as specified.Review the following safety precautions toavoid injury and prevent damage to this product or any products connected to it.Carefully read all instructions.Retain these instructions for future reference.To avoidfire or personalinjury Do not operate without covers.Do not operate this product with covers or panels removed,or with the case open.Hazardous voltage exposure is possible.Do not operate with suspected failures.If you suspect that there is damage to this product,have it inspected by qualified service personnel.Disable the product if it is damaged.Do not use the product if it is damagedor operates incorrectly.If in doubt about safety of the product,turn it off and disconnect the power cord.Clearly mark the product to prevent its further operation.Examine the exterior of the product before you use it.Look for cracks or missing pieces.Do not operate in wet/damp conditions.Be aware that condensation may occur if a unit is moved from a cold to a warm environment.Do not operate in an explosive atmosphere.Keep product surfaces clean and dry.Remove the input signals before you clean the product.Service safety summaryThe Service safety summary section contains additional information required tosafely perform service on the product.Only qualified personnel should performservice procedures.Read this Service safety summary and the General safetysummary before performing any service procedures.Do not service alone.Do not perform internal service or adjustments of thisproduct unless another person capable of renderingfirst aid and resuscitation ispresent.Important safety informationDisconnect power.To avoid electric shock,switch off the product power anddisconnect the power cord from the mains power before removing any covers orpanels,or opening the case for servicing.Terms in this manualThese terms may appear in this manual:WARNING.Warning statements identify conditions or practices that could resultin injury or loss of life.CAUTION.Caution statements identify conditions or practices that could result indamage to this product or other property.Symbols and terms on the productThese terms may appear on the product:DANGER indicates an injury hazard immediately accessible as you readthe marking.WARNING indicates an injury hazard not immediately accessible as youread the marking.CAUTION indicates a hazard to property including the product.When this symbol is marked on the product,be sure to consult the manualtofind out the nature of the potential hazards and any actions which have tobe taken to avoid them.(This symbol may also be used to refer the user toratings in the manual.)The following symbol(s)may appear on the product:Product descriptionEnvironmental considerationsThis section provides information about the environmental impact of the product.Product end-of-lifehandling Observe the following guidelines when recycling an instrument or component: Equipment recycling.Production of this equipment required the extraction and use of natural resources.The equipment may contain substances that could be harmful to the environment or human health if improperly handled at the product’s end of life.To avoid release of such substances into the environment and to reduce the use of natural resources,we encourage you to recycle this product in an appropriate system that will ensure that most of the materials are reused or recycled appropriately.This symbol indicates that this product complies with the applicable EuropeanUnion requirements according to Directives2002/96/EC and2006/66/ECon waste electrical and electronic equipment(WEEE)and batteries.Forinformation about recycling options,check the Support/Service section of theTektronix Web site().Restriction of hazardoussubstances This product is classified as an industrial monitoring and control instrument accessory,and is not required to comply with the substance restrictions of the recast RoHS Directive2011/65/EU until July22,2017.Product descriptionThe80X01(one-meter)and80X02(two-meter)electrical sampling moduleextender cables(referred to as the extender cable or the extender in this document)are for use with supported electrical sampling modules.(See page5,Supportedmodules.).Use the extender to move the sampling module from its instrument compartment,closer to the device under test,so that you can use shorter signal ing theextender avoids input-signal degradation that can occur when using long-lengthsignal cables between the sampling module and the device under test.Product descriptionSupported sampling oscilloscopesThe extender cable is for use with the following sampling oscilloscopeinstruments:DSA8300Digital Serial AnalyzerLegacy sampling oscilloscope instruments:DSA8200Digital Serial AnalyzerCSA8000,CSA8000B,and CSA8200Communications Signal AnalyzersTDS8000,TDS8000B,and TDS8200Digital Sampling OscilloscopesSupported modules80E01,80E02,80E03,80E04,80E06,80E11,and80E11X1Electrical samplingmodulesOther modules82A04BGuidelinesObserve the following guidelines to avoid damaging your sampling modules orinstruments:The extender cannot be used with any large-compartment modules.Some small modules are mechanically blocked from use with the extender.When connecting an80X02extender to an80X01extender,connect theextenders in the following order:Instrument-80X02-80X01-samplingmodule.Always wear a grounded wrist strap,grounded foot strap,and static resistantapparel while installing module extenders and modules.Observe standard anti-static handling precautions when connecting signalcables to sampling modules.Change to instrument operating temperature range when using80X01or80X02When you install one or more of the extenders in an instrument,the upper end ofthe instrument operating temperature range changes as follows:No extender cable(s)installed:+10°C to+40°CWith extender cable(s)installed:+10°C–+35°CInstallation instructionsChange to minimum horizontal position when using80X01or80X02Installing the80X01or80X01extender cable increases the minimum horizontalposition setting as follows:80X01:+5ns80X02:+10nsThis affects waveforms acquired from all modules,extended or not.Horizontalposition is a global setting.Installation instructionsCAUTION.For the DSA8300with TekScope software version6.1.X or greater,follow proper module exchange procedures to remove,install,or exchangemodules or module extenders with the instrument powered on(View/ChangeModule Config tool).Refer to the product documentation for instructions.For all legacy instruments(DSA8200Digital Serial Analyzer,CSA8000,CSA8000B,and CSA8200Communications Signal Analyzer,TDS8000,TDS8000B,and TDS8200Digital Sampling Oscilloscopes),andDSA8300instruments with TekScope software version6.0.X,power off theinstrument before removing,installing,or exchanging modules or moduleextenders.Removing or installing modules in these instruments while powered onmay result in damage to the module and/or mainframe instrument.Always wear a grounded wrist strap,grounded foot strap,and static resistantapparel while installing this module extender and any modules.Observe standard anti-static handling precautions when connecting signal cablesto sampling modules.NOTE.DSA8300Digital Serial Analyzer instruments with TekScope softwareversion6.1.X or greater have a View/Change Module Config function that allowsremoving,installing,or exchanging modules or module extenders while the maininstrument is powered on.All earlier instruments,and earlier TekScope softwareversions,require that you power off the main instrument before removing,installing,or exchanging modules or extenders.NOTE.The80X02sampling module extender is keyed to prevent connecting todevices not intended to be extended and to prevent two or more80X02extendersfrom being connected in series.To connect an80X02extender to an80X01extender,connect the cables in thefollowing order:Instrument-80X02-80X01-sampling module.Installation instructions Do the following steps to install the extender between the instrument and the electrical sampling module:1.Connect an antistatic wrist strap to the instrument front-panel groundconnection.Place the strap on your wrist.2.Remove power:DSA8300(with TekScope software version6.1or later):Run theUtilities>View/Change Module Config tool;follow on-screeninstructions to remove a module and/or install the“To Instrument”end ofthe extender in a small module slot.Then go to step4.DSA8300with TekScope software version6.0X,and all Legacyinstruments:Push the On/Standby button on the front panel to poweroff the instrument.If there is a module in the slot where you are installing the extender,remove the module after the instrument has powered off. 3.Install the extender connector labeled To Instrument into a suitable slot inthe instrument.See the sampling module user manual if you require more information.4.Attach the connector marked To Sampling Module to a supported samplingmodule.(See page5.)5.Apply power to the module:DSA8300(with TekScope software version6.1or later):Click theFinish button in the View/Change Module Config tool.This appliespower to the module slot.DSA8300with TekScope software version6.0X,and all Legacyinstruments:Push the On/Standby button on the front panel to poweron the instrument.Wait for the boot-up cycle to complete.Installation instructions6.Run a compensation on each channel of all newly installed modules or moduleextenders(select Utilities>Compensation).You must run compensation,even if module(s)and/or extenders were moved from one slot to another.Seethe instrument documentation or TekScope application help for instructionson how to run compensation.7.You can now use the instrument to take measurements.NOTE.Check the module compensation status for thefirst20minutes byviewing the compensation status icon on the instrument user interface,or byquerying the compensation status from the programmatic interface.It may takeup to20minutes for the sampling module on the extender cable to reach astable temperature.If the compensation status indicates that a module requirescompensation,rerun compensation on the module to be sure that the instrumentand module are within measurement accuracy specifications.。

芯海科技 32位MCU系列 产品手册

芯海科技产品手册CHIPSEA PRODUCT MANUAL芯海科技成立于2003年9月,是一家集感知、计算、控制、连接于一体的全信号链集成电路设计企业。

专注于高精度ADC、高可靠性MCU、测量算法以及AIoT 一站式解决方案的研发设计。

产品和方案广泛应用于工业测量与工业控制、通信与计算机、锂电管理、消费电子、汽车电子、智慧家居、智能仪表、智慧健康等领域。

公司总部位于深圳,在合肥、西安、上海、成都设立子公司,是国家级高新技术企业,被广东省科技厅认定为“广东省物联网芯片开发与应用工程技术研究中心”,获得国家级专精特新“小巨人”称号。

建有可靠性检测中心、健康测量实验室、感知实验室、MCU实验室。

公司年均研发投入超过20%,研发人员占比近70%,核心成员均有10年以上工作经验。

截止到2022年上半年,芯海科技累计拥有全球专利申请近800件,累计拥有已授权专利近350件(含美国专利),拥有专利数量在科创板芯片设计上市公司中名列前茅。

企业简介ABOUT CHIPSEA1523健康测量信号调理数据转换器模拟前端32位MCU 8位MCU010406091113信号链无线产品低功耗蓝牙开发生态开发生态鸿蒙智联解决方案OKOK智能物联解决方案健身行业SaaS 解决方案2021221719电源管理AIoT产品快 充电池管理MCUC H I P S E A32位MCU系列产品概述芯海科技的CS32系列32位MCU基于Arm®Cortex®-M处理器,内嵌Flash存储器,集成高精度ADC和丰富的模拟外设。

该产品系列品类齐全,同时保持了集成度高和易于开发的特点,提供了丰富的软件和开发工具支持,广泛应用于工业控制、汽车电子、智能家居、消费类电子等领域。

产品特色典型应用高可靠低功耗高精度32KB64KB 128KB 256KB 512KB 1024KB ��TWS电子烟电表电动自行车扫地机器人无人机C H I P S E A 产品选型C H I P S E AC H I P S E A8位MCU系列产品概述芯海科技的8位MCU采用芯海科技自主知识产权的8位RISC内核,并集成12位ADC、内部基准电压、OTP或Flash存储器、PWM等资源,支持C语言开发,具有低功耗、易开发等特点。

ADC0804Philips说明书翻译

ADC0804Philips说明书翻译ADC0804翻译ADC0804说明书ADC0803芯片族是一个系列,它是由三个8位的CMOS逐次采用逐次比较型的A / D转换器和一系列的电容外加一个自动调零的比较器组成的。

这些转换器是为了满足使微处理器的控制总线使用最少的外部线路而设计的。

三态输出数据线可以直接连接到数据总线上。

差分模拟输入电压能够有助于共模抑制,并提供了一种调整零刻度偏移方法。

此外,参考电压的输入提供了一种手段将晓得模拟电压编码成为一个完整的8位编码。

?5 V单电源?保证规格为1 MHz的CLOC图1.引脚说明应用?传感器到微处理器接口?数字温度计?数字控制的自动调温器?微处理器为基础的监测和控制系统特点?兼容大多数微处理器?差分输入?三态输出?逻辑电平与TTL兼容的MOS ?可使用内部或外部时钟使用?模拟输入范围为0 V至V CC订购信息1ADC0804翻译极限参数注意:1避免环境温度高于25 °C,遵循如下比率:N封装为13.5 mW/°C;D 封装为11.1 mW/°C.框图图2.框图2ADC0804翻译直流电气特性注意:1、逻辑电压输入必须保持在:–0.05 ≤V IN ≤V CC + 0.05 V;2、参考输入典型电压VCC =5 V;3、为了防止锁存错误,V REF /2 和V IN必须在Vcc已经打开的前提下才可以使用。

3ADC0804翻译AC电气特性1. 精度最好保证在f CLK=1MHz。

在更高的时钟频率时,准确度可能会降低。

功能描述该设备采用逐次比较型。

模拟开关由于连续相近的逻辑值被顺序地关闭,直到输入到自动调零比较器的电压[V IN(+)- V IN(- )]与解码器的电压相匹配。

在所有的位被测试和确定后,与输入电压相应的8位二进制码被输送到输出锁存器上。

如果在CS输入为低且WR有一个脉冲传来则转换开始。

当WR或者CS的输入端发生了一个有高电平到低电平的跳变信号,SAR被初始化,移位寄存器复位,而INTR输出被设置为高电平。

TI 经典模数转换器讲解之ADS805

TI 经典模数转换器讲解之ADS805

模数转换器,ADS805,速度不算太快,但是一般情况下就够用了,整体

综合性能还是蛮好的。

它可以用在CCD 成像、数字化基带处理、复印机和测试仪器等等。

特性:

1.20MHz 、12 位,高动态范围

2.高信噪比68dB

3.内外参考电压

4.具有输入超调警示标志,在信号调理电路中能够利用此标志进行增益减小

调节

5.数字识错技术保障良好的线性度

1 管脚具有超过限定值指示功能15 管脚为输出使能端

18 管脚为输入变化范围选择

19 管脚为参考电压选择端

20、22 管脚分别为底层参考和顶层参考

23 管脚为补充输入端

28 为给入的输出驱动电压

图3 时序图通过以上时序图可以知道,在六个时间循环中完成一次数据转换。

这个信号是交流单耦合截至形式指向ADS804,使用低失真电压反馈放大器OPA642,顶部和底部引用(REFT,REFB)提供一个+3V 和+2V 参考电压,在这里,两个电阻对(2 x 2kΩ)是用于创建一个共模电压约+2.5V 到偏置的ADS805 的补充输入电压。

Silicon Labs微控制器C8051F系列100MIPs CPU单片机12ADC 12DAC

增加了中断源

标准的8051只有7个中断源,而Cygnal C8051F系列单片机扩展了中断处理,这对于时实多任务系统的处理是很重要的。扩展的中断系统向CIP-51提供22个中断源,(英格迪电子13510285528只做原装)允许大量的模拟和数字外设中断。一个中断处理需要较少的CPU干预,却有更高的执行效率。

对于开发和调试嵌入式应用来说,与用传统的专用仿真芯片、目标电缆及仿真头的仿真器相比,更具优越性能,更能真实“在片”(英格迪电子13510285528只做原装)仿真实时信息。Cygnal的调试环境既便于使用又能保证精确模拟外设的性能。

Cygnal C8051F系列单片机开发工具即突破了昂贵开发系统旧模式,又创立了低价位仿真新思路。为应用技术的开发提供了极大的方便

5软件强制复位

6 CNVSTRAD转换启动

7 外部引脚RST复位可双向复位

8 提供内部时钟源

标准的8051只有外部时钟,Cygnal C8051F系列单片机有内部独立的时钟源。C8051F300/F302提供的内部时钟误差在2%以内,在系统复位后默认内部时钟。(英格迪电子13510285528只做原装)如果需要,可接外部时钟并可在程序运行时实现内外部时钟之间的切换。外部时钟可以是晶体RCC或外部时钟脉冲,以上的功能在低功耗应用系统中非常有用。[1]

3,定时器0溢出

4,外部时钟输

5,ECI系统时钟

6,外部振荡源频率(8C8051F00x/01x没有后两个时钟源)

每个捕捉/比较模块都有4或6种工作方式(边沿触发)捕捉软件定时器高速输出8位脉冲宽度调制器频率输出16位脉冲宽度调制器C8051F00x/01x没有后两种工作方式PCA捕捉/比较模块的I/O和外部时钟输入可以通过数字交叉开关连到I/O端口引脚[1]

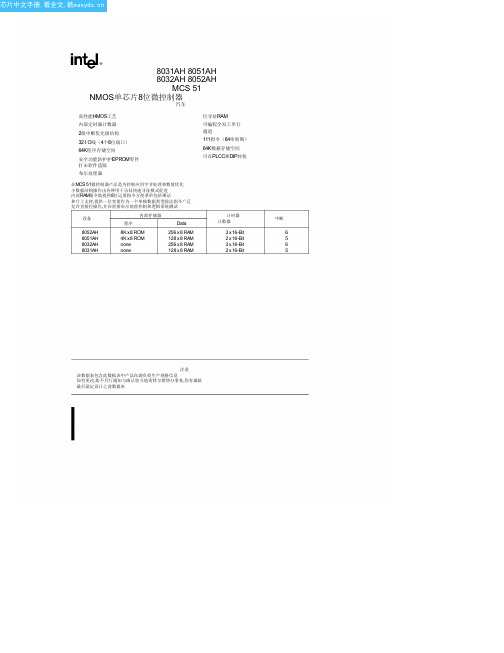

8052AH中文资料(Intel)中文数据手册「EasyDatasheet - 矽搜」

注意 该数据表包含此数据表中产品在满负荷生产规格信息

如有更改,恕不另行通知与确认您当地英特尔销售办事处,你有最新

最后敲定设计之前数据表

芯片中文手册,看全文,戳

车用微控制器MCS 51

产品选项

Intel扩展和汽车级温度范围

产品设计以满足这些需求 应用程序运行要求超过 商业标准

端口2

端口2是一个具有内部8位双向IO端口 上拉港口2输出缓冲器能驱动源4 LS TTL输入端口2引脚有1秒写入

他们是拉高由内部上拉和

该国可以作为输入作为输入端口2

引脚被外部拉低时将输出电流

(IIL 就因为内部上拉数据表) ups

端口2时发出高位地址字节 从外部程序存储器,并在取 访问使用16位外部数据存储器 地址(MOVX DPTR)在该应用中它

小数据结构操作由各种用于访问快速寻址模式促进

内部RAM指令集提供8位运算指令方便菜单包括乘法 和片上支持,提供一位变量作为一个单独数据类型除法指令广泛 允许直接位操作,并在需要布尔处理控制和逻辑系统测试

设备

内部存储器

程序

Data

8052AH 8051AH 8032AH 8031AH

8K x 8 ROM 4K x 8 ROM none none

塞斯外部数据存储器

PSEN

编程使能是读选通到外部 程序存储器

当该装置从外部执行代码

程序存储器PSEN被激活两次,每次马 折角周期,除两个PSEN激活

在每个访问外部数据被跳过 记忆

EA V PP

外部访问允许EA必须与V 为使所有MCS 51单片机DE副从外部程序存储器取指, 地点0至0FFFH(0到1FFFH在8032AH 和8052AH)

基于8051微控制器的广告牌设计

10 O 10 0

1 加

单 片 机 P 口低 4 位 输 出 的 行 号 经 两 片 7H 1 8 成 1 4C3 组 的4 / 6 线 译 码 器 译 码 后 生 成 1 条 行 选 通 信 号 线 , 再 经 过 8 1 6