HMD4M36M9EAG-6中文资料

MEAN WELL 六槽产品介绍说明书

Six-NicheNew Product IntroductionDate: 27.10.2022Hank Lan6-Niche Product LinesGreen Energy Power SolutionsCharger Product CategoryCategorySectionPhotoSeriesWarrantyRemarkPortableDesktop styleENP/ENC Series 120/180/240/360W 3years Programmable Adaptor styleGC Series30/120/160/220/330W 2years Constant Voltage PA/PB Series 120/230W NPB Series 120/240/360W 3yearsBasic Programmable Voltage(NPB-120~360)StationaryScrew MountedPB Series 300/360/600/1000W NPB/NPP Series 450/750/1200/1700W 3years NPB: Intelligent auto-rangingNPP: Charger + Power 2 in 1RPB/DBU Series1600/3200W5yearsProgrammable HEP Series600/1000W6years1.Potted, Suitable for Harsh Environment 2.Programmable Rack-mountedRCB/DBR Series 1600/3200W 5 years1.Rack type, hot swap2.Programmable NEW NRND NEWNRNDBatteries CharacteristicsLithium Manganese Oxide (LiMn2O4)Lithium Cobalt Oxide (LiCoO2)Lithium Nickel Manganese Cobalt Oxide (LiNiMnCoO2)Lithium Nickel Cobalt Aluminum Oxide (LiNiCoAlO2)Lithium Iron Phosphate (LiFePO4F)LithiumTitanate(Li4Ti5O12)Absorbent Glass Mat (AGM)Enhanced Flooded Battery (EFB)Lead AcidSealed MaintenanceFree (SMF)CompleteMaintenance Free(CMF)Zenite Nihonium (ZiNn)•Complete Power : 120/240/360/450/750/1200/1700W•Complete Model : Basic NPB-120~360, Intelligent NPB-450~1700,Power supply +Charger NPP-450~1700•Intelligent Function : Auto Battery Sensing Function Charging (Patent),Built-in CANBus Protocol (NPB-450~1700)•Flexibility : Adjustable 2or 3stage Charging,Adjustable Charging Parameter (NPB)•Wide Vo Range: 12V (10.5~21V ) / 24V (21~42V ) / 48V (42~80V ) / 72V (54~100V )Covers most Lead-acid & Li-ion batteries voltage range Modification (MOQ) not needed•Smaller Size :0~45% smaller size compared to same power old gen PB series •Approvals :CB,UL, DEKRA CE/UKCA certification (62368-1+60335-2-29)•Application :Camper Van,Medical Cart, Electric Unicycle, AGV, AMR,Battery-powered Scrubber, Power Tools, Security/Fire alarm UPS and more Charger New Product IntroductionNPB / NPP FeaturesNPB SeriesNPP SeriesOutput Power 120W 240W 360W 450W 750W1200W1700W450W750W1200W1700WProduct Type Basic Charger Professional Intelligent ChargerPower Supply + Charger 2-in-1Auto Ranging ( Patent: CN111711254B )Vo Adj.( Equipped with auto ranging mode )Io Adj.CANBus Charging Stage Adjustable 2-stage or 3-stage Fixed 3-stage Suitable Batteries Lead-acid, Li-ion Lead-acid Price$$$$$$Charger New Product IntroductionNPB vs. NPP ComparisonNPB Basic Function Introduction –Charging Curve Setting (NPB-120~360series)SW Position3-stage 2-stage OFFONAuto-Ranging Mode operation onlyCharging Curve can be set via SBP-001 with computerOperating Mode SettingCharger (Factory Default)Jumper Removed Power SupplyJumper ConnectedJumper provided as accessoryCharger Power Supply setting by JumperVo/Io Adjustment Vo x Io ≤Rated Power and meet Vo vs. Io curveCharger AccessoryAccessory–Mounting bracket , Carry HandleNPB-120/240/360Series NPB/NPP-450/750/1200/1700 SeriesInverter Product CategoryCategory Product Image Series Warranty RemarkTrue Sine Wave TS Series200 /400 /700 /1000 / 1500 / 3000W3YearsTN Series1500 / 3000W Built-in AC/SolarChargerNTS Series Built-in:250W /400WExternal: 300/450/750/1200/1700/2200/3200WMEAN WELLExclusive Design NTU Series1200/1700/2200/3200WBuilt-inAC-bypass(UPS function)ISI Series500W Built-in MPPTSolar ChargerSquareSine WaveA301/2Series100/150/300/600/1000/1700/2500W 1 Year NEWNEWNRND•Full range product :Built-in Type NTS-250P/400P ( PCB Type -Exclusive product by MEAN WELL )External Type NTS-300/450/750/1200/1700/2200/3200,NTU-1200/1700/2200/3200•Environment Friendly :Packaging Eco FriendlyNo load dissipation <1.2~1.7W (NTS)•Smaller size :4~37%smaller size compared to same power old gen TS series,Casing screw hole spacing same as TS,easy for replacement•Flexibility :DIP S.W adjustable AC output voltage, frequency, saving mode -User friendly interface •Wide Input Range: 12V(10~16.5V )/24V (20~33V )/48V (40~66V ),Suitable for Lead-acid + Li-ion.Modification (MOQ) not needed.•Multiple Output Socket :EU,US, UK(Optional), AU(Optional), CN, UN •Common Application :No AC Grid,UPS Backup Supply,e.g.:Vehicle,Vessel, Regions with unstable power grids,Fire Alarm facility backup and moreInverter New Product IntroductionNTS/NTU FeaturesAC Voltage / Frequency SettingSW1SW2SW3OFF OFF 100Vac or 200Vac ON: 50Hz OFF ON 110Vac or 220Vac ON OFF 115Vac or 230Vac OFF:60HzON ON120Vac or 240VacBy SW1~3Energy Saving ModeSW4Load Condition Output Status ON:Energy Saving Mode < 10W (3sec)OFF >25WON OFF:Non-Saving ModeAlways onBy SW41.Send a load detection pulse every 3s2.Internal processor calculates the loading condition3.Decide either stand-by or output continuous power based on output currentSupport IRC1 / IRC2 / IRC3 & RS-232 / UARTNTS-250P/400P NTS-300/450NTS-750/1200/2200/3200NTU-750/1200/2200/3200 IRC 1/2/3X XRS-232 / UART(UART)XUPS Function X X XCharger/Inverter New Product IntroductionCharger and Inverter Paired OperationBattery Charger Standalone InverterAC-DC Charger (NPB series)DC-AC Inverter (NTS series)Application Example–RV Camper VanNPP-1700-48→Charge48V Bat.→ TS-700/3000-148→ microwave, fridge, AC…SD-1000L-12 12V →igniter, toilet flush motorApplication Example –Medical CartENC-180-12→ Charge 12V Bat. → TS-200-212B→ monitor, printerApplication Example –Portable Light TowerNPB-360-24→Charge 24V Bat.→TS-3000-224B→HLG-320→ LED Light TowerCharger/Inverter New Production IntroductionPotential Market•Handheld drill •Lawn mower•Tapping machine •Electric screwdriver •Detached house (Appliances...)•Vehicle (Caravan, ambulance …)•Boat (Air conditioner, TV …)•Medical cart (Monitor, AC ..)•Security & Fire alarm •Factory UPS •Office UPS•Household UPS•E-bike / scooters •Golf cart •Hoverboard •AGVElectric VehiclesRechargeable Power toolsNon-grid-tied Power SourceUtility PowerBackupOnline Expo–Landing Pagehttps:///inverter/NTS/EN/index.htmlSecurity Power SolutionsProductProfile Type SeriesName WattFunctionDesign ref.SafetyWarranty ChargerChargingAdj.UPS ACokDCOKBAT.LowNoBAT.Alarm ComBasicEnclosed SCP35W50W75W2yrsAD55W155W2yrsAdvanceLAD120W240W360W600W(TTL)(TTL)(buzzeroptional)(360/ 600WU A R To p t i o n a l)GB179453yrsOpen-FramePSC35W60W100W160W(RELAY)(TTL)2yrsDin-Rail(QuickAttach)DRC40W60W100W180W(RELAY)(TTL)3yrs 240W UL2524Security Power Quick Selection Table© 2022 MEAN WELL All rights reservedLAD (2022.8launch)AD (2000.10launch)Series LAD-120/240/360/600(Basic)LAD-360U /600U (UART communication)AD-55/ 155Output Power 120W /240W/360W/600W360W/600W55W/155W VoCH1 Power 13.8V/27.6V/41.5V/55.2V (360W/600W: 41.5V/55.2V)13.8V/27.6VCH2 Charger FunctionUPS AC OKTTL signal UART communicationBat. Low Polarity Bat.Full BuzzerAC and DC Switches Protection SC /OLP /OVP /OTP /Bat. Low / Reverse Polarity ProtectionSC /OLP /OVPSafety Approval CB/UL/EAC/RCM/CE/UKCA ; Design refer to GB17945CB/TUV/UL/EAC/CE/UKCAWarranty3 years2 yearsSecurity Power New Product IntroductionEconomical Enclosed LAD SeriesNEWLAD Series TTL Signals FunctionLAD-120/240series TTL signalsLAD-360/600(U) series TTL/(UART)signalsWith general purpose industrial PSU, security system needs to designcontrol board for AC OK, battery disconnect/reverse polarity & battery low Complicated circuit design and high costLAD series built-in these TTL signals to read AC Ok,Battery disconnect/reverse polarity, Battery low, Battery full and Discharge signal.AC Main/Battery Backup On/Off SwitchFire Safety Alarm System requires manual ON/OFF Switch for AC main supply power and Battery Backup power. Installed AC ON/OFF and Battery Backup ON/OFF Switches →Increase CostLAD series built-in AC ON/OFF & Battery Backup →Lower CostBattery BackupSwitchAC main SwitchNote: Battery Backup switch : Disconnect backup supply but battery can still be charged.ACmainsBat. BackupSecurity Power New Product IntroductionDIN-Rail Security Power DRC-180 Series•Series Model:DRC-40 / 60 / 100 / 180•Application method:Battery+DRC-180 +DC Load parallel with DC-BUS•New product features:✓Combine Power Supply+DC-UPS function (2 in 1), suitable for space limited condition ✓Built-in charger (13.8V/4A、27.6V/2A)✓Built-in AC OK , battery low alarm signal✓Battery reverse polarity protection by fuse✓Suitable 12V/24V system,Lead-Acid / Lithium-Ion battery•Application: Security system,Emergency Lighting,Fire alarm system,Access system,Car parkSecurity Power New Product IntroductionDRC-180 Application Diagram•Series Model:DRS-240 /480, Output Voltage:12V/24V/36V/48V•Digital all-in-one design =power supply + charger + DC-UPS + monitor (MODBus )•90~305Vac input,cover North America 277Vac market•Complete monitor features:AC Fail, Charger Fail, BAT. Low, DC OK, LED status…•Suitable for various battery types :•Charging current adjustable 20~100% •2-stage or 3-stage charging configurable•Safety:UL/EN 62368-1, EAC, CE, UKCA Design refer to:UL2524, EN54-4, GB17945•Application:B.A. (BDA), fire alarms, emergency lighting, etc.•Release date:2022.3Security Power New Product IntroductionAll-in-one Intelligent Security Power DRS seriesDRS-240/480 FeaturesDC OutputAlarm Relays (From-C)Connector: Temperaturecompensation, Address,Force start (UVP 87%→70%)MODBus,CANBus,SBP-001InterfaceBattery Start ButtonSVR Charging Io Adj.DIP SW, 2/3-stagesetting, curve selectionAC Input TerminalBattery Terminal•Series Model :DUPS20/40•Application :Power Supply + DUPS20/40 + Battery Parallel to DC Bus,A Peripheral DC-UPS module that can be use with SDR/NDR up to 960W•New Product Features:✓Digital design, high accuracy voltage/current detection ✓20A (480W) and 40A (960W) dual power level models✓Suitable for 24V systems, support Lead-acid or Li-Ion batteries•Application:factory automation, semiconductor fabrication, security monitoring system, fire alarm system, data center, parking lot, etc. where backup UPS is required•Release date:2021.9, DR-UPS40 is on NRND list, please recommend DUPS40Security Power New Product IntroductionDC-UPS Module DUPS20/40 SeriesApplication Example –Public Safety UPSApplication Example–Bi-Directional Amplifier6-Niche New Product SummaryApplicationProductsCategorySeriesGreen EnergyandEnergy StorageChargerNPB-120/240/360/450/750/1200/1700 WNPP-450/750/1200/1700 WInverter NTS-250P/400P/300/450/750/1200/1700/2200/3200 W NTU-1200/1700/2200/3200 W DC-DC SPOL-01/12N78SecurityEnclosedLAD-120/240/360(U) /600(U) W DIN-RailDRC-180 WDRS-240/480 W DUPS20/40ITEAdaptorGST360A/BApplicationProductCategory Series Application Est. ReleaseGreen EnergyandEnergy Storage Adaptor GPD100100W Type-C PD Charger2023.Q1(Under development)DC-DC DDRH-15/30/45/120/240RSDH-150/300PV system peripheral power supply2023.Q1(Under development) DIN Rail HDCB-1C10AHVDC circuit protection device•100~800VDC short circuit protection•Pre-charge, Remote control,Monitoring, Resettable•Pair with HVDC centralized power2023.Q2(Planning) Inverter NTN-5000AC power backup (mini-generator)•Home energy storage•Portable power station2023.Q3(Planning)6-Niche Under-Development/PlanningNEW Inverter NTS/NTU and Charger NPB/NPP are fully released, speed up PB/TS replacementGreen EnergyFrom single device to building system,MEAN WELL has complete security power products Promote PSC/SCP/LAD /DRC /DRS seriesSecuritySummary –6-Niche Product Line Promotion StrategyNiche Market .Niche Products .Value Added .Higher MarginRight timingNiche Market。

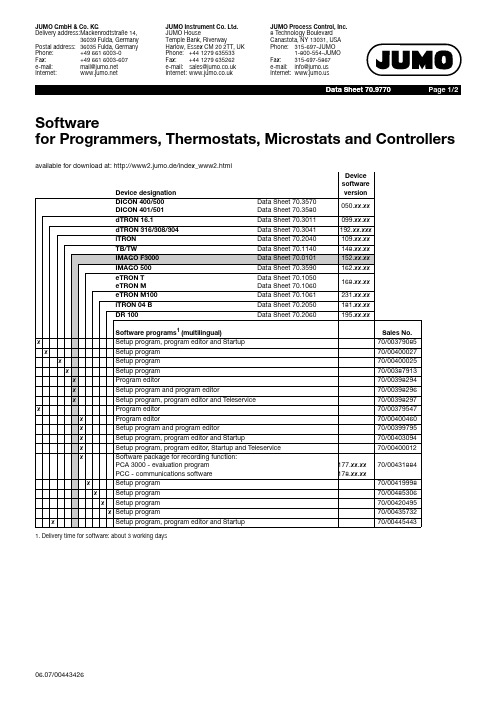

JUMO设备型号说明书

Page 2/2

Accessories for Programmers, Thermostats, Microstats and Controllers

Device designation

DICON 400/500 DICON 401/501

Data Sheet 70.3570 Data Sheet 70.3580

Software programs1 (multilingual)

x

Setup program, program editor and Startup

x

Setup program

x

Setup program

x

Setup program

x

Program editor

x

Setup program and program editor

e-mail:

mail@

Internet:

JUMO Instrument Co. Ltd. JUMO House Temple Bank, Riverway Harlow, Essex CM 20 2TT, UK Phone: +44 1279 635533 Fax: +44 1279 635262 e-mail: sales@ Internet:

eTRON T eTRON M

Data Sheet 70.1050 Data Sheet 70.1060

eTRON M100

Data Sheet 70.1061

iTRON 04 B

Data Sheet 70.2050

mTRON

Data Sheet 70.4010 ... 45

蒙特塞姆36英寸x24英寸工具柜和橱柜说明书

OWNER'S MANUAL36" X 24" TOOL CHEST AND CABINETM362404CH/M362406TCLIFE ORGANIZEDMontezuma is committed to helping you succeed in both your workand personal life by being organized, prepared and equipped withthe right tools, gear and home supplies at your finger tips.We are here to ensure that your life is organized.Thank you for your purchase of this Montezuma Tool Chest and Cabinet.ATTENTIONTO REDUCE THE RISK OF INJURY, THE USER MUST READ ANDUNDERSTAND THIS INSTRUCTION MANUAL BEFORE USING THIS PRODUCT FOR THE FIRST TIME. SAVE THESE INSTRUCTIONS FOR FUTURE REFERENCE.Fill in the following information and retainthis owner's manual for future reference:MODEL(S):DATE OF PURCHASE:PLACE OF PURCHASE:RECEIPT NO:2SPECIFICATIONSMAXIMUM PRODUCT WEIGHT (INCLUDING CONTENTS): 1,800 lb (816 kg) MAXIMUM DRAWER WEIGHT: 150 lb (68 kg)POWER STRIPMODEL: LTS-04C/CH-04FSURGE PROTECTIVE DEVICESRATING: 120 V AC 15 A 60 Hz 1875 WUSB: TOTAL 2.1 A – Check your device for compatibilityUSB O/P: IT EQUIPMENT ONLYVPR: 500-1000 V (L-N) TYPE 3 SPDCONFORMS TO UL STD. NO 1363 AND ANSI/UL STD. NO. 1449CERTIFIED TO CSA STD. C22.2 NO. 308&8336" x 24" 4-DRAWER TOOL CHESTM362404CHOVERALL DIMENSIONS:36-5/8" W x 24-5/8" D x 25" H(93 cm W x 62.5 cm D x 63.5 cm H)NET WEIGHT: 143.3 lb (65 kg)INSIDE TILL/DRAWER DIMENSIONS:REF DIMENSIONS QTYA 33-5/8" W x 23-3/8" D x 8-1/2" H (85.3 cm W x 59.4 cm D x 21.7 cm H)1B 32-1/2" W x 21-1/8" D x 2-3/8" H(82.5 cm W x 53.8 cm D x 5.9 cm H)436" x 24" 6-DRAWER TOOL CABINET M362406TCOVERALL DIMENSIONS:36-5/8" W x 24-5/8" D x 41-1/8" H(93 cm W x 62.5 cm D x 104.5 cm H)NET WEIGHT: 249.12 lb (113 kg)INSIDE DRAWER DIMENSIONS:REF DIMENSIONS QTYA 32-1/2" W x 21-1/8" D x 2-3/8" H(82.5 cm W x 53.8 cm D x 5.9 cm H)3B 32-1/2" W x 21-1/8" D x 5-1/4" H(82.5 cm W x 53.8 cm D x 13.4 cm H)2C 32-1/2" W x 21-1/8"D x 8-1/4" H(82.5 cm W x 53.8 cm D x 20.9 cm H)1* Dimensions do not include side handles.45CHEST PARTS LISTToorderreplacementparts,*****************************************************(Monday–Friday, 8:00 am–4:30 pm, CST). Have the part number and quantity ready. Replacement keys may be ordered using the code that appears on the face of the lock. Not all parts are covered under warranty. Those parts not covered can be purchased.REF DESCRIPTION PART NUMBERQTY 1Chest Handle30188312M4 x 12 mm Phillips Head Bolt 32008423Gas Strut 30320224Grommet 31402725Power Strip 33305916Till Liner55209317Lock and Key (1201–1204)30416628Drawer Liner 55188449Slide Set 300380–300381410Connector240091211M6 x 12 mm Hex Bolt3210514The keys are taped to the top storage area of the chest.6Toorderreplacementparts,*****************************************************(Monday–Friday, 8:00 am–4:30 pm, CST). Have the part number and quantity ready. Replacement keys may be ordered using the code that appears on the face of the lock. Not all parts are covered under warranty. Those parts not covered can be purchased.REF DESCRIPTION PART NUMBERQTY 1Work Top 57201412Power Strip 33305913Grommet 31402714Cabinet Handle30614225M6 x 12 mm Phillips Head Bolt 320323106Cord Wrap 23687017Slide Set 300380–30038188Swivel Caster 30223129Washer3240021610M8 x 25 mm Hex Bolt 3210471611Drawer Liner 551884612Rigid Caster302232213Lock and Key (1201–1204)3041661They keys are taped to the top of the caster carton, which isplaced in the bottom drawer of the cabinet.HANDLE INSTALLATION NOTE: Assemble the handles first to make iteasier to move the cabinet.Position the handles over the holes in thecabinet and attach with the M6 x 12 mmPhillips head bolts provided. Tightensecurely using a 10 mm socket.CASTER INSTALLATION CAUTION: Two or more people are requiredto lay down or stand up the cabinet. Use theside handles for assistance. DO NOT standin front of or behind the product during thisprocess. Lock drawers before proceeding.Carefully lay the cabinet on its back, with asoft mat underneath for protection.Position the two swivel casters on thecabinet bottom, on either the left or rightside. Insert four M8 x 25 mm hex boltsthrough washers, then through each casterPOWER STRIP INSTALLATION Cut the black strip holding the cord, thencabinet and through the grommet. Tightenthe grommet.CHEST AND CABINET CONNECTIONCAUTION: Two or more people may be Array required to complete this step.NOTE: It is not required to remove theworktop attached to the cabinet. If you dowant remove the worktop, first remove thedrawers, then unbolt the worktop.Place the chest on the cabinet. Attach theconnectors to the chest, making sure thehook head snaps in the square hole on theback of the chest. Fasten the M6 x 12 mmhex bolts to the cabinet.8RAISE AND RELEASE DRAWER FRONTSThese units are equipped with raise andrelease drawer fronts. To open, lift up on thedrawer front while pulling towards you. Toclose, shut the drawer firmly until the latchengages.LiftIf the drawer does not stay closed, the hookmay be bent, or it may be rubbing againstthe drawer slides. To fix this problem, lightlybend the hook until the drawer will engagein the slide.DRAWER REMOVALPull the drawer out so that it’s almost fully extended. Push up on the black release leveron one side, while pushing down on the black release lever on the other side. While holding the levers in these positions, pull the drawer outward until it is released from the drawer slide.ONE SIDE – PUSH UPOTHER SIDE – PUSH DOWNDRAWER REPLACEMENTExtend the drawer slides from the unit. Insert the brackets on each side of the drawerinto the slots in the slides, being careful that they are properly positioned. Once properly inserted, completely close the drawer to set the slides in position.9MAINTENANCEPeriodically clean the drawer fronts, trim, and other surfaces with mild detergent and water.Lubricate the casters with high quality bearing grease (annually/yearly).Lubricate the slides (twice a year) with a product like WD40 or other quality lubricant. This is especially important in low temperatures, which can cause the bearing to become stiff.Grease and oil can be removed with most standard cleaning fluids. For safety, use anonflammable cleaning fluid.SAFETYRISK OF ELECTRIC SHOCK. To reduce the risk of electric shock, use indoors in adry location only. Do not plug the power strip into another power strip. Not for use for a permanent installation.Changes or modifications to this unit not expressly approved by the party responsible for compliance could void the user's authority to operate the equipment.Close the cover and lock the drawers before moving this product. The drawers could come open and make the product unstable and tip, which may cause personal injury or product damage.Do not attempt to lift the unit by its side handles using chains, ropes or other liftingdevices. The side handle could fail, which may cause personal injury or damage to the product.DO NOT stand on this product or lean on the drawers or work surface.WEAR SAFETY GLASSES when removing or repositioning the slides. The tool could slip, which may cause personal injury.When moving this product, do not pull it. Push the product to prevent personal injury.USE THE BRAKES when not moving this product. This will prevent the product from rolling, which may cause personal injury or product damage.BE CAREFUL when opening more than one drawer. The product could become unstable and tip, which may cause personal injury or product damage.DO NOT mount this product on a truck bed or any other moving object. This may cause personal injury or product damage, and will void the warranty.Secure this product properly before moving it with a forklift.DO NOT tow with power equipment. The product could tip, which may cause personal injury or product damage.Keep the product on level surfaces. The product could become unstable and tip if stored or moved on an uneven surface, which may cause personal injury or product damage. 10This product is warranted to be free from defects in materialsand workmanship for a period of five (5) years from the dateof original purchase.Ifthisproductisdefective,*********************************or call 1-800-459-4409 (Monday–Friday, 8:00 am–4:30 pm, CST). If the product is defective, we will replace the defective part at no cost to you.Please do not ship your product back to the store or to usunless we send you written instructions for return.In the event it becomes necessary for your productto be returned, we will notify you how to proceed.A copy of your original purchase receipt must accompanythe returned product.WARNINGCancer and Reproductive Harm – 11Manufactured by:QUALITY CRAFTRomeoville, IL, USA 60446****************************1-800-459-4409(Monday to Friday, 8:00 am–4:30 pm, CST)Made in ChinaM362404CH/M362406TC_05/20。

MEMORY存储芯片MT46H32M32LFJG-6AT中文规格书

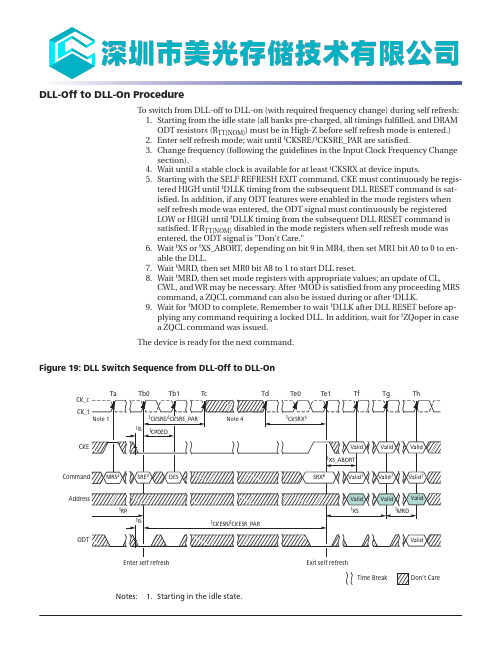

DLL-Off to DLL-On ProcedureTo switch from DLL-off to DLL-on (with required frequency change) during self refresh:1.Starting from the idle state (all banks pre-charged, all timings fulfilled, and DRAMODT resistors (R TT(NOM)) must be in High-Z before self refresh mode is entered.)2.Enter self refresh mode; wait until t CKSRE/t CKSRE_PAR are satisfied.3.Change frequency (following the guidelines in the Input Clock Frequency Changesection).4.Wait until a stable clock is available for at least t CKSRX at device inputs.5.Starting with the SELF REFRESH EXIT command, CKE must continuously be regis-tered HIGH until t DLLK timing from the subsequent DLL RESET command is sat-isfied. In addition, if any ODT features were enabled in the mode registers when self refresh mode was entered, the ODT signal must continuously be registered LOW or HIGH until t DLLK timing from the subsequent DLL RESET command is satisfied. If R TT(NOM) disabled in the mode registers when self refresh mode was entered, the ODT signal is "Don't Care."6.Wait t XS or t XS_ABORT, depending on bit 9 in MR4, then set MR1 bit A0 to 0 to en-able the DLL.7.Wait t MRD, then set MR0 bit A8 to 1 to start DLL reset.8.Wait t MRD, then set mode registers with appropriate values; an update of CL,CWL, and WR may be necessary. After t MOD is satisfied from any proceeding MRS command, a ZQCL command can also be issued during or after t DLLK.9.Wait for t MOD to complete. Remember to wait t DLLK after DLL RESET before ap-plying any command requiring a locked DLL. In addition, wait for t ZQoper in case a ZQCL command was issued.The device is ready for the next command.Figure 19: DLL Switch Sequence from DLL-Off to DLL-OnCK_cCK_tTa Tb0Tb1Tc Td Te0Te1Tf TgTh Don’t CareTime Break CKEEnter self refresh Exit self refreshODTAddressNotes: 1.Starting in the idle state.2.Enter SR.3.Change frequency.4.Clock must be stable t CKSRX.5.Exit SR.6.Set DLL to on by setting MR1 to A0 = 0.7.Update mode registers.8.Issue any valid command.Input Clock Frequency ChangeAfter the device is initialized, it requires the clock to be stable during almost all states of normal operation. This means that after the clock frequency has been set and is in the stable state, the clock period is not allowed to deviate except for what is allowed by the clock jitter and spread spectrum clocking (SSC) specifications. The input clock frequen-cy can be changed from one stable clock rate to another stable clock rate only when in self refresh mode. Outside of self refresh mode, it is illegal to change the clock frequen-cy.After the device has been successfully placed in self refresh mode and t CKSRE/t CKSRE_PAR have been satisfied, the state of the clock becomes a "Don’t Care." Follow-ing a "Don’t Care," changing the clock frequency is permissible, provided the new clock frequency is stable prior to t CKSRX. When entering and exiting self refresh mode for the sole purpose of changing the clock frequency, the self refresh entry and exit specifica-tions must still be met as outlined in SELF REFRESH Operation.For the new clock frequency, additional MRS commands to MR0, MR2, MR3, MR4, MR5,and MR6 may need to be issued to program appropriate CL, CWL, gear-down mode,READ and WRITE preamble, Command Address Latency, and data rate values.When the clock rate is being increased (faster), the MR settings that require additional clocks should be updated prior to the clock rate being increased. In particular, the PL latency must be disabled when the clock rate changes, ie. while in self refresh mode. For example, if changing the clock rate from DDR4-2133 to DDR4-2933 with CA parity mode enabled, MR5[2:0] must first change from PL = 4 to PL = disable prior to PL = 6.The correct procedure would be to (1) change PL = 4 to disable via MR5 [2:0], (2) enter self refresh mode, (3) change clock rate from DDR4-2133 to DDR4-2933, (4) exit self re-fresh mode, (5) Enable CA parity mode setting PL = 6 vis MR5 [2:0].If the MR settings that require additional clocks are updated after the clock rate has been increased, for example. after exiting self refresh mode, the required MR settings must be updated prior to removing the DRAM from the IDLE state, unless the DRAM is RESET. If the DRAM leaves the IDLE state to enter self refresh mode or ZQ Calibration,the updating of the required MR settings may be deferred to the next time the DRAM enters the IDLE state.If MR6 is issued prior to self refresh entry for the new data rate value, DLL will relock automatically at self refresh exit. However, if MR6 is issued after self refresh entry, MR0must be issued to reset the DLL.The device input clock frequency can change only within the minimum and maximum operating frequency specified for the particular speed grade. Any frequency change be-low the minimum operating frequency would require the use of DLL-on mode to DLL-off mode transition sequence (see DLL-On/Off Switching Procedures).4Gb: x8, x16 Automotive DDR4 SDRAM Input Clock Frequency ChangeWrite LevelingFor better signal integrity, DDR4 memory modules use fly-by topology for the com-mands, addresses, control signals, and clocks. Fly-by topology has benefits from the re-duced number of stubs and their length, but it also causes flight-time skew between clock and strobe at every DRAM on the DIMM. This makes it difficult for the controller to maintain t DQSS, t DSS, and t DSH specifications. Therefore, the device supports a write leveling feature to allow the controller to compensate for skew. This feature may not be required under some system conditions, provided the host can maintain the t DQSS, t DSS, and t DSH specifications.The memory controller can use the write leveling feature and feedback from the device to adjust the DQS (DQS_t, DQS_c) to CK (CK_t, CK_c) relationship. The memory con-troller involved in the leveling must have an adjustable delay setting on DQS to align the rising edge of DQS with that of the clock at the DRAM pin. The DRAM asynchronously feeds back CK, sampled with the rising edge of DQS, through the DQ bus. The controller repeatedly delays DQS until a transition from 0 to 1 is detected. The DQS delay estab-lished though this exercise would ensure the t DQSS specification. Besides t DQSS, t DSS and t DSH specifications also need to be fulfilled. One way to achieve this is to combine the actual t DQSS in the application with an appropriate duty cycle and jitter on the DQS signals. Depending on the actual t DQSS in the application, the actual values for t DQSL and t DQSH may have to be better than the absolute limits provided in the AC Timing Parameters section in order to satisfy t DSS and t DSH specifications. A conceptual tim-ing of this scheme is shown below.Figure 20: Write Leveling Concept, Example 1diff_DQSdiff_DQSDQ diff_DQSDQ T0T1T2T3T4T5CK_cCK_tT6T7CK_c CK_tSource Destination DQS driven by the controller during leveling mode must be terminated by the DRAM based on the ranks populated. Similarly, the DQ bus driven by the DRAM must also be terminated at the controller.All data bits carry the leveling feedback to the controller across the DRAM configura-tions: x4, x8, and x16. On a x16 device, both byte lanes should be leveled independently.Therefore, a separate feedback mechanism should be available for each byte lane. The upper data bits should provide the feedback of the upper diff_DQS(diff_UDQS)-to-clock relationship; the lower data bits would indicate the lower diff_DQS(diff_LDQS)-to-clock relationship.4Gb: x8, x16 Automotive DDR4 SDRAM Write Leveling。

埃森·莫勒尔系列NZM型号的电缆保护器说明书

Eaton 259531Eaton Moeller series NZM - Molded Case Circuit Breaker.Undervoltage release, 24VAC, +2early N/O, 1General specificationsEaton Moeller series NZM release259531NZM1-XUHIV24AC401508259531937 mm66 mm32 mm0.084 kgUL/CSAIECRoHS conform UL (File No. E140305)CSA-C22.2 No. 5-09CE markingIEC60947CSA (Class No. 1437-01)UL (Category Control Number DIHS) UL listedCSA certifiedUL489CSA (File No. 22086)Product Name Catalog Number Model Code EANProduct Length/Depth Product Height Product Width Product Weight Compliances CertificationsIs the panel builder's responsibility. The specifications for the switchgear must be observed.24 VMeets the product standard's requirements.10 msIs the panel builder's responsibility. The specifications for the switchgear must be observed.Does not apply, since the entire switchgear needs to be evaluated.1.5 VAMeets the product standard's requirements.0 VTwo early-make auxiliary contacts0.8 W24 VIs the panel builder's responsibility.15 ms eaton-digital-nzm-brochure-br013003en-en-us.pdfeaton-feerum-the-whole-grain-solution-success-story-en-us.pdf eaton-digital-nzm-catalog-ca013003en-en-us.pdfDA-DC-03_NZM1eaton-circuit-breaker-release-nzm-mccb-dimensions.epseaton-circuit-breaker-undervoltage-nzm-mccb-3d-drawing-004.eps M1-XUHIV24ACIL01203002ZIntroduction of the new digital circuit breaker NZMThe new digital NZM RangeDA-CS-nzm1_xuDA-CD-nzm1_xueaton-nzm-technical-information-sheet10.11 Short-circuit ratingRated control supply voltage (Us) at AC, 50 Hz - min 10.4 Clearances and creepage distancesMinimum command time - min10.12 Electromagnetic compatibility10.2.5 LiftingPick-up power consumption at AC (undervoltage release) 10.2.3.1 Verification of thermal stability of enclosures Rated control supply voltage (Us) at DC - minFitted with:Pick-up power consumption at DC (undervoltage release) Rated control supply voltage (Us) at AC, 50 Hz - max 10.8 Connections for external conductorsMinimum command time - maxSpecial features BrochuresCatalogs Certification reports DrawingseCAD model Installation instructions Installation videos mCAD model Technical data sheetsUndervoltage release with 2 early-make auxiliary contacts, e.g., for early-make connection ofundervoltage release inmain switch applications, aswell as for interlock and loadshedding circuits.For use with emergency-stop devices in connectionwith an emergency-stopbutton.When the under-voltage tripis switched off, accidentalcontact with the circuitbreaker’s primary contacts isprevented when switchedon.Early make of auxiliarycontacts on switching onand off (manual operation):approx. 20 msUndervoltage releasescannot be installedsimultaneously with NZM...-XHIV... early-make auxiliarycontact or NZM...-XA...shunt release.Rated control supply voltage (Us) at DC - max0 V10.9.3 Impulse withstand voltageIs the panel builder's responsibility.Rated control supply voltage24 V 50/60 Hz10.6 Incorporation of switching devices and componentsDoes not apply, since the entire switchgear needs to be evaluated.10.5 Protection against electric shockDoes not apply, since the entire switchgear needs to be evaluated.Used withNZM1(-4), N(S)1(-4)Electric connection typeScrew connection10.13 Mechanical functionThe device meets the requirements, provided the information in the instruction leaflet (IL) is observed.10.2.6 Mechanical impactDoes not apply, since the entire switchgear needs to be evaluated.10.9.4 Testing of enclosures made of insulating materialIs the panel builder's responsibility.Number of contacts (normally closed contacts)10.3 Degree of protection of assembliesDoes not apply, since the entire switchgear needs to be evaluated.Voltage typeACDrop-out voltage of undervoltage release AC/DC - min0.35 x UsFrameNZM1Reaction time19 msSuitable forOff-load switchVoltage tolerance - min.85Rated control voltage (relay contacts)24 V ACPower consumption1.5 VA (sealing AC)0.8 W (sealing DC)10.2.3.2 Verification of resistance of insulating materials to normal heatMeets the product standard's requirements.Drop-out voltage of undervoltage release AC/DC - max0.7 x Us10.2.3.3 Resist. of insul. mat. to abnormal heat/fire by internal elect. effectsMeets the product standard's requirements.Connection typeWith terminal block on the left-hand switch side10.9.2 Power-frequency electric strengthIs the panel builder's responsibility.Voltage tolerance - max1.1Undelayed short-circuit release - min0 ARated control supply voltage (Us) at AC, 60 Hz - min24 V10.7 Internal electrical circuits and connectionsIs the panel builder's responsibility.Terminal capacity (solid/flexible conductor)0.75 mm² - 2.5 mm² (2x) at shunt release with ferrule18 - 14 AWG (1x) at shunt release18 - 14 AWG (1x) for undervoltage releases, off-delayed0.75 mm² - 2.5 mm² (1x) at shunt release with ferrule0.75 mm² - 2.5 mm² (1x) for undervoltage releases, off-delayed with ferrule0.75 mm² - 2.5 mm² (2x) for undervoltage releases, off-delayed with ferrule18 - 14 AWG (2x) at shunt release18 - 14 AWG (2x) for undervoltage releases, off-delayed10.10 Temperature riseThe panel builder is responsible for the temperature rise calculation. Eaton will provide heat dissipation data for the devices.TypeAccessoryUndervoltage release withearly-make auxiliary contact10.2.2 Corrosion resistanceMeets the product standard's requirements.10.2.4 Resistance to ultra-violet (UV) radiationMeets the product standard's requirements.10.2.7 InscriptionsMeets the product standard's requirements.Rated control supply voltage (Us) at AC, 60 Hz - max24 VNumber of contacts (normally open contacts)2Undelayed short-circuit release - max0 AEaton Corporation plc Eaton House30 Pembroke Road Dublin 4, Ireland © 2023 Eaton. All Rights Reserved. Eaton is a registered trademark.All other trademarks areproperty of their respectiveowners./socialmediaNumber of contacts (change-over contacts)。

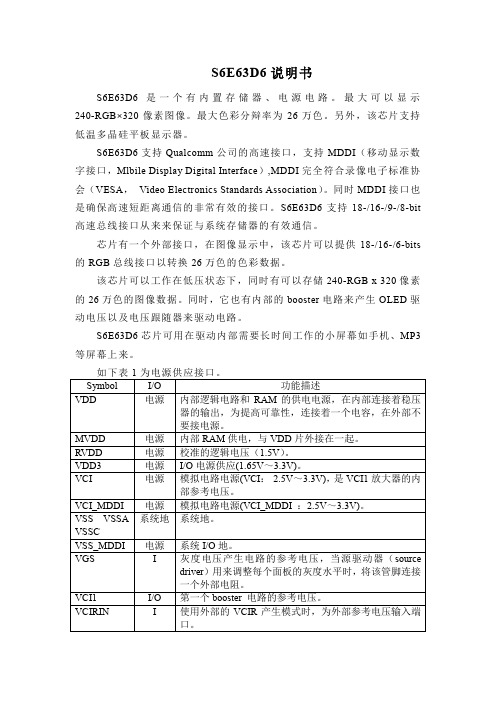

三星AMOLED驱动芯片中文版说明书

表 5 所示为其他端口。 Symbol I/O 功能描述 DUMMYR[3:1] 电阻测量管脚,正常情况下悬空。 DUMMYL[3:1] DUMMY 无用管脚,悬空即可。 V0/V63 O 伽玛电压镜像管脚。 VDD3DUM O 内部与 VDD3 接在一起。

VSSDUM FUSE_EN RTEST EN_EXCLK EN_CLK TEST_MODE[1:0] TEST_IN[6:0] TE TEST_OUT[2:0]

表 2 系统接口

表3为 Symbol MDP MDN MSP MSN GPIO[9:0] (DB[17:8]) S_CSB(DB [7])

MDDI 管脚作用。 I/O 功能描述 I/O MDDI 数据输入/输出正端,如果 MDDI 不用,该端口悬空。 I/O MDDI 数据输入/输出负端,如果 MDDI 不用,该端口悬空。 I MDDI 数据选通输入正端,如果 MDDI 不用,该端口悬空。 I MDDI 数据选通输入负端,如果 MDDI 不用,该端口悬空。 I/O 总体输入输出,如果在 MDDI 中没有用 GPIO 的话,这些管 脚应该置地。 O 子屏幕驱动 IC 片选信号。 低电平时说明子屏幕驱动 IC 可用,高电平时说明子屏幕驱动

表 1 电源接口

如表 2 所示为系统接口。 Symbol I/O 功能描述 S_PB I 选择 CPU 接口模式,低电平时为并行接口,高电平时为串行 接口。 MDDI_E I 选择 MDDI 接口,低电平时 MDDI 接口不可用,高电平时 N MDDI 接口可用。 ID_MIB I 选择 CPU 种类, 低电平为 intel 80 系列 CPU, 高电平为 motorola 68 系列 CPU,如果 S_PB 是高电平,该端口为 ID 设置端口。 CSB I 片选信号,低电平芯片可用,高电平芯片不可用。 RS I 寄存器选择管脚。 低电平时,指令/状态,高电平时为指令参数/RAM 数据。 不用时需与 VDD3 接在一起。 RW_WR I 管脚作用 CPU 种类 管脚说明 B/SCL RW 68 系列 读写选择,低电平写,高电平读。 WRB 80 系列 写选通作用,在上升沿捕获数据。 SCL 串行接口 时钟同步信号。 E_RDB I 管脚作用 CPU 种类 管脚说明 E 68 系列 读写操作使能端。 RDB 80 系列 读选通作用,低电平时读出数据。 选择串行模式时,将此端口接在 VDD3 上。 SDI I 串行接口的数据输入接口,在 SCL 上升沿捕捉到输入数据,

LEMO连接器样本

PHW PUW

浮动式插座,带线夹,配短护套

尺寸 (mm) 线缆外径

˜L

产品编号

线缆组

外壳材料 L S1 Max Min

ø 23

PHW.3K.93C.CLCT96Z

2-4

105 15 9.5 8.9 黄铜镀铬

PHW.3K.93C.CLCT12Z

3

139 20 12.5 11.6

S1

注:短护套需另外订购。(见第8页)

外壳材料

FXW.3K.93C.CLM FXW.3K.93C.TLM准F2母光纤插芯PSS.F2.BA2.LCT10需另外订购。

2

FMW EDW

固定式插头,带圆法兰(4个螺丝固定),带线夹,配短护套

ø 22.5 ø 38

˜101 ˜71

10

S 15

产品编号

线缆组

线缆外径 Max Min

外壳材料

ø 3.4

EDW.3K.93C.CLC

黄铜镀铬

EDW.3K.93C.TLC

不锈钢

ø 18 ø 23

注:两个标准F2公光纤插芯FFS.F2.BA2.LCT10需另外订购。

外壳材料

黄铜镀铬 不锈钢

EBW 固定式插座,前端带方法兰(4个螺丝固定)

29 23

ø 3.4

ø 23 ø 23

42.5

3

3

产品编号

多芯系列

18

同轴以及混装系列

20

3K.93C 系列高清电视连接系统 HDTV 高清电视光纤连接器全球标准

瑞士雷莫(LEMO)在高清电视(HDTV)引入早期就开发 了 3K.93C 系列连接器,并使之成为了高清电视的连接 标准。目前在全球应用的连接器中,是唯一能完全匹配 SMPTE、ARIB 和 EBU 标准的连接器。具有超过 2 万次 插拔使用寿命,且性能优越,插入损耗仅 0.1dB 。LEMO 3K.93C 系列连接器被各个国内外知名的转播公司作为 高清摄像系统的标准接口。

Intermec Models AV6 和 AV9 的电子产品说明书

Models AV6 and AV9 Compliance InsertFor Users in the United States and CanadaThe users of this product are cautioned to use accessories and peripherals approved by Intermec Technologies Corporation. The use of accessories other than those recommended, or changes to this product that are not approved by Intermec Technologies Corporation, may void the compliance of this product and may result in the loss of the user’s authority to operate the equipment.Les utilisateurs de ce produit sont avisés d’utiliser des accessoires et des périphériques approuvés par Intermec TechnologiesCorporation. L’utilisation d’accessoires autres que ceux recommandés ou des changements à ce produit qui ne sont pas approuvés par Intermec Technologies Corporation peuvent annuler la conformité de ce produit et mettre fin au droit qu’a l’usager d’utiliser l'équipement.FCC Digital Emissions ComplianceIntermec Models AV6 and AV9 have been tested and found to comply with the limits for a Class B digital device, pursuant to Part 15 of the FCC Rules. These limits are designed to provide reasonable protection against harmful interference in a residential installation. This equipment generates, uses, and can radiate radio frequency energy and, if not installed and used in accordance with the instructions, may cause harmful interference to radio communications. However, there is no guarantee that interference will not occur in a particular installation. If this equipment does cause harmful interference to radio or television reception, which can be determined by turning the equipment off and on, the user is encouraged to try to correct the interference by one or more of the following measures:•Reorient or relocate the radio or television receiving antenna.•Increase the separation between the computer equipment and receiver.•Connect the equipment into an outlet on a circuit different from that to which the radio or television receiver is connected.•Consult the dealer or an experienced radio television technician for help.Canadian Digital Apparatus ComplianceThese Class B digital products meet all requirements of the Canadian Interference-Causing Equipment Regulations.Conformité aux normes canadiennes sur les appareils numériquesCet appareil numérique de la classe B respecte toutes les exigences du Réglement sur le matériel brouilleur du Canada.For Users Outside of the United States or CanadaThe users of this product are cautioned to use accessories and peripherals approved by Intermec Technologies Corporation. The use of accessories other than those recommended, or changes to this product that are not approved by Intermec Technologies Corporation, may void the compliance of this product and may result in the loss of the user’s authority to operate the equipment.Caution: This marking indicates that the user should read all included documentation before use.Attention: Ce marquage indique que l’usager doit, avant l’utilisation, lire toute la documentation incluse.Caution: For use with Intermec Model CN3 series and Model CN4 series only. For vehicle power adapter use P/N 852-057-005. Use only Intermec approved vehicle installation methods.Attention: Pour utilisation avec le modèle CN3 et le modèle CN4 Intermec exclusivement. Pour l'adaptateur d'alimentation, utilisez la référence 852-057-005. N'utiliser que des méthodes d'installation dans un véhicule approuvées par Intermec.Caution: This marking indicates that the user should read all included documentation before use.Caution: For use with Intermec Model CN3 series and CN4 series only. For vehicle power adapter use P/N852-057-005. Use only Intermec approved vehicle installation methods.S&E对于美国或加拿大以外的用户敬告本产品的用户,请务必使用 Intermec Technologies Corporation 许可的附件和外围设备。

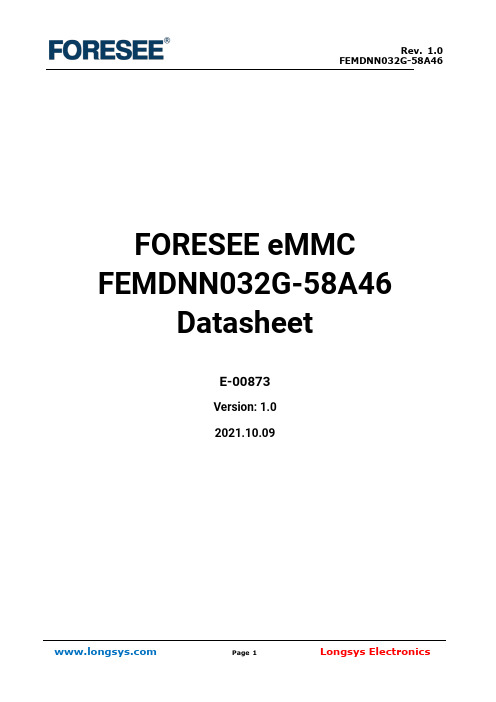

长斯系电子 FORESEE eMMC FEMDNN032G-58A46 数据手册说明书

FORESEE eMMC FEMDNN032G-58A46DatasheetE-00873Version: 1.02021.10.09LONGSYS ELECTRONICS RESERVES THE RIGHT TO CHANGE PRODUCTS, INFORMATION AND SPECIFICATIONS WITHOUT NOTICE.Products and specifications discussed herein are for reference purposes only. All information discussed herein is provided on an “AS IS” basis, without warranties of any kind.This document and all information discussed herein remain the sole and exclusive property of Longsys Electronics. No license of any patent, copyright, mask work, trademark or any other intellectual property right is granted by one party to the other party under this document, by implication, estoppel or other-wise.Longsys products are not intended for use in life support, critical care, medical, safety equipment, or similar applications where product failure could result in loss of life or personal or physical harm, or any military or defense application, or any governmental procurement to which special terms or provisions may apply.For updates or additional information about Longsys products, contact your nearest Longsys office.All brand names, trademarks and registered trademarks belong to their respective owners.ⓒ 2021 Shenzhen Longsys Electronics Co., Ltd. All rights reserved.CONTENTS1.Introduction (4)2. Product List (4)3. Features (4)4. Functional Description (5)5. Product Specifications (6)5.1 Performance (6)5.2 Power Consumption (6)6. Pin Assignments (7)6.1 Ball Array view (7)6.2 Ball Array view (8)7. Usage Overview (9)7.1 General description (9)7.2 Partition Management (9)7.3 Automatic Sleep Mode (11)7.4 Sleep (CMD5) (11)7.5 H/W Reset operation (12)7.6 High-speed mode selection (12)7.7 Bus width selection (12)7.8 Partition configuration (12)7.9 CID register (12)7.10 CSD register (13)7.11 Extended CSD register (14)7.12 OCR Register (23)7.13 Field firmware update(FFU) (23)7.14 S.M.A.R.T. Health Report (25)8. Package Dimension (26)9 Connection Guide (26)9.1 Schematic Diagram (26)10. Processing Guide (27)1.IntroductionISOCOM eMMC is an embedded storage solution designed in the BGA package. The ISOCOM eMMC consists of NAND flash and eMMC controller. The controller could manage the interface protocols,wear-leveling,bad block management and ECC.ISOCOM eMMC has high performance at a competitive cost, high quality and low power consumption, and eMMC is compatible with JEDEC standard eMMC 5.1 specifications.3. Features➢eMMC5.1 specification compatibility (Backward compatible to eMMC4.41/4.5/5.0)➢Bus mode- Data bus width: 1 bit (default), 4 bits, 8 bits- Data transfer rate: up to 400MB/s (HS400)- MMC I/F Clock frequency : 0~200MHz➢Operating voltage range- Vcc(NAND) : 2.7 - 3.6V- Vccq(Controller) : 1.7 - 1.95V / 2.7 - 3.6V➢Temperature- Operation (-25℃~ +85℃)- Storage without operation (-40℃~ +85℃)➢Sudden-Power-Loss safeguard➢Hardware ECC engine➢Unique firmware backup mechanism ➢Global-wear-leveling➢Supported features.-HS400, HS200-Partitioning, RPMB-Boot feature, boot partition-HW Reset/SW Reset-Discard, Trim, Erase, Sanitize-Background operations, HPI-Enhanced reliable write-S.M.A.R.T. Health Report-FFU-Sleep / awake➢Others- Compliance with the RoHS Directive4. Functional DescriptionISOCOM eMMC with powerful L2P (Logical to Physical) NAND Flash management algorithm provides unique functions:➢Host independence from details of operating NAND flash➢Internal ECC to correct defect in NAND flash➢Sudden-Power-Loss safeguardTo prevent from data loss, a mechanism named Sudden-Power-Loss safeguard is added in the eMMC. In the case of sudden power-failure, the eMMC would work properly after power cycling.➢Global-wear-levelingTo achieve the best stability and device endurance, this eMMC equips the Global Wear Leveling algorithm. It ensures that not only normal area, but also the frequently accessed area, such as FAT, would be programmed and erased evenly.➢IDA(Initial Data Acceleration)The eMMC prevents the pre-burned data from data-loss with IDA, in case of our customer had pre-burned data to eMMC, before the eMMC being SMT.➢CacheThe eMMC enhanced the data written performance with Cache, with which our customer would get more endurance and reliability.5. Product Specifications• Test Condition: Bus width x8, 200MHz DDR, 512KB data transfer, w/o file system overhead, measured on internal board • Test tool: uBOOT (Without O/S)• Chunk size: 1MB,• Test area: 100MB/ Full-range of LBA.5.2 Power Consumption5.2.1 Active power consumption during operation• Power Measurement conditions: Bus configuration =x8 @200MHz DDR, 25℃.• Vcc:3.3V & Vccq:1.8V.• The measurement for max RMS current is the average RMS current consumption over a period of 100ms.5.2.2 Low power mode (stand-by)• Power Measurement conditions: Bus configuration =x8 @200MHz DDR, 25℃.• Standby: Nand Vcc & Controller Vccq power supply is switched on.• The measurement for max RMS current is the average RMS current consumption over a period of 100ms.5.2.3 Low power mode (sleep)• Power Measurement conditions: Bus configuration =x8 @200MHz DDR, 25℃.• Sleep: Nand Vcc power supply is switched off(Controller Vccq on)• The measurement for max RMS current is the average RMS current consumption over a period of 100ms.6. Pin Assignments6.1 Ball Array viewFBGA153 - Ball Array (Top view(ball site down))Note:NC: No Connect, shall be connected to ground or left floating. RFU: Reserved for Future Use, must be left floating for future use. VSF: Vendor Specific Function, must be left floating.7.1 General descriptionThe eMMC can be operated in 1, 4, or 8-bit mode. NAND flash memory is managed by a controller inside, which manages ECC, wear leveling and bad block management. The eMMC provides easy integration with the host process that all flash management hassles are invisible to the host.7.2 Partition ManagementThe embedded device offers also the possibility of configuring by the host additional split local memory partitions with independent addressable space starting from logical address 0x00000000 for different usage models. Default size of each Boot Area Partition is 4096 KB and can be changed by Vendor Command as multiple of 128KB. Boot area partition size is calculated as ( 128KB * BOOT_SIZE_MUL TI ) The size of Boot Area Partition 1 and 2 cannot be set independently and is set as same value Boot area partition which is enhanced partition. Therefore memory block area scan is classified as follows:➢Factory configuration supplies boot partitions.➢The RPMB partition is 4MB.➢The host is free to configure one segment in the User Data Area to be implemented as enhanced storage media, and to specify its starting location and size in terms of Write Protect Groups. The attributes of this Enhanced User Data Area can be programmed only once during the device life-cycle (one-time programmable).➢Up to four General Purpose Area Partitions can be configured to store user data or sensitive data, or for other host usage models. The size of these partitions is a multiple of the write protect group. Size and attributes can be programmed once in device life-cycle (one-time programmable). Each of the General Purpose Area Partitions can be implemented with enhanced technological features.Partitions and user data area configuration(The size of RPMB area partition is 4MB)In boot operation mode, the master can read boot data from the slave (device) by keeping CMD line low or sending CMD0 with argument + 0xFFFFFFFA, before issuing CMD1. The data can be read from either boot area or user area dependingState diagram (boot mode)State diagram (alternative boot mode)State diagram (boot mode)*7.3 Automatic Sleep ModeIf host does not issue any command during certain duration (1s), after previously issued command is completed, the device enters “Power Saving mode” to reduce power consumption. At this time, commands arriving at the device while it is in power saving mode will be serviced in normal fashion. The below table explains the condition to enter and exit Auto Power Saving Mode7.4 Sleep (CMD5)A card may be switched between a Sleep state and a Standby state by SLEEP/AWAKE (CMD5). In the Sleep state the power consumption of the memory device is minimized. In this state the memory device reacts only to the commands RESET (CMD0 with argument of either 0x00000000 or 0xF0F0F0F0 or H/W reset) and SLEEP/AWAKE (CMD5). All the other commands are ignored by the memory device. The timeout for state transitions between Standby state and Sleep state is defined in the EXT_CSD register S_A_timeout. The maximum current consumptions during the Sleep state are defined in the EXT_CSD registers S_A_VCC and S_A_VCCQ. Sleep command: The bit 15 as set to 1 in SLEEP/ AWAKE (CMD5) argument. A wake command: The bit 15 as set to 0 in SLEEP/AWAKE (CMD5) argument.7.5 H/W Reset operationDevice will detect the rising edge of RST_n signal to trigger internal reset sequenceH/W reset waveform7.6 High-speed mode selectionAfter the host verifies that the card complies with version 4.0, or higher, of this standard, it has to enable the high speed mode timing in the card, before changing the clock frequency to a frequency higher than 20MHz. For the host to change to a higher clock frequency, it has to enable the high speed interface timing. The host uses the SWITCH command to write 0x01 to the HS_TIMING byte, in the Modes segment of the EXT_CSD register.7.7 Bus width selectionAfter the host has verified the functional pins on the bus it should change the bus width configuration accordingly, using the SWITCH command. The bus width configuration is changed by writing to the BUS_WIDTH byte in the Modes Segment of the EXT_CSD register (using the SWITCH command to do so). After power-on, or software reset, the contents of the BUS_WIDTH byte is 0x00.7.9 CID registerThe Card Identification (CID) register is 128 bits wide. It contains the card identification information used during the card identification phase (protocol). Every individual flash or I/O card shall have an unique identification number. Every type of ROM cards (defined by content) shall have a unique identification number. The structure of the CID register is defined7.10 CSD registerThe Card-Specific Data (CSD) register provides information on how to access the card contents. The CSD defines the data format, error correction type, maximum data access time, data transfer speed, whether the DSR register can be used etc. The programmable part of the register (entries marked by W or E, see below) can be changed by CMD27. The type of the CSD Registry entries coded as follows:7.11 Extended CSD registerThe Extended CSD register defines the card properties and selected modes. It is 512 bytes long. The most significant 320 bytes are the Properties segment, which defines the card capabilities and cannot be modified by the host. The lower 192 bytes are the Modes segment, which defines the configuration the card is working in. These modes can be changed by the host by means of the SWITCH command.Notes: 1.R= Read-onlyR/W=One-Time Programmable and readableR/W/E=Multiple writable with value kept after a power cycle, assertion of the RST_n signal, and any CMD0 reset,and readableTBD=To Be Defined.2.Reserved bits should be read as 0.7.12 OCR RegisterThe 32-bit operation conditions register stores the VCCQ voltage profile of the eMMC. In addition, this register includes a status information bit. This status bit is set if the eMMC power up procedure has been finished. The OCR register shallNote*: This bit is set to LOW if the eMMC has not finished the power up routine. The supported voltage range is coded as shown in table.7.13 Field firmware update(FFU)To download a new firmware, the controller requires instruction sequence following JEDEC standard.Longsys eMMC only supports Manual mode (MODE_OPERATION_CODES is not supported). For more details, refer to the App note.SUPPORTED_MODE[493] (Read Only)BIT[0] : ‘0’ FFU is not supported by the device.‘1’ FFU is supported by the device.BIT[1] : ‘0’ Vendor specific mode (VSM) is not supported by the device.‘1’ Vendor specific mode is supported by the device.FFU_FEATURE[492] (Read Only)BIT[0] : ‘0’ Device does not support MODE_OPERATION_CODES field (Manual mode)‘1’ Device supports MODE_OPERATION_CODES field (Auto mode)FFU_ARG[490-487] (Read Only)Using this field the device reports to the host which value the host should set as an argument for read and write commands in FFU mode.FW_CONFIG[169] (R/W)BIT[0] : Update disable0x0 : FW updates enabled.0x1 : FW update disabled permanentlyFFU_STATUS[26] (R/W/E_P)OPERATION_CODES_TIMEOUT[491](Read Only)Maximum timeout for the SWITCH command when setting a value to the MODE_OPERATION_CODES field.The register is set to ‘0’, because the controller doesn’t support MODE_OPERATION_CODES.MODE_OPERATION_CODES[29] (W/E_P)The host sets the operation to be performed at the selected mode, in case MODE_CONFIGS is set toFFU_MODE,MODE_OPERATION_CODES could have the following values :7.14 S.M.A.R.T. Health ReportS.M.A.R.T. is a monitoring system that detects and reports on various indicators of eMMC reliability(Including original bad blocks, increased bad blocks, power-up number, power-loss counts and etc), with the intent of enabling the anticipation of hardware failures. We may be able to use recorded S.M.A.R.T. data to discover where the faults lie, ensure how to solve the problems and prevent them from recurring in future eMMC designs (For details, please refer to app note).8. Package Dimension11.5mm x 13.0mm x 1.0mm Package Dimension9 Connection Guide9.1 Schematic Diagram➢Coupling capacitor should be connected with VCC/VCCQ and VSS as closely as possible.➢The resistance on the CLK line is highly recommended (0Ω by default). 0Ω~100Ω is also avail able. ➢LONGSYS recommends to separate VCC and VCCQ power.➢VDDi Capacitor is min 0.1uF.➢LONGSYS recommends lay the VSS between the CLK and the Data lines.The resistance on the CLK line is highly recommended (0Ω by default)10. Processing GuideIt is recommended to follow the instructions of Moisture Sensitivity Level 3.In the case of Pre-program before SMT, It is highly recommended to limit the size of data pre-programmed to the eMMC,please contact your agency for more information.➢The amount of data pre-programmed (data written before SMT) is limited, it should be managed properly.➢Maximum size for the data-written to IDA.。

3680系列精密潜入杆电阻器产品说明书

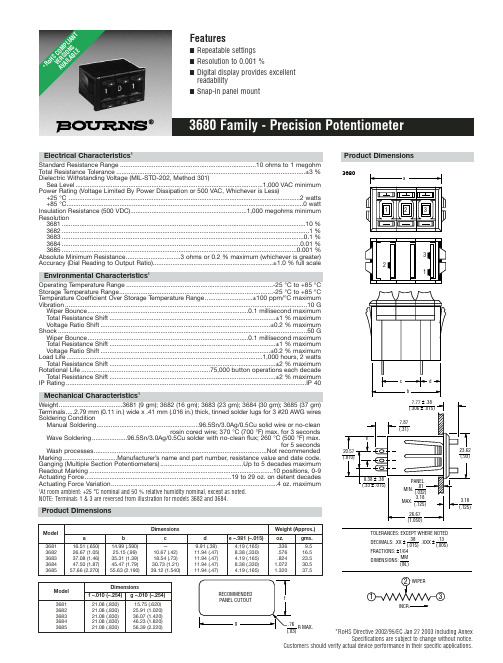

*RoHS Directive 2002/95/EC Jan 27 2003 including AnnexSpecifications are subject to change without notice.Customers should verify actual device performance in their specific applications.Electrical Characteristics 1Standard Resistance Range .............................................................................10 ohms to 1 megohm Total Resistance Tolerance...........................................................................................................±3 %Dielectric Withstanding Voltage (MIL-STD-202, Method 301)Sea Level..........................................................................................................1,000 VAC minimum Power Rating (Voltage Limited By Power Dissipation or 500 VAC, Whichever is Less)+25 °C ...................................................................................................................................2 watts +85 °C......................................................................................................................................0 watt Insulation Resistance (500 VDC)..................................................................1,000 megohms minimum Resolution3681..........................................................................................................................................10 %3682............................................................................................................................................1 %3683.........................................................................................................................................0.1 %3684.......................................................................................................................................0.01 %3685.....................................................................................................................................0.001 %Absolute Minimum Resistance...............................3 ohms or 0.2 % maximum (whichever is greater)Accuracy (Dial Reading to Output Ratio)....................................................................±1.0 % full scaleEnvironmental Characteristics1Operating Temperature Range ...................................................................................-25 °C to +85 °C Storage Temperature Range.......................................................................................-25 °C to +85 °C Temperature Coefficient Over Storage Temperature Range...........................±100 ppm/°C maximum Vibration.........................................................................................................................................10 G Wiper Bounce...........................................................................................0.1 millisecond maximum Total Resistance Shift..............................................................................................±1 % maximum Voltage Ratio Shift................................................................................................±0.2 % maximum Shock.............................................................................................................................................50 G Wiper Bounce...........................................................................................0.1 millisecond maximum Total Resistance Shift..............................................................................................±1 % maximum Voltage Ratio Shift................................................................................................±0.2 % maximum Load Life...............................................................................................................1,000 hours, 2 watts Total Resistance Shift..............................................................................................±2 % maximum Rotational Life.........................................................................75,000 button operations each decade Total Resistance Shift..............................................................................................±2 % maximum IP Rating........................................................................................................................................IP 40Mechanical Characteristics 1Weight....................................3681 (9 gm); 3682 (16 gm); 3683 (23 gm); 3684 (30 gm); 3685 (37 gm)T erminals.....2.79 mm (0.11 in.) wide x .41 mm (.016 in.) thick, tinned solder lugs for 3 #20 AWG wires Soldering ConditionManual Soldering..........................................................96.5Sn/3.0Ag/0.5Cu solid wire or no-cleanrosin cored wire; 370 °C (700 °F) max. for 3 secondsWave Soldering....................96.5Sn/3.0Ag/0.5Cu solder with no-clean flux; 260 °C (500 °F) max.for 5 secondsWash processes..................................................................................................Not recommended Marking...............................Manufacturer’s name and part number, resistance value and date code.Ganging (Multiple Section Potentiometers)...............................................Up to 5 decades maximum Readout Marking........................................................................................................10 positions, 0-9Actuating Force...................................................................................19 to 29 oz. on detent decades Actuating Force Variation..............................................................................................4 oz. maximum1At room ambient: +25 °C nominal and 50 % relative humidity nominal, except as noted.NOTE: Terminals 1 & 3 are reversed from illustration for models 3682 and 3684.3680INCR.Product DimensionsDimensionsWeight (Approx.)Model a b c d e –.381 (–.015)oz.gms.368116.51 (.650)14.99 (.590)—9.91 (.39) 4.19 (.165).3369.5368226.67 (1.05)25.15 (.99)10.67 (.42)11.94 (.47)8.38 (.330).57616.5368337.08 (1.46)35.31 (1.39)18.54 (.73)11.94 (.47) 4.19 (.165).82423.5368447.50 (1.87)45.47 (1.79)30.73 (1.21)11.94 (.47)8.38 (.330) 1.07230.5368557.66 (2.270)55.63 (2.190)39.12 (1.540)11.94 (.47)4.19 (.165)1.32037.5DimensionsModel f –.010 (–.254)g –.010 (–.254)368121.08 (.830)15.75 (.620)368221.08 (.830)25.91 (1.020)368321.08 (.830)36.07 (1.420)368421.08 (.830)46.23 (1.820)368521.08 (.830)56.39 (2.220)*Ro H S C O M P L I A N T V E R S I O N S A V A I L A B L ESpecifications are subject to change without notice.Customers should verify actual device performance in their specific applications.Recommended Part NumbersBOLDFACE LISTINGS ARE IN STOCK AND READILY AVAILABLE THROUGH DISTRIBUTION.FOR OTHER OPTIONS CONSULT FACTORY.RoHS IDENTIFIER:L =COMPLIANTBLANK =NON-COMPLIANTREV. 05/07。

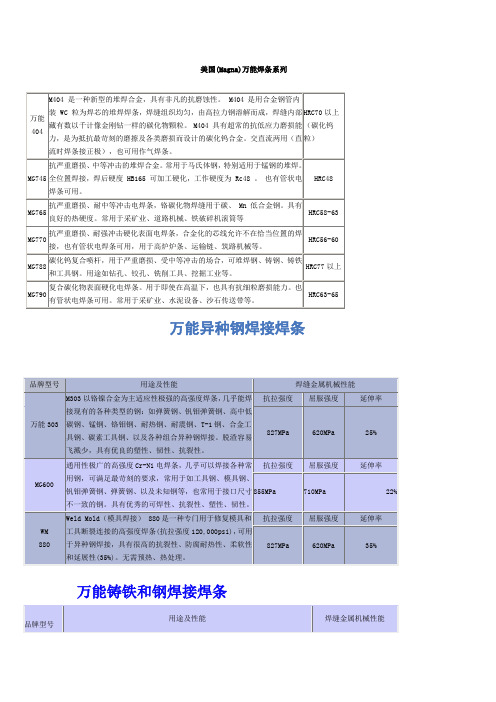

美国(Magna)万能焊条

美国(Magna)万能焊条系列万能异种钢焊接焊条万能铸铁和钢焊接焊条万能异种金属间焊接焊条万能铜金属焊接焊条气焊万能 33F 高韧度, 适用于各钢类之气焊条焊金流动性与银焊条相似。

万能 51 适用于铝及铸锌件之修理, 对铝与铜之焊接尤佳, 可做铝之此型T接及搭接, 铝及异指类金属之焊接。

万能 55 本焊条是专门对铝, 铝合金, 铸铝而特吶设计的, 具备有此一种焊材可解决任何铝之焊接问题。

万能 66F 是一种附带药皮的高银含量全功能焊条,适用于维修应用,对几乎所有黑色及有色金属的焊接都有带腐蚀性的出众效果。

万能 67F 最幼细的, 涂以银质焊料之多用途焊枝为特殊之维修工作而配方。

万能 75F 一种多用途的青铜质合金, 用于铸铁和其它金属的焊接。

万能 77F 为焊接因磨损及破坏了的零件而设的超级敏感焊金。

万能 88C 自生熔剂超强力软焊焊合金, 并具超强抗腐蚀之万能合金。

电弧焊万能 8N12 多效的焊条用于焊接抗高温合金钢, 英高镍, 纯镍, 和所有镍合金. 可焊接50种以上的不同合金。

万能 100 是最经济且速度最快之开槽焊条。

万能 150 用来切割和穿洞。

万能 210 具有广泛用途之电焊枝。

万能 303 一种具有高效二相杆敷金属的焊条, 具有优越的抗裂作用。

万能 305 高强度可在任何位置施杆之电杆条,对T-型钢, 管道及圆形管与钢板之焊接最适用。

万能 307 钢合金焊枝。

万能 393 特佳流火烧焊, 防止腐蚀。

万能 395 特制的Duplex不锈钢焊条。

万能 400 完全是针对轧碎而设计, 有优越之填补率而节省许多焊条。

万能 401 用于一般耐冲击及耐磨耗。

万能 402 可耐非常强劲的冲击及锰钢的接合。

万能 403 含钦及铬合金乏耐磨炉条最耐高低重压之磨擦。

万能 404 密度高硬度均匀之碳化钨电焊条, 可作最耐磨损之硬化补面。

( 亦可用于气杆)万能 405 可堆填的焊条。

(强韧可机械加工火焰硬化)万能 440 高速工具钢焊条, 专为耐长期磨损刀刃而设的独有合金。

HMD4M36M9G-6中文资料

5 0.4

UNITS mA mA mA mA mA mA mA mA mA mA µA µA V V

HANBit Electronics Co.,Ltd.

元器件交易网

HANBiT

HMD4M36M9G, HMD4M36M9AG

ICC5 : Standby Current (/RAS=/CAS=Vcc-0.2V ) ICC6 : /CAS-Before-/RAS Refresh Current * (/RAS and /CAS cycling @tRC=min ) IIL : Input Leakage Current (Any input 0V ≤ VIN ≤ 6.5V, all other pins not under test = 0V) IOL : Output Leakage Current (Data out is disabled, 0V ≤ VOUT ≤ 5.5V VOH : Output High Voltage Level (IOH= -5mA ) VOL : Output Low Voltage Level (IOL = 4.2mA ) * NOTE: ICC1, ICC3, ICC4 and ICC6 are dependent on output loading and cycle rates. Specified values are obtained with the

MEMORY存储芯片MT46V8M16TG-6G B中文规格书

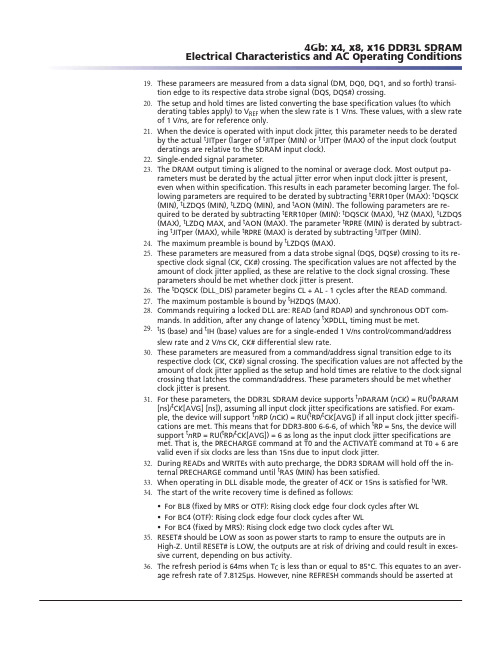

19.These parameers are measured from a data signal (DM, DQ0, DQ1, and so forth) transi-tion edge to its respective data strobe signal (DQS, DQS#) crossing.20.The setup and hold times are listed converting the base specification values (to which derating tables apply) to V REF when the slew rate is 1 V/ns. These values, with a slew rate of 1 V/ns, are for reference only.21.When the device is operated with input clock jitter, this parameter needs to be derated by the actual t JITper (larger of t JITper (MIN) or t JITper (MAX) of the input clock (output deratings are relative to the SDRAM input clock).22.Single-ended signal parameter.23.The DRAM output timing is aligned to the nominal or average clock. Most output pa-rameters must be derated by the actual jitter error when input clock jitter is present,even when within specification. This results in each parameter becoming larger. The fol-lowing parameters are required to be derated by subtracting t ERR10per (MAX): t DQSCK (MIN), t LZDQS (MIN), t LZDQ (MIN), and t AON (MIN). The following parameters are re-quired to be derated by subtracting t ERR10per (MIN): t DQSCK (MAX), t HZ (MAX), t LZDQS (MAX), t LZDQ MAX, and t AON (MAX). The parameter t RPRE (MIN) is derated by subtract-ing t JITper (MAX), while t RPRE (MAX) is derated by subtracting t JITper (MIN).24.The maximum preamble is bound by t LZDQS (MAX).25.These parameters are measured from a data strobe signal (DQS, DQS#) crossing to its re-spective clock signal (CK, CK#) crossing. The specification values are not affected by the amount of clock jitter applied, as these are relative to the clock signal crossing. These parameters should be met whether clock jitter is present.26.The t DQSCK (DLL_DIS) parameter begins CL + AL - 1 cycles after the READ command.27.The maximum postamble is bound by t HZDQS (MAX).mands requiring a locked DLL are: READ (and RDAP) and synchronous ODT com-mands. In addition, after any change of latency t XPDLL, timing must be met.29.t IS (base) and t IH (base) values are for a single-ended 1 V/ns control/command/addressslew rate and 2 V/ns CK, CK# differential slew rate.30.These parameters are measured from a command/address signal transition edge to its respective clock (CK, CK#) signal crossing. The specification values are not affected by the amount of clock jitter applied as the setup and hold times are relative to the clock signal crossing that latches the command/address. These parameters should be met whether clock jitter is present.31.For these parameters, the DDR3L SDRAM device supports t n PARAM (n CK) = RU(t PARAM[ns]/t CK[AVG] [ns]), assuming all input clock jitter specifications are satisfied. For exam-ple, the device will support t n RP (n CK) = RU(t RP/t CK[AVG]) if all input clock jitter specifi-cations are met. This means that for DDR3-800 6-6-6, of which t RP = 5ns, the device will support t n RP = RU(t RP/t CK[AVG]) = 6 as long as the input clock jitter specifications are met. That is, the PRECHARGE command at T0 and the ACTIVATE command at T0 + 6 are valid even if six clocks are less than 15ns due to input clock jitter.32.During READs and WRITEs with auto precharge, the DDR3 SDRAM will hold off the in-ternal PRECHARGE command until t RAS (MIN) has been satisfied.33.When operating in DLL disable mode, the greater of 4CK or 15ns is satisfied for t WR.34.The start of the write recovery time is defined as follows:•For BL8 (fixed by MRS or OTF): Rising clock edge four clock cycles after WL•For BC4 (OTF): Rising clock edge four clock cycles after WL•For BC4 (fixed by MRS): Rising clock edge two clock cycles after WL35.RESET# should be LOW as soon as power starts to ramp to ensure the outputs are in High-Z. Until RESET# is LOW, the outputs are at risk of driving and could result in exces-sive current, depending on bus activity.36.The refresh period is 64ms when T C is less than or equal to 85°C. This equates to an aver-age refresh rate of 7.8125μs. However, nine REFRESH commands should be asserted at4Gb: x4, x8, x16 DDR3L SDRAM Electrical Characteristics and AC Operating ConditionsTable 17: I DD5B Measurement LoopNotes: 1.DQ, DQS, DQS# are midlevel.2.DM is LOW.4Gb: x4, x8, x16 DDR3L SDRAM Electrical Specifications – I DD Specifications and Conditions。

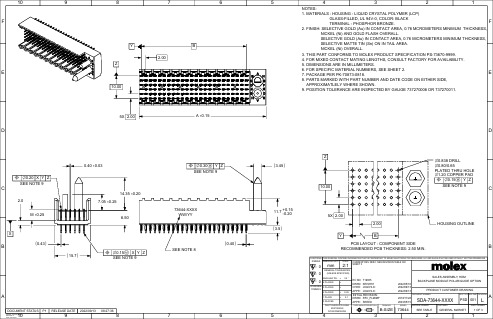

摩乐斯电子技术有限公司 HDM 后平面模块极性引脚选项销售集装箱 型号:73644说明书

DOCUMENT STATUS P1RELEASE DATE 2022/09/1308:27:36 FUNCTIONAL SYMBOLS =0=0=0DIVISIONAL SYMBOLS THIS DRAWING CONTAINS INFORMATION THAT IS PROPRIETARY TO MOLEX ELECTRONIC TECHNOLOGIES, LLC AND SHOULD NOT BE USED WITHOUT WRITTEN PERMISSIONCURRENT REV DESC: SEE REVISION TABLE ON SHEET 3EC NO:719835DRWN:KRISHH12022/05/16CHK'D:JKACHLIC 2022/09/13APPR:JKACHLIC 2022/09/13INITIAL REVISION:DRWN:RFC_PLMIMP 2018/11/28APPR:SREED 2003/05/15THIRD ANGLE PROJECTION DRAWING SERIES B-SIZE 73644SALES ASSEMBLY , HDM BACKPLANE MODULE POLAR/GUIDE OPTION PRODUCT CUSTOMER DRAWING DOCUMENT NUMBER DOC TYPE DOC PART REVISION SDA-73644-XXXX PSD 001L MATERIAL NUMBER CUSTOMER SHEET NUMBER SEE TABLE GENERAL MARKET 1 OF 3DIMENSION UNITS SCALE mm 2:1GENERAL TOLERANCES (UNLESS SPECIFIED)ANGULAR TOL ±0.5 °4 PLACES ±3 PLACES ±2 PLACES ±0.051 PLACE ±0.10 PLACES ±DRAFT WHERE APPLICABLE MUST REMAINWITHIN DIMENSIONS NOTES:1. MATERIALS : HOUSING - LIQUID CRYSTAL POLYMER (LCP) GLASS-FILLED, UL 94V-0, COLOR: BLACK TERMINAL - PHOSPHOR BRONZE.2. FINISH: SELECTIVE GOLD (Au) IN CONTACT AREA, 0.76 MCROMETERS MINIMUM THICKNESS, NICKEL (Ni) AND GOLD FLASH OVERALL. SELECTIVE GOLD (Au) IN CONTACT AREA, 0.76 MICROMETERS MINIMUM THICKNESS, SELECTIVE MATTE TIN (Sn) ON IN TAIL AREA. NICKEL (Ni) OVERALL.3. THIS PART CONFORMS TO MOLEX PRODUCT SPECIFICATION PS-73670-9999.4. FOR MIXED CONTACT MATING LENGTHS, CONSULT FACTORY FOR AVAILABILITY.5. DIMENSIONS ARE IN MILLIMETERS.6. FOR SPECIFIC MATERIAL NUMBERS, SEE SHEET 2.7. PACKAGE PER PK-70873-0818.8. PARTS MARKED WITH PART NUMBER AND DATE CODE ON EITHER SIDE, APPROXIMATLELY WHERE SHOWN.9. POSITION TOLERANCE ARE INSPECTED BY GAUGE 737270006 OR 737270011.B2.00A ±0.1510.005X 2.0014.35±0.207.05±0.25 6.502.0M ±0.25�15.7��0.43�0.40±0.03�0.40�11.7+0.15-0.20�3.5��3.45� PCB LAYOUT : COMPONENT SIDE RECOMMENDED PCB THICKNESS: 2.50 MIN.10.005X 2.002.00BHOUSING OUTLINE0.80/0.65⌀0.838 DRILL PLATED THRU HOLE ⌀1.20 COPPER PAD⌖⌀0.15ⓂY Z⌀SEE NOTE 9ZY 73644-XXXX WW/YY SEE NOTE 8⌖⌀0.30ⓂY ZSEE NOTE 9⌖⌀0.15ⓂX Y ZSEE NOTE 9⌖⌀0.20X Y Z SEE NOTE 9ZY 1A A2BB 3CC 4DD 5E E6F F78910XFORMAT: master-tb-prod-BREVISION: J1DATE: 2021/05/01DOCUMENT STATUSP1RELEASE DATE 2022/09/1308:27:36 FUNCTIONAL SYMBOLS =0=0=0DIVISIONAL SYMBOLS DIMENSION UNITS SCALE mm 2:1GENERAL TOLERANCES (UNLESS SPECIFIED)ANGULAR TOL ±0.5 °4 PLACES ±3 PLACES ±2 PLACES ±0.051 PLACE ±0.10 PLACES ±DRAFT WHERE APPLICABLE MUST REMAIN WITHIN DIMENSIONS CURRENT REV DESC: SEE REVISION TABLE ON SHEET 3EC NO:719835DRWN:KRISHH12022/05/16CHK'D:JKACHLIC 2022/09/13APPR:JKACHLIC 2022/09/13INITIAL REVISION:DRWN:RFC_PLMIMP 2018/11/28APPR:SREED 2003/05/15THIRD ANGLE PROJECTION DRAWING SERIES B-SIZE 73644THIS DRAWING CONTAINS INFORMATION THAT IS PROPRIETARY TO MOLEX ELECTRONIC TECHNOLOGIES, LLC AND SHOULD NOT BE USED WITHOUT WRITTEN PERMISSION SALES ASSEMBLY , HDM BACKPLANE MODULE POLAR/GUIDE OPTION PRODUCT CUSTOMER DRAWING DOCUMENT NUMBER DOC TYPE DOC PART REVISION SDA-73644-XXXX PSD 001L MATERIAL NUMBER CUSTOMER SHEET NUMBER SEE TABLE GENERAL MARKET 2 OF 3MATERIALNUMBER NUMBER OF SIGNAL CONTACTS PLATING DIM "A"DIM "B"DIM "M"73644-00**72SELECTIVE GOLD/GOLD FLASH 31.6022.00 5.0073644-01**72SELECTIVE GOLD/GOLD FLASH 31.6022.00 5.5073644-02**72SELECTIVE GOLD/GOLD FLASH 31.6022.00 6.0073644-10**144SELECTIVE GOLD/GOLD FLASH 55.6046.00 5.0073644-11**144SELECTIVE GOLD/GOLD FLASH 55.6046.00 5.5073644-12**144SELECTIVE GOLD/GOLD FLASH 55.6046.00 6.0073644-20**72 SELECTIVE GOLD/SELECTIVE MATTE TIN 31.6022.00 5.0073644-21**72 SELECTIVE GOLD/SELECTIVE MATTE TIN 31.6022.00 5.5073644-22**72 SELECTIVE GOLD/SELECTIVE MATTE TIN 31.6022.00 6.0073644-30**144 SELECTIVE GOLD/SELECTIVE MATTE TIN 55.6046.00 5.0073644-31**144 SELECTIVE GOLD/SELECTIVE MATTE TIN 55.6046.00 5.5073644-32**144 SELECTIVE GOLD/SELECTIVE MATTE TIN 55.6046.00 6.001A A2BB 3C C 4D D5EE 6F F78910LOCATION ALOCATION B ROW F ROW ALOCATION BLOCATION AREF. MATERIAL NUMBER 73644-0008GUIDE PIN IS IN LOCATION BPOLARIZING KEY IS IN LOCATION A, POSITION E REF. MATERIAL NUMBER 73644-0009GUIDE PIN IS IN LOCATION A POLARIZING KEY IS IN LOCATION B, POSITION E MATERIAL NUMBER ASSIGNMENT 73644 - * * * *CIRCUIT SIZE0= 72 CIRCUIT, GOLD/GOLD FLASH1= 144 CIRCUIT, GOLD/GOLD FLASH2= 72 CIRCUIT, GOLD/MATTE TIN3= 144 CIRCUIT, GOLD/MATTE TIN* FORMERLY TIN/ LEAD 0= 5.00 MATING LENGTH1= 5.50 MATING LENGTH2= 6.00 MATING LENGTHNUMBER GUIDE POST LOCATION POLAR KEY POSITION 00B A 01A 02B B 03A 04B C 05A 06B D 07A 08B E 09A 10B F 11A 12B G 13A 14B H 15A 16B N/A17A 18N/ADOCUMENT STATUS P1RELEASE DATE 2022/09/1308:27:3632FUNCTIONAL SYMBOLS =0=0=0A 5B FDIVISIONAL SYMBOLS 91CDIMENSION UNITS SCALE mm 1:1GENERAL TOLERANCES (UNLESS SPECIFIED)ANGULAR TOL ±0.5 °4 PLACES ±3 PLACES ±2 PLACES ±0.051 PLACE ±0.10 PLACES ±DRAFT WHERE APPLICABLE MUST REMAINWITHIN DIMENSIONS SALES ASSEMBLY , HDM BACKPLANE MODULE POLAR/GUIDE OPTION PRODUCT CUSTOMER DRAWING DOCUMENT NUMBER DOC TYPE DOC PART REVISION SDA-73644-XXXX PSD 001L MATERIAL NUMBER CUSTOMER SHEET NUMBER SEE TABLE GENERAL MARKET 3 OF 3CURRENT REV DESC: SEE REVISION TABLE ON SHEET 3EC NO:719835DRWN:KRISHH12022/05/16CHK'D:JKACHLIC 2022/09/13APPR:JKACHLIC 2022/09/13INITIAL REVISION:DRWN:RFC_PLMIMP 2018/11/28APPR:SREED 2003/05/15THIRD ANGLE PROJECTION DRAWING SERIES B-SIZE 73644THIS DRAWING CONTAINS INFORMATION THAT IS PROPRIETARY TO MOLEX ELECTRONIC TECHNOLOGIES, LLC AND SHOULD NOT BE USED WITHOUT WRITTEN PERMISSIONE 6E 710F BA8D D C 4DATE REV DESCRIPTION05/19/2022L1. DRAWING MIGRATION.2. SHEET 1: E07:DIMENSION 0.92 REMOVED BECAUSE DIM 'A' AND DIM 'B' ARE WITH SAME CENTER LINE, SO DIM 0.92 IS NOT REQUIRED.3. SHEET 1: C09: DIM 0.42 CHANGED TO 0.40±0.03MM, TO FOLLOW ACTUAL COMPONENT DIMENSION.0.394. SHEET 1: D06: TOLERANCE OF DIM 'A' CHANGED TO ±0.15 FROM ±0.10, TO FOLLOW ACTUAL COMPONENT DIMENSION.5. SHEET 1: C10: DIM 2.00 CHANGED TO DIM 2.0 TO INCREASE THE TOLERANCE TO FOLLOW ACTUAL COMPONENT DIMENSION.6. SHEET 1: E04: ADDED NOTE 9 FOR POSITION TOLERANCE MEASUREMENT.7. SHEET 1: E08, E07, C04, B03 : REMOVED BRACKET FROM THE BASIC DIMENSION 10.00, B , 10.00, B RESPECTIVELY FOR TP CONTROL8. SHEET 1: B08, C10, C06, C01 : ADDED "SEE NOTE 8" FOR TP CONTROL9. SHEET 1: C08: DIM 7.05±0.20 AND 14.35±0.15 CHANGED TO 7.05±0.25 AND 14.35±0.15 RESPECTIVELY.。

MEMORY存储芯片MT46V8M16FJ-6中文规格书

fresh mode, the DLL remains disabled even upon exit of SELF REFRESH operation untilit is re-enabled and reset.The DRAM is not tested to check—nor does Micron warrant compliance with—normalmode timings or functionality when the DLL is disabled. An attempt has been made tohave the DRAM operate in the normal mode where reasonably possible when the DLLhas been disabled; however, by industry standard, a few known exceptions are defined:•ODT is not allowed to be used•The output data is no longer edge-aligned to the clock•CL and CWL can only be six clocksWhen the DLL is disabled, timing and functionality can vary from the normal operationspecifications when the DLL is enabled (see DLL Disable Mode (page 125)). Disablingthe DLL also implies the need to change the clock frequency (see Input Clock Frequen-cy Change (page 129)).Output Drive StrengthThe DDR3 SDRAM uses a programmable impedance output buffer. The drive strengthmode register setting is defined by MR1[5, 1]. RZQ/7 (34ȍ [NOM]) is the primary outputdriver impedance setting for DDR3 SDRAM devices. To calibrate the output driver im-pedance, an external precision resistor (RZQ) is connected between the ZQ ball andV SSQ. The value of the resistor must be 240ȍ ±1%.The output impedance is set during initialization. Additional impedance calibration up-dates do not affect device operation, and all data sheet timings and current specifica-tions are met during an update.To meet the 34ȍ specification, the output drive strength must be set to 34ȍ during initi-alization. To obtain a calibrated output driver impedance after power-up, the DDR3SDRAM needs a calibration command that is part of the initialization and reset proce-dure.OUTPUT ENABLE/DISABLEThe OUTPUT ENABLE function is defined by MR1[12], as shown in Figure 56 (page146). When enabled (MR1[12] = 0), all outputs (DQ, DQS, DQS#) function when in thenormal mode of operation. When disabled (MR1[12] = 1), all DDR3 SDRAM outputs(DQ and DQS, DQS#) are tri-stated. The output disable feature is intended to be usedduring I DD characterization of the READ current and during t DQSS margining (writeleveling) only.TDQS EnableTermination data strobe (TDQS) is a feature of the x8 DDR3 SDRAM configuration thatprovides termination resistance (R TT) and may be useful in some system configurations.TDQS is not supported in x4 or x16 configurations. When enabled via the mode register(MR1[11]), the R TT that is applied to DQS and DQS# is also applied to TDQS and TDQS#.In contrast to the RDQS function of DDR2 SDRAM, DDR3’s TDQS provides the termina-tion resistance R TT only. The OUTPUT DATA STROBE function of RDQS is not providedby TDQS; thus, R ON does not apply to TDQS and TDQS#. The TDQS and DM functionsshare the same ball. When the TDQS function is enabled via the mode register, the DMfunction is not supported. When the TDQS function is disabled, the DM function is pro-vided, and the TDQS# ball is not used. The TDQS function is available in the x8 DDR3DLL Disable ModeIf the DLL is disabled by the mode register (MR1[0] can be switched during initializationor later), the DRAM is targeted, but not guaranteed, to operate similarly to the normalmode, with a few notable exceptions:•The DRAM supports only one value of CAS latency (CL = 6) and one value of CASWRITE latency (CWL = 6).•DLL disable mode affects the read data clock-to-data strobe relationship (t DQSCK),but not the read data-to-data strobe relationship (t DQSQ, t QH). Special attention isrequired to line up the read data with the controller time domain when the DLL is dis-abled.•In normal operation (DLL on), t DQSCK starts from the rising clock edge AL + CLcycles after the READ command. In DLL disable mode, t DQSCK starts AL + CL - 1 cy-cles after the READ command. Additionally, with the DLL disabled, the value oft DQSCK could be larger than t CK.The ODT feature (including dynamic ODT) is not supported during DLL disable mode.The ODT resistors must be disabled by continuously registering the ODT ball LOW byprogramming R TT,nom MR1[9, 6, 2] and R TT(WR) MR2[10, 9] to 0 while in the DLL disablemode.Specific steps must be followed to switch between the DLL enable and DLL disablemodes due to a gap in the allowed clock rates between the two modes (t CK [AVG] MAXand t CK [DLL_DIS] MIN, respectively). The only time the clock is allowed to cross thisclock rate gap is during self refresh mode. Thus, the required procedure for switchingfrom the DLL enable mode to the DLL disable mode is to change frequency during selfrefresh:1.Starting from the idle state (all banks are precharged, all timings are fulfilled, ODTis turned off, and R TT,nom and R TT(WR) are High-Z), set MR1[0] to 1 to disable theDLL.2.Enter self refresh mode after t MOD has been satisfied.3.After t CKSRE is satisfied, change the frequency to the desired clock rate.4.Self refresh may be exited when the clock is stable with the new frequency fort CKSRX. After t XS is satisfied, update the mode registers with appropriate values.5.The DRAM will be ready for its next command in the DLL disable mode after thegreater of t MRD or t MOD has been satisfied. A ZQCL command should be issuedwith appropriate timings met.。

MH64S72VJG-5资料