数字电路后端设计_逻辑综合资料共59页文档

集成电路后端设计简介.pptx

N型MOS管物理结构和电路符号

栅极 源极

导体 绝缘体

栅极

栅极

n

n

p 掺杂半导体衬底

n 型MOS管

漏极 源极

漏极 源极

漏极

衬底 耗尽型电路符号

衬底 增强型电路符号

第6页/共74页

P型MOS管物理结构和电路符号

栅极 源极

导体 绝缘体

栅极

栅极

p

p

n 掺杂半导体衬底

p 型MOS管

漏极

源极

第37页/共74页

CMOS传输门

CMOS传输门工作原理: 在图中的CMOS传输门采用了P管和N管对,控制信号和C分别控制P管和N管,使两管同时关断和开通。

由于PMOS管对输入信号S高电平的传输性能好,而NMOS管对输入信号S低电平的传输性能好,从而使信 号S可以获得全幅度的传送而没有电平损失。

第38页/共74页

第14页/共74页

MOS晶体管性能分析

描述NMOS器件在三个区域中性能的理想表达式为:

Ids=

0

(a)截止区

Vgs-VT≤0

(b)线性区

0<Vgs-VT< Vds (c)饱和区

第15页/共74页

MOS器件电压-电流特性

N型MOS管和P型MOS管工作在线性区和饱和区时的电压-电流特性曲线:

线性区 ︱Vds︱=︱Vgs-Vt︱

(0V)。值得指出的是,任一种逻辑状态,不管

是Vi为VDD或为VSS,两个晶体管必有一个截止。

因此,在任一逻辑状态下,只有非常小的电流从

VDD流向VSS,所以耗电很少。对高密度应用来说,

CMOS的低功耗是它最重要的优点。

第24页/共74页

数字电路与逻辑设计方案课件

数字电路及逻辑设计

数字逻辑基础

数字电路及逻辑设计

数字逻辑基础

数字电路及逻辑设计

学时安排及考核办法

课堂教学共计54学时 实验教学18学时

72学时

考核:闭卷 期末50%+综合50% (综合=实验15%+期中平时测验25%+作业10%)

数字逻辑基础

数字电路及逻辑设计

其余码制还有2421码,其权值依次为2、4、2、1;余3码, 由8421BCD码每个代码加0011得到;格雷码是一种循环码, 其特点是任意相邻的两个数码,仅有一位代码不同,其它位 相同。

数字逻辑基础

数字电路及逻辑设计

种类 十进制

常用的几种BCD码

8421码

2421码

0

0000

0000

1

0001

0001

数字逻辑基础

数字电路及逻辑设计

②位权:任一计数制中的每一位数,其大小都对应该位上的 数码乘上一个固定的数,这个固定的数称作各位的权,简称 位权。位权是各种计数制中基数的幂。

十进制数(2368)10=2×103+3×102+6×101+8×100

其中各位上的数码与10的幂相乘表示该位数的实际代表 值,如2×103代表2000,3×102代表300,6×101代表60, 8×100代表8。而各位上的10的幂就是十进制数各位的权。

数字逻辑基础

把下列二进制数转换成十六进制数。

(1001101110011011)2=( 9B9B)16 (11100100110110)2=( 3936 )16

把下列十进制数转换成二进制、八进制和十六进制数。

(364.5)10=( 101101100.1 )2=(16C.8 )16 =( 554.4 )8 (74)10=( 1001010 )2=( 4A )16 =( 112 )8

数字后端简要流程教材

• set_max_delay: 1、对于仅包含组合逻辑的模块,用此命令约束所有输入到输出 的总延时。 例如: set_max_delay 5 -from all_inputs() -to all_outputs 2、对于含有多个时钟的模块,可用通常的方法定义一个时钟, 用此命令进行约束定义时钟和其他时钟之间的关系。 例如:set_max_delay 0 –from CLK2 –to all_register(clock_pin) • set_min_delay: 1、对于仅包含组合逻辑的模块,定义指定路径的最小延时。 例如:set_min_delay 3 -from all_inputs() 2、和set_fix_hold一起使用,只是DC添加一定的延迟,满足最 小延迟需求。

set_operating_conditions set_drive on Clock set_driving_cell on inputs

Clock Divider Logic Block B Block A

set_load on outputs set_max_capacitance set_max_transition &set_max_fanout on input &output ports or current_design;

数字后端简要流程

HDL代码

逻辑综合

布局布线

形式验证

综合的定义

• 逻辑综合:决定设计电路逻辑门之间的相互连接。 • 逻辑综合的目的:决定电路门级结构,寻求时序、面积和功耗的平衡, 增强电路的测试性。 • 逻辑综合的过程(constraint_driven) : Synthesis = Translation + Logic Optimization + Mapping

电子工程数字电路设计(知识点)

电子工程数字电路设计(知识点)数字电路设计是电子工程的重要内容,涉及到数字信号的处理和控制。

在电子工程领域中,数字电路是一类电路系统,用于处理和控制数字信号,并实现各种功能。

本文将介绍数字电路设计的知识点,包括逻辑门、组合逻辑电路和时序逻辑电路。

一、逻辑门逻辑门是数字电路设计的基础组成部分,用于处理和操作数字信号。

在数字电路中常见的逻辑门有与门(AND)、或门(OR)、非门(NOT)以及它们的组合形式(如与非门、或非门)。

1. 与门(AND)与门是最基本的逻辑门之一,其输出信号仅在所有输入信号均为高电平时才输出高电平。

与门的符号为“&&”。

2. 或门(OR)或门是另一个常见的逻辑门,其输出信号仅在任一输入信号为高电平时即输出高电平。

或门的符号为“||”。

3. 非门(NOT)非门是最简单的逻辑门,其输出信号与输入信号相反。

非门的符号为“!”。

二、组合逻辑电路组合逻辑电路是由逻辑门组成的电路,根据输入信号的不同组合产生不同的输出信号。

组合逻辑电路的输出仅与当前输入信号有关,而与过去的输入信号或时序无关。

1. 译码器译码器是一种常见的组合逻辑电路,用于将一组输入信号转换为对应的输出信号。

常见的译码器有二进制译码器和十进制译码器等。

2. 多路选择器多路选择器是另一种常见的组合逻辑电路,用于根据选择信号选择不同的输入信号输出。

多路选择器的输出信号与选择信号相关。

三、时序逻辑电路时序逻辑电路是由触发器和组合逻辑电路组成的电路系统,其输出信号不仅与当前输入信号相关,还与过去的输入信号和时序有关。

1. 触发器触发器是时序逻辑电路的基本组成单元,用于存储和延时信号。

常见的触发器有D触发器、JK触发器和T触发器等。

2. 计数器计数器是一种常见的时序逻辑电路,用于计数和记录输入脉冲的数量。

计数器可以分为正向计数器和逆向计数器。

四、应用场景数字电路设计在现代电子工程中具有广泛的应用。

以下是一些常见的应用场景:1. 中央处理器(CPU)中央处理器是计算机的核心部件,其中包含了大量的数字电路设计。

数字电路与逻辑设计综合设计

八、 参考文献

[1] 康华光主编,电子技术基础(数字部分),高等教育出 版社 [2] 蔡声镇、吴允平主编,电子技术基础实践(技能篇), 福建科技出版社

[3] 蔡声镇、吴允平主编,电子技术基础实践(实验篇), 福建科技出版社

[4] /

[5] /

(1-15)

五、总电路图

存在问题和改进措施:

1. 不适用于大于4人的竞赛,如何扩展?

2. 音响电路发出声响单一,如何改进?

3. 抢答控制精度太低,如何提高?

4. 抢答定时时间太短,如何延长?

5. 若用于竞赛现场,还有那些问题需要考虑?

(1-16)

六、系统接线图

计时

7 6

抢答控制器

电源电路

2

2 7

0

0 0 1

0

0 1 0

0

1 0 0

1

0 0 0

0

0 0 0

0

0 0 1

0

1 1 0

1

0 1 0

可得逻辑函数如下:

A Q 4 Q3 Q 2Q1 Q 4Q3 Q 2 Q1

C Q4 Q3 Q 2 Q1

B Q 4 Q3Q2 Q1 Q 4Q3 Q 2 Q1

D0

(1-7)

A

D B C

编码电路

(1-18)

七、应注意的工程问题

a b c d e f g

a b c d e f g

共阳

共阴

如何选择?如何连接?

(1-19)

七、应注意的工程问题

4. 供电电压、功率和电源的电路形式要根据实际需要合 理选择;若电源选择不当,往往会导致系统性能下降, 甚至不能正常工作; 5. 印刷电路板的设计要遵循布线规则;尽可能等所有元 器件(特别是特殊元器件)全部到位后才开始布板; 6. IC插座、接插件尽量少用,系统设计模块化,尽量减 少板件和板件之间的连接线数量,注意根据信号的类 型正确选择合适的导线。 7. 安装、焊接技术一定要熟练掌握,尽可能做到准确无 误,不假焊、不虚焊; 8. 正确选用滤波电路是电路稳定工作的重要条件。

数字电路后端设计_逻辑综合讲义.共63页文档

谢谢!

63

26、要使整个人生都过得舒适、愉快,这是不可能的,因为人类必须具备一种能应付逆境的态度。——卢梭

▪

27、只有把抱怨环境的心情,化为上进的力量,才是成功的保证。——罗曼·罗兰

▪

28、知之者不如好之者,好之者不如乐之者。——孔子

▪

29、勇猛、大胆和坚定的决心能够抵得上武一个强壮的盲人,倚靠在明眼的跛子肩上。——叔本华

数字电路后端设计_逻辑综合讲义.

1、 舟 遥 遥 以 轻飏, 风飘飘 而吹衣 。 2、 秋 菊 有 佳 色,裛 露掇其 英。 3、 日 月 掷 人 去,有 志不获 骋。 4、 未 言 心 相 醉,不 再接杯 酒。 5、 黄 发 垂 髫 ,并怡 然自乐 。

▪

DC逻辑综合(DC课件整理)

A D SET Q

这些变量必须准确指定,否则可能产生意外的结果,灵活的使用这些变量可 以可以大大减少工作量例如:你可以指定了一个标准单元库作为一个目标库 (target_library),然后在 link_1ibrary 列表中指定压焊点工艺库以及所有其 它的宏模块(RAMS、ROMs、etc.),这意味着用户将能够利用标准单元库出现的 单元综合设计,然后再在设计中连接 pads 和宏模块的实例,如果压焊点工艺库 被包含在 target_1ibrary 列表中,那么 DC 可能使用 pads 综合内核的逻辑。 target_1ibrary 名也应该被包含在 link_1ibrary 列表中,这很重要,因为如果 link_library 中没有 target_library 的内容,那么当把门级网表读入 DC 中时, DC 将不能解析在网表中映射的单元,这种情况下 DC 产生警告信息,它不能解析

关键变量的介绍:

1、target_1ibrary变量:是DC中保留的变量,这个变量指定的库是DC用来构建

一个电路的。DC进行映射的几个步骤:设置它让它指向你的生产商提供的库文件。

使用厂家提供的工艺库中的时序数据计算这些门的时序。从target_1ibrary指定

的库中选择功能正确的门。设定目标库使用如下语句: set target _1ibrary

详细布线

版图设计后进 行STA

时序满足将要求吗

数字电路讲义数字电路基础

(1-11)

十六进制与二进制之间的转换:

(10011100101101001000)B= (1001 1100 1011 0100 1000)B =

从末位开始 四位一组

(9

C

B

4

=( 9CB48 ) H

8 )H

第13页/共59页

(1-12)

八进制与二进制之间的转换:

(10011100101101001000)B= (10 011 100 101 101 001 000)B =

§ 1.1 数字电路的基础知识

1.1.1 数字信号和模拟信号

电

模拟信号

子

电

路 中

随时间连续变化的信号

的

信

号

数字信号 时间和幅度都是离散的

第2页/共59页

(1-1)

模拟信号: 正弦波信号 u

t

锯齿波信号

u

t

第3页/共59页

(1-2)

研究模拟信号时,我们注重电路 输入、输出信号间的大小、相位关系。 相应的电子电路就是模拟电路,包括 交直流放大器、滤波器、信号发生器 等。

四变量卡诺图

CD

00

01

11

10

AB

00 1 1 0 1

01 1 0 φ 1

11 0 φ 0 1

10 1 1 0 1

单元编号 0010,对 应于最小 项:

ABC D

函数取0、1均可, 称为无所谓状态 (或任意状态)。

第42页/共59页

(1-41)

有时为了方便,用二进制对应的十进制 表示单元编号。

BC

从末位开始三位 一组

(2

3

45

5

逻辑综合理论

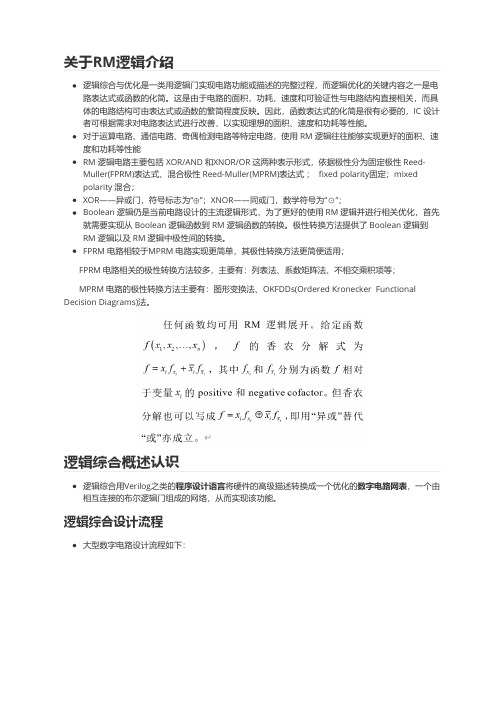

关于RM逻辑介绍逻辑综合与优化是一类用逻辑门实现电路功能或描述的完整过程,而逻辑优化的关键内容之一是电路表达式或函数的化简。

这是由于电路的面积,功耗,速度和可验证性与电路结构直接相关,而具体的电路结构可由表达式或函数的繁简程度反映。

因此,函数表达式的化简是很有必要的,IC 设计者可根据需求对电路表达式进行改善,以实现理想的面积、速度和功耗等性能。

对于运算电路、通信电路、奇偶检测电路等特定电路,使用 RM 逻辑往往能够实现更好的面积、速度和功耗等性能RM 逻辑电路主要包括 XOR/AND 和XNOR/OR 这两种表示形式,依据极性分为固定极性 Reed-Muller(FPRM)表达式、混合极性 Reed-Muller(MPRM)表达式; fixed polarity固定;mixedpolarity 混合;XOR——异或门,符号标志为“⊕”;XNOR——同或门,数学符号为“⊙”;Boolean 逻辑仍是当前电路设计的主流逻辑形式,为了更好的使用 RM 逻辑并进行相关优化,首先就需要实现从 Boolean 逻辑函数到 RM 逻辑函数的转换。

极性转换方法提供了 Boolean 逻辑到RM 逻辑以及 RM 逻辑中极性间的转换。

FPRM 电路相较于MPRM 电路实现更简单,其极性转换方法更简便适用;FPRM 电路相关的极性转换方法较多,主要有:列表法、系数矩阵法、不相交乘积项等;MPRM 电路的极性转换方法主要有:图形变换法、OKFDDs(Ordered Kronecker Functional Decision Diagrams)法。

逻辑综合概述认识逻辑综合用Verilog之类的程序设计语言将硬件的高级描述转换成一个优化的数字电路网表,一个由相互连接的布尔逻辑门组成的网络,从而实现该功能。

逻辑综合设计流程大型数字电路设计流程如下:EDA是用来完成芯片的功能设计、综合、验证、物理设计等流程的设计方式,其中,逻辑级自动综合与优化属于EDA前端设计技术;逻辑综合完成就进入后端设计阶段;布局:就是将综合后的门级电路网表的每个工艺单元合理的摆放到芯片的各个位置;布局的任务是确定每个单元的位置,尽可能减小布线的开销。

数字电路逻辑设计

数字电路逻辑设计数字电路逻辑设计是一种以数字信号作为输入和输出的电路设计方法。

它主要通过组合逻辑和时序逻辑的组合来实现特定的功能。

在数字电路逻辑设计中,使用的元件包括门电路、触发器、寄存器、多路选择器等。

数字电路逻辑设计通常遵循以下几个步骤:1. 需求分析:根据实际需求确定所设计的电路要实现的功能和输入输出的要求。

2. 逻辑设计:根据需求分析结果,设计出满足要求的逻辑电路。

这一步主要包括选择适当的门电路和触发器来实现所需的逻辑功能。

3. 逻辑验证:通过逻辑仿真和测试来验证设计的正确性。

逻辑仿真可以使用专门的仿真工具来模拟电路的运行,以确保电路在不同输入条件下的输出与预期一致。

4. 时序设计:如果所设计的电路涉及到时序逻辑,需要对时序进行设计。

时序设计主要包括时钟分频、状态机设计等。

5. 物理设计:将逻辑设计转换为电路结构和布局,包括确定电路元件的布局和布线方式。

6. 电路制造:根据物理设计结果进行电路的制造和组装。

7. 电路测试:对制造的电路进行测试,以确保其功能和性能满足设计要求。

除了以上的主要步骤,数字电路逻辑设计还需要考虑一些关键因素,如电路的功耗、面积和时序性能等。

在设计过程中,设计人员需要根据实际需求和限制条件进行权衡和优化。

总之,数字电路逻辑设计是一项需要经验和技能的工作。

通过合理的分析和设计,可以实现各种复杂的数字电路,满足不同应用领域的需求。

数字电路逻辑设计是现代电子领域中至关重要的一部分。

它涉及到将现实世界中的信息转变为可操作的数字信号,并通过逻辑门、触发器和其他元件的组合来实现特定的功能。

数字电路逻辑设计在各个领域中发挥着重要的作用,包括计算机科学、通信、控制系统等。

在数字电路逻辑设计中,逻辑门是最基本的构建模块之一。

逻辑门通过接受输入信号并根据特定的逻辑规则产生输出信号。

最常见的逻辑门包括与门、或门、非门和异或门。

通过逻辑门的组合,可以实现更复杂的逻辑功能。

触发器是另一种常用的数字电路元件。

数字集成电路后端设计

43

• 部分截图

2015-3-3

44

7、Standard Cell Placement 注意:这里我们选M1、M2

2015-3-3

45

• 本实验参考步骤 • 选择Place—Specify Placement Blockage for Strip and Route 选择M1、M2;

2015-3-3

2015-3-3

11

• 注意我们使用的是TSMC18工艺,pad名称 的部分截图:

2015-3-3

12

• pad_locs.io文档就是编写添加进来的pad的摆 放位置,如图示:

2015-3-3

13

输入、输出、电源和地的摆放位置示例

2015-3-3

14

• MY_CHIP_PAD.sdc文件是DC综 合之后的时序约束文件,需要进行 修改!只需保留clk和输入输出的 延迟约束信息,其他删除!修改输 入输出信号:输入信号前要加i, 输出信号前加o,clk信号不变。参 考示例文件进行修改。

16

2015-3-3

3、Import Data

• 在linux终端执行:encounter命令,进入图 形界面:

2015-3-3

17

将相关文件和库导进去

• 选择Design—Design Import 在Verilog Netlist 中输入:hardreg.vg hardreg_pad.v; • Top Cell中选择:By User:MY_CHIP_PAD; • 在时间库中Max Timing Libraries: slow.lib tpz973gwc.lib Min timing Libraries: fast.lib tpz973gbc.lib; • 在物理库LEF Files中依次填 写:tsmc18_61m_cic.lef、tpz973g_51m_cic.lef、 tsmc18_61m_antenna_cic.lef、 antenna_6_cic.lef(注意库的顺序不能颠倒,否 则加载报错); • Timing Constraint File : MY_CHIP_PAD.sdc ; 2015-3-3 18 IO Assignment File: pad_locs.io

数字电路与逻辑设计方案

总结词

总结词

在设计时序逻辑电路时,需要先确定状态转移图和状 态方程,然后选择合适的触发器和记忆元件实现状态

转移,最后根据实际需求进行优化和调整。

详细描述

时序逻辑电路的设计关键是选择合适的触发器和记忆 元件,并设计合理的状态转移图和状态方程。

可编程逻辑电路设计

总结词

可编程逻辑电路是一种可以通过编程实现各种逻 辑功能的数字电路。

数字电路与逻辑设计方 案

目录 CONTENT

• 数字电路基础 • 逻辑设计原理 • 数字电路设计流程 • 常见数字电路设计实例 • 数字电路发展趋势与挑战

01

数字电路基础

数字电路的定义与特点

数字电路的定义

数字电路是处理离散信号的电路,其输入和输出信号通常为二进制形 式(0和1)。

数字电路的特点

05

数字电路发展趋势与挑战

集成电路的发展趋势

集成度不断提高

01

随着半导体工艺的进步,集成电路的晶体管数量越来越多,集

成度越来越高,实现了更复杂的功能。

异构集成

02

将不同类型的芯片集成在一个封装内,实现更高效的系统级集

成。

3D集成

03

通过堆叠芯片实现更短的距离和更高的连接密度,提高集成度

和性能。

低功耗设计挑战

能效比要求

随着移动设备和物联网设备的普及,对集成电路的能效比要求越来越高,需要 降低功耗以满足更长的续航时间。

低功耗技术

采用低功耗设计技术,如动态电压和频率调节、多核异构、低功耗待机模式等, 降低芯片功耗。

高性能设计挑战

高速度和低延迟

随着数据传输速率的提高,需要降低信 号延迟和提高数据传输速度以满足实时 性要求。