74HC373中文资料

74HC373中文资料_数据手册_参数

All information provided in this document is subject to legal disclaimers.

Rev. 6 — 26 February 2016

© NXP Semiconductors N.V. 2016. All rights reserved.

+& +&7

9&& 4 ' ' 4 4 ' ' 4 /(

DDH

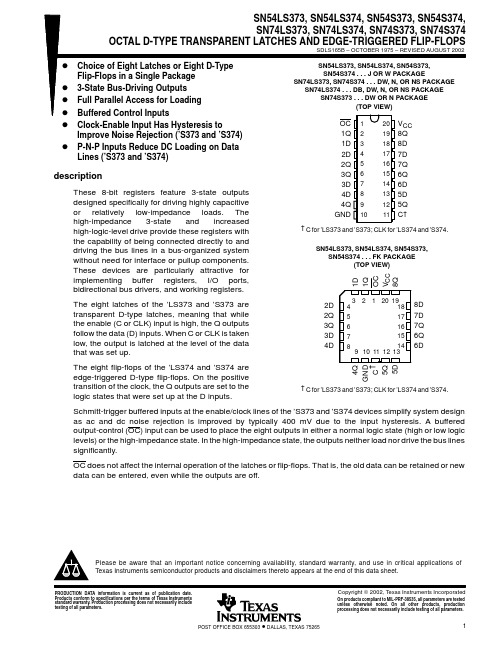

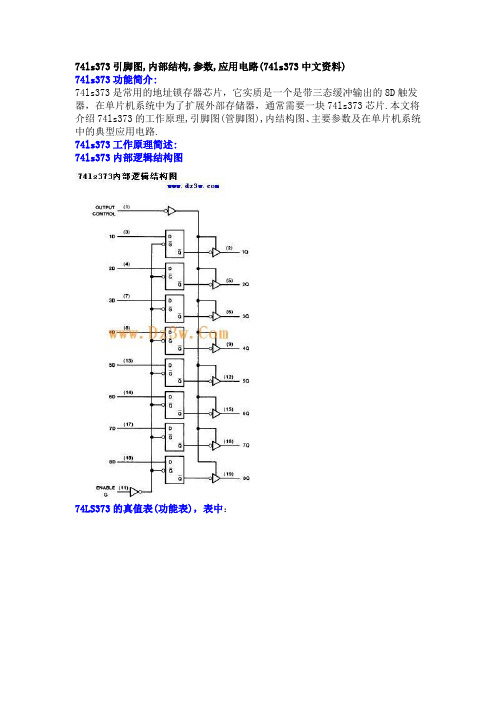

Fig 6. Pin configuration SO20, SSOP20 and TSSOP20

WHUPLQDO LQGH[DUHD

4 of 25

NXP Semiconductors

74HC373; 74HCT373

Octal D-type transparent latch; 3-state

6. Functional description

6.1 Function table

Table 3. Function table[1]

Pin 1 2, 5, 6, 9, 12, 15, 16, 19 3, 4, 7, 8, 13, 14, 17, 18 10 11 20

Description 3-state output enable input (active LOW) 3-state latch output data input ground (0 V) latch enable input (active HIGH) supply voltage

3 of 25

NXP Semiconductors

74HC373; 74HCT373

74LS373中文资料_数据手册_参数

4Q

GND

C†

† C for ’LS373 and ’S373; CLK for ’LS374 and ’S374.

5Q

5D

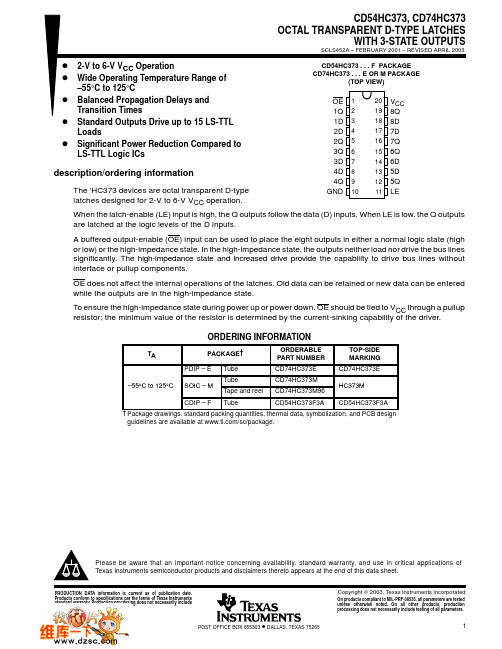

Schmitt-trigger buffered inputs at the enable/clock lines of the ’S373 and ’S374 devices simplify system design as ac and dc noise rejection is improved by typically 400 mV due to the input hysteresis. A buffered output-control (OC) input can be used to place the eight outputs in either a normal logic state (high or low logic levels) or the high-impedance state. In the high-impedance state, the outputs neither load nor drive the bus lines significantly.

74HC373中文资料

74HC373和74LS373原理一样,8数据锁存器。

主要用于数码管、按键等等的控制1. 真值表Dn LE OE OnH H L HL H L LX L L QoX X H Z这个就是真值表,表示这个芯片在输入和其它的情况下的输出情况。

每个芯片的数据手册(datasheet)中都有真值表。

布尔逻辑比较简单,在此不赘述;2. 高阻态就是输出既不是高电平,也不是低电平,而是高阻抗的状态;在这种状态下,可以多个芯片并联输出;但是,这些芯片中只能有一个处于非高阻态状态,否则会将芯片烧毁; 高阻态的概念在RS232和RS422通讯中还可以用到。

3. 数据锁存当输入的数据消失时,在芯片的输出端,数据仍然保持;这个概念在并行数据扩展中经常使用到。

4. 数据缓冲加强驱动能力。

74LS244/74LS245/74LS373/74LS573都具备数据缓冲的能力。

OE:output_enable,输出使能;LE:latch_enable,数据锁存使能,latch是锁存的意思;Dn:第n路输入数据;On:第n路输出数据;再看这个真值表,意思如下:第四行:当OE=1是,无论Dn、LE为何,输出端为高阻态;第三行:当OE=0、LE=0时,输出端保持不变;第二行第一行:当OE=0、LE=1时,输出端数据等于输入端数据;结合下面的波形图,在实际应用的时候是这样做的:a.OE=0;b.先将数据从单片机的口线上输出到Dn;c.再将LE从0->1->0d.这时,你所需要输出的数据就锁存在On上了,输入的数据在变化也影响不到输出的数据了;实际上,单片机现在在忙着干别的事情,串行通信、扫描键盘……单片机的资源有限啊。

在单片机按照RAM方式进行并行数据的扩展时,使用movx @dptr, A这条指令时,这些时序是由单片机来实现的。

后面的表格中还有需要时间的参数,你不需要去管它,因为这些参数都是几十ns级别的,对于单片机在12M下的每个指令周期最小是1us的情况下,完全可以实现;如果是你自己来实现这个逻辑,类似的指令如下:mov P0,A ;将数据输出到并行数据端口clr LEsetb LEclr LE ;上面三条指令完成LE的波形从0->1->0的变化74ls573跟74LS373逻辑上完全一样,只不过是管脚定义不一样,数据输入和输出端。

74HC373及74HCT373规格书

74HC373; 74HCT373Octal D-type transparent latch; 3-stateRev. 4 — 3 September 2010Product data sheet1. General descriptionThe 74HC373; 74HCT373 is a high-speed Si-gate CMOS device and is pin compatiblewith Low-power Schottky TTL. It is specified in compliance with JEDEC standard no. 7A.The 74HC373; 74HCT373 is an octal D-type transparent latch featuring separate D-typeinputs for each latch and 3-state outputs for bus oriented applications. A latch enable (LE)input and an output enable (OE) input are common to all latches.The 74HC373; 74HCT373 consists of eight D-type transparent latches with 3-state trueoutputs. When LE is HIGH, data at the Dn inputs enters the latches. In this condition thelatches are transparent, i.e. a latch output will change state each time its correspondingD input changes.When LE is LOW the latches store the information that was present at the D inputs aset-up time preceding the HIGH-to-LOW transition of LE. When OE is LOW, the contentsof the 8 latches are available at the outputs. When OE is HIGH, the outputs go to the high-impedance OFF-state. Operation of the OE input does not affect the state of the latches.The 74HC373; 74HCT373 is functionally identical to:•74HC563; 74HCT563: but inverted outputs and different pin arrangement•74HC573; 74HCT573: but different pin arrangement2. Features and benefits3-state non-inverting outputs for bus oriented applicationsCommon 3-state output enable inputFunctionally identical to the 74HC563; 74HCT563 and 74HC573; 74HCT573ESD protection:HBM JESD22-A114F exceeds 2000VMM JESD22-A115-A exceeds 200VSpecified from −40°C to+85°C and from −40°C to+125°C3. Ordering information4. Functional diagramTable 1.Ordering informationType number PackageTemperature rangeName DescriptionVersion 74HC373N −40°C to +125°CDIP20plastic dual in-line package; 20leads (300mil)SOT146-174HCT373N 74HC373D −40°C to +125°CSO20plastic small outline package; 20leads;body width 7.5mmSOT163-174HCT373D 74HC373DB −40°C to +125°CSSOP20plastic shrink small outline package; 20leads; body width 5.3mmSOT339-174HCT373DB 74HC373PW −40°C to +125°CTSSOP20plastic thin shrink small outline package; 20leads; body width 4.4mmSOT360-174HCT373PW 74HC373BQ −40°C to +125°CDHVQFN20plastic dual in-line compatible thermal enhanced very thin quad flat package; no leads; 20terminals; body 2.5×4.5×0.85mmSOT764-174HCT373BQ5. Pinning information5.1Pinning5.2Pin descriptionTable 2.Pin descriptionSymbol Pin DescriptionOE13-state output enable input (active LOW) Q0, Q1, Q2, Q3, Q4, Q5, Q6, Q72, 5, 6, 9, 12, 15, 16, 193-state latch outputD0, D1, D2, D3, D4, D5, D6, D73, 4, 7, 8, 13, 14, 17, 18data inputGND10ground (0V)LE11latch enable input (active HIGH)V CC20supply voltage6. Functional description6.1Function table[1]H =HIGH voltage level;h =HIGH voltage level one set-up time prior to the HIGH-to-LOW LE transition;L =LOW voltage level;I =LOW voltage level one set-up time prior to the HIGH-to-LOW LE transition;X =don’t care;Z = high-impedance OFF-state.7. Limiting values[1]For DIP20 package: P tot derates linearly with 12mW/K above 70°C.[2]For SO20: P tot derates linearly with 8mW/K above 70°C.[3]For SSOP20 and TSSOP20 packages: P tot derates linearly with 5.5mW/K above 60°C.[4]For DHVQFN20 package: P tot derates linearly with 4.5mW/K above 60°C.Table 3.Function table [1]Operating mode Control Input Internal latches Output OE LE Dn Qn Enable and read register (transparent mode)L H L L L H H H Latch and read register L L l L L h H H Latch register and disable outputsHXXXZTable 4.Limiting valuesIn accordance with the Absolute Maximum Rating System (IEC 60134). Voltages are referenced to GND (ground = 0 V).Symbol Parameter ConditionsMin Max Unit V CC supply voltage −0.5+7V I IK input clamping current V I < −0.5V or V I >V CC +0.5 V -±20mA I OK output clamping current V O <−0.5V or V O >V CC +0.5V -±20mA I O output current V O = −0.5V to (V CC +0.5V)-±35mA I CC supply current -+70mA I GND ground current -−70mA T stg storage temperature −65+150°C P tottotal power dissipationDIP20 package [1]-750mW SO20 package [2]-500mW SSOP20 package [3]500mW TSSOP20 package [3]500mW DHVQFN20 package[4]-500mW8. Recommended operating conditions9. Static characteristicsTable 5.Recommended operating conditions Voltages are referenced to GND (ground = 0V)Symbol Parameter Conditions74HC37374HCT373UnitMin Typ Max Min Typ Max V CC supply voltage 2.0 5.0 6.0 4.5 5.0 5.5V V I input voltage 0-V CC 0-V CC V V O output voltage 0-V CC 0-V CC V T amb ambient temperature−40+25+125−40+25+125°C Δt/ΔVinput transition rise and fall rateV CC = 2.0 V --625---ns/V V CC = 4.5 V - 1.67139- 1.67139ns/V V CC = 6.0 V --83---ns/V Table 6.Static characteristics 74HC373At recommended operating conditions; voltages are referenced to GND (ground = 0 V).Symbol ParameterConditions Min Typ Max Unit T amb =25°CV IHHIGH-level input voltageV CC = 2.0 V 1.5 1.2-V V CC = 4.5 V 3.15 2.4-V V CC = 6.0 V4.2 3.2-V V ILLOW-level input voltageV CC = 2.0 V -0.80.5V V CC = 4.5 V - 2.1 1.35V V CC = 6.0 V- 2.8 1.8V V OHHIGH-level output voltageV I = V IH or V IL---I O =−20μA; V CC =2.0V 1.9 2.0-V I O =−20μA; V CC =4.5V 4.4 4.5-V I O =−20μA; V CC =6.0V 5.9 6.0-V I O = −6.0 mA; V CC = 4.5 V 3.98 4.32-V I O = −7.8 mA; V CC = 6.0 V5.48 5.81-V V OLLOW-level output voltageV I = V IH or V ILI O =20μA; V CC =2.0V -00.1V I O =20μA; V CC =4.5V -00.1V I O =20μA; V CC =6.0V -00.1V I O = 6.0 mA; V CC = 4.5 V -0.150.26V I O = 7.8 mA; V CC = 6.0 V-0.160.26V I I input leakage current V I =V CC or GND; V CC = 6.0 V --±0.1μA I OZ OFF-state output current V I =V IH or V IL ; V CC =6.0V; V O =V CC or GND --±0.5μA I CC supply current V CC = 6.0 V; I O = 0 A; V I =V CC or GND--8.0μA C Iinput capacitance-3.5-pFT amb =−40°C to +85°CV IHHIGH-level input voltageV CC = 2.0 V 1.5--V V CC = 4.5 V 3.15--V V CC = 6.0 V4.2--V V ILLOW-level input voltageV CC = 2.0 V --0.5V V CC = 4.5 V -- 1.35V V CC = 6.0 V-- 1.8VV OHHIGH-level output voltageV I = V IH or V ILI O =−20μA; V CC =2.0V 1.9--V I O =−20μA; V CC =4.5V 4.4--V I O =−20μA; V CC =6.0V 5.9--V I O = −6.0 mA; V CC = 4.5 V 3.84--V I O = −7.8 mA; V CC = 6.0 V5.34--VV OLLOW-level output voltageV I = V IH or V ILI O =20μA; V CC =2.0V --0.1V I O =20μA; V CC =4.5V --0.1V I O =20μA; V CC =6.0V --0.1V I O = 6.0 mA; V CC = 4.5 V --0.33V I O = 7.8 mA; V CC = 6.0 V--0.33V I I input leakage current V I =V CC or GND; V CC = 6.0 V --±1.0μA I OZ OFF-state output current V I =V IH or V IL ; V CC =6.0V; V O =V CC or GND --±5.0μA I CCsupply currentV CC = 6.0 V; I O =0 A; V I =V CC or GND -80μAT amb =−40°C to +125°C V IHHIGH-level input voltageV CC = 2.0 V 1.5--V V CC = 4.5 V 3.15--V V CC = 6.0 V4.2--V V ILLOW-level input voltageV CC = 2.0 V --0.5V V CC = 4.5 V -- 1.35V V CC = 6.0 V-- 1.8VV OHHIGH-level output voltageV I = V IH or V ILI O =−20μA; V CC =2.0V 1.9--V I O =−20μA; V CC =4.5V 4.4--V I O =−20μA; V CC =6.0V 5.9--V I O = −6.0 mA; V CC = 4.5 V 3.7--V I O = −7.8 mA; V CC = 6.0 V5.2--VTable 6.Static characteristics 74HC373 …continuedAt recommended operating conditions; voltages are referenced to GND (ground = 0 V).Symbol ParameterConditions Min Typ Max UnitV OL LOW-level output voltage V I = V IH or V ILI O=20μA; V CC=2.0V--0.1VI O=20μA; V CC=4.5V--0.1VI O=20μA; V CC=6.0V--0.1VI O = 6.0 mA; V CC = 4.5 V--0.4VI O = 7.8 mA; V CC = 6.0 V--0.4V I I input leakage current V I=V CC or GND; V CC = 6.0 V--±1.0μA I OZ OFF-state output current V I=V IH or V IL; V CC=6.0V;V O=V CC or GND--±10.0μAI CC supply current V CC = 6.0 V; I O = 0 A;V I=V CC or GND --160μATable 6.Static characteristics 74HC373 …continuedAt recommended operating conditions; voltages are referenced to GND (ground = 0 V).Symbol Parameter Conditions Min Typ Max Unit Table 7.Static characteristics 74HCT373At recommended operating conditions; voltages are referenced to GND (ground=0V).Symbol Parameter Conditions Min Typ Max Unit T amb=25°CV IH HIGH-level input voltage V CC=4.5V to 5.5V 2.0 1.6-VV IL LOW-level input voltage V CC=4.5V to 5.5V- 1.20.8VV OH HIGH-level output voltage V I=V IH or V ILI O=−20μA; V CC=4.5V 4.4 4.5-VI O=−6.0mA; V CC=4.5V 3.98 4.32-VV OL LOW-level output voltage V I=V IH or V ILI O=20μA; V CC=4.5V-0.00.1VI O=6.0mA;V CC=4.5V-0.160.26VI I input leakage current V I=V CC or GND; V CC=5.5V--±0.1μA I OZ OFF-state output current V I=V IH or V IL; V CC=5.5V;V O=V CC or GND per input pin;other inputs at V CC or GND; I O=0 A--±0.5μAI CC supply current V I=V CC or GND; I O=0A;V CC=5.5V--8.0μAΔI CC additional supply current V I=V CC−2.1V;other inputs at V CC or GND;V CC=4.5V to5.5V; I O=0ADn-30108μALE-150540μAOE-100360μA C I input capacitance- 3.5-pF T amb=−40°C to +85°CV IH HIGH-level input voltage V CC=4.5V to 5.5V 2.0--VV IL LOW-level input voltage V CC=4.5V to 5.5V--0.8VV OHHIGH-level output voltageV I =V IH or V ILI O =−20μA; V CC =4.5V4.4--V I O =−6.0μA; V CC =4.5V3.84--V V OLLOW-level output voltageV I =V IH or V ILI O =20μA; V CC =4.5V --0.1V I O =6.0mA;V CC =4.5V--0.33V I I input leakage current V I =V CC or GND; V CC =5.5V --±1.0μA I OZOFF-state output currentV I =V IH or V IL ; V CC =5.5V; V O =V CC or GND per input pin; other inputs at V CC or GND; I O =0 A --±5.0μAI CC supply currentV I =V CC or GND; I O =0A; V CC =5.5V--80μAΔI CCadditional supply currentV I =V CC −2.1V;other inputs at V CC or GND; V CC =4.5V to 5.5V; I O =0A Dn --135μA LE --675μA OE--450μAT amb =−40°C to +125°C V IH HIGH-level input voltage V CC =4.5V to 5.5V 2.0--V V IL LOW-level input voltage V CC =4.5V to 5.5V --0.8VV OHHIGH-level output voltageV I =V IH or V ILI O =−20μA; V CC =4.5V 4.4--V I O =−6.0mA; V CC =4.5V3.7--VV OLLOW-level output voltageV I =V IH or V ILI O =20μA; V CC =4.5V --0.1V I O =6.0mA;V CC =4.5V--0.4V I I input leakage current V I =V CC or GND; V CC =5.5V --±1.0μA I OZOFF-state output currentV I =V IH or V IL ; V CC =5.5V; V O =V CC or GND per input pin; other inputs at V CC or GND; I O =0 A --±10μAI CC supply currentV I =V CC or GND; I O =0A; V CC =5.5V--160μAΔI CCadditional supply currentV I =V CC −2.1V;other inputs at V CC or GND; V CC =4.5V to 5.5V; I O =0A Dn --147μA LE --735μA OE--490μATable 7.Static characteristics 74HCT373 …continuedAt recommended operating conditions; voltages are referenced to GND (ground =0V).Symbol ParameterConditions MinTypMaxUnit10. Dynamic characteristicsTable 8.Dynamic characteristics 74HC373Voltages are referenced to GND(ground =0V); C L = 50 pF unless otherwise specified; for test circuit see Figure12. Symbol Parameter Conditions Min Typ Max Unit T amb=25°Ct pd propagation delay Dn to Qn; see Figure8[1]V CC = 2.0 V-41150nsV CC = 4.5 V-1530nsV CC=5V; C L=15pF-12-nsV CC = 6.0 V-1226nsLE to Qn; see Figure9V CC = 2.0 V-50175nsV CC = 4.5 V-1835nsV CC=5V; C L=15pF-15-nsV CC = 6.0 V-1430ns t en enable time OE to Qn; see Figure10[2]V CC = 2.0 V-44150nsV CC = 4.5 V-1630nsV CC = 6.0 V-1326ns t dis disable time OE to Qn; see Figure10[3]V CC = 2.0 V-47150nsV CC = 4.5 V-1730nsV CC = 6.0 V-1426ns t t transition time Qn; see Figure8 and Figure9[4]V CC = 2.0 V-1460nsV CC = 4.5 V-512nsV CC = 6.0 V-410ns t W pulse width LE HIGH; see Figure9V CC = 2.0 V8017-nsV CC = 4.5 V166-nsV CC = 6.0 V145-ns t su set-up time Dn to LE; see Figure11V CC = 2.0 V5014-nsV CC = 4.5 V105-nsV CC = 6.0 V94-ns t h hold time Dn to LE; see Figure11V CC = 2.0 V+5−8-nsV CC = 4.5 V+5−3-nsV CC = 6.0 V+5−2-ns C PD power dissipation capacitance per latch; V I=GND to V CC[5]-45-pFTable 8.Dynamic characteristics 74HC373 …continuedVoltages are referenced to GND(ground =0V); C L = 50 pF unless otherwise specified; for test circuit see Figure12. Symbol Parameter Conditions Min Typ Max Unit T amb=−40°C to+85°Ct pd propagation delay Dn to Qn; see Figure8[1]V CC = 2.0 V--190nsV CC = 4.5 V--38nsV CC = 6.0 V--33nsLE to Qn; see Figure9V CC = 2.0 V--220nsV CC = 4.5 V--44nsV CC = 6.0 V--37ns t en enable time OE to Qn; see Figure10[2]V CC = 2.0 V--190nsV CC = 4.5 V--38nsV CC = 6.0 V--33ns t dis disable time OE to Qn; see Figure10[3]V CC = 2.0 V--190nsV CC = 4.5 V--38nsV CC = 6.0 V--33ns t t transition time Qn; see Figure8 and Figure9[4]V CC = 2.0 V--75nsV CC = 4.5 V--15nsV CC = 6.0 V--13ns t W pulse width LE HIGH; see Figure9V CC = 2.0 V100--nsV CC = 4.5 V20--nsV CC = 6.0 V17--ns t su set-up time Dn to LE; see Figure11V CC = 2.0 V65--nsV CC = 4.5 V13--nsV CC = 6.0 V11--ns t h hold time Dn to LE; see Figure11V CC = 2.0 V5--nsV CC = 4.5 V5--nsV CC = 6.0 V5--nsTable 8.Dynamic characteristics 74HC373 …continuedVoltages are referenced to GND(ground =0V); C L = 50 pF unless otherwise specified; for test circuit see Figure12. Symbol Parameter Conditions Min Typ Max Unit T amb=−40°C to+125°Ct pd propagation delay Dn to Qn; see Figure8[1]V CC = 2.0 V--225nsV CC = 4.5 V--45nsV CC = 6.0 V--38nsLE to Qn; see Figure9V CC = 2.0 V--265nsV CC = 4.5 V--53nsV CC = 6.0 V--45ns t en enable time OE to Qn; see Figure10[2]V CC = 2.0 V--225nsV CC = 4.5 V--45nsV CC = 6.0 V--38ns t dis disable time OE to Qn; see Figure10[3]V CC = 2.0 V--225nsV CC = 4.5 V--45nsV CC = 6.0 V--38ns t t transition time Qn; see Figure8 and Figure9[4]V CC = 2.0 V--90nsV CC = 4.5 V--18nsV CC = 6.0 V--15ns t W pulse width LE HIGH; see Figure9V CC = 2.0 V120--nsV CC = 4.5 V24--nsV CC = 6.0 V20--ns t su set-up time Dn to LE; see Figure11V CC = 2.0 V75--nsV CC = 4.5 V15--nsV CC = 6.0 V13--ns[1]t pd is the same as t PLH and t PHL .[2]t en is the same as t PZH and t PZL .[3]t dis is the same as t PLZ and t PHZ .[4]t t is the same as t THL and t TLH .[5]C PD is used to determine the dynamic power dissipation (P D in μW).P D =C PD ×V CC 2×f i ×N +∑(C L ×V CC 2×f o ) where:f i =input frequency in MHz;f o =output frequency in MHz;C L =output load capacitance in pF;V CC =supply voltage in V;N =number of inputs switching;∑(C L ×V CC 2×f o )=sum of outputs.t hhold timeDn to LE; see Figure 11V CC = 2.0 V 5--ns V CC = 4.5 V 5--ns V CC = 6.0 V5--nsTable 8.Dynamic characteristics 74HC373 …continuedVoltages are referenced to GND (ground =0V); C L = 50 pF unless otherwise specified; for test circuit see Figure 12.Symbol Parameter ConditionsMin Typ Max Unit Table 9.Dynamic characteristics 74HCT373Voltages are referenced to GND (ground =0V); C L = 50 pF unless otherwise specified; for test circuit see Figure 12.Symbol Parameter Conditions Min Typ Max UnitT amb =25°C t pdpropagation delayDn to Qn; see Figure 8[1]V CC = 4.5 V-1730ns V CC =5V; C L =15pF -14-ns LE to Qn; see Figure 9V CC = 4.5 V-1632ns V CC =5V; C L =15pF-13-ns t en enable time OE to Qn; see Figure 10[2]V CC = 4.5 V-1932ns t dis disable time OE to Qn; see Figure 10[3]V CC = 4.5 V-1830ns t t transition time Qn; see Figure 8 and Figure 9[4]V CC = 4.5 V -512ns t W pulse width LE HIGH; see Figure 9V CC = 4.5 V164-ns t su set-up time Dn to LE; see Figure 11V CC = 4.5 V126-ns t h hold timeDn to LE; see Figure 11V CC = 4.5 V4−1-ns C PDpower dissipation capacitanceper latch;V I =GND to (V CC −1.5V)[5]-41-pFTable 9.Dynamic characteristics 74HCT373 …continuedVoltages are referenced to GND(ground =0V); C L = 50 pF unless otherwise specified; for test circuit see Figure12. Symbol Parameter Conditions Min Typ Max Unit T amb=−40°C to+85°Ct pd propagation delay Dn to Qn; see Figure8[1]V CC = 4.5 V--38nsLE to Qn; see Figure9V CC = 4.5 V--40ns t en enable time OE to Qn; see Figure10[2]V CC = 4.5 V--40ns t dis disable time OE to Qn; see Figure10[3]V CC = 4.5 V--38ns t t transition time Qn; see Figure8 and Figure9[4]V CC = 4.5 V--15ns t W pulse width LE HIGH; see Figure9V CC = 4.5 V20--ns t su set-up time Dn to LE; see Figure11V CC = 4.5 V15--ns t h hold time Dn to LE; see Figure11V CC = 4.5 V4--ns T amb=−40°C to+125°Ct pd propagation delay Dn to Qn; see Figure8[1]V CC = 4.5 V--45nsLE to Qn; see Figure9V CC = 4.5 V--48ns t en enable time OE to Qn; see Figure10[2]V CC = 4.5 V--48ns t dis disable time OE to Qn; see Figure10[3]V CC = 4.5 V--45ns t t transition time Qn; see Figure8 and Figure9[4]V CC = 4.5 V--18ns t W pulse width LE HIGH; see Figure9V CC = 4.5 V24--ns t su set-up time Dn to LE Dn to LE; see Figure11V CC = 4.5 V18--nsTable 9.Dynamic characteristics 74HCT373 …continuedVoltages are referenced to GND(ground =0V); C L = 50 pF unless otherwise specified; for test circuit see Figure12. Symbol Parameter Conditions Min Typ Max Unit t h hold time Dn to LE Dn to LE; see Figure11V CC = 4.5 V4--ns[1]t pd is the same as t PLH and t PHL.[2]t en is the same as t PZH and t PZL.[3]t dis is the same as t PLZ and t PHZ.[4]t t is the same as t THL and t TLH.[5]C PD is used to determine the dynamic power dissipation (P D in μW).P D=C PD×V CC2×f i×N+∑(C L×V CC2×f o) where:f i=input frequency in MHz;f o=output frequency in MHz;C L=output load capacitance in pF;V CC=supply voltage in V;N=number of inputs switching;∑(C L×V CC2×f o)=sum of outputs.11. WaveformsTable 10.Measurement pointsType Input OutputV M V M74HC3730.5V CC0.5V CC 74HCT373 1.3V 1.3VTable 11.Test dataType Input Load S1 positionV I t r, t f C L R L t PHL, t PLH t PZH, t PHZ t PZL, t PLZ 74HC373V CC6ns15pF, 50 pF1kΩopen GND V CC74HCT3733V6ns15pF, 50 pF1kΩopen GND V CC12. Package outlineDIP20: plastic dual in-line package; 20 leads (300 mil)SOT146-1Fig 13.Package outline SOT146-1 (DIP20)SO20: plastic small outline package; 20 leads; body width 7.5 mm SOT163-1Fig 14.Package outline SOT163-1 (SO20)SSOP20: plastic shrink small outline package; 20 leads; body width 5.3 mm SOT339-1Fig 15.Package outline SOT339-1 (SSOP20)TSSOP20: plastic thin shrink small outline package; 20 leads; body width 4.4 mm SOT360-1Fig 16.Package outline SOT360-1 (TSSOP20)Fig 17.Package outline SOT764-1 (DHVQFN20)SOT764-1DHVQFN20: plastic dual in-line compatible thermal enhanced very thin quad flat package; no leads;20 terminals; body 2.5 x 4.5 x 0.85 mm13. Abbreviations14. Revision historyTable 12.AbbreviationsAcronym DescriptionCMOS Complementary Metal Oxide Semiconductor ESD ElectroStatic Discharge HBM Human Body Model MM Machine ModelTTLTransistor-Transistor LogicTable 13.Revision historyDocument ID Release date Data sheet status Change notice Supersedes 74HC_HCT373 v.420100903Product data sheet-74HC_HCT373 v.3Modifications:•The format of this data sheet has been redesigned to comply with the new identity guidelines of NXP Semiconductors.•Legal texts have been adapted to the new company name where appropriate.•Figure 5 changed: inversion sign added to the output buffers.74HC_HCT373 v.320060120Product data sheet -74HC_HCT373_CNV v.274HC_HCT373_CNV v.219970827Product specification--15. Legal information15.1 Data sheet status[1]Please consult the most recently issued document before initiating or completing a design.[2]The term ‘short data sheet’ is explained in section “Definitions”.[3]The product status of device(s) described in this document may have changed since this document was published and may differ in case of multiple devices. The latest product statusinformation is available on the Internet at URL .15.2 DefinitionsDraft — The document is a draft version only. The content is still under internal review and subject to formal approval, which may result in modifications or additions. NXP Semiconductors does not give any representations or warranties as to the accuracy or completeness of information included herein and shall have no liability for the consequences of use of such information.Short data sheet — A short data sheet is an extract from a full data sheet with the same product type number(s) and title. A short data sheet is intended for quick reference only and should not be relied upon to contain detailed and full information. For detailed and full information see the relevant full data sheet, which is available on request via the local NXP Semiconductors sales office. In case of any inconsistency or conflict with the short data sheet, the full data sheet shall prevail.Product specification — The information and data provided in a Product data sheet shall define the specification of the product as agreed between NXP Semiconductors and its customer, unless NXP Semiconductors and customer have explicitly agreed otherwise in writing. In no event however, shall an agreement be valid in which the NXP Semiconductors product is deemed to offer functions and qualities beyond those described in the Product data sheet.15.3 DisclaimersLimited warranty and liability — Information in this document is believed to be accurate and reliable. However, NXP Semiconductors does not give any representations or warranties, expressed or implied, as to the accuracy or completeness of such information and shall have no liability for the consequences of use of such information.In no event shall NXP Semiconductors be liable for any indirect, incidental, punitive, special or consequential damages (including - without limitation - lost profits, lost savings, business interruption, costs related to the removal or replacement of any products or rework charges) whether or not such damages are based on tort (including negligence), warranty, breach of contract or any other legal theory.Notwithstanding any damages that customer might incur for any reason whatsoever, NXP Semiconductors’ aggregate and cumulative liability towards customer for the products described herein shall be limited in accordance with the Terms and conditions of commercial sale of NXP Semiconductors.Right to make changes — NXP Semiconductors reserves the right to make changes to information published in this document, including without limitation specifications and product descriptions, at any time and without notice. This document supersedes and replaces all information supplied prior to the publication hereof.Suitability for use in automotive applications — This NXP Semiconductors product has been qualified for use in automotive applications. The product is not designed, authorized or warranted to be suitable for use in medical, military, aircraft, space or life support equipment, nor in applications where failure or malfunction of an NXP Semiconductors product can reasonably be expected to result in personal injury, death or severe property or environmental damage. NXP Semiconductors accepts no liability for inclusion and/or use of NXP Semiconductors products in such equipment or applications and therefore such inclusion and/or use is at the customer’s own risk.Applications — Applications that are described herein for any of these products are for illustrative purposes only. NXP Semiconductors makes no representation or warranty that such applications will be suitable for the specified use without further testing or modification.Customers are responsible for the design and operation of their applications and products using NXP Semiconductors products, and NXP Semiconductors accepts no liability for any assistance with applications or customer product design. It is customer’s sole responsibility to determine whether the NXP Semiconductors product is suitable and fit for the customer’s applications and products planned, as well as for the planned application and use of customer’s third party customer(s). Customers should provide appropriate design and operating safeguards to minimize the risks associated with their applications and products.NXP Semiconductors does not accept any liability related to any default, damage, costs or problem which is based on any weakness or default in the customer’s applications or products, or the application or use by customer’s third party customer(s). Customer is responsible for doing all necessary testing for the customer’s applications and products using NXP Semiconductors products in order to avoid a default of the applications and the products or of the application or use by customer’s third partycustomer(s). NXP does not accept any liability in this respect.Limiting values — Stress above one or more limiting values (as defined in the Absolute Maximum Ratings System of IEC60134) will cause permanent damage to the device. Limiting values are stress ratings only and (proper) operation of the device at these or any other conditions above those given in the Recommended operating conditions section (if present) or the Characteristics sections of this document is not warranted. Constant or repeated exposure to limiting values will permanently and irreversibly affect the quality and reliability of the device.Terms and conditions of commercial sale — NXP Semiconductors products are sold subject to the general terms and conditions of commercial sale, as published at /profile/terms, unless otherwise agreed in a valid written individual agreement. In case an individual agreement is concluded only the terms and conditions of the respective agreement shall apply. NXP Semiconductors hereby expressly objects to applying the customer’s general terms and conditions with regard to the purchase of NXP Semiconductors products by customer.No offer to sell or license — Nothing in this document may be interpreted or construed as an offer to sell products that is open for acceptance or the grant, conveyance or implication of any license under any copyrights, patents or other industrial or intellectual property rights.Document status[1][2]Product status[3]DefinitionObjective [short] data sheet Development This document contains data from the objective specification for product development. Preliminary [short] data sheet Qualification This document contains data from the preliminary specification.Product [short] data sheet Production This document contains the product specification.Export control — This document as well as the item(s) described herein may be subject to export control regulations. Export might require a prior authorization from national authorities.15.4 TrademarksNotice: All referenced brands, product names, service names and trademarks are the property of their respective owners.16. Contact informationFor more information, please visit: For sales office addresses, please send an email to: salesaddresses@。

74hc373锁存器作用

74HC373锁存器作用什么是74HC373锁存器?74HC373是一种集成电路芯片,属于高速CMOS逻辑系列,由意法半导体公司生产。

它是一种8位锁存器,可用于在数字电路中存储8位数据。

锁存器是数电中常见的一个功能模块,用于存储和保持信号。

74HC373锁存器的作用74HC373锁存器在数字电路中起到重要的作用,以下是几个典型的应用场景:1. 数据缓存在某些情况下,需要将某个电平的信号保持一段时间,并在需要时输出。

74HC373锁存器可以用作数据缓存,将输入信号锁存,并在需要时输出。

这在通信系统、计算机存储和控制电路中经常使用。

通过将数据输入到锁存器中,可以防止数据丢失,确保在更合适的时机进行处理。

2. 数据传输74HC373锁存器通常被用作数据传输的工具。

当需要将数据从一个电路传输到另一个电路时,可以使用锁存器来暂存待传输的数据。

通过将数据输入到锁存器中,并在需要传输时将数据输出,可以确保数据传输的可靠性和稳定性。

3. 地址寄存器在微处理器系统中,锁存器经常被用作地址寄存器。

地址寄存器用于存储指令的地址,以便微处理器能够从存储器中读取指令。

通过使用74HC373锁存器作为地址寄存器,可以实现高效的地址存储和解码。

4. 控制信号在数字电路中,锁存器也可以用于存储和控制信号的生成。

通过将控制信号输入到锁存器中,并根据需要输出,可以实现复杂的控制逻辑。

锁存器可以存储不同的控制状态,并在需要时将相应的控制信号输出到其他电路中,从而实现对数字系统的控制。

5. 边沿检测锁存器还可以用于边沿检测。

在数字信号处理中,有时需要检测信号的上升沿或下降沿。

通过将信号输入到锁存器中,并与之前的状态进行比较,可以检测到信号的边沿。

这对于时序控制和触发器电路非常有用。

总结74HC373锁存器是一种常见的集成电路芯片,用于存储和保持信号。

它的作用多种多样,可以用于数据缓存、数据传输、地址寄存器、控制信号和边沿检测等场景。

锁存器在数字电路中起到重要的作用,对于数字系统的设计和控制至关重要。

74hc373中文资料

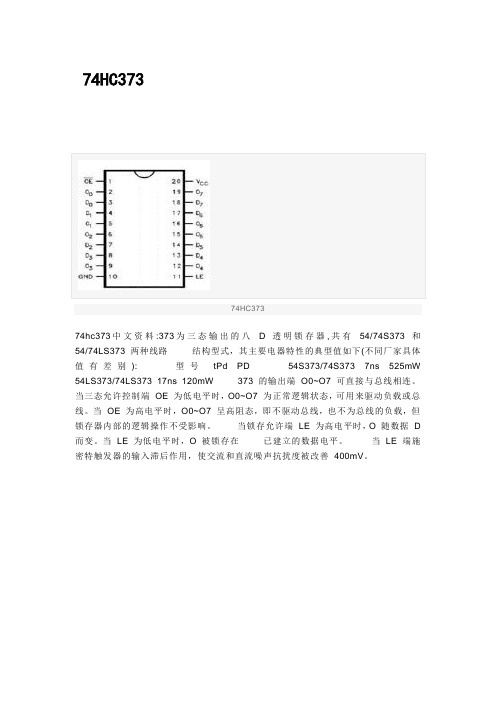

54/74373八D锁存器(3S,锁存允许输入有回环特性)简要说明:373为三态输出的八D透明锁存器,共有54/74S373和54/74LS373两种线路结构型式,其主要电器特性的典型值如下(不同厂家具体值有差别):型号t Pd P D54S373/74S373 7ns 525mW54LS373/74LS373 17ns 120mW373的输出端O0~O7可直接与总线相连。

当三态允许控制端OE为低电平时,O0~O7为正常逻辑状态,可用来驱动负载或总线。

当OE为高电平时,O0~O7呈高阻态,即不驱动总线,也不为总线的负载,但锁存器内部的逻辑操作不受影响。

当锁存允许端LE为高电平时,O随数据D而变。

当LE为低电平时,O被锁存在已建立的数据电平。

当LE端施密特触发器的输入滞后作用,使交流和直流噪声抗扰度被改善400mV。

引出端符号:D0~D7 数据输入端OE 三态允许控制端(低电平有效)LE 锁存允许端O0~O7 输出端外部管腿图:逻辑图:真值表:极限值:电源电压 (7V)输入电压54/74S373…………………………….………….5.5V54/74LS373…………………………………….7V输出高阻态时高电平电压 …………………………. 5.5V工作环境温度54XXX ………………………………….-55~125℃ 74XXX ………………………………….0~70℃存储温度 …………………………………………. -65~150℃推荐工作条件:54/74S373 54LS373/74LS373最小额定最大最小额定最大单位54 4.5 5 5.5 4.5 5 5.5电源电压Vcc74 4.75 5 5.25 4.75 5 5.25V 输入高电平电压V iH 2 2 V54 0.8 0.7输入低电平电压V iL74 0.8 0.8V54 -2 -1输出高电平电流I OH74 -6.5 -2.6mA54 20 12 输出低电平电流I OL74 20 24 mAwww.elecfans.comLE(H) 6 15脉冲宽度t w LE(L) 7.3 15 ns保持时间t H D 10↓ 10↓ ns 建立时间t set D 0↓0↓ns静态特性(TA 为工作环境温度范围) S373 LS373参 数测 试 条 件【1】最小 最大 最小 最大 单位V IK 输入嵌位电压 Vcc=最小,I ik =-18mA-1.5-1.5 VV OH 输出高电平电压Vcc =最小,V IL =最大,V IH =2V ,I OH =最大2.4 2.4 V54 0.5 0.4 V OL 输出低电平电压Vcc=最小,V IL =最大,V IH =2V,I OL =最大74 0.5 0.5 V V I =5.5V 1 I I 最大输入电压时输入电流Vcc =最大V I =7V 0.1 mA V IL =0.5V -0.25I IL 输入低电平电流 Vcc =最大,V IL =0.4V -0.4mA I IH 输入高电平电流 Vcc =最大,V IH =2.7V50 20 uA I OS 输出短路电流 Vcc =最大-40 -100 -30 -130 mA Icc 电源电流 Vcc =最大,OE 接4.5V160 40 mA V 0=2.4V 50 I OZH 输出高阻态时高电平电流 Vcc =最大,V IH =2VV 0=2.7V 20 mA V 0=0.5V-50 I OZL 输出高阻态时低电平电流Vcc =最大,V IH =2VV 0=0.4V-20 mA[1]: 测试条件中的“最小”和“最大”用推荐工作条件中的相应值。

74ls373中文资料

PD

m

54S373/74S373

7ns

54LS373/74LS373

17ns

525mW 120mW

r

a 373 的输出端 O0~O7 可直接与总线相连。

当三态允许控制端 OE 为低电平时,O0~O7 为正常逻辑状态,可用来驱动负载或总

- 线。当 OE 为高电平时,O0~O7 呈高阻态,即不驱动总线,也不为总线的负载,但

单位

VIK输入嵌位电压

VOH输出高电平电压

VOL输出低电平电压 II最大输入电压时输入

电流 IIL输入低电平电流 IIH输入高电平电流

Vcc=最小,Iik=-18mA

Vcc=最小,VIL=最大, VIH=2V,IOH=最大

Vcc=最小,VIL=最大, 54

VIH=2V,IOL=最大

74

Vcc=最大

VI=5.5V VI=7V

54LS373/74LS373 最小 额定 最大

单位

电源电压 Vcc

54 4.5

5

74 4.75

5

输入高电平电压ViH

2

输入低电平电压ViL

54 74

5.5

4.5

5

5.5

5.25 4.75

5

5.25

V

2

V

0.8 0.8

0.7 0.8

V

输出高电平电流IOH

54 74

-2

-1

mA

-6.5

-2.6

输出低电平电流IOL

. 输出高阻态时高电平电压 ………………………….

工作环境温度

w 54XXX

………………………………….

74XXX

………………………………….

74系列芯片简介3——中英文名称对照

74HC191 DECADE UP/DN COUNTER 十进制加减计数

74HC192 DECADE UP/DN COUNTER 十进制加减计数器

74HC193 BINARY UP/DN COUNTER 二进制加减计数

74HC4020 14-Stage Binary Counter 14输出计数器

74HC4017 Decade Counter/Divider with 10 Decoded Outputs 十进制计数器带10个译码输出端

74HC4040 12 Stage Binary Counter 12出计数器

74HC237 3-8 LINE DECODER 地址锁3线至8线译码器

74HC242/243 TRI-STAT TRANSCEIVER 三态收发器

44 OCTAL 3-STATE BUFFER 八个三态缓冲门

74HC245 OCTAL 3-STATE TRANSCEIVER 三态收发器

74HC113 DUAL J-K FLIP-FLOP PRESET 双JK触发器

74HC123A RETRIGGERABLE MONOSTAB 可重触发单稳

74HC125 TRI-STATE QUAD BUFFERS 四个三态门

74HC126 TRI-STATE QUAD BUFFERS 六三态门

74HC149 8-8 LINE PRIORITY ENCODER 编码器

74HC151 8-CHANNEL DIGITAL MUX 8通道多路器

74HC153 DUAL 4-INPUT MUX 双四输入多路器

74VHC373资料

74VHC373OCTAL D-TYPE LATCHWITH 3STATE OUTPUT NON INVERTINGJune 1999s HIGH SPEED:t PD =5.0ns (TYP.)at V CC =5V sLOW POWER DISSIPATION:I CC =4µA (MAX.)at T A =25o C sHIGH NOISE IMMUNITY:V NIH =V NIL =28%V CC (MIN.)s POWER DOWN PROTECTION ON INPUTS sSYMMETRICAL OUTPUT IMPEDANCE:|I OH |=I OL =8mA (MIN)sBALANCED PROPAGATION DELAYS:t PLH ≅t PHLsOPERATING VOLTAGERANGE:V CC (OPR)=2V to 5.5VsPIN AND FUNCTION COMPATIBLE WITH 74SERIES 373s IMPROVED LATCH-UP IMMUNITY sLOW NOISE:V OLP =0.9V(Max.)DESCRIPTIONThe 74VHC373is an advanced high-speed CMOS OCTAL D-TYPE LATCH with 3STATE OUTPUT NON INVERTING fabricated with sub-micron silicon gate and double-layer metal wiring C 2MOS technology.This 8bit D-Type latch is controlled by a latch enable input (LE)and an output enable input (OE).While the LE input is held at a high level,the Qoutputs will follow the data inputs precisely.When the LE is taken low,the Q outputs will be latched precisely at the logic level of D input data.While the (OE)input is low,the 8outputs will be in a normal logic state (high or low logic level)and while high level the outputs will be in a high impedance state.Power down protection is provided on all inputs and 0to 7V can be accepted on inputs with no regard to the supply voltage.This device can be used to interface 5V to 3V.All inputs and outputs are equipped with protection circuits against static discharge,giving them 2KV ESD immunity and transient excess voltage.PIN CONNECTION AND IEC LOGIC SYMBOLSORDER CODES :74VHC373M 74VHC373TM(Micro Package)T(TSSOP Package)®1/1074VHC373INPUT EQUIVALENT CIRCUIT PIN DESCRIPTIONPIN No SYMBOL NAME AND FUNCTION1OE3State Output EnableInput(Active LOW)D0to D7Data Inputs2,5,6,9,12,15,16,19Q0to Q73State Outputs3,4,7,8,13,14,17,1811LE Latch EnableInput10GND Ground(0V)20V CC Positive Supply Voltage TRUTH TABLEINPUTS OUTPUTS OE LE D QH X X ZL L X NO CHANGE*L H L LL H H HX:DON’T CAREZ:HIGHIMPEDANCE*:Q OUTPUTSARELATCHEDAT THE TIMEWHENTHE LEINPUT ISTAKENLOWLOGIC LEVEL.LOGIC DIAGRAM2/10ABSOLUTE MAXIMUM RATINGSSymbol ParameterValue Unit V CC Supply Voltage -0.5to +7.0V V I DC Input Voltage -0.5to +7.0V V O DC Output Voltage -0.5to V CC +0.5V I IK DC Input Diode Current -20mA I OK DC Output Diode Current ±20mA I O DC Output Current ±25mA I CC or I GND DC V CC or Ground Current±75mAT stg Storage Temperature -65to +150o C T LLead Temperature (10sec)300oCAbsolute Maximum Ratingsarethose values beyond which dam age to the device may occur.Functional operation un der these condition is not implied.RECOMMENDED OPERATING CONDITIONSSymbol ParameterValue Unit V CC Supply Voltage 2.0to 5.5V V I Input Voltage 0to 5.5V V O Output Voltage 0to V CC VT op Operating Temperature-40to +85oCdt/dvInput Rise and Fall Time (see note 1)(V CC =3.3±0.3V)(V CC =5.0±0.5V)0to 1000to 20ns/V ns/V1)V IN from 30%to70%of V CCDC SPECIFICATIONSSymbolParameterTest Conditions ValueUnitV CC (V)T A =25oC -40to 85oC Min.Typ.Max.Min.Max.V IH High Level Input Voltage 2.0 1.5 1.5V 3.0to 5.50.7V CC0.7V CCV IL Low Level Input Voltage2.00.50.5V3.0to 5.50.3V CC0.3V CC V OHHigh Level Output Voltage2.0I O =-50µA 1.9 2.0 1.9V3.0I O =-50µA 2.9 3.0 2.94.5I O =-50µA 4.4 4.54.43.0I O =-4mA 2.58 2.484.5I O =-8mA 3.943.8V OLLow Level Output Voltage2.0I O =50µA 0.00.10.1V3.0I O =50µA 0.00.10.14.5I O =50µA 0.00.10.13.0I O =4mA 0.360.444.5I O =8mA 0.360.44I OZHigh Impedance Output Leakage Current5.5V I =V IH or V IL V O =V CC or GND ±0.25±2.5µAI I Input Leakage Current 0to 5.5V I =5.5V or GND ±0.1±1.0µA I CCQuiescent Supply Current5.5V I =V CC or GND440µA74VHC3733/10CAPACITIVE CHARACTERISTICSSymbolParameterTest ConditionsValueUnitT A =25oC -40to 85oC Min.Typ.Max.Min.Max.C IN Input Capacitance 41010pF C OUT Output Capacitance 6pF C PDPower Dissipation Capacitance (note 1)27pF1)C PD isdefined as the value of the IC’sinternal equiva lent capacitance which is calculated fromthe operating current consumption without load.(Referto Test Circuit).Average operating current can be obtained bythe following equation.I CC (opr)=C PD •V CC •f IN +I CC /8(per Latch)AC ELECTRICAL CHARACTERISTICS (Input t r =t f =3ns)SymbolParameterTest Condition ValueUnitV CC (V)C L (pF)T A =25oC-40to 85oCMin.Typ.Max.Min.Max.t PLH t PHLPropagation Delay Time LE to Q3.3(*)157.011.01.013.0ns3.3(*)509.514.5 1.016.55.0(**)15 4.97.2 1.08.55.0(**)50 6.49.2 1.010.5t PLH t PHLPropagation Delay Time D to Q3.3(*)157.311.4 1.013.5ns3.3(*)509.814.9 1.017.05.0(**)15 5.07.2 1.08.55.0(**)506.59.2 1.010.5t PZL t PZHOutput EnableTime3.3(*)15R L =1K Ω7.311.4 1.013.5ns 3.3(*)50R L =1K Ω9.814.9 1.017.05.0(**)15R L =1K Ω 5.58.1 1.09.55.0(**)50R L =1K Ω7.010.1 1.011.5t PLZ t PHZ Output Disable Time 3.3(*)50R L=1K Ω9.513.2 1.015.0ns 5.0(**)50R L =1K Ω6.59.2 1.010.5t w Pulse Width (LE)HIGH3.3(*) 5.0 5.0ns 5.0(**)5.0 5.0t s Setup Time D to LE HIGH or LOW 3.3(*) 4.0 4.0ns 5.0(**) 4.0 4.0t h Hold Time D toLE HIGH or LOW3.3(*)1.0 1.0ns 5.0(**) 1.01.0t OSLH t OSHLOutput to Output Skew Time (note 1)3.3(*)50 1.5 1.5ns5.0(**)501.01.0(*)Voltag e range is 3.3V ±0.3V (**)Voltage range is 5V ±0.5VNote 1:Parameter guaranteed bydesign.t soLH =|t pLHm -t pLHn |,t soHL =|t pHLm -t pHLn |74VHC3734/10DYNAMIC SWITCHING CHARACTERISTICSSymbol Parameter Test Conditions Value UnitV CC (V)T A=25o C-40to85o C Min.Typ.Max.Min.Max.V OLP Dynamic Low VoltageQuiet Output(note1,2)5.0C L=50pF 0.60.9VV OLV-0.9-0.6V IHD Dynamic High VoltageInput(note1,3)5.0 3.5V ILD Dynamic Low VoltageInput(note1,3)5.0 1.51)Worst case package.2)Max num ber of outputs defined as(n).Data inputs aredriven0V to5.0V,(n-1)outputs switching and one out put at GND.3)Max num ber of data inputs(n)switching.(n-1)switching0V to5.0V.Inputs under test switching:5.0V to threshold(V ILD),0V to threshold(V IHD),f=1MHz. TEST CIRCUITTEST SWITCHt PLH,t PHL Opent PZL,t PLZ V CCt PZH,t PHZ GNDC L=15/50pF or equ ivalent(includes jigand probe capacitance)R L=R1=1KΩorequivalentR T=Z OU T of pulse generator(typ ically50Ω)74VHC3735/1074VHC373WAVEFORM1:LE TO Qn PROPAGATION DELAYS,LE MINIMUM PULSE WIDTH, Dn TO LE SETUP AND HOLD TIMES(f=1MHz;50%duty cycle)6/1074VHC373 WAVEFORM2:OUTPUT ENABLE AND DISABLE TIMES(f=1MHz;50%duty cycle)WAVEFORM3:PROPAGATION DELAY TIME(f=1MHz;50%duty cycle)7/10DIM.mm inch MIN.TYP.MAX.MIN.TYP.MAX.A 2.650.104a10.100.200.0040.007a2 2.450.096b 0.350.490.0130.019b10.230.320.0090.012C 0.500.020c145(typ.)D 12.6013.000.4960.512E 10.0010.650.3930.419e 1.270.050e311.430.450F 7.407.600.2910.299L 0.50 1.270.190.050M 0.750.029S8(max.)P013LSO-20MECHANICAL DATA74VHC3738/10DIM.mminch MIN.TYP.MAX.MIN.TYP.MAX.A 1.10.433A10.050.100.150.0020.0040.006A20.850.90.950.3350.3540.374b 0.190.300.00750.0118c 0.090.20.00350.0079D 6.4 6.5 6.60.2520.2560.260E 6.25 6.4 6.50.2460.2520.256E1 4.34.4 4.480.1690.1730.176e 0.65BSC0.0256BSCK 0o 4o 8o 0o 4o 8o L0.500.600.700.0200.0240.028cEbA2AE1D1PIN 1IDENTIFICATIONA1LK eTSSOP20MECHANICAL DATA74VHC3739/1074VHC373Information furnished is believed to be accurate and reliable.However,STMicroelectronics assumes no responsibility for the consequence s of use of such information nor for any infringement of patents or other rights of third parties which may result from its use.No license is granted by implication or otherwise under any patent or patent rights of STMicroelectronics.Specification mentioned in this publication are subject to change without notice.This publication supersedes and replaces all information previously supplied.STMicroelectronics products are not authorized for use as critical components in life support devices or systems without express written approval of STMicroelectronics.The ST logo is a trademark of STMicroelectronics©1999STMicroelectronics–Printed in Italy–All Rights ReservedSTMicroelectronics GROUP OF COMPANIESAustralia-Brazil-Canada-China-France-Germany-Italy-Japan-Korea-Malaysia-Malta-Mexico-Morocco-The Netherlands-Singapore-Spain-Sweden-Switzerland-Taiwan-Thailand-United Kingdom-U.S.A..10/10。

74ls373中文资料

LS373 最小 最大

单位

VIK输入嵌位电压

Vcc=最小,Iik=-18mA

-1.5

-1.5 V

VOH输出高电平电压

Vcc=最小,VIL=最大, VIH=2V,IOH=最大

2.4

2.4

V

VOL输出低电平电压

Vcc=最小,VIL=最大, VIH=2V,IOL=最大

54 74

0.5 0.5

0.4 0.5

OE 到 O0~O7

(LS373 为 667 Ω)

45pF)

15

28

ns

18

36

tPHZ

OE 到

tPLZ

O0~O7

9

20

CL=5pF

12

ns 25

[2] tPLH输出由低到高传输延迟时间 tPHL输出由高到低传输延迟时间

17ic电子渠道网可为您提供免费的中文资料、电路图 等资料并可提供在线采购电子元器件等

本站最新动态

·3.1号起本站将实行新的会员收费标准 ·会员管理中心推出重复库存清除功能 ·教您如何选择一个好的IC交易平台! ·你的论坛你做主,赶快来体验吧 ·好消息:本站所有广告按点击次数…

MCP1316中文资料MCP1317应用MCP1318 MCP1319封装 图MCP1320管脚

·MCP111 中文资料 MCP112 应用 pdf … ·MCP102中文资料MCP103应用MCP1… ·MCP41010 中文资料 MCP41050 应用… ·MCP40D17中文资料 MCP40D18应用… ·DS12R885 中文资料 DS12CR887 应… ·MAX6972ATJ 中文资料 MAX6973AT… ·MCP14E3中文资料MCP14E4 应用 pd… ·MCP6V06中文资料 MCP6V07应用 p… ·MCP6V01中文资料MCP6V02应用 pd… ·MCP6S91中文资料 MCP6S92应用 pd…

74LS373的资料

74LS373中文资料

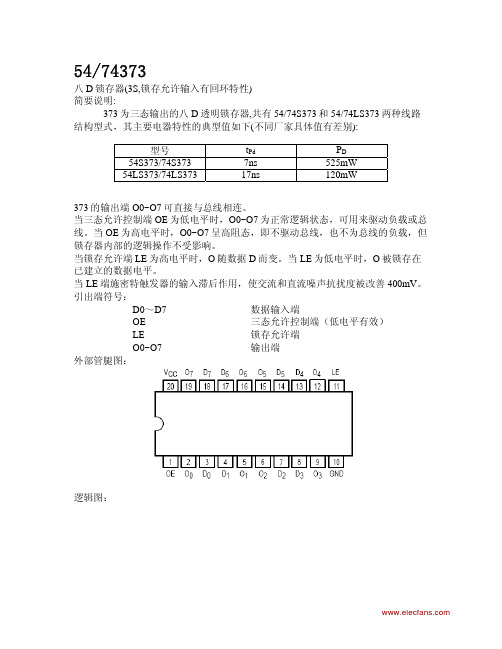

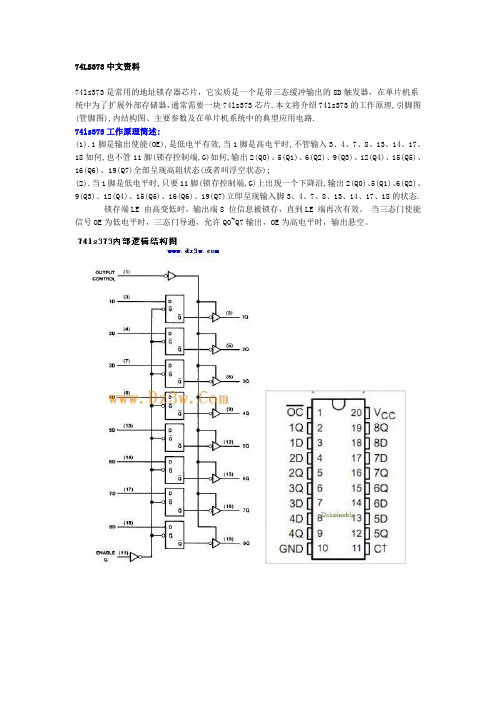

74ls373是常用的地址锁存器芯片,它实质是一个是带三态缓冲输出的8D触发器,在单片机系统中为了扩展外部存储器,通常需要一块74ls373芯片.本文将介绍74ls373的工作原理,引脚图(管脚图),内结构图、主要参数及在单片机系统中的典型应用电路.

74ls373工作原理简述:

(1).1脚是输出使能(OE),是低电平有效,当1脚是高电平时,不管输入3、4、7、8、13、14、17、18如何,也不管11脚(锁存控制端,G)如何,输出2(Q0)、5(Q1)、6(Q2)、9(Q3)、12(Q4)、15(Q5)、16(Q6)、19(Q7)全部呈现高阻状态(或者叫浮空状态);

(2).当1脚是低电平时,只要11脚(锁存控制端,G)上出现一个下降沿,输出2(Q0)、5(Q1)、6(Q2)、9(Q3)、12(Q4)、15(Q5)、16(Q6)、19(Q7)立即呈现输入脚3、4、7、8、13、14、17、18的状态.

锁存端LE 由高变低时,输出端8 位信息被锁存,直到LE 端再次有效。

当三态门使能信号OE为低电平时,三态门导通,允许Q0~Q7输出,OE为高电平时,输出悬空。

L——低电平;

H——高电平;

X——不定态;

Q0——建立稳态前Q的电平;

G——输入端,与8031ALE连高电平:畅通无阻低电平:关门锁存。

图中OE——使能端,接地。

当G=“1”时,74LS373输出端1Q—8Q与输入端1D—8D相同;

当G为下降沿时,将输入数据锁存。

74HCT373

1.一般说明:74HC373 ,74HCT373是一个高速Si -gate CMOS设备和引脚兼容与低功率肖特基TTL 。

它是符合JEDEC标准没有规定。

7A。

74HC373 74HCT373是一个八进制D型透明锁存设有独立的D型输入每个锁存和三态输出总线导向的应用。

锁存使能(LE )输入和输出使能(OE)输入共同所有插销。

74HC373 74HCT373由8个D型透明锁存器三态真输出。

LE为高电平时,数据在DN输入进入闩锁。

在此条件下锁存器是透明的,即一个锁存输出状态会改变其对应的每次D输入的变化。

当LE是低锁存器存储的信息,是目前在D输入一个建立时间前HIGH - to-LOW过渡LE 。

当OEIS低的内容的8个锁存器提供输出。

当OEIS高,输出到高高阻关断状态。

的OEinput操作不影响锁存器的状态。

74HC373 ,74HCT373是功能上等同于:•74HC563 ;的74HCT563 :但反向输出和不同的引脚排列•74HC573 ;的74HCT573 :但不同的引脚排列2.特点和优点:三态非反相输出总线导向的应用常见的3态输出使能输入功能相同的74HC563;74HCT563和74HC573;74HCT573ESD保护:HBM JESD22-A114F超过2000 VMM JESD22-A115-A超过200 V40CTO+85C40CTO+125 C3.功能图图1 功能图图2 逻辑符号图3 逻辑图4.管脚信息引脚配置DIP20,SO20,SSOP20和TSSOP20表2中。

引脚说明符号引脚说明OE 1 3态输出使能输入(低电平有效)Q0,Q1,Q2,Q3,Q4,Q5,Q6,5,6,9,12,15,16,三态锁存输出5.功能描述5.1功能表表3中。

功能表[1] H=高电平;H =高电压等级的设置时间之前HIGH-LOW LE过渡;L =低电压水平;I =低电平一建立时间之前HIGH-LOW LE过渡;X =不关心;Z =高阻关断状态。

74ls373引脚图

74ls373引脚图,内部结构,参数,应用电路(74ls373中文资料)74ls373功能简介:74ls373是常用的地址锁存器芯片,它实质是一个是带三态缓冲输出的8D触发器,在单片机系统中为了扩展外部存储器,通常需要一块74ls373芯片.本文将介绍74ls373的工作原理,引脚图(管脚图),内结构图、主要参数及在单片机系统中的典型应用电路.74ls373工作原理简述:74ls373内部逻辑结构图74LS373的真值表(功能表),表中:L——低电平;H——高电平;X——不定态;Q0——建立稳态前Q的电平;G——输入端,与8031ALE连高电平:畅通无阻低电平:关门锁存。

图中OE——使能端,接地。

当G=“1”时,74LS373输出端1Q—8Q与输入端1D—8D相同;E G 功能0 0 直通Qi = Di0 1 保持(Qi保持不变)1 X 输出高阻74ls373电气特性74ls373推荐工作条件74ls373在单片机系统中的应用电路图:当74LS373用作地址锁存器时,应使OE为低电平,此时锁存使能端C为高电平时,输出Q0~Q7 状态与输入端D1~D7状态相同;当C发生负的跳变时,输入端D0~D7 数据锁入Q0~Q7。

51单片机的ALE信号可以直接与74LS373的C连接。

在MCS-51单片机系统中,常采用74LS373作为地址锁存器使用,其连接方法如上图所示。

其中输入端1D~8D接至单片机的P0口,输出端提供的是低8位地址,G端接至单片机的地址锁存允许信号ALE。

输出允许端OE接地,表示输出三态门一直打开。

1D~8D为8个输入端。

1Q~8Q为8个输出端。

G是数据锁存控制端;当G=1时,锁存器输出端同输入端;当G由“1”变为“0”时,数据输入锁存器中。

OE为输出允许端;当OE=“0”时,三态门打开;当OE=“1”时,三态门关闭,输出呈高阻状态。

(1).1脚是输出使能(OE),是低电平有效,当1脚是高电平时,不管输入3、4、7、8、13、14、17、18如何,也不管11脚(锁存控制端,G)如何,输出2(Q0)、5(Q1)、6(Q2)、9(Q3)、12(Q4)、15(Q5)、16(Q6)、19(Q7)全部呈现高阻状态(或者叫浮空状态);(2).当1脚是低电平时,只要11脚(锁存控制端,G)上出现一个下降沿,输出2(Q0)、5(Q1)、6(Q2)、9(Q3)、12(Q4)、15(Q5)、16(Q6)、19(Q7)立即呈现输入脚3、4、7、8、13、14、17、18的状态.锁存端LE 由高变低时,输出端8 位信息被锁存,直到LE 端再次有效。

74HC373

74HC373简介74HC373 是一款高速 CMOS 8 位透明锁存器,适用于数据存储和数据传输应用。

它采用了 CMOS 技术,工作电源范围为2V 至 6V,具有低功耗特性。

74HC373 具有以下特性:•具有 8 位并行数据输入和 8 位并行数据输出端口•可对数据进行锁存,并且锁存的数据可以通过并行输出端口进行读取•提供了 OE (输出使能) 输入端口,可以用来控制并行输出的打开和关闭•具有 3-state 输出,可以通过输出使能端口控制输出的高阻态和有效态之间的切换•提供了 3V 至 6V 的输出电压范围引脚描述74HC373 的引脚描述如下:序号引脚名称描述1OE输出使能输入端口2LE锁存使能输入端口3D0数据输入端口 0 4D1数据输入端口 1 5D2数据输入端口 2 6D3数据输入端口 3 7D4数据输入端口 4 8D5数据输入端口 59D6数据输入端口 6 10D7数据输入端口 7 11GND地12Q0数据输出端口 0 13Q1数据输出端口 1 14Q2数据输出端口 2 15Q3数据输出端口 3 16Q4数据输出端口 4 17Q5数据输出端口 518Q6数据输出端口 619Q7数据输出端口 720VCC电源输入功能描述74HC373 作为一个透明锁存器,可以通过锁存使能输入端口(LE)来控制数据的锁存和透明传输。

当 LE 为高电平时,数据输入端口的数据将被锁存,锁存后的数据可以通过数据输出端口(Q)进行读取。

当 LE 为低电平时,数据输入端口的数据将直接透明传输到数据输出端口。

除了锁存使能输入端口,74HC373 还提供了输出使能输入端口(OE),用于控制输出的打开和关闭。

工作原理74HC373 的工作原理如下:1.当锁存使能输入端口(LE)为高电平时,数据输入端口(D0-D7)的数据将被锁存。

2.锁存的数据可以通过数据输出端口(Q0-Q7)进行读取。

3.当锁存使能输入端口(LE)为低电平时,数据输入端口的数据将直接透明传输到数据输出端口。

74hc373

74HC373

74HC373

74hc373中文资料:373为三态输出的八 D 透明锁存器,共有54/74S373 和54/74LS373 两种线路结构型式,其主要电器特性的典型值如下(不同厂家具体值有差别): 型号tPd PD 54S373/74S373 7ns 525mW 54LS373/74LS373 17ns 120mW 373 的输出端O0~O7 可直接与总线相连。

当三态允许控制端OE 为低电平时,O0~O7 为正常逻辑状态,可用来驱动负载或总线。

当OE 为高电平时,O0~O7 呈高阻态,即不驱动总线,也不为总线的负载,但锁存器内部的逻辑操作不受影响。

当锁存允许端LE 为高电平时,O 随数据 D 而变。

当LE 为低电平时,O 被锁存在已建立的数据电平。

当LE 端施密特触发器的输入滞后作用,使交流和直流噪声抗扰度被改善400mV。

74ls373中文资料

型号

tPd

54S373/74S373

7ns

54LS373/74LS373

17ns

PD 525mW 120mW

373 的输出端 O0~O7 可直接与总线相连。

当三态允许控制端 OE 为低电平时,O0~O7 为正常逻辑状态,可用来驱动负载或总

线。当 OE 为高电平时,O0~O7 呈高阻态,即不驱动总线,也不为总线的负载,但

ic中文-17IC中文资料网 - IC中文资料-IC渠道网 IC中文资料 - 电源 - 嵌入式 - 电路图 - 单片机 - 应用方案 - 技术文章

首 页 IC库存 电子资讯 技术资料

IC

非IC

求购信息

PDF 资料

IC库存搜索: 请输入IC型号

搜索

最新搜索: VN2406LZL1 MAX881REUB+T IC42S16400-6TG LTC2230IUP MSR320 HLMP-2700 GS-R405S EPF10K10LI84 …

IC中文资料

型号A开头

型号B 开头

型号C开头

·MCP1316中文资料MCP1317应用MCP1318 MCP1319封装图MC... ·MCP111 中文资料 MCP112 应用 pdf 封装图 管脚说明... ·MCP102中文资料MCP103应用MCP111 MCP121封装图MCP131... ·MCP41010 中文资料 MCP41050 应用 pdf MCP41100 封... ·MCP40D17中文资料 MCP40D18应用 pdf MCP40D19 封装图... ·DS12R885 中文资料 DS12CR887 应用 pdf DS12R887封... ·MAX6972ATJ 中文资料 MAX6973ATJ 应用 pdf 封装图 管脚... ·MCP14E3中文资料MCP14E4 应用 pdf 封装图 MCP14E5管脚说... ·MCP6V06中文资料 MCP6V07应用 pdf 封装图 MCP6V08管脚说... ·MCP6V01中文资料MCP6V02应用 pdf 封装图MCP6V03 管脚说明...

74hc373跟74ls373区别

74hc373跟74ls373区别

LS即(Low Speed),HC即(Highspeed CMOS)从名字上很简单理解,前者是低速芯片,后都是高速CMOS芯片,后者可以在更高的频率下工作,两者在功能上是一样的。

HC373是5V的,LS373可以做到3V和5V兼容,平常用时就那么点区分,也就是说你的单片机假如使用3.3V,那就用LS的,当然略微贵一点点了。

LS与HC的区分

1、LS是低功耗肖特基,HC是高速COMS。

LS的速度比HC略快。

HCT输入输出与LS兼容,但是功耗低;F是高速肖特基电路;

2、LS是TTL电平,HC是COMS电平

3、LS输入开路为高电平,HC输入不允许开路,hc 一般都要求有上下拉电阻来确定输入端无效时的电平。

LS 却没有这个要求

4、LS输出下拉强上拉弱,HC上拉下拉相同。

5、工作电压不同,LS只能用5V,而HC一般为2V到6V;

6、电平不同。

LS是TTL电平,其低电平和高电平分别为0.8和V2.4,而CMOS在工作电压为5V时分别为0.3V和3.6V,所以CMOS可以驱动TTL,但反过来是不行的

7、驱动力量不同,LS一般高电平的驱动力量为5mA,低电平为20mA;而CMOS的凹凸电平均为5mA;

8、CMOS器件抗静电力量差,易发生栓锁问题,所以CMOS的输入

脚不能直接接电源。

HD74HC373FPEL中文资料

HD74HC373, HD74HC533Octal D-type Transparent Latches (with 3-state outputs)Octal D-type Transparent Latches (with inverted 3-state outputs)REJ03D0619-0200(Previous ADE-205-498)Rev.2.00Mar 30, 2006 DescriptionWhen the latch enable input is high, the Q outputs of HD74HC373 will follow the D inputs and the Q outputs ofHD74HC533 will follow the inversion of the D inputs. When the latch enable goes low, data at the D inputs will be retained at the outputs until latch enable returns high again. When a high logic level is applied to the output control input, all outputs go to a high impedance state, regardless of what signals are present at the other inputs and the state of the storage elements.Features• High Speed Operation: t pd (D to Q) = 16 ns typ (C L = 50 pF)• High Output Current: Fanout of 15 LSTTL Loads• Wide Operating Voltage: V CC = 2 to 6 V• Low Input Current: 1 µA max• Low Quiescent Supply Current: I CC (static) = 4 µA max (Ta = 25°C)• Ordering InformationPart Name Package TypePackage Code(Previous Code)PackageAbbreviationTaping Abbreviation(Quantity)HD74HC373P HD74HC533P DILP-20 pinPRDP0020AC-B(DP-20NEV)P —HD74HC373FPEL HD74HC533FPEL SOP-20 pin (JEITA)PRSP0020DD-B(FP-20DAV)FP EL (2,000 pcs/reel)HD74HC533RPEL SOP-20 pin (JEDEC) PRSP0020DC-A(FP-20DBV)RP EL (1,000 pcs/reel)HD74HC373TELL TSSOP-20pin PTSP0020JB-A(TTP-20DAV)T ELL(2,000pcs/reel)Note: Please consult the sales office for the above package availability. Function TableOutput Control Enable G D HD74HC373QHD74HC533QL H H H L L H L L H L L X No change No changeH X X Z Z Note: 1. H; High level, L; Low level, X; Irrelevant, Z; High impedancePin Arrangement HD74HC373HD74HC533Logic DiagramHD74HC373HD74HC533Absolute Maximum RatingsUnit Item SymbolRatingsSupply voltage range V CC–0.5 to 7.0 VInput / Output voltage V IN, V OUT–0.5 to V CC +0.5 VInput / Output diode current I IK, I OK±20 mA Output current I OUT±35 mAV CC, GND current I CC or I GND±75 mAmW Power dissipation P T 500Storage temperature Tstg –65 to +150 °CNote: The absolute maximum ratings are values, which must not individually be exceeded, and furthermore, no two of which may be realized at the same time.Recommended Operating ConditionsItem Symbol Ratings Unit ConditionsSupply voltageV CC 2 to 6 VInput / Output voltage V IN , V OUT 0 to V CC V Operating temperature Ta –40 to 85 °C0 to 1000 V CC = 2.0 V0 to 500 V CC = 4.5 VInput rise / fall time *1t r , t f0 to 400ns V CC = 6.0 VNote: 1. This item guarantees maximum limit when one input switches.Waveform: Refer to test circuit of switching characteristics.Electrical CharacteristicsTa = 25°CTa = –40 to+85°CItem Symbol V CC (V) Min Typ Max Min Max UnitTest Conditions2.0 1.5 — — 1.5 — 4.53.15 — — 3.15 —V IH 6.0 4.2 — — 4.2 —V2.0 — — 0.5 — 0.5 4.5 — — 1.35 — 1.35Input voltage V IL6.0 — — 1.8 — 1.8 V 2.0 1.9 2.0 — 1.9 — 4.5 4.4 4.5 — 4.4 — 6.0 5.9 6.0 — 5.9 — I OH = –20 µA 4.5 4.18 — — 4.13 — I OH = –6 mAV OH6.0 5.68 — — 5.63 —V Vin = V IH or V IL I OH = –7.8 mA2.0 — 0.0 0.1 — 0.1 4.5 — 0.0 0.1 — 0.1 6.0 — 0.0 0.1 — 0.1 I OL = 20 µA 4.5 — — 0.26 — 0.33I OH = 6 mAOutput voltage V OL6.0 — — 0.26 — 0.33 V Vin = V IH or V IL I OH =7.8 mAOff-state outputcurrentI OZ 6.0 — — ±0.5 — ±5.0 µA Vin = V IH or V IL ,Vout = V CC or GND Input currentIin 6.0 — — ±0.1 — ±1.0 µA Vin = V CC or GND Quiescent supply current I CC 6.0 — — 4.0 — 40 µA Vin = V CC or GND, Iout = 0 µASwitching Characteristics (C L = 50 pF, Input t r = t f = 6 ns)Ta = 25°CTa = –40 to +85°CItem Symbol V CC (V) Min Typ Max UnitTest Conditions 2.0 — — 150 — 190 4.5 — 18 30 — 38t PLH t PHL 6.0 — — 26 — 33nsG to Q 2.0 — — 125 — 155 4.5 — 16 25 — 31 Propagation delay time t PLH t PHL6.0 — — 21 — 26 ns D to Q 2.0 — — 150 — 190 4.5 — 12 30 — 38 t ZL6.0 — — 26 — 33ns 2.0 — — 150 — 190 4.5 — 15 30 — 38 Output enable timet ZH6.0 — — 26 — 33 ns 2.0 — — 150 — 190 4.5 — 13 30 — 38 t LZ6.0 — — 26 — 33ns 2.0 — — 150 — 190 4.5 — 16 30 — 38 Output disable timet HZ6.0 — — 26 — 33ns 2.0 100 — — 125 — 4.5 20 1 — 25 — Setup time t su6.0 17 — — 21— ns 2.0 50 — — 65 — 4.5 10 1 — 13—Hold timet h6.0 9 — — 11 —ns 2.0 80 — — 100 — 4.5 16 6 — 20 — Pulse width t w6.0 14 — — 17—ns 2.0 — — 60 — 75 4.5 — 4 12 — 15 Output rise/fall timet TLH t THL 6.0 — — 10 — 13 ns Input capacitance Cin— — 5 10 — 10 pFTest CircuitWaveformsPackage Dimensions RENESAS SALES OFFICESRefer to "/en/network" for the latest and detailed information.Renesas Technology America, Inc.450 Holger Way, San Jose, CA 95134-1368, U.S.ATel: <1> (408) 382-7500, Fax: <1> (408) 382-7501Renesas Technology Europe LimitedDukes Meadow, Millboard Road, Bourne End, Buckinghamshire, SL8 5FH, U.K.Tel: <44> (1628) 585-100, Fax: <44> (1628) 585-900Renesas Technology (Shanghai) Co., Ltd.Unit 204, 205, AZIACenter, No.1233 Lujiazui Ring Rd, Pudong District, Shanghai, China 200120Tel: <86> (21) 5877-1818, Fax: <86> (21) 6887-7898Renesas Technology Hong Kong Ltd.7th Floor, North Tower, World Finance Centre, Harbour City, 1 Canton Road, Tsimshatsui, Kowloon, Hong KongTel: <852> 2265-6688, Fax: <852> 2730-6071Renesas Technology Taiwan Co., Ltd.10th Floor, No.99, Fushing North Road, Taipei, TaiwanTel: <886> (2) 2715-2888, Fax: <886> (2) 2713-2999Renesas Technology Singapore Pte. Ltd.1 Harbour Front Avenue, #06-10, Keppel Bay Tower, Singapore 098632Tel: <65> 6213-0200, Fax: <65> 6278-8001Renesas Technology Korea Co., Ltd.Kukje Center Bldg. 18th Fl., 191, 2-ka, Hangang-ro, Yongsan-ku, Seoul 140-702, KoreaTel: <82> (2) 796-3115, Fax: <82> (2) 796-2145Renesas Technology Malaysia Sdn. BhdUnit 906, Block B, Menara Amcorp, Amcorp Trade Centre, No.18, Jalan Persiaran Barat, 46050 Petaling Jaya, Selangor Darul Ehsan, MalaysiaTel: <603> 7955-9390, Fax: <603> 7955-9510© 2006. Renesas Technology Corp., All rights reserved. Printed in Japan.。

TC74HC373AP(F),TC74HC373AFW,TC74HC373AFW(ELP),TC74HC373AP, 规格书,Datasheet 资料

0 to VCC

V

0 to VCC

V

−40 to 85

°C

0 to 1000 (VCC = 2.0 V)

0 to 500 (VCC = 4.5 V)

ns

0 to 400 (VCC = 6.0 V)

Note: The operating ranges must be maintained to ensure the normal operation of the device. Unused inputs must be tied to either VCC or GND.

Ta = 25°C

Ta =

−40 to 85°C Unit

Typ. Limit Limit

⎯

75

95

⎯

15

19

ns

⎯

13

16

⎯

50

65

⎯

10

13

ns

⎯

9

11

⎯

5

5

⎯

5

5

ns

⎯

5

5

4

芯天下--/

2007-10-01

TC74HC373AP/AF

AC Characteristics (input: tr = tf = 6 ns)

System Diagram

2

芯天下--/

2007-10-01

Absolute Maximum Ratings (Note 1)

TC74HC373AP/AF

Characteristics

Symbol

Rating

Unit

Supply voltage range DC input voltage DC output voltage Input diode current Output diode current DC output current DC VCC/ground current Power dissipation Storage temperature

HC373技术参数资料

standard warranty. Production processing does not necessarily include testing of all parameters.24IMPORTANT NOTICETexas Instruments Incorporated and its subsidiaries (TI) reserve the right to make corrections, modifications, enhancements, improvements, and other changes to its products and services at any time and to discontinue any product or service without notice. Customers should obtain the latest relevant information before placing orders and should verify that such information is current and complete. All products are sold subject to TI’s terms and conditions of sale supplied at the time of order acknowledgment.TI warrants performance of its hardware products to the specifications applicable at the time of sale in accordance with TI’s standard warranty. T esting and other quality control techniques are used to the extent TI deems necessary to support this warranty. Except where mandated by government requirements, testing of all parameters of each product is not necessarily performed.TI assumes no liability for applications assistance or customer product design. Customers are responsible for their products and applications using TI components. T o minimize the risks associated with customer products and applications, customers should provide adequate design and operating safeguards.TI does not warrant or represent that any license, either express or implied, is granted under any TI patent right, copyright, mask work right, or other TI intellectual property right relating to any combination, machine, or process in which TI products or services are used. Information published by TI regarding third-party products or services does not constitute a license from TI to use such products or services or a warranty or endorsement thereof. Use of such information may require a license from a third party under the patents or other intellectual property of the third party, or a license from TI under the patents or other intellectual property of TI.Reproduction of information in TI data books or data sheets is permissible only if reproduction is without alteration and is accompanied by all associated warranties, conditions, limitations, and notices. Reproduction of this information with alteration is an unfair and deceptive business practice. TI is not responsible or liable for such altered documentation.Resale of TI products or services with statements different from or beyond the parameters stated by TI for that product or service voids all express and any implied warranties for the associated TI product or service and is an unfair and deceptive business practice. TI is not responsible or liable for any such statements. Following are URLs where you can obtain information on other Texas Instruments products and application solutions:Products ApplicationsAmplifiers Audio /audioData Converters Automotive /automotiveDSP Broadband /broadbandInterface Digital Control /digitalcontrolLogic Military /militaryPower Mgmt Optical Networking /opticalnetwork Microcontrollers Security /securityTelephony /telephonyVideo & Imaging /videoWireless /wirelessMailing Address:Texas InstrumentsPost Office Box 655303 Dallas, Texas 75265Copyright 2004, Texas Instruments Incorporated。