3706 datasheet

LTC3706EGN#PBF;LTC3706EGN#TRPBF;LTC3706IGN#PBF;LTC3706IGN#TRPBF;中文规格书,Datasheet资料

13706fdTYPICAL APPLICATIONDESCRIPTIONForward Controller with PolyPhase CapabilityThe L TC ®3706 is a PolyPhase capable secondary-side controller for synchronous forward converters. When used in conjunction with the L TC3705 gate driver and primary-side controller , the part creates a complete isolated power supply that combines the power of PolyPhase operation with the speed of secondary-side control.The L TC3706 has been designed to simplify the design of highly efficient, secondary-side forward converters. Working in concert with the L TC3705, the L TC3706 forms a robust, self-starting converter that eliminates the need for the separate bias regulator that is commonly used in secondary-side control applications. In addition, a pro-prietary scheme is used to multiplex gate drive signals and DC bias power across the isolation barrier through a single, tiny pulse transformer .The L TC3706 provides remote sensing, accurate power good and overvoltage monitoring circuits to support preci-sion, high current applications. A linear regulator controller with thermal protection is also provided to simplify the generation of secondary-side bias voltage.The L TC3706 is available in a 24-lead SSOP package.36V-72V to 3.3V/20A Isolated Forward ConverterFEATURESAPPLICATIONSnIsolated 48V Telecommunication Systems n Internet Servers and Routersn Distributed Power Step-Down Converters nAutomotive and Heavy EquipmentnSecondary-Side Control for Fast T ransient Response n Self-Starting Architecture Eliminates Need for Separate Bias Regulatorn Proprietary Gate Drive Encoding Scheme Reduces System Complexityn PolyPhase ® Operation Reduces C INRequirements n Current Mode Control Ensures Current Sharing n PLL Fixed Frequency: 100kHz to 500kHz n ±1% Output Voltage Accuracy n T rue Remote Sense Differential Amplifier n Power Good Output Voltage Monitor n High Voltage Linear Regulator Controller n Wide Supply Range: 5V to 30Vn Available in a Narrow 24-Lead SSOP PackageV IN –V IN +3OUT –OUT +L , L T , L TC, L TM, PolyPhase, Burst Mode, Linear Technology and the Linear logo are registered trademarks and No R SENSE and ThinSOT are trademarks of Linear Technology Corporation. All other trademarks are the property of their respective owners. Protected by U.S. Patents including 6144194, other patents pending./23706fdPIN CONFIGURATIONABSOLUTE MAXIMUM RATINGSV CC ........................................................... –0.3V to 10V V IN ........................................................... –0.3V to 33V SW ............................................................... –5V to 50V NDRV ......................................................... –0.3V to 13V ITH, RUN/SS, V SOUT , V S +, V S –, REGSD ....... –0.3V to 7VAll Other Pins ............................................ –0.3V to 10VOperating Temperature Range (Note 2) LTC3706E GN .......................................–40°C to 85°C LTC3706IGN ........................................–40°C to 85°C Junction Temperature (Note 3) ............................ 125°C Storage Temperature Range ..................–65°C to 150°C Lead Temperature (Soldering, 10 sec) ...................300°C(Note 1)ORDER INFORMATIONLEAD FREE FINISH TAPE AND REEL PART MARKING PACKAGE DESCRIPTION TEMPERATURE RANGE L TC3706EGN#PBF L TC3706EGN#TRPBF L TC3706EGN 24-Lead Plastic SSOP –40°C to 85°C L TC3706IGN#PBF L TC3706IGN#TRPBF L TC3706IGN 24-Lead Plastic SSOP –40°C to 85°C LEAD BASED FINISH TAPE AND REEL PART MARKING PACKAGE DESCRIPTION TEMPERATURE RANGE L TC3706EGN L TC3706EGN#TR L TC3706EGN 24-Lead Plastic SSOP –40°C to 85°C L TC3706IGNL TC3706IGN#TRL TC3706IGN24-Lead Plastic SSOP–40°C to 85°CConsult L TC Marketing for parts specified with wider operating temperature ranges.For more information on lead free part marking, go to: http://www.linear .com/leadfree/For more information on tape and reel specifications, go to: http://www.linear .com/tapeandreel//ELECTRICAL CHARACTERISTICSThel indicates specifications which apply over the full operating temperature range, otherwise specifications are at T A = 25°C. V CC = 7V, V IN = 15V, GND = PGND = 0V, unless otherwise noted.SYMBOL PARAMETER CONDITIONS MIN TYP MAX UNITS Main Control LoopV FB Regulated Feedback Voltage(Note 4) ITH = 1.2V l0.5940.6000.606V I FB Feedback Input Current(Note 4)2100nA ∆V FB(LINREG)Feedback Voltage Line Regulation V IN = 6V to 30V, ITH = 1.2V0.001%/V ∆V FB(LOADREG)Feedback Voltage Load Regulation Measured in Servo Loop,ITH = 0.5V to 2Vl–0.01–0.1%V ISMAX Maximum Current Sense Threshold R SENSE Mode, 0V < V IS– < 5VV IS– = V CC, 0V < V IS+ < 2V (CT Mode)681.15781.28881.4mVVV ISOC Over-Current Shutdown Threshold R SENSE Mode, 0V < V IS– < 5VV IS– = V CC, 0V < V IS+ < 2V (CT Mode)871.451001.651131.85mVVg m T ransconductance Amplifier g m 2.40 2.75 3.10mS I RUN/SS(C)Soft-Start Charge Current V RUN/SS = 2V–4–5–6µA I RUN/SS(D)Soft-Start Discharge Current3µA V RUN/SS RUN/SS Pin On Threshold V RUN/SS Rising l0.40.450.5V t ON,MIN Minimum On-Time200ns FG, SG R UP FG, SG Driver Pull-Up On Resistance FG, SG Low 1.5 2.7ΩFG, SG R DOWN FG, SG Driver Pull-Down On Resistance FG, SG High 1.5 2.7ΩPT+, PT– R UP PT+, PT– Driver Pull-Up Resistance PT+, PT– Low 1.5 2.7ΩPT+, PT– R DOWN PT+, PT– Driver Pull-Down Resistance PT+, PT– High 1.5 2.7Ω∆V FB(OV)Output Overvoltage Threshold V FB Rising151719% V CC SupplyV CCOP Operating Voltage Range510V V CCREG Regulated Output Voltage 6.67.07.4VI CC Supply CurrentOperatingShutdown f OSC = 200kHz (Note 5)V RUN/SS = GND4.2240mAµAV UVLO UV Lockout V CC Rising l 4.52 4.60 4.70V V HYS UV Hysteresis0.4V V IN SupplyV INOP Operating Voltage Range530VI IN Supply CurrentNormal ModeShutdown f OSC = 200kHzV RUN/SS = GND900460µAµAV INUVLO UV Lockout V IN Rising l 3.90 4.30 4.51V V INHYS0.2V V REGSD REGSD Shutdown Threshold V REGSD Rising4Vg m,REGSD REGSD T ransconductance5µS /33706fd43706fdELECTRICAL CHARACTERISTICS Note 1: Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. Exposure to any Absolute Maximum Rating condition for extended periods may affect device reliability and lifetime.Note 2: The L TC3706E is guaranteed to meet the performance specifica-tions over the 0°C to 85°C operating temperature range. Specifications over the –40°C to 85°C operating temperature range are assured by design, characterization and correlation with statistical process controls. The L TC3706I is guaranteed and tested over the full –40°C to 85°C operating temperature range.Note 3: Junction temperature T J (in °C) is calculated from the ambient tem-perature T A and the average power dissipation P D (in Watts) by the formula: T J = T A + θJA • P DRefer to the Applications Information section for details.Note 4: The L TC3706 is tested in a feedback loop that servos V FB to a voltage near the internal 0.6V reference voltage to obtain the specified ITH voltage (V ITH = 1.2V).Note 5: Operating supply current is measured in test mode. Dynamic supply current is higher due to the internal gate charge being delivered at the switching frequency. See the Typical Performance Characteristics section.SYMBOL PARAMETERCONDITIONSMINTYP MAXUNITSOscillator and Phase-Locked LoopI FS FS/SYNC Pin Sourcing Current 20µA f LOW Oscillator Low Frequency Set Point V FS/SYNC = GND 165200235kHz f HIGH Oscillator High Frequency Set Point V FS/SYNC = VCC247300353kHz ∆f (R FS )Oscillator Resistor Set Accuracy 75kΩ < R FS/SYNC < 175kΩ–2220%f PLL(MAX)Maximum PLL Sync Frequency 500kHz f PLL(MIN)Minimum PLL Sync Frequency75kHzPGOOD Output V FBH /0.6Power Good Upper Threshold V FB Rising 115117119%V FBL1/0.6Power Good Lower Threshold V FB Rising 91.59394.5%V FBL2/0.6Power Good Lower Threshold V FB Falling89.59192.5%Differential Amplifier (V SENSE AMP)ADA GainV S – = GND, 1V ≤ V S + ≤ 5V0.9901 1.010V/V CMRR DA Common Mode Rejection Ratio 75dB R IN Input Resistance 80kΩf BW–3dB Bandwidth3MHzThe l indicates specifications which apply over the full operatingtemperature range, otherwise specifications are at T A = 25°C. V CC = 7V, V IN = 15V, GND = PGND = 0V, unless otherwise noted./53706fdTYPICAL PERFORMANCE CHARACTERISTICSMaximum Current Sense RUN/SS ON Threshold Oscillator Frequency T A = 25°C, unless otherwise noted.Maximum Current Sense IS Pins Source Current V CC Supply Current V CC Regulator Output Voltage Maximum Current Sense /63706fdGate Driver On-Resistance TYPICAL PERFORMANCE CHARACTERISTICST A = 25°C, unless otherwise noted.Undervoltage Lockout REGSD Shutdown Threshold /PIN FUNCTIONSSG (Pin 1): Gate Drive for the “Synchronous” MOSFET. FG (Pin 2): Gate Drive for the “Forward” MOSFET. PGOOD (Pin 3): Open-Drain Power Good Output. The FBpin is monitored to ensure that the output is in regulation. When the output is not in regulation, the PGOOD pin is pulled low.MODE (Pin 4): Tie to either GND or V CC to set the maxi-mum duty cycle at either 50% or 75% respectively. Tie to ground through either a 200k or 100k resistor (50% or 75% maximum duty cycle) to disable pulse encoding. In this mode, normal PWM signals will be generated at the PT+ pin, while a clock signal is generated at the PT– pin. PHASE (Pin 5): Control Input to the Phase Selector. This pin determines the phasing of the controller CLK relative to the synchronizing signal at the FS/SYNC pin.FB (Pin 6): The Inverting Input of the Main Loop Error Amplifier.ITH (Pin 7): The Output of the Main Loop Error Amplifier. Place compensation components between the ITH pin and GND.RUN/SS (Pin 8): Combination Run Control and Soft-Start Inputs. A capacitor to ground sets the ramp time of the output voltage. Holding this pin below 0.4V causes the IC to shut down all internal circuitry.V SOUT, V S+, V S– (Pins 9, 10, 11): V SOUT is the output of a precision, unity-gain differential amplifier. Tie V S+ and V S– to the output of the main DC/DC converter to achieve true remote differential sensing. This allows DCR error effects to be minimized.GND (Pin 12): Signal Ground.FS/SYNC (Pin 13): Combination Frequency Set and SYNC pin. Tie to GND or V CC to run at 200kHz and 300kHz respectively. Place a single resistor to ground at this pin to set the frequency between 100kHz and 500kHz. To synchronize, drive this pin with a clock signal to achieve PLL synchronization from 75kHz to 500kHz. Sources 20µA of current.SLP (Pin 14): Slope Compensation Input. Place a single resistor to ground to set the desired amount of slope compensation.I S– (Pin 15): Negative Input to the Current Sense Circuit. When using current sense transformers, this pin may be tied to V CC for single-ended sensing with a 1.28V maximum current trip level.I S+ (Pin 16): Positive Input to the Current Sense Circuit. Connect to the positive end of a current sense resistor or to the output of a current sense transformer. REGSD (Pin 17):T his p in i s u sed t o p revent o verheating o f t he external linear regulator pass device that generates the V CC supply voltage from the V IN voltage. A current proportional to the voltage across the external pass device flows out of this pin. The IC shuts down the linear regulator when the voltage on this pin exceeds 4V. Place a resistor (or a resistor and capacitor in parallel) between this pin and GND to limit the temperature rise of the external pass device. NDRV (Pin 18): Drive Output for the External Pass Device of the V CC Linear Regulator. Connect to the base (NPN) or gate (NMOS) of an external N-type device.V IN (Pin 19): Connect to a higher voltage bias supply, typically the output of a peak detected bias winding. When not used, tie together with the V CC and NDRV pins.SW (Pin 20): Connect to the drain of the “synchronous” MOSFET. This input is used for adaptive shoot-through prevention and leading edge blanking.PT–, PT+ (Pins 21, 22): Pulse T ransformer Driver Outputs. For most applications, these connect to a pulse trans-former (with a series DC blocking capacitor). The PWM information is multiplexed together with DC power and sent through a single pulse transformer to the primary side. This information may be decoded by the L TC3705 gate driver and primary-side controller.PGND (Pin 23): Gate Driver Ground Pin.V CC (Pin 24): Main V CC Input for all Driver and Control Circuitry./73706fdBLOCK DIAGRAM83706fd/OPERATIONMain Control LoopThe L TC3706 is designed to work in a constant frequency, current mode 2-transistor forward converter. During normal operation, the primary-side MOSFETs (both top and bottom) are “clocked” on together with the forward MOSFET on the secondary side. This applies the reflected input voltage across the inductor on the secondary side. When the current in the inductor has ramped up to the peak value as commanded by the voltage on the ITH pin, the current sense comparator is tripped, turning off the primary-side and forward MOSFE Ts. To avoid turning on the synchronous MOSFET prematurely and causing shoot-through, the voltage on the SW pin is monitored. This voltage will usually fall below 0V soon after the primary-side MOSFETs have turned completely off. When this condition is detected, the synchronous MOSFET is quickly turned on, causing the inductor current to ramp back downwards. The error amplifier senses the output voltage, and adjusts the ITH voltage to obtain the peak current needed to maintain the desired main-loop output voltage. The L TC3706 always operates in a continuous current, synchronous switching mode. This ensures a rapid transient response as well as a stable bias supply voltage at light loads. A maximum duty cycle (either 50% or 75%) is internally set via clock dividers to prevent saturation of the main transformer. In the event of an overvoltage on the output, the synchronous MOSFET is quickly turned on to help protect critical loads from damage.Gate Drive EncodingSince the L TC3706 controller resides on the secondary side of an isolation barrier, communication to the primary-side power MOSFETs is generally done through a transformer. Moreover, it is often necessary to generate a low voltage bias supply for the primary-side gate drive circuitry. In order to reduce the number of isolated windings present in the system, the L TC3706 uses a proprietary scheme to encode the PWM gate drive information and multiplex it together with bias power for the primary-side drive and control, using a single pulse transformer. Note that, unlike optoisolators and other modulation techniques, this multiplexing scheme does not introduce a significant time delay into the system.For most forward converter applications, the PT+ and PT– outputs will contain a pulse-encoded PWM signal. These outputs are driven in a complementary fashion with an essentially constant 50% duty cycle. This results in a stable volt-second balance as well as an efficient transfer of bias power across the pulse transformer. As shown in Figure 1, the beginning of the positive half-cycle coincides with the turn-on of the primary-side MOSFETs. Likewise, the beginning of the negative half-cycle coincides with the maximum duty cycle (forced turn-off of primary switches). At the appropriate time during the positive half-cycle, the end of the on-time (PWM going LOW) is signaled by briefly applying a zero volt differential across the pulse transformer. Figure 1 illustrates the operation of this multiplexing scheme.The L TC3705 primary-side controller and gate driver will decode this PWM information as well as extract the power needed for primary-side gate drive.Figure 1. Gate Drive Encoding Scheme (V MODE = GND)DUTY CYCLE = 15%V PT1+ – V PT1DUTY CYCLE = 0%/93706fd103706fdOPERATIONvalues using the SLP pin as shown in Table 1. Note that the amount of slope compensation doubles when the duty cycle exceeds 50%.Table 1SLP PIN SLOPE (D < 0.5)SLOPE (D > 0.5)GND 0.05 • I SMAX • f OSC0.1 • I SMAX • f OSCV CCNone None 400kΩ to GND 0.1 • I SMAX • f OSC 0.2 • I SMAX • f OSC 200kΩ to GND 0.15 • I SMAX • f OSC 0.3 • I SMAX • f OSC 100kΩ to GND 0.25 • I SMAX • f OSC 0.5 • I SMAX • f OSC 50kΩ to GND0.5 • I SMAX • f OSC1.0 • I SMAX • f OSCIn Table 1 above, I SMAX is the maximum current limit, and f OSC is the switching frequency.Current Sensing and Current LimitFor current sensing, the L TC3706 supports either a current sense resistor or a current sense transformer . The current sense resistor may either be placed in series with the inductor (either high side or ground lead sensing), or in the source of the “forward” switch. If a current sense transformer is used, the I S – input should be tied to V CC and the I S + pin to the output of the current sense transformer . This causes the gain of the internal current sense amplifier to be reduced by a factor of 16×, so that the maximum current sense voltage (current limit) is increased from 78mV to 1.28V . An internal, adaptive leading edge blanking circuit ensures clean operation for “switch” current sensing applications.Current limit is achieved in the L TC3706 by limiting the maximum voltage excursion of the error signal (ITH volt-age). Note that if slope compensation is used, the precise value at which current limit occurs will be a function of duty cycle (See the Typical Performance Characteristics section). If a short circuit is applied, an independent overcurrent comparator may be tripped. In this case, the L TC3706 will enter a “hiccup” mode using the soft-start circuitry.Self-Starting ArchitectureWhen the LTC3706 is used in conjunction with the LTC3705 primary-side controller and gate driver , a complete self-starting isolated supply is formed. When input voltage is first applied in such an application, the L TC3705 will begin switching in an “open-loop” fashion, causing the main output to slowly ramp upwards. This is the primary-side soft-start mode. On the secondary side, the L TC3706 derives its operating bias voltage from a peak-charged capacitor . This peak-charged voltage will rise more rapidly than the main output of the converter , so that the L TC3706 will become operational well before the output voltage has reached its final value.When the L TC3706 has adequate operating voltage, it will begin the procedure of assuming control from the primary side. To do this, it first measures the voltage on the power supply’s main output and then automatically advances its own soft-start voltage to correspond to the main output voltage. This ensures that the output voltage increases monotonically as the soft-start control is transferred from primary to secondary. The L TC3706 then begins sending PWM signals to the L TC3705 on the primary side through a pulse transformer . When the L TC3705 has detected a stable signal from the secondary controller , it transfers control of the primary switches over to the L TC3706, beginning the secondary-side soft-start mode. The L TC3706 continues in this mode until the output voltage has ramped up to its final value. If for any reason, the L TC3706 either stops sending (or initially fails to send) PWM information to the L TC3705, the L TC3705 will detect a FAUL T and initiate a soft-start retry. (See the L TC3705 data sheet.) Slope CompensationSlope compensation is added at the input of the PWM comparator to improve stability and noise margin of the peak current control loop. The amount of slope compen-sation can be selected from one of five preprogrammed/分销商库存信息:LINEAR-TECHNOLOGYLTC3706EGN#PBF LTC3706EGN#TRPBF LTC3706IGN#PBF LTC3706IGN#TRPBF。

9906;中文规格书,Datasheet资料

Nominal data

Type Phase Nominal voltage Frequency Speed Power input Min. ambient temperature Max. ambient temperature Air flow Sound power level Sound pressure level VAC Hz min-1 W °C °C m3/h B dB(A) 9906 1~ 115 60 2850 12.0 -40 70 135 5.4 42

/

9906

AC axial compact fan

Technical features

General description AC voltage fan with internal rotor shaded-pole motor. Protected from overload by impedance protection. Fan housing made of metal, impeller made of mineral-reinforced PA plastic. Air exhaust over bars. Direction of rotation counter-clockwise seen on rotor. Electrical connection to 2 flat plugs 2.8 x 0.5 mm. Fan housing with grounding lug for M4 tapping screw. Mass 320 g. Please note our new ACmaxx series. With identical fastening dimensions and voltages, this series achieves higher energy efficiency. 0.325 kg 119 x 119 x 25 mm Mineral-reinforced PA plastic Metal Air exhaust over bars Left, looking at rotor Ball bearings 52500 h 25000 h 2 flat plugs 2.8 x 0.5 mm Protected from overload using impedance protection VDE, CSA, UL, CE

和谐XPS安全自动化产品数据表说明书

Product data sheetSpecificationsTime delayed output, Harmony XPS,for Estop, guard, OSSD, 24 V AC/DC, springXPSBAT12A1ACMainRange of ProductHarmony Safety Automation Product or Component Type Safety module Safety module name XPSBATSafety module application For emergency stop and protective guard applications For OSSD monitoringFunction of moduleEmergency stop button with 2 NC contacts Guard monitoring with 1 or 2 limit switches Light curtain monitoring RFID switchMonitoring of electro-sensitive protection equipment (ESPE)Safety levelCan reach PL e/category 4 for normally open relay contact ISO 13849-1Can reach SILCL 3 for normally open relay contact IEC 62061Can reach SIL 3 for normally open relay contact IEC 61508Can reach PL c/category 1 for normally closed relay contact ISO 13849-1Can reach SILCL 1 for normally closed relay contact IEC 62061Can reach SIL 1 for normally closed relay contact IEC 61508Safety reliability dataMTTFd > 30 years ISO 13849-1Dcavg >= 99 % ISO 13849-1PFHd = 0.98E-09 for SS0 ISO 13849-1PFHd = 0.96E-09 for SS1 ISO 13849-1HFT = 1 IEC 62061PFHd = 0.98E-09 for SS0 IEC 62061PFHd = 0.96E-09 for SS1 IEC 62061SFF > 99% IEC 62061HFT = 1 IEC 61508-1PFHd = 0.98E-09 for SS0 IEC 61508-1PFHd = 0.96E-09 for SS1 IEC 61508-1SFF > 99% IEC 61508-1Type = B IEC 61508-1Electrical circuit type NC pair OSSD pairConnections - terminalsRemovable spring terminal block, 0.2...2.5 mm² solid or flexibleRemovable spring terminal block, 0.25...2.5 mm² flexible with ferrule single conductor Removable spring terminal block, 0.2...1.5 mm² solid or flexible twin conductorRemovable spring terminal block, 2 x 0.25...1 mm² flexible with ferrule without cable end, with bezel Removable spring terminal block, 2 x 0.5...1.5 mm² flexible with ferrule with cable end, with bezel [Us] Rated Supply Voltage24 V AC - 15...10 %24 V DC - 20...20 %ComplementarySynchronisation time between inputs 0.5 s 2 sType of startAutomatic/manual/monitored Power consumption in W2 W 24 V DCD i s c l a i m e r : T h i s d o c u m e n t a t i o n i s n o t i n t e n d e d a s a s u b s t i t u t e f o r a n d i s n o t t o b e u s e d f o r d e t e r m i n i n g s u i t a b i l i t y o r r e l i a b i l i t y o f t h e s e p r o d u c t s f o r s p e c i f i c u s e r a p p l i c a t i o n sPower consumption in VA5 VA 24 V AC 50/60 HzInput protection type Internal, electronicSafety outputs 2 NO1 NOSafety inputs2Maximum wire resistance500 OhmTime delay range0...900 sInput compatibility Normally closed circuit ISO 14119Mechanical contact ISO 14119OSSD pair IEC 61496-1-2Normally closed circuit ISO 138503-wire proximity sensors PNP[Ie] rated operational current5 A AC-13 A AC-155 A DC-13 A DC-13Control outputs 3 pulsed outputInput/Output type Semiconductor output Z1, 20 mA[Ith] conventional free air12 Athermal currentAssociated fuse rating6 A gG NO relay output circuit IEC 60947-1 Minimum output current20 mA relay outputMinimum output voltage24 V relay outputMaximum response time on20 msinput open[Ui] rated insulation voltage250 V 2)EN/IEC 60947-1[Uimp] rated impulse withstand4 kV II EN/IEC 60947-1voltageLocal signalling LED green power power ONLED red error errorLED yellow state 1 safety output instantaneousLED yellow state 2 safety output delayedLED yellow start 1 startLED yellow start 2 startLED yellow S12 safety input S12LED yellow S22 safety input S22Mounting Support35 mm symmetrical DIN railDepth 4.72 in (120 mm)Height 3.94 in (100 mm)Width 1.77 in (45 mm)Net Weight0.77 lb(US) (0.350 kg)EnvironmentStandards IEC 60947-5-1IEC 61508-1 functional safety standardIEC 61508-2 functional safety standardIEC 61508-3 functional safety standardIEC 61508-4 functional safety standardIEC 61508-5 functional safety standardIEC 61508-6 functional safety standardIEC 61508-7 functional safety standardISO 13849-1 functional safety standardIEC 62061 functional safety standardProduct certifications TÜVcULusIP degree of protection IP20 terminals)EN/IEC 60529IP40 housing)EN/IEC 60529IP54 mounting area)EN/IEC 60529 Ambient air temperature for-13…131 °F (-25…55 °C)operationAmbient Air Temperature for-13…185 °F (-25…85 °C)StorageRelative Humidity5…95 % non-condensingOrdering and shipping detailsCategory22477-SAFETY MODULES (PREVENTA)Discount Schedule SAF2GTIN3606482034037Nbr. of units in pkg.1Package weight(Lbs)10.65 oz (302 g)Returnability NoPacking UnitsUnit Type of Package 1PCEPackage 1 Height 2.52 in (6.4 cm)Package 1 width 5.24 in (13.3 cm)Package 1 Length 6.02 in (15.3 cm)Unit Type of Package 2S03Number of Units in Package 216Package 2 Weight11.92 lb(US) (5.409 kg)Package 2 Height11.81 in (30 cm)Package 2 width11.81 in (30 cm)Package 2 Length15.75 in (40 cm)Package 3 Height11.81 in (30 cm)Offer SustainabilitySustainable offer status Green Premium productCalifornia proposition 65WARNING: This product can expose you to chemicals including: Lead and lead compounds, which isknown to the State of California to cause cancer and birth defects or other reproductive harm. For moreinformation go to REACh Regulation REACh DeclarationEU RoHS Directive Pro-active compliance (Product out of EU RoHS legal scope)EU RoHS DeclarationMercury free YesRoHS exemption information YesChina RoHS Regulation China RoHS declarationEnvironmental Disclosure Product Environmental ProfileCircularity Profile End of Life InformationWEEE The product must be disposed on European Union markets following specific waste collection andnever end up in rubbish bins.Dimensions Drawings DimensionsFront and Side Views(A) : Product drawing(B) : Spring terminal(C) : Side view(1) : Removable terminal blocks, top(2) : Removable terminal blocks, bottom(3) : LED indicators(4) : Delay factor selector(5) : Delay base selector(6) : Sealable transparent coverMounting to DIN railScrew-mountingConnections and SchemaWiring Diagram(1) : A1-A2 (Power supply)(2) : S11–S21 (Control outputs (DC+) of safety-related inputs), S12-S22 (Input channels (CH+) of safety-related inputs)(3) : Y1 (Control output of Start/Restart input), Y2 (Input channel for automatic/manual start), Y3 (Input channel for monitored start with falling edge)13-14-23-24 : Terminals of the safety-related outputs (instantaneous)37-38 : Terminals of the safety-related outputs (delayed)Z1 : Solid state output, not safety-related。

2N3906中文资料(nte)中文数据手册「EasyDatasheet - 矽搜」

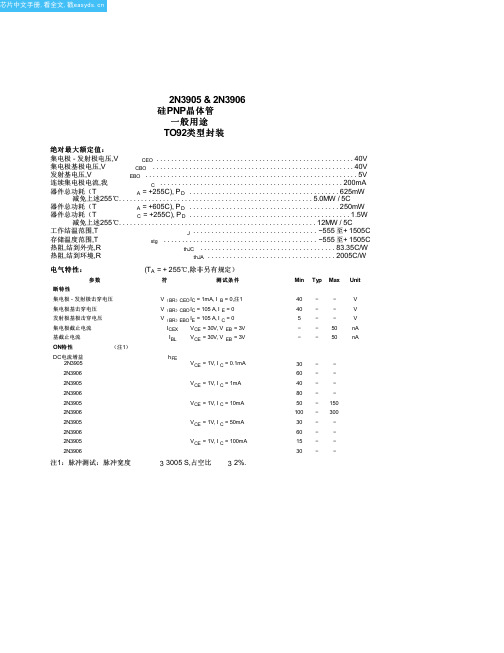

VCE = 1V, I C = 1mA

40 − − 80 − −

2N3905 2N3906

VCE = 1V, I C = 10mA

50 − 150 100 − 300

2N3905 2N3906

VCE = 1V, I C = 50mA

30 − − 60 − −

2N3905 2N3906

VCE = 1V, I C = 100mA

芯片中文手册,看全文,戳

2N3905 & 2N3906 硅PNP晶体管

一般用途

TO92类型封装

绝对最大额定值:

集电极 - 发射极电压,V

CEO . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 40V

器件总功耗(T

C = +255C), PD . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1.5W

减免上述255℃. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 12MW / 5C

减免上述255℃. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5.0MW / 5C

器件总功耗(T

GS-2406T PLUS GS-3405T PLUS Series 热转式 热感式 SUR

GS-2406T PLUS / GS-3405T PLUS / Series热转式/热感式SURPASS PLUS条码印表机使用手册Ver.1.1.3Agency Compliance and ApprovalsEN 55032, Class AEN 55024This is a class A product. In a domestic environment this product may cause radiointerference in which case the user may be required to take adequate measures.FCC part 15B, Class AThis equipment has been tested and found to comply with the limits for a Class Adigital device, pursuant to Part 15 of the FCC Rules. These limits are designed toprovide reasonable protection against harmful interference when the equipment isoperated in a commercial environment. This equipment generates, uses, and canradiate radio frequency energy and, if not installed and used in accordance with themanufacturer’s instruction manual, may cause harmful interference with radiocommunications. Operation of this equipment in a residential area is likely to causeharmful interference, in which case you will be required to correct the interference atyour own expense.FCC 符合声明此设施符合第15 部份的规则。

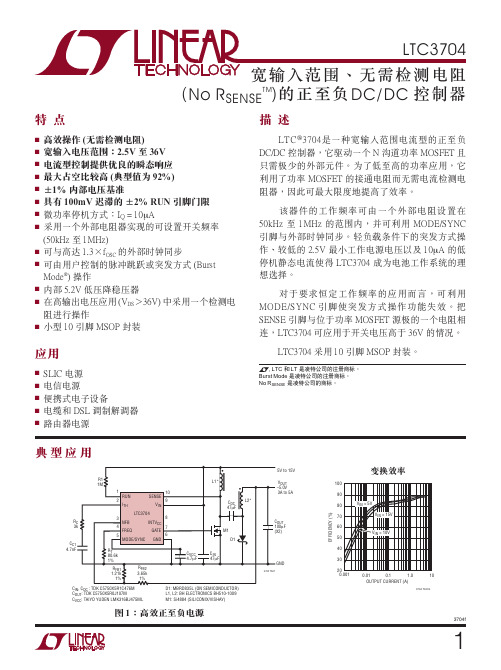

LT3704 中文数据手册 datasheet

LQWYFF 3hP^_`h LQWYFF 3hP`hIF

LQWYFF 3hP`hIF

LQWYFF <ZIF LQWYFF 3hPh@ tWUl1OsSCV LQWYFF `@`.

pqh?F

pn

,>DyP^_2HV1

pc

,>DyP^_1@V1

H3 UIUHT A >6h

cRVF A 966hKu .P</ YV\QF A 6Y P ;Y YV\QF A 6Y P ;Y

NDNCM > ;3XZRIKBC2OTJA > 3RZ;h6B_]\

Ny

@>

.MF

cRVF

RZPc@

RZPc43;V_44oc@V

pV\QF.PLQ/ PRGH5V\QF _7^.hF4r

pV\QF.PD[/ PRGH5V\QF _4^.hF4r

YLO.PRGH/

Y`s PRGH5V\QF ^.`h

YLK.PRGH/

s`s PRGH5V\QF ^.`h

UPRGH5V\QF PRGH5V\QF ^.1H`d

YIUHT

IUHT OI<v`h

AT|`TF

YLQWYFF qYLQWYFF

qYLQ7 qYLQWYFF

qYLQ8 YOGR.ORDG/

YGURSRXW

LLQWYFF

YUXQ1 YUXQx

_7^.`h

^.`h`@`. U@SC 6uSCUXps<Z tWSC

UXQ ^.`h2HTc?

UXQ ^.`h1@Tc?

YUXQ.K\VW/ LUXQ YQIE

UXQ OI^.c?`p UXQ ^.`. <JP`h

3706M-E1S中文资料

————————————————————————————————————————————初级控制全隔离电池充电IC AP3706Jul. 2008 Rev. 1.3 BCD 半导体制造有限公司概述AP3706 是高性能的 ,专为 储电池充电和适配器应用设计的AC/DC 电源控制器. 该设备采用脉冲频率调制(PFM )方法建立非连续导通模式(DCM )反激式电源.AP3706 提供恒压恒流控制(CV/CC)而不需要光电耦合器和二次线路控制。

在保持稳定的同时,它取消(原来必要的)环路补偿电路。

AP3706 实现了卓越的控制能力和高效能转换, 空载功耗在265V AC 输入时低于200mW 。

AP3706 提供SOIC-8 和 DIP-8 封装规格。

主要特点· 初级端控制矩形恒流和恒压输出 · 取消光耦合器和次级CV/CC 控制线路 · 取消环路补偿电路· DCM 工作在反激式拓扑结构· 任意频率调制降低系统电磁干扰(EMI ) · 波谷导通大功率 NPN 晶体管 · 内置软启动 · 开放电路保护 · 超电压保护 · 短路保护应用· 适配器/为手机、无绳电话、PDA\MP3和其他便携仪器充电 · 待机和备用电源应用图 1. AP3706 封装图管脚编排图 2. AP3706管脚编排(顶视)————————————————————————————————————————————初级控制全隔离电池充电IC AP3706图 3. AP3706实用结构图Jul. 2008 Rev. 1.3 BCD 半导体制造有限公司————————————————————————————————————————————初级控制全隔离电池充电IC AP3706编号信息BCD半导体无铅产品, 指定后缀为"E1", 遵从RoHS规定.商品后缀"G1"为环保封装。

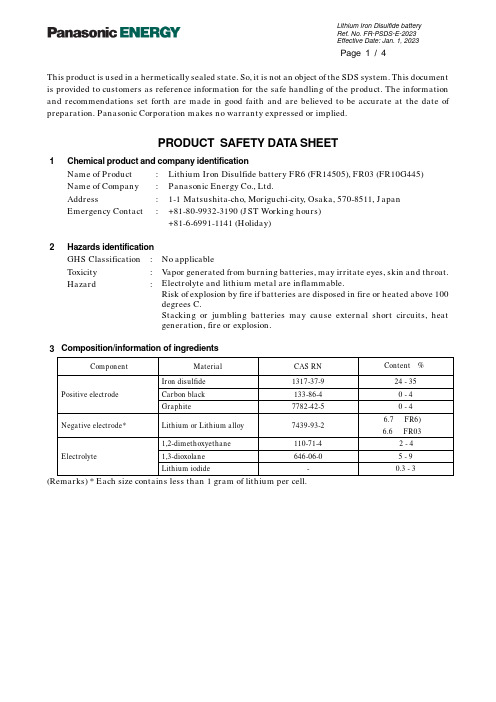

潘森高能电池产品安全数据表说明书

This product is used in a hermetically sealed state. So, it is not an object of the SDS system. This document is provided to customers as reference information for the safe handling of the product. The information and recommendations set forth are made in good faith and are believed to be accurate at the date of preparation. Panasonic Corporation makes no warranty expressed or implied.PRODUCT SAFETY DATA SHEET1 Chemical product and company identificationName of Product : Lithium Iron Disulfide battery FR6 (FR14505), FR03 (FR10G445)Name of Company : Panasonic Energy Co., Ltd.Address : 1-1Matsushita-cho, Moriguchi-city, Osaka, 570-8511, JapanEmergency Contact : +81-80-9932-3190 (JST Working hours)+81-6-6991-1141 (Holiday)2Hazards identificationGHS Classification : No applicableToxicity : Vapor generated from burning batteries, may irritate eyes, skin and throat.Hazard : Electrolyte and lithium metal are inflammable.Risk of explosion by fire if batteries are disposed in fire or heated above 100degrees C.Stacking or jumbling batteries may cause external short circuits, heatgeneration, fire or explosion.3Composition/information of ingredientsComponent Material CAS RN Content •i%•jPositive electrode Iron disulfide 1317-37-9 24 - 35 Carbon black 133-86-4 0 - 4 Graphite 7782-42-5 0 - 4Negative electrode* Lithium or Lithium alloy 7439-93-2 6.7 •iFR6) 6.6 •iFR03•jElectrolyte 1,2-dimethoxyethane 110-71-4 2 - 4 1,3-dioxolane 646-06-0 5 - 9 Lithium iodide - 0.3 - 3(Remarks) * Each size contains less than 1 gram of lithium per cell.4First aid measures (in case of electrolyte leakage from the battery)Eye contact : Flush the eyes with plenty of clean water for at least 15 minutesimmediately, without rubbing. Get immediate medical treatment.If appropriate procedures are not taken, this may cause eye injury.Skin contact : Wash the affected area under tepid running water using a mildsoap. If appropriates procedures are not taken, this may cause soreson the skin. Get medical attention if irritation develops or persists.Inhalation: Remove to fresh air immediately. Get medical treatmentimmediately.5 Firefighting measuresFire extinguishing agent : Alcohol-resistant foam and dry sand are effective.Extinguishing method : Be sure on the windward to extinguish the fire, since vapor maymake eyes, nose and throat irritate, Wear the respiratory protectionequipment in some cases.6Accidental release measures (in case of electrolyte leakage from the battery)Take up with absorbent cloth, treat cloth as inflammable.Move the battery away from the fire.7 Handling and storageHandling : žWhen packing the batteries, do not allow battery terminals tocontact each other, or contact with other metals. Be sure to packbatteries by providing partitions in the packaging box, or in aseparate plastic bag so that the single batteries are not mixedtogether.žUse strong material for packaging boxes so that they will not bedamaged by vibration, impact, dropping and stacking duringtheir transportation.žDo not short-circuit, recharge, deform, throw into fire ordisassemble.žDo not mix different type of batteries.žDo not solder directly onto batteries.žInsert the battery correctly in electrical equipment.Storage : •E Do not let water penetrate into packaging boxes during theirstorage and transportation.•E Do not store the battery in places of the high temperature orunder direct sunlight.žPlease also avoid the places of high humidity. Be sure not toexpose the battery to condensation, rain or frozen condition8.Exposure controls and personal protectionAcceptable concentration : Not specified about Lithium Battery.Facilities : Nothing in particularProtective Equipment (in case of electrolyte leakage from the battery)Respiratory Protection : For most condition no respiratory protection.Hand Protection : Safety gloves.Eye Protection : Safety goggle9.Physical and chemical propertiesAppearance : Cylindrical shapeNominal Voltage : 1.5 V10. Stability and reactivitySince batteries utilize a chemical reaction they are actually considered a chemical product.As such, battery performance will deteriorate over time even if stored for a long period of time without being used. In addition, the various usage conditions such as discharge, ambient temperature, etc. are not maintained within the specified ranges the life expectancy of the battery may be shortened or the device in which the battery is used may be damaged by electrolyte leakage.11.Toxicological informationSwallowing can lead to chemical bums, perforation of soft tissue, and death. Severe bums can occur within 2 hours of ingestion. Seek medical attention immediately.12.Ecological informationIn case of the worn out battery was disposed in land, the battery case may be corroded, and leak electrolyte. However, there is no environmental impact information.Mercury (Hg), Cadmium (Cd) and Lead (Pb) are not used in cell.13.Disposal considerationsWhen the battery is worn out, dispose of it under the ordinance of each local government.14.Transport informationHandlingDuring the transportation of a large amount of batteries by ship, trailer or railway, do not leave them in the places of high temperatures and do not allow them to be exposed to condensation.During the transportation do not allow packages to be dropped or damaged.Proper shipping name : Lithium metal batteriesUN Number, UN Class : UN3090, Class9 (for the Air transport by PI968 Section IA or IB): Exemption (for the Marine transport SP188 and the Air transportby Section II of PI 969 or 970)Even though the cells are classified as lithium metal batteries(UN3090 or UN3091), they are not subject to some requirements ofDangerous Goods Regulations because they meet the following:1. for cells, the lithium content is not more than 1 g ;2. each cell is of the type proven to meet the requirements of each test inthe UN Manual of T ests and Criteria, PartúL, sub-section 38.3.3. each cell is manufactured in ISO9001 certified factory.4. the test summary is available from;https:///ww/downloads/battery-test-summary Please refer to the following reference information about concrete ways of transportation. Actual content of packaging label and shipping documents varies by shipping companies. Make sure to confirm in advance with your shipping company.Information of referenceReference Packing Instruction(PI)/Special provision(SP)NoteAir transport IATA DGR PI 968 SectionúJ A Cells, Cargo Aircraft only; Net quantity perpackage Max. 35kgPI 968 SectionúJ B Cells, Cargo Aircraft only; net quantity perpackage Max. 2.5kgPI 969 SectionúK Cells packed with equipmentPI 970 SectionúK Cells contained in equipment Marine transport IMDG Code SP 18815.Regulatory information•E IATA Dangerous Goods Regulations Edition 64 (IATA DGR)•E IMO International Maritime Dangerous Goods Code 2020 and 2022 Edition (IMDG Code)•E UN Recommendations on the Transportation of Dangerous Goods, Model Regulations•E UN Recommendations on the Transportation of Dangerous Goods, Manual of Tests and Criteria •E EU Battery Directive•i2006/66/EC, 2013/56/EU)•E Regulation (EC) No. 1907/2006 on the Registration, Evaluation, Authorization and Restriction of Chemicals (REACH)•E State of California Regulations - Best management practices for Perchlorate Materials•E Act on Preventing Environmental Pollution of Mercury (Japan)16.Other informationThis PSDS is provided to customers as reference information in order to handle batteries safely.It is necessary for the customer to take appropriate measures depending on the actual situation such as the individual handling, based on this information.Prepared by: Engineering DepartmentEnergy Device Business DivisionPanasonic Energy Co., Ltd.。

UC3906 Datasheet

UC2906UC3906 Sealed Lead-Acid Battery ChargerFEATURES•Optimum Control for Maximum Battery Capacity and Life •Internal State Logic Provides Three Charge States •Precision Reference Tracks Battery Requirements OverTemperature•Controls Both Voltage and Current at Charger Output •System Interface Functions •Typical Standby SupplyCurrent of only 1.6mA DESCRIPTIONThe UC2906 series of battery charger controllers contains all of the necessary circuitry to optimally control the charge and hold cycle for sealed lead-acid batter-ies. These integrated circuits monitor and control both the output voltage and cur-rent of the charger through three separate charge states; a high current bulk-charge state, a controlled over-charge, and a precision float-charge, or standby, state.Optimum charging conditions are maintained over an extended temperature range with an internal reference that tracks the nominal temperature charac-teristics of the lead-acid cell. A typical standby supply current requirement of only 1.6mA allows these ICs to predictably monitor ambient temperatures.Separate voltage loop and current limit amplifiers regulate the output voltage and current levels in the charger by controlling the onboard driver. The driver will sup-ply up to 25mA of base drive to an external pass device. Voltage and current sense comparators are used to sense the battery condition and respond with logic inputs to the charge state logic. A charge enable comparator with a trickle bias output can be used to implement a low current turn-on mode of the charger, preventing high current charging during abnormal conditions such as a shorted battery cell.Other features include a supply under-voltage sense circuit with a logic output to indicate when input power is present. In addition the over-charge state of the charger can be externally monitored and terminated using the over-charge indi-cate output and over-charge terminate input.UC2906UC3906 Supply Voltage (+V IN). . . . . . . . . . . . . . . . . . . . . . . . . . . 40VOpen Collector Output Voltages. . . . . . . . . . . . . . . . . . . 40VAmplifier and Comparator Input Voltages. . . -0.3V to +40VOver-Charge Terminate Input Voltage. . . . . . -0.3V to +40VCurrent Sense Amplifier Output Current. . . . . . . . . . 80mAOther Open Collector Output Currents. . . . . . . . . . . . 20mATrickle Bias Voltage Differential with respect to V IN. . . -32VTrickle Bias Output Current. . . . . . . . . . . . . . . . . . . . -40mADriver Current. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 80mAPower Dissipation at T A = 25°C(Note 2). . . . . . . . 1000mWPower Dissipation at T C = 25°C (Note 2). . . . . . . . 2000mWOperating Junction Temperature. . . . . . . . -55°C to +150°CStorage Temperature. . . . . . . . . . . . . . . . . -65°C to +150°CLead Temperature (Soldering, 10 Seconds). . . . . . . 300°CNote 1:Voltages are referenced to ground (Pin 6). Currentsare positive into, negative out of, the specified terminals.Note 2: Consult Packaging section of Databook for thermallimitations and considerations of packages.ABSOLUTE MAXIMUM RATINGS (Note 1)Unless otherwise stated, these specifications apply for T A = -40°C to +70°C for theUC2906 and 0°C to +70°C for the UC3906, +V IN = 10V, T A = T J.ELECTRICAL CHARACTERISTICS:the reference and the thermal resistance, junction-to-ambient.ELECTRICAL CHARACTERISTICS:Unless otherwise stated, these specifications apply for T A = -40°C to +70°C for theUC2906 and 0°C to +70°C for the UC3906, +V IN = 10V, T A = T J.UC2906UC3906Dual Level Float Charger OperationsThe UC2906 is shown configured as a dual level float charger in Figure 1. All high currents are handled by the external PNP pass transistor with the driver supplying base drive to this device. This scheme uses the TRICKLE BIAS output and the charge enable comparator to givethe charger a low current turn on mode. The output cur-rent of the charger is limited to a low-level until the battery reaches a specified voltage, preventing a high current charging if a battery cell is shorted. Figure 2 shows the state diagram of the charger. Upon turn on the UV sense circuitry puts the charger in state 1, the high rate bulk-charge state. In this state, once the enable threshold has been exceeded, the charger will supply a peak current that is determined by the 250mV offset in the C/L ampli-fier and the sensing resistor R S.T o guarantee full re-charge of the battery, the charger’s voltage loop has an elevated regulating level, V OC , during state 1 and state 2. When the battery voltage reaches 95% of V OC , the charger enters the over-charge state,state 2. The charger stays in this state until the OVER-CHARGE TERMINATE pin goes high. In Figure 1, the charger uses the current sense amplifier to generate this signal by sensing when the charge current has tapered to a specified level, I OCT . Alternatively the over-charge could have been controlled by an external source, such as a timer, by using the OVER-CHARGE INDICATE signal at Pin 9. If a load is applied to the battery and begins to dis-charge it, the charger will contribute its full output to the load. If the battery drops 10% below the float level, the charger will reset itself to state 1. When the load is re-moved a full charge cycle will follow. A graphical repre-sentation of a charge, and discharge, cycle of the duallever float charger is shown in Figure 3.UC2906UC3906OPERATION AND APPLICATION INFORMATIONUC2906UC3906 OPERATION AND APPLICATION INFORMATION (continued)Compensated Reference Matches Battery Requirements When the charger is in the float state, the battery will be maintained at a precise float voltage, V F . The accuracy of this float state will maximize the standby life of the battery while the bulk-charge and over-charge states guarantee rapid and full re-charge. All of the voltage thresholds on the UC2906 are derived from the internal reference. This reference has a temperature coefficient that tracks the temperature characteristic of the optimum-charge and hold levels for sealed lead-acid cells. This further guaran-tees that proper charging occurs, even at temperature ex-tremes.Dual Step Current Charger OperationFigures 4, 5 and 6 illustrate the UC2906’s use in a differ-ent charging scheme. The dual step current charger is useful when a large string of series cells must be charged. The holding-charge state maintains a slightly elevated voltage across the batteries with the holding cur-rent, 1H . This will tend to guarantee equal charge distribu-tion between the cells. The bulk-charge state is similar to that of the float charger with the exception that when V 12is reached, no over-charge state occurs since Pin 8 is tied high at all times. The current sense amplifier is used to regulate the holding current. In some applications a series resistor, or external buffering transistor, may be requiredat the current sense output to prevent excessive power dissipation on the UC2906.A PNP Pass Device Reduces Minimum Input to Out-put DifferentialThe configuration of the driver on the UC2906 allows a good bit of flexibility when interfacing to an external pass transistor. The two chargers shown in Figures 1 and 4both use PNP pass devices, although an NPN device driven from the source output of the UC2906 driver can also be used. In situations where the charger must oper-ate with low input to output differentials the PNP pass de-vice should be configured as shown in Figure 4. The PNP can be operated in a saturated mode with only the series diode and sense resistor adding to the minimum differen-tial. The series diode, D1, in many applications, can be eliminated. This diode prevents any discharging of the battery, except through the sensing divider, when the charger is attached to the battery with no input supply voltage. If discharging under this condition must be kept to an absolute minimum, the sense divider can be refer-enced to the POWER INDICATE pin, Pin 7, instead of ground. In this manner the open collector off state of Pin 7 will prevent the divider resistors from discharging thebattery when the input supply is removed.UC2906UC3906OPERATION AND APPLICATION INFORMATION (continued)UC2906UC3906 OPERATION AND APPLICATION INFORMATION (continued)UNITRODE INTEGRA TED CIRCUITS7 CONTINENTAL BLVD. • MERRIMACK, NH 03054TEL. 603-424-2410 • FAX 603-424-3460IMPORTANT NOTICETexas Instruments and its subsidiaries (TI) reserve the right to make changes to their products or to discontinue any product or service without notice, and advise customers to obtain the latest version of relevant information to verify, before placing orders, that information being relied on is current and complete. All products are sold subject to the terms and conditions of sale supplied at the time of order acknowledgement, including those pertaining to warranty, patent infringement, and limitation of liability.TI warrants performance of its semiconductor products to the specifications applicable at the time of sale in accordance with TI’s standard warranty. Testing and other quality control techniques are utilized to the extent TI deems necessary to support this warranty. Specific testing of all parameters of each device is not necessarily performed, except those mandated by government requirements.CERTAIN APPLICATIONS USING SEMICONDUCTOR PRODUCTS MAY INVOLVE POTENTIAL RISKS OF DEATH, PERSONAL INJURY, OR SEVERE PROPERTY OR ENVIRONMENTAL DAMAGE (“CRITICAL APPLICATIONS”). TI SEMICONDUCTOR PRODUCTS ARE NOT DESIGNED, AUTHORIZED, OR WARRANTED TO BE SUITABLE FOR USE IN LIFE-SUPPORT DEVICES OR SYSTEMS OR OTHER CRITICAL APPLICATIONS. INCLUSION OF TI PRODUCTS IN SUCH APPLICATIONS IS UNDERSTOOD TO BE FULLY AT THE CUSTOMER’S RISK.In order to minimize risks associated with the customer’s applications, adequate design and operating safeguards must be provided by the customer to minimize inherent or procedural hazards.TI assumes no liability for applications assistance or customer product design. TI does not warrant or represent that any license, either express or implied, is granted under any patent right, copyright, mask work right, or other intellectual property right of TI covering or relating to any combination, machine, or process in which such semiconductor products or services might be or are used. TI’s publication of information regarding any third party’s products or services does not constitute TI’s approval, warranty or endorsement thereof.Copyright © 1999, Texas Instruments IncorporatedThis datasheet has been downloaded from:Free DownloadDaily Updated Database100% Free Datasheet Search Site100% Free IC Replacement Search SiteConvenient Electronic DictionaryFast Search SystemAll Datasheets Cannot Be Modified Without PermissionCopyright © Each Manufacturing Company。

UC3706中文资料

UC2706UC3706Dual Output DriverFEATURES•Dual,1.5A Totem Pole Outputs •40nsec Rise and Fall into 1000pF •Parallel or Push-Pull Operation •Single-Ended to Push-Pull Conversion •High-Speed,Power MOSFET Compatible•Low Cross-Conduction Current Spike •Analog,Latched Shutdown •Internal Deadband Inhibit Circuit •Low Quiescent Current •5to 40V Operation•Thermal Shutdown Protection •16-Pin Dual-In-Line Package •20-Pin Surface Mount PackageDESCRIPTIONThe UC1706family of output drivers are made with a high-speed Schottky process to interface between low-level control functions and high-power switching devices -particularly power MOSFET's.These de-vices implement three generalized functions as outlined below.First:They accept a single-ended,low-current digital input of either polar-ity and process it to activate a pair of high-current,totem pole outputs which can source or sink up to 1.5A each.Second:They provide an optional single-ended to push-pull conversion through the use of an internal flip-flop driven by double-pulse-suppression logic.With the flip-flop disabled,the outputs work in parallel for 3.0A capability.Third:Protection functions are also included for pulse-by-pulse current limiting,automatic deadband control,and thermal shutdown.These devices are available in a two-watt plastic “bat-wing”DIP for op-eration over a 0°C to 70°C temperature range and,with reduced power,in a hermetically sealed cerdip for -55°C to +125°C operation.Also avail-able in surface mount Q and Lpackages.BLOCK DIAGRAMINV N.I OUT H L H LH H L LL H L LOUT =INV and N.I.OUT =INV or N.I.TRUTHTABLE10/98ABSOLUTE MAXIMUM RATINGS.......................................N--Pkg ............J--Pkg Supply Voltage,V IN .........................40V..................40V Collector Supply Voltage,V C ..................40V..................40V Output Current (Each Output,Source or Sink)Steady--State..........................±500mA..............±500mA Peak Transient..........................±1.5A................±1.0A Capacitive Discharge Energy..............20m J .................15m J Digital Inputs ..............................5.5V .................5.5V Analog Stop Inputs.........................V IN ..................V IN Power Dissipation at T A =25°C (See Note).......2W ..................1W Power Dissipation at T (Leads/Case)=25°C......5W ...................2(See Note)Operating Temperature Range ......................--55°C to +125°C Storage Temperature Range........................--65°C to +150°C Lead Temperature (Soldering,10Seconds)................300°CNote:All voltages are with respect to the four ground pins which must be connected together.All currents are positive into,negative out of the specified trerminal.ConsultPackaging sections of the Databook for thermal limitations and considerations of package.CONNECTION DIAGRAMSground.ELECTRICAL CHARACTERISTICS:Unless otherwise stated,these specifications apply for T A =–55°C to +125°C forthe UC1706,–25°C to +85°C for the UC2706and 0°C to +70°C for the UC3706;V IN =V C =20V.T A =T J .PARAMETERSTEST CONDITIONSMINTYP MAX UNITS V IN Supply Current V IN =40V810mA V C Supply Current V C =40V,Outputs Low 45mA V C Leakage Current V IN =0,V C =30V,No Load.050.1mA Digital Input Low Level 0.8V Digital Input High Level 2.2V Input Current V I =0–0.6–1.0mA Input LeakageV I =5V.050.1mAELECTRICAL CHARACTERISTICS:Unless otherwise stated,these specifications apply for T A=–55°C to+125°C for the UC1706,–25°C to+85°C for the UC2706and0°C to+70°C for the UC3706;V IN=V C=20V.T A=T J.PARAMETERS TEST CONDITIONS MIN TYP MAX UNITS Output High Sat.,V C-V O I O=-50mA 2.0VOutput Low Sat.,V O I O=50mA0.4VI O=500mA 2.5VInhibit Threshold V REF=0.5V0.40.6VV REF=3.5V 3.3 3.7V Inhibit Input Current V REF=0–10–20m A Analog Threshold V CM=0to15V100130160mV Input Bias Current V CM=0–10–20m A Thermal Shutdown155°CTYPICAL SWITCHING CHARACTERISTICS:V IN=V C=20V,T A=25°C.Delays measured to10%output change.PARAMETERS TEST CONDITIONS OUTPUT C L=UNITS From Inv.Input to Output:open 1.0 2.2nF Rise Time Delay110130140ns 10%to90%Rise204060ns Fall Time Delay8090110ns 90%to10%Fall253050ns From N.I.Input to Output:Rise Time Delay120130140ns 10%to90%Rise204060ns Fall Time Delay100120130ns 90%to10%Fall253050ns V C Cross-Conduction Current Spike Duration Output Rise25nsOutput Fall0ns Inhibit Delay Inhibit Ref.=1V,Inhibit Inv.=0.5to1.5V250ns Analog Shutdown Delay Stop Non-Inv.=0V,Stop Inv.=0to0.5V180nsCIRCUIT DESCRIPTIONOutputsThe totem-pole outputs have been designed to minimize cross-conduction current spikes while maximizing fast, high-current rise and fall times.Current limiting can be done externally either at the outputs or at the common V C pin.The output diodes included have slow recovery and should be shunted with high-speed external diodes when driving high-frequency inductive loads.Flip/FlopGrounding pin7activates the internal flip-flop to alter-nate the two outputs.With pin7open,the two outputs operate simultaneously and can be paralleled for higher current operation.Since the flip-flop is triggered by the digital input,an off-time of at last200nsec must be pro-vided to allow the flip/flop to change states.Note that the circuit logic is configured such that the“OFF”state is de-fined as the outputs low.Digital InputsWith both an inverting and non-inverting input available, either active-high or active-low signals may be accepted. These are true TTL compatible inputs—the threshold is approximately1.2V with no hysteresis;and external pull-up resistors are not required.Inhibit CircuitAlthough it may have other uses,this circuit is included to eliminate the need for deadband control when driving relatively slow bipolar power transistors.A diode from each inhibit input to the opposite power switch collector will keep one output from turning-on until the other has turned-off.The threshold is determined by the voltage on pin15which can be set from0.5to3.5V.When this cir-cuit is not used,ground pin15and leave1and16open.UC3706CIRCUIT DESCRIPTION(cont.)APPLICATIONSLevel Shifting to Ground Referenced PWMsAnalog ShutdownThis circuit is included to get a latched shutdown as close to the outputs as possible,from a time standpoint.With an internal 130mV threshold,this comparator has a common-mode range from ground to (V IN –3V).When not used,both inputs should be grounded.The time re-quired for this circuit to latch is inversely proportional to the amount of overdrive but reaches a minimum of 180nsec.As with the flip-flop,an input off-time of at least 200nsec is required to reset the latch between pulses.Supply VoltageWith an internal 5V regulator,this circuit is optimized foruse with a 7to 40V supply;however,with some slight re-sponse time degradation,it can also be driven from 5V .When V IN is low,the entire circuit is disabled and no cur-rent is drawn from V C .When combined with a UC1840PWM,the Driver Bias switch can be used to supply V IN to the UC1706.V IN switching should be fast as if V C is high,undefined operation of the outputs may occur with VI N less than 5V .Thermal ConsiderationsShould the chip temperature reach approximately 155°C,a parallel,non--inverting input is activated driving both outputs to the low state.UC3706 APPLICATIONS(cont'd)UNITRODE CORPORA TION7CONTINENTAL BLVD.•MERRIMACK,NH03054TEL.(603)424-2410•FAX(603)424-3460IMPORTANT NOTICETexas Instruments and its subsidiaries (TI) reserve the right to make changes to their products or to discontinue any product or service without notice, and advise customers to obtain the latest version of relevant information to verify, before placing orders, that information being relied on is current and complete. All products are sold subject to the terms and conditions of sale supplied at the time of order acknowledgement, including those pertaining to warranty, patent infringement, and limitation of liability.TI warrants performance of its semiconductor products to the specifications applicable at the time of sale in accordance with TI’s standard warranty. Testing and other quality control techniques are utilized to the extent TI deems necessary to support this warranty. Specific testing of all parameters of each device is not necessarily performed, except those mandated by government requirements.CERTAIN APPLICATIONS USING SEMICONDUCTOR PRODUCTS MAY INVOLVE POTENTIAL RISKS OF DEATH, PERSONAL INJURY, OR SEVERE PROPERTY OR ENVIRONMENTAL DAMAGE (“CRITICAL APPLICATIONS”). TI SEMICONDUCTOR PRODUCTS ARE NOT DESIGNED, AUTHORIZED, OR WARRANTED TO BE SUITABLE FOR USE IN LIFE-SUPPORT DEVICES OR SYSTEMS OR OTHER CRITICAL APPLICATIONS. INCLUSION OF TI PRODUCTS IN SUCH APPLICATIONS IS UNDERSTOOD TO BE FULLY AT THE CUSTOMER’S RISK.In order to minimize risks associated with the customer’s applications, adequate design and operating safeguards must be provided by the customer to minimize inherent or procedural hazards.TI assumes no liability for applications assistance or customer product design. TI does not warrant or represent that any license, either express or implied, is granted under any patent right, copyright, mask work right, or other intellectual property right of TI covering or relating to any combination, machine, or process in which such semiconductor products or services might be or are used. TI’s publication of information regarding any third party’s products or services does not constitute TI’s approval, warranty or endorsement thereof.Copyright © 1999, Texas Instruments Incorporated。

TS-SEN-PD-0007A.0-BF3703 Datasheet