P4C1298-15CC中文资料

LTC1297中文资料

LTC1292D LTC1297D MIN TYP MAX ± 3.0 ± 0.75 ± 4.0 12

UNITS LSB LSB LSB Bits V

±1 ±1 ±1 ±1

±1 ±1 ±1 ±1

±1 ±1 ±1 ±1

2

U

µA µA µA µA

W

U

U

W W

W

元器件交易网

LTC1292/LTC1297 AC CHARACTERISTICS

LTC1292/7 TA01

U

Power Supply Current vs Sampling Frequency

1000 100 10 1 1 10 1k 100 fSAMPLE (Hz) 10k 100k

LTC1297• TA02

UO

U

1

元器件交易网

LTC1292/LTC1297 ABSOLUTE

U U W CO VERTER A D ULTIPLEXER CHARACTERISTICS (Note 3)

PARAMETER Offset Error Linearity Error (INL) Gain Error Minimum Resolution for Which No Missing Codes are Guaranteed Analog and REF Input Range On Channel Leakage Current (Note 8) (Note 7) On Channel = 5V Off Channel = 0V On Channel = 0V Off Channel = 5V Off Channel Lekage Current (Note 8) On Channel = 5V Off Channel = 0V On Channel = 0V Off Channel = 5V

EP4CE15E22C9L中文资料(Altera)中文数据手册「EasyDatasheet - 矽搜」

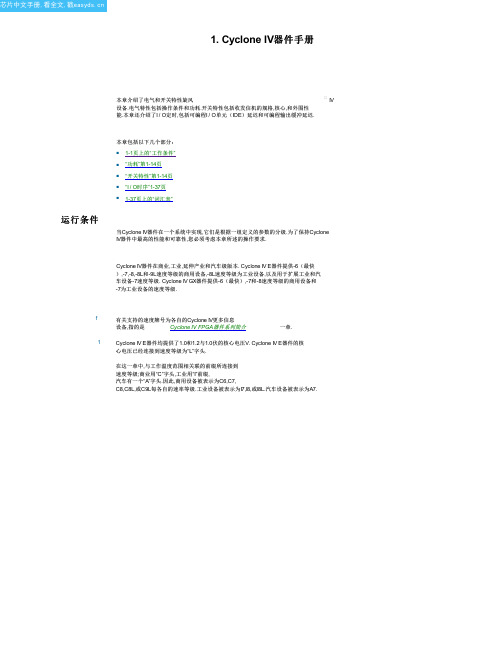

Cyclone IV器件在商业,工业,延伸产业和汽车级版本. Cyclone IV E器件提供-6(最快 ),-7,-8,-8L和-9L速度等级的商用设备,-8L速度等级为工业设备,以及用于扩展工业和汽 车设备-7速度等级. Cyclone IV GX器件提供-6(最快),-7和-8速度等级的商用设备和 -7为工业设备的速度等级.

条件( V)

过冲持续时间为%高时间

Unit

交流输入

Vi

电压

VI = 4.20 VI = 4.25 VI = 4.30 VI = 4.35 VI = 4.40 VI = 4.45 VI = 4.50 VI = 4.55 VI = 4.60

100

%

98

%

65

%

43

%

29

%

20

%

13

%

9

%

6

%

图1-1

示出的方法来确定过冲持续时间.该

芯片中文手册,看全文,戳

1–2

第 1章: Cyclone IV器件手册

运行条件

1

Cyclone IV E工业设备I7提供具有扩展的工作温度范围.

绝对最大额定值

绝对最大额定值规定的最大工作条件Cyclone IV器件.该值是基于与所述设备和击穿和损伤 机理理论模型进行的实验.该装置的功能操作不在这些条件暗示.

从的Cyclone IV E和Cyclone IV GX器件的预期值.所有物资必须是没有高原严格单调.

表 1-3.推荐工作条件 Cyclone IV E器件

符

参数

VCCINT (3) VCCIO (3), (4) VCCA (3)

电源电压为内部逻辑, 1.2-V操作

CD4690资料

BACKSIDE IS CATHODE

FIGURE 1

DESIGN DATA

METALLIZATION: Top: (Anode).....................Al Back: (Cathode)................Au AL THICKNESS....... ......25,000 Å Min GOLD THICKNESS..........4,000 Å Min CHIP THICKNESS....................10 Mils CIRCUIT LAYOUT DATA: For Zener operation, cathode must be operated positive with respect to anode. TOLERANCES: ALL Dimensions + 2 mils

CD4678 thru CD4717

23 MILS 15 MILS

µA

50 50 50 50 50 50 50 50 50 50 50 50 50 50 50 50 50 50 50 50 50 50 50 50 50 50 50 50 50 50 50 50 50 50 50 50 50 50 50 50

NOTE 1

The JEDEC type numbers shown above have a standard tolerance of + 5% oF the nominal Zener voltage. Vz is measured with the diode in thermal equilibrium at 25°C + 3°C. VZ @ 100 µ A minus VZ @ 10µ A. Zener voltage is read using a pulse measurement, 10 milliseconds maximum.

L-HPC中文手册(日本信越Shinetsu)

0.55

3.6 53

8 115000 660 挤压制粒,药物层积 (有时崩解优于 LH-31 )

LH-B1 . 不含纤 55 维

0.48

0.69

2.5 40 11 140000 790 流化床制粒,高剂量 处方直接压片

详细说明见本册 20 页。

6

外观 白色略带微黄粉末 真实密度 1.3g/m 3 ( 用氦比重计测得 ) 溶解性 不溶于水部分溶于有机溶剂 在水中膨胀 溶于 10% 的氢氧化钠溶液,呈混浊的粘性液体 热解温度 大约 290 ℃

80

75

崩解时间

35.5

L-HPC(LH-21)

-

5

硬脂酸镁

0.5

0.5

有 L-HPC 7.8 8.6

直接压片的最终结果(在片剂含量为 40% )

目前的产品( LH-21 )的性能与微晶纤维素的标准型号一样好,甚至超越了微晶纤维素。在高速旋转过程 中, LH-21 显示出很高的片重差别, LH-B1 和高密度型号微晶纤维素相似,片重差不大。

14

在湿法制粒中, L-HPC 在制软材过程中能起到缓释作用而适合广泛的水分含量。 LH-21 的特色被应用于 此。特别是低溶解性和低吸湿度的活性组分,可以用大量的 L-HPC 来改善崩解性。而在制片过程中用 20%-40% 的 L-HPC 也是为了此目的——如此高的含量,对于稳定性影响不大,而离子性的崩解剂就不同了。 如此应用,片剂崩解成很好的个体颗粒,这样就可以快速、完全溶解。

径

度(μ ( g/mL ) ( g/mL ) 纵横 安 氧基

合

表

m)

比 息 含量

度

观

角

典型应用

LH-11 . 多纤维 55

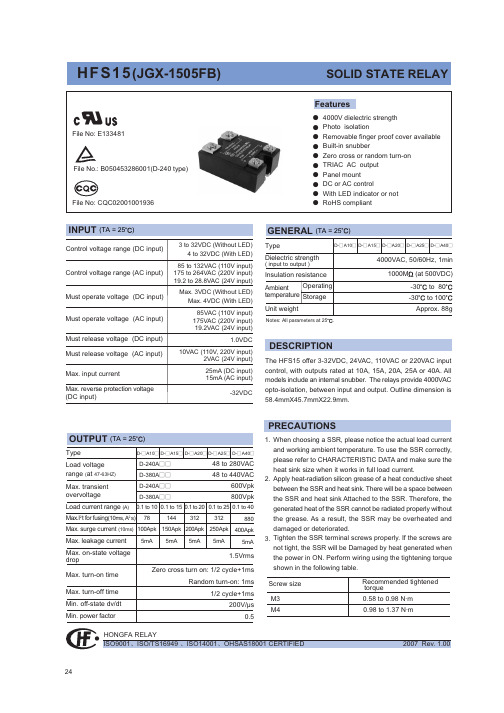

HFS15中文资料

64

54 9 4

T`k_flk G\Xk P`eb

164

4

64

84

:4

<4

544

174 164

4

64

84

:4

<4

544

@dY`\ek Q\dg\iXkli\ - .

@dY`\ek Q\dg\iXkli\ - .

C`jZcX`d\i

Q_`j [XkXj_\\k `j ]fi k_\ Zljkfd\ijv i\]\i\eZ\2 @cc k_\ jg\Z`]`ZXk`fej Xi\ jlYa\Zk kf Z_Xe^\ n`k_flk efk`Z\2 T\ Zflc[ efk \mXclXk\ Xcc k_\ g\i]fidXeZ\ Xe[ Xcc k_\ gXiXd\k\ij ]fi \m\ip gfjj`Yc\ Xggc`ZXk`fe2 Q_lj k_\ lj\i j_flc[ Y\ `e X i`^_k gfj`k`fe kf Z_ffj\ k_\ jl`kXYc\ gif[lZk ]fi k_\`i fne Xggc`ZXk`fe2 H] k_\i\ `j Xep hl\ip0 gc\Xj\ ZfekXZk Gfe^]X ]fi k_\ k\Z_e`ZXc j\im`Z\2 Gfn\m\i0 `k `j k_\ lj\ivj i\jgfej`Y`c`kp kf [\k\id`e\ n_`Z_ gif[lZk j_flc[ Y\ lj\[ fecp2

644

4

174 164

4

64

84

:4

<4

544

KldY\i f] ZpZc\j -Xk 94Gq.

@dY`\ek Q\dg\iXkli\ - .

ADS1298中文版及常见问题资料

ADS1298 用于生物电位测量的低功率,8通道,24位模拟前端威尔逊中心电位(WCT)和胸导在标准的ECG 12导联中,定义WCT电压为右肢(RA),左肢(LA),和左腿(LL)电极的平均值。

这个电平用作胸导测量的参考电平。

ADS1294/6/8有三个内置低噪声运放产生WCT电平。

图47所示为实现框图。

芯片提供灵活的选择方式从八个信号(IN1P-IN4N)中任意选取一个输入到运放产生电平。

因此允许RA,LA,和LL电极根据导联结构连接到前四通道任意输入。

WCT电路的三个运放可通过寄存器设置独立掉电。

使两个运放上电,可在WCT脚产生任意两个电极的平均电平。

一个运放上电可提供WCT脚的缓冲电极电平。

注意:WCT 运放有驱动强度限制所以需要使用缓冲如果用来驱动一个低阻抗负载。

当使用WCT缓冲中任意1,2或3个查看表5的性能指标。

如表5所示,当超过一个WCT运放掉电总噪声降低。

噪声降低是由于噪声平均值被运放输出端网络结构影响。

单个缓冲掉电节省的功率可忽略不计因为主电路结构是三个运放共用的。

WCT节点的带宽被RC网络限制。

这个内部共用网络由三个30K电阻和一个80pF 电容组成。

需要说明的是要达到最佳性能要在外部增加100pF电容。

如表5所示,有效带宽取决于掉电运放数目。

WCT只能用来驱动非常高阻抗的输入(通常大于500M)。

典型应用是将WCT信号接入ADS1294/6/8的反相输入作为胸导信号参考。

如前文所提,三个WCT运放可以连接八个模拟输入的任意一个。

运放的输入信号被斩波取样,其斩波频率随ADS1294/6/8的数据速率而变。

斩波频率与最大数据速率比为1:1。

例如:数据速率为32kSPS时,斩波频率是32KHz。

斩波频率在数据速率为四个比较低的等级时(即4kSPS,2kSPS,1kSPS,500SPS)固定为4KHz。

斩波频率在WCT运放输出端显示为基于直流电平的一个小方波。

方波的幅度是运放的偏移电压典型值是5mVpp。

CY7C1399-15ZI中文资料

2

元器件交易网

CY7C1399

Electrical Characteristics Over the Operating Range(continued)

7C1399–25 Parameter VOH VOL VIH VIL IIX IOZ IOS ICC ISB1 Description Output HIGH Voltage Output LOW Voltage Input HIGH Voltage Input LOW Voltage Input Load Current Output Leakage Current Output Short Circuit Current[2] VCC Operating Supply Current Automatic CE Power-Down Current — TTL Inputs Automatic CE Power-Down Current — CMOS Inputs[3] GND ≤ VI ≤ VCC, Output Disabled VCC = Max., VOUT = GND VCC = Max., IOUT = 0 mA, f = fMAX = 1/tRC Max. V CC, CE ≥ VIH, VIN ≥ VIH, or VIN ≤ VIL, f = fMAX Max. VCC, CE ≥ VCC–0.3V, VIN ≥ VCC – 0.3V, or VIN ≤ 0.3V, WE≥VCC–0.3V or WE≤ 0.3V, f=fMAX L Test Conditions VCC = Min., IOH = –2.0 mA VCC = Min., IOL = 4.0 mA 2.2 –0.3 –1 –5 Min. 2.4 0.4 VCC +0.3V 0.8 +1 +5 –300 45 5 3 500 L 50 2.2 –0.3 –1 –5 Max. 7C1399–35 Min. 2.4 0.4 VCC +0.3V 0.8 +1 +5 –300 40 5 3 500 50 Max. Unit V V V V µA µA mA mA mA mA µA µA

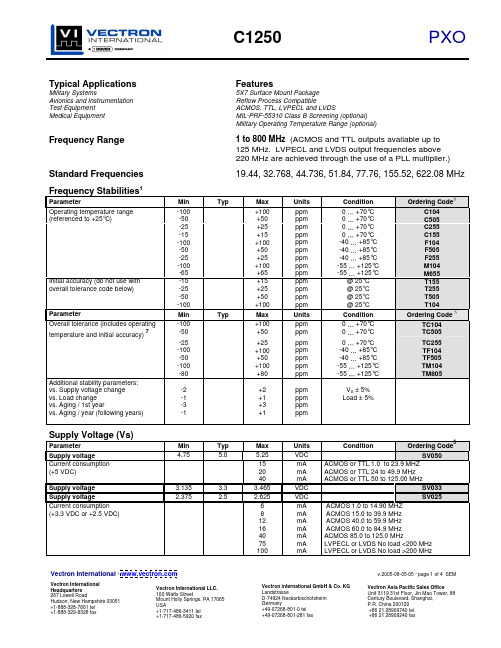

C1250资料

Vectron International· v.2005-08-05-05 · page 1 of 4 SEMVectron International Frequency Range1 to 800 MHz (ACMOS and TTL outputs available up to 125 MHz. LVPECL and LVDS output frequencies above 220 MHz are achieved through the use of a PLL multiplier.)Standard Frequencies 19.44, 32.768, 44.736, 51.84, 77.76, 155.52, 622.08 MHzFrequency Stabilities 1ParameterMin TypMax Units Condition Ordering Code5Operating temperature range -100 +100 ppm 0 +70°C C104 (referenced to +25°C)-50 +50 ppm 0 +70°C C505 -25 +25 ppm 0 +70°C C255 -15 +15 ppm 0 +70°C C155 -100 +100 ppm -40 +85°C F104 -50 +50 ppm -40 +85°C F505 -25 +25 ppm -40 +85°C F255 -100 +100 ppm -55 +125°C M104 -65 +65 ppm -55 +125°C M655 Initial accuracy (do not use with -15 +15 ppm @ 25°C T155 overall tolerance code below)-25 +25 ppm @ 25°C T255 -50 +50 ppm @ 25°C T505 -100 +100 ppm @ 25°C T104ParameterMin TypMax Units Condition Ordering Code5Overall tolerance (includes operating -100 +100 ppm 0 +70°C TC104 temperature and initial accuracy)7-50 +50 ppm 0 +70°C TC505-25 +25 ppm 0 +70°C TC255 -100 +100 ppm -40 +85°C TF104 -50 +50 ppm -40 +85°C TF505 -100 +100 ppm -55 +125°C TM104 -80+80 ppm -55 +125°C TM805Additional stability parameters: vs. Supply voltage change vs. Load change vs. Aging / 1st yearvs. Aging / year (following years)-2 -1 -3 -1+2 +1 +3 +1ppm ppm ppm ppmV S ± 5% Load ± 5%Supply Voltage (Vs)ParameterMin Typ Max Units ConditionOrdering Code5Supply voltage4.755.05.25 VDC SV050Current consumption 15 mA ACMOS or TTL 1.0 to 23.9 MHZ (+5 VDC)20 mA ACMOS or TTL 24 to 49.9 MHz 40 mA ACMOS or TTL 50 to 125.00 MHzSupply voltage 3.135 3.3 3.465 VDC SV033 Supply voltage2.375 2.52.625 VDC SV025Current consumption 6 mA ACMOS 1.0 to 14.90 MHZ (+3.3 VDC or +2.5 VDC)8 mA ACMOS 15.0 to 39.9 MHz 12 mA ACMOS 40.0 to 59.9 MHz 16 mA ACMOS 60.0 to 84.9 MHz 40 mA ACMOS 85.0 to 125.0 MHz75 mA LVPECL or LVDS No load <200 MHz 100mALVPECL or LVDS No load >200 MHzTypical ApplicationsFeaturesMilitary Systems5X7 Surface Mount Package Avionics and Instrumentation Reflow Process CompatibleTest Equipment ACMOS, TTL, LVPECL and LVDSMedical EquipmentMIL-PRF-55310 Class B Screening (optional) Military Operating Temperature Range (optional)Vectron International· v.2005-08-05-05 · page 2 of 4 SEMVectron International RF OutputParameterMinTyp MaxUnits ConditionOrdering Code5Signal ACMOSRFALoad1550 pF Signal Level (Vol) 0.5 VDC Vs= 5.0V and 15pF load 0.3 VDC Vs=3.3V and 15pF load 0.25VDC Vs=2.5V and 15pF load Signal Level (Voh)4.5 VDC Vs=5.0V and 15pF load 3.0 VDC Vs=3.3V and 15pF load 2.25VDC Vs=2.5V and 15pF loadRise and fall times for ACMOS (measured 10% to 90%) 10 6 3 ns ns ns 1.0 to 23.9 MHz 24.0 to 79.9 MHz 80.0 to 125.0MHz Duty cycle 45 4055 60% %@ 50% Vs< 15 MHz @ 50% Vs > 15 MHzSignal TTLRFT Load10 Signal Level (Vol) 0.5VDC Vs= 5.0V and 15pF load Signal Level (Voh)4.5VDC Vs= 5.0V and 15pF loadRise and fall times for TTL (measured 0.8V to 2.0V) 5 3 ns ns 1.0 to 23.9 MHz 24 to 125 MHz Duty Cycle45 4055 60% % @ 1.4V < 15 MHz @ 1.4V > 15 MHzSignal LVPECLRFPLoad50 Into Vcc-2V or Thevenin Equivalent Signal Level (Vol) Vs -1.62VDC -40 +85°C operating temp Signal Level (Voh)Vs- 1.025VDC -40 +85°C operating tempRise and fall times (measured @ 20% to 80%)1000 600 ps ps <100 MHz > 100 MHz Duty cycle LVPECL 4555 % @ 50% VddJitter (rms) 10 0.5 ps ps BW = 10Hz to 20 MHz BW = 12 kHz to 20 MHz Period Jitter (pk-pk) 40ps10,000 Samples - Rising edgeSignal LVDSRFLLoad60100 140Between outputsSignal Level (Vol)1.2 VDC Signal Level (Voh)1.4 VDC Differential Voltage (Vod)240 330 460 mVpeakCommon Mode (Offset) Voltage (Vos) 1.1251.2 1.375 V Start-up Time10 mS Rise and fall times 6001000 ps measured @ 20% to 80% of VodDuty cycle 4555 % @ 50% of Vod Jitter (rms) 5 1 ps ps BW = 10Hz to 20 MHz BW = 12 kHz to 20 MHz Period Jitter (pk-pk)40ps 10,000 Samples - Rising edgeAdditional ParametersScreening Vectron Verification9V Screening Class B, MIL-PRF-55310, Rev.D BOutput Enable6Logic "0" input = Outputs disabled (Tri-state)Logic "1" or floating input = Outputs enabled ) Standard (All outputs)Logic "0" or floating input = Outputs enabledLogic "1" input = Outputs disabled (Tri-state )Custom (Contact factory for availability)Weight< 2 gramsProcessing & PackingHandling & processing noteVectron International· v.2005-08-05-05 · page 3 of 4 SEMVectron International Standard EnvironmentalsParameterTest ConditionVibration MIL-STD-202, Method 204, Condition G (30 G, 10Hz-2000Hz) ShockMIL-STD-202, Method 213, Condition I (100 G, 6ms, Sawtooth) AccelerationMIL-STD-883, Method 2001, Condition A (5000 G, Y1 Plane)Temperature Cycling MIL-STD-883, Method 1010, Condition B Thermal Shock MIL-STD-883, Method 107, Condition BSolderabilityMIL-STD-202, Method 208Leak Test (Fine and Gross)MIL-STD-883, Method 1014, Condition A1 and C1Absolute Maximum RatingsParameterMinTypMax Units Condition Supply voltage (Vs) 7.0 V Vs=5.0VDC 7.0 V Vs=3.3VDCOperable temperature range -55 +125 °C Storage temperature range-62+125°CEnclosuresType A ACMOS or TTLType B LVPECL or LVDSPackage Codes:CodesHeight CodesHeight A1 = 4 leads0.074 ± 0.007 B1 = 6 leads0.074 ± 0.007 E1 = Enable/Disable pin 1 (1.88 ± 0.178) E1 = Enable/Disable pin 1 (1.88 ± 0.178)X = N/C pin 1 E2 = Enable/Disable pin 2 X = N/C pin 1 and pin 2 T = Tinned J leads 8T = Tinned J leads 8X = No TinningX = No TinningPin ConnectionsPin Connections1 Enable/Disable or N/C 3 RF Output 1 Enable/Disable or N/C4 RF Output2 Ground (case) 4 Supply Voltage2 N/C5 Complementary Output 3 Ground (Case)6 Supply VoltageVectron International· v.2005-08-05-05 · page 4 of 4 SEMVectron InternationalHow to Order this Product: 10Step 1Use this worksheet to forward the following information to your factory representative (example follows):ModelStabilityCodeInitial AccuracyCode(if required)Supply Voltage Code RF Output Code Screening Code Package Code Enable/DisableCodeTinning CodeC1250 C505 T505SV033RFAVA1E1TStep 2The factory representative will then respond with a Vectron Part Number in the following configuration: Model Package CodeDash Dash NumberC1250[Customer Specified Package Code]-[Factory Generated 4 digit number]Typical P/N C1250A1-0001Notes:1Contact factory for improved stabilities or additional product options. Not all options and codes are available at all frequencies, RF outputs and supply voltages.2Unless otherwise stated all values are valid after warm-up time and refer to typical conditions for supply voltage, frequency control voltage, load, temperature (25°C).3Phase noise degrades with increasing output frequency. 4Subject to technical modification. 5Contact factory for availability. 6Contact factory for other options.7Overall stabilities do not require an initial accuracy code.8Leads tinned IAW Vectron International standard procedure (GR-37409). 9Vectron Verification IAW Vectron International standard process (HK-69314). 10Please be sure to specify nominal frequency.。

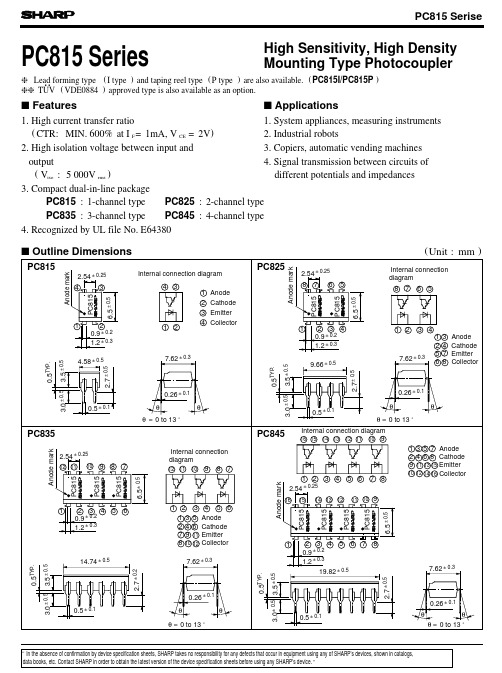

PC815中文资料

Fig. 9 Collector Dark Current vs.

Ambient Temperature

10 - 4

gg TUV ( VDE0884 ) approved type is also available as an option.

s Features

s Applications

1. High current transfer ratio

1. System appliances, measuring instruments

PC815 Series

s Absolute Maximum Ratings

Input Output

Parameter Forward current *1Peak forward current Reverse voltage Power dissipation Collector-emitter voltage Emitter-collector voltage Collector current Collector power dissipation Total power dissipation *2 Isolation voltage Operating temperature Storage temperature *3Soldering temperature

4. Recognized by UL file No. E64380

s Outline Dimensions

Anode mark PC815 6.5 ± 0.5

PC815

2.54 ± 0.25

4

3

1

2

0.9 ± 0.2

1.2 ± 0.3

Internal connection diagram

FPGA可编程逻辑器件芯片EP4CE115F29C8L中文规格书

Mode 0 (continuous frame mode) is popular for camera pipe operation. Often, the camera pipe is enabled statically, and updates to the coefficients are only required from time to time. On demand software may enable the configuration DMA in stop mode to trigger the fetch of one single BCL. In this mode, the PVP_IPFn_TAG register is useful to match status results with a respective configuration. The new BCL only updates coefficients of processing blocks. The BCL does not alter the pipe configuration.Mode 1 (back-to-back mode) is useful in camera pipe mode when coefficients have to change every N th frame. This mode supports on-the-fly reprogramming of coefficients, but it does not support on-the-fly reprogramming of pipe configurations. The following settings must not change unless the DRAIN bit is set:•Pipe structure (PVP_xxx_CFG registers)•Fundamental operating modes (such as 1st-derivative to 2nd-derivative mode of PEC)•Input format and OPORT configuration (PVP_IPFn_CTL registers)•Horizontal size of input frame (HCNT)If any of the above settings change on-the-fly, the PVP_IPFn_PIPECTL.DRAIN bit must be set for proper operation to use Mode 2. In memory pipe mode, the PVP_IPFn_PIPECTL.DRAIN bit causes of few clock cycles of overhead depending to pipeline depth. In camera pipe mode, the PVP_IPFn_PIPECTL.DRAIN bit causes the loss of an entire frame. Operation stops after the pipe has been drained and resumes with the next incoming VSYNC signal.Whenever the next PVP job stalls until the completion event of the data output DMA is flagged either as an interrupt or as a system trigger, setting the PVP_IPFn_PIPECTL.DRAIN bit is a requirement at the appli-cation level. The data output DMA work unit does not complete as long as related data sticks in the pipe. The data in the pipe does not progress until the configuration DMA and data source grant. Such deadlock situations can be avoided by using Mode 2. Once a deadlock occurs, it can be resolved by Mode 3 opera-tion.Mode 3 (drain now instruction) is more similar to a one-time instruction than an operating mode. This mode is used whenever software needs to respond to unpredictable events. For example, while the camera >01Mode 2: Auto-Completion ModeFCNT frames are requested by the IPFn, and these feed the pipe. The last datawords are automatically pushed out, and the operation automatically completes.If a new configuration is granted by DMA or by MMR writes, the configuration isapplied for the next FCNT set of frames.All processing blocks auto-disable. A new configuration must set all wanted STARTbits again.01Mode 3: Drain Now InstructionThis combination instructs the IPFn to flush all content out of the pipe.All processing blocks auto-disable. A new configuration must set all wanted STARTbits again.Table 30-47:Operating Modes by FCNT and DRAIN Selections (Continued)FCNT DRAINModeConfiguring with Daisy Chain MethodConfiguration and coefficient memory mapped registers (MMRs) of all processing blocks are double buff-ered. Whenever PVP_IPFn_FCNT is zero and the PVP_IPF0_CFG.START and PVP_IPF1_CFG.START bits =1, the values are copied from MMR registers into application buffers at the frame boundary. Due to the pipe-lined nature of the PVP, not all values are copied at the same time. Rather, the timing of value copying is closely related to how the VSYNC of the next frame progresses through the pipe. New settings apply to the first pixel of the new frame immediately after the last pixel of the old frame has been processed. The update command is daisy chained through the pipe, starting from the IPFn blocks through to the OPFn blocks. While sequencing through the daisy chain operation, hardware clears the PVP_xxx_CFG.START bits of all involved processing blocks in MMR space. Write conflicts can occur if software attempts to write the PVP_xxx_CFG registers during the daisy chain operation.The PVP_STAT register provides two status bits that report whether a daisy chain operation is ongoing in the camera pipes (PVP_STAT.CPDC ) or in the memory pipe (PVP_STAT.MPDC ). These bits are set along with the PVP_IPF0_CFG.START or PVP_IPF1_CFG.START bit and are cleared if the output formatters have been updated.In camera pipe mode, the PVP_STAT.CPDC bit is cleared only after the daisy chain progresses through the furthest of the enabled OPFn blocks. During this time, software should not write the PVP registers. If soft-ware mistakenly does write to these registers, the event is reported by the PVP_STAT.CPWRERR and PVP_STAT.MPWRERR flags. While all status bits in the PVP_STAT register are self clearing, the PVP_ILAT register latches the events until cleared by a software handshake.A PVP block which is enabled in either the camera pipe or memory pipe can be moved to the other pipe only after the drain done command is received for the former pipe. This restriction ensures that the PVP completely processes all the pixels in one pipe and disables the PVP block, before the PVP is enables the PVP block for pixel processing in the next pipe.NOTE :Camera pipes and memory pipes can be configured by MMR writes or BCL fetches. These are sepa-rate control mechanisms and are not intended to be mixed for a given pipe during ongoing opera-tion. Before switching from one method to the other, inspect the daisy chain and drain status bits in the PVP_STAT register to ensure no operation from the other method is pending.PMA5ACU7PEC2x HCNT + 11 if 2nd derivative mode with ZCRSS=0, otherwise 1xHCNT + 6IIMn6UDS varies with settingsTable 30-48:Block Latencies (Continued)PVP Block Latency [Data Clocks]P IPELINED V ISION P ROCESSOR (PVP)P ROGRAMMING M ODELto handle the three data flows, BCS, data IN, data OUT, and optionally status data OUT. If the descrip-tors are all completed by the core, multiple PVP memory pipe jobs can be chained without any further core intervention as the DMA operations run through the chained lists and handle the multiple dataflows autonomously. The following description assumes the memory pipe is inactive, (a non initialized state PVP_CTL.MPEN =0).To run a PVP memory pipe job from the PVP memory pipe job list, the PVP first loads the memorypipe configuration into the respective shadow registers of the respective PCP elements to build the PVP memory pipe. The configuration within the shadow register is activated (transferred from shadowregister to active register) using hardware triggers (staggered transfer). This configuration stream into the shadow registers is handled by DMA 45 which is controlled by a linked descriptor list. The last valid descriptor must contain a DMA_CFG.FLOW field =0 (STOP Mode) to gracefully stop the DMA 45 aftercompleting the PVP memory pipe job list and avoid loading non valid data into PVP memory pipeconfiguration register. All DMA_CFG descriptor fields within the linked list have DMA_CFG.FLOW =6 or =7 (descriptor list mode) or alternatively DMA_CFG.FLOW =4 (descriptor array mode).A 1-dimensional DMA operation is shown in the following figure. Note however, a 2-dimensionalDMA operation can also be used.Figure 30-55:Static Linked Descriptor List for Configuration Data (BCL Data)•Job List Global TriggerAfter the first initialization of the linked descriptor list the parameter registers of DMA 45 have to beinitialized, particularly the DMA_DSCPTR_NXT and DMA_CFG register. The DMA 45 is started but thenstalls until the PVP memory pipe is enabled and the PVP_IPFn_FCNT =0.To generate a unique synchronization signal that synchronizes the Data Out (DMA 42) and Data In(DMA 43) stream, all DMA_CFG descriptor fields of DMA 45 should have the bit field DMA_CFG.TRIG =1.This generates a trigger signal after a new configuration is loaded into the shadow registers.•Job List StartAfter setting up the three DMA linked lists, the memory pipe has to be activated (PVP_CTL.MPEN =1).。

PSL620C技术说明书V4.3

国电南自Q/GDNZ.J.01.72-2000标准备案号:1539- 2000PSL 620C系列数字式线路保护技术说明书国电动份GUODIAN NANJING AUTOMATION CO.,LTDPSL620C数字式线路保护装置技术说明书V4.30国电南京自动化股份有限公司2005年12月版本声明本技术说明书适用于以下版本的保护程序:PSL621C距离保护版本: 4.53PSL621C零序重合闸保护版本: 4.52PSL622C高频保护版本: 4.10PSL623C过流零序重合闸保护版本: 4.53PSL626C过流距离重合闸保护版本: 2.82PSL627C过流重合闸保护版本: 2.82产品说明书版本修改记录表1098765432 V4.3 增加具备双以太网通信口(或三以太网)、RS485串行通信口、V4.52 2005.12 就地打印串行通讯口、PSView调试分析软件串行通讯口1 V4.0 增加装置整体结构图、面板布置图、结构安装图等 V4.50 2003.9 序号 说明书版本修 改 摘 要 软件版本号 修改日期* 技术支持:电话(025)51183140传真(025)51183144* 本说明书可能会被修改,请注意核对实际产品与说明书的版本是否相符* 2005年12月 第1版 第1次印刷目 录1 概述 (1)1.1适用范围 (1)1.2功能配置及型号 (1)1.3性能特点 (1)2 技术性能及指标 (3)2.1额定电气参数 (3)2.2技术性能及指标 (3)2.3环境条件 (4)2.4绝缘性能 (4)2.5电磁兼容性能 (5)2.6机械性能 (5)3 PSL621C线路保护装置 (6)3.1功能及原理 (6)3.1.1 启动元件 (6)3.1.2 选相元件 (6)3.1.3 距离保护 (6)3.1.4 零序保护 (12)3.1.5 重合闸继电器 (14)3.1.6 失灵启动 (16)3.1.7 合闸加速保护 (16)3.1.8 交流电压电流异常判断 (17)3.1.9 过流保护 (18)3.1.10 低周减载、低压减载 (18)3.2硬件构成 (20)3.2.1 硬件配置 (20)3.2.2 各模件说明 (22)3.3定值与整定 (31)3.3.1 装置整定项目与有关参数整定范围 (31)3.3.2 整定计算及整定方法简介 (33)4 PSL622C线路保护装置 (37)4.1功能及原理 (37)4.1.1 高频保护 (37)4.2硬件构成 (44)4.2.1 硬件配置 (44)4.2.2 各模件说明 (45)4.3定值与整定 (46)4.3.1 装置整定项目与有关参数整定范围 (46)4.3.2 整定计算及整定方法简介 (47)5 PSL623C线路保护装置 (49)5.1功能及原理 (49)5.2硬件构成 (50)5.2.1 硬件配置 (50)5.2.2 各模件说明 (51)5.3定值与整定 (52)5.3.1 装置整定项目与有关参数整定范围 (52)5.3.2 整定计算及整定方法简介 (54)6 PSL626C 线路保护装置 (56)6.1功能及原理 (56)6.2硬件构成 (60)6.2.1 硬件配置 (60)6.2.2 各模件说明 (61)6.3定值与整定 (65)6.3.1 装置整定项目与有关参数整定范围 (65)6.3.2 整定计算及整定方法简介 (66)7 PSL627C 线路保护装置 (69)7.1功能及原理 (69)7.2硬件构成 (70)7.2.1 硬件配置 (70)7.2.2 各模件说明 (71)7.3定值清单及整定说明 (72)7.3.1 装置整定项目与有关参数整定范围 (72)7.3.2 整定计算及整定方法简介 (73)8 信息记录和分析 (75)9 与变电站自动化系统配合 (75)10 事件信息一览表 (76)1 概述1.1 适用范围PSL 620C系列数字式线路保护装置是以距离保护、零序保护和三相一次重合闸为基本配置的成套线路保护装置,并集成了电压切换箱和三相操作箱,适用于110KV、66KV或35KV输配电线路。

CA42中英文对照规格书全正文(新) FREE

修改记录Revision Record目录CATALOG1.适用范围Scope (3)2.产品代码说明 Product identification (3)3.规格范围 The range of the specification (3)4.电性参数检测标准、检测条件及其温度特性Temperature characteristic (4)5.形状及尺寸 Appearance & Dimensions (4)6.标志 Marking (5)7.容量范围、壳号The range of the capacitance and case (5)8.可靠性试验Reliable performance (6)9.无铅产品识别标识The lead-free product identifying label 710.特性曲线Typical Characteristic curve (7)11.包装Packing (9)12.安装方法 The method of mounting (12)13.使用注意事项Note in use (12)14.贮存 Storage (13)15.订货资料 Ordering information (13)1. 适用范围Scope本规格书适用于树脂包封固体电解质钽电容器(无铅)。

This specification applies to Epoxy-coated Solid Electrolytic Tantalum Capacitors (LEAD FREE ).2.产品代码说明 Product identification⑴ ⑵⑶ ⑷⑸ ⑹⑺说明Explain :⑴企业代码company logo ⑵产品型号series: CA42表示树脂包封固体电解质钽电容器的型号.CA42 representseries number of epoxy-coated solid electrolytic tantalum capacitors⑶容 量capacitance code :容量用皮法拉表示,前两位数字是有效数字,第三位数字是跟随零的个数。

LT6604IUFF-15#PBF,LT6604CUFF-15#PBF,LT6604CUFF-15#TRPBF,LT6604IUFF-15#TRPBF, 规格书,Datasheet 资料

T YPICAL APPLICATIOND ESCRIPTION Differential Amplifi er and15MHz Lowpass FilterThe LT ®6604-15 consists of two matched, fully differential amplifi ers, each with a 4th order, 15MHz lowpass fi lter. The fi xed frequency lowpass fi lter approximates a Chebyshev response. By integrating a fi lter and a differential ampli-fi er, distortion and noise are made exceptionally low. At unity gain, the measured in band signal-to-noise ratio is an impressive 76dB. At higher gains, the input referred noise decreases, allowing the part to process smaller input differential signals without signifi cantly degrading the signal-to-noise ratio.Gain and phase are highly matched between the two chan-nels. Gain for each channel is independently programmed using two external resistors. The LT6604-15 enables level shifting by providing an adjustable output common mode voltage, making it ideal for directly interfacing to ADCs.The LT6604-15 is fully specifi ed for 3V operation. The differential design enables outstanding performance at a 2V P-P signal level for a single 3V supply. See the back page of this datasheet for a complete list of related single and dual differential amplifi ers with integrated 2.5MHz to 20MHz lowpass fi lters.Channel to Channel Gain MatchingF EATURESA PPLICATIONS nDual Differential Amplifi er with 15MHz Lowpass Filters 4th Order Filters Approximates Chebyshev Response Guaranteed Phase and Gain Matching Resistor-Programmable Differential Gain n 76dB Signal-to-Noise (3V Supply, 2V P-P Output)n Low Distortion, 2V P-P , 800Ω Load, V S = 3V 1MHz: 86dBc 2nd, 90dBc 3rd 10MHz: 63dBc 2nd, 69dBc 3rd n Specifi ed for Operation with 3V , 5V and ±5V Supplies n Fully Differential Inputs and Outputsn Adjustable Output Common Mode Voltage n Small 4mm × 7mm × 0.75mm QFN PackagenDual Differential ADC Driver Plus Filter n Single-Ended to Differential Converter n Matched, Dual, Differential Filter Stagen Common Mode T ranslation of Differential Signals nHigh Speed ADC Antialiasing and DAC Smoothing in Wireless Infrastructure or Networking Applications n High Speed Test and Measurement Equipment n Medical ImagingL , L T , L TC and L TM are registered trademarks of Linear Technology Corporation. All other trademarks are the property of their respective owners.+––0.2512160.15660415 TA01b841014620–0.2–0.1–0.150.05–0.050.10.200.25GAIN MATCH (dB)LT6604-15P IN CONFIGURATIONA BSOLUTE MAXIMUM RATINGS Total Supply Voltage .................................................11V Operating Temperature Range (Note 6)....–40°C to 85°C Specifi ed Temperature Range (Note 7) ....–40°C to 85°C Junction Temperature ...........................................150°C Storage Temperature Range ...................–65°C to 150°C Input Current+IN, –IN, V OCM , V MID (Note 8) .........................±10mA Lead Temperature (Soldering, 10 sec) ..................300°CPARAMETERCONDITIONSMIN TYP MAX UNITS Filter Gain Either Channel, V S = 3VV IN = 2V P-P , f IN = DC to 260kHzV IN = 2V P-P , f IN =1.5MHz (Gain Relative to 260kHz)V IN = 2V P-P , f IN = 7.5MHz (Gain Relative to 260kHz)V IN = 2V P-P , f IN = 12MHz (Gain Relative to 260kHz)V IN = 2V P-P , f IN = 15MHz (Gain Relative to 260kHz)V IN = 2V P-P , f IN = 45MHz (Gain Relative to 260kHz)V IN = 2V P-P , f IN = 75MHz (Gain Relative to 260kHz)l l l l l l–0.5–0.1–0.3–0.3–0.70.1000.20–29–460.50.10.41.01.0–25dB dB dB dB dB dB dBORDER INFORMATIONLEAD FREE FINISH TAPE AND REEL PART MARKING*PACKAGE DESCRIPTIONSPECIFIED TEMPERATURE RANGE L T6604CUFF-15#PBF L T6604CUFF-15#TRPBF 6041534-Lead (4mm × 7mm) Plastic QFN 0°C to 70°C L T6604IUFF-15#PBFL T6604IUFF-15#TRPBF6041534-Lead (4mm × 7mm) Plastic QFN–40°C to 85°CConsult L TC Marketing for parts specifi ed with wider operating temperature ranges. *The temperature grade is identifi ed by a label on the shipping container.Consult L TC Marketing for information on non-standard lead based fi nish parts.For more information on lead free part marking, go to: http://www.linear .com/leadfree/ For more information on tape and reel specifi cations, go to: http://www.linear .com/tapeandreel/E LECTRICAL CHARACTERISTICS The l denotes specifi cations that apply over the full operating temperaturerange, otherwise specifi cations are at T A = 25°C. Unless otherwise specifi ed V S = 5V (V + = 5V , V –= 0V), R IN = 536Ω, and R LOAD = 1k.31 V –32 V –33 N C34 V M I D AV +B 17N C 16N C 15V O C M B 1430 NC 29 –OUTA 28 NC 27 +OUTA 26 NC 25 V +A 24 V –23 NC 22 NC 21 –OUTB 20 NC 19 +OUTB 18 NCNC 1+INA 2NC 3–INA 4NC 5V OCMA 6V – 7V MIDB 8NC 9+INB 10NC 11–INB 12NC 13TOP VIEW UFF PACKAGE34-LEAD (4mm × 7mm) PLASTIC QFN35T JMAX = 150°C, θJA = 34°C/W , θJC = 2.7°C/WEXPOSED PAD (PIN 35) IS V –, MUST BE SOLDERED TO PCB(Note 1)LT6604-15 E LECTRICAL CHARACTERISTICSThel denotes specifi cations that apply over the full operating temperature range, otherwise specifi cations are at T A = 25°C. Unless otherwise specifi ed V S = 5V (V+ = 5V, V– = 0V), R IN = 536Ω, and R LOAD = 1k.PARAMETER CONDITIONS MIN TYP MAX UNITSMatching of Filter Gain, V S = 3V V IN = 2V P-P, f IN = DC to 260kHzV IN = 2V P-P, f IN = 1.5MHz (Gain Relative to 260kHz)V IN = 2V P-P, f IN = 7.5MHz (Gain Relative to 260kHz)V IN = 2V P-P, f IN = 12MHz (Gain Relative to 260kHz)V IN = 2V P-P, f IN = 15MHz (Gain Relative to 260kHz)V IN = 2V P-P, f IN = 45MHz (Gain Relative to 260kHz)V IN = 2V P-P, f IN = 75MHz (Gain Relative to 260kHz)llllll0.050.010.020.030.060.130.150.50.10.30.40.61.52.8dBdBdBdBdBdBdBMatching of Filter Phase, V S = 3V V IN = 2V P-P, f IN = 1.5MHzV IN = 2V P-P, f IN = 7.5MHzV IN = 2V P-P, f IN = 12MHz lll0.60.80.9134degdegdegFilter Gain Either Channel, V S = 5V V IN = 2V P-P, f IN = DC to 260kHzV IN = 2V P-P, f IN =1.5MHz (Gain Relative to 260kHz)V IN = 2V P-P, f IN = 7.5MHz (Gain Relative to 260kHz)V IN = 2V P-P, f IN = 12MHz (Gain Relative to 260kHz)V IN = 2V P-P, f IN = 15MHz (Gain Relative to 260kHz)V IN = 2V P-P, f IN = 45MHz (Gain Relative to 260kHz)V IN = 2V P-P, f IN = 75MHz (Gain Relative to 260kHz)llllll–0.5–0.1–0.4–0.4–0.80.1–29–460.50.10.30.90.9–25dBdBdBdBdBdBdBMatching of Filter Gain, V S = 5V V IN = 2V P-P, f IN = DC to 260kHzV IN = 2V P-P, f IN =1.5MHz (Gain Relative to 260kHz)V IN = 2V P-P, f IN = 7.5MHz (Gain Relative to 260kHz)V IN = 2V P-P, f IN = 12MHz (Gain Relative to 260kHz)V IN = 2V P-P, f IN = 15MHz (Gain Relative to 260kHz)V IN = 2V P-P, f IN = 45MHz (Gain Relative to 260kHz)V IN = 2V P-P, f IN = 75MHz (Gain Relative to 260kHz)llllll0.050.010.020.030.060.130.150.50.10.30.40.61.52.8dBdBdBdBdBdBdBMatching of Filter Phase, V S = 5V V IN = 2V P-P, f IN = 1.5MHzV IN = 2V P-P, f IN = 7.5MHzV IN = 2V P-P, f IN = 12MHz lll0.60.80.9134degdegdegFilter Gain Either Channel, V S = ±5V V IN = 2V P-P, f IN = DC to 260kHz–0.6–0.10.4dBFilter Gain, R IN = 133ΩV IN = 0.5V P-P, f IN = DC to 260kHz V S = 3VV S = 5VV S = ±5V 11.511.511.412.012.011.912.512.512.4dBdBdBFilter Gain Temperature Coeffi cient (Note 2)f IN = 250kHz, V IN = 2V P-P780ppm/°C Noise Noise BW = 10kHz to 15MHz, R IN = 536Ω109μV RMSDistortion (Note 4)1MHz, 2V P-P, R L = 800Ω, V S = 3V 2nd Harmonic3rd Harmonic 8690dBcdBc10MHz, 2V P-P, R L = 800Ω, V S = 3V 2nd Harmonic3rd Harmonic 6369dBcdBcChannel Separation (Note 9)1MHz, 2V P-P, R L = 800Ω–117dB10MHz, 2V P-P, R L = 800Ω–102dBDifferential Output Swing Measured Between +OUT and –OUT, V OCM shorted to V MIDV S = 5VV S = 3V ll3.803.754.754.50V P-P_DIFFV P-P_DIFFInput Bias Current Average of IN+ and IN–l–90–35μAInput Referred Differential Offset R IN = 536Ω V S = 3VV S = 5VV S = ±5V lll51010253035mVmVmVR IN = 133Ω V S = 3VV S = 5VV S = ±5V lll555151720mVmVmVLT6604-15PARAMETER CONDITIONSMIN TYP MAX UNITS Differential Offset Drift10μV/°CInput Common Mode Voltage (Note 3)Differential Input = 500mV P-P, R IN = 133ΩV S = 3V V S = 5V V S = ±5Vl l l00–2.51.531V V VOutput Common Mode Voltage (Note 5)Differential Output = 2V P-P, V MID = Open, Common Mode Voltage at V OCM V S = 3V V S = 5V V S = ±5V l l l 11.5–1 1.532V V V Output Common Mode Offset (with Respect to V OCM )V S = 3V V S = 5V V S = ±5V l l l –35–40–5555–10404035mV mV mV Common Mode Rejection Ratio 64dB Voltage at V MID V S = 3V V S = 5Vl 2.45 2.501.5 2.56V V V MID Input Resistance l 4.3 5.77.7kΩV OCM Bias CurrentV OCM = V MID = V S /2 V S = 3VV S = 5V l l –10–10–2–2μA μAPower Supply Current (per Channel)V S = 3V, V S = 5V V S = 3V V S = 5V V S = ±5Vl l l 35343839444548mA mA mA mA Power Supply Voltagel311VE LECTRICAL CHARACTERISTICS The l denotes specifi cations that apply over the full operating temperaturerange, otherwise specifi cations are at T A = 25°C. Unless otherwise specified V S = 5V (V + = 5V , V –= 0V), R IN = 536Ω, and R LOAD = 1k.Note 1: Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. Exposure to any Absolute Maximum Rating condition for extended periods may affect device reliability and lifetime.Note 2: This is the temperature coeffi cient of the internal feedback resistors assuming a temperature independent external resistor (R IN ).Note 3: The input common mode voltage is the average of the voltagesapplied to the external resistors (R IN ). Specification guaranteed for R IN ≥ 100Ω.Note 4: Distortion is measured differentially using a differential stimulus. The input common mode voltage, the voltage at V OCM , and the voltage at V MID are equal to one half of the total power supply voltage.Note 5: Output common mode voltage is the average of the +OUT and –OUT voltages. The output common mode voltage is equal to V OCM .Note 6: The L T6604C-15 is guaranteed functional over the operating temperature range –40°C to 85°C.Note 7: The L T6604C-15 is guaranteed to meet 0°C to 70°C specifi cations and is designed, characterized and expected to meet the extendedtemperature limits, but is not tested at –40°C and 85°C. The L T6604I-15 is guaranteed to meet specifi ed performance from –40°C to 85°C.Note 8: Input pins (+IN, –IN, V OCM and V MID ) are protected by steering diodes to either supply. If the inputs should exceed either supply voltage, the input current should be limited to less than 10mA. In addition, the inputs +IN, –IN are protected by a pair of back-to-back diodes. If the differential input voltage exceeds 1.4V , the input current should be limited to less than 10mA.Note 9: Channel separation (the inverse of crosstalk) is measured by driving a signal into one input, while terminating the other input. Channel separation is the ratio of the resulting output signal at the driven channel to the output at the channel that is not driven.LT6604-15T YPICAL PERFORMANCE CHARACTERISTICS Output ImpedanceCommon Mode Rejection RatioPower Supply Rejection RatioDistortion vs FrequencyDistortion vs Signal LevelAmplitude ResponsePassband Gain and PhasePassband Gain and DelayFREQUENCY (MHz)0.1–20G A I N (d B )–10010110100660415 G01–30–40–50–60FREQUENCY (MHz)G A I N (d B )PHASE (DEG)–3–1120660415 G02–5–7–4–20–6–8–945135225–45–135090180–90–180–2255101525FREQUENCY (MHz)G A I N (d B )DELAY (ns)6101420660415 G042–248120–4–630405*********4515505101525FREQUENCY (MHz)1O U T P U T I M P E D A N C E (Ω)100.110100660415 G050.11100FREQUENCY (MHz)0.1C M R R (d B )607080110100660415 G065040306575554535FREQUENCY (MHz)0.150P S R R (d B )607080110100660415 G07403020100FREQUENCY (MHz)0.1–100–110D I S T O R T I O N (d B c )–60–50110100660415 G08–70–80–90INPUT LEVEL (V P-P )–60–50–404660415 G09–70–801235–90–100–110D I S T O R T I O N (d B c )Passband Gain and DelayFREQUENCY (MHz)G A I N (d B )DELAY (ns)–3–1120660415 G03–5–7–4–20–6–8–9304050201025354515505101525LT6604-15TYPICAL PERFORMANCE CHARACTERISTICSDistortion vs Output Common Mode LevelSingle Channel Supply Current vs Total Supply VoltageT ransient Response,Channel Separation vs Frequency (Note 9)Distortion vs Signal LevelDistortion vs Input Common Mode LevelDistortion vs Input Common Mode LevelINPUT LEVEL (V P-P )–60–50–404660415 G10–70–801235–90–100–110D I S T O R T I O N (d B c )INPUT COMMON MODE VOTLAGE RELATIVE TO V MID (V)–3–110–100D I S T O R T I O N C O M P O N E N T (d B c )–90–80–70–60–50–40–2–1012660415 G113INPUT COMMON MODE VOTLAGE RELATIVE TO V MID (V)–3–100D I S T O R T I O N C O M P O NE N T (d B c )–90–80–70–60–50–40–2–1012660415 G123(V OCM – V MID ) VOLTAGE (V)D I S T O R T I O N C O M P O NE N T (d B c )–70–60–500.51 1.5660415 G13–80–90–1.5–1–0.502 2.5–100–110–402V P-P 1MHz INPUT GAIN = 1,R L = 800Ω AT EACH OUTPUTT A = 25°CTOTAL SUPPLY VOLTAGE (V)20S U P P L Y C U R R E N T (m A )3040502535452468660415 G141012OUT –200mV/DIV IN +500mV/DIVIN –100ns/DIVDIFFERENTIAL GAIN = 1SINGLE-ENDED INPUT DIFFERENTAL OUTPUT660415 G15OUT +200mV/DIVFREQUENCY (MHz)0.1–50–60C H A N N E L S E P A R A T I O N (d B )–40110100660415 G16–70–80–100–90–120–130–110LT6604-15 P IN FUNCTIONS+INA and –INA (Pins 2, 4): Channel A Input Pins. Signals can be applied to either or both input pins through identi-cal external resistors, R IN. The DC gain from differential inputs to the differential outputs is 536Ω/R IN.V OCMA (Pin 6): DC Common Mode Reference Voltage for the 2nd Filter Stage in Channel A. Its value programs the common mode voltage of the differential output of the fi lter. Pin 6 is a high impedance input, which can be driven from an external voltage reference, or Pin 6 can be tied to Pin 34 on the PC board. Pin 6 should be bypassed with a 0.01μF ceramic capacitor unless it is connected to a ground plane.V– (Pins 7, 24, 31, 32, 35): Negative Power Supply Pin (can be ground).V MIDB (Pin 8): The V MIDB pin is internally biased at mid-supply, see Block Diagram. For single supply operation the V MIDB pin should be bypassed with a quality 0.01μF ceramic capacitor to ground. For dual supply operation, Pin 8 can be bypassed or connected to a high quality DC ground. A ground plane should be used. A poor ground will increase noise and distortion. Pin 8 sets the output common mode voltage of the 1st Filter Stage in channel B. It has a 5.5kΩ impedance, and it can be overridden with an external low impedance voltage source.+INB and –INB (Pins 10, 12): Channel B Input Pins. Signals can be applied to either or both input pins through identi-cal external resistors, R IN. The DC gain from differential inputs to the differential outputs is 536Ω/R IN.V OCMB (Pin 14):Is the DC Common Mode Reference Voltage for the 2nd Filter Stage in Channel B. Its value programs the common mode voltage of the differential output of the fi lter. Pin 14 is a high impedance input, which can be driven from an external voltage reference, or Pin 14 can be tied to Pin 8 on the PC board. Pin 14 should be bypassed with a 0.01μF ceramic capacitor unless it is connected to a ground plane.V+A and V+B (Pins 25, 17): Positive Power Supply Pins for Channels A and B. For a single 3.3V or 5V supply (Pins 7, 24, 31, 32 and 35 grounded) a quality 0.1μF ceramic bypass capacitor is required from the positive supply pin (Pins 25, 17) to the negative supply pin (Pins 7, 24, 31, 32 and 35). The bypass should be as close as possible to the IC. For dual supply applications, bypass the negative supply pins to ground and Pins 25 and 17 to ground with a quality 0.1μF ceramic capacitor.+OUTB and –OUTB (Pins 19, 21): Output Pins. Pins 19 and 21 are the fi lter differential outputs for channel B. With a typical short-circuit current limit greater than ±40mA each pin can drive a 100Ω and/or 50pF load to AC ground.+OUTA and –OUTA (Pins 27, 29): Output Pins. Pins 27 and 29 are the fi lter differential outputs for channel A. With a typical short-circuit current limit greater than ±40mA each pin can drive a 100Ω and/or 50pF load to AC ground.V MIDA (Pin 34): The V MIDA pin is internally biased at mid-supply, see Block Diagram. For single supply operation the V MIDA pin should be bypassed with a quality 0.01μF ceramic capacitor to ground. For dual supply operation, Pin 34 can be bypassed or connected to a high quality DC ground. A ground plane should be used. A poor ground will increase noise and distortion. Pin 34 sets the output common mode voltage of the 1st stage fi lter stage in chan-nel A. It has a 5.5kΩ impedance, and it can be overridden with an external low impedance voltage source. Exposed Pad (Pin 35): V–. The Exposed Pad must be soldered to the PCB.LT6604-15BLOCK DIAGRAMV IN –V IN +V IN +V IN –OCMBNCNCV BNC+OUTA–OUTANCNCV +ANCV –NCNC+OUTBNC–OUTBV –V –V NCLT6604-15APPLICATIONS INFORMATIONInterfacing to the L T6604-15Note: The LT6604-15 contains two identical fi lters. The following applications information only refers to one fi lter. The two fi lters are independent except that they share thesame negative supply voltage V –. The two filters can be used simultaneously by replicating the example circuits. The referenced pin numbers correspond to the A channel fi lterThe LT6604-15 channel requires two equal external re-sistors, R IN , to set the differential gain to 536Ω/R IN . The inputs to the fi lter are the voltages V IN + and V IN – presented to these external components, Figure 1. The difference between V IN + and V IN – is the differential input voltage. The average of V IN + and V IN – is the common mode input voltage. Similarly, the voltages V OUT + and V OUT – appearing at Pins 27 and 29 of the LT6604-15 are the fi lter outputs. The dif-ference between V OUT + and V OUT – is the differential output voltage. The average of V OUT + and V OUT – is the commonmode output voltage. Figure 1 illustrates the LT6604-15 operating with a single 3.3V supply and unity passband gain; the input signal is DC coupled. The common mode input voltage is 0.5V, and the differential input voltage is 2V P-P . The common mode output voltage is 1.65V, and the differential output voltage is 2V P-P for frequencies below 15MHz. The common mode output voltage is determined by the voltage at V OCM . Since V OCM is shorted to V MID , the output common mode is the mid-supply voltage. In addition, the common mode input voltage can be equal to the mid-supply voltage of V MID .Figure 2 shows how to AC couple signals into the LT6604-15. In this instance, the input is a single-ended signal. AC cou-pling allows the processing of single-ended or differential signals with arbitrary common mode levels. The 0.1μF coupling capacitor and the 536Ω gain setting resistor form a high pass fi lter, attenuating signals below 3kHz. Larger values of coupling capacitors will proportionally reduce this highpass 3dB frequency.V INV INOUT +OUT –t321t3210V OUT+OUT –3221t100–1Figure 1Figure 2LT6604-15APPLICATIONS INFORMATIONIn Figure 3 the LT6604-15 is providing 12dB of gain. The gain resistor has an optional 62pF in parallel to improve the passband fl atness near 15MHz. The common mode output voltage is set to 2V.Use Figure 4 to determine the interface between the LT6604-15 and a current output DAC. The gain, or “tran-simpedance,” is defi ned as A = V OUT /I IN . To compute the transimpedance, use the following equation:A =536•R1(R1+R2)(Ω)By setting R1 + R2 = 536Ω, the gain equation reduces to A = R1 (Ω).The voltage at the pins of the DAC is determined by R1, R2, the voltage on V MID and the DAC output current. Consider Figure 4 with R1 = 49.9Ω and R2 = 487Ω. Thevoltage at V MID , for V S = 3.3V, is 1.65V. The voltage at the DAC pins is given by: V DAC =V MID •R1R1+R2+536+I IN •R1•R2R1+R2=77mV +I IN •45.3ΩI IN is I IN + or I IN –. The transimpedance in this example is 49.8Ω.Evaluating the L T6604-15The low impedance levels and high frequency operation of the LT6604-15 require some attention to the matching networks between the LT6604-15 and other devices. The previous examples assume an ideal (0Ω) source impedance and a large (1k) load resistance. Among practical examplesV INV INOUT +OUT–t32103210OUT+OUT–660415 F04=V OUT + – V OUT –I IN + – I IN –536 • R1R1 + R2Figure 3Figure 4Figure 511660415fbA PPLICATIONS INFORMATION where impedance must be considered is the evaluation of the LT6604-15 with a network analyzer.Figure 5 is a laboratory setup that can be used to char-acterize the LT6604-15 using single-ended instruments with 50Ω source impedance and 50Ω input impedance. For a unity gain confi guration the LT6604-15 requires an 536Ω source resistance yet the network analyzer output is calibrated for a 50Ω load resistance. The 1:1 transformer, 52.3Ω and 523Ω resistors satisfy the two constraints above. The transformer converts the single-ended source into a differential stimulus. Similarly, the output of the LT6604-15 will have lower distortion with larger load resistance yet the analyzer input is typically 50Ω. The 4:1 turns (16:1 impedance) transformer and the two 402Ω resistors of Figure 5, present the output of the LT6604-15 with a 1600Ω differential load, or the equiva-lent of 800Ω to ground at each output. The impedance seen by the network analyzer input is still 50Ω, reducing refl ections in the cabling between the transformer and analyzer input.Differential and Common Mode Voltage Ranges The differential amplifi ers inside the LT6604-15 contain circuitry to limit the maximum peak-to-peak differential voltage through the fi lter. This limiting function prevents excessive power dissipation in the internal circuitry and provides output short-circuit protection. The limiting function begins to take effect at output signal levelsabove 2V P-P and it becomes noticeable above 3.5V P-P . This is illustrated in Figure 6; the LT6604-15 channel was confi gured with unity passband gain and the input of the fi lter was driven with a 1MHz signal. Because this voltage limiting takes place well before the output stage of the fi lter reaches the supply rails, the input/output behavior of the IC shown in Figure 6 is relatively independent of the power supply voltage.The two amplifi ers inside the LT6604-15 channel have independent control of their output common mode voltage (see the Block Diagram section). The following guidelines will optimize the performance of the fi lter. V MID can be allowed to float, but it must be bypassed to an AC ground with a 0.01μF capacitor or some instability may be observed. V MID can be driven from a low impedance source, provided it remains at least 1.5V above V – and at least 1.5V below V +. An internal resistor divider sets the voltage of V MID . While the internal 11k resistors are well matched, their absolute value can vary by ±20%. This should be taken into consideration when connecting an external resistor network to alter the voltage of V MID . V OCM can be shorted to V MID for simplicity. If a different common mode output voltage is required, connect V OCM to a voltage source or resistor network. For 3V and 3.3V supplies the voltage at V OCM must be less than or equal to the mid supply level. For example, voltage (V OCM ) ≤ 1.65V on a single 3.3V supply. For power supply voltages higher than 3.3V the voltage at V OCM can be set above mid supply. The voltage on V OCM should not be more than 1V below the voltage on V MID . The voltage on V OCM should not be more than 2V above the voltage on V MID . V OCM is a high impedance input.The LT6604-15 was designed to process a variety of input signals including signals centered on the mid-supply volt-age and signals that swing between ground and a positive voltage in a single supply system (Figure 1). The range of allowable input common mode voltage (the average of V IN + and V IN – in Figure 1) is determined by the power supply level and gain setting (see Distortion vs Input Common Mode Level in the Typical Performance Characteristics).1MHz INPUT LEVEL (V P-P )200–20–40–60–80–10035660415 F0612467O U T P U T L E V E L (d B V )Figure 6. Output Level vs Input Level, Differential 1MHz Input, Gain = 1芯天下--/Common Mode DC CurrentsIn applications like Figure 1 and Figure 3 where the LT6604-15 not only provides lowpass fi ltering but also level shifts the common mode voltage of the input signal, DC currents will be generated through the DC path between input and output terminals. Minimize these currents to decrease power dissipation and distortion. Consider the application in Figure 3. V MID sets the output common mode voltage of the 1st differential amplifi er inside the LT6604-15 channel (see the Block Diagram section) at 2.5V. Since the input common mode voltage is near 0V, there will be approxi-mately a total of 2.5V drop across the series combination of the internal 536Ω feedback resistor and the external 133Ω input resistor. The resulting 3.7mA common mode DC current in each input path, must be absorbed by the sources V IN+ and V IN–. V OCM sets the common mode output voltage of the 2nd differential amplifi er inside the LT6604-15 channel, and therefore sets the common mode output voltage of the fi lter. Since, in the example of Figure 3, V OCM differs from V MID by 0.5V, an additional 2.5mA (1.25mA per side) of DC current will fl ow in the resistors coupling the 1st differential amplifi er output stage to the fi lter output. Thus, a total of 9.9mA per channel is used to translate the common mode voltages.A simple modifi cation to Figure 3 will reduce the DC com-mon mode currents by 40%. If V MID is shorted to V OCM the common mode output voltage of both op amp stages will be 2V and the resulting DC current will be 6mA per channel. Of course, by AC coupling the inputs of Figure 3, the common mode DC current can be reduced to 2.5mA per channel.NoiseThe noise performance of the LT6604-15 channel can be evaluated with the circuit of Figure 6. Given the low noise output of the LT6604-15 and the 6dB attenuation of the transformer coupling network, it will be necessary to measure the noise fl oor of the spectrum analyzer and subtract the instrument noise from the fi lter noise mea-surement.Example: With the IC removed and the 25Ω resistors grounded, Figure 6, measure the total integrated noise (e S) of the spectrum analyzer from 10kHz to 15MHz. With the IC inserted, the signal source (V IN) disconnected, and the input resistors grounded, measure the total integrated noise out of the fi lter (e O). With the signal source connected, set the frequency to 1 MHz and adjust the amplitude until V IN measures 100mV P-P. Measure the output amplitude, V OUT, and compute the passband gain A = V OUT/V IN. Now compute the input referred integrated noise (e IN) as:e INTable 1 lists the typical input referred integrated noise for various values of R IN.Table 1. Noise PerformancePASSBANDGAINR ININPUT REFERREDINTEGRATED NOISE10kHz TO 15MHzINPUT REFERREDINTEGRATED NOISE10kHz TO 30MHz 4133Ω36μV RMS51μV RMS2267Ω62μV RMS92μV RMS1536Ω109μV RMS169μV RMSAPPLICATIONS INFORMATION芯天下--/12660415fb。

P4C1298-25PM中文资料

Document # SRAM135 REV ORDESCRIPTIONThe P4C1298/L are a 262,144-bit ultra high speed static RAM organized as 64K x 4. The CMOS memory requires no clock or refreshing and has equal access and cycle times. Inputs and outputs are fully TTL-compatible. The RAM operates from a single 5V±10% tolerance power supply. With battery backup, data integrity is maintained for supply voltages down to 2.0V. Current drain is typically 10 µA from a 2.0V supply.Data Retention with 2.0V Supply Three-State OutputsTTL/CMOS Compatible Outputs Fully TTL Compatible Inputs Standard Pinout (JEDEC Approved)– 28-Pin 300 mil DIP, SOJ – 28-Pin 350x550 mil LCCFEATURESFull CMOS, 6T CellHigh Speed (Equal Access and Cycle Times)– 15/20/25/35 ns (Commercial/Industrial)– 15/20/25/35/45 ns (Military)Low PowerSingle 5V±10% Power SupplyOutput Enable & Chip Enable control functionsFUNCTIONAL BLOCK DIAGRAM PIN CONFIGURATIONP4C1298/P4C1298LULTRA HIGH SPEED 64K x 4STATIC CMOS RAMAccess times as fast as 15 nanoseconds are available,permitting greatly enhanced system speeds. CMOS is utilized to reduce power consumption.The P4C1298 is available in a 28-pin 300 mil DIP or SOJ, as well as a 28-pin 350x500 mil LCC package, providingexcellent board level densities.DIP (P5, C5)SOJ (J5)LCC (L5)P4C1298/LMAXIMUM RATINGS (1)Symbol Parameter Value Unit V CCPower Supply Pin with –0.5 to +7VRespect to GND Terminal Voltage with –0.5 to V TERM Respect to GND V CC +0.5V (up to 7.0V)T AOperating Temperature–55 to +125°CSymbol Parameter Value Unit T BIAS Temperature Under –55 to +125°C BiasT STG Storage Temperature –65 to +150°C P T Power Dissipation 1.0W I OUTDC Output Current50mARECOMMENDED OPERATINGTEMPERATURE AND SUPPLY VOLTAGEIndustrial CommercialGrade(2)Ambient Temperature GND V CC –40°C to +85°C 0°C to +70°C0V 0V5.0V ± 10%5.0V ± 10%Symbol C IN C OUTParameter Input Capacitance Output CapacitanceConditions V IN = 0V V OUT = 0V57Unit pF pFCAPACITANCES (4)V CC = 5.0V, T A = 25°C, f = 1.0MHz DC ELECTRICAL CHARACTERISTICSOver recommended operating temperature and supply voltage (2)Notes:1.Stresses greater than those listed under MAXIMUM RATINGS may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to MAXIMUM rating conditions for extended periods may affect reliability.2.Extended temperature operation guaranteed with 400 linear feet per minute of air flow.3.Transient inputs with V IL and I IL not more negative than –3.0V and –100mA, respectively, are permissible for pulse widths up to 20 ns.4.This parameter is sampled and not 100% tested.Typ. I SB Standby Power SupplyCurrent (TTL Input Levels)CE ≥ V IHV CC = Max ., f = Max., Outputs Open___4010mA mA ___CE ≥ V HCV CC = Max., f = 0, Outputs Open V IN ≤ V LC or V IN ≥ V HCStandby Power Supply Current(CMOS Input Levels)I SB1Symbol V IH V IL V HC V LC V CD V OL V OH I LI I LO ParameterInput High Voltage Input Low Voltage CMOS Input High Voltage CMOS Input Low Voltage Input Clamp Diode Voltage Output Low Voltage (TTL Load)Output High Voltage (TTL Load)Input Leakage CurrentOutput Leakage Current Test ConditionsV CC = Min., I IN = 18 mA I OL = +8 mA, V CC = Min.I OH = –4 mA, V CC = Min.V CC = Max.V IN = GND to V CC V CC = Max., CE = V IH V OUT = GND to V CCP4C1298Min 2.2–0.5(3)V CC –0.2–0.5(3)2.4–5–5MaxV CC +0.50.8V CC +0.50.2–1.20.4+5+5UnitV V V V V V VµAµA Military -55°C to +125°C 0V 5.0V ± 10%___2010___P4C1298LMin 2.2–0.5(3)V CC –0.2–0.5(3)2.4–10–10MaxV CC +0.50.8V CC +0.50.2–1.20.4+10+10___20mA ___N/A MilInd/CommMilInd/Comm10mA___N/A___*V CC = 5.5V. Tested with outputs open. f = Max. Switching inputs are 0V and 3V. CE = V ILDATA RETENTION CHARACTERISTICS (P4C1298L ONLY)Symbol V DR I CCDR t CDR t R †ParameterV CC for Data Retention Data Retention Current Chip Deselect to Data Retention Time Operation Recovery TimeTest ConditionsCE ≥ V CC –0.2V,V IN ≥ V CC –0.2V or V IN ≤ 0.2V Min 2.00t RC §Typ.*V CC =2.0V3.0V1015Max V CC = 2.0V 3.0V10002000Unit V µA ns nsDATA RETENTION WAVEFORM*T A = +25°C§t RC = Read Cycle Time†This parameter is guaranteed but not tested.I CCSymbolParameterTemperatureRange Dynamic Operating Current*Commercial Industrial –15–20–25–35Unit mA mA POWER DISSIPATION CHARACTERISTICS VS. SPEED115120135160160125115110MilitarymA120120150160P4C1298/LAC CHARACTERISTICS—READ CYCLE(V CC = 5V ± 10%, All Temperature Ranges)(2)TIMING WAVEFORM OF READ CYCLE NO. 2 (ADDRESS CONTROLLED)(5,6)Sym.t RC t AA t AC t OH t LZ t HZ t PU t PDParameter Read Cycle Time Address Access Time Chip Enable Access Time Output Hold from Address Change Chip Enable to Output in Low Z Chip Disable to Output in High Z Chip Enable to Power Up Time Chip Disable to Power Down Time-15Min 1533Max 1515815-20Min 20330Max20201020-25Min 2533Max 25251525-35Min3533Max 35351535Unit ns ns ns ns ns ns ns ns-45Min 4533Max45452045t OE Output Enable Low to Data Valid ns TIMING WAVEFORM OF READ CYCLE NO. 1 (OE CONTROLLED)(5)t OLZ t OHZ Output Enable Low to Low Z Output Enable High to High Z 810152530ns ns 000099152020Notes:5.CE is LOW and WE is HIGH for READ cycle.6.WE is HIGH, and address must be valid prior to or coincident with CEtransition LOW.7.Transition is measured ±200mV from steady state voltage prior tochange with specified loading in Figure 1. This parameter is sampled and not 100% tested.8.Read Cycle Time is measured from the last valid address to the firsttransitioning address.TIMING WAVEFORM OF READ CYCLE NO. 3 (CE CONTROLLED)(5,6)P4C1298/L12.Write Cycle Time is measured from the last valid address to the firsttransition address.13.Transition is measured ±200mV from steady state voltage prior tochange with specified loading in Figure 1. This parameter is sampled and not 100% tested.Notes:9.CE and WE must be LOW for WRITE cycle.10. OE is LOW for this WRITE cycle.11.If CE goes HIGH simultaneously with WE HIGH, the output remainsin a high impedance state.TIMING WAVEFORM OF WRITE CYCLE NO. 1 (WE CONTROLLED) (9)AC CHARACTERISTICS - WRITE CYCLE(V CC = 5V ± 10%, All Temperature Ranges)(2)Input Pulse Levels GND to 3.0VInput Rise and Fall Times 3ns Input Timing Reference Level 1.5V Output Timing Reference Level 1.5VOutput LoadSee Figures 1 and 2Mode CE WE Output Power Standby H X High Z Standby Read L H D OUT Active WriteLLD INActive* including scope and test fixture.Note:Because of the ultra-high speed of the P4C1298, care must be taken when testing this device; an inadequate setup can cause a normal functioning part to be rejected as faulty. Long high-inductance leads that cause supply bounce must be avoided by bringing the V CC and ground planes directly up to the contactor fingers. A 0.01 µF highfrequency capacitor is also required between V CC and ground. To avoid signal reflections, proper termination must be used; for example, a 50Ωtest environment should be terminated into a 50Ω load with 1.73V (Thevenin Voltage) at the comparator input, and a 116Ω resistor must be used in series with D OUT to match 166Ω (Thevenin Resistance).Figure 1. Output LoadFigure 2. Thevenin EquivalentAC TEST CONDITIONSTRUTH TABLETIMING WAVEFORM OF WRITE CYCLE NO. 2 (CE CONTROLLED)(9,10)P4C1298/LORDERING INFORMATIONSELECTION GUIDEThe P4C1298 is available in the following temperature, speed and package options.SOJ SMALL OUTLINE IC PACKAGEPLASTIC DUAL IN-LINE PACKAGEP4C1298/LRECTANGULAR LEADLESS CHIP CARRIERSIDEBRAZED DUAL IN-LINE PACKAGEPage 11 of 11Document # SRAM135 REV OR REVISIONS DOCUMENT NUMBER :SRAM135DOCUMENT TITLE :P4C1298/P4C1298L ULTRA HIGH SPEED 64K x 4 STATIC CMOS RAM REV.ISSUE DATE ORIG. OF CHANGE DESCRIPTION OF CHANGE OR Apr-07JDB New Data Sheet元器件交易网。

PT4142C中文资料

Mechanical Vibration

Weight Flammability

Io

Vin Vo tol

Regtemp Regline

Regload

∆Votot

η

Vr

ttr ∆Vtr Isc ƒs UVLO VIH VIL IIL Iin standby Cin Cout

—

—

—

—

A

VDC %Vo mV %Vo %Vo mV %Vo mV %Vo mV

%

%Vo mVpp µs %Vo mV A kHz

V

V

µA mA µF µF V pF MΩ °C °C 106 Hrs

G’s

G’s

grams

Notes: (1) The DC/DC converter will operate at no load with reduced specifications.

• Short Circuit Protection • Over Temperature Shutdown • Under-Voltage Lockout • UL1950 Recognized • CSA 22.2 950 Certified • EN60950 Approved • 4×106 Hrs MTBF

(2) The Remote On/Off (pin 1) has an internal pull-up, and if it is left open circuit the module will operate when input power is applied. Refer to the application notes for interface considerations.

单片机应用技术C语言课件汇总全书电子教案完整版课件最全幻灯片最新课件电子教案幻灯片

一、电源电路 —— 单片机的工作电压

单片机要想工作,首先要有为整个系统提供电源的供电模 块。电源模块的稳定可靠是系统平稳运行的前提和基础。

51系列单片机工作电源的电压一般为+4.5~+5.5 V,典型 值为+5V,即将单片机的VCC脚接+5V电源,GND脚接地。

二、时钟电路 —— 单片机的“心脏”

同时P1口的部分引脚还具有第二功能:

✤ P1.5:MOSI端(用于ISP编程,主出从入数据端)。 ✤ P1.6:MOSO端(用于ISP编程,主入从出数据端)。 ✤ P1.7:SCK端(用于ISP编程,串行时钟输入端)。

3.P2口

P2口为8位准双向I/O口。当用作通用并行I/O口时,其操 作方式与P0、P1口类似,每一位可驱动4个TTL负载。当用于 外接存储器或者扩展I/O接口时,P2口作为扩展的高8位地址 (A8~A15)总线口,与P0口共同构成16位地址总线(A0~ A15)。

ALE/

30

地址锁存允许信号端

四、AT89S51的功能特性

✤兼容MCS-51系列产品。 ✤4KB Flash存储器,支持

在线编程,可反复擦写 1 000次。 ✤ 128B片内RAM。 ✤ 工作电压4.5~5.5 V。 ✤ 全静态时钟0~33 MHz。

✤ 32个双向I/O口线。 ✤ 2个16位定时/计数器。 ✤ 5个中断源,2个中断优

信收发器,也可以当同步移位器使用

中断系统

共含有5个中断源(2个外部中断、2个定时/计数 器中断和1个串行中断),并具有2级的优先级别 选择

时钟电路

需外接晶振和微调电容构成振荡电路,产生单 片机运行的脉冲时序

二、单片机的I/O端口

AT89S51单片机有4个并行的I/O端口,即P0、P1、P2 和P3口。每个端口均由8个引脚(即8位)构成,包括一个 锁存器、一个输出驱动器和一个输入缓冲器。

PC4351C-12SFH资料

Subminature PCB Powe r RelayFEATURES10 Amp continous contact capa city 1 Form A & 1 form C contact fo rms Class "B" insulation standard Subminature designSensitive version available4 Kv dielectric between coil an d contacts PC435Load Type 10 Amps @ 125 VAC Normally Open ContactUL/CUR RATINGSCHARACTERISTICSOperate Time 8 ms. Max.Release Time Insulation Resistance 5 ms. Max.1000 megohms min, at 500VDC, 50%RH Dielectric Strength 4000 Vrms, 1 min. between coil and contacts Shock Resistance 10 g, 11ms, functional; 100 g, destructive Vibration Resistance DA 1.6 mm, 10 - 55 Hz Power Consumption .45 WAmbient Temperature Range -40 to 70 C operating for class B, -40 to 130 C s torage Weight7 grams approx.Sales: Call Toll Free (888)997-3933 Fax (818) 342-5296 email: pickerwest@ URL: 3220 Commander Drive, Suite 102, Carrollton, T exas 75006PC435 Rev C 3-29-04PAGE 1ORDERING INFORMATIONExample:PC435Model -12Sealed, immersion cleanableContact Form 1A, 1C-1C CONTACT DATAMaterialInitial Contact Resistance Service LifeMechanical ElectricalAgCdO (Silver Cadmium Oxide)100 milliohms max @ 0.1A, 6VDC 1 X 1071 X 105Operations OperationsEnclosureS: Sealed; C: Flux Free Insulation SystemNil: Class B (155 degrees C), F: Class F (125 degrees C)F S Nil: Standard .45 W, H: Sensitive .2 W-H5 Amps @ 250 VAC, 30 VDC1000 Vrms, 1 min. between open contacts File # E93379General Use 1/4 HP @ 250 VACNormally Closed Contact5 Amps @ 125 VAC 3 Amps @ 250 VAC, 30 VDCCoil SensitivityMotor LampTV-5Coil VoltagePC435PC435COIL DATASales: Call Toll Free (888) 997-3933 F ax (818) 342-5296 email: pickerwest@sbc URL: 3220 Commander Drive, Suite 102, Car rollton, Texas 75006PAGE 2Dimensions in Inches (millimet ers)Side View End View(15.3).60(7.6)(10.2).40(7.6).30.30Bottom View PC Board LayoutWiring DiagramTolerances +.010 unless otherwise notedNotes:Contact Form C shownOn Contact Forms A & B Unused Pins are Omitte d(15.7).618(20.5).807(4.0).157(10.6).417(1.3).051 Dia. Typ.。

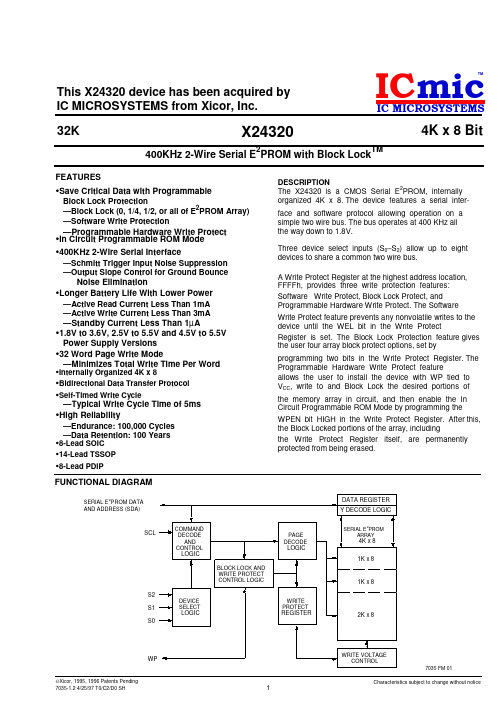

X24320V14IG资料

DESCRIPTION The X24320 is a CMOS Serial E2PROM, internally organized 4K x 8. The and software protocol allowing operation on a simple two wire bus. The bus operates at 400 KHz all the way down to 1.8V.

4K x 8 Bit

FEATURES

•Save Critical Data with Programmable

Block Lock Protection —Block Lock (0, 1/4, 1/2, or all of E2PROM Array) —Software Write Protection

•1.8V to 3.6V, 2.5V to 5.5V and 4.5V to 5.5V

Power Supply Versions

•32 Word Page Write Mode

—Minimizes Total Write Time Per Word

•Internally Organized 4K x 8 •Bidirectional Data Transfer Protocol •Self-Timed Write Cycle

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

Document # SRAM135 REV ORDESCRIPTIONThe P4C1298/L are a 262,144-bit ultra high speed static RAM organized as 64K x 4. The CMOS memory requires no clock or refreshing and has equal access and cycle times. Inputs and outputs are fully TTL-compatible. The RAM operates from a single 5V±10% tolerance power supply. With battery backup, data integrity is maintained for supply voltages down to 2.0V. Current drain is typically 10 µA from a 2.0V supply.Data Retention with 2.0V Supply Three-State OutputsTTL/CMOS Compatible Outputs Fully TTL Compatible Inputs Standard Pinout (JEDEC Approved)– 28-Pin 300 mil DIP, SOJ – 28-Pin 350x550 mil LCCFEATURESFull CMOS, 6T CellHigh Speed (Equal Access and Cycle Times)– 15/20/25/35 ns (Commercial/Industrial)– 15/20/25/35/45 ns (Military)Low PowerSingle 5V±10% Power SupplyOutput Enable & Chip Enable control functionsFUNCTIONAL BLOCK DIAGRAM PIN CONFIGURATIONP4C1298/P4C1298LULTRA HIGH SPEED 64K x 4STATIC CMOS RAMAccess times as fast as 15 nanoseconds are available,permitting greatly enhanced system speeds. CMOS is utilized to reduce power consumption.The P4C1298 is available in a 28-pin 300 mil DIP or SOJ, as well as a 28-pin 350x500 mil LCC package, providingexcellent board level densities.DIP (P5, C5)SOJ (J5)LCC (L5)P4C1298/LMAXIMUM RATINGS (1)Symbol Parameter Value Unit V CCPower Supply Pin with –0.5 to +7VRespect to GND Terminal Voltage with –0.5 to V TERM Respect to GND V CC +0.5V (up to 7.0V)T AOperating Temperature–55 to +125°CSymbol Parameter Value Unit T BIAS Temperature Under –55 to +125°C BiasT STG Storage Temperature –65 to +150°C P T Power Dissipation 1.0W I OUTDC Output Current50mARECOMMENDED OPERATINGTEMPERATURE AND SUPPLY VOLTAGEIndustrial CommercialGrade(2)Ambient Temperature GND V CC –40°C to +85°C 0°C to +70°C0V 0V5.0V ± 10%5.0V ± 10%Symbol C IN C OUTParameter Input Capacitance Output CapacitanceConditions V IN = 0V V OUT = 0V57Unit pF pFCAPACITANCES (4)V CC = 5.0V, T A = 25°C, f = 1.0MHz DC ELECTRICAL CHARACTERISTICSOver recommended operating temperature and supply voltage (2)Notes:1.Stresses greater than those listed under MAXIMUM RATINGS may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to MAXIMUM rating conditions for extended periods may affect reliability.2.Extended temperature operation guaranteed with 400 linear feet per minute of air flow.3.Transient inputs with V IL and I IL not more negative than –3.0V and –100mA, respectively, are permissible for pulse widths up to 20 ns.4.This parameter is sampled and not 100% tested.Typ. I SB Standby Power SupplyCurrent (TTL Input Levels)CE ≥ V IHV CC = Max ., f = Max., Outputs Open___4010mA mA ___CE ≥ V HCV CC = Max., f = 0, Outputs Open V IN ≤ V LC or V IN ≥ V HCStandby Power Supply Current(CMOS Input Levels)I SB1Symbol V IH V IL V HC V LC V CD V OL V OH I LI I LO ParameterInput High Voltage Input Low Voltage CMOS Input High Voltage CMOS Input Low Voltage Input Clamp Diode Voltage Output Low Voltage (TTL Load)Output High Voltage (TTL Load)Input Leakage CurrentOutput Leakage Current Test ConditionsV CC = Min., I IN = 18 mA I OL = +8 mA, V CC = Min.I OH = –4 mA, V CC = Min.V CC = Max.V IN = GND to V CC V CC = Max., CE = V IH V OUT = GND to V CCP4C1298Min 2.2–0.5(3)V CC –0.2–0.5(3)2.4–5–5MaxV CC +0.50.8V CC +0.50.2–1.20.4+5+5UnitV V V V V V VµAµA Military -55°C to +125°C 0V 5.0V ± 10%___2010___P4C1298LMin 2.2–0.5(3)V CC –0.2–0.5(3)2.4–10–10MaxV CC +0.50.8V CC +0.50.2–1.20.4+10+10___20mA ___N/A MilInd/CommMilInd/Comm10mA___N/A___*V CC = 5.5V. Tested with outputs open. f = Max. Switching inputs are 0V and 3V. CE = V ILDATA RETENTION CHARACTERISTICS (P4C1298L ONLY)Symbol V DR I CCDR t CDR t R †ParameterV CC for Data Retention Data Retention Current Chip Deselect to Data Retention Time Operation Recovery TimeTest ConditionsCE ≥ V CC –0.2V,V IN ≥ V CC –0.2V or V IN ≤ 0.2V Min 2.00t RC §Typ.*V CC =2.0V3.0V1015Max V CC = 2.0V 3.0V10002000Unit V µA ns nsDATA RETENTION WAVEFORM*T A = +25°C§t RC = Read Cycle Time†This parameter is guaranteed but not tested.I CCSymbolParameterTemperatureRange Dynamic Operating Current*Commercial Industrial –15–20–25–35Unit mA mA POWER DISSIPATION CHARACTERISTICS VS. SPEED115120135160160125115110MilitarymA120120150160P4C1298/LAC CHARACTERISTICS—READ CYCLE(V CC = 5V ± 10%, All Temperature Ranges)(2)TIMING WAVEFORM OF READ CYCLE NO. 2 (ADDRESS CONTROLLED)(5,6)Sym.t RC t AA t AC t OH t LZ t HZ t PU t PDParameter Read Cycle Time Address Access Time Chip Enable Access Time Output Hold from Address Change Chip Enable to Output in Low Z Chip Disable to Output in High Z Chip Enable to Power Up Time Chip Disable to Power Down Time-15Min 1533Max 1515815-20Min 20330Max20201020-25Min 2533Max 25251525-35Min3533Max 35351535Unit ns ns ns ns ns ns ns ns-45Min 4533Max45452045t OE Output Enable Low to Data Valid ns TIMING WAVEFORM OF READ CYCLE NO. 1 (OE CONTROLLED)(5)t OLZ t OHZ Output Enable Low to Low Z Output Enable High to High Z 810152530ns ns 000099152020Notes:5.CE is LOW and WE is HIGH for READ cycle.6.WE is HIGH, and address must be valid prior to or coincident with CEtransition LOW.7.Transition is measured ±200mV from steady state voltage prior tochange with specified loading in Figure 1. This parameter is sampled and not 100% tested.8.Read Cycle Time is measured from the last valid address to the firsttransitioning address.TIMING WAVEFORM OF READ CYCLE NO. 3 (CE CONTROLLED)(5,6)P4C1298/L12.Write Cycle Time is measured from the last valid address to the firsttransition address.13.Transition is measured ±200mV from steady state voltage prior tochange with specified loading in Figure 1. This parameter is sampled and not 100% tested.Notes:9.CE and WE must be LOW for WRITE cycle.10. OE is LOW for this WRITE cycle.11.If CE goes HIGH simultaneously with WE HIGH, the output remainsin a high impedance state.TIMING WAVEFORM OF WRITE CYCLE NO. 1 (WE CONTROLLED) (9)AC CHARACTERISTICS - WRITE CYCLE(V CC = 5V ± 10%, All Temperature Ranges)(2)Input Pulse Levels GND to 3.0VInput Rise and Fall Times 3ns Input Timing Reference Level 1.5V Output Timing Reference Level 1.5VOutput LoadSee Figures 1 and 2Mode CE WE Output Power Standby H X High Z Standby Read L H D OUT Active WriteLLD INActive* including scope and test fixture.Note:Because of the ultra-high speed of the P4C1298, care must be taken when testing this device; an inadequate setup can cause a normal functioning part to be rejected as faulty. Long high-inductance leads that cause supply bounce must be avoided by bringing the V CC and ground planes directly up to the contactor fingers. A 0.01 µF highfrequency capacitor is also required between V CC and ground. To avoid signal reflections, proper termination must be used; for example, a 50Ωtest environment should be terminated into a 50Ω load with 1.73V (Thevenin Voltage) at the comparator input, and a 116Ω resistor must be used in series with D OUT to match 166Ω (Thevenin Resistance).Figure 1. Output LoadFigure 2. Thevenin EquivalentAC TEST CONDITIONSTRUTH TABLETIMING WAVEFORM OF WRITE CYCLE NO. 2 (CE CONTROLLED)(9,10)P4C1298/LORDERING INFORMATIONSELECTION GUIDEThe P4C1298 is available in the following temperature, speed and package options.SOJ SMALL OUTLINE IC PACKAGEPLASTIC DUAL IN-LINE PACKAGEP4C1298/LRECTANGULAR LEADLESS CHIP CARRIERSIDEBRAZED DUAL IN-LINE PACKAGEPage 11 of 11Document # SRAM135 REV OR REVISIONS DOCUMENT NUMBER :SRAM135DOCUMENT TITLE :P4C1298/P4C1298L ULTRA HIGH SPEED 64K x 4 STATIC CMOS RAM REV.ISSUE DATE ORIG. OF CHANGE DESCRIPTION OF CHANGE OR Apr-07JDB New Data Sheet元器件交易网。