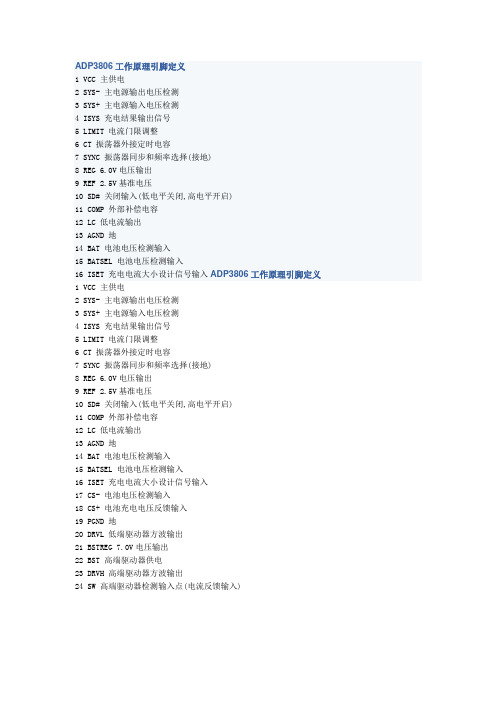

3.2.4 -3.38086引脚信号和功能

音频功率放大器LM386引脚图及功能

音频功率放大器LM386引脚图及功能1、LM386描述LM386是一种音频集成功放,具有自身功耗低、更新内链增益可调整、电源电压范围大、外接元件少和总谐波失真小等优点的功率放大器,广泛应用于录音机和收音机之中。

LM386是美国国家半导体公司生产的音频功率放大器,主要应用于低电压消费类产品。

为使外围元件最少,电压增益内置为20。

但在1脚和8脚之间增加一只外接电阻和电容,便可将电压增益调为任意值,直至200。

输入端以地位参考,同时输出端被自动偏置到电源电压的一半,在6V电源电压下,它的静态功耗仅为24mW,使得LM386特别适用于电池供电的场合。

特性静态功耗低,约为4mA,可用于电池供电;工作电压范围宽,4-12Vor5-18V;外围元件少;电压增益可调,20-200;低失真度;2、LM386电气参数1)极限参数:电源电压(LM386N-1,-3,LM386M-1)15V电源电压(LM386N-4)22V封装耗散(LM386N)1.25W(LM386M)0.73W(LM386MM-1)0.595W输入电压±0.4V储存温度-65℃至+150℃操作温度0℃至+70℃结温+150℃焊接信息焊接(10秒)260℃小外形封装(SOIC和MSOP)气相(60秒)215℃红外(15秒)220℃热电阻qJC(DIP)37℃/WqJA(DIP)107℃/WqJC(SO封装)35℃/W qJA(SO封装)172℃/W qJA(MSOP封装)210℃/W qJC(MSOP封装)56℃/W 2)电气特性3、LM386内部电路及工作原理LM386内部电路原理图如图所示。

与通用型集成运放相类似,它是一个三级放大电路。

第一级为差分放大电路,T1和T3、T2和T4分别构成复合管,作为差分放大电路的放大管;T5和T6组成镜像电流源作为T1和T2的有源负载;T3和T4信号从管的基极输入,从T2管的集电极输出,为双端输入单端输出差分电路。

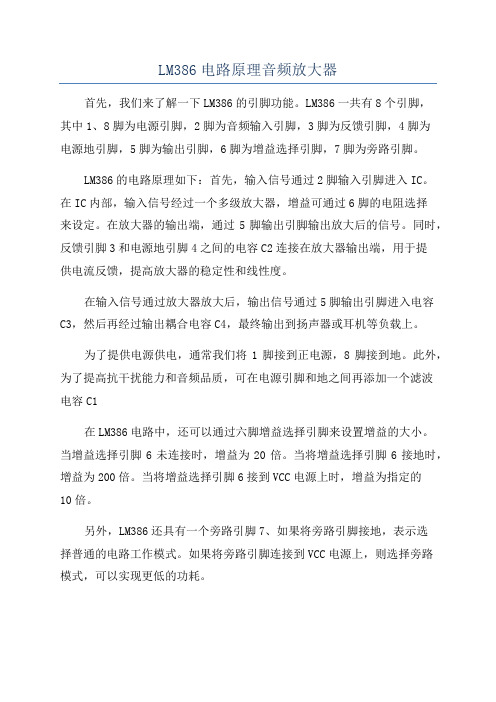

LM386电路原理音频放大器

LM386电路原理音频放大器首先,我们来了解一下LM386的引脚功能。

LM386一共有8个引脚,其中1、8脚为电源引脚,2脚为音频输入引脚,3脚为反馈引脚,4脚为电源地引脚,5脚为输出引脚,6脚为增益选择引脚,7脚为旁路引脚。

LM386的电路原理如下:首先,输入信号通过2脚输入引脚进入IC。

在IC内部,输入信号经过一个多级放大器,增益可通过6脚的电阻选择来设定。

在放大器的输出端,通过5脚输出引脚输出放大后的信号。

同时,反馈引脚3和电源地引脚4之间的电容C2连接在放大器输出端,用于提供电流反馈,提高放大器的稳定性和线性度。

在输入信号通过放大器放大后,输出信号通过5脚输出引脚进入电容C3,然后再经过输出耦合电容C4,最终输出到扬声器或耳机等负载上。

为了提供电源供电,通常我们将1脚接到正电源,8脚接到地。

此外,为了提高抗干扰能力和音频品质,可在电源引脚和地之间再添加一个滤波电容C1在LM386电路中,还可以通过六脚增益选择引脚来设置增益的大小。

当增益选择引脚6未连接时,增益为20倍。

当将增益选择引脚6接地时,增益为200倍。

当将增益选择引脚6接到VCC电源上时,增益为指定的10倍。

另外,LM386还具有一个旁路引脚7、如果将旁路引脚接地,表示选择普通的电路工作模式。

如果将旁路引脚连接到VCC电源上,则选择旁路模式,可以实现更低的功耗。

需要注意的是,由于LM386是低功耗集成电路,因此在选择电源时要注意其电流输出能力。

同时,为了保证音频质量,应尽可能降低输入信号的幅度,避免出现过载,以及合理选择反馈和耦合电容的数值。

总之,LM386是一款功能齐全且易于使用的音频放大器集成电路。

我们可以根据实际需要调整增益和工作模式,实现不同的音频放大应用。

希望以上内容能对你理解LM386电路原理有所帮助。

第5章8086引脚

⑧ALE,地址锁存允许信号 ⑨READY(Ready),准备就绪信号 ⑩INTR,可屏蔽中断请求信号 ⑪INTA,中断响应信号 ⑫NMI,非屏蔽中断请求信号 ⑬RESET,系统复位信号 ⑭DEN,数据允许信号 ⑮DT/R,数据发送/接收控制信号

⑯HOLD,总线保持请求信号输入 ⑰HLDA,总线保持响应信号 ⑱TEST,测试信号 ⑲CLK,时钟输入信号 ⑳VCC(+5V),GND

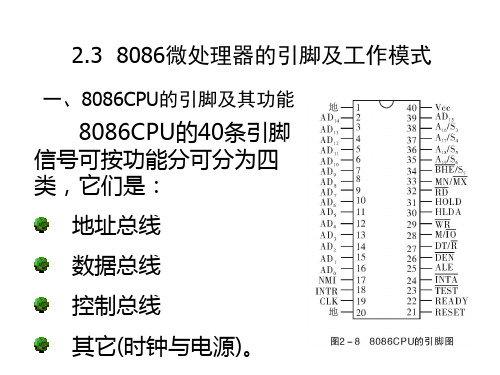

2.3 8086微处理器的引脚及工作模式

一、8086CPU的引脚及其功能

8086CPU的40条引脚 信号可按功能分可分为四 类,它们是:

地址总线 数据总线 控制总线

其它(时钟与电源)。

1.最小模式和最大模式概念

(1)最小模式: 在系统中只有一个微处理器。

(2)最大模式: 两个或多个微处理器(主处理器、协处理

(2)最大模式( MN/MX接地)

8086 CPU工作在最大模式时,其24~31引脚需重新定义, 如表2-4所示。

①QS1/QS0,指令队列状态信号。 ②S2、S1、S0 ,总线周期状态信号。 ③LOCK ,总线封锁信号。 ④RQ/GT1和RQ/GT0 ,总线请求信 号输入/总线请求信号允典型配置

1.8086最小工作模式的典型配置

在最小工作模式系统配置中,除了 8086CPU外,还需要在外围电路中加入:

· 1片8284A,作为时钟发生器。

· 3片8282(8位锁存器)或74LS373,作为 地址锁存器。

· 2片8286/8287或74LS245,作为双向 总线收发器,以增加数据总线的驱动能力。

2.8086最大工作模式的典型配置

从图2-9和图2-10中可以看出,8086CPU在最 大模式和最小模式之间的主要区别是:在最大模 式下,需要增加一个转换控制信号的电路,用来 对 CPU 发 出 的 控 制 信 号 进 行 变 换 和 组 合 , 即 8288总线控制器。

lm3886tf功放管引脚阻值

标题:LM3886TF功放管引脚阻值一、LM3886TF功放管介绍LM3886TF是一种高性能的Overture系列音频功放芯片,具有高品质音质和稳定的性能。

该芯片采用了国际先进的多晶技术,能够在低电压条件下提供更大的输出功率,广泛应用于音频功放系统中。

二、LM3886TF功放管引脚图示LM3886TF功放管引脚一共有11个,分别为V-, OUT1, GND, V+, BYP, IN-, IN+, COMP, GND, SD, MUTE, V-. 下面详细介绍每个引脚的功能及阻值。

三、LM3886TF功放管引脚功能及阻值1. V-:负电源输入端,用于连接负电源。

推荐的阻值为100kΩ。

2. OUT1:输出端1,连接输出器件或负载。

无需外接电阻。

3. GND:地线端,接地用。

无需外接电阻。

4. V+:正电源输入端,用于连接正电源。

推荐的阻值为100kΩ。

5. BYP:旁路输入端,旁路输入滤波电容用。

推荐的阻值为10kΩ。

6. IN-:差分输入端负极,接受差分输入信号。

推荐的阻值为10kΩ。

7. IN+:差分输入端正极,接受差分输入信号。

推荐的阻值为10kΩ。

8. COMP:补偿电路输入端,用于连接补偿电路。

推荐的阻值为22kΩ。

9. GND:地线端,接地用。

无需外接电阻。

10. SD:关断端,用于控制功放芯片的开关机。

推荐的阻值为10kΩ。

11. MUTE:静音端,用于控制功放芯片的静音功能。

推荐的阻值为10kΩ。

四、LM3886TF功放管引脚阻值选择注意事项1. 在选用引脚阻值时,应根据实际系统需求和设计规范选择合适的阻值。

选择过大或者过小的阻值都会影响芯片的性能和稳定性。

2. 建议在实际设计中进行测试验证,以确保选用的阻值符合系统要求。

五、结语LM3886TF功放管引脚阻值的选择对于功放系统的性能和稳定性具有重要影响,正确选用合适的阻值是保证系统正常运行的重要因素。

希望本文对LM3886TF功放管引脚阻值的选择有所帮助,也希望读者能在实际设计中根据具体情况进行合理选用,确保系统的稳定性和性能。

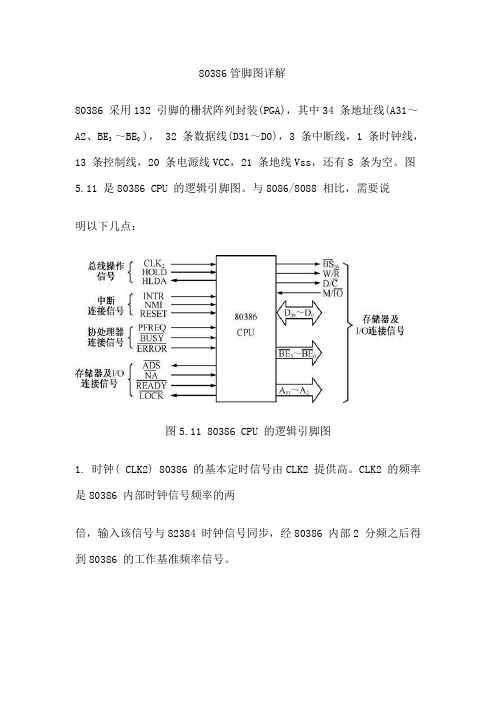

80386管脚图详解

80386管脚图详解80386 采用132 引脚的栅状阵列封装(PGA),其中34 条地址线(A31~A2、BE3 ~BE0 ), 32 条数据线(D31~D0),3 条中断线,1 条时钟线,13 条控制线,20 条电源线VCC,21 条地线Vss,还有8 条为空。

图5.11 是80386 CPU 的逻辑引脚图。

与8086/8088 相比,需要说明以下几点:图5.11 80386 CPU 的逻辑引脚图1. 时钟( CLK2) 80386 的基本定时信号由CLK2 提供高。

CLK2 的频率是80386 内部时钟信号频率的两倍,输入该信号与82384 时钟信号同步,经80386 内部2 分频之后得到80386 的工作基准频率信号。

2. 数据总线(D31~D0) 它为80386 和其他设备之间提供数据通路,32 位数据总线,双向三态,一次可传送8 位、16 位或32 位数据,由输入信号(BE3 ~BE0 )和BE16确定,在任何写操作周期(包括暂停周期和停机周期),80386 总是驱动数据总线的所有32 位信号,而不管当前总线的实际宽度。

·136·微机原理与接口技术3. 地址总线(A31~A2,BE3 ~BE0 )1.(1) A31~A2:地址总线,输出三态,和BE3 ~BE0 相结合起到32 位地址的作用。

80386 地址总线包含A2~A31 地址线和字节选通线BE3 ~BE0 。

BE3 ~BE0 线的功能与8086 和80286 系统的A0 和BHE 的非常相似,它们是内部地址信号A0 和A1 的译码。

80386 有一个32 位数据总线,所以内存可以建立4B 宽的存储体。

BE3 ~BE0 信号是用来选通这4 个存储体。

这些单独选通可以使80386 的内存传送或者接收字节、字或者双字。

1.(2) BE3 ~BE0 :字节选通信号。

用于选通在当前的传送操作要涉及4B 数据中的那几个字节。

LM3886功放电路图解析

LM3886功放电路图解析在额定工作电压下最大可达68W的连续不失真平均功率,同样具有比较完善的过压过流过热保护功能,最可贵的是它具有自动抗开关机时的电流冲击的功能,使扬声器能够安全的工作。

1.Im3886功放作用2.Im3886功放电路图3.Im3886功放工作原理Im3886功放工作原理如下:C1、C2为电源退耦电容,取值0.01uF--1uF之间,不同大小及品牌对声音有点影响,一般取值104P,即0.1uF,然后随便抓随便装,位置放得下即可。

C7、R1组成静音电路,容量和电阻的值决定了静音时间长短,电容可取10uF--100uF,电阻可取10K--100K,值越大则静音时间越长,一般取图中参数即可,对音质无影响,随便抓随便上,注意耐压大于50V。

C8、R6组成所谓的“茹贝尔网络”,配合输出电感起稳定电路的作用,C8一般取值0.01uF--0.22uF之间,R6一般取1--22欧之间,由电容的取值大小以及电阻的选用功率大小可看出电路的稳定情况,一般用得越大则说明电路存在稳定性问题的可能越大。

本处选用104和1/4W 10欧,实测过不装也没问题,装上为求心安,毕竟不怕一万,只怕万一。

RL为输出电感和输出电阻并联组成,起隔离喇叭反向电动势作用,电感及电阻取值会对声音取向有小影响,此处用1.5mm漆包线绕15-20圈,成直径6mm左右电感,中间穿一个10--22欧1W的电阻。

R2、R3两个电阻决定了电路的闭环增益,即放大倍数,值为R2/R3+1,R2一般取33K--56K之间,R3一般取1K--3.3K之间,不同搭配对声音影响比较大,本处选47K、3.3K,放大倍数约为15.5倍,如前级输出电平较低,可适当减小R3的值或增大R2的值,放大倍数建议不要超过20倍。

C9为反馈电容,品牌以及容量对电路的声音取向有相当大的影响,最好用音频专用无极型的,一般取值在10uF--100uF之间,容量越大,则低频下潜会越深,但高频会相对变暗(不同电容会有不同表现,愿意折腾的就换这个电容玩了),反之表现就相反。

lm3886tf功放管引脚阻值 -回复

lm3886tf功放管引脚阻值-回复什么是LM3886TF功放管?LM3886TF是一种高性能音频功放芯片,它采用了全新的高电流的稳压增益器,具有很低的失真、高的输出功率和优异的总谐波失真。

LM3886TF通常用于音频放大器,提供高品质的音频放大效果。

LM3886TF功放管的引脚配置和功用是什么?LM3886TF功放管具有11个引脚,它们分别是:Mute、ByPass、Input1、Input2、GND、Vcc、Vee、Output1、Output2、Vsense和PVcc。

1. Mute引脚:用于控制功放管的静音功能。

当该引脚为低电平时,功放器静音;当该引脚为高电平时,功放器工作。

2. ByPass引脚:用于控制Mute引脚的使能功能。

当该引脚为低电平时,Mute引脚不起作用;当该引脚为高电平时,Mute引脚功能正常。

3. Input1和Input2引脚:用于输入音频信号。

通常的连接方式是将音频源的正极接到Input1引脚,负极接到Input2引脚。

4. GND引脚:作为地线引脚,与音频信号源的地线相连。

5. Vcc引脚:供给功放管的正电压。

6. Vee引脚:供给功放管的负电压。

7. Output1和Output2引脚:用于输出放大后的音频信号。

根据需要,可以连接至扬声器或其他音频设备。

8. Vsense引脚:用于检测输出电流。

9. PVcc引脚:供给功放管的电源。

在使用LM3886TF功放管时,我们需要注意的是:1. 引脚的电源接法需严格按照数据手册提供的电源接法来连接,以确保功放管的正常工作。

2. 在连接输入音频信号时,应注意正负极的正确连接,并避免短路或误接。

3. 根据输出功率的需求,选择合适的输出连接方式,以充分利用LM3886TF功放管提供的音频放大效果。

4. 在连接扬声器或其他音频设备时,应注意输出引脚的正负极的正确接法,并避免短路或误接。

5. 根据设计需求,合理选择Mute、ByPass等引脚的连接方式,以实现静音、控制等特殊功能。

优秀的功放IC,LM3886基本应用电路图

优秀的功放IC,LM3886基本应用电路图LM3886是单声道、中功率、高性能音频功放IC,是美国国家半导体(NS)公司的“序曲”(OVerture)音频功放系列具有代表性的IC之一。

它采用11脚TO-220封装并具有输入静音功能,适合小型有源音箱、环绕声放大器和高保真立体声电视机等用作功放。

LM3886主要性能简介1、连续平均输出功率:60W/4Ω(Vcc=±28V)30W/8Ω(Vcc=±28V)50W/8Ω(Vcc=±35V)2、瞬时最大输出功率: 150W3、失真度:(THD+噪声)0.03%(20Hz~20kHz)4、噪声电平:2.0μV5、信噪比:>92dB6、互调失真:(按SMPTE标准)0.004%此IC的最大特点是自身保护功能齐全,无须外接各种保护电路,它内含NS公司研制的SPIKe(自身瞬时温度)保护电路,对输出级晶体管的安全工作区(SOA)进行动态检测与保护,从而全面实现过压、欠压、过载、输出短路(包括短路到地与短路到电源)、热失控和瞬时温度冲击等保护功能。

附图1是3886内部等效电路。

电路工作原理简析R2为LM3886的同相输入端提供偏压;并联在两个输入端的C2是用来减小放大器的高频增益,以免输出管出现振荡,同时抑制输入的电磁干扰噪声;R5、R4、C4组成反馈回路,放大器的低频响应和高频转折频率fH取决于R3、C3;R4、C4、R5和R3决定高频增益和低通转折频率fL(fH、fL的计算公式略)。

C4是补偿元件,它与R4、R5共同起减小高频增益的作用。

R8、R9、C5与开关(图中虚线所示)组成静音控制电路:当开关断开时,LM3886停上输出,即静音起作用;接通开关时静音解除,R8将⑧脚输出电流限制到0.5mA(LM3886的⑧脚电流≥0.5mA)。

C5为静音通、断提供较大的时间常数。

R6、C6的作用为防止放大器产生高频振荡。

L1、R7作用:如果负载呈容性(如扬声器电缆较长),则放大器在高频下会过载,并使方波响应出现转折,为避免此现象,在输出端串入LR组成的并联电路,此时L呈现较大感抗,10Ω电阻将放大器与容性负载隔离开来并降低L与容性负载所构成回路的Q值;低频下则10Ω电阻被L短路,放大器通过感抗很小的L直接驱动负载。

43 80868088 CPU的引脚信号 和工作模式

8088

4.3.1.2 最小模式的引脚信号

1. 2. 3.

4.

5.

数据和地址引脚 读写控制引脚 中断请求和响应引脚 总线请求和响应引脚 其它引脚

1. 数据和地址引脚

AD7~AD0(Address/Data) 地址/数据分时复用引脚,双向、三态 在访问存储器或外设的总线操作周期中, 这些引脚在第一个时钟周期输出存储器或 I/O端口的低8位地址A7~A0 其他时间用于传送8位数据D7~D0

(1)20位地址总线—— A采用3个三态透明锁存器8282进行锁存和驱动 8282 A19~A16 19/S6~A16/S3 STB (2)8位数据总线—— OE* 8088 采用数据收发器8286进行驱动 A15~A8 A15~A8 8282 STB (3)系统控制信号—— OE* 由8088引脚直接提供8282 A7~A0 AD7~AD0

INTA*(Interrupt Acknowledge) 可屏蔽中断响应,输出、低电平有效 有效时,表示来自INTR引脚的中断请求 已被CPU响应,CPU进入中断响应周期 中断响应周期是连续的两个,每个都发出 有效响应信号,以便通知外设他们的中断 请求已被响应、并令有关设备将中断向量 号送到数据总线

“引脚”小结

CPU引脚是系统总线的基本信号 可以分成三类信号: 8位数据线:D0~D7 20位地址线:A0~A19 有问题! 控制线:

ALE、IO/M*、WR*、RD*、READY INTR、INTA*、NMI,HOLD、HLDA RESET、CLK、Vcc、GND

“引脚”提问

最大工作模式

4.3.1.1 8086/8088的两种工作模式(续)

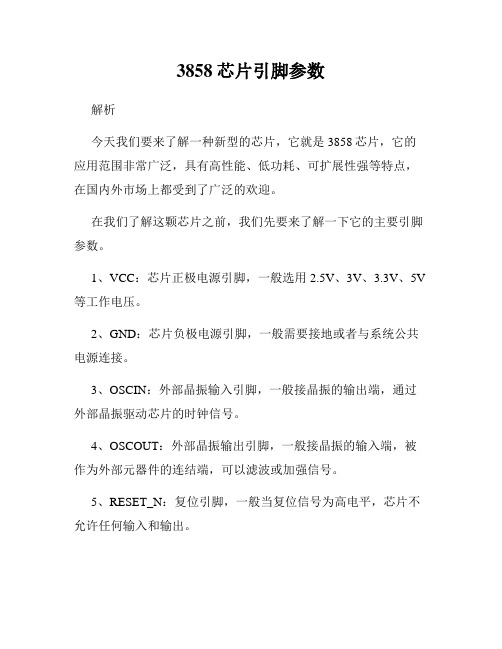

3858芯片引脚参数

3858芯片引脚参数解析今天我们要来了解一种新型的芯片,它就是3858芯片,它的应用范围非常广泛,具有高性能、低功耗、可扩展性强等特点,在国内外市场上都受到了广泛的欢迎。

在我们了解这颗芯片之前,我们先要来了解一下它的主要引脚参数。

1、VCC:芯片正极电源引脚,一般选用2.5V、3V、3.3V、5V 等工作电压。

2、GND:芯片负极电源引脚,一般需要接地或者与系统公共电源连接。

3、OSCIN:外部晶振输入引脚,一般接晶振的输出端,通过外部晶振驱动芯片的时钟信号。

4、OSCOUT:外部晶振输出引脚,一般接晶振的输入端,被作为外部元器件的连结端,可以滤波或加强信号。

5、RESET_N:复位引脚,一般当复位信号为高电平,芯片不允许任何输入和输出。

6、IRQ_N:中断请求引脚,一般用于芯片与外部系统的通信。

当IRQ01为低电平,表示其他设备需要处理,芯片需要中断来执行操作。

7、GPIO0-20:通用输入输出引脚,可由程序控制为输入或输出端口,在不同的应用场景中功能不同。

8、VREF:ADC参考电压输入引脚,一般为2.5V或其他电压值,用于芯片内部AD转换器的电压参考。

9、AIN0-7:模拟信号输入引脚,一般用于连接外部传感器或其他信号源输入,用来接收模拟信号并转换成数字信号。

10、AVDD:芯片内部模拟电路的正极电源引脚,一般与VCC共用电源,但由于芯片的电流需求不同,电源接线也不同。

11、AVSS:芯片内部模拟电路的负极电源引脚,一般与GND相连,也需要与VREF共用地。

以上就是3858芯片的主要引脚参数介绍。

当然,这些参数并不是只有这些,不同的芯片厂家可能会有一些小的差异,但我们所需要关注的引脚参数也不会大到十分复杂。

总结:本文主要向大家介绍了3858芯片的主要引脚参数,不同的芯片可能会有不同的引脚参数,但本文的内容足以解决大部分用户在使用芯片时所遇到的问题。

希望本文能够对您有所帮助。

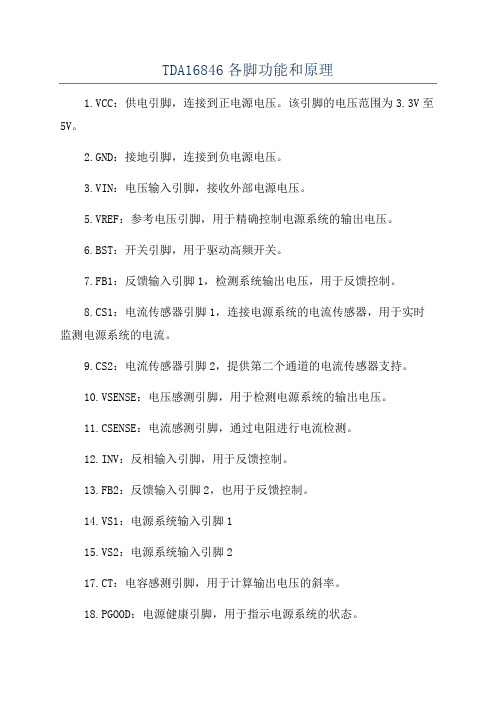

TDA16846各脚功能和原理

TDA16846各脚功能和原理

1.VCC:供电引脚,连接到正电源电压。

该引脚的电压范围为3.3V至5V。

2.GND:接地引脚,连接到负电源电压。

3.VIN:电压输入引脚,接收外部电源电压。

5.VREF:参考电压引脚,用于精确控制电源系统的输出电压。

6.BST:开关引脚,用于驱动高频开关。

7.FB1:反馈输入引脚1,检测系统输出电压,用于反馈控制。

8.CS1:电流传感器引脚1,连接电源系统的电流传感器,用于实时监测电源系统的电流。

9.CS2:电流传感器引脚2,提供第二个通道的电流传感器支持。

10.VSENSE:电压感测引脚,用于检测电源系统的输出电压。

11.CSENSE:电流感测引脚,通过电阻进行电流检测。

12.INV:反相输入引脚,用于反馈控制。

13.FB2:反馈输入引脚2,也用于反馈控制。

14.VS1:电源系统输入引脚1

15.VS2:电源系统输入引脚2

17.CT:电容感测引脚,用于计算输出电压的斜率。

18.PGOOD:电源健康引脚,用于指示电源系统的状态。

19.OVP:过压保护引脚,用于监测输出电压,一旦超过设定阈值,就会触发过压保护。

20.OCSET:过流保护引脚,用于设置过流保护的阈值。

21.OCP:过流保护触发引脚,当输出电流超过设定的阈值时触发过流保护。

22.REF:参考电压输出引脚,可以将此引脚连接到其他电路中作为参考电压。

3.2.4 -3.38086引脚信号和功能

HLDA

BHE A19 ~ A16

8282

(2)

OE

8286

8086

MN/MX

ALE

DIR

(2) OE

A15 ~ A0 HLDA D15 数据 ~ 总线 D0

地 址 总 线

8288 INTA

MRDC MWTC IORC IOWC

DT/R

DEN

S0 S1 S2 INTR NMI

S0 S1 S2

INTA MEMR MEMW IOR IOW

17、RESET:复位信号

输入,高电平有效。使CPU停止现行操作,并进行初始化: 标志寄存器,IP,DS,SS,ES及指令队列清零;

CS设置为FFFFH。

18、CLK:时钟信号(单相,占空比为1/3) 8086 5MHZ 8086-1 10MHZ 8086-2 8MHZ

19、VCC,GND:电源及地

BHE

A0

0

0 0 1 1

1

0

1

数据总线使用情况 16位字传送 数据总线高8位,奇地址 数据总线低8位,偶地址 无效

第 12 页

2 最小模式下引脚信号和功能

4、ALE:地址锁存允许信号 输出、高电平有效。表示总线上的是地址信息,在T1产生正 脉冲,利用其下降沿锁存地址信息。 5、 M / IO :存储器/输入输出控制信号 输出,三态,高电平表示当前的信息是地址信息;低电平表 示当前访问的是I/O口。 6、 RD :读信号 输出,三态,低电平有效。表示当前总线周期正在读存储器 或从I/O口输入信息。 7、 WR :写信号 输出,三态,低电平有效。表示CPU正向存储器写入数据或 向I/O口输出数据。

称为“存储单元”。

• 每个字节用一组二进制数进行编号,称为“地址

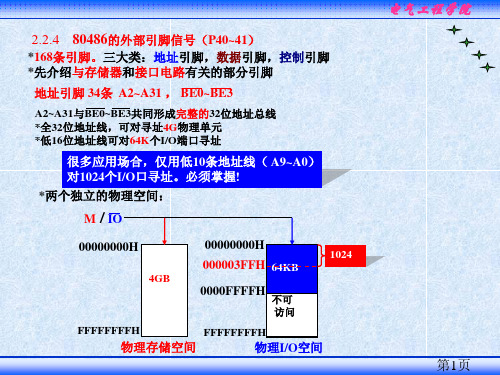

(08)80486的外部引脚信号2.2.4

BE信号与A0、A1的关系

BE0 0 1 1 1 BE1 X 0 1 1 BE2 X X 0 1 BE3 X X X 0 A1 0 0 1 1 A0 0 1 0 1

在BE信号配合下,数据总线还可以按字节传送: BE0:对应D0~D7,为低,实现该字节的传送 BE1:对应D8~D15,为低,实现该字节的传送 BE2:对应D16~D23,为低,实现该字节的传送 BE3:对应D24~D31,为低,实现该字节的传送 地址总线 BE3 BE2 BE1 BE0

4GB

00000000H 000003FFH 64KB 0000FFFFH

不可 访问

1024

FFFFFFFFH

FFFFFFFFH

物理存储空间

物理I/O空间

第1页

电气工程学院

*字节控制信号BE0~BE3(Byte Enable)

地址总线的组成部分,他们可以产生A0和A1,与前辈CPU兼容。 它们还分别对应数据线。

wrwriteread输出读写控制lock总线锁定486cpu独占总线不允许其它主控设备占用总线不允许处理器以外的信号打断当前总线的操作3总线控制信号adsaddressstatus地址状态输出信号为低表明地址信号和总线定义信号miodcwr等有效它标志一个总线周期的开始

电气工程学院

2.2.4 80486的外部引脚信号(P40~41)

控制类引脚 1)CLK 时钟信号 提供基本的定时和内部的工作频率 2)总线周期定义类信号 *M / IO (Memory/IO port) 输出 (**) 当AD输出一个地址信号时,是访问存储器还是访问I/O端口? M / IO信号从逻辑上把二者区分开: =1,访问存储器,I/O不予响应 =0,访问I/O端口,M不予响应

lm3886电路讲解

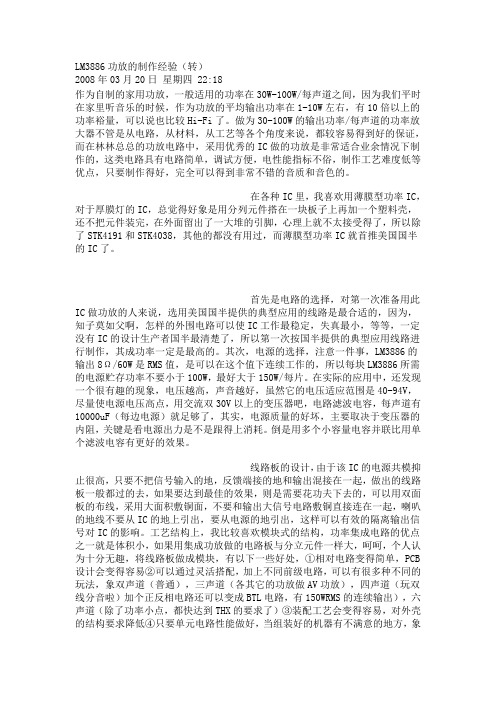

LM3886功放的制作经验(转)2008年03月20日星期四 22:18作为自制的家用功放,一般适用的功率在30W-100W/每声道之间,因为我们平时在家里听音乐的时候,作为功放的平均输出功率在1-10W左右,有10倍以上的功率裕量,可以说也比较Hi-Fi了。

做为30-100W的输出功率/每声道的功率放大器不管是从电路,从材料,从工艺等各个角度来说,都较容易得到好的保证,而在林林总总的功放电路中,采用优秀的IC做的功放是非常适合业余情况下制作的,这类电路具有电路简单,调试方便,电性能指标不俗,制作工艺难度低等优点,只要制作得好,完全可以得到非常不错的音质和音色的。

在各种IC里,我喜欢用薄膜型功率IC,对于厚膜灯的IC,总觉得好象是用分列元件搭在一块板子上再加一个塑料壳,还不把元件装完,在外面留出了一大堆的引脚,心理上就不太接受得了,所以除了STK4191和STK4038,其他的都没有用过,而薄膜型功率IC就首推美国国半的IC了。

首先是电路的选择,对第一次准备用此IC做功放的人来说,选用美国国半提供的典型应用的线路是最合适的,因为,知子莫如父啊,怎样的外围电路可以使IC工作最稳定,失真最小,等等,一定没有IC的设计生产者国半最清楚了,所以第一次按国半提供的典型应用线路进行制作,其成功率一定是最高的。

其次,电源的选择,注意一件事,LM3886的输出8Ω/60W是RMS值,是可以在这个值下连续工作的,所以每块LM3886所需的电源贮存功率不要小于100W,最好大于150W/每片。

在实际的应用中,还发现一个很有趣的现象,电压越高,声音越好,虽然它的电压适应范围是40-94V,尽量使电源电压高点,用交流双30V以上的变压器吧,电路滤波电容,每声道有10000uF(每边电源)就足够了,其实,电源质量的好坏,主要取决于变压器的内阻,关键是看电源出力是不是跟得上消耗。

倒是用多个小容量电容并联比用单个滤波电容有更好的效果。

ADP3806工作原理引脚定义

ADP3806工作原理引脚定义1 VCC 主供电2 SYS- 主电源输出电压检测3 SYS+ 主电源输入电压检测4 ISYS 充电结果输出信号5 LIMIT 电流门限调整6 CT 振荡器外接定时电容7 SYNC 振荡器同步和频率选择(接地)8 REG 6.0V电压输出9 REF 2.5V基准电压10 SD# 关闭输入(低电平关闭,高电平开启)11 COMP 外部补偿电容12 LC 低电流输出13 AGND 地14 BAT 电池电压检测输入15 BATSEL 电池电压检测输入16 ISET 充电电流大小设计信号输入ADP3806工作原理引脚定义1 VCC 主供电2 SYS- 主电源输出电压检测3 SYS+ 主电源输入电压检测4 ISYS 充电结果输出信号5 LIMIT 电流门限调整6 CT 振荡器外接定时电容7 SYNC 振荡器同步和频率选择(接地)8 REG 6.0V电压输出9 REF 2.5V基准电压10 SD# 关闭输入(低电平关闭,高电平开启)11 COMP 外部补偿电容12 LC 低电流输出13 AGND 地14 BAT 电池电压检测输入15 BATSEL 电池电压检测输入16 ISET 充电电流大小设计信号输入17 CS- 电池电压检测输入18 CS+ 电池充电电压反馈输入19 PGND 地20 DRVL 低端驱动器方波输出21 BSTREG 7.0V电压输出22 BST 高端驱动器供电23 DRVH 高端驱动器方波输出24 SW 高端驱动器检测输入点(电流反馈输入)1.主供电VINVIN通过R13(10Ω)的电阻向ADP3806供电;VIN通过Q1→L1→Rcs→BATTERY对电池充电。

2.线性电压通过ADP3806内部的VREF、+VREGLIVELO BIAS线性电源产生2.5V的REF电压,6.0的REG 电压的7.0V的BSTREG电压。

3.驱动控制电路BOOTSTRAPPED SYNCHRONOUS DRIVER为充电驱动控制电路,为ADP3806的核心电路,受3个信号的控制。

3868集成电路

XS3868蓝牙立体声音频模块编制:sisim2012-03-20■ 功能描述※ XS3868是一个高集成度,低成本,低功耗的蓝牙立体声音频模组符合Bluetooth 2.0规范。

※ 支持A2DP V1.2,AVRCP V1.4 profiles.集成EERPOM,可配置工作模式及参数。

※ 立体声音频输出可直接驱动40mW@32Ω speeker 而不需要隔直电容集成上电复位及可编程的低电压监测功能。

※ 6个按键输入,包括开关机键、配对键、音量加、音量减、上一曲、下一曲。

※ 2个指示灯用于指示不同的工作状态。

■ 技术参数CA TEGOIESFEA TURE IMPLEMENTA TIONBluetoothV ersion 2.0F requency 2.402-2.480GHz Class2Max Transmit Power4dBm(at antenna pad) Receive sensitivity Better than-82dBm Range 10metersData Rates Up to 3Mbps(over the air) Wireless SpecificationUART DA TA Transfer Rate 115200bpsHost lnterface UARTNo flow control supportAudio lnterfaces Microphone Mono microphone input with bias A2DP-Sink OnlyA VRCP-ControllerOnly ProfilesSupply 3.0V-3.6V DC Supply voltage IO1.7V-3.6V DCOperational-L ess than 25 mA(active) PowerConsumption CurrentConsumption Ldle(sleep )<1.0mA Connections External Antenna Connection via S M T pad PhysicalDimensions30m m ×17mm×3.4mmXS3868蓝牙立体声音频模块蓝牙立体声音频模块■PIN 腳位定义图序号 名称 类型 描述1 2 AOM Audio 音频输出公共端 3 AOL Audio 左声道音频输出4 AOR Audio 右声道音频输出 5 MICIN Audio Mic 输入脚 6 MICBIAS Audio MICBIAS7 LED1 Sink 指示灯1控制端 8 LED2 Sink 指示灯2控制端9 10 VBUCK Digital空脚11 GND Power 地 12 VCC Power13 1V8Power LDO输出1.8V 14 ONKET Digital 开关机按键信号/PLA Y/PAUSE 15 VOL+ Digital 音量加按键信号 16 VOL- Digital 音量减按键信号 17 RESET Digital 外部复位脚/NC18 19 MFB1 Digital配对按键信号 20 UAR T _TX Digital UART 发送信号 21 UAR T _RX Di g ital UART 接收信号 22 PrevDigital上一曲23Next Digital 下一曲AUDIOENABLEVBAT MODE POWER■ 尺寸图■ 模块工作流程:1:模块上电时,发出“嘟嘟“两声,表示模块已经上电工作,这时LED1,LED2会交替闪动几次, 然后LED1灭掉,LED2常亮,这时表示蓝牙模块在回连上一次配对过的设备。

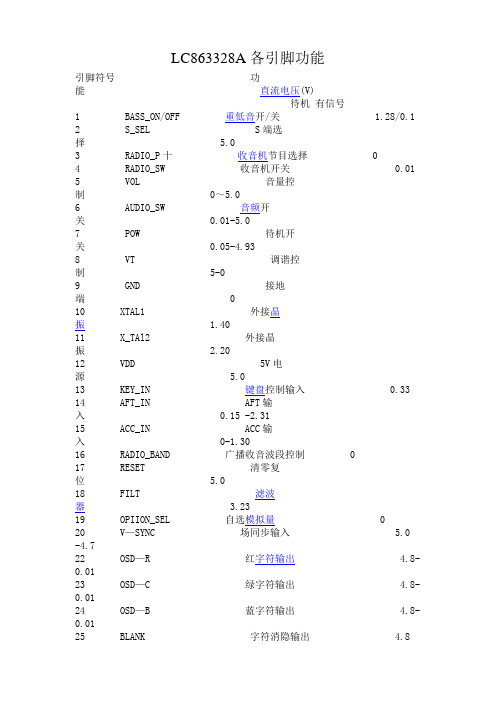

1.LC863328A各引脚功能

LC863328A各引脚功能引脚符号功能直流电压(V)待机有信号1 BASS_ON/OFF 重低音开/关 1.28/0.12 S_SEL S端选择 5.03 RADIO_P十收音机节目选择 04 RADIO_SW 收音机开关 0.015 VOL 音量控制 0~5.06 AUDIO_SW 音频开关 0.01-5.07 POW 待机开关 0.05-4.938 VT 调谐控制 5-09 GND 接地端 010 XTAL1 外接晶振 1.4011 X_TAl2 外接晶振 2.2012 VDD 5V电源 5.013 KEY_IN 键盘控制输入 0.3314 AFT_IN AFT输入 0.15 -2.3115 ACC_IN ACC输入 0-1.3016 RADIO_BAND 广播收音波段控制 017 RESET 清零复位 5.018 FILT 滤波器 3.2319 OPIION_SEL 自选模拟量 020 V—SYNC 场同步输入 5.0 -4.722 OSD—R 红字符输出 4.8- 0.0123 OSD—C 绿字符输出 4.8- 0.0124 OSD—B 蓝字符输出 4.8- 0.0125 BLANK 字符消隐输出 4.8 -0.0126 HALFTONE 半透明控制 4.8- 0.0127 DATA 数据线 4.7428 CIDCK 时钟线 4.8329 SDA I2C总线数据线 5.030 SCL I2C总线时钟线 5.0- 4.831 SAFrY 保护控制信号输入端 0.83- 5.032 PC PC接口 5.033 SD 同步识别信号输入 0.30- 1.234 REMOCON 遥控信号输入 4.235 SIF1 NTSC中频切换 5.036 RADIO_P- 收音机节目选择 5.037 TV/AV TV/AV切换 0.06-538 AV1/AV2 AVl/AY2转换 0.06-539 MUET 静音 0.06-540 BAND3_BU 频段切换3 0.0-0.2241 BAND2_BH 频段切换2 5.042 BAND1_BL 频段切换1 5.0表注1.电压值是用数字万用表实测,电阻值用MF—47型普通万用表Rx1k挡实测。

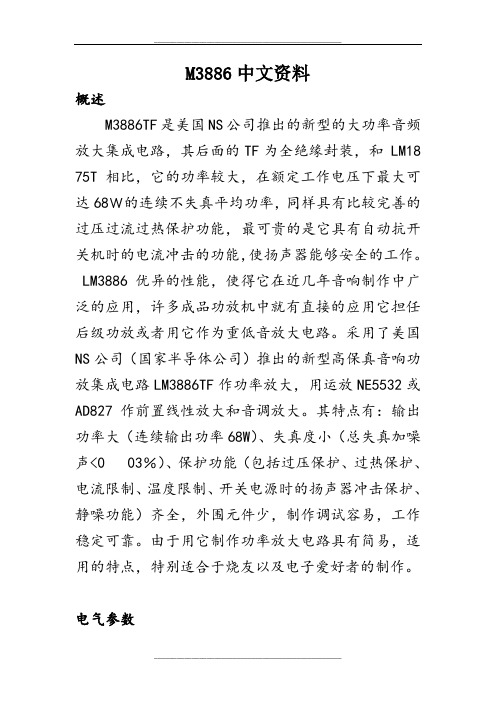

LM3886中文资料

M3886中文资料概述M3886TF是美国NS公司推出的新型的大功率音频放大集成电路,其后面的TF为全绝缘封装,和 LM18 75T相比,它的功率较大,在额定工作电压下最大可达68W的连续不失真平均功率,同样具有比较完善的过压过流过热保护功能,最可贵的是它具有自动抗开关机时的电流冲击的功能,使扬声器能够安全的工作。

LM3886优异的性能,使得它在近几年音响制作中广泛的应用,许多成品功放机中就有直接的应用它担任后级功放或者用它作为重低音放大电路。

采用了美国NS公司(国家半导体公司)推出的新型高保真音响功放集成电路LM3886TF作功率放大,用运放NE5532或AD827作前置线性放大和音调放大。

其特点有:输出功率大(连续输出功率68W)、失真度小(总失真加噪声<003%)、保护功能(包括过压保护、过热保护、电流限制、温度限制、开关电源时的扬声器冲击保护、静噪功能)齐全,外围元件少,制作调试容易,工作稳定可靠。

由于用它制作功率放大电路具有简易,适用的特点,特别适合于烧友以及电子爱好者的制作。

电气参数LM3886TF在VCC=VEE=28V、 4欧负载时能达到6 8W的连续平均功率,在VCC=VEE=35V,8欧负载时能达到50W的平均功率。

具有较宽的电源电压范围VCC+ VEE为20V-94V;总谐波失真+噪声:60W 20Hz<F;转换速率(SLEW RATE):VIN=2.0VP-P、tRISE=2ns 时的值为 19V /us总静态电流:50mA输入偏流:0.2uA增益带宽乘积: 8 MHZ内部电路图应用电路(1)应用电路LM3886带过压、过高温保护并且具有静噪功能的68W单声道高保真功率放大器,其主要电气参数如表所示。

LM3886采用11脚TO-220封装。

LM3886典型应用电路如图3所示。

LM3886在供电电压为。

10V以上时即可工作,只是输出功率降低。

IM3886的⑧脚为静音控制端,当流过该脚的电流大于1mA时,输出电路执行静音操作,输出端无信号输出。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

15、READY:准备好信号

输入,高电平有效。高电平表示存储器或I/O口已准备好接 收数据,外部使READY为低电平CPU要插入等待周期。

第 15 页

16、TEST:测试信号 输入,低电平有效。有效时CPU退出WAIT指令。

3、RQ/GT0,RQ/GT1:总线请求/总线允许信号

双向,低电平有效。有两个总线请求与总线响应信号,支

持多处理器工作。

4、QS1,QS0:指令队列状态信号

输出,两个信号组合指示指令队列状态。

第 20 页

3.3.1 8086的存储器组织

1 存储器物理组织

• 80X86微机内存储器以“字节”为基本单位,

说明: (1)由3片8282(低电平锁存,功能同74LS373)锁存地

址A0~A19和BHE。ALE为锁存信号。

(2)由2片8286(双向缓冲器,功能同74LS244)做数据 总线D15~D0的缓冲器,以增加总线驱动能力。 / R做方向 DT 选择, DEN 为选通信号。 (3)控制信号M / IO 和RD , WR 完成信息传递控制。

地址的位数决定了可以编号的字节的个数,也就是内存储 器的大小,称作容量。

可编号的字节数

n位地址

2n个字节

用20位二进制表示存储器地址: 最小地址为00000H(00000000000000000000),

最大地址为FFFFFH(11111111111111111111),

共有220个不同的地址,最多可以连接1M B的存储器。 存放数据: 低位存低地址单元,高位存高地址单元 字节型,字型,双字型数据如何存放?

第9 页

2 最小模式下引脚信号和功能

当8086的引脚MN/MX接成高电平时CPU处于最小模式工 作方式,此时系统中仅有一个处理器。在此模式下 CPU各引脚定义如下:

1、AD0~AD15:地址/数据复用总线

双向,三态,高电平有效。分时传送16位数据和地址的

低16位。由ALE锁存地址信息。在总线周期T1用来输出 地址,在其他时钟周期中,读周期时处于悬浮状态,写 周期时传送数据。

8086的总线周期 中断响应 读I/O端口 写I/O端口 暂停 取指 读存储器(数据) 写存储器 无效(无总线周期)

8288的输出命令

INTA

IORC IOWC、 AIOWC

/

MRDC MRDC MWTC、 AMWC

/

第 19 页

3 最大模式下引脚信号和功能

2、LOCK:总线封锁信号

三态,输出,低电平有效。有效时禁止其他部件占用总线。

FFFFFH

34H 11H

第 23 页

3.3.1 8086的存储器组织

2 存储器分段结构

8086 CPU为了寻址1 MB的存储空间,采用了分段的形 式,即将1 MB的存储空间分成若干个逻辑段,而4个 当前逻辑段的基地址设置在CPU内的4个段寄存器中, 即代码段寄存器CS、数据段寄存器DS、堆栈段寄存器 SS和附加段寄存器ES。 一个程序可使用一个逻辑段或多个逻辑段。 每个逻辑段小于等于64KB。 逻辑段之间可以是连续的、分开的、部分重叠或完全 重叠的。

29

28 27 26 25 24

输出、三态

输出、三态 输出、三态 输出、三态 输出 输出

第6 页

DEN

ALE

INTA

8086引脚信号定义

最大方式信号(MN/=GND)

RQ / GT 1,0 请求/允许总线访问控

制

30,31

29 26~28

双向

输出、三 态 输出、三 态

LOCK

S 2、1、0 S S

称为“存储单元”。

• 每个字节用一组二进制数进行编号,称为“地址

存储单元 的地址

”

0 23456 65535 10010011

字节(存储单元)

存储单元的内容

假设“地址”为23456的单元存放了数据10010011, 写作(23456)= 10010011

第 21 页

3.3.1 8086的存储器组织

BHE

A0

0

0 0 1 1

1

0

1

数据总线使用情况 16位字传送 数据总线高8位,奇地址 数据总线低8位,偶地址 无效

第 12 页

2 最小模式下引脚信号和功能

4、ALE:地址锁存允许信号 输出、高电平有效。表示总线上的是地址信息,在T1产生正 脉冲,利用其下降沿锁存地址信息。 5、 M / IO :存储器/输入输出控制信号 输出,三态,高电平表示当前的信息是地址信息;低电平表 示当前访问的是I/O口。 6、 RD :读信号 输出,三态,低电平有效。表示当前总线周期正在读存储器 或从I/O口输入信息。 7、 WR :写信号 输出,三态,低电平有效。表示CPU正向存储器写入数据或 向I/O口输出数据。

INTR NMI

第 18 页

3 最大模式下引脚信号和功能

1、S2,S1,S0总线周期状态信号(26-28)

输出,三个信号组合产生系统控制信号,这些信号由 总线控制器8288译码产生响应的控制信号。

S2 0 0 0 0 1 1 1 1 S1 0 0 1 1 0 0 1 1

S0 0 1 0 1 0 1 0 1

第 22 页

3.3.1 8086的存储器组织

存储器操作

读操作:从某个存储单元取出事先存储的程序指令或数据。 读操作不改变原存储单元的内容。 写操作:把一个数据存入指定的存储单元。写操作之后, 该存储单元原来的内容被新的内容所“覆盖”,不复存在 。 “访问(Access)”:一次存储器的读操作或写操作统称为对存储 器 的一次“访问”。 00000H 从20300H单元读出它的 内容“34H”之后,该单元 20300H 的内容仍然是“34H”。 向20300H单元写入“11H” 之后,该单元内容变成 “11H”,原来的数据“34H”

最大64KB

段”等。

第 25 页

3.3.1 8086的存储器组织

8086引脚图:

8086的40条引脚信号按功 能可分为四部分——地址总线、 数据总线、控制总线以及其他 (时钟与电源)。

第3 页

3.2.4 8086引脚信号和工作模式

1 8086引脚信号和功能

(S2)M/IO RD (LOCK)WR (S0)DEN (S1)DT/R 总线 (RQ0)HOLD 控制 (RQ1)HLDA READY CPU TEST 控制 RESET MN/MX CLK 系 统 控 制 AD0 ~ AD15 A16/S3 ~ A19/S6 BHE/S7 ALE(QS0) INTA(QS1) INTR NMI 总 线 信 号 中 断 控 制

地 址 总 线

8282

(2)

OE

DIR(2) OE

8286

数据 总线

READY

M/IO RD WR INTR INTA NMI HOLD HLDA

M/IO RD WR INTR INTA NMI HOLD HLDA READY

控 制 总 线

最小模式下计算机总线图

第8 页

2.3 8086引脚信号和工作模式

第 24 页

3.3.1 8086的存储器组织

存储器分段结构

“逻辑段(Segment)”:

内存中的一片区域,用来

存放某一种类型的信息。 例如,用一片存储区存放 某程序所使用的数据,该存储区 称为“数据段”。类似的,还有 存放程序代码的“代码段”,存 放程序运行时临时信息的“堆栈

段i-1 段i 段i+1

第 10 页

2 最小模式下引脚信号和功能

2、A16/S3~A19/S6:地址/状态复用引脚 输出,三态,高电平有效。分时输出地址的高4位或CPU 当前状态。地址信息由ALE锁存。T1输出高4位地址,其 他时钟周期输出CPU当前状态。

S5:表示中断允许位的当前状态。

S6:表示8086CPU与总线相连。恒为0 S4 S3 特性(所使用的段寄存器) 0 0 ES 0 1 SS 0 1 CS(或者不是寄存器操作) 1 1 DS

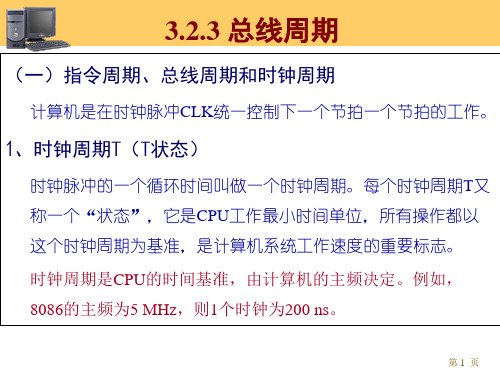

3.2.3 总线周期

(一)指令周期、总线周期和时钟周期

计算机是在时钟脉冲CLK统一控制下一个节拍一个节拍的工作。

1、时钟周期T(T状态)

时钟脉冲的一个循环时间叫做一个时钟周期。每个时钟周期T又

称一个“状态”,它是CPU工作最小时间单位,所有操作都以

这个时钟周期为基准,是计算机系统工作速度的重要标志。 时钟周期是CPU的时间基准,由计算机的主频决定。例如, 8086的主频为5 MHz,则1个时钟为200 ns。

HLDA

BHE A19 ~ A16

8282

(2)

OE

8286

8086

MN/MX

ALE

DIR

(2) OE

A15 ~ A0 HLDA D15 数据 ~ 总线 D0

地 址 总 线

8288 INTA

MRDC 0 S1 S2 INTR NMI

S0 S1 S2

INTA MEMR MEMW IOR IOW

第5 页

引 脚 号

类 型

RD

TEST READY

RESET NMI INTR CLK VCC GND

8086引脚信号定义

最小方式信号(MN/=MX=VCC) HOLD HLDA 保持请求 保持响应 31 30 输入 输出

WR

M/IO DT/R

写控制

存储器/IO控制 数据发送/接收 数据允许 地址锁存允许 中断响应

第1 页

3.2.3 总线周期

2、总线周期(机器周期)

CPU从存储器或I/O口存取一个字或字节的时间称为总线周期 8086的总线周期有:存储器读写周期、 输入/输出周期、中断响