AT27LV020A-90VC中文资料

AT90SC144144CT中文资料

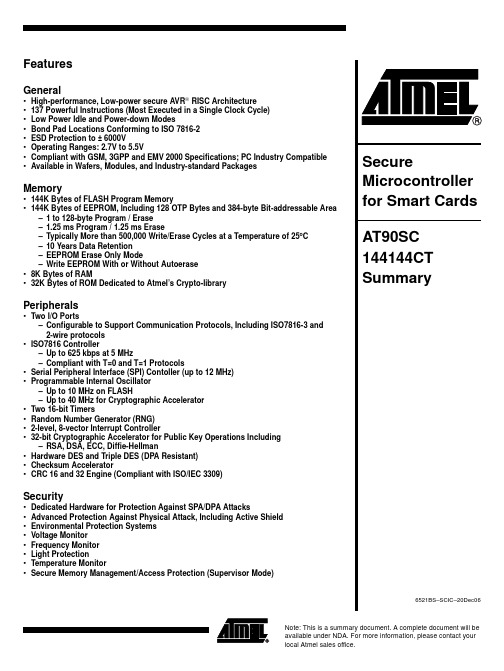

Features Array General•High-performance, Low-power secure AVR® RISC Architecture•137 Powerful Instructions (Most Executed in a Single Clock Cycle)•Low Power Idle and Power-down Modes•Bond Pad Locations Conforming to ISO 7816-2•ESD Protection to ± 6000V•Operating Ranges: 2.7V to 5.5V•Compliant with GSM, 3GPP and EMV 2000 Specifications; PC Industry Compatible •Available in Wafers, Modules, and Industry-standard PackagesMemory•144K Bytes of FLASH Program Memory•144K Bytes of EEPROM, Including 128 OTP Bytes and 384-byte Bit-addressable Area –1 to 128-byte Program / Erase–1.25 ms Program / 1.25 ms Erase–Typically More than 500,000 Write/Erase Cycles at a Temperature of 25o C–10 Years Data Retention–EEPROM Erase Only Mode–Write EEPROM With or Without Autoerase•8K Bytes of RAM•32K Bytes of ROM Dedicated to Atmel’s Crypto-libraryPeripherals•Two I/O Ports–Configurable to Support Communication Protocols, Including ISO7816-3 and2-wire protocols•ISO7816 Controller–Up to 625 kbps at 5 MHz–Compliant with T=0 and T=1 Protocols•Serial Peripheral Interface (SPI) Contoller (up to 12 MHz)•Programmable Internal Oscillator–Up to 10 MHz on FLASH–Up to 40 MHz for Cryptographic Accelerator•Two 16-bit Timers•Random Number Generator (RNG)•2-level, 8-vector Interrupt Controller•32-bit Cryptographic Accelerator for Public Key Operations Including –RSA, DSA, ECC, Diffie-Hellman•Hardware DES and Triple DES (DPA Resistant)•Checksum Accelerator•CRC 16 and 32 Engine (Compliant with ISO/IEC 3309)Security•Dedicated Hardware for Protection Against SPA/DPA Attacks•Advanced Protection Against Physical Attack, Including Active Shield •Environmental Protection Systems•Voltage Monitor•Frequency Monitor•Light Protection•Temperature Monitor•Secure Memory Management/Access Protection (Supervisor Mode)Development Tools•Voyager Emulation Platform (ATV4 Standard) to Support Software Development•IAR Embedded Workbench® V3.20c Debugger or Atmel’s AVR Studio® Version 4.07 or Above•Software Libraries and Application NotesCertification•EAL4+•VISA•CAST•FIPSDescriptionThe AT90SC144144CT is a low-power, high-performance, 8/16-bit microcontroller with ROM program memory, EEPROM data memory, based on the secureAVR enhanced RISC architecture. By executing powerful instructions in a single clock cycle, the AT90SC144144CT achieves throughputs close to 1 MIPS per MHz. Its Harvard architecture includes 32 general-purpose working registers directly connected to the ALU, allowing two independent registers to be accessed in one single instruction executed in one clock cycle.The ability to map the EEPROM in the code space allows parts of the program memory to be reprogrammed in-system. This technology combined with the versatile 8/16-bit CPU on a monolithic chip provides a highly flexible and cost-effective solution to many smart card applications. The AT90SC144144CT benefits of advanced EEPROM functions (XP Mode), but can also be configured to offer compatibility with previous product generations (e.g. AT90SC25672R or AT90SC19236R). The cryptographic accelerator, running with the secureAVR core, featured in the AT90SC144144CT series is the new AdvX‰. It is based on a 32-bit multiplier-accumulator architecture which is designed to perform fast encryption and authen-tication functions. This enables fast computation and low-power operation. The controlling firmware is located either in the dedicated ROM memory (Atmel’s cryptolibrary supports standard finite field arithmetic functions including RSA, DSA, DH and ECC) or in the ROM program memory (customer specific).Additional security features include power and frequency protection logic, logical scrambling on program data and addresses, Power Analysis countermeasures and memory accesses controlled by a supervisor mode.Figure 1 shows the AT90SC144144CT block diagram.Figure 1.Disclaimer: Atmel Corporation makes no warranty for the use of its products, other than those expressly contained in the Company’s standard warranty which is detailed in Atmel’s Terms and Conditions located on the Company’s web site. The Company assumes no responsibility for any errors which may appear in this document, reserves the right to change devices or specifications detailed herein at any time without notice, and does not make any commitment to update the information contained herein. No licenses to patents or other intellectual property of Atmel are granted by the Company in connection with the sale of Atmel products, expressly or by implication. Atmel’s products are not authorized for use as critical components in life support devices or systems.Atmel CorporationAtmel Operations2325 Orchard Parkway San Jose, CA 95131, USA Tel: 1(408) 441-0311Fax: 1(408) 487-2600Regional HeadquartersEuropeAtmel SarlRoute des Arsenaux 41Case Postale 80CH-1705 Fribourg SwitzerlandTel: (41) 26-426-5555Fax: (41) 26-426-5500AsiaRoom 1219Chinachem Golden Plaza 77 Mody Road Tsimshatsui East Kowloon Hong KongTel: (852) 2721-9778Fax: (852) 2722-1369Japan9F, Tonetsu Shinkawa Bldg.1-24-8 ShinkawaChuo-ku, Tokyo 104-0033JapanTel: (81) 3-3523-3551Fax: (81) 3-3523-7581Memory2325 Orchard Parkway San Jose, CA 95131, USA Tel: 1(408) 441-0311Fax: 1(408) 436-4314Microcontrollers2325 Orchard Parkway San Jose, CA 95131, USA Tel: 1(408) 441-0311Fax: 1(408) 436-4314La Chantrerie BP 7060244306 Nantes Cedex 3, France Tel: (33) 2-40-18-18-18Fax: (33) 2-40-18-19-60ASIC/ASSP/Smart CardsZone Industrielle13106 Rousset Cedex, France Tel: (33) 4-42-53-60-00Fax: (33) 4-42-53-60-011150 East Cheyenne Mtn. Blvd.Colorado Springs, CO 80906, USA Tel: 1(719) 576-3300Fax: 1(719) 540-1759Scottish Enterprise Technology Park Maxwell BuildingEast Kilbride G75 0QR, Scotland Tel: (44) 1355-803-000Fax: (44) 1355-242-743RF/AutomotiveTheresienstrasse 2Postfach 353574025 Heilbronn, Germany Tel: (49) 71-31-67-0Fax: (49) 71-31-67-23401150 East Cheyenne Mtn. Blvd.Colorado Springs, CO 80906, USA Tel: 1(719) 576-3300Fax: 1(719) 540-1759Biometrics/Imaging/Hi-Rel MPU/ High Speed Converters/RF DatacomAvenue de Rochepleine BP 12338521 Saint-Egreve Cedex, France Tel: (33) 4-76-58-30-00Fax: (33) 4-76-58-34-80Literature Requests/literatureATMEL ®, AVR ® and AVRstudio ® are registered trademarks of Atmel; secureAVR ™ and AdvX ™ are trademarks of Atmel.EWAVR ® is a registered trademark of IAR Systems AB. Other terms and product names may be the trademark of others.Disclaimer: Atmel Corporation makes no warranty for the use of its products, other than those expressly contained in the Company’s standard warranty which is detailed in Atmel’s Terms and Conditions located on the Company’s web site. The Company assumes no responsibility for any errors which may appear in this document, reserves the right to change devices or specifications detailed herein at any time without notice, and does not make any commitment to update the information contained herein. No licenses to patents or other intellectual property of Atmel are granted by the Company in connection with the sale of Atmel products, expressly or by implication. Atmel’s products are not authorized for use as critical components in life support devices or systems.Atmel CorporationAtmel Operations2325 Orchard Parkway San Jose, CA 95131, USA Tel: 1(408) 441-0311Fax: 1(408) 487-2600Regional HeadquartersEuropeAtmel SarlRoute des Arsenaux 41Case Postale 80CH-1705 Fribourg SwitzerlandTel: (41) 26-426-5555Fax: (41) 26-426-5500AsiaRoom 1219Chinachem Golden Plaza 77 Mody Road Tsimshatsui East Kowloon Hong KongTel: (852) 2721-9778Fax: (852) 2722-1369Japan9F, Tonetsu Shinkawa Bldg.1-24-8 ShinkawaChuo-ku, Tokyo 104-0033JapanTel: (81) 3-3523-3551Fax: (81) 3-3523-7581Memory2325 Orchard Parkway San Jose, CA 95131, USA Tel: 1(408) 441-0311Fax: 1(408) 436-4314Microcontrollers2325 Orchard Parkway San Jose, CA 95131, USA Tel: 1(408) 441-0311Fax: 1(408) 436-4314La Chantrerie BP 7060244306 Nantes Cedex 3, France Tel: (33) 2-40-18-18-18Fax: (33) 2-40-18-19-60ASIC/ASSP/Smart CardsZone Industrielle13106 Rousset Cedex, France Tel: (33) 4-42-53-60-00Fax: (33) 4-42-53-60-011150 East Cheyenne Mtn. Blvd.Colorado Springs, CO 80906, USA Tel: 1(719) 576-3300Fax: 1(719) 540-1759Scottish Enterprise Technology Park Maxwell BuildingEast Kilbride G75 0QR, Scotland Tel: (44) 1355-803-000Fax: (44) 1355-242-743RF/AutomotiveTheresienstrasse 2Postfach 353574025 Heilbronn, Germany Tel: (49) 71-31-67-0Fax: (49) 71-31-67-23401150 East Cheyenne Mtn. Blvd.Colorado Springs, CO 80906, USA Tel: 1(719) 576-3300Fax: 1(719) 540-1759Biometrics/Imaging/Hi-Rel MPU/ High Speed Converters/RF DatacomAvenue de Rochepleine BP 12338521 Saint-Egreve Cedex, France Tel: (33) 4-76-58-30-00Fax: (33) 4-76-58-34-80Literature Requests/literature。

EN29LV160B-70TP资料

0.FEATURES• 3.0V, single power supply operation- Minimizes system level power requirements• High performance- Access times as fast as 70 ns• Low power consumption (typical values at 5 MHz)- 9 mA typical active read current- 20 mA typical program/erase current- 1 µA typical standby current (standard access time to active mode)• Flexible Sector Architecture:- One 16 Kbyte, two 8 Kbyte, one 32 Kbyte, andthirty-one 64 Kbyte sectors (byte mode) - One 8 Kword, two 4 Kword, one 16 Kword and thirty-one 32 Kword sectors (word mode) - Supports full chip erase- Individual sector erase supported - Sector protection:Hardware locking of sectors to preventprogram or erase operations within individual sectorsAdditionally, temporary Sector GroupUnprotect allows code changes in previously locked sectors.• High performance program/erase speed- Byte program time: 8µs typical - Sector erase time: 500ms typical - Chip erase time: 17.5s typical• JEDEC Standard program and erase commands• JEDEC standard DATA polling and toggle bits feature• Single Sector and Chip Erase • Sector Unprotect Mode• Embedded Erase and Program Algorithms • Erase Suspend / Resume modes:Read and program another Sector during Erase Suspend Mode• 0.23 µm triple-metal double-poly triple-well CMOS Flash Technology • Low Vcc write inhibit < 2.5V• >100K program/erase endurance cycle• Package Options - 48-pin TSOP (Type 1) - 48 ball 6mm x 8mm FBGA • Commercial Temperature RangeGENERAL DESCRIPTIONThe EN29LV160 is a 16-Megabit, electrically erasable, read/write non-volatile flash memory, organized as 2,097,152 bytes or 1,048,576 words. Any byte can be programmed typically in 8µs. The EN29LV160 features 3.0V voltage read and write operation, with access times as fast as 70ns to eliminate the need for WAIT states in high-performance microprocessor systems.The EN29LV160 has separate Output Enable (OE ), Chip Enable (CE ), and Write Enable (WE) controls, which eliminate bus contention issues. This device is designed to allow either single Sector or full chip erase operation, where each Sector can be individually protected againstprogram/erase operations or temporarily unprotected to erase or program. The device can sustain a minimum of 100K program/erase cycles on each Sector.EN29LV160 ******PRELIMINARY DRAFT******16 Megabit (2048K x 8-bit / 1024K x 16-bit) Flash Memory Boot Sector Flash Memory, CMOS 3.0 Volt-onlyCONNECTION DIAGRAMSA6 A5 A4A1A3 A2 FBGATop View, Balls Facing DownA13A9 A3 RY/BY#WE# A7 B6 B5 B4B1B3 B2 A12A8 A4NCRESET# A17 C6C5C4C1C3C2A14A10 A2A18NCA6 D6 D5 D4D1D3 D2 A15A11 A1NCA19A5 E6E5E4E1E3E2A16DQ7A0DQ2DQ5DQ0F6F5F4F3F2BYTE#DQ14CE#DQ10DQ12DQ8G6G5G4G3G2DQ15/A-1DQ13OE#DQ11Vcc DQ9H6H5H3H2VssDQ6VssDQ4DQ1F1G1H4H1DQ312 3 4 5 6 78 91011 12 1314 15 16 17 18 19202122 2324 48 47 46 45 44 43 42 41 40 39 38 37 36 35 34 33 32 31 30 29 28 27 26 25Standard TSOPA15A14A13A12A11A10A9A8A19NC WE#RESET#NCNC RY/BY#A18A17A7A6A5A4A3A2A1A16 BYTE# VssDQ15/A-1DQ7 DQ14 DQ6 DQ13 DQ5 DQ12 DQ4 Vcc DQ11 DQ3 DQ10 DQ2 DQ9 DQ1 DQ8 DQ0 OE# Vss CE# A0TABLE 1. PIN DESCRIPTION FIGURE 1. LOGIC DIAGRAM Pin Name FunctionA0-A19 20AddressesDQ0-DQ14 15 Data Inputs/OutputsDQ15 / A-1 DQ15 (data input/output, word mode), A-1 (LSB address input, byte mode)CE# ChipEnable OE# OutputEnable RESET# Hardware Reset PinRY/BY# Ready/BusyOutput WE# WriteEnableVcc Supply Voltage(2.7-3.6V)Vss Ground NC Not Connected to anythingBYTE# Byte/WordModeEN29LV160A0 – A19WECEOERY/BY ResetByteTable 2. Sector Address Tables (EN29LV160T)Address Range (in hexadecimal)Sector A19 A18 A17 A16 A15 A14A13A12Sector Size(Kbytes/ Kwords)Byte mode (x8) Word Mode(x16) SA0 0 0 0 0 0 X X X 62/32 000000–00FFFF 00000–07FFF SA1 0 0 0 0 1 X X X 64/32 010000–01FFFF 08000–0FFFF SA2 0 0 0 1 0 X X X 64/32 020000–02FFFF 10000–17FFF SA3 0 0 0 1 1 X X X 64/32 030000–03FFFF 18000–1FFFF SA4 0 0 1 0 0 X X X 64/32 040000–04FFFF 20000–27FFF SA5 0 0 1 0 1 X X X 64/32 050000–05FFFF 28000–2FFFF SA6 0 0 1 1 0 X X X 64/32 060000–06FFFF 30000–37FFF SA7 0 0 1 1 1 X X X 64/32 070000–07FFFF 38000–3FFFF SA8 0 1 0 0 0 X X X 64/32 080000–08FFFF 40000–47FFF SA9 0 1 0 0 1 X X X 64/32 090000–09FFFF 48000–4FFFF SA10 0 1 0 1 0 X X X 64/32 0A0000–0AFFFF 50000–57FFF SA11 0 1 0 1 1 X X X 64/32 0B0000–0BFFFF 58000–5FFFF SA12 0 1 1 0 0 X X X 64/32 0C0000–0CFFFF 60000–67FFF SA13 0 1 1 0 1 X X X 64/32 0D0000–0DFFFF 68000–6FFFF SA14 0 1 1 1 0 X X X 64/32 0E0000–0EFFFF 70000–77FFF SA15 0 1 1 1 1 X X X 64/32 0F0000–0FFFFF 78000–7FFFF SA16 1 0 0 0 0 X X X 64/32 100000–10FFFF 80000–87FFF SA17 1 0 0 0 1 X X X 64/32 110000–11FFFF 88000–8FFFF SA18 1 0 0 1 0 X X X 64/32 120000–12FFFF 90000–97FFF SA19 1 0 0 1 1 X X X 64/32 130000–13FFFF 98000–9FFFF SA20 1 0 1 0 0 X X X 64/32 140000–14FFFF A0000–A7FFF SA21 1 0 1 0 1 X X X 64/32 150000–15FFFF A8000–AFFFF SA22 1 0 1 1 0 X X X 64/32 160000–16FFFF B0000–B7FFF SA23 1 0 1 1 1 X X X 64/32 170000–17FFFF B8000–BFFFF SA24 1 1 0 0 0 X X X 64/32 180000–18FFFF C0000–C7FFF SA25 1 1 0 0 1 X X X 64/32 190000–19FFFF C8000–CFFFF SA26 1 1 0 1 0 X X X 64/32 1A0000–1AFFFF D0000–D7FFF SA27 1 1 0 1 1 X X X 64/32 1B0000–1BFFFF D8000–DFFFF SA28 1 1 1 0 0 X X X 64/32 1C0000–1CFFFF E0000–E7FFF SA29 1 1 1 0 1 X X X 64/32 1D0000–1DFFFF E8000–EFFFF SA30 1 1 1 1 0 X X X 64/32 1E0000–1EFFFF F0000–F7FFF SA31 1 1 1 1 1 0 X X 32/16 1F0000–1F7FFF F8000–FBFFF SA32 1 1 1 1 1 1 0 0 8/4 1F8000–1F9FFF FC000–FCFFF SA33 1 1 1 1 1 1 0 1 8/41FA000–1FBFFF FD000–FDFFFSA34 1 1 1 1 1 1 1 X16/8 1FC000–1FFFFF FE000–FFFFFTable 3. Sector Address Tables (EN29LV160B)Address Range (in hexadecimal) Sector A19 A18 A17 A16 A15 A14A13A12Sector Size (Kbytes/ Kwords)Byte mode (x8)Word Mode(x16) SA0 0 0 0 0 0 0 0 X 16/8 000000–003FFF 00000–01FFF SA1 0 0 0 0 0 0 1 0 8/4 004000–005FFF 02000–02FFF SA2 0 0 0 0 0 0 1 18/4006000–007FFF 03000–03FFFSA3 0 0 0 0 0 1 X X 32/16 008000–00FFFF 04000–07FFF SA4 0 0 0 0 1 X X X 64/32 010000–01FFFF 08000–0FFFF SA5 0 0 0 1 0 X X X 64/32 020000–02FFFF 10000–17FFF SA6 0 0 0 1 1 X X X 64/32 030000–03FFFF 18000–1FFFF SA7 0 0 1 0 0 X X X 64/32 040000–04FFFF 20000–27FFF SA8 0 0 1 0 1 X X X 64/32 050000–05FFFF 28000–2FFFF SA9 0 0 1 1 0 X X X 64/32 060000–06FFFF 30000–37FFF SA10 0 0 1 1 1 X X X 64/32 070000–07FFFF 38000–3FFFF SA11 0 1 0 0 0 X X X 64/32 080000–08FFFF 40000–47FFF SA12 0 1 0 0 1 X X X 64/32 090000–09FFFF 48000–4FFFF SA13 0 1 0 1 0 X X X 64/32 0A0000–0AFFFF 50000–57FFF SA14 0 1 0 1 1 X X X 64/32 0B0000–0BFFFF58000–5FFFFSA15 0 1 1 0 0 X X X 64/32 0C0000–0CFFFF 60000–67FFF SA16 0 1 1 0 1 X X X 64/32 0D0000–0DFFFF 68000–6FFFF SA17 0 1 1 1 0 X X X 64/32 0E0000–0EFFFF 70000–77FFF SA18 0 1 1 1 1 X X X 64/32 0F0000–0FFFFF 78000–7FFFF SA19 1 0 0 0 0 X X X 64/32 100000–10FFFF 80000–87FFF SA20 1 0 0 0 1 X X X 64/32 110000–11FFFF 88000–8FFFF SA21 1 0 0 1 0 X X X 64/32 120000–12FFFF 90000–97FFF SA22 1 0 0 1 1 X X X 64/32 130000–13FFFF 98000–9FFFF SA23 1 0 1 0 0 X X X 64/32 140000–14FFFF A0000–A7FFF SA24 1 0 1 0 1 X X X 64/32 150000–15FFFF A8000–AFFFF SA25 1 0 1 1 0 X X X 64/32 160000–16FFFF B0000–B7FFF SA26 1 0 1 1 1 X X X 64/32 170000–17FFFF B8000–BFFFF SA27 1 1 0 0 0 X X X 64/32 180000–18FFFF C0000–C7FFF SA28 1 1 0 0 1 X X X 64/32 190000–19FFFF C8000–CFFFF SA29 1 1 0 1 0 X X X 64/32 1A0000–1AFFFF D0000–D7FFF SA30 1 1 0 1 1 X X X 64/32 1B0000–1BFFFF D8000–DFFFF SA31 1 1 1 0 0 X X X 64/32 1C0000–1CFFFF E0000–E7FFF SA32 1 1 1 0 1 X X X 64/32 1D0000–1DFFFF E8000–EFFFF SA33 1 1 1 1 0 X X X 64/32 1E0000–1EFFFF F0000–F7FFF SA34 1 1 1 1 1 X X X 64/321F0000–1FFFFF F8000–FFFFFPRODUCT SELECTOR GUIDEProduct Number EN29LV160Regulated Voltage Range: Vcc=3.0 – 3.6 VSpeed OptionFull Voltage Range: Vcc=2.7 – 3.6 V-70 -90Max Access Time, ns (t acc ) 70 90Max CE# Access, ns (t ce ) 70 90Max OE# Access, ns (t oe ) 30 35BLOCK DIAGRAMWECE OEState ControlCommand RegisterErase Voltage GeneratorInput/Output BuffersProgram Voltage GeneratorChip Enable Output EnableLogicData LatchY-Decoder X-DecoderY-GatingCell MatrixTimerVcc DetectorA0-A19Vcc VssDQ0-DQ15 (A-1)Address LatchBlock Protect SwitchesSTBSTBRY/BYTABLE 3. OPERATING MODES16M FLASH USER MODE TABLEDQ8-DQ15Operation CE# OE# WE# Reset# A0-A19 DQ0-DQ7 Byte# = V IH Byte#= V IL Read L L H H A IN D OUT D OUT High-Z Write L H L H A IN D IN D IN High-Z CMOS Standby V cc ± 0.3V X X V cc ± 0.3V X High-Z High-Z High-Z TTL Standby H X X H X High-Z High-Z High-Z Output Disable L H H H X High-Z High-Z High-Z Hardware Reset X X X L X High-Z High-Z High-Z TemporarySector Unprotect X X X V IDA IN D IN D IN XNotes:L=logic low= V IL , H=Logic High= V IH , V ID =11 ± 0.5V, X=Don’t Care (either L or H, but not floating!), D IN =Data In, D OUT =Data Out, A IN =Address InTABLE 4. DEVICE IDENTIFICTION (Autoselect Codes)16M FLASH MANUFACTURER/DEVICE ID TABLENote:1. A8=H is recommended for Manufacturing ID check. If a manufacturing ID is read with A8=L, the chip will output a configuration code 7Fh2. A9 = VID is for HV A9 Autoselect mode only. A9 must be ≤ Vcc (CMOS logic level) for Command Autoselect Mode.Description Mode A19 to A12A11 toA10A92A8A7A6A5 to A2A1 A0 DQ8to DQ15 DQ7 to DQ0 Manufacturer ID:EonL L H X X V IDH1X L X L L X 1CH Word L L H22h C4H Device ID (top bootblock) Byte L L H X X V ID X X L X L H X C4H Word L L H22h49H Device ID(bottom bootblock)Byte L L HX X V IDXXLXLHX 49H X01h(Protected)Sector ProtectionVerification L L H SA X V IDX X L X H LX00h(Unprotected)OE CE WEUSER MODE DEFINITIONSWord / Byte ConfigurationThe signal set on the BYTE# Pin controls whether the device data I/O pins DQ15-DQ0 operate in the byte or word configuration. When the Byte# Pin is set at logic ‘1’, then the device is in word configuration, DQ15-DQ0 are active and are controlled by CE# and OE#.On the other hand, if the Byte# Pin is set at logic ‘0’, then the device is in byte configuration, and only data I/O pins DQ0-DQ7 are active and controlled by CE# and OE#. The data I/O pins DQ8-DQ14 are tri-stated, and the DQ15 pin is used as an input for the LSB (A-1) address function.Standby ModeThe EN29LV160 has a CMOS-compatible standby mode, which reduces the current to < 1µA (typical). It is placed in CMOS-compatible standby when the CE pin is at V CC± 0.5. RESET# and BYTE# pin must also be at CMOS input levels. The device also has a TTL-compatible standby mode, which reduces the maximum V CC current to < 1mA. It is placed in TTL-compatible standby when the pin is at V IH. When in standby modes, the outputs are in a high-impedance state independent of the OE input.Read ModeThe device is automatically set to reading array data after device power-up. No commands are required to retrieve data. The device is also ready to read array data after completing an Embedded Program or Embedded Erase algorithm.After the device accepts an Erase Suspend command, the device enters the Erase Suspend mode. The system can read array data using the standard read timings, except that if it reads at an address within erase-suspended sectors, the device outputs status data. After completing a programming operation in the Erase Suspend mode, the system may once again read array data with the same exception. See “Erase Suspend/Erase Resume Commands” for more additional information.The system must issue the reset command to re-enable the device for reading array data if DQ5 goes high, or while in the autoselect mode. See the “Reset Command” additional details.Output Disable ModeWhen the CE or OE pin is at a logic high level (V IH), the output from the EN29LV160 is disabled. The output pins are placed in a high impedance state.Auto Select Identification ModeThe autoselect mode provides manufacturer and device identification, and sector protection verification, through identifier codes output on DQ15–DQ0. This mode is primarily intended for programming equipment to automatically match a device to be programmed with its corresponding programming algorithm. However, the autoselect codes can also be accessed in-system through the command register.When using programming equipment, the autoselect mode requires V ID (10.5 V to 11.5 V) on address pin A9. Address pins A6, A1, and A0 must be as shown in Autoselect Codes table. In addition, when verifying sector protection, the sector address must appear on the appropriate highest order address bits. Refer to the corresponding Sector Address Tables. The Command Definitions table shows the remaining address bits that are don’t-care. When all necessary bits have been set as required, the programming equipment may then read the corresponding identifier code on DQ15–DQ0.To access the autoselect codes in-system; the host system can issue the autoselect command via the command register, as shown in the Command Definitions table. This method does not require V ID. See “Command Definitions” for details on using the autoselect mode.Write ModeProgramming is a four-bus-cycle operation. The program command sequence is initiated by writing two unlock write cycles, followed by the program set-up command. The program address and data are written next, which in turn initiate the Embedded Program algorithm. The system is not required to provide further controls or timings. The device automatically provides internally generated program pulses and verifies the programmed cell margin. The Command Definitions in Table 5 show the address and data requirements for the byte program command sequence.When the Embedded Program algorithm is complete, the device then returns to reading array data and addresses are no longer latched. The system can determine the status of the program operation by using DQ7 or DQ6. See “Write Operation Status” for information on these status bits.Any commands written to the device during the Embedded Program Algorithm are ignored.Programming is allowed in any sequence and across sector boundaries. A bit cannot be programmed from a “0” back to a “1”. Attempting to do so may halt the operation and set DQ5 to “1”, or cause the Data# Polling algorithm to indicate the operation was successful. However, a succeeding read will show that the data is still “0”. Only erase operations can convert a “0” to a “1”.Sector Protection/UnprotectionThe hardware sector protection feature disables both program and erase operations in any sector. The hardware sector unprotection feature re-enables both program and erase operations in previously protected sectors.There are two methods to enabling this hardware protection circuitry. The first one requires only that the RESET# pin be at V ID and then standard microprocessor timings can be used to enable or disable this feature. See Flowchart 7a and 7b for the algorithm and Figure 12 for the timings.When doing Sector Unprotect, all the other sectors should be protected first.The second method is meant for programming equipment. This method requires V ID be applied to both OE# and A9 pin and non-standard microprocessor timings are used. This method is described in a separate document called EN29LV160 Supplement, which can be obtained by contacting a representative of Eon Silicon Solution, Inc.Temporary Sector UnprotectThis feature allows temporary unprotection of previously protectedsector groups to change data while in-system. The Sector Unprotectmode is activated by setting the RESET# pin to V ID. During this mode,formerly protected sectors can be programmed or erased by simplyselecting the sector addresses. Once is removed from the RESET#pin, all the previously protected sectors are protected again. Seeaccompanying figure and timing diagrams for more details.COMMON FLASH MEMORYINTERFACE(CFI)The common flash interface (CFI) specification outlines device and host systems software interrogation handshake, which allows specific vendor-specified software algorithms to be used for entire families of devices. Software support canStartReset#=V ID(note 1)Perform Erase or ProgramOperationsReset#=V IHTemporary SectorUnprotect Completed (note 2)Notes:1. All protected sectors unprotected.2. Previously protected sectors protected again.then be device-independent, JEDEC ID-independent, and forward- and backward-compatible for the specified flash device families. Flash vendirs can standardize their existing interfaces for long-term compatibility. This device enters the CFI Query mode when the system writes the CFI Query command, 98h, to address 55h in word mode (or address AAh in byte mode), any time the device is ready to read array data. The system can read CFI information at the addresses given in Tables 5-8. In word mode, the upper address bits (A7–MSB) must be all zeros. To terminate reading CFI data, the system must write the reset command.The system can also write the CFI query command when the device is in the autoselect mode. The device enters the CFI query mode and the system can read CFI data at the addresses given in Tables 5–8. The system must write the reset command to return the device to the autoselect mode.Table 5. CFI Query Identification StringAdresses (Word Mode)Adresses(Byte Mode) Data Description10h 11h 12h 20h22h24h0051h0052h0059hQuery Unique ASCII string “QRY”13h 14h 26h28h0002h0000hPrimary OEM Command Set15h 16h 2Ah2Ch0040h0000hAddress for Primary Extended Table17h 18h 2Eh30h0000h0000hAlternate OEM Command set (00h = none exists)19h 1Ah 32h34h0000h0000hAddress for Alternate OEM Extended Table (00h = none exists Table 6. System Interface StringAddresses (Word Mode)Addresses(Byte Mode) Data Description1Bh 36h 0027hVccMin(write/erase)D7-D4: volt, D3 –D0: 100 millivolt1Ch 38h 0036h Vcc Max (write/erase)D7-D4: volt, D3 –D0: 100 millivolt1Dh 3Ah 0000h Vpp Min. voltage (00h = no Vpp pin present)1Eh 3Ch 0000h Vpp Max. voltage (00h = no Vpp pin present)1Fh 3Eh 0004hTypical timeout per single byte/word write 2^N µs20h 40h 0000hTypical timeout for Min, size buffer write 2^N µs (00h = notsupported)21h 42h 000Ah Typical timeout per individual block erase 2^N ms22h 44h 0000h Typical timeout for full chip erase 2^N ms (00h = not supported) 23h 46h 0005h Max. timeout for byte/word write 2^N times typical24h 48h 0000h Max. timeout for buffer write 2^N times typical25h 4Ah 0004h Max. timeout per individual block erase 2^N times typical26h 4Ch 0000h Max timeout for full chip erase 2^N times typical (00h = notsupported)Table 7. Device Geometry DefinitionAddresses (Word mode)Addresses(Byte Mode) Data Description27h 4Eh 0015h Device Size = 2^N byte28h 29h 50h 52h 0002h 0000h Flash Device Interface description (refer to CFI publication 100) 2Ah 2Bh 54h 56h 0000h 0000h Max. number of byte in multi-byte write = 2^N (00h = not supported)2Ch 58h 0004h Number of Erase Block Regions within device 2Dh 2Eh 2Fh 30h 5Ah 5Ch 5Eh 60h 0000h 0000h 0040h 0000h Erase Block Region 1 Information(refer to the CFI specification of CFI publication 100)31h 32h 33h 34h 62h 64h 66h 68h 0001h 0000h 0020h 0000h Erase Block Region 2 Information35h 36h 37h 38h 6Ah 6Ch 6Eh 70h 0000h 0000h 0080h 0000h Erase Block Region 3 Information39h 3Ah 3Bh 3Ch72h 74h 76h 78h001Eh 0000h 0000h 0001hErase Block Region 4 InformationTable 8. Primary Vendor-specific Extended QueryAdresses (Word Mode)Addresses (Byte Mode)Data Description 40h 41h 42h 80h 82h 84h 0050h0052h 0049hQuery-unique ASCII string “PRI” 43h 86h 0031h Major version number, ASCII 44h88h0030h Minor version number, ASCII45h 8Ah 0000hAddress Sensitive Unlock0 = Required, 1 = Not Required 46h 8Ch 0002hErase Suspend0 = Not Supported, 1 = To Read Only, 2 = To Read & Write 47h 8Eh 0001hSector Protect0 = Not Supported, X = Number of sectors in per group 48h 90h 0001hSector Temporary Unprotect00 = Not Supported, 01 = Supported 49h 92h 0004h Sector Protect/Unprotect scheme01 = 29F040 mode, 02 = 29F016 mode,03 = 29F400 mode, 04 = 29LV800A mode 4Ah 94h 0000hSimultaneous Operation00 = Not Supported, 01 = Supported 4Bh 96h 0000hBurst Mode Type00 = Not Supported, 01 = Supported 4Ch 98h 0000hPage Mode Type00 = Not Supported, 01 = 4 Word Page, 02 = 8 Word PageHardware Data protectionThe command sequence requirement of unlock cycles for programming or erasing provides data protection against inadvertent writes as seen in the Command Definitions table. Additionally, the following hardware data protection measures prevent accidental erasure or programming, which might otherwise be caused by false system level signals during Vcc power up and power down transitions, or from system noise.Low V CC Write InhibitWhen Vcc is less than V LKO, the device does not accept any write cycles. This protects data during Vcc power up and power down. The command register and all internal program/erase circuits are disabled, and the device resets. Subsequent writes are ignored until Vcc is greater than V LKO. The system must provide the proper signals to the control pins to prevent unintentional writes when Vcc is greater than V LKO. Write Pulse “Glitch” protectionNoise pulses of less than 5 ns (typical) on OE, CE or W E do not initiate a write cycle.Logical InhibitWrite cycles are inhibited by holding any one of OE = VIL, CE = VIH, or W E = VIH. To initiate a write cycle, CE and W E must be a logical zero while OE is a logical one. If CE, W E, and OE are all logical zero (not recommended usage), it will be considered a read.Power-up Write InhibitDuring power-up, the device automatically resets to READ mode and locks out write cycles. Even with CE = V IL, W E = V IL and OE = V IH, the device will not accept commands on the rising edge of W E.COMMAND DEFINITIONSThe operations of the EN29LV160 are selected by one or more commands written into the command register to perform Read/Reset Memory, Read ID, Read Sector Protection, Program, Sector Erase, Chip Erase, Erase Suspend and Erase Resume. Commands are made up of data sequences written at specific addresses via the command register. The sequences for the specified operation are defined in the Command Definitions table (Table 5). Incorrect addresses, incorrect data values or improper sequences will reset the device to Read Mode.Table 9. EN29LV160 Command DefinitionsBus Cycles1stWrite Cycle 2ndWrite Cycle 3rdWrite Cycle4thWrite Cycle5thWrite Cycle6thWrite Cycle Command SequenceC y c l e sAdd DataAdd DataAdd DataAdd DataAdd DataAdd DataRead 1 RA RDReset 1 xxx F0Word555 2AA555000/1007F/1CManufacturerID Byte 4AAA AA55555AAA90000/2007F/1CWord 555 2AA555 x0122C4 Device ID Top Boot Byte 4 AAA AA55555 AAA 90x02 C4Word 555 2AA555 x01 2249Device ID Bottom Boot Byte 4AAA AA55555AAA 90x02 49XX00Word5552AA555(SA)X02XX0100A u t o s e l e c tSector Protect Verify Byte4AAA AA55555AAA90(SA)X0401Word 555 2AA555ProgramByte 4 AAA AA55555 AAAA0 PA PDWord555 2AA555Unlock BypassByte3 AAA AA55555 AAA 20Unlock Bypass Program 2 XXX A0 PA PD Unlock Bypass Reset2 XXX 90 XXX 00 Word555 2AA555 5552AA 555Chip EraseByte 6 AAA AA55555 AAA 80 AAA AA 555 55 AAA 10Word555 2AA555 5552AASector EraseByte6 AAA AA55555 AAA 80 AAA AA 555 55 SA 30Erase Suspend 1 xxx B0 Erase Resume1 xxx 30Address and Data values indicated in hexRA = Read Address: address of the memory location to be read. This is a read cycle. RD = Read Data: data read from location RA during Read operation. This is a read cycle. PA = Program Address: address of the memory location to be programmed. X = Don’t-Care PD = Program Data: data to be programmed at location PASA = Sector Address: address of the Sector to be erased or verified. Address bits A19-A12 uniquely select any Sector.Reading Array DataThe device is automatically set to reading array data after power up. No commands are required to retrieve data. The device is also ready to read array data after completing an Embedded Program or Embedded Erase algorithm.Following an Erase Suspend command, Erase Suspend mode is entered. The system can read array data using the standard read timings, with the only difference in that if it reads at an address within erase suspended sectors, the device outputs status data. After completing a programming operation in the Erase Suspend mode, the system may once again read array data with the same exception.The Reset command must be issued to re-enable the device for reading array data if DQ5 goes high, or while in the autoselect mode. See next section for details on Reset.Reset CommandWriting the reset command to the device resets the device to reading array data. Address bits are don’t-care for this command.The reset command may be written between the sequence cycles in an erase command sequence before erasing begins. This resets the device to reading array data. Once erasure begins, however, the device ignores reset commands until the operation is complete. The reset command may be written between the sequence cycles in a program command sequence before programming begins. This resets the device to reading array data (also applies to programming in Erase Suspend mode). Once programming begins, however, the device ignores reset commands until the operation is complete.The reset command may be written between the sequence cycles in an autoselect command sequence. Once in the autoselect mode, the reset command must be written to return to reading array data (also applies to autoselect during Erase Suspend).If DQ5 goes high during a program or erase operation, writing the reset command returns the device to reading array data (also applies during Erase Suspend).Autoselect Command SequenceThe autoselect command sequence allows the host system to access the manufacturer and devices codes, and determine whether or not a sector is protected. The Command Definitions table shows the address and data requirements. This is an alternative to the method that requires V ID on address bit A9 and is intended for PROM programmers.Two unlock cycles followed by the autoselect command initiate the autoselect command sequence. Autoselect mode is then entered and the system may read at addresses shown in Table 4 any number of times, without needing another command sequence.The system must write the reset command to exit the autoselect mode and return to reading array data. Word / Byte Programming CommandThe device may be programmed by byte or by word, depending on the state of the Byte# Pin. Programming the EN29LV160 is performed by using a four bus-cycle operation (two unlock write cycles followed by the Program Setup command and Program Data Write cycle). When the program command is executed, no additional CPU controls or timings are necessary. An internal timer terminates the program operation automatically. Address is latched on the falling edge of CE or W E, whichever is last; data is latched on the rising edge of CE or W E, whichever is first. Programming status may be checked by sampling data on DQ7 (DATA polling) or on DQ6 (toggle bit). ). When the program operation is successfully completed, the device returns to read mode and the user can read the data programmed to the device at that address. Note that data can not be programmed from a 0 to a 1. Only an erase operation can change a data from 0 to 1. When programming time limit is exceeded, DQ5 will produce a logical “1” and a Reset command can return the device to Read mode.Unlock BypassTo speed up programming operation, the Unlock Bypass Command may be used. Once this feature is activated, the shorter two cycle Unlock Bypass Program command can be used instead of the normal four cycle Program Command to program the device. This mode is exited after issuing the Unlock Bypass Reset Command. The device powers up with this feature disabled.。

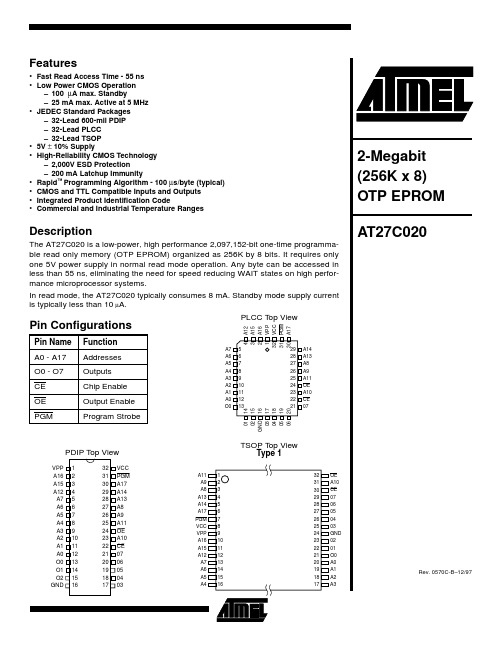

AT27C020中文资料

The AT27C020 is available in a choice of industry standard JEDEC-approved one-time programmable (OTP) plastic PDIP, PLCC, and TSOP packages. All devices feature two-line control (CE, OE) to give designers the flexibility to pre-vent bus contention.With 256K byte storage capability, the AT27C020 allows firmware to be stored reliably and to be accessed by the system without the delays of mass storage media. Atmel’s 27C020 have additional features to ensure high quality and efficient production use. The Rapid™Program-ming Algorithm reduces the time required to program the part and guarantees reliable programming. Programming time is typically only 100 µs/byte. The Integrated Product Identification Code electronically identifies the device and manufacturer. This feature is used by industry standard programming equipment to select the proper programming algorithms and voltages.System ConsiderationsSwitching between active and standby conditions via the Chip Enable pin may produce transient voltage excursions. Unless accommodated by the system design, these tran-sients may exceed data sheet limits, resulting in device non-conformance. At a minimum, a 0.1 µF high frequency, low inherent inductance, ceramic capacitor should be uti-lized for each device. This capacitor should be connected between the V CC and Ground terminals of the device, as close to the device as possible. Additionally, to stabilize the supply voltage level on printed circuit boards with large EPROM arrays, a 4.7 µF bulk electrolytic capacitor should be utilized, again connected between the V CC and Ground terminals. This capacitor should be positioned as close as possible to the point where the power supply is connected to the array.Block DiagramAbsolute Maximum Ratings*T emperature Under Bias.......................-55°C to +125°C *NOTICE:Stresses beyond those listed under “Absolute Maximum Ratings” may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of this specification is not implied. Exposure to abso-lute maximum rating conditions for extended periods may affect device reliability.Note:1.Minimum voltage is -0.6V DC which mayundershoot to -2.0V for pulses of less than 20 ns. Maximum output pin voltage is V CC + 0.75V DC which may overshoot to +7.0V for pulses of less than 20 ns.Storage T emperature............................-65°C to +150°C Voltage on Any Pin withRespect to Ground...............................-2.0V to +7.0V (1)Voltage on A9 withRespect to Ground ............................-2.0V to +14.0V (1)V PP Supply Voltage withRespect to Ground.............................-2.0V to +14.0V (1)Operating ModesNotes:1.X can be V IL or V IH.2.Refer to Programming Characteristics.3.V H = 12.0 ± 0.5V .4.T wo identifier bytes may be selected. All Ai inputs are held low (V IL ), except A9 which is set to V H and A0 which is toggledlow (V IL ) to select the Manufacturer’s Identification byte and high (V IH ) to select the Device Code byte.Mode/Pin CE OE PGM Ai V PP Outputs ReadV IL V IL X (1)Ai X D OUT Output Disable X V IH X X X HighZ Standby V IH X X X X High Z Rapid Program (2)V IL V IH V IL Ai V PP D IN PGM Verify V IL V IL V IH Ai V PP D OUT PGM InhibitV IH X X X V PP High Z Product Identification (4)V ILV ILXA9 = V H (3)A0 = V IH or V IL A1 - A17 = V ILXIdentification CodeAC Characteristics for Read OperationNote:1.2, 3, 4, 5. See AC Waveforms for Read Operation diagram.Symbol ParameterAT27C020Units -55-70-90-12-15Condition Min Max MinMax MinMax MinMax MinMax t ACC (3)Address to Output Delay CE =OE = V IL 557090120150ns t CE (2)CE to Output Delay OE = V IL 557090120150ns t OE (2)(3)OE to Output Delay CE = V IL2030353540ns t DF(4)(5)OE or CE High to Output Float,whichever occurred first 1820203040nst OH Output Holdfrom Address,CE or OE,whichever occurred first77000nsDC and AC Operating Conditions for Read OperationAT27C020-55-70-90-12-15Operating T emperature (Case)Com.0°C - 70°C 0°C - 70°C 0°C - 70°C 0°C - 70°C 0°C - 70°C Ind.-40°C - 85C -40°C - 85C -40°C - 85C -40°C - 85C -40°C - 85C V CC Power Supply5V ± 10%5V ± 10%5V ± 10%5V ± 10%5V ± 10%DC and Operating Characteristics for Read OperationNotes:1.V CC must be applied simultaneously or before V PP , and removed simultaneously or after V PP .2.V PP may be connected directly to V CC except during programming. The supply current would then be the sum of I CC and I PP .Symbol Parameter ConditionMinMax Units I LI Input Load Current V IN = 0V to V CC (Com., Ind.)±1.0µA I LO Output Leakage Current V OUT = 0V to V CC (Com., Ind.)±5.0µA I PP (2)V PP (1) Read/Standby Current V PP = V CC±10µA I SB V CC (1) Standby Current I SB1 (CMOS), CE = V CC ± 0.3V 100µA I SB2 (TTL), CE = 2.0 to V CC + 0.5V 1.0mA I CC V CC Active Current f = 5 MHz, I OUT = 0 mA, CE = V IL25mA V IL Input Low Voltage -0.60.8V V IH Input High Voltage 2.0V CC + 0.5V V OL Output Low Voltage I OL = 2.1 mA 0.4V V OH Output High VoltageI OH = -400 µA2.4VAC Waveforms for Read Operation (1)Notes: 1.Timing measurement references are 0.8V and 2.0V . Input AC drive levels are 0.45V and 2.4V , unless otherwise specified.2.OE may be delayed up to t CE - t OE after the falling edge of CE without impact on t CE.3.ACC - t OE after the address is valid without impact on t ACC .4.This parameter is only sampled and is not 100% tested.5.Output float is defined as the point when data is no longer driven.Input Test Waveforms and Measurement LevelsFor -55 devices only:t R , t FFor -70,-90,-12,-15 devices only:t R , t F < 20 ns (10% to 90%)Pin Capacitancef = 1 MHz, T = 25°C (1)Note:1.T ypical values for nominal supply voltage. This parameter is only sampled and is not 100% tested.TypMax Units Conditions C IN 48pF V IN = 0V C OUT812pFV OUT = 0VOutput Test Load (1)Note: 1.CL = 100 pF including jig capacitance except -55 devices where CL = 30 pF.Programming Waveforms (1)Notes: 1.The Input Timing reference is 0.8V for V IL and 2.0V for V IH.2.t OE and t DFP are characteristics of the device but must be accommodated by the programmer.3.When programming the A T27C020, a 0.1 µF capacitor is required across V PP and ground to suppress voltage transients.DC Programming CharacteristicsT A = 25 ± 5°C, V CC = 6.5 ± 0.25V, V PP = 13.0 ± 0.25VSymbol Parameter Test ConditionsLimitsUnits Min MaxI LI Input Load Current V IN = V IL, V IH±10µA V IL Input Low Level-0.60.8V V IH Input High Level 2.0VCC+ 1.0V V OL Output Low Voltage I OL = 2.1 mA0.4V V OH Output High Voltage I OH = -400 µA 2.4V I CC2V CC Supply Current (Program and Verify)40mA I PP2V PP Supply Current CE = PGM = V IL20mA V ID A9 Product Identification Voltage11.512.5VAC Programming CharacteristicsT A = 25 ± 5°C, V CC = 6.5 ± 0.25V,V PP = 13.0 ± 0.25VNotes:1.V CC must be applied simultaneously or before V PP and removed simultaneously or after V PP .2.This parameter is only sampled and is not 100% tested. Output Float is defined as the point where data is no longer driven— see timing diagram.3.Program Pulse width tolerance is 100 µs ± 5%.Symbol ParameterTest Condition (1)LimitsUnits Min Max t AS Address Setup Time Input Rise and Fall Times:(10% to 90%) 20 ns.Input Pulse Levels:0.45V to 2.4V Input Timing Reference Level:0.8V to 2.0V Output Timing Reference Level:0.8V to 2.0V2µs t CES CE Setup Time 2µs t OES OE Setup Time 2µs t DS Data Setup Time 2µs t AH Address Hold Time 0µs t DH Data Hold Time2µst DFP OE High to Output Float Delay (2)0130ns t VPS V PP Setup Time 2µs t VCS V CC Set up Time2µs t PW PGM Program Pulse Width (3)95105µs t OE Data Valid from OE150ns t PRTV PP Pulse Rise Time During Programming50nsAtmel’s 27C020 Integrated Product Identification CodePinsCodes A0O7O6O5O4O3O2O1O0Hex DataManufacturer 0000111101E Device T ype111186Rapid Programming AlgorithmA 100 µs PGM pulse width is used to program. The address is set to the first location. V CC is raised to 6.5V and V PP is raised to 13.0V. Each address is first programmed with one 100 µs PGM pulse without verification. Then a verification / reprogramming loop is executed for each address. In the event a byte fails to pass verification, up to 10 successive 100 µs pulses are applied with a verification after each pulse. If the byte fails to verify after 10 pulses have been applied, the part is considered failed. After the byte verifies properly, the next address is selected until all have been checked. V PP is then lowered to 5.0V and V CC to 5.0V. All bytes are read again and compared with the origi-nal data to determine if the device passes or fails.Ordering Informationt ACC (ns)I CC (mA)Ordering Code Package Operation Range Active Standby55250.1A T27C020-55JCA T27C020-55PCA T27C020-55TC 32J32P632TCommercial(0°C to 70°C)250.1A T27C020-55JIA T27C020-55PIA T27C020-55TI 32J32P632TIndustrial(-40°C to 85°C)70250.1A T27C020-70JCA T27C020-70PCA T27C020-70TC 32J32P632TCommercial(0°C to 70°C)250.1A T27C020-70JIA T27C020-70PIAT27C020-70TI 32J32P632TIndustrial(-40°C to 85°C)90250.1A T27C020-90JCA T27C020-90PCA T27C020-90TC 32J32P632TCommercial(0°C to 70°C)250.1A T27C020-90JIA T27C020-90PIAT27C020-90TI 32J32P632TIndustrial(-40°C to 85°C)120250.1A T27C020-12JCA T27C020-12PCA T27C020-12TC 32J32P632TCommercial(0°C to 70°C)250.1A T27C020-12JIA T27C020-12PIA T27C020-12TI 32J32P632TIndustrial(-40°C to 85°C)150250.1A T27C020-15JCA T27C020-15PCA T27C020-15TC 32J32P632TCommercial(0°C to 70°C)250.1A T27C020-15JIA T27C020-15PIA T27C020-15TI 32J32P632TIndustrial(-40°C to 85°C)Package Type32J32-Lead,Plastic J-Leaded Chip Carrier (PLCC)32P632-Lead, 0.600" Wide, Plastic Dual Inline Package (PDIP) 32T32-Lead, Plastic Thin Small Outline Package (TSOP)。

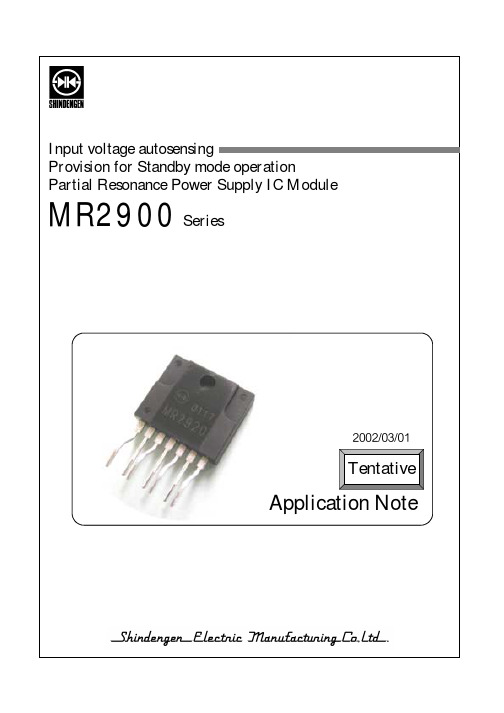

MR2920中文资料

Input voltage autosensingProvision for Standby mode operation Partial Resonance Power Supply IC Module MR29001. The circuit diagrams and parts tables provided for reference purposes in this document are for the use of persons with basic circuit design knowledge to aid in understanding the product.As such they do not constitute a guarantee of output, temperature, or other characteristics, or characteristics or safety as determined by the relevant authorities.2. The products noted in this document are semiconductor components for use in general electronic equipment and for general industrial use. Consideration has been given to ensure safety and reliability as appropriate for the importance of the systems used by the customer. Please contact Shindengen's sales section if any points are unclear.3. Fail-safe design and safety requirements must be considered in applications in which particularly high levels of reliability and safety are required (eg nuclear power control, aerospace, traffic equipment, medical equipment used in life-support, combustion control equipment, various types of safety equipment).Please contact our sales department if anything is unclear.4. Shindengen takes no responsibility for losses or damage incurred, or infringements of patents or other rights, as a result of the use of the circuit diagrams and parts tables provided for reference purposes in this document.5. The circuit diagrams and parts tables provided for reference purposes in this document do not guarantee or authorize execution of intellectual property rights, or any other rights, of Shindengen or third parties.6. Systems using Shindengen products noted in this document and which are strategic materials as defined in the Foreign Exchange and Foreign Trade Control Law or the Export and Trade Control Law require export permission under the relevant legislation prior to export.Inquiries: Functional Devices Division, Device Sales Department, Device Sales SectionPh 03-5951-8131Fax 03-5951-8089Thank you July 1st, 19951. Outline1.1 Introduction (4)Characteristics (4)1.2Applications (4)1.31.4 Absolute Maximum Ratings (4)and Reference Output Capacities1.5 Equivalent Circuit and Dimensions (4)2. Block Diagram2.1 Block Diagram (5)2.2 Pin Function Description (5)3. Operation Description3.1 Start-up Circuit (6)3.2 On-trigger Circuit (7)3.3 Partial Resonance (7)3.4 Standby Mode Control (8)3.5 Output Voltage Control (9)3.6 Soft Drive Circuit (9)3.7 Circuit for Load Shorts (10)3.8 Collector Pin (pin 7) (10)3.9 Thermal Shut-down Circuit (TSD) (10)3.10 Over-voltage Protection Circuit (OVP) (10)3.11 Malfunction Prevention Circuit (11)(patent applied for)3.12 Over-current Protection Circuit (11)4. Standard Circuit (12)5. Design Procedures5.1 Design Flow Chart (13)5.2 Main Transformer Design Procedure (13)5.3 Main Transformer Design Examples (15)5.4 Selection of Constants for (18)Peripheral Components6. Cooling Design6.1 Junction Temperature and Power Losses (19)6.2 Junction Temperature (19)and Thermal Resistance6.3 Cautions for Cooling Design (19)The values presented in this document are based on tentative specifications as of June 29th, 2001, and may change in futureThe MR2900 Series IC modules are designed for both 200V and autosensing input with a burst-mode switching function at micro-loads. These modules are of the partial resonance type, and are comprised of a switching device optimized for both 200V and autosensing power supply input, and a control IC. They are designed to provide the following power supply characteristics.1.2 Characteristics1. An ultra high-speed IGBT with 900V resistance ensures high efficiency and low noise at partial resonance.2. An ultra high-speed IGBT with 900V resistance simplifies design for autosensing power supply input.3. Very low power consumption at micro-loads (in burst mode).4. Onboard start-up circuit eliminates the need for start-up resistors.5. Soft drive circuit achieves low noise levels.6. Excess current protection function (ton limit, primary current limit).7. Excess voltage protection and thermal shut-down function.8. Power supply circuits may be constructed with a minimum of external components. 9. The use of a full mold package provides benefits in insulation design.1.3 ApplicationsTVs, displays, printers, VTR, DVD, STB, air-conditioners, refrigerators, and other electrical appliances, and office equipment.1.4 Absolute Maximum Ratings and Reference Output CapacitiesAbsolute maximum ratingsMaximum output capacity P o [W ]Peak input voltagePeak input currentInput voltage rangeModelV in [V ]I in [A ]90V to 276VAC180V to 276VACMR2920 7 100 150MR2940 90010 150 225Maximum output capacity and input voltage range differ with design conditions.1.5 Equivalent Circuit and DimensionsCollector GNDV ccEmitter/OCL F/BZ/C V in 4.5±0.54.2±0.5 4.25.0±0.2+0.27.6±0.52.7±0.20.7±0.22.2 Pin Function DescriptionPin numberAbbreviationDescription1Z/CTrigger input pinZero detection voltage: 0.35VStandby: Up to 4.5V in standby mode.2 F/B Feedback signal input pint on(min) to t on(max): 1.5V to 4.5V/0μs to 25μs Standby: Oscillation stopped at up to 0.8V. Standby: Oscillation started at 1.8V or higher.3 GND GND pin4 V cc IC power supply pinOscillation start voltage: V cc ≧14V Oscillation stop voltage: V cc ≦8.5V Excess voltage latching voltage:V cc =20V 5 V in Start pinCurrent supplied V in →V cc at start-up Start-up circuit OFF:V cc ≧14V Start-up circuit ON: V cc ≦7.6V6Emitter /OCL Main switching device emitter and current detection pin Excess current detection threshold:0.6VExcess current detection threshold at standby: 50mV7 Collecter Main switching device collector pinCollector Emitter/OCLV cc Z/C F/B V in GNDshort, oscillation is stopped when the voltage at the V cc pin reaches 8.5V, and when this voltage drops to 7.6V the start-up circuit operates again and the voltage at the V cc pin then begins rising. See Fig.3.2.Incorporation of the functions described above improve efficiency, particularly during standby, and reduces the number of start-up resistors required, thus reducing the overall number of components.The MR2000 Series employs current-critical operation to detect energy bursts at the secondary side of the main transformer and switch on the main switching device.Energy discharge timing is detected at the negative edge of the control coil voltage waveform (0.2V in the diagram at right), and the main switching device switched on for current-critical operation.The on-trigger detection voltage (0.2V) incorporates a 50mV hystersis to increase noise resistance.3.3 Partial ResonanceIn current-critical switching power supplies (RCC), damping begins at the resonance frequency (determined by the primary inductance L P of the main transformer and the resonating condenser C) when the secondary current in the circuit formed by connecting the resonating condenser between the collector and GND of the main switching device reaches 0A.The discharge current of the resonating condenser flows through the primary coil and returns energy to the input. Adjustment of the CR time constant applied to the Z/C pin (see diagram at right) allows the main switching device to be turned on at the trough of the damping voltage waveform, thus permitting a reduction in turn-on losses.In a circuit using partial resonance, the energy stored in the resonating condenser during the OFF period of the main switching device is returned to the input, thus permitting a reduction in turn-on losses. This allows the connection of a large-capacity condenser between the collector and GND of the main switching device, and thus permits a reduction in noise.The use of partial resonance is effective in permitting a simple circuit configuration with improved efficiency andnoise reduction.3.4 Standby Mode Control (patent applied for)The MR2000 Series is able to switch between two methodsof output voltage control - normal operation and the standbymode, in a single power supply.The standby mode supported by this IC employs the burst method for intermittent operation under light loads to reduce oscillation frequency and switching losses, and is effective in reducing the standby input voltage undermicro-loads.A unique characteristic of this IC is the use of the burstmode for intermittent operation without stopping IC control, and thus minimizing output ripple. The Z/C pin is clamped to a voltage of 4.5V (typical) or less by an external signal to allow selection of standby modecontrol. The standby mode is cleared (ie restored to thenormal mode) by clearing the clamp voltage on the Z/C pin, and applying a voltage of 4.5V (typical) or higher.In normal operation the ON range of the main switching device is controlled in a linear manner in relation to voltage variation at the F/B pin, while in standby mode operation the Emitter/OCL pin current detection threshold value isswitched from 0.6V for the normal mode to 0.05V for thestandby mode.The collector current is fixed at a peak value by the currentdetection threshold value, and the burst mode is selected.Burst mode control is such that oscillation occurs when the voltage at the F/B pin is 1.8V (typical) or higher, and isstopped when this voltage is 0.8V (typical) or lower.As output voltage control in the standby mode fixes thedrain current peak value for each oscillation cycle, the dutyratio of the oscillating and non-oscillating intervals is varied to ensure a constant voltage.3.5 Output Voltage Control (normal operation)The MR2000 Series controls output voltage with the ON range proportional to the voltage at the F/B pin.When the voltage at the F/B pin is 1.5V the ON range is 0µs, and is controlled in a linear manner so that when the voltage is 4.5V the ON range is 25µs. A current of 200µA=IF/B (typical) flows at the F/B pin, and the impedance of the photocoupler transistor connected externally between the F/B pin and GND is varied with the control signal from the secondary output detection circuit, thus controlling the ON range of the main switching device to produce a constant voltage.The maximum ON range is adjusted by setting the maximum value for the voltage at the F/B pin using a resistor connected externally between the F/B pin and GND.3.6 Soft Drive Circuit (patent applied for)The MR2000 Series supplies the main switching device gate drive voltage from two separate drive circuits.A voltage exceeding the threshold value for the main switching device is supplied from the first drive circuit at the leading edge of the drive voltage waveform to switch on the main switching device with the optimum timing.The drive voltage is then supplied gradually by the second drive circuit (see Fig.3.9).Supply of drive voltage in this manner reduces drive losses, as well as reducing noise due to gate charge current and discharge current when the resonating condenser is switched on.3.7 Circuit for Load ShortsThe MR2000 Series is designed so that when droop occurs under excessive load, output voltage drops, and control coil voltage drops in proportion.When the control coil voltage falls below 4.5V (typical) the standby mode is selected and the Emitter/OCL pin threshold voltage changes from 0.6V to 0.05V, thus limiting the collector current to approximately 1/10th of its previous value.This design permits a reduction in the stress on the MR2000 Series IC in the case of a load short, and control of the short-circuit current in the secondary diode and load circuit.3.8 Collector Pin (pin 7)The collector pin on the main switching device.The transformer is designed, and the resonating condenser adjusted, to ensure that V CE(max) is less than 900V.Depending upon input conditions, the collector pin may be subjected to reverse bias for a period during partial resonance.This IC employs an ultra high-speed IGBT in the main switching device. This device differs from MOSFET devices in that it has no body diode structure, thus requiring connection of an external high-speed diode between the Collector and Emitter/OCL pins.3.9 Thermal Shut-down Circuit (TSD)The MR2000 Series incorporates a thermal shut-down circuit.The onboard IC is latched at 150°C (typical) and oscillation is then stopped.Unlatch is achieved by momentarily dropping the voltage at the V cc pin to V UL (unlatch voltage) or lower.3.10 Over-voltage Protection Circuit (OVP)The MR2000 Series incorporates an over-voltage protection circuit (OVP).Latching occurs when the control coil voltage exceeds 20V (typical), and secondary output over-voltage protection then operates indirectly.Unlatch is achieved in the same manner as for the overheat protection circuit.3.11 Malfunction Prevention Circuit (patent applied for)The use of current-critical operation in the MR2000 Series ensures that the main transformer does not become saturated provided the droop setting is optimized.On the other hand, at start-up, and in the case of a load short, the output voltage is very much less than the set voltage.As the control coil voltage is proportional to the output voltage it also reaches an extremely small value, and the on-trigger timing may be incorrectly detected due to the ringing voltage while the device is OFF and switched on before the current-critical point.To counter this problem, the MR2000 Seriesincorporates a circuit to prevent on-trigger malfunction at start-up, and in the case of a load short. This function disables the on-trigger for a period of 2.7μs (typical) after the main switching device in the IC is switched OFF (on-dead time). This prevents incorrect detection due to the ringing voltage while the device is OFF.This design permits detection of the point at which the transformer secondary current is 0A at start-up, and in the case of a load short. The main switching device is then switched on at this point, allowing abnormal oscillation to be controlled.3.12 Over-current Protection CircuitA current detection resistor is connected between theEmitter/OCL pin and GND to detect current betweenthe emitter of the main switching device and the emitter current detection pin.During stable operation the main switching devicecurrent is limited by pulse-by-pulse operation with the0.6V threshold value.The leading edge clamp function preventsmalfunctioning and thus prevents incorrect detection atturn-on.During standby, the 50mV threshold value is selected and the oscillation noise from the transformer due to burst oscillation is reduced.V O NGND5.2 Main Transformer Design ProcedureThis design procedure provides an example of an electrical design procedure.Ensure that design of insulation materials, insulation configuration, and structure are in accordance with the necessary safety standards as determined by the relevant authorities.5.2.1 Standard Design ConditionsAbbreviation Unit ReferencevalueMinimum input voltage V AC(min) V ― Rated output voltage V o V ― Rated output current I o A ― Maximum output current I o(max) A ― Efficiencyη0.80~0.85Minimum oscillation frequency f (min) kHz 25k ~50kHz Duty ratio D 0.50~0.70 Control coil voltageV NC V 15~17V Effective cross-sectional area of transformer core A e mm 2― Magnetic flux density variation ΔB mT 250~320mTCoil current densityα A/mm 24~6A/mm 2Note that the above values are for reference only, and should be adjusted to suit load conditions.ReexaminationgReview transformer core size and oscillation frequency and redesign if I g is 1mm or greater.V FNC is the control coil voltage rectification diode forward voltage.The reference value for determining the control coil voltage V NC(min) is 15V to 17V.If the V NC(min) value is too small, start-up characteristics may deteriorate and start-up may become difficult. If the V NC(min) value is too large, the over-voltage latch stop voltage V OP is able to be reached easily. Check the V NC(min) voltage in an actual circuit during the design process to determine its optimum value.A NC C5.3 Main Transformer Design Examples5.3.1 Initial SetupInput voltage AC90~276V V O1:DC135V, 0.45A Efficiency 85% V O2:DC35V,0.40ARated output V O3:DC16V,0.40ATotal output 81.2W Oscillationfrequency at droop 29.6kHzDroop output110.36W (rated output x 1.36) Duty ratioT ON /T=0.655P on(max) is s or less. L °C isq μs.q andS1S2S35.4 Selection of Constants for Peripheral ComponentsT j(max) for the MR Series is 150°C.As operation of the MR Series is accompanied by an increase in temperature associated with power losses, it is necessary to consider the type of heat sink to be used. While a design which ensures that T j(max) is not exceeded is of absolute importance, the overheat protection function (T SD =150°C (typical)) must be also considered in any design. The extent to which T j is derated in a design is therefore extremely important in improving reliability.The majority of power losses during operation of the MR Series are associated with the internal MOSFET.If the majority of power losses are considered as ON losses, they may be expressed by the following equation.P D =V DS ×I DThe temperature increase (ΔT j ) due to power losses (P D ) is expressed as,ΔT j +T a ≦T j(max)and if T SD =150°C (typical) and T SD(min)=120°C are assumed, P D is limited so that the following equation is satisfied.ΔT j +T a ≦T SD(min)T j may be calculated as follows using the thermal resistance θja .T j =( P D ×θja ) +T aθja is the thermal resistance in the vicinity of the junction, and is expressed as follows.θja =θjc +θcf +θfaThermal shutdown (TSD) is a protective function which stops and latches operation at 150°C in the event of abnormal heating of the MR1520. Circuit design therefore requires a cooling design in which temperature has been sufficiently derated. Shindengen recommends that cooling design be such that case temperature does not exceed 100°C.6.1 Junction Temperature and Power Losses 6.2 Junction Temperature and Thermal Resistance Abbreviation UnitThermal resistance between junction and vicinity. θja ℃/WThermal resistance between junction and case. θjc ℃/WThermal resistance between case and fins(contact thermal resistance).θcf ℃/W Thermal resistance between case and fins(contact thermal resistance).θfa ℃/W 6.3 Cautions for Cooling Design。

国家及地区代码-V1.1

地区代码 004 184 200 007 006 001 009 131 005 212 008 003 013 012 010 014 213 018 017 020 031 030 016 033 022 202 023 029 025 027 015 024 214 026 019 021 036 215 044 039 043 173 093 047 045 041 035 011 042 216 046 204 037 217 049 050 071 052 051 053 054 002 055 060 056 218 059

南苏丹

South Sudan

249

169 NT

中立区

Neutral Zone

229

170 NU

纽埃

Niue

230

171 NZ

纽西兰

New Zealand

133

172 OM

阿曼

Oman

138

173 PA

巴拿马

Panama

141

174 PE

秘鲁

Peru

144

175 PF

法属玻里尼西亚

French Polynesia

地区简称 AD AE AF AG AI AL AM AN AO AQ AR AS AT AU AW AZ BA BB BD BE BF BG BH BI BJ BL BM BN BO BR BS BT BV BW BY BZ CA CC CD CF CG CH CI CI CK CL CM CN CO CQ CR CU CV CX CY CZ DE DJ DK DM DO DZ EC EE EG EH ER

Norfolk Island

227

EN29LV640L-90TIP资料