第6章 ARM9、Cortex M4M7 DMA与定时器

ARM Cortex各系列处理器分类比较之欧阳文创编

Cortex-M系列M0:Cortex-M0是目前最小的ARM处理器,该处理器的芯片面积非常小,能耗极低,且编程所需的代码占用量很少,这就使得开发人员可以直接跳过16位系统,以接近8 位系统的成本开销获取 32 位系统的性能。

Cortex-M0 处理器超低的门数开销,使得它可以用在仿真和数模混合设备中。

M0+:以Cortex-M0 处理器为基础,保留了全部指令集和数据兼容性,同时进一步降低了能耗,提高了性能。

2级流水线,性能效率可达1.08 DMIPS/MHz。

M1:第一个专为 FPGA 中的实现设计的 ARM 处理器。

Cortex-M1 处理器面向所有主要 FPGA 设备并包括对领先的 FPGA 综合工具的支持,允许设计者为每个项目选择最佳实现。

M3:适用于具有较高确定性的实时应用,它经过专门开发,可使合作伙伴针对广泛的设备(包括微控制器、汽车车身系统、工业控制系统以及无线网络和传感器)开发高性能低成本平台。

此处理器具有出色的计算性能以及对事件的优异系统响应能力,同时可应实际中对低动态和静态功率需求的挑战。

M4:由 ARM 专门开发的最新嵌入式处理器,用以满足需要有效且易于使用的控制和信号处理功能混合的数字信号控制市场。

M7:在 ARM Cortex-M 处理器系列中,Cortex-M7 的性能最为出色。

它拥有六级超标量流水线、灵活的系统和内存接口(包括AXI 和AHB)、缓存(Cache)以及高度耦合内存(TCM),为MCU 提供出色的整数、浮点和 DSP 性能。

互联:64位 AMBA4 AXI, AHB外设端口 (64MB 到 512MB)指令缓存:0 到 64kB,双路组相联,带有可选 ECC数据缓存:0 到 64kB,四路组相联,带有可选 ECC指令TCM:0 到 16MB,带有可选 ECC数据TCM:0 到 16MB,带有可选 ECCCortex-M系列规格对比Cortex-A系列:ARM Cortex-A 系列是一系列用于复杂操作系统和用户应用程序的应用程序处理器。

Cortex-M4 Systick滴答定时器

Cortex-M4 Systick滴答定时器关于systick在Cortex-M4中有讲到,我们大家平常在单片机开发中经常会使用到延时函数,一般的,我们会使用变量自加循环判断的方法来实现软件延时。

但是这种方法有个弊端——延时时间不精确。

主要体现在:1、在C语言编写的延时函数中,每条函数语句的执行时间可能不同,这样,在实现延时的过程中,想通过增加或减少函数语句来实现延时的增加或减小控制起来不太方便,时间的精确性当然很难控制;2、由于各种不同的控制器运行的主频可能不同,执行相同的延时函数所需要的的时间值可能就不同。

这样,使得这种延时函数在不同的平台上移植起来时间的精确性就更不可靠。

所以,我们就不使用这样的延时方法。

从ARM Cortex-M0内核开始,一直到现在的ARM Cortex-M4,这些内核中都搭载了systick滴答定时器,它放在了NVIC中,主要目的是为了给操作系统提供一个滴答中断。

当然,毕竟它也是一个定时器,我们就可以利用它来做到精确的软件延时。

systick定时器是一个递减的计数器,如果设定初值并使能它以后,它会在每个系统时钟周期里计数器减1,直到减到0为止。

然后,systick计数器自动重装初值并继续递减计数,如果软件上又使能了systick计数器的中断,那么,在systick计数器减到0的时候,中断被触发,当然,中断标志位也被置位。

那么,每次计数器递减到0,所经过的时间值为:系统时钟周期*计数器初值。

systick定时器内部几个常用的寄存器:1、systick控制及状态寄存器CTRL:其中,CTRL[16]位是COUNTFLAG标志位,当systick计数到0的时候,该位置1,如果读取该位,则硬件自动清0,所以我们可以用软件判断是否计数到0。

CTRL[2]位是CLKSOURE标志位,用来指示当前systick定时器的时钟源,CLKSOURCE=1表示时钟源是内核时钟(一般我们会选择这种情况);CLKSOURCE=0表示时钟源是外部时钟源。

Cortex-M4原理与实践实验报告7 并行ADC与DAC

Cortex-M4原理与实践实验报告题目:并行ADC与DAC一、实验目的1. 熟悉并口 AD/DA 芯片的结构及工作方式2. 熟悉并行口的扩展编程二、实验设备1.计算机一台,操作系统为WindosXP或Windos7,装有CCSv6.0软件。

2.EK-TM4C1294XL实验开发板一块。

B连接线一条。

三、实验原理和流程1、Dac7821芯片原理(1)Dac7821 芯片简介Dac7821 是一个12 位的电流输出的数模转换器,器件的工作电压为2.5V 到5.5V。

芯片是通过快速的并口接口工作。

如图1为芯片的功能框图。

图 1 Dac7821功能框图(2)Dac7821时序图(3)Dac7821时序要求图 3 DA时序要求(4)Dac7821时序要求图 4 Dac7821管脚定义图 2 Dac7821时序图2、ADS7881芯片原理(1)ADS7881芯片简介ADS7881是12位4-MSPS AD转换器,提供2.5V的内部参考电压。

该芯片提供了一个12位的并行接口与额外的与8位模式的接口。

如图5为改芯片的功能框图。

图 5 ADS7881功能框图(2)ADS7881管脚定义图6ADS7881管脚定义(3)ADS7881时序图图7 ADS7881时序图(4)ADS7881时序要求图8 AD时序要求流程图如下:开始初始化系统时钟初始化对应的GPIO口根据时序图赋值结束图9 DA实验流程图开始初始化系统时钟初始化对应的GPIO口和UART根据时序图给相应的IO赋高低电平读转化后的数据并打印输出结束图10 AD实验流程图四、实验代码、注释1、DA实验实验代码:#include <stdbool.h>#include <stdint.h>#include "inc/hw_gpio.h"#include "inc/hw_memmap.h"#include "inc/hw_types.h"#include "driverlib/gpio.h"#include "driverlib/epi.h"#include "driverlib/rom_map.h"#include "driverlib/sysctl.h"#include "driverlib/timer.h"#include "driverlib/rom.h"#include "inc/tm4c1294ncpdt.h"#define DAC_DATAH_PERIPH_G SYSCTL_PERIPH_GPIOG #define DAC_DATAH_BASE_G GPIO_PORTG_BASE#define DAC_DATAH_D11 0x40026004#define DAC_DATAH_D11_S(a) ((a) >> 11)#define DAC_DATAH_D10 0x40026008#define DAC_DATAH_D10_S(a) ((a) >> 9)#define DAC_DATAH_PERIPH_A SYSCTL_PERIPH_GPIOA#define DAC_DATAH_BASE_A GPIO_PORTA_BASE#define DAC_DATAH_D9 0x40004200#define DAC_DATAH_D9_S(a) ((a) >> 2)#define DAC_DATAH_D8 0x40004100#define DAC_DATAH_D8_S(a) ((a) >> 2)#define DAC_DATAH_PERIPH_C SYSCTL_PERIPH_GPIOC#define DAC_DATAH_BASE_C GPIO_PORTC_BASE#define DAC_DATAH_D7 0x40006040#define DAC_DATAH_D7_S(a) ((a) >> 3)#define DAC_DATAH_D6 0x40006080#define DAC_DATAH_D6_S(a) ((a) >> 1) //#define DAC_DATAH_D5 0x40006100 //0000 0100 //#define DAC_DATAH_D5_S(a) ((a) << 1) //0001 0000#define DAC_DATAH_D4 0x40006200 //0000 0100 //#define DAC_DATAH_D4_S(a) ((a) << 3) //0001 0000#define DAC_DATAH_PERIPH_K SYSCTL_PERIPH_GPIOK#define DAC_DATAH_BASE_K GPIO_PORTK_BASE#define DAC_DATAH_D3_S(a) ((a) << 3) //0001 1011 0000 1000 #define DAC_DATAH_D3 0x40061020 //1000 0000#define DAC_DATAH_D2_S(a) ((a) << 1)#define DAC_DATAH_D2 0x40061010#define DAC_DATAH_D1_S(a) ((a) >> 1)#define DAC_DATAH_D1 0x40061008#define DAC_DATAH_D0_S(a) ((a) >> 3)#define DAC_DATAH_D0 0x40061004#define DAC_DATAH_PIN_11 GPIO_PIN_0#define DAC_DATAH_PIN_10 GPIO_PIN_1#define DAC_DATAH_PIN_9 GPIO_PIN_7#define DAC_DATAH_PIN_8 GPIO_PIN_6#define DAC_DATAH_PIN_7 GPIO_PIN_4#define DAC_DATAH_PIN_6 GPIO_PIN_5#define DAC_DATAH_PIN_5 GPIO_PIN_6#define DAC_DATAH_PIN_4 GPIO_PIN_7#define DAC_DATAH_PIN_3 GPIO_PIN_3#define DAC_DATAH_PIN_2 GPIO_PIN_2#define DAC_DATAH_PIN_1 GPIO_PIN_1#define DAC_DATAH_PIN_0 GPIO_PIN_0#define DAC_WR_CS_RD_PERIPH SYSCTL_PERIPH_GPIOE#define DAC_WR_CS_RD_BASE GPIO_PORTE_BASE#define DAC_WR_PIN GPIO_PIN_2#define DAC_WR_PIN_REG 0x40024010#define DAC_CS_PIN GPIO_PIN_1#define DAC_CS_PIN_REG 0x40024008#define SET_DAC_DA TA(ui16Byte) \{ \HWREG(DAC_DATAH_D11) = DAC_DA TAH_D11_S(ui16Byte); \HWREG(DAC_DATAH_D10) = DAC_DATAH_D10_S(ui16Byte); \HWREG(DAC_DATAH_D9) = DAC_DATAH_D9_S(ui16Byte); \HWREG(DAC_DATAH_D8) = DAC_DATAH_D8_S(ui16Byte); \HWREG(DAC_DATAH_D7) = DAC_DATAH_D7_S(ui16Byte); \HWREG(DAC_DATAH_D6) = DAC_DATAH_D6_S(ui16Byte); \HWREG(DAC_DATAH_D5) = DAC_DATAH_D5_S(ui16Byte); \HWREG(DAC_DATAH_D4) = DAC_DATAH_D4_S(ui16Byte); \HWREG(DAC_DATAH_D3) = DAC_DATAH_D3_S(ui16Byte); \HWREG(DAC_DATAH_D2) = DAC_DATAH_D2_S(ui16Byte); \HWREG(DAC_DATAH_D1) = DAC_DATAH_D1_S(ui16Byte); \HWREG(DAC_DATAH_D0) = DAC_DATAH_D0_S(ui16Byte); \}uint32_t g_ui32SysClock;void WriteDataGPIO(uint16_t ui16Data){// 数据写入HWREG(DAC_CS_PIN_REG)=0xff; //CS高电平SysCtlDelay(3);HWREG(DAC_WR_PIN_REG) = 0; // WR低电平SysCtlDelay(1);HWREG(DAC_CS_PIN_REG) = 0; // CS低电平SET_DAC_DA TA(ui16Data);SysCtlDelay(5);HWREG(DAC_CS_PIN_REG) = 0xFF; // CS高电平SysCtlDelay(1);HWREG(DAC_WR_PIN_REG) = 0xFF; //WR高电平SysCtlDelay(6);// Pull CS Low.HWREG(DAC_CS_PIN_REG) = 0; //CS低电平SysCtlDelay(3);HWREG(DAC_CS_PIN_REG)=0xff; //CS高电平}void main(){volatile uint32_t ui32Loop,ui32val,ui32Loop0,ui32Loop1,ui32Loop2,ui32Loop3,ui32Loop4;SYSCTL_RCGCGPIO_R |= SYSCTL_RCGCGPIO_R5;// 使能各模块SysCtlPeripheralEnable(SYSCTL_PERIPH_GPIOF);GPIOPinTypeGPIOOutput(GPIO_PORTF_BASE, GPIO_PIN_0 | GPIO_PIN_4);SysCtlPeripheralEnable(DAC_DATAH_PERIPH_A);SysCtlPeripheralEnable(DAC_DATAH_PERIPH_C);SysCtlPeripheralEnable(DAC_DATAH_PERIPH_G);SysCtlPeripheralEnable(DAC_DATAH_PERIPH_K);SysCtlPeripheralEnable(DAC_WR_CS_RD_PERIPH);SysCtlGPIOAHBEnable(SYSCTL_PERIPH_GPIOA);SysCtlGPIOAHBEnable(SYSCTL_PERIPH_GPIOC);SysCtlGPIOAHBEnable(SYSCTL_PERIPH_GPIOG);SysCtlGPIOAHBEnable(SYSCTL_PERIPH_GPIOK);SysCtlGPIOAHBEnable(SYSCTL_PERIPH_GPIOE);// 配置功能输出GPIOPinTypeGPIOOutput(DAC_WR_CS_RD_BASE, DAC_CS_PIN);GPIOPinTypeGPIOOutput(DAC_WR_CS_RD_BASE, DAC_WR_PIN);GPIOPinTypeGPIOOutput(DAC_DATAH_BASE_C, DAC_DATAH_PIN_7 |DAC_DATAH_PIN_6 | DAC_DATAH_PIN_5 | DAC_DATAH_PIN_4);GPIOPinTypeGPIOOutput(DAC_DATAH_BASE_K, DAC_DATAH_PIN_3 |DAC_DATAH_PIN_2 | DAC_DA TAH_PIN_1 | DAC_DATAH_PIN_0);GPIOPinTypeGPIOOutput(DAC_DATAH_BASE_A, DAC_DATAH_PIN_9 | DAC_DATAH_PIN_8);GPIOPinTypeGPIOOutput(DAC_DATAH_BASE_G, DAC_DATAH_PIN_11 | DAC_DATAH_PIN_10);// 设置系统时钟g_ui32SysClock = SysCtlClockFreqSet((SYSCTL_OSC_INT | SYSCTL_USE_PLL |SYSCTL_CFG_VCO_320), 120000000);ui32val = 2000;while(1){WriteDataGPIO(ui32val);SysCtlDelay(100);for(ui32Loop = 0; ui32Loop < 2000000; ui32Loop++){}ui32val += 100;if(ui32val >= 4000)ui32val = 0;}}实验现象:因没有示波器无法查看2、AD实验实验代码:#include "stdint.h"#include "stdbool.h"#include "driverlib/debug.h"//调试#include "inc/hw_types.h"//数据类型设置,寄存器访问封装#include "inc/hw_memmap.h"//基址#include "driverlib/fpu.h"#include "driverlib/sysctl.h"//使能寄存器#include "driverlib/rom.h"#include "driverlib/pin_map.h"#include "grlib/grlib.h"#include "driverlib/gpio.h"#include "driverlib/adc.h"#include "inc/hw_gpio.h"#include "inc/tm4c1294ncpdt.h"#include "driverlib/uart.h"#include "utils/uartstdio.h"volatile uint32_t ui32SysClock;void InitConsole(void)//UART初始化{// 由于UART0使用PA0,PA1两个引脚,因此需要使能GPIOA模块SysCtlPeripheralEnable(SYSCTL_PERIPH_GPIOA);// 因为有引脚复用,所以要对PA0和PA1两个引脚的功能进行选择// 这里将它们选择为执行UART0模块的功能GPIOPinConfigure(GPIO_PA0_U0RX);GPIOPinConfigure(GPIO_PA1_U0TX);// 对于PA0和PA1两个引脚,在将它们作为UART功能使用之前,需要对它们做一些有关UART的配置GPIOPinTypeUART(GPIO_PORTA_BASE, GPIO_PIN_0 | GPIO_PIN_1);UARTStdioConfig(0, 115200, ui32SysClock);}void GPIOint()//GPIO口初始化{GPIO_PORTA_AHB_DIR_R = 0x00; //PA7,PA6,对应并口线D8,D9GPIO_PORTC_AHB_DIR_R = 0x00; //PC7-4,对应并口线D4-D7GPIO_PORTD_AHB_DIR_R = 0x30;//PD4,PD5,对应AD_convst,AD_byteGPIO_PORTE_AHB_DIR_R = 0x03; //PE0对应RD,PE1对应CSGPIO_PORTG_AHB_DIR_R = 0x00; //PG1,PG0,对应并口线D10,D11GPIO_PORTK_DIR_R = 0x00; //PK3-0,对应并口线D0-D3//启用数字I/O功能GPIO_PORTA_AHB_DEN_R = 0xc0; //1100 0000 PA7,PA6置1GPIO_PORTC_AHB_DEN_R = 0xf0;//1111 0000,PC7-4置1GPIO_PORTD_AHB_DEN_R = 0x70;//0111 0000,PD4,PD5置1GPIO_PORTE_AHB_DEN_R = 0x03;//0000 0011,PE0对应RD,PE1对应CS 置1GPIO_PORTG_AHB_DEN_R = 0x03;//0000 0011,PG1,PG0置1GPIO_PORTK_DEN_R = 0x0f;//0000 1111,PK3-0置1}int main(void){volatile uint32_t ui32Loop,ui32Loop0,ui32Loop1,ui32Loop2,ui32Loop3,ui32Loop4;ui32SysClock=SysCtlClockFreqSet((SYSCTL_OSC_INT | SYSCTL_USE_PLL | SYSCTL_CFG_VCO_320), 120000000);//初始化系统时钟SYSCTL_RCGCGPIO_R |= (SYSCTL_RCGCGPIO_R9 | SYSCTL_RCGCGPIO_R6 | SYSCTL_RCGCGPIO_R4 |SYSCTL_RCGCGPIO_R3| SYSCTL_RCGCGPIO_R2 | SYSCTL_RCGCGPIO_R1 | SYSCTL_RCGCGPIO_R0);//使能GPIO用到的端口时钟ui32Loop = SYSCTL_RCGCGPIO_R;//时钟信号赋值GPIOint();//GPIO口初始化InitConsole();//UART初始化while(1)//根据时序图给相应的IO赋高低电平{GPIOPinWrite(GPIO_PORTD_BASE,GPIO_PIN_6|GPIO_PIN_5|GPIO_PIN_4,0x10);GPIOPinWrite(GPIO_PORTE_BASE,GPIO_PIN_0|GPIO_PIN_1,0x03);GPIOPinWrite(GPIO_PORTE_BASE,GPIO_PIN_0|GPIO_PIN_1,0x01);GPIOPinWrite(GPIO_PORTD_BASE,GPIO_PIN_6|GPIO_PIN_5|GPIO_PIN_4,0x10);GPIOPinWrite(GPIO_PORTD_BASE,GPIO_PIN_6|GPIO_PIN_5|GPIO_PIN_4,0x40);GPIOPinWrite(GPIO_PORTE_BASE,GPIO_PIN_0|GPIO_PIN_1,0x03);GPIOPinWrite(GPIO_PORTD_BASE,GPIO_PIN_6|GPIO_PIN_5|GPIO_PIN_4,0x00);GPIOPinWrite(GPIO_PORTE_BASE,GPIO_PIN_0|GPIO_PIN_1,0x01);GPIOPinWrite(GPIO_PORTD_BASE,GPIO_PIN_6|GPIO_PIN_5|GPIO_PIN_4,0x10);SysCtlDelay(10);GPIOPinWrite(GPIO_PORTE_BASE,GPIO_PIN_0|GPIO_PIN_1,0x00);SysCtlDelay(10);GPIOPinWrite(GPIO_PORTD_BASE,GPIO_PIN_6|GPIO_PIN_5|GPIO_PIN_4,0x50);ui32Loop1 = (GPIO_PORTG_AHB_DA TA_R&0x03);//PG1,PG0,并口线D10,D11ui32Loop2 = (GPIO_PORTA_AHB_DA TA_R&0xc0);//PA7,PA6,并口线D8,D9ui32Loop3 = (GPIO_PORTC_AHB_DA TA_R&0xf0);//PC7-4,并口线D4-D7ui32Loop4 = (GPIO_PORTK_DA TA_R&0x0f) ;//PK3-0,并口线D0-D3ui32Loop0 = (ui32Loop1%2*8+ui32Loop1/2*4+ui32Loop2/64)*256+((ui32Loop3&0x10)/16*8+(ui32Loop3& 0x20)/32*4+(ui32Loop3&0x40)/64*2+(ui32Loop3&0x80)/128)*16+ui32Loop4;UARTprintf("%04d \n",ui32Loop0);SysCtlDelay(10);GPIOPinWrite(GPIO_PORTE_BASE,GPIO_PIN_0|GPIO_PIN_1,0x03);}}实验现象:当跳帽套上时J32的23管脚的时候,串口的数值与滚轮装置的转变而转变。

ARM Cortex-M4学习与实践——纪成

J-Link

P&E Multilink

OSBDM

山东大学 Kinetis培训

Kinetis调试工具

山东大学智能车工作室根据开源资料,自行设计了OSBDM调试器和 USBDM调试器,其中OSBDM由飞思卡尔官方开源,目前由P&E公司维护, USBDM由网友pgo开源和维护。 经过二次设计和完善,目前山大设计的OSBDM分别支持CW、IAR和 Keil MDK三种开发环境,而且支持飞思卡尔几乎全系列MCU,包括: Freescale HCS12/HCS12(X)/HCS08(已测试MC9S12DG128、MC9S08JM60) Freescale Coldfire V1,V2,V3,V4(已测试MCF52259) Freescale DSC全系列(已测试MC56F8366) Freescale PowerPC架构的Qorivva系列(已测试MPC5604B) Freescale Cortex-M4核的Kinetis系列(已测试K10、K60)

山东大学 Kinetis培训

一、飞思卡尔Kinetis功能特性

1、ARM发展史 2、ARMv7处理器分类 3、ARM Cortex-M4特性 4、飞思卡尔Kinetis家族介绍 5、K60内部资源介绍

山东大学 Kinetis培训

ARM发展史

ARM架构发展历程

山东大学 Kinetis培训

ARMv7处理器分类

ARMv7根据应用分类:

• 应用处理器(Cortex-A系列) Aplication Processor • 实时控制器(Cortex-R系列) Real-time Processor • 微控制器(Cortex-M系列) Micro Controller 山东大学 Kinetis培训

计科一班 林永强 Cortex M4处理器

Cortex M4处理器班级:计科一班姓名:林永强学号:2013041488Cortex-M4处理器包含以下部分:编程模型,内存模型,异常模型,故障处理,电源管理。

Cortex-M4是一种面向数字信号处理(DOC)和高级微控制器(MCU)应用的高效率的信号处理能力,同时还低能耗,低成本,简单的特点。

Cortex-M4处理器内集成了单循环乘法(MAU)单元、饱和算法指令和可选择的单精度浮点单元(FPU),同时还保留了Cortex-M 系列的一贯特色技术,比如处理性能量高,完整休眠状态。

一.编程模型除了单个核寄存器的描述外,它包含了用于软件的处理器模式和特权级别的信息执行堆栈。

1. 软件执行的处理器模式和特权级别处理器模式:a.用于执行应用软件的线程模式。

处理器在复位时进入线程模式。

b.用于处理异常的处理程序模式。

处理器完成所有异常处理时,返回到线程模式。

软件执行的特权级别:(1)未经授权的软件:a.对MSR和MRS指令访问有限,且不能使用CPS指令b.无法访问系统定时器,NVIC,或系统控制块c.可能有限制访问内存或外设。

未经授权的软件在特权级执行。

(2)特权的软件可以使用所有的指令,并拥有所有的资源。

特权级别的特权软件执行。

在线程模式,控制寄存器控制软件是否执行特权,在处理程序模式中,软件执行始终是特权的。

只有特权的软件可以写入控制寄存器来改变线程模式的软件执行权限级别。

未经授权的软件可以使用SVC4指令使主管C所有将控制权转让给特权软件。

2.栈处理器使用全栈。

这意味着堆栈指针保存在内存中的最后一个堆栈的地址。

当处理器推动新项目入栈,它使STACK指针和写项目到新的存储位置。

处理器实现了2个栈,主栈和进程栈,在独立寄存器中有一个指针。

在线程模式,控制寄存器控制处理器是否使用主堆栈或进程的堆栈,在处理程序模式中,处理器总是使用主堆栈。

3.核心寄存器(1)核心寄存器:r0-r12是32位通用寄存器的数据操作。

嵌入式系统试题库

嵌入式系统试题库一、选择题(20分)1、下列描述不属于RISC 计算机的特点的是()。

A. 流水线每周期前进一步。

B. 更多通用寄存器。

C. 指令长度不固定,执行需要多个周期。

D. 独立的Lo a d和St or e指令完成数据在寄存器和外部存储器之间的传输。

2、存储一个32位数Ox2168465到2000H,....__,2003H四个字节单元中,若以小端模式存储,则2000H 存储单元的内容为()。

A 、Ox21A 、OvB、Ox68B 、3.3vC 、Ox65C 、+sv ,..___,+15vD 、Ox023、RS232-C 串口通信中,表示逻辑1的电平是()。

D 、-5v ,.___,-15v4、ARM 汇编语句"A DD R O, R 2, R 3, LSL#l"的作用是()。

A. R O= R 2 + (R3 << 1)C. R 3= R O+ (R 2 << 1) B. R O=(R 2<< 1) + R 3D. (R 3 << 1)= R O+ R2 5、I RQ中断的入口地址是()。

A 、OxOOOOOOOOB 、Ox00000008C 、Ox00000018D 、Ox000000146、S3C 2440X 1/0口常用的控制器是()。

A. 端口控制寄存器(GP A C ON -G PJ C O N )。

B. 端口数据寄存器(GPA DAT-G PJ D AT )。

C. 外部中断控制寄存器(EXT I N T n )。

D. 以上都是。

7、GET伪指令的含义是()A. 包含一个外部文件B. 定义程序的入口C. 定义一个宏D. 声明一个变量8、A DD R O, R l, #3 ; #3属于()寻址方式。

A. 立即寻址B. 多寄存器寻址C. 寄存器直接寻址D. 相对寻址9、ARM 指令集和Th um b 指令集分别是()位的。

ARM Cortex系列

Cortex系列ARM核心及体系结构介绍作者:杨硕,华清远见嵌入式学院讲师。

众所周知,英国的ARM公司是嵌入式微处理器世界当中的佼佼者。

ARM一直以来都是自己研发微处理器内核架构,然后将这些架构的知识产权授权给各个芯片厂商,精简的CPU架构,高效的处理能力以及成功的商业模式让ARM公司获得了巨大的成功,使他迅速占据了32位嵌入式微处理器的大部分市场份额,甚至现在,ARM芯片在上网本市场的也大有与INTEL 的ATOM处理器一较高低的实力。

目前,随着对嵌入式系统的要求越来越高,作为其核心的嵌入式微处理器的综合性能也受到日益严峻的考验,最典型的例子就是伴随3G网络的推广,对手机的本地处理能力要求很高,现在一个高端的智能手机的处理能力几乎可以和几年前的笔记本电脑相当。

为了迎合市场的需求,ARM公司也在加紧研发他们最新的ARM架构,Cortex系列就是这样的产品。

在Cortex之前,ARM核都是以ARM为前缀命名的,从ARM1一直到ARM11,之后就是Cortex系列了。

Cortex在英语中有大脑皮层的意思,而大脑皮层正是人脑最核心的部分,估计ARM公司如此命名正有此含义吧。

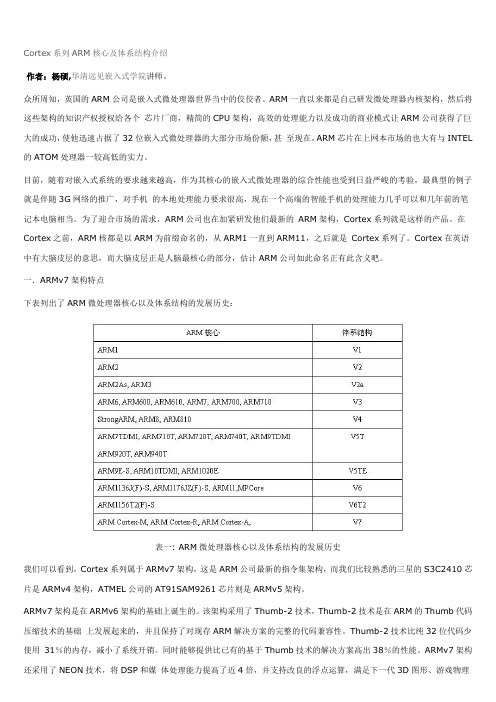

一.ARMv7架构特点下表列出了ARM微处理器核心以及体系结构的发展历史:表一: ARM微处理器核心以及体系结构的发展历史我们可以看到,Cortex系列属于ARMv7架构,这是ARM公司最新的指令集架构,而我们比较熟悉的三星的S3C2410芯片是ARMv4架构,ATMEL公司的AT91SAM9261芯片则是ARMv5架构。

ARMv7架构是在ARMv6架构的基础上诞生的。

该架构采用了Thumb-2技术,Thumb-2技术是在ARM的Thumb代码压缩技术的基础上发展起来的,并且保持了对现存ARM解决方案的完整的代码兼容性。

Thumb-2技术比纯32位代码少使用31%的内存,减小了系统开销。

同时能够提供比已有的基于Thumb技术的解决方案高出38%的性能。

cortex m0 定时器 c语言

《探索Cortex M0定时器在C语言中的应用》1. 前言Cortex M0是一款广泛应用于嵌入式系统中的微控制器,其定时器功能在实际开发中具有重要意义。

本文将深入探讨Cortex M0定时器在C语言中的应用,旨在帮助读者全面理解和灵活应用这一主题。

2. Cortex M0定时器概述在嵌入式系统中,定时器是一种常见的硬件设施,用于按照特定的时间间隔产生中断或执行特定的任务。

Cortex M0处理器内置了多个定时器,可用于计时、延时、PWM发生等各种应用场景。

3. 定时器的初始化与配置在C语言中,通过寄存器的操作可以对Cortex M0定时器进行初始化和配置。

首先需要设置定时器的工作模式、时钟源、重载值等参数,然后启动定时器开始计时。

这一部分的代码编写对于理解定时器的工作原理至关重要。

4. 定时器中断的处理定时器到达设定的计时值后会触发中断,此时需要编写中断服务函数来处理定时器中断。

在C语言中,对于中断的处理需要合理设置中断优先级、清除中断标志位等操作,以确保定时器中断能够被正确响应并执行相应的任务。

5. 定时器应用案例分析通过一个简单的定时器应用案例,我们可以更加直观地理解Cortex M0定时器在C语言中的应用。

可以利用定时器产生一定频率的脉冲信号,或者实现精确的延时功能等。

6. 总结与展望通过本文的学习,读者可以全面理解Cortex M0定时器在C语言中的应用,掌握定时器的初始化配置、中断处理等关键技术,从而能够灵活应用定时器功能解决实际的嵌入式系统开发问题。

未来,随着嵌入式系统的不断发展,定时器功能将会变得更加重要和多样化。

个人观点:在嵌入式系统开发中,定时器功能是一项必不可少的技术。

CortexM0定时器作为处理器的核心功能之一,其灵活性和高效性使得它在各种嵌入式系统中得到广泛应用。

对于嵌入式系统工程师来说,深入理解Cortex M0定时器在C语言中的应用,能够为他们的工作带来更多的可能性和灵活性。

STM32单片机基础知识

STM32单片机基础知识STMicroelectronics的STM32系列是一系列广受欢迎的32位ARM Cortex-M微控制器(MCU)。

这些单片机被广泛应用于嵌入式系统,因为它们具有高性能、低功耗、丰富的外设和丰富的开发工具生态系统。

1、处理器核心STM32系列单片机采用不同版本的ARM Cortex-M处理器核心,可根据应用的性能和功耗需求进行选择。

从低功耗的Cortex-M0到高性能的Cortex-M7,这些核心提供了广泛的选择,适用于各种嵌入式应用。

选型时需要考虑处理器性能、成本、功耗以及应用的实际需求。

Cortex-M0:特点:Cortex-M0是Cortex-M系列中的低功耗、低成本核心,适用于对功耗有严格要求的应用。

它是一种精简指令集(RISC)架构,具有简化的指令集和低延迟的操作。

性能:Cortex-M0通常具有较低的时钟速度,适用于低复杂度的嵌入式系统。

应用:它常用于传感器、小型家电、智能卡和其他低功耗、成本敏感的应用。

Cortex-M0+:特点:Cortex-M0+是Cortex-M系列中的改进型号,继承了Cortex-M0的低功耗特性,并增加了一些性能和功能。

它具有更高的性能和更多的指令,可提供更好的性价比。

性能:Cortex-M0+通常比Cortex-M0具有更高的时钟速度,同时保持低功耗,适用于中等复杂度的应用。

应用:它常用于物联网设备、便携式医疗设备、智能传感器等。

Cortex-M3:特点:Cortex-M3是Cortex-M系列中的通用用途核心,适用于广泛的应用领域。

它具有较高的性能和更多的功能,适合中等和高复杂度的嵌入式系统。

性能:Cortex-M3通常具有更高的时钟速度和更大的指令集,支持多线程处理,适用于实时操作系统(RTOS)。

应用:它广泛用于工业自动化、消费电子、汽车电子等多个领域,要求高性能和实时性。

Cortex-M4:特点:Cortex-M4是Cortex-M系列中的高性能型号,具有浮点运算单元(FPU),能够进行单精度浮点数运算。

(完整word)CORTEX-M4知识点总结,推荐文档

Cortex-M4内核知识点总结余明目录Cortex-M4内核知识点总结 (1)1 ARM处理器简介 (4)2 架构 (5)2.1架构简介 (5)2.2编程模型 (5)2.3存储器系统 (8)2.4复位和复位流程 (12)3 指令集 (14)3.1 CM4指令集特点 (14)3.2 Cortex-M处理器间的指令集比较 (14)3.3 汇编指令简要介绍 (14)3.3.1 处理器内传送数据 (14)3.3.2 存储器访问指令 (15)3.3.3 算数运算 (16)3.3.4 逻辑运算 (17)3.3.5 移位 (17)3.3.6 异常相关指令 (17)4 存储器系统 (18)4.1 存储器外设 (18)4.2 Bootloader (18)4.3位段操作 (19)4.4 存储器大小端 (19)5 异常和中断 (21)5.1 中断简介 (21)5.2异常类型 (21)5.3 中断管理 (22)5.4 异常或中断屏蔽寄存器 (23)5.4.1 PRIMASK (23)5.4.2 FAULMASK (M0中无) (23)5.4.3 BASEPRI(M0中无) (23)5.5 中断状态及中断行为 (23)5.5.1 中断状态 (23)5.5.2 中断行为 (24)5.6 各Cortex-M处理器NVIC差异 (26)6 异常处理 (28)6.1 C实现的异常处理 (28)6.2 栈帧 (28)6.3 EXC_RETURN (29)6.4异常流程 (30)6.4.1 异常进入和压栈 (30)6.4.2 异常返回和出栈 (31)7 低功耗和系统控制特性 (32)7.1 低功耗模式 (32)7.1 SysTick定时器 (32)8 OS支持特性 (34)8.1 OS支持特性简介 (34)8.2 SVC和PendSV (34)8.3 实际的上下文切换 (35)1 ARM处理器简介ARM处理器的种类很多,从手机上的高端处理器芯片到面向微控制器的芯片,都有ARM的身影。

第六章STM32 定时器的使用

6.4 定时器实训

定时器控制跑马灯(P190)

1.理解STM32通ห้องสมุดไป่ตู้定时器的结构和基本工作原理; 2.掌握STM32通用定时器初始化和操作方法; 3.理解中断概念; 4.掌握STM3中断服务程序的写法。

硬件设计 硬件连接图如下,实验板上stm32f103x处理器

通过配置GPIO实现如下功能:D3~D6轮流点亮,点亮时 间持续1秒。

TIM2定时器中断配置:

void TIM2_Config(void) //TIM2定时器配置 { TIM_TimeBaseInitTypeDef TIM_TimeBaseInitStructure;

RCC_APB1PeriphClockCmd(RCC_APB1Periph_TIM2,ENABLE); TIM_DeInit(TIM2); //重设TIM2寄存器默认值 TIM_TimeBaseInitStructure.TIM_Period = 1000-1;//自动重装载计数值; TIM_TimeBaseInitStructure.TIM_Prescaler = (72-1);//时钟分频系数 // TIM_TimeBaseInitStructure.TIM_ClockDivision = TIM_CKD_DIV1;//采样分频 TIM_TimeBaseInitStructure.TIM_CounterMode = TIM_CounterMode_Up;// TIM_TimeBaseInit(TIM2,&TIM_TimeBaseInitStructure);

预分频器寄存器在事件更新时采用

3)自动装载寄存器:TIMx_ARR

自动装载寄存器是预先装载的(要在使能定时器之前设定好) ,根据在TIMx_CR1寄存器中自动装载使能位(ARPE)的设 置,预装载寄存器的内容立即或者在每次更新事件时传送到

ARM9、Cortex M4M7 DMA与定时器

本章主要内容

6.1 ARM9 DMA原理 6.2 Cortex M4/M7 DMA原理 6.3 ARM9定时器 6.4 Cortex M4/M7定时器种类及功能

原理 思考与与习题

6.1.1 DMA请求源

如果由DCON寄存器选择了硬件DMA请求模式,则DMA控制器的每个通道 都可以在4个DMA源中选择DMA请求源的其中之一。(注意如果选择了软件请 求模式,此DMA请求源没有一点意义)表6-1显示了每个通道的DMA请求源。

每个DMA通道都有9个控制寄存器 ( 总 计 36 个 , DMA 控 制 器 有 4 个 通 道)。其中6个控制寄存器控制DMA 的传输,另外3个监视DMA控制器的 状态。这些寄存器的详情如下。

回本节目录

⑴ DMA初始源地址寄存器

DMA初始源地址寄存器DISRC0~3分别对应DMA的4 个通道,用于存放要传输的源数据起始地址,其描述 见表6-2、6-3所示。

DMA有两种不同的传输大小:单元(unit)和突发4 (Burst 4)。

DMA在大块数据传输期间将牢牢的掌握总线。因此 其它总线主机不能得到总线。

单元(unit)传输大小:一次读操作和一次写操作被 执行。

突发4传输大小:在突发4传输中分别可以执行4种连 续读取和写入。

回本节目录

6.1.5 DMA专用寄存器

6.1.3基本DMA时序

DMA服务意味着在DMA运行期间执行成对的读取和写入周期,形 成单次DMA操作。图6-1显示了S3C2440A的DMA操作的基本时序。

● XnXDREQ和XnXDACK的建立时间和延迟时间在所有模式中都 相同。

● 如果XnXDREQ的完成遇到其建立时间,它将同步两次并接着发 出XnXDACK。

嵌入式系统原理及应用第9章 ARM9定时器计数器程序设计

比特位

描述

初值

[15:0]

看门狗计数常数寄存器值(Count Reload Value)

0x8000

7

3. 看门狗计数寄存器(WTCNT)

看门狗计数寄存器WTCNT(Watchdog Timer Counter Register) 是一个实时动态变化的减法计数器,WTCNT工作时存储当前计数值。 WTCNT是可读写的,地址为0x53000008,复位后初值为0x8000。 看门狗计数寄存器的位功能描述如下表所示。

14

9.3.2 TIMER部件的操作

每个定时/计数器都是16位的减法计数器,是通过定时器自己的时钟驱 动的。当计数器减到0时,可产生定时器中断请求信号,通知CPU定时 器的操作已经完成了。此时定时/计数缓冲寄存器TCNTBn(Timer Counter Buffer Register n)的值将自动装载到递减计数器,开始下 一轮的操作。但是,若定时器停止工作,则TCNTBn的值将不会重新装 载到计数器中。

定时器比较缓冲寄存器TCMPBn(Timer Compare Buffer Register n)的值用于脉宽调制。当计数器的值与比较寄存器的值相同时,定时 器的逻辑将改变输出电平。因此TCMPBn确定脉宽调制信号输出的上升 时间(或下降时间)。

每个定时器(TIMER4除外)均含有TCNTBn,TCNTn,TCMPBn和 TCMPn四种计数缓冲寄存器,其中定时器计数寄存器TCNTn(Timer Counter Register n)和定时器比较寄存器TCMPn(Timer Compare Register n)是内部寄存器(编程不可见),内部寄存器 TCNTn的值可以通过计数观察寄存器读取。

15

PCLK

CORTEX-M4知识点总结

Cortex-M4内核知识点总结余明目录Cortex-M4内核知识点总结 (1)1 ARM处理器简介 (4)2 架构 (5)2.1架构简介 (5)2.2编程模型 (5)2.3存储器系统 (8)2.4复位和复位流程 (12)3 指令集 (14)3.1 CM4指令集特点 (14)3.2 Cortex-M处理器间的指令集比较 (14)3.3 汇编指令简要介绍 (14)3.3.1 处理器内传送数据 (14)3.3.2 存储器访问指令 (15)3.3.3 算数运算 (16)3.3.4 逻辑运算 (17)3.3.5 移位 (17)3.3.6 异常相关指令 (17)4 存储器系统 (18)4.1 存储器外设 (18)4.2 Bootloader (18)4.3位段操作 (19)4.4 存储器大小端 (19)5 异常和中断 (21)5.1 中断简介 (21)5.2异常类型 (21)5.3 中断管理 (22)5.4 异常或中断屏蔽寄存器 (23)5.4.1 PRIMASK (23)5.4.2 FAULMASK (M0中无) (23)5.4.3 BASEPRI(M0中无) (23)5.5 中断状态及中断行为 (23)5.5.1 中断状态 (23)5.5.2 中断行为 (24)5.6 各Cortex-M处理器NVIC差异 (26)6 异常处理 (28)6.1 C实现的异常处理 (28)6.2 栈帧 (28)6.3 EXC_RETURN (29)6.4异常流程 (30)6.4.1 异常进入和压栈 (30)6.4.2 异常返回和出栈 (31)7 低功耗和系统控制特性 (32)7.1 低功耗模式 (32)7.1 SysTick定时器 (32)8 OS支持特性 (34)8.1 OS支持特性简介 (34)8.2 SVC和PendSV (34)8.3 实际的上下文切换 (35)1 ARM处理器简介ARM处理器的种类很多,从手机上的高端处理器芯片到面向微控制器的芯片,都有ARM的身影。

嵌入式系统原理及应用基于arm-cortexm4体系结构

嵌入式系统原理及应用基于arm-cortexm4体系结构1. 引言1.1 概述嵌入式系统是指嵌入到其他设备中的计算机系统,它具有高度集成、可靠性强和功耗低等特点。

随着科技的不断发展和进步,嵌入式系统在各个领域得到了广泛的应用,包括但不限于消费电子产品、医疗设备、交通工具以及智能家居等。

本文将重点介绍基于ARM Cortex-M4体系结构的嵌入式系统原理及应用。

ARM Cortex-M4是一种32位RISC处理器架构,被广泛应用于微控制器(MCU)领域。

通过对ARM Cortex-M4架构的详细介绍,我们可以深入了解其特点和优势,并在后续章节中探讨如何实际开发嵌入式系统。

1.2 文章结构本文分为以下几个部分:第二部分将概述嵌入式系统的定义,并讨论其特点和应用领域。

我们将从整体上了解什么是嵌入式系统以及它们在现实生活中扮演的角色。

第三部分将详细介绍ARM Cortex-M4架构。

我们将对ARM体系结构进行概览,并重点讨论Cortex-M系列的特点和分类。

接着,我们将深入研究Cortex-M4架构以及其独特的特性。

第四部分将介绍嵌入式系统开发流程和工具链。

我们将概述嵌入式开发的一般流程,并讨论如何选择和配置合适的嵌入式开发工具链。

此外,我们还会提供一些关于开发板硬件选择和选型指南的实用信息。

第五部分将通过应用案例分析和实践,展示嵌入式系统在不同领域中的具体应用。

我们将着重介绍实时操作系统(RTOS)在嵌入式开发中的应用、传感器与嵌入式系统集成设计实例以及基于ARM Cortex-M4的音频处理应用案例。

最后,第六部分是本文的结论部分,我们将对全文进行总结并提出进一步研究和应用的展望。

1.3 目的本文旨在深入探讨基于ARM Cortex-M4体系结构的嵌入式系统原理及应用。

通过对该体系结构的详细介绍和相关案例分析,读者能够更好地了解嵌入式系统在各个领域中的实际运用方式,并且为他们在嵌入式系统开发中提供指导和帮助。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

Ch

-0

nXDRE

Q0

UART

0

SDI

Time

r

USB device

EP1

I2SSD

O

PCMIN

Ch

nXDRE

UART

I2SS

-1

Q1

1

DI

SPI0

USB device

PCMOU

EP2

T

SDI

Ch -2

I2SSD O

I2SS DI

SDI

Time r

USB device EP3

PCMIN

MICIN

Ch -3

INT

[29]

CURR_TC (终点计数)的中断使能/禁止设置 0:禁止CURR_TC中断。用户必须观察状态寄存器的传输计数(即定时查询) 1:当所有传输完成产生中断请求(即CURR_TC 变为0) 一个原子传输的传输大小选择(即释放总线前每次DMA 拥有总线执行传输) 0:执行一个单元传输 1:执行一个长度为4的突发传输 单服务模式和全服务模式之间的服务模式选择 0:选择每次原子传输(单次或突发4)后DMA 停止和等待其它DMA 请求的单服务模式。 1:选择传输计数达到0前重复请求得到原子传输的全服务模式。此模式不需要额外请求。 注意即使在全服务模式中,在每个原子传输后DMA 释放总线并且为了预防其它总线主机的渴望得到 总线而接着试图重新得到总线。

表6-9 DMA初始目标控制寄存器(DIDSTC)的位描述 DIDSTCn CHK_INT 位 [2] 描述 初始状态 当设置了自动再加载时发生中断的时间选择 0:在TC到达0时发生中断 0 1:在执行完自动再加载后发生中断 bit[1]是用于目标位置的选择 0:目标在系统总线(AHB)上 0 1:目标在外设总线(APB)上 位[0]是用于地址增加的选择 0:增加 1:固定 如果为0,地址将根据单次和突发模式中每次传输后其数据大小而增加。 0 如果为1,在传输后地址不改变。(突发模式中,地址只在突发传输期 间增加,但在传输后又回到其第一个值。)

表6-5 DMA初始源控制寄存器(DISRCC)的位描述

DISRCC n

位

描述 bit[1]是用于源位置的选择 0:源在系统总线(AHB)上 1:源在外设总线(APB)上 位[0]是用于地址增加的选择 0:增加 1:固定 如果为0,地址将根据单次和突发模式中每次传输后其数据大小而 增加。如果为1,在传输后地址不改变。(突发模式中,地址只在 突发传输期间增加,但在传输后又回到其第一个值)

表6-7 DMA初始目标地址寄存器(DIDST)的位描述

DIDSTn D_ADD R 位 [3 0: 0] 描述 要传输的目标数据基本地址 (开始地址)。当且仅当CURR_DST为 0 并且DMA ACK 为1时将此位的值锁存到CURR_DST中。 初始状态 0x00000000

⑷ DMA初始目标控制(DIDSTC)

INC

[0]

0

⑶ DMA 初始目标(DIDST)寄存器

DMA初始目标寄存器DIDST0~3分别对应DMA的4个通道的 初始目标地址,用于存放要传输的目标数据地址,其描述见表 6-6、6-7所示。

表6-6 DMA初始目标地址寄存器(DIDST)

寄存器 DIDST0 DIDST1 DIDST2 DIDST3 地址 0x4B000008 0x4B000048 0x4B000088 0x4B0000C8 读/ 写 读/ 写 描述 DMA0初始目标地址寄存器 DMA1初始目标地址寄存器 DMA2初始目标地址寄存器 DMA3初始目标地址寄存器 0x00000000 复位值

回本节目录

6.1.1 DMA请求源(续)

如果由DCON寄存器选择了硬件DMA请求模式,则DMA控制器的每个通道 都可以在4个DMA源中选择DMA请求源的其中之一。(注意如果选择了软件请 求模式,此DMA请求源没有一点意义)表6-1显示了每个通道的DMA请求源。

表6-1 每个通道DMA请求源

Source 0 Sour ce1 Sour ce2 Sour ce3 Source4 Source 5 Source 6

读/写

DMA2控制寄存器

0x00000000

DCON3

0x4B0000D0 DMA3控制寄存器

表6-10 DMA控制寄存器(DCON)

表6-11 DMA控制寄存器(DCON)的位描述

DCONn 位 描述 查询模式和握手模式之间选择其中之一 0:选择查询模式 1:选择握手模式 两种模式下DMA控制器开始其传输并为发出的DREQ而发出DACK。两种模式之间的差异为是否需要 等待取消 DACK 。握手模式中, DMA 控制器在开始新的传输前等待取消 DREQ 。如果其发现了取消 DREQ,其取消DACK并等待另一个DREQ的发出。与之对比,查询模式中DMA控制器不等待直到取 消DREQ。其只是取消DACK并且如果发出DACK接着开始另一个传输。我们建议外部DMA请求源使 用握手模式以预防新传输的非预定开始。

回本节目录

6.1.5 DMA专用寄存器

每个 DMA 通道都有 9 个控制寄存器 (总计 36 个, DMA 控制器有 4 个通 道)。其中6个控制寄存器控制DMA 的传输,另外3个监视DMA控制器的 状态。这些寄存器的详情如下。

回本节目录

⑴ DMA初始源地址寄存器 DMA初始源地址寄存器DISRC0~3分别对应DMA的4 个通道,用于存放要传输的源数据起始地址,其描述 见表6-2、6-3所示。

LOC

[1]

INC

[0]

⑸ DMA 控制(DCON)寄存器

DMA 控制(DCON)寄存器机器描述位如表6-10、6-11所示。

寄存器 DCON0 地址 0x4B000010 DMA0控制寄存器 DCON1 0x4B000050 DMA1控制寄存器 DCON2 0x4B000090 读/写 描述 复位值

回本章目录

6.1.1 DMA请求源

主要知识点: 1 DMA的概念 2 DMA请求源 3 请求源编号概念(6个源) 4 DMA通道的概念(4个通道,每个通道6个请求源) 5 初始源地址寄存器DISRCn、初始源控制寄存器DISRCCn 6 初始目标地址寄存器DIDSTn、初始目标控制寄存器 7 控制寄存器DCONn

6.1.3基本DMA时序

DMA 服务意味着在 DMA运行期间执行成对的读取和写入周期,形 成单次DMA操作。图6-1显示了S3C2440A的DMA操作的基本时序。 ● XnXDREQ和XnXDACK的建立时间和延迟时间在所有模式中都 相同。 ● 如果XnXDREQ的完成遇到其建立时间,它将同步两次并接着发 出XnXDACK。 ● 发出XnXDACK 后, DMA 请求总线并且其如果得到总线将执行 其的操作。 查询/握手模式:查询和握手模式是描述 XnXDREQ和XnXDACK之 间的协议。一次传输(单次 /突发传输)的最后, DMA 将检查双同步 XnXDREQ的状态。 查询模式:如果保持 XnXDREQ的发出,立即开始下次的传输。否 则其等待XnXDREQ 的发出。 握 手 模 式 : 如 果 发 出 XnXDREQ , DMA 在 2 个 周 期 内 取 消 XnXDACK。否则在取消XnXDREQ前一直等待。

6.1.2 DMA工作过程(续) 另外如果遇到以下状况之一则清除了DMA ACK。 ● 在全服务模式中CURR_TC变为0; ● 在单服务模式中完成原子操作。 注意在单服务模式中有三个主 FSM 的状态要执行并且接着要 停止和等待其它DMA REQ。如果DMA REQ 出现了要重复所有 的三个状态。所以发出DMA ACK并接着取消原子传输。与之对 比,在全服务模式中,主FSM在状态3中等待直到 CURR_TC变 为0。所以在所有传输期间发出 DMA ACK并接着在当TC到达0 时取消。 总之当且仅当在CURR_TC变为0时才发出INT REQ,与服务 模式(单顾服务模式或全顾服务模式)无关。

表6-2 DMA初始源地址寄存器(DISRC)

DISRCn 位 描述 初始状态

S_ADDR

[30: 0]

要传输的源数据基本地址(开始地址)。当且仅当 CURR_SRC 为0 并且DMA ACK 为1 时将此位的值锁 0x0000000 存到CURR_SRC 中。 0

表6-3 DMA初始源地址寄存器(DISRC)的位描述

第六章 ARM9、Cortex M4/M7 DMA与定时器

本章主要内容

6.1 ARM9 DMA原理

6.2 Cortex M4/M7 DMA原理 6.3 ARM9定时器 6.4 Cortex M4/M7定时器种类及功能 原理

思考与与习题

6.1 ARM9 DMA原理

6.1.1 DMA请求源 6.1.2 DMA工作过程 6.1.3 基本DMA时序 6.1.4 DMA传输大小 6.1.5 DMA专用寄存器

寄存器 DISRC0 DISRC1 DISRC2 DISRC3 地址 0x4B000000 0x4B000040 0x4B000080 0x4B0000C0 读/ 写 读/写 描述 DMA0初始源地址寄存器 DMA1初始源地址寄存器 DMA2初始源地址寄存器 DMA3初始源地址寄存器 复位值 0x0000000 0

DMA初始目标控制(DIDSTC)寄存器机器描述位如表6-8、6-9所示。

表6-8 DMA初始目标控制寄存器(DIDSTC)

寄存器 DIDST C0 DIDST C1 DIDST C2 DIDST C3 地址 0x4B0000 0C 0x4B0000 4C 0x4B0000 8C 0x4B0000 CC 读/写 描述 DMA0初始目标控制寄存器 DMA1初始目标控制寄存器 读/写 DMA2初始目标控制寄存器 DMA3初始目标控制寄存器 0x0000000 0 复位值

回本节目录

6.1.3基本DMA时序(续)

在取消XnXDACK(高电平)后就必须发出XnXDREQ (低电平)。