高效率同步降压型转换器的版图设计研究毕业论文

基于DPLL同步的高频降压型DC—DC转换器设计

Ab s t r a c t :Th i s p a p e r p r e s e n t s a d e s i g n o f d i g i t a l p h a s e — l o c k e d l o o p( DPLL) s y n c h r o n i z e d h i g h — f r e q u e nc y h y s t e r e t i c c o n t r o l DC— DC b u c k c o n v e r t e r . Di g i t a l p h a s e — l o c k e d l o o p o p e r a t i o n i s l o c k e d t o t h e r e f e r e n c e c l o c k f r e q u e n c y ,a n d d i g i t a l c o nt r o l d e l a y l i n e( DCDL)i s u s e d t o e l i mi n a t e t h e d u t y c y c l e ’ S ,a n d h e n c e t h e

最近 1 0年 , 嵌 入 式 技 术 促 进 便 携 式 电子 产 品 以

惊人 的 速 度 迅 猛 发 展 和 普 及 。 目前 , 高效 能、 高 精 度、 微体积的 D C — D C转 换 器 成 为 除 高 效 能 电池 以 外 制 约 小 型 轻 量 高 档 便 携 式 电子 产 品进 ~ 步 发 展 的瓶

o n DP L L s y n c h r o n i z a t i o n

Mu Ni a n q i a ng

( De p a r t me n t o f El e c t r i c a l En g i n e e r i n g ,S h a n d o n g Al u mi n u m Vo c a t i o n a l Co l l e g e ,Z i b o 2 5 5 0 6 5,Ch i n a )

如何设计高效率的降压转换器

如何设计高效率的降压转换器尽管器件的开关频率有时是固定的,还是有须要研究开关频率的问题,主要的权衡因素是效率。

简而言之,MOSFET有确定的导通和关断时光。

当频率增强时,过渡时光在总时光中所占的百分比会增强。

结果是:效率降低了。

假如效率是最重要的设计目标,就需要考虑降低开关频率。

假如系统效率足够高,就可以采纳更高的开关频率。

频率更高,就可以用法更小的外部无源器件,即输出电感和。

外部器件设计分立解决计划是相当有难度的,大约需要40个器件,这是个需要额外付出大量努力的复杂工作。

在设计电压模式降压控制器时,外部器件和其寄生效应对系统性能起了很大的打算作用。

在研究每种器件时,我们再详加讲述。

采纳这种特别降压转换器时,我们必需挑选5个额外器件,包括输入电容、输出电容、输出电感,高边和低边MOSFET。

挑选输出电感器时,要满足输出纹波的要求,以及减小PWM对瞬态负载的响应时光。

电感值的下限是由纹波要求确定的。

在寻觅最小(可能也是最廉价的)电感器之前,要记住的一点是,电感并不是完善的器件。

实际的电感器有饱和等级。

饱和级别必需高于系统中的峰值电流,才干设计出胜利的产品。

有阅历的设计者还明了,感值并不是不随电流变幻的常量。

实际上,流过器件的电流变大,感值会降低的。

请核实电感器的数据表,确保你所挑选的感值对系统中的峰值电流是足够的。

在更大层面上可能犯的错误是挑选最好的电感,虽然当心谨慎还是须要的。

更大的感值可以削减输出纹波,但也会限制压摆率。

终于,大电感会限制对负载瞬态的响应时光。

因此在挑选电感器时,是挑选在更低的峰峰值纹波电流条件下更宁静的输出,还是需要系统能够对瞬态大事做出迅速的响应,是需要做出明确的折衷。

输入电容负责汲取高边MOSFET输入电流的沟通重量。

因此,其RMS电流容量必需足够大,才干处理由高边MOSFET吸收的沟通重量。

因为质第1页共3页。

同步降压式DC-DC转换器的稳定性设计

不 同 的 电子 设 备 可 能 对 电源 系 统 有 不 同 的结 构 要

求 ,但 对 电源 系 统 转 换 效 率 的 要 求 却 基 本 相 同 。

D — C C D 转换 器 主要 用 来 实 现 电源 系 统 中 的二 次 电 压 变 换 或 是 手 持 式 设 备 等 用 电池 供 电设 备 的一 次 电压 变 换 ,其 可分 为 隔 离 与 非 隔 离 型 、升压 与 降 压 型 、 同步 与 异 步 型 等 等 。随着 半导 体 片 向低

Ke ywor s DC— d: DC ; i e r rg ao ; c tk o e; y h o usbu k; mp s to t r L n a e ultr S hot y did S nc r no c Co en a in newo k

现 代 电子 设 备 巾 郜 包 含有 电源 系 统 ,且 电 源 来自1 r A CC V

J. k 6 Q 44

O

1 j kI

极 管 两 端 存 在 压 降 ,相 当一 部 分 的 电 源 能量 被 其 一

HA0 e — i n W i— a g q

(e igsm cn u t ’ eief t yf e e ig 10 1 , hn) B in e io d co d vc a o v ,B in 0 0 5 C ia j ' t cri j

A bsr t t ac :Du u te h g fii n . e I h i h e ’ e t DC—DC c nv re swi e y u e n m o e n ee tonc d vc s tc o et ri d l s d i d r lc r i e ie .Ast e tc noo y h e h lg

一种高效率升降压DC-DC变换器的研究

a n d i t i s d i v i d e d i n t o 3 k i n d s o f s t e p — d o wn , b u c k — b o o s t a n d s t e p — u p mo d e . I n t h e p r o c e s s o f c o n t r o l , t h e mo d e s c a n r e a l i z e n o i n t e r v a l b e t we e n s wi t c h e s , e ic f i e n c y o f t h e p r o p o s e d t o p o l o g y i s v e r i ie f d b y a n

第3 6 卷第 6 期 2 0 1 6年 l 2月

辽宁工业大学学报 ( 自然科学版)

J o u r n a l o f L i a o n i n g U n i v e r s i t y o f T e c h n o l o g y ( Na t u r a l S c i e n c e E d i t i o n )

、 , o 】 . 3 6 . No . 6 De c . 2 01 6

种 高效率升 降压 D C - D C 变换器 D O I : 1 0 . 1 5 9 1 6 的研  ̄ . i s s n 1 6 7 4 究 — 3 2 6 1 . 2 0 1 6 . 0 6 . 0 5

一

陈 弯,陈永真 ,赵 子龙

( 辽 宁 工业 大 学 电子 与信 息 1 : 程 学 院,辽 宁 锦 州 1 2 1 0 0 1 )

摘

要:在降压 变换器、升压 变换器和具有升降压功 能变换器的基础上 ,研 究了一种 简单 、高效、宽输 入输

如何设计面向大降压比应用的同步降压转换器

如何设计面向大降压比应用的同步降压转换器引言DC-DC 降压转换器已在工业领域得到了广泛应用,其中最常用到的拓扑便是降压转换器。

半导体技术的发展使得现今的电子设备能在越来越低的3.3V、2.5V、1.8V 甚至低至1V 电压下工作。

传统采用一个二极管的降压转换器的转换效率很低,尤其是在较低的输出电压下,原因是由于二极管通常会消耗不少的功率,其典型正向电压降为0.35V~0.5V,从而造成了较大比例的功率损耗。

同步降压转换器采用MOSFET 来代替二极管,该解决方案具有高效率、高输出电流和低输出电压等优势。

MOSFET 中的电压降与其接通电阻和电流成比例,其典型值为0.1V~0.3V。

因此,功率损耗便可大大下降,从而达到很高的转换效率。

另一方面,许多应用要求的输入电压范围很大。

例如汽车应用中要求的输入电压范围比较大,而汽车电池的电压一般为12V 或24V,在尖峰情况下可能会达到40V。

由于输入电压很高而输出电压很低(或者是输出电流很高),因此需要使用大降压比的转换器。

具有大降压比和低输出电压特性的功率转换器一般采用两级转换。

第一级转换是将高输入电压转换为中间电压,第二级转换则将中间电压转换为需要的低输出电压。

采用两级转换的原因很多。

首先,大降压比则意味着需要低占空比。

例如,一个24V 输入及1.2V 输出的转换器,其要求的占空比为0.05,这对效率和性能而言都非常不利。

甚至对于一般的降压转换器而言,这个很低的占空比是无法达到。

第二,支持输出电压低于1.2V 的设备一般其输入电压不会大于10V 到15V。

但是,根据之前所述,在汽车等一些设备中,甚至会出现高达40V 的高输入电压。

可是,对于能接受20V 以上输入电压的设备,其输出电压往往都高于1.2V。

因此,对于高输入低输出的电压应用来说,采用两级转换是非常合理。

两级转换的不良效率效率是两级转换器所需要关注的一个主要问题。

尽管对个别级的转换而。

一种高效率同步降压型DC—DC转换器集成电路的设计

一种高效率同步降压型DC—DC转换器集成电路的设计设计了一种高效率同步降压型DC-DC转换器集成电路。

采用了同步整流技术和突发模式控制技术,使得转换效率高达92%。

采用根据不同占空比调节斜率补偿技术—四段式斜率补偿,提高电路性能的同时可以有效地提高了系统的稳定性。

集成了完善的保护电路,包括过压保护、过温保护和短路保护等,使得系统更安全、更稳定。

标签:降压型DC-DC;四段式斜率补偿技术;突发模式;同步整流引言随着科学技术的发展,电子系统的应用领域越来越广泛,电子设备与人们的工作、生活的关系日益密切。

任何电子设备都离不开可靠的电源,并且对电源的要求也越来越高。

同时,电源技术又与现代控制理论、材料科学、电机工程、微电子技术等许多领域密切相关。

目前电源技术已逐步发展成为一门多学科互相渗透的综合性技术学科。

它为现代通讯、电子仪器、计算机、工业自动化、电力工程、国防及某些高新技术提供高质量、高效率、高可靠性的电源。

本文开发的集成电路,采用了同步整流技术和突发模式控制技术,在轻负载条件下也具有很高的转换效率。

采用根据不同占空比调节斜坡补偿技术,消除亚谐波振荡。

1电路原理1.1电路内部原理结构图图1为内部原理结构图,包括使能电路、带隙基准电路、振荡器、误差放大器、脉宽调制比较器电路、突发模式电路、斜率补偿电路和保护电路等。

1.2使能电路输入部分由上拉PMOS管和迟滞整形电路组成。

由于上拉PMOS管处在饱和状态,并且W/L很小,所以上拉管电阻很大。

输入部分这样设计是为了防止电源电压的抖动对芯片的影响。

只要EN管脚达到NMOS的阈值电压,NMOS 就会导通。

1.3基准电路带隙基准的工作原理是根据硅材料的带隙电压与电压和温度无关的特性,利用VT的正温度系数与双极型晶体管基极-发射极间的电压VBE的负温度系数相互抵消,来产生低温漂、高精度的基准电压源。

电路由运放、ΔVBE产生电路、修调和分压电路组成。

根据带隙基准原理可以得到该电路的ΔVBE其中R4、R5、R6、R7、R8和R9是修调电阻,就是为了修调出零温度系数的带隙基准电压值。

MAX17502同步降压DCDC转换器

MAX17502同步降压DC/DC转换器MAX17502 ,MAX17502高效率,高电压,同步降压型的DC-DC转换器工作在4.5V 至60V的输入电压范围和设计应用范围广。

超宽输入操作,使得它不仅为工业控制和楼宇自动化的理想,但也基站,家庭娱乐,电信和汽车应用。

它提供高达1A的输出电流超过3.3V 和5V的输出电压的温度。

输出电压范围内随温度的±1.6%准确。

器件工作在-40°C至+125°C 的工业温度范围内,在一个微小的,10针(3毫米×2毫米)的TDFN无铅(Pb)免费包带有裸焊盘。

该器件具有峰值脉冲宽度调制(PWM)电流模式控制。

PWM操作,确保在所有操作条件下的恒定开关频率。

低电阻,片上,PMOS / NMOS开关,确保在满负荷高效率,同时最大限度地减少关键的电感,使布局更简单的任务,与分立式解决方案相比,该器件提供固定开关频率为600kHz。

为了降低输入浪涌电流,该器件提供SS引脚与一个外部电容器地面可调电压软启动功能。

该器件还集成了一个输出使能/欠压锁定引脚(EN / UVLO)功能,允许用户打开部分所需的输入电压水平。

漏极开路,低电平有效的RESET引脚提供了一个延迟的电源良好信号系统实现成功调节输出电压时。

该设备支持低功耗的打嗝模式限流,过载,输出短路条件下的保护。

关键特性消除外部元件,并降低总成本没有高效率和降低成本的肖特基同步操作超紧凑布局的内部补偿全陶瓷电容器DC-DC稳压器的数量减少股票4.5V至60V的宽工作电压范围固定3.3V和5V输出在整个温度范围内提供高达1A600kHz的开关频率降低功耗最高效率> 90%关断电流1μA(典型值)运行可靠,在恶劣的工业环境打嗝模式电流限制与自动重启动内置监测输出电压(漏极开路,低电平有效RESET引脚)电阻可编程UVLO阈值具有可调软启动和预偏置电源,最多增加安全可选的可调输出和PFM(可根据工厂要求)-40°C至+125°C工业温度范围(本文转自电子工程世界:/dygl/2012/1218/article_15254.html)。

同步降压式 DC-DC 转换器能够最大限度地提高降压 转换效率的原因及其使用

同步降压式DC/DC转换器能够最大限度地提高降压转换效率的原因及其使用在包括汽车、工业自动化、电信、计算机、白色家电和消费电子在内的各种系统中,将高母线电压降至较低电压,从而为IC和其他负载供电的需求越来越大。

设计者面临的挑战是,如何以最高的效率、最小的热负荷、低成本以及尽可能小的解决方案尺寸来实现这种降压转换。

传统的异步降压转换器提供了一种潜在的低成本解决方案,但其转换效率较低,不能满足许多电子系统的需求。

设计者可以利用同步DC/DC转换器和同步DC/DC控制器来开发紧凑型高效率解决方案。

本文简要介绍了电子系统对高效DC/DC转换的性能要求,并回顾了异步和同步DC/DC转换器的区别。

然后,介绍来自Diodes,Inc、STMicroelectronics和ON Semiconductor的几种同步DC/DC 转换器设计方案,以及评估板和设计指南。

这些方案有助于快速启动高效率解决方案的开发。

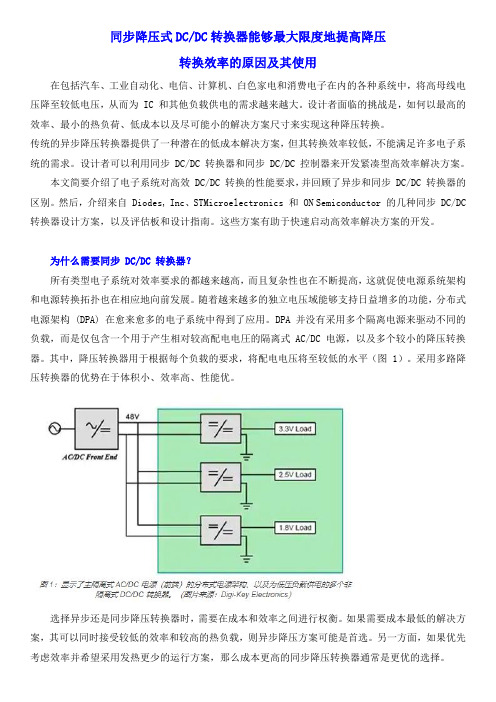

为什么需要同步DC/DC转换器?所有类型电子系统对效率要求的都越来越高,而且复杂性也在不断提高,这就促使电源系统架构和电源转换拓扑也在相应地向前发展。

随着越来越多的独立电压域能够支持日益增多的功能,分布式电源架构(DPA)在愈来愈多的电子系统中得到了应用。

DPA并没有采用多个隔离电源来驱动不同的负载,而是仅包含一个用于产生相对较高配电电圧的隔离式AC/DC电源,以及多个较小的降压转换器。

其中,降压转换器用于根据每个负载的要求,将配电电压将至较低的水平(图1)。

采用多路降压转换器的优势在于体积小、效率高、性能优。

选择异步还是同步降压转换器时,需要在成本和效率之间进行权衡。

如果需要成本最低的解决方案,其可以同时接受较低的效率和较高的热负载,则异步降压方案可能是首选。

另一方面,如果优先考虑效率并希望采用发热更少的运行方案,那么成本更高的同步降压转换器通常是更优的选择。

同步与异步降压转换器的比较典型的异步降压转换器应用如图2所示。

降压型PWMDCDC转换器芯片的系统分析与设计

摘要本论文从DC-DC转换器的buck拓扑结构出发,分析了DC-DC转换器的基本工作原理。

根据便携式设备对体积、成本和功耗的严格要求,设计了芯片的系统结构,并且进行了电路设计、仿真和版图设计。

本课题的主要特点有:PWM调制方式使得电源芯片的噪声抑制和电磁兼容性能大大提高;电流模式保证了芯片拥有较好的负载、电源调整性能和较快的瞬态响应,整个电路变成了一阶系统,使得补偿网络易于实现,系统稳定性得以提高,减小了输出电压的波动;采用JAZZ的BCD05工艺大大降低了功率开关管的导通电阻,提高了系统的转换效率;较高的开关频率使外部电容、电感等常规大体积的元件可以选用小容量的表面贴装器件,极大的减小了电源系统的体积。

设计了一个内部电源调整模块,大大提高了输入电源的电压范围。

本文还在系统补偿网络的选取上采用了一种新颖的方法。

使用简单的计算公式得出补偿网络中元件的具体参数,以保证在不同的输出滤波电容和负载情况下,电源系统保持稳定。

本文对关键电路进行了Spectre模拟验证,根据工作模式选择合适的外部元件对系统进行模拟,并给出模拟结果和结果分析。

模拟结果证明该转换器满足了不同负载下高效率的设计要求。

在输入4.73V-15V,输出1.235V-13V的范围内,均可以达到2A的输出电流,并且保持系统稳定。

开关频率为400KHZ,最大占空比为90%以上。

在运用范围内的最高效率超过95%。

关键词:开关电源DC-DC转换器电流模式脉冲宽度调制降压型AbstractThis thesis discusses the fundamental of a buck DC-DC converter. According to the strict request for the bulk, cost and power, the architecture of the system is designed.The following is the main characteristics of the converter: PWM control mode improves the noise and EMI performance of power supply ic;Advanced Current Mode circuit are specially used to ensure better supply & load line regulation and better transient response,more easyer compensation net and better stability ,and less fluctuate of output voltage;using the BCD05 technology of JAZZ company make the resistance of switch MOSFET less than the traditional one,improves efficiency of the power supply;With high frequency of switch,SMT (Surface mounting technology) capacitor & inductor can be applied to minimize the bulk of the power supply system.This thesis has given a new method of selecting compensation network. Use simple formula for calculating compensation reached the network element specific parameters. To ensure that the different output filter capacitor and load cases, the power system remains stable.Simulate all critical functional blocks and give results with Spectre. Select different components, simulate the system and give the results about system characters. The result showed the efficiency at the variable loads. In the voltage range of input 4.75V-15V and output 1.235V-13V, the converter can be reached 2A of output current, and maintain system stability. Switching frequency is 400KHZ, maximum duty cycle is 90%.The maximum efficiency is over 95%.Keywords: switching supply DC-DC converter current-mode PWM control buck目录摘要 (I)Abstract (II)1 绪论1.1 DC-DC转换器的发展 (1)1.2 DC-DC转换器的设计要求 (3)1.3 研究生阶段所做工作 (5)1.4 课题特色与创新点 (5)1.5课题特点及结构安排 (6)2 开关电源基础2.1 降压型开关电源的基本原理 (8)2.2 DC-DC转换器的调制方式 (11)3 降压型PWM电流模式开关电源系统分析3.1 开环稳定性分析 (16)3.2电流环稳定性分析 (19)3.3buck结构的效率分析 (20)3.4大信号特性分析 (23)4 DC-DC转换器控制电路的设计4.1内部电源调整模块的设计 (28)4.2带隙基准电路的设计(包含热关断) (34)4.3误差放大器的设计 (37)4.4峰值电流检测与放大电路的设计 (40)4.5时钟与斜坡信号发生电路的设计 (44)4.6欠压保护电路的设计 (48)4.7锁定比较器的设计 (50)4.8功率管驱动电路的设计 (52)5 整体电路的设计与仿真5.1 外围元件的选取 (55)5.2 系统仿真波形 (58)6 芯片版图的设计6.1 版图设计方法和技术 (62)6.2 芯片版图结构 (64)7 结论 (66)致谢 (68)参考文献 (69)附录攻读硕士学位期间发表的论文目录 (73)1 绪论电源是电子设备的动力心脏[1],其性能的优劣直接影响到整个系统的安全性和可靠性。

高效率同步降压型转换器的版图设计研究初版

摘要随着集成电路已经进入深亚微米时代,版图设计早已成为集成电路产业链中重要的一环。

它不仅是芯片是否能被生成的保证,同时也关系到实际产品的性能是否能满足预期的目标。

因此,同步降压型转换器的版图设计研究具有非常重要的意义。

该芯片是一个高频率,同步整流,降压型开关模式转换器。

具有内置的功率MOS,实现了连续输出2A电流,具有优异的负载和电路调控能力。

在很宽的输入电压范围,该芯片具有同步操作模式,在保证输出电流效率更高的范围内,电流模式能提供快速的瞬态响应和简化环路稳定性。

该芯片具有完整的保护功能,如过电流保护和热关机。

该芯片采用的是节省空间的SOT23-8引脚封装。

关键词:高效率,同步整流,电流模式ABSTRACTWith the integrated circuit has entered the deep sub-micron times,the layout design had became an important part of the integrated circuit industry is not only the chip can be generated,but also related to whether the actual product performance can achieve the expected ,it is very important to research layout design of the synchronous and step-down converter.This chip is a high-frequency, synchronous,rectified, step-down, switch-mode converter with built-in power MOSFETs. It offers a very compact solution to achieve a 2A continuous output current with excellent load and line regulation over a wide input supply range. The MP1494 has synchronous mode operation for higher efficiency over the output current load range. Current-mode operation provides fast transient response and eases loop protection features include over-current protection and thermal shut MP1494 requires a minimal number of readily-available standard external components,and is available in a space-saving 8-pin package.Key words:high-frequency, synchronous rectifier,current mode目录第1章.课题整体框架.............................................. 课题任务............................................................. 课题要求............................................................. 研究意义............................................................. 第2章.设计方案.................................................. 软件部分............................................................ 软件工具............................................................ cadence操作说明.................................................... 集成电路版图可靠性需要避免的三大效应................................ PAE................................................................. Latch_up............................................................ ESD效应............................................................ 子模块版图.......................................................... LDO模块............................................................ UVLO模块........................................................... freq_comp模块...................................................... control_logic模块.................................................. current_sense模块.................................................. EN模块............................................................. HS_control模块..................................................... OCP模块............................................................ EA_compensation模块................................................ 模块................................................................. 模块................................................................. 模块................................................................. 模块................................................................. 模块................................................................. 模块................................................................. 顶层版图............................................................ 顶层版图布局........................................................ 顶层版图............................................................ 第3章.实现功能.................................................. 实现功能描述........................................................ 部分模块功能介绍.................................................... 第4章.调试与实现................................................ 调试中遇到的重点与难点.............................................. 不接Power的Nwell.................................................. 高压器件的第五端.................................................... 解决方案............................................................ 不接Power的Nwell的解决方案........................................ 高压器件的第五端的连接方式..........................................实现展示............................................................ 高压器件的第五端连接正确之后的验证.................................. 第5章.总结...................................................... 参考文献............................................................. 致谢................................................................. 附录................................................................. 附录一:IC版图设计中电阻的匹配基础篇................................第1章.课题整体框架课题任务随着电子产品轻、薄化的发展趋势,要求电子元器件体积更小,功耗更低。

buck变换器毕业论文

buck变换器毕业论⽂buck变换器毕业论⽂专业:电⽓⼯程与⾃动化⾼频同步整流BUCK变换器的设计与仿真摘要便携式电⼦产品的⼴泛应⽤,推动了开关电源技术的迅速发展。

因为开关电源具有体积⼩、重量轻以及功率密度和输出效率⾼等诸多优点,⼰经逐渐取代了传统的线性电源,随之成为电源芯⽚中的主流产品。

随着开关电源技术应⽤领域的扩⼤,对开关电源的要求也⽇益提⾼,⾼效率、⾼可靠性以及⾼功率密度成为趋势,这就对开关电源芯⽚设计提出了新的挑战。

本⽂⾸先概述了现有开关电源设计技术及其发展趋势,接着介绍了BUCK变换器的电路结构、⼯作原理及控制原理。

最后进⾏了芯⽚系统的仿真研究,其中⾸先介绍了所选芯⽚的性能特点及其经典电路图,然后利⽤LTSPICE进⾏了仿真验证。

关键词:开关电源,BUCK变换器,同步整流,LTSPICE仿真The Design and Simulation of the High-Frequency Synchronous BUCK ConvertersAbstractThe widely use in portable electronic products promoted the rapid development of switching power supply technology. The switching power converters are increasingly replacing traditional linear power supply due to its small space, light weight, low power dissipation, high efficiency, adoption and broad applicability, etc. As the application field expanded, switching power converters have to become more efficient and more reliable with high power density to meet such a stringent requirement. The article introduces the status of switching power converters and its development trend, then shows the circuit of BUCK converters, and then analyzes its working principle and control theory. Finally, the simulation of the BUCK chip was carried out. This section firstly introduces the performance characteristics of the selected chip and its classic circuit, then shows the results of the simulation.Key Words:Switching power supply; BUCK converter; Synchronous rectification; Simulation based on LTSPICE⽬录摘要 (ⅰ)Abstract (ⅱ)第⼀章引⾔ (1)1.1 课题的背景和研究意义 (1)1.2 开关电源技术研究现状 (2)1.2.1 半导体功率器件 (2)1.2.2 软开关技术 (2)1.2.3 同步整流技术 (3)1.2.4 电压调节模块 (3)1.3 开关电源技术发展趋势 (4)1.3.1 ⾼效率 (4)1.3.2 低压⼤电流 (4)1.3.3 智能化设计 (5)1.3.4 标准化⼯作 (5)1.4 论⽂结构和主要内容 (5)第⼆章同步整流BUCK变换器原理 (7)2.1 BUKC变换器主电路结构和⼯作原理 (7)2.2 BUKC变换器稳态分析 (8)2.2.1 连续导通模式(CCM) (8)2.2.2 不连续导通模式(DCM) (11)2.2.3 CCM和DCM的临界条件 (14)2.3 BUKC变换器控制原理 (15)2.3.1 脉冲宽度调节(PWM) (16)2.3.2 脉冲频率调节(PFM) (18)第三章降压型开关电源芯⽚的仿真研究 (20)3.1 LTC3854特点及典型应⽤电路 (20)3.2 仿真及结果分析 (21)第四章结语 (24)参考⽂献 (25)致谢 (26)第⼀章引⾔1.1 课题的背景和研究意义随着电⼦技术的快速发展,电⼦设备的种类越来越多,电⼦设备与⼈们的⼯作、⽣活的关系也⽇益密切。

同步降压转换器的设计方案

同步降压转换器的设计方案

设计降压转换器并不是件轻松的工作。

许多使用者都希望转换器是一

个盒子,一端输入一个直流电压,另一端输出另一个直流电压。

这个盒子可以

有很多形式,可以是降阶来产生一个更低的电压,或是升压来产生一个更高的

电压。

还有很多特殊的选项,如升降压、反激和单端初级电感转换器(SEPIC),这是一种能让输出电压大于、小于或等于输入电压的DC-DC 转换器。

如果一

个系统采用交流电工作,第一个AC-DC 模块应当产生系统所需的最高的直流

电压。

因此,使用最广的器件是降压转换器。

使用开关稳压器的降压转换器具有所有转换器当中最高的效率。

高效率

意味着转换过程中的能量损耗更少,而且能简化热管理。

选择IC

上面提到的控制环路使降压转换器能够保持一个稳定的输出电压。

这种

环路有几种实现方法。

最简单的转换器使用的是电压反馈或电流反馈。

这些转

换器很耐用,控制方式很直接,而且性价比很好。

由于降压转换器开始用于各

种应用中,这种转换器的一些弱点也开始暴露出来。

以一种改进方法是所谓的

磁滞控制,Intersil 的ISL62871 就是采用这种控制方法的器件。

转换效率与负

载的曲线如

图2,Intersil ISL62871 的负载与效率曲线,Vout=1.1Vtips:感谢大家的阅读,本文由我司收集整编。

仅供参阅!。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

(此文档为word格式,下载后您可任意编辑修改!)摘要随着集成电路已经进入深亚微米时代,版图设计早已成为集成电路产业链中重要的一环。

它不仅是芯片是否能被生成的保证,同时也关系到实际产品的性能是否能满足预期的目标。

因此,同步降压型转换器的版图设计研究具有非常重要的意义。

该芯片是一个高频率,同步整流,降压型开关模式转换器。

具有内置的功率MOS,实现了连续输出2A电流,具有优异的负载和电路调控能力。

在很宽的输入电压范围,该芯片具有同步操作模式,在保证输出电流效率更高的范围内,电流模式能提供快速的瞬态响应和简化环路稳定性。

该芯片具有完整的保护功能,如过电流保护和热关机。

该芯片采用的是节省空间的SOT23-8引脚封装。

关键词:高效率,同步整流,电流模式ABSTRACTWith the integrated circuit times,the layout design important part of the integrated circuit industry chain.It is not only the chip can be generated,but also related to whether the actual product performance can achieve the expected target.Thereforce,it is very important to research layout design of the synchronous and step-down converter.This chip is a , switch-mode converter with built-in power MOSFETs. It offers a very compact solution to achieve a 2A continuous output current with excellent load and line regulation over a wide input supply range. The MP1494 for provides fast transient response and eases loop stabilization.Full protection features include over-current protection and thermal shut down.The MP1494 requires a minimal number of readily-available standard external components,and is available in a space-saving 8-pin package.Key words:Environment)、版图编辑(Virtuoso Layout Editor)等等。

版图编辑(Virtuoso Layout Editor)是版图编辑者最常用的设计工具,下面通过2.1.2 模块流程图来介绍一下版图编辑(Virtuoso Layout Editor)的使用。

2.1.2 cadence操作说明常用的cadence配套文件包含以下三个,如图2-1所示。

cadence为启动cadence ic51的脚本文件(该脚本文件内含启动cadence ic51的快捷方式icfb&,其中&表示cadence ic51以后台运行的方式打开),cds.lib为库管理文件(library manager),.cdsinit为cadence启动文件(可以用来自定义额外加载的东西)。

图2-1 cadence配套文件运行cadence启动脚本文件,cadence ic51启动过程如图2-2所示。

图2-2 cadence ic51启动过程软件启动完成之后,生成如图2-3所示的CDS.log窗口。

位于窗口下方,mouse字样上方的是CIW窗口(Command Interpreter Window),即为命令解释窗,此外cadence软件内嵌的控制窗口,通过此处可以在cadence软件启动之后加载脚本文件等。

图2-3 CDS.log窗口启动cadence软件之后,通过如图2-4所示的操作步骤建立一个新的库,在这个库下完成版图的编辑。

图2-4 建库按图示2-4操作后,会出现NEW Library建立窗口,在左侧Name处填写新建立的Library的名字,在右侧Technology File下方可以选择新建立的库是否需要绑定一个已存在的技术库(an existing techfile)或者绑定一个由Foundry 提供的最为基本的技术文件(a new techfile),甚至也可以只建立一个空库,不需要任何技术支持(Don`t need a techfile)。

一般情况下,如果Foundry提供了完整的PDK,我们则在建库的时候可以选择绑定一个已存在的技术库(an existing techfile),操作如图2-5所示。

图2-5 新建库的设置点击ok后,弹出如图2-6所示窗口,选择本次项目所需技术库“UTC06_BCD_5V_18V_30V_40V”。

再次点击ok之后,一个绑定了技术库的Library就建立好了。

图2-6 选择需要绑定的技术库我们可以在Library Manager窗口通过查看库的基本属性,如建立时间,存在目录的具体位置等等。

我们可以通过这里验证库是否建立正确,在Library Manager中选中库,右击选择Property即可弹出如图2-7所示的属性窗口。

图2-7 库的属性在新建立的库中新建一个view为Virtuoso的Cellview,在此Cellview绘制版图,操作如图2-8所示。

图2-8 新建Cellview2.2 集成电路版图可靠性需要避免的三大效应2.2.1 PAE2.2.1.1 PAE简介芯片中金属线或者多晶硅(polysilicon)等导体,就像是一根根天线,当有游离的电荷时,这些“天线”便会将它们收集起来,天线越长,收集的电荷也就越多,当电荷足够多时,就会产生放电对芯片内部产生破坏,这就是天线效应(PAE)。

IC现代工艺中经常使用的一种方法是离子刻蚀(plasma etching),这种方法就是将物质高度电离并保持一定的能量,然后将这种物质刻蚀在晶圆上,从而形成某一层。

理论上,打入晶圆的离子总的对外电性应该是呈现中性的,也就是说正离子和负离子是成对出现,但在实际中,打入晶圆的离子并不成对,这样,就产生了游离电荷。

另外,离子注入(ion implanting)也可能导致电荷的聚集。

可见,这种由工艺带来的影响我们是无法彻底消除的,但是,这种影响却是可以尽量减小的。

在CMOS工艺中,P型衬底是要接地的,如果这些收集了电荷的导体和衬底间有电气通路的话,那么这些电荷就会跑到衬底上去,将不会造成什么影响;如果这条通路不存在,这些电荷还是要放掉的,那么,在哪放电就会对哪里造成不可挽回的后果,一般来讲,最容易遭到伤害的地方就是栅氧化层。

通常情况下,我们用“天线比率”(“antenna ratio”)来衡量一颗芯片能发生天线效应的几率。

“天线比率”的定义是:构成所谓“天线”的导体(一般是金属)的面积与所相连的栅氧化层面积的比率。

随着工艺技术的发展,栅的尺寸越来越小,金属的层数越来越多,发生天线效应的可能性就越大,所以,在0.4umDMSPTMSP以上工艺,我们一般不大会考虑天线效应。

而采用0.4um以下的工艺就不得不考虑这个问题了。

可通过插入二极管(NAC Diode)的方法来解决天线效应,这样当金属收集到电荷以后就通过二极管来放电,避免了对栅极的击穿。

注:DMSP——Double Metal Single PolyTMSP——Three Metal Single Poly2.2.1.2防止PAE的方法1)跳线法。

又分为“向上跳线”和“向下跳线”两种方式。

跳线即断开存在天线效应的金属层,通过通孔连接到其它层(向上跳线法接到天线层的上一层,向下跳线法接到下一层),最后再回到当前层。

这种方法通过改变金属布线的层次来解决天线效应,但是同时增加了通孔,由于通孔的电阻很大,会直接影响到芯片的时序和串扰问题,所以在使用此方法时要严格控制布线层次变化和通孔的数量,一般情况下在跳线处孔越多越好。

在版图设计中,向上跳线法用的较多,此法的原理是:考虑当前金属层对栅极的天线效应时,上一层金属还不存在,通过跳线,减小存在天线效应的导体面积来消除天线效应。

现代的多层金属布线工艺,在低层金属里出现PAE 效应,一般都可采用向上跳线的方法消除。

但当最高层出现天线效应时,采用什么方法呢?这就是下面要介绍的另一种消除天线效应的方法了。

2)添加天线器件,给“天线”加上反偏二极管。

通过给直接连接到栅的存在天线效应的金属层接上反偏二极管,形成一个电荷泄放回路,累积电荷就对栅氧构不成威胁,从而消除了天线效应。

当金属层位置有足够空间时,可直接加上二极管,若遇到布线阻碍或金属层位于禁止区域时,就需要通过通孔将金属线延伸到附近有足够空间的地方,插入二极管。

3)给所有器件的输入端口都加上保护二极管。

此法能保证完全消除天线效应,但是会在没有天线效应的金属布线上浪费很多不必要的资源,且使芯片的面积增大数倍,这是VLSI 设计不允许出现的。

所以这种方法是不合理,也是不可取的。

4)对于上述方法都不能消除的长走线上的PAE,可通过插入缓冲器,切断长线来消除天线效应。

在实际设计中,需要考虑到性能和面积及其它因素的折衷要求,常常将法1、法2 和法4 结合使用来消除天线效应。

2.2.2 Latch_up2.2.2.1 Latch_up简介Latch-up原理分析:CMOS电路中在电源VDD和地线GND之间由于寄生的PNP和NPN相互影响可能会产生的一些低阻抗通路,使VDD和GND之间产生大电流,这就称为闩锁效应(latch_up)。

闩锁效应剖面图与等效电路图如图2-9所示。

随着IC制造工艺的发展,集成度越来越高,产生latch_up的可能性会越来越高。

图2-9 闩锁效应剖面图与等效电路图如图2-10所示,当无外界干扰未引起触发时,两个BJT处于截止状态,集电极电流是C-B反向漏电流构成,电流增益非常小,此时latch up不会产生。

图2-10 不会发生闩锁效应的分析电路图如图2-11所示,当一个BJT集电极电流受外部干扰突然增加到一定值时,会反馈至另外一个BJT,从而使两个BJT因触发而导通,如果整个环路增益大于1,则VDD至GND间形成低阻通路,Latch up由此产生。