DSS6-015AS;中文规格书,Datasheet资料

PVG612AS-TPBF;PVG612A;PVG612AS-T;PVG612ASPBF;中文规格书,Datasheet资料

The PVG612A Series Photovoltaic Relay is a sin glepole, normally open solid-state re lay that can replace electromechani cal re lays in many applications. It util izes International Rectifier’s proprietary HEXFET power MOSFET as the output switch, driven by an inte grated circuit photovoltaic gen erator of novel construction. The output switch is con trolled by radiation from a GaAlAs light emit ting diode (LED) which is optically isolated from the photovol taic generator. These units exceed the performance capabilities of electromechanical relays in operating life, sensitivity, stability of on-resistance, miniaturization, insensitivity to magnetic fields and ruggedess. The compact PVG612A is particularly suited for isolated switching of high currents from 12 to 48 Volt AC or DC power sources. Series PVG612A Relays are packaged in a 6-pin, molded DIP package with either thru-hole or surface mount (gull-wing) termi nals. It is avail able in standard plastic ship ping tubes or on tape-and-reel. Please refer to Part Identifica tion in formation opposite.

PPA0155中文资料

532PDA Pigtailed Photodiode SpecificationsAbsolute Maximum RatingsAbsolute maximum limits mean that no catastrophic damage will occur if the product is subjected to these ratings for short periods, provided that each limiting parameter is in isolation and all other parameters have values within the performance specification. It should not be assumed that limiting values of more than one parameter can be applied to the product at the same time.Parameter Symbol Minimum Maximum Units Reverse Voltage Vr-20V Reverse Current Ir-1mA Forward Voltage Vf-1V Forward Current If-5mA Power Dissipation--50mW Operating Temperature Tc–40+85°C Storage Temperature Ts–40+85°C Soldering – 10 seconds--+260°C Fiber Pull--10NPerformance SpecificationsTest Conditions:Unless Otherwise Stated PDA2446 Parameter Symbol Vr = 5 V, Tc = +25°C Min.Max.Units Dark Current Id-1nATc= +85°C-50nA Reverse Breakdown Voltage Vbr Ir = 10 µA35-V Capacitance C 1 MHz- 1.7pF Responsivity Rλ = 1300 nm0.7-A/W Operating Wavelengthλ80% points12001650nM Small Signal Bandwidth Bw 1.5-GHz Linearity X1Second Order-Vr = 15 V-70dBcfl = 135 MHzf2 = 190 MHz70% Modulation0 dBm Optical PowerThird Order-As above-85dBcFiber Pigtail: Tight jacketed, self-mode stripping, singlemode fiberParameter Minimum Maximum Units Length 1.0-mCore Diameter810µmCladding Diameter122128µmConcentricity Error-8%Secondary Jacket Diameter0.8 1.0mm533PDA Mechanical Outline OptionsALL DIMENSIONS IN MILLIMETERSPDA2446-DALL DIMENSIONS IN MILLIMETERS PDA2446 Electrical Pin-OutsPIN 1: CATHODE +VEPIN 2: CASEPIN 3: ANODE –VE534Ordering InformationPDA2446-XI-XXConnector Type:AP = Angle Polished FC/PCAS = Angle Polished SC/PCUS = Ultra Polished SC/PCSF = Super Polished FC/PCFlange Type:B = BarrelD = 2 hole PCB mount, 12.7 mm between centersAdditional options are available to meet your specific needs. Please contact your local representative for details.535536537Performance Specifications Absolute Limiting RatingsAbsolute (limiting) ratings mean that no catastrophic damage will occur if the product is subjected to these ratings for short periods, provided that each limiting parameter is in isolation and all other parameters have values within the performance specification. It should not be assumed that limiting values of more than one parameter can be applied to the product at the same time.ParameterSymbol MinimumMaximumUnits Supply VoltageV DD - 5.5V Photodiode Voltage (Negative)V pin -–7V Power Dissipation--350mW Operating Temperature Tc –40+85°C Storage Temperature Ts –40+85°C Soldering – 10 seconds --+260°C Fiber Pull --10NPerformance Specifications [1]Parameter Minimum MaximumUnits Responsivity 0.75-A/W Sensitivity [2]52 Mb/s –39-dBm 155 Mb/s –36Overload [2,3]–7-dBm Bandwidth 52 Mb/s 35-MHz 155 Mb/s90Output Impedance 3060ohms V DD Supply Voltage 4.75 5.25V V DD Supply Current -50mAPhotodiode Supply–7–4.5VNotes:1. Measured over the operating temperature range and power supply tolerance.2. Measured at the data rate specified for 1 x 10-10 using an infinite extinction ratio laser source modulated with a 223-1PRBS pattern.3. Higher overload performance available. Contact your local Hewlett-Packard Components representative for details.Fiber Pigtail: Tight jacketed, self-mode stripping, multimodeParameter MinimumMaximumUnits Length0.4 1.2m Core Diameter 4753µm Cladding Diameter 122128µm Concentricity Error-8%Secondary Jacket Diameter0.81.0mmSchematic Diagram321. GND 2. V OUT 3. V pin 4. +V DD538Drawing DimensionsPPA0052-FC-A PPA0155-FC-AMIN.––––12.00.27M8 x 0.7513.35A B C ∅D E ∅F ∅G H DIM.MIN.2.08–––– 2.54 NOM.–∅J L M N P ∅Q ∅RDIM.ALL DIMENSIONS IN MILLIMETERSMAX.19.59.515.09.1–0.3313.55MAX.2.321.652.26.88.24.2PPA0052-SC-APPA0155-SC-AMIN.–––––12.0A B C D E FDIM.MIN.2.00.27–2.08 2.54 NOM.17.8G ∅H ∅J ∅K ∅L M DIM.ALL DIMENSIONS IN MILLIMETERSMAX.9.523.013.515.58.0–MAX.3.00.337.52.518.2PPA1052-APPA1155-AMIN.––12.0–0.27400A B C D ∅E FDIM.MIN. 2.54 NOM.––13.352.1–∅G H K L ∅M ∅NDIM.ALL DIMENSIONS IN MILLIMETERSMAX.25.019.5–9.50.331200MAX.9.52.013.552.46.25539Ordering InformationAllowable Part Numbers:PPA0052-XX -A PPA0052 - FC - A PPA0155-XX -APPA0052 - SC - A Receptacle Type:PPA1052 - A - FP FC = FC PPA1052 - A - ST SC = SCPPA1052 - A - DN PPA1052 - A - SC PPA1052-X -XX PPA1052 - D - FP PPA1155-X -XXPPA1052 - D - ST Connector Type:PPA1052 - D - DN FP = FC/PC PPA1052 - D - SC ST* = ST DN = DIN PPA0155 - FC - A SC = SCPPA0155 - SC - A PPA1155 - A - FP Flange Type:PPA1155 - A - ST A = 2 hole Panel mount, 13.4 mm between centers PPA1155 - A - DN D = 2 hole PCB mount, 12.7 mm between centersPPA1155 - A - SC PPA1155 - D - FP PPA1155 - D - ST PPA1155 - D - DN PPA1155 - D - SC*ST is a registered trademark of AT&T.PPA1052-D PPA1155-DMIN.––12.0–0.274002.54 NOM.A B C D ∅EF ∅GDIM.MIN.3.8–0.9 12.7 NOM.2.1––H J K L ∅M ∅N P DIM.ALL DIMENSIONS IN MILLIMETERSMAX.25.018.0–9.50.331200MAX.4.27.51.12.46.257.5。

DSS-201LS22B中文资料

M

DC Spark-over voltage tolerance

M 20 A S

A

Taping form

22

Taping dimensions

R

Packing form

Axial taping No taping

Code 12 22 00

Taping width 26 52 No taping

Pitch 10 10

14

元器件交易网

DSSV Series

SURGE ABSORBER

■Features

UL1459 FAX CSA-22.2 No.225-M90 ●Protects telephone line equipment (telephone, modem, facsimile etc.) against surge and overvoltage (UL1459, CSA-22.2 No. 225-M90).

B F R

Bulk pack Flat pack taping Reel taping

Marking

Color code Black Brown Red Orange Yellow Green Blue Purple Gray White

First color band Part number

Second color band The unit digit of lot number

UL 497A 3

FCC 1 FCC cycle 1)

DSSV-201M-YD

1 FCC10/560 sec. 100A ±3times, 10/160 sec. 200A ±3times 2 DOC 1cycle 10/1000 sec. 1KV-12times, 100/1000 sec. 1KV-12times respectively. 3 UL Standard UL 497A File No. E131010 N

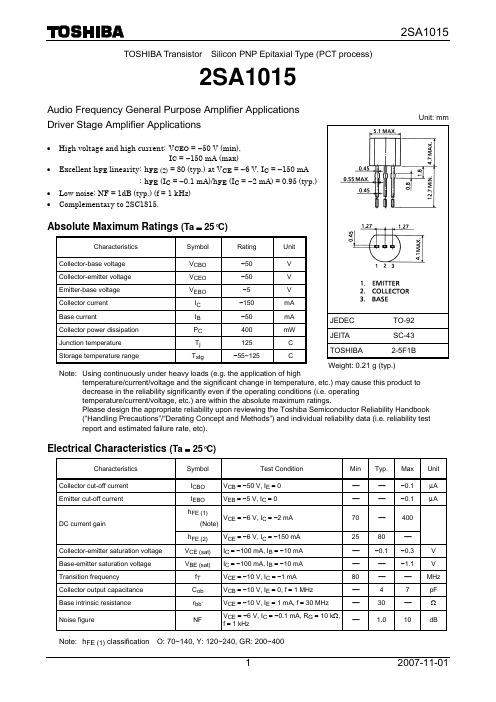

东芝2SA1015管数据表说明书

TOSHIBA Transistor Silicon PNP Epitaxial Type (PCT process)2SA1015Audio Frequency General Purpose Amplifier ApplicationsDriver Stage Amplifier Applications•High voltage and high current: V CEO = −50 V (min),I C = −150 mA (max)•Excellent h FE linearity : h FE (2) = 80 (typ.) at V CE = −6 V, I C = −150 mA:h FE (I C = −0.1 mA)/h FE (I C = −2 mA) = 0.95 (typ.)•Low noise: NF = 1dB (typ.) (f = 1 kHz)•Complementary to 2SC1815.Absolute Maximum Ratings (Ta = 25°C)Characteristics SymbolRatingUnitCollector-base voltage V CBO−50 VCollector-emitter voltage V CEO−50 VEmitter-base voltage V EBO−5 VCollector current I C−150 mABase current I B−50 mACollector power dissipation P C 400mWJunction temperature T j125 °CStorage temperature range T stg−55~125 °CNote: Using continuously under heavy loads (e.g. the application of hightemperature/current/voltage and the significant change in temperature, etc.) may cause this product todecrease in the reliability significantly even if the operating conditions (i.e. operatingtemperature/current/voltage, etc.) are within the absolute maximum ratings.Please design the appropriate reliability upon reviewing the Toshiba Semiconductor Reliability Handbook(“Handling Precautions”/“Derating Concept and Methods”) and individual reliability data (i.e. reliability testreport and estimated failure rate, etc).Electrical Characteristics (Ta = 25°C)Characteristics Symbol TestCondition MinTyp.Max Unit Collector cut-off current I CBO V CB=−50 V, I E= 0 ⎯ ⎯−0.1μA Emitter cut-off current I EBO V EB=−5 V, I C= 0 ⎯⎯−0.1μAh FE (1)(Note)V CE=−6 V, I C=−2 mA 70 ⎯ 400DC current gainh FE (2)V CE=−6 V, I C=−150 mA 25 80 ⎯Collector-emitter saturation voltage V CE (sat)I C=−100 mA, I B=−10 mA ⎯−0.1 −0.3VBase-emitter saturation voltage V BE (sat)I C=−100 mA, I B=−10 mA ⎯⎯−1.1V Transition frequency f T V CE=−10 V, I C=−1 mA 80 ⎯⎯ MHz Collector output capacitance C ob V CB=−10 V, I E= 0, f = 1 MHz ⎯ 4 7 pF Base intrinsic resistance r bb’V CE=−10 V, I E= 1 mA, f = 30 MHz ⎯ 30 ⎯ΩNoise figure NF V CE=−6 V, I C=−0.1 mA, R G= 10 kΩ,f = 1 kHz⎯ 1.0 10 dBNote: h FE (1) classification O: 70~140, Y: 120~240, GR: 200~400Unit: mmJEDEC TO-92 JEITA SC-43 TOSHIBA 2-5F1B Weight: 0.21 g (typ.)RESTRICTIONS ON PRODUCT USE•Toshiba Corporation, and its subsidiaries and affiliates (collectively “TOSHIBA”), reserve the right to make changes to the information in this document, and related hardware, software and systems (collectively “Product”) without notice.•This document and any information herein may not be reproduced without prior written permission from TOSHIBA. Even with TOSHIBA’s written permission, reproduction is permissible only if reproduction is without alteration/omission.•Though TOSHIBA works continually to improve Product’s quality and reliability, Product can malfunction or fail. Customers are responsible for complying with safety standards and for providing adequate designs and safeguards for their hardware, software and systems which minimize risk and avoid situations in which a malfunction or failure of Product could cause loss of human life, bodily injury or damage to property, including data loss or corruption. Before creating and producing designs and using, customers must also refer to and comply with (a) the latest versions of all relevant TOSHIBA information, including without limitation, this document, the specifications, the data sheets and application notes for Product and the precautions and conditions set forth in the “TOSHIBA Semiconductor Reliability Handbook” and (b) the instructions for the application that Product will be used with or for. Customers are solely responsible for all aspects of their own product design or applications, including but not limited to (a) determining the appropriateness of the use of this Product in such design or applications; (b) evaluating and determining the applicability of any information contained in this document, or in charts, diagrams, programs, algorithms, sample application circuits, or any other referenced documents; and (c) validating all operating parameters for such designs and applications. TOSHIBA ASSUMES NO LIABILITY FOR CUSTOMERS’ PRODUCT DESIGN OR APPLICATIONS.•Product is intended for use in general electronics applications (e.g., computers, personal equipment, office equipment, measuring equipment, industrial robots and home electronics appliances) or for specific applications as expressly stated in this document.Product is neither intended nor warranted for use in equipment or systems that require extraordinarily high levels of quality and/or reliability and/or a malfunction or failure of which may cause loss of human life, bodily injury, serious property damage or serious public impact (“Unintended Use”). Unintended Use includes, without limitation, equipment used in nuclear facilities, equipment used in the aerospace industry, medical equipment, equipment used for automobiles, trains, ships and other transportation, traffic signaling equipment, equipment used to control combustions or explosions, safety devices, elevators and escalators, devices related to electric power, and equipment used in finance-related fields. Do not use Product for Unintended Use unless specifically permitted in this document.•Do not disassemble, analyze, reverse-engineer, alter, modify, translate or copy Product, whether in whole or in part.•Product shall not be used for or incorporated into any products or systems whose manufacture, use, or sale is prohibited under any applicable laws or regulations.•The information contained herein is presented only as guidance for Product use. No responsibility is assumed by TOSHIBA for any infringement of patents or any other intellectual property rights of third parties that may result from the use of Product. No license to any intellectual property right is granted by this document, whether express or implied, by estoppel or otherwise.•ABSENT A WRITTEN SIGNED AGREEMENT, EXCEPT AS PROVIDED IN THE RELEVANT TERMS AND CONDITIONS OF SALE FOR PRODUCT, AND TO THE MAXIMUM EXTENT ALLOWABLE BY LAW, TOSHIBA (1) ASSUMES NO LIABILITYWHATSOEVER, INCLUDING WITHOUT LIMITATION, INDIRECT, CONSEQUENTIAL, SPECIAL, OR INCIDENTAL DAMAGES OR LOSS, INCLUDING WITHOUT LIMITATION, LOSS OF PROFITS, LOSS OF OPPORTUNITIES, BUSINESS INTERRUPTION AND LOSS OF DATA, AND (2) DISCLAIMS ANY AND ALL EXPRESS OR IMPLIED WARRANTIES AND CONDITIONS RELATED TO SALE, USE OF PRODUCT, OR INFORMATION, INCLUDING WARRANTIES OR CONDITIONS OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, ACCURACY OF INFORMATION, OR NONINFRINGEMENT.•Do not use or otherwise make available Product or related software or technology for any military purposes, including without limitation, for the design, development, use, stockpiling or manufacturing of nuclear, chemical, or biological weapons or missile technology products (mass destruction weapons). Product and related software and technology may be controlled under the Japanese Foreign Exchange and Foreign Trade Law and the U.S. Export Administration Regulations. Export and re-export of Product or related software or technology are strictly prohibited except in compliance with all applicable export laws and regulations. •Please contact your TOSHIBA sales representative for details as to environmental matters such as the RoHS compatibility of Product.Please use Product in compliance with all applicable laws and regulations that regulate the inclusion or use of controlled substances, including without limitation, the EU RoHS Directive. TOSHIBA assumes no liability for damages or losses occurring as a result of noncompliance with applicable laws and regulations.。

NSD-2101-ASST;中文规格书,Datasheet资料

DSS炉维护手册中文版

本资料来源于网络,版权归原著作所有,禁止使用于一切商业行为,仅供交流学习用!请在下载后24小时内删除!

本资料来源于网络,版权归原著作所有,禁止使用于一切商业行为,仅供交流学习用!请在下载后24小时内删除!

本资料来源于网络,版权归原著作所有,禁止使用于一切商业行为,仅供交流学习用!请在下载后24小时内删除!

本资料来源于网络,版权归原著作所有,禁止使用于一切商业行为,仅供交流学习用!请在下载后24小时内删除!

本资料来源于网络,版权归原著作所有,禁止使用于一切商业行为,仅供交流学习用!请在下载后24小时内删除!

本资料来源于网络,版权归原著作所有,禁止使用于一切商业行为,仅供交流学习用!请在下载后24小时内删除!

本资料来源于网络,版权归原著作所有,禁止使用于一切商业行为,仅供交流学习用!请在下载后24小时内删除!

本资料来源于网络,版权归原著作所有,禁止使用于一切商业行为,仅供交流学习用!请在下载后24小时内删除!

本资料来源于网络,版权归原著作所有,禁止使用于一切商业行为,仅供交流学习用!请在下载后24小时内删除!

本资料来源于网络,版权归原著作所有,禁止使用于一切商业行为,仅供交流学习用!请在下载后24小时内删除!

本资料来源于网络,版权归原著作所有,禁止使用于一切商业行为,仅供交流学习用!请在下载后24小时内删除!

本资料来源于网络,版权归原著作所有,禁止使用于一切商业行为,仅供交流学习用!请在下载后24小时内删除!

本资料来源于网络,版权归原著作所有,禁止使用于一切商业行为,仅供交流学习用!请在下载后24小时内删除!

本资料来源于网络,版权归原著作所有,禁止使用于一切商业行为,仅供交流学习用!请在下载后24小时内删除!

本资料来源于网络,版权归原著作所有,禁止使用于一切商业行为,仅供交流学习用!请在下载后24小时内删除!

DSS-T 管理端说明书

DSS Manager User’s ManualVersion 3.11Table of Contents1OVERVIEW AND ENVIRONMENT (1)1.1Overview (1)1.2System (1)1.3Requirement for Configuration (3)2PROCEDURE OF CONFIGURATION (4)3LOGIN SYSTEM (5)3.1Login Interface (5)3.2Buttons (6)4SYSTEM SETTINGS (7)5MANAGE DEVICE (10)5.1Add Organization (10)5.2Add Device (14)5.2.1Add Encoder (14)5.2.2Add Decoder (19)5.2.3Add Video Wall (20)5.2.4Add Alarm Host (20)5.2.5Add ANPR Device (20)5.2.6Add Intelligent Device (20)5.2.7Add Matrix (21)5.2.8Add A&C (21)5.2.9Add Transcoder (21)5.3Manage Channel (21)6MANAGE ACCOUNT (22)6.1Add User Role (22)6.2Add User (24)7SERVER MANAGEMENT (27)8DAILY OPERATION (29)8.1Add Normal Plan (29)8.2Alarm (33)8.2.1Set Contacts (33)8.2.2Set Link Level (34)8.2.3Set Alarm Time Template (35)8.2.4Set Alarm Storm (36)8.2.5Set Alarm Video on Wall (37)8.3Map (40)8.4Set TV Wall (42)8.5Door Timeout Setup (45)8.6Resources Binding (45)8.7Video Diagnosis (46)8.7.1Diagnosis Item (47)8.7.2Diagnosis Task (48)8.7.3Diagnosis Scheme (49)8.8Config Intelligent Traffic (50)8.8.1Configure ANPR Point (50)8.8.2Configure ANPR Region (51)8.9Set Cascading (52)8.10Upload (53)8.11Backup and Restore (53)8.11.1System Backup (53)8.11.2Restore (54)8.12Resource Re-Config (54)8.12.1Video Server (54)8.12.2Picture Server (55)8.12.3Parameter Re-Config (55)8.13Statistics (55)8.13.1Overview (55)8.13.2Server (58)8.13.3Device (59)8.13.4Management (60)8.13.5Operator (61)8.13.6User Count (61)WelcomeThank you for using our Digital Surveillance System (DSS)!This user’s manual is designed to be a reference tool for operation of your system. Here you can find detailed operation information about DSS.1Overview and Environment1.1OverviewDSS is a hard & software device with Linux structure. It is based on network to connects those decentral and independent on-site monitoring thus achieving centralized monitoring and management crossing area and industry. It provides user with a brand new, direct management tool. Besides A/V, alarm, remote collection, transmission, storage, processing, DSS has advantages of high quality, wide coverage, multi-task, integrable, easy management, one-stop service.●Advanced All-In-One structureUsing leading All-In-One architecture, integrated within DSS series of main control,forwarding, storage, device management and all other functions, eliminates the need for proprietary forwarding servers, storage servers, so that the system set up more convenient.●Real UPnPJust plug it in, configure IP address, DSS series can immediately start working.●One-key upgradeFor subsequent software version upgrade, support network or USB disk one-key upgrade, and make sure that data will not be lost, and the business will not stop.●Higher performanceOne unit DSS series forwarding capacity max 1000Mbit/s, storage capacity max 700 Mbit/s.●Higher securityDSS series supports anti-virus, anti-hacker attack.●Higher stability⏹Forced system power 500 times without exception⏹using self-developed technology and unique new storage disk format⏹provides long-term storage and playback performance decay⏹support hot-swap of storage disk●Higher reliability⏹ support network redundancy⏹Database double-click hot spare1.2SystemThe system network is in Figure 1- 1.Figure 1- 11.3Requirement for ConfigurationChart 1- 12Procedure of ConfigurationYou can refer to the following figure of procedures to configure DSS’s operation. See Figure 2- 1.Figure 2- 13Login System3.1Login InterfaceYou can refer to the following steps to login DSS manager.Step 1. In Internet Explorer, input IP address of DSS, press Enter. You will see Figure 3- 1.Figure 3- 1Note:You can download DSS Client on this login page. If it is your first time login DSS Manager, please add its IP address into the trusted site of your explorer.Step 2. Input Username and Password. Default username is: system. Default password is:123456.For security reason, please change your login password after you first login. Password can contains number, letter, underline and other symbols.Step 3. Click Login.After login, you will see Figure 3- 2.Figure 3- 2Note:●When you exit the system, click Exit in the upper-right corner. Click OK in the prompt box.●If you want to change password, click, and select Modify Password. You can changepassword in the prompt box.3.2Buttons4 System SettingsWhen you first login the system, you shall configure system settings in order to make the system run properly.Configure the system as follows:Step 1. Select System > Parameters, you will see Figure 4- 1.Figure 4- 1Step 2. Configure parameters. Step 3. Click Submit.5Manage DeviceDSS supports adding organization and different types of device.5.1Add OrganizationBefore you add device, you need to add organization of current device. You can arrange, organize and manage layer of device in Org.The default first-level organization is root node. Newly added organization will be displayed below the root node.●Select General> Org, see Figure 5- 1.Figure 5- 1●Click . System pops up a Edit Org box, see Figure 5- 2.Figure 5- 2Step 1. Edit Org Name, and click OK.Step 2. Click . System pops up an Add Org box, see Figure 5- 3.Figure 5- 3Step 3. You can enter designated Org Name and click OK. For multiple layers of organizations, you shall repeat these steps. See Figure 5- 4.Figure 5- 4Note:You can only edit root node and the organization cannot be deleted.Select Org> Logic Org, click . System shows new loggic org box, see Figure 5- 5.Figure 5- 5Step 1. Enter organization name, and click OK.Step 2. On the left, select logic org and click , select setup. See Figure 5- 6.You also can double click login org on the left, and there will be root node shown below.Figure 5- 6You cn adjust channel position with , , , .Step 3. In config channel area, select alternate channel and add it to selected channel. SeeFigure 5- 7.Figure 5- 7You can adjust channel position via , , , buttons.Step 4. Add user. Please refer to Ch 6.1.Note:In Figure 6-1, on the left, select logic org for device tree display.Step 5. Add role. Please refer to Ch 6.2. After configuration is complete, you can login with theadded user account. Click on General area to view. See Figure 5- 8.Figure 5- 85.2Add DeviceYou can add device in two ways:●Device: Manage in device mode, where you can add, edit and delete devices, also you canconfigure and manage deployed devices.●Ch annel: Manage in channel mode there you can view all devices’ monitoring spot andalarm channel.5.2.1 Add EncoderDSS Manager supports manually adding encoder and auto search deployed encoder.●Manually AddStep 1. Select General>Device>Device, system displays device interface.Step 2. ClickStep 3. Click . System displays Add Encoder box, see Figure 5- 9.Figure 5- 9Step 4. Set Input Info, and click Getting Info. System will automatically get info of video channel, alarm input channel and alarm output channel.Note: If you add device with IP section, domain name or auto register, then you cannot get info of video channel, alarm input channel and alarm output channel by clicking on Getting Info.Step 5. Click OK as finishing adding encoder.●Auto SearchSystem automatically adds encoder as follows:Step 1. Click . System auto searches the device and the result shall look like Figure 5- 10.Figure 5- 10●Click to edit device info.●Enter IP address in IP field and click Search to search IP within the range.Step 2. Check device to add, and click .System pops up a Add Encoder box, seeFigure 5- 11.Figure 5- 11Step 3. Select Org, input username and password. Username and password is the login username and password of device. Default username and password is admin/admin.Step 4. Click OK.When device status switches from to as in Figure 5- 12. You also can view added device by selecting Controlled Status in the upper-right corner in Auto Search Encoder interface.Figure 5- 12Step 5. Click Close.System will add the device into corresponding organizations. You may also edit and delete added device, please refer Ch 3.2.5.2.2 Add DecoderDSS Manager supports manually adding decoder and auto search deployed decoder. Please refer to Ch 5.2.1.When you add decoder, please refer to Chart 5- 1.Chart 5- 15.2.3 Add Video WallDSS Manager supports adding of video wall. Please refer to Ch 5.2.1.5.2.4 Add Alarm HostDSS support manually adding of alarm host. Please refer to Ch 5.2.1.5.2.5 Add ANPR DeviceDSS supports manually adding of ANPR device. Please refer to Ch 5.2.1.5.2.6 Add Intelligent DeviceDSS Manager supports manually adding of intelligent device. Please refer to Ch 5.2.1. Step 1. Add IVS device.Step 2. Download and install IVS control.1. Click in IVS device Operation column. If you have no installed IVS control, systemwill pop up a message and ask you to download it and re-login the platform.2. Click OK. System pops up download box.3. Click Save.4. When downloading is complete, click Close.5. Open the downloaded file and install IvsConfigCtrl_Setup.exe.6. Log in IVS interface again.Step 3. Bind video channel to IVS device.1. Click Add.2. Double click device on the left and select channel and select IVS channel on the right.Click . System will bind video channel and IVS channel.3. Check IVS analysis, configure device name, device port and select strea,.4. Click OK. System says successfully saved.5. Click OK.Step 4. Click in Config column to configure rule.●Detection zone: By drawing detection zone, it will detects the entire drawn zone. It will notdetect areas outside the detection zone. There is only one detection zone. You can set more than one excluded zone. If no detection zone is set, it will detect the entire area.●Scene mark: By drawing mark zone and set actual distance for vertical length and horizontallength. Event detector will decide road length and width with a series of algorithm and detect over speed, under speed and etc.●Target filter: Set size or dimension of target and only reserves target within range.●Rule config: Config alarm rule. You can add multiple rules to one channel. Rule type:perimeter protection, tripwire and etc.●Parame ter config: Config jitter rate, sensitivity and etc. Please refer to IVS user’smanual.5.2.7 Add MatrixDSS Manager supports manually adding of matrix device. Please refer to Ch 5.2.1.5.2.8 Add A&CDSS supports manually adding of A&C. Please refer to Ch 5.2.1.5.2.9 Add TranscoderDSS Manager supports manually adding of transcoder. Please refer to Ch 5.2.1.5.3Manage ChannelIn Channel, you can view added video channel, alarm input channel and alarm output channel. You can search added channel in Video Channel interface.Alarm Channel includes alarm input and output channels. You can search added channels here.6Manage AccountDSS Manager allows user to add and delete accounts. User must create user role before adding user. Existing user can login manager and login the client. Different users may have different operation rights according to their user role.6.1Add User RoleBefore you configure user, you must set user role and grand certain rights to the role.Rights of user role includes Administrator Menu right, Operator Menu right and Device right. You must grand these rights before operate.For example, you want to grant right as administrator:Step 1. Click General>Account. System displays Account interface.Step 2. Click Role tab.Step 3. Click . System pops up Add Role box.Step 4. Input Role Name, and select Role Level.Note: If you check Copy Role next to Role Name, and select one role from the dropdown box, then the info will be pasted to your selected role.Step 5. Click Device Rights page, select right in Right Trees and select channel in Channel Tree on the right. See Figure 6- 1.Figure 6- 1Note:●Click so you can copy setting from the selected node to current node.●If you do not check corresponding device right, then all users under this role will have nocorresponding rights.●You must add TV wall in Business>TV Wall before set right of TV wall. Please refer to fontcolor in “0 video input” device.●Red: the channel has not configured on map.●Grey: the channel is added on map.Step 6. Drag device under ANPR input, A&C input and alarm input onto map.Step 7. Complete config of e-map.●Config video wall.Step 8. Click System Rights tag, select corresponding system rights. See Figure 6- 2.Figure 6- 2Note:●If you do not check corresponding device right, then all users under this role will have nocorresponding rights. For example, if Operator Menu is not checked, then when this user logs in Operator, there will be no menu displayed.●Operator menu in system right means C/S and B/S format menu in Client.Step 9. Click OK to add the role.6.2Add UserIf you have added user role, now you can add user of that role.Step 1. Click User tab under Account.Step 2. Click . System pops up Add User box.Step 3. Create a username, a password and confirm password. Select Department and Role.See Figure 6- 3.Figure 6- 3Note:●If you check Reusable box next to Username, then you allows more than one user to loginsystem with this Username at the same time.●If you do not select a role, then the user will have no System Rights or Device Rights.●You can select more than one role at a time.●You can click Optional in the lower-left corner to fill in extra info.Step 4. Click Optional, system display interface as in Figure 6- 4.Figure 6- 4Step 5. Set parameters. Step 6. Click OK to add user.7Server ManagementDSS series Manager provides server management function. Server management has center unit and video unit.●Center serverHas not added dual hot spare.Step 1. Open General>Server>Center Server, you can see operation status of center server. See Figure 7- 1.Figure 7- 1Step 2. Click , you can view center server’s name, video unit status and picture unit status, server type, IP and status. See Figure 7- 2.Figure 7- 2Add dual hot spare.Please refer to DSS Platform Initialization User’s Manual Ch 2.3.Open General>Server>Center Server, you can see operation status of center server.●Video ServerStep 1. Open General>Server>Video Server, you can see operation status of sub server. See Figure 7- 3.Step 2. Click or , you can edit or delete video server. Click you can enter initialization page.Step 3. Click , you can view each video server name, server type, IP and status.8Daily Operation8.1Add Normal PlanDSS Manager supports record plan of channel which allow front-end device to record during planned period.System saves record file to network storage server. You can plan the file in General >Playback on Operator-end.Step 1. Select Business>Storage. System displays Storage interface as in Figure 8- 1.Figure 8- 1Step 2. Set record time.a) Click Time Template in the upper-right corner of storage interface. System displays TimeTemplate interface. Default Time Templates are weekend, weekday and 24-hour.b) Click . System pops a Add Time Template box. See Figure 8- 2.Figure 8- 2c) Input Template Name, select cycle period. Set single system, cycle mode and never stop.See Figure 8- 3.Figure 8- 3Note:If you check Copy next to Template Name, and select template in the dropdown list, then youcan copy configured template to current template.d) Click OK.See Figure 8- 4.Figure 8- 4Step 3. Set normal plan.a) Click Normal Plan in the upper right corner of Storage interface. System displays NormalPlan interface.b) Click . System pops up Add Record Plan box. See Figure 8- 5.Figure 8- 5can clickc) Input Plan Name, and select Template, Bit Stream. Check Record Plan. See Figure 8- 6.Figure 8- 6Step 4. Click OK. System displays configured record plan.8.2AlarmDSS Manager supports alarm, including Alarm Scheme, Output Alarm Video to the Wall, Alarm Type, Alarm Time Template, Link Level and Contacts.●Alarm Scheme: set alarm scheme template.●Output Alarm Video to the Wall: Make alarm video display on wall.●Alarm Type: Set system alarm interval and customize alarm as batch.● Alarm Time Template: Set alarm time template.●Link Level: Set alarm link level.●Contacts: Set user who to receive alarm notice.Alarm flow chart is in Figure 8- 7.Figure 8- 78.2.1 Set ContactsWhen you add user into contacts and if the setup of Link Level includes email or sms, then system will send email or sms to the new contact.Step 1. Click Alarm tab. System displays Alarm interface.Step 2. Click .Step 3. Click . System pops up a Add Contacts box. See Figure 8- 8.Figure 8- 8Step 4. Input User Name, ID No., Email and Telephone.Step 5. Click OK.8.2.2 Set Link LevelYou can set Link Level and its corresponding Link Mode as 1 is the highest and 5 is the lowest. Step 1. Click . System pops up an interface as in Figure 8- 9.Figure 8- 9Step 2. Click . See Figure 8- 10.Figure 8- 10Step 3. Set Link Level Name and select Link Mode.Step 4. Click OK.8.2.3 Set Alarm Time TemplateYou can follow these steps:Step 1. Click . System displays time template interface.Step 2. Click Add. System pops up an Add Alarm Time Template box.Step 3. Input Template Name, select cycle period. Set Single Period and link level. See Figure 8-11.Figure 8- 11Note:●If you check the Copy box next to Template Name, then you need to select template in thedropdown box.●You shall set Link Level first before select level here. Please refer to Ch 7.2.2.●Click to set Link Level of other periods.Step 4. Click OK.8.2.4 Set Alarm StormYou can set alarm interval and customized alarm storm as batch.●Set alarm interval as batchStep 1. Click . System displays Alarm Storm interface.Step 2. Select one or more alarm storm, and click . System pops up abox as in Figure 8- 12.Figure 8- 12Step 3. Set Alarm Interval.Note: The interval cannot be over 86400 seconds.Step 4. Click OK.You can click to stop alarm interval as batch.8.2.5 Set Alarm Video on WallNote:You shall configure TV wall before outputting alarm video to the TV wall. Please refer to font color in “0 video input” device list.●Red: the channel has not configured on map.●Grey: the channel is added on map.Step 1. Drag ANPR input, A&C input and alarm input on the right onto map.Step 2. Complete e-map config.Configure Alarm Scheme as follows:Step 1. Click .Step 2. Click . System pops up an Add Alarm Scheme box as in Figure 8- 13.Figure 8- 13Step 3. Input Scheme Name, select template and check Enable.Note: You must configure Alarm Time Template before selecting time template here. To configure Alarm Time Template please refer to Ch 7.2.3.Step 4. Click Next. System displays Alarm Source and Operation interface.Step 5. Click . System displays Add Alarm Source and Link Operation 1 box, seeFigure 8- 14.Figure 8- 14Step 6. In Alarm Source area, select alarm source and its link operation. Alarm source includes device, video channel, alarm input channel, intelligent channel, A&C channel and system. Different alarm source corresponds to different alarm type.Step 7. In Corresponding Link Operation area, select link operation. Link operation includes Record, and TV Wall.●For link operation, if you select record, you shall select video channel under Record tab, andset record time.Note:If you need pre-record, then select device record needed.●When link level is video wall, you shall add alarm video wall task first, before selectingcorresponding video wall in link level. Please refer to Ch 8.2.6.Step 8. Click Save. System prompts a message “Successfully save scheme rule!”.Step 9. Click OK.Step 10. Click Next. System displays Alarm Preview interface as in Figure 8- 15.Figure 8- 15Step 11. Click Finish.When alarm occurs, system performs link operation according to Alarm Scheme settings, and shows alarm info in Statistics>Device>Device Alarm Info.8.3MapDSS Manager supports super map, raster map, google and google offline map. You can add video device onto the map.Note:If there is no electronic map, please refer to DSS Platform Initialization User’s Manual.To add electronic map:Step 1. Select Business>Map.Step 2. Click Add map.Step 3. Select picture you want to add, click submit.Figure 8- 16Step 4. Drag device under Video Device tab onto the right onto the map. See Figure 8- 17Figure 8- 17Color of text in Video Device list:●Red: the channel is not configured on map.●Grey: the channel is shown on map.Step 5. Drag device under Alarm Input tab onto map.Step 6. Click Save.8.4Set TV WallDSS Manager supports configuration of TV wall.After TV wall is configured, you can make video display on TV wall from Client. Please refer to DSS Cl ient User’s Manual’s Ch 5.5.Note: User of Client must have TV wall right in order to configure video display on TV wall.To configure TV wall, please follow:Step 1. Add decoder. Please refer to Ch 5.2.1.Step 2. Select Business>TV Wall, system displays TV Wall interface.Step 3. Click . System pops up a Add TV Wall box, see Figure 8- 18.Figure 8- 18Step 4. Input TV Wall Scheme Name and click to select layout of 1*1, 2*2, 3*3 or 4*4. See Figure 8- 19.You also can click to customize TV wall.Figure 8- 19Note:●Press Ctrl and now you can select more than one screen. Click on the right tocombine selected screens. You can cancel combination by clicking on . Before you combine screens, you must add video wall equipment.●Double click the screen or right-click and select Properties. In the pop-up box, you can setexact position, size and name of screen.●Select a screen, and right click to delete or rename the screen.Step 5. Click Next. System displays Select decode channel interface.Step 6. In Device Tree, select decoder and drag it to corresponding TV wall. See Figure 8- 20.Figure 8- 20Note: Right-click can cancel current binding and rename screen.Step 7. Click Next. System displays Enable interface.Step 8. Check Apply Now.Note: If you do not check Apply Now, then you cannot select this TV wall on Client.Step 9. Click Finish.8.5Door Timeout SetupDSS supports door timeout setup. If door unlock exceeds set threshold, then system links to level alarm.The higher to level, the higher the threshold will be.Step 1. Select Business>Door Timeout Setup.Step 2. Input alarm level name and threshold.Step 3. Click Submit.8.6Resources BindingDSS supports A&C, alarm host and ANPR resources binding.For example, to set A&C.Step 1. Select Business>Resources Binding>Access and Control. Click . See Figure 8- 21.Figure 8- 21Step 2. Select source channel and video channel. Click OK.8.7Video DiagnosisDSS series Manager supports configuration of video diagnosis, including scheme config, task config and diagnosis item config.●Scheme config: configure video diagnosis scheme template.●Task confi: configure video diagnosis task.●Diagnosis item config: configure video diagnosis item.Flow of video diagnosis is shown in Figure 8- 22.。

APHB1608SGYC;中文规格书,Datasheet资料

DATE: APR/20/2012 DRAWN: D.M.Su

PAGE: 3 OF 6 ERP: 1203011315

/

Yellow

SPEC NO: DSAK7900 APPROVED: WYNEC

REV NO: V.5B CHECKED: Allen Liu

DATE: APR/20/2012 DRAWN: D.M.Su

Parameter Power dissipation DC Forward Current Peak Forward Current [1] Reverse Voltage Operating Temperature Storage Temperature

Note: 1. 1/10 Duty Cycle, 0.1ms Pulse Width.

Viewing Angle [1] 2θ1/2 130°

Typ. 15 5

Water Clear

5 3

Electrical / Optical Characteristics at TA=25°C

Symbol λpeak λD [1] Δλ1/2 C VF [2] IR Parameter Peak Wavelength Dominant Wavelength Spectral Line Half-width Capacitance Forward Voltage Reverse Current Device Super Bright Green Yellow Super Bright Green Yellow Super Bright Green Yellow Super Bright Green Yellow Super Bright Green Yellow Super Bright Green Yellow Typ. 565 590 568 588 30 35 15 20 2.2 2.1 2.5 2.5 10 10 Max. Units nm nm nm pF V uA Test Conditions IF=20mA IF=20mA IF=20mA VF=0V;f=1MHz IF=20mA VR = 5V

FFPF30UA60S;中文规格书,Datasheet资料

oC

Ratings 2.5

Units oC/W

Tape Width

-

Quantity

50

©2009 Fairchild Semiconductor Corporation

1

FFPF30UA60S Rev. A

/

FFPF30UA60S UItrafast Rectifier

Working Peak Reverse Voltage

DC Blocking Voltage Average Rectified Forward Current Non-repetitive Peak Surge Current 60Hz Single Half-Sine Wave

@ TC = 43oC

Figure 1. Typical Forward Voltage Drop vs. Forward Current

100

Forward Current, I [A] F

TC = 125oC 10

TC = 25oC

TC = 75oC

1

0.0

0.5

1.0

1.5

2.0

2.5

Forward Voltage, V [V] F

FFPF30UA60S UItrafast Rectifier

FFPF30UA60S UItrafast Rectifier

Features

• Ultrafast switching, Trr < 90ns • High Reverse Voltage and High Reliability • Avalanche Energy Rated • Max Forward Voltage, VF < 2.2V • RoHS Compliant

DS_SMD_0806规格书标准

60o

Radiation table

Angle, o 0 20 30 40 50 60 70

Relative intensity, % 100 97 92 80 66 52 36

CIE coordinates (White colour)

0.355 0.350 0.345 0.340 0.335 0.330 0.325

Input, V Output, V Output current, A Power, W Weight, g Dimmensions(LxWxHxCable), mm Efficiency, %

Input, V Output, V Output current, A Power, W Weight, g Dimmensions(LxWxHxCable), mm Efficiency, %

Input, V Output, V Output current, A Power, W Weight, g Dimmensions(LxWxHxCable), mm Efficiency, %

Input, V Output, V Output current, A Power, W Weight, g Dimmensions(LxWxHxCable), mm Efficiency, %

CIE tolerance table (White colour) 6100 ± 200 K

Cx

Cy

CIE tolerance table (Warm White colour) 3000 ± 100 K

Cx

Cy

0,317

0,326

0,316

0,342

0,323

0,352

0,324

深入理解MOSFET规格书-datasheet

深入理解MOSFET规格书/datasheet

对于电源方面的工程师、技术人员而言,相信大家对MOSFET都不会陌生。

工程师们要选用某个型号的MOSFET时,首先要看的就是规格书

/datasheet,拿到MOSFET的规格书/datasheet时,我们要怎幺去理解那十几

页到几十页的内容呢?

注:1. 后续内容中规格书/datasheet统一称为datasheet;

2. 本文中有关MOSFET datasheet的数据截图来自英飞凌IPP60R190C6 datasheet。

1.关于VDS

Datasheet上电气参数第一个就是V(BR)DSS,即DS击穿电压,也就是我们关心的MOSFET的耐压。

此处V(BR)DSS的最小值是600V,是不是表示设计中只要MOSFET上电压不超过600V MOSFET就能工作在安全状态?

相信很多人的答案是“是”,曾经我也是这幺认为的,但这个正确答案是“不是”。

这个参数是有条件的,这个最小值600V是在Tj=25℃的值,也就是只有在Tj=25℃时,MOSFET上电压不超过600V才算是工作在安全状态。

MOSFET V(BR)DSS是正温度系数的,其实datasheet上有一张V(BR)DSS与Tj的关系图(Table 17),如下:

要是电源用在寒冷的地方,环境温度低到-40℃甚至更低的话,MOSFET

V(BR)DSS值所以在MOSFET使用中,我们都会保留一定的VDS的电压。

仕様一覧(GB)-06版

电动注塑机FANUC ROBOSHOT@-S15+A / @-S30+A @-S50+A /@-S100+A / @-S150+A规格一览表•规格表、主要设置条件•外形尺寸图•标准装配、选配项目(机械部分、控制部分和软件、螺杆和料筒)•平面布置图、详细设置条件•ROBOSHOT-LINK+RSHOT α-S i A(C)-062013.12< ROBOSHOT @-S15+A机构部规格单位内容---双曲肘kN 150 (15tonf) mm 260 - 130mm 160mm φ60mm 260 × 235mm 355 × 340注1)mm 150 × 135mm 50kN 7 (0.7tonf)mm 141618mm 565675cm 391119最大射出压力注2)MPa 250250230最大保压压力注2)MPa 250230190最大射出率注3)cm 3/s 80105133最大射出速度注3)mm/s 525螺杆最高转速min -1450最大射出压力注2)MPa 250250230最大保压压力注2)MPa 250230190最大射出率注3)cm 3/s 123160203最大射出速度注3)mm/s 800螺杆最高转速min -1450kN 5 (0.5tonf)料筒3喷嘴1加热器功率kW 2.4 2.83.1射出速度800mm/s规格 约 1.5注1)当模具尺寸小于此尺寸时,锁模力可能受到限制。

注2)最大射出压力、最大保压压力是射出装置的输出值,并不是树脂的压力。

最大射出压力、最大保压压力是可能设定的最大值。

根据成型条件不同,最大射出压力、最大保压压力可能受到限制。

注3)最大射出率、最大射出速度的数值是计算值。

最大射出率、最大射出速度的数值,并不是最大射出压力发生时的保证值。

注4)此数值是未安装选配项目时的数值。

注5)上表中数值,均按照1MPa=10kgf/cm2进行换算。

IEC61215 标准 (中文版)[1]

![IEC61215 标准 (中文版)[1]](https://img.taocdn.com/s3/m/4820797977232f60ddcca177.png)

IEC61215 标准(中文版)美国光伏检测室( ASU-PTL)中国全权代理Solspring International Energy Group太阳普林国际能源集团(加拿大)2005年中国目的1。

决定组件的电性能和热性能。

2。

表明组件在合理的成本和时间内,能够承受长时间的气候暴露。

取样根据 IEC 60410 标准,8块用于质量测试的组件应从一批或几批产品中任意抽取。

通过的标准:1。

最大输出 (The degradation of Max. output power does not exceedthe prescribed limit after each test nor 8% after each test sequence)2。

电路 (no sample has exhibited any open-circuit during the tests)3。

目测迹象(There is no visual evidence of a major defect) 4。

绝缘性(The insulation test requirements are met after the tests)5。

湿漏电 (The wet leakage current test requirements are met at thebeginning and the end of each sequence and after the damp heat test)6。

特殊要求(Specific requirements of the individual tests are met)5kWh/m2目测,电性能,绝缘,湿漏1 12 22热循环 200电性能紫外线湿热热循环 50户外暴二极管热试验湿冻机械强度雹击热斑终端试验目测,电性能,绝缘,IEC61215 (第二版)标签每一个组件的标签都应包括以下内容且清楚可读:1. 生产厂商名字或标志。

BYV410X-600,127;中文规格书,Datasheet资料

BYV410X-600Enhanced ultrafast dual rectifier diodeRev. 01 — 29 June 2009Product data sheet 1.Product profile1.1General descriptionEnhanced ultrafast dual rectifier diode in a SOT186A (TO-220AB) plastic package.1.2Features and benefitsHigh thermal cycling performance Isolated packageLow thermal resistance Soft recovery characteristic minimizes power consuming oscillationsVery low on-state losses1.3ApplicationsDual mode (DCM and CCM) PFC Power Factor Correction (PFC) forInterleaved Topology1.4Quick reference dataTable 1.Quick referenceSymbol Parameter Conditions Min Typ Max UnitI O(AV)average outputcurrent square-wave pulse; δ=0.5;T h≤42°C; both diodesconducting; see Figure 1;see Figure 2--20ADynamic characteristicst rr reverse recoverytime I F=1A;V R=30V;dI F/dt=100A/µs;T j=25°C; see Figure 5-2035nsQ r recovered charge I F=1A;V R=30V;dI F/dt=100A/µs-1528nC Static characteristicsV F forward voltage I F=10A;T j=25°C;see Figure 4- 1.4 2.1VI F=10A;T j=150°C- 1.3 1.9V2.Pinning information3.Ordering information4.Limiting valuesTable 2.Pinning information Pin Symbol Description Simplified outline Graphic symbol1A1anode 1SOT186A(TO-220F)2K cathode 3A2anode 2mbn.c.mounting base; isolated321mbsym125Table 3.Ordering informationType numberPackage NameDescriptionVersion BYV410X-600TO-220Fplastic single-ended package; isolated heatsink mounted; 1 mounting hole; 3-lead TO-220 "full pack"SOT186ATable 4.Limiting values In accordance with the Absolute Maximum Rating System (IEC 60134).Symbol ParameterConditionsMin Max Unit V RRM repetitive peak reverse voltage-600V V RWM crest working reverse voltage -600V V R reverse voltage DC-600V I O(AV)average output currentsquare-wave pulse; δ=0.5; T h ≤42°C; both diodes conducting; see Figure 1; see Figure 2-20A I FRM repetitive peak forward current square-wave pulse; δ=0.5; t p =25µs; T h ≤60°C; per diode -20A I FSM non-repetitive peak forward current t p =8.3ms; sine-wave pulse; T j(init)=25°C; per diode -132A t p =10ms; sine-wave pulse; T j(init)25°C; per diode-120A T stg storage temperature -40150°C T jjunction temperature-150°C5.Thermal characteristics6.Isolation characteristicsTable 5.Thermal characteristics Symbol ParameterConditionsMin Typ Max Unit R th(j-h)thermal resistance from junction to heatsinkwith heatsink compound; per diode; see Figure 3--5K/W with heatsink compound; both diodes conducting--3K/W R th(j-a)thermal resistance from junction to ambient free air-55-K/WTable 6.Isolation characteristics Symbol ParameterConditionsMin Typ Max Unit V isol(RMS)RMS isolation voltage50 Hz < f < 60 Hz; sinusoidal waveform; relative humidity < 65 %; clean and dust free; from all terminals to external heatsink --2500VC isolisolation capacitance from cathode to external heatsink; f = 1 MHz-10-pF7.CharacteristicsTable 7.Characteristics Symbol Parameter ConditionsMin Typ Max Unit Static characteristicsV F forward voltage I F =10A; T j =25°C; see Figure 4- 1.4 2.1V I F =10A; T j =150°C - 1.3 1.9V I Rreverse currentV R =600V; T j =100°C -0.7 1.5mA V R =600V; T j =25°C-1050µADynamic characteristics Q r recovered charge I F =1A; V R =30V;dI F /dt =100A/µs -1528nC t rr reverse recovery timeI F =1A; V R =30V;dI F /dt =100A/µs; T j =25°C;see Figure 5-2035ns I RM peak reverse recovery current I F =1A; V R =30V;dI F /dt =100A/µs; see Figure 5- 1.4 1.9A V FRforward recovery voltageI F =1A; dI F /dt =100A/µs; see Figure 6- 3.2-V8.Package outlinePlastic single-ended package; isolated heatsink mounted;1 mounting hole; 3-lead TO-220 'full pack'SOT186AFig 7.Package outline SOT186A (TO-220F)9.Revision historyTable 8.Revision historyDocument ID Release date Data sheet status Change notice Supersedes BYV410X-600_120090629Product data sheet--10.Legal information10.1Data sheet status[1]Please consult the most recently issued document before initiating or completing a design.[2]The term 'short data sheet' is explained in section "Definitions".[3]The product status of device(s) described in this document may have changed since this document was published and may differ in case of multiple devices. The latest product status information is available on the Internet at URL .10.2DefinitionsDraft — The document is a draft version only. The content is still under internal review and subject to formal approval, which may result in modifications or additions. NXP Semiconductors does not give any representations or warranties as to the accuracy or completeness ofinformation included herein and shall have no liability for the consequences of use of such information.Short data sheet — A short data sheet is an extract from a full data sheet with the same product type number(s) and title. A short data sheet is intended for quick reference only and should not be relied upon to contain detailed and full information. For detailed and full information see the relevant full data sheet, which is available on request via the local NXP Semiconductors sales office. In case of any inconsistency or conflict with the short data sheet, the full data sheet shall prevail.10.3DisclaimersGeneral — Information in this document is believed to be accurate andreliable. However, NXP Semiconductors does not give any representations or warranties, expressed or implied, as to the accuracy or completeness of such information and shall have no liability for the consequences of use of such information.Right to make changes — NXP Semiconductors reserves the right to make changes to information published in this document, including withoutlimitation specifications and product descriptions, at any time and without notice. This document supersedes and replaces all information supplied prior to the publication hereof.Suitability for use — NXP Semiconductors products are not designed, authorized or warranted to be suitable for use in medical, military, aircraft, space or life support equipment, nor in applications where failure ormalfunction of an NXP Semiconductors product can reasonably be expected to result in personal injury, death or severe property or environmentaldamage. NXP Semiconductors accepts no liability for inclusion and/or use of NXP Semiconductors products in such equipment or applications and therefore such inclusion and/or use is at the customer’s own risk.Applications — Applications that are described herein for any of these products are for illustrative purposes only. NXP Semiconductors makes no representation or warranty that such applications will be suitable for the specified use without further testing or modification.Quick reference data — The Quick reference data is an extract of theproduct data given in the Limiting values and Characteristics sections of this document, and as such is not complete, exhaustive or legally binding. Limiting values — Stress above one or more limiting values (as defined in the Absolute Maximum Ratings System of IEC 60134) may cause permanent damage to the device. Limiting values are stress ratings only and operation of the device at these or any other conditions above those given in theCharacteristics sections of this document is not implied. Exposure to limiting values for extended periods may affect device reliability.Terms and conditions of sale — NXP Semiconductors products are sold subject to the general terms and conditions of commercial sale, as published at /profile/terms , including those pertaining to warranty, intellectual property rights infringement and limitation of liability, unlessexplicitly otherwise agreed to in writing by NXP Semiconductors. In case of any inconsistency or conflict between information in this document and such terms and conditions, the latter will prevail.No offer to sell or license — Nothing in this document may be interpreted or construed as an offer to sell products that is open for acceptance or the grant, conveyance or implication of any license under any copyrights, patents or other industrial or intellectual property rights.Export control — This document as well as the item(s) described herein may be subject to export control regulations. Export might require a prior authorization from national authorities.10.4TrademarksNotice: All referenced brands, product names, service names and trademarks are the property of their respective owners.11.Contact informationFor more information, please visit: For sales office addresses, please send an email to: salesaddresses@Document status [1][2]Product status [3]DefinitionObjective [short] data sheet Development This document contains data from the objective specification for product development.Preliminary [short] data sheet Qualification This document contains data from the preliminary specification.Product [short] data sheetProductionThis document contains the product specification.12.Contents1Product profile. . . . . . . . . . . . . . . . . . . . . . . . . . .11.1General description . . . . . . . . . . . . . . . . . . . . . .11.2Features and benefits. . . . . . . . . . . . . . . . . . . . .11.3Applications . . . . . . . . . . . . . . . . . . . . . . . . . . . .11.4Quick reference data . . . . . . . . . . . . . . . . . . . . .12Pinning information. . . . . . . . . . . . . . . . . . . . . . .23Ordering information. . . . . . . . . . . . . . . . . . . . . .24Limiting values. . . . . . . . . . . . . . . . . . . . . . . . . . .25Thermal characteristics . . . . . . . . . . . . . . . . . . .46Isolation characteristics . . . . . . . . . . . . . . . . . . .47Characteristics. . . . . . . . . . . . . . . . . . . . . . . . . . .58Package outline. . . . . . . . . . . . . . . . . . . . . . . . . .79Revision history. . . . . . . . . . . . . . . . . . . . . . . . . .810Legal information. . . . . . . . . . . . . . . . . . . . . . . . .910.1Data sheet status . . . . . . . . . . . . . . . . . . . . . . . .910.2Definitions. . . . . . . . . . . . . . . . . . . . . . . . . . . . . .910.3Disclaimers. . . . . . . . . . . . . . . . . . . . . . . . . . . . .910.4Trademarks. . . . . . . . . . . . . . . . . . . . . . . . . . . . .911Contact information. . . . . . . . . . . . . . . . . . . . . . .9Please be aware that important notices concerning this document and the product(s)described herein, have been included in section ‘Legal information’.© NXP B.V.2009.All rights reserved.For more information, please visit: For sales office addresses, please send an email to: salesaddresses@分销商库存信息: NXPBYV410X-600,127。

MF-R015600-2, 规格书,Datasheet 资料