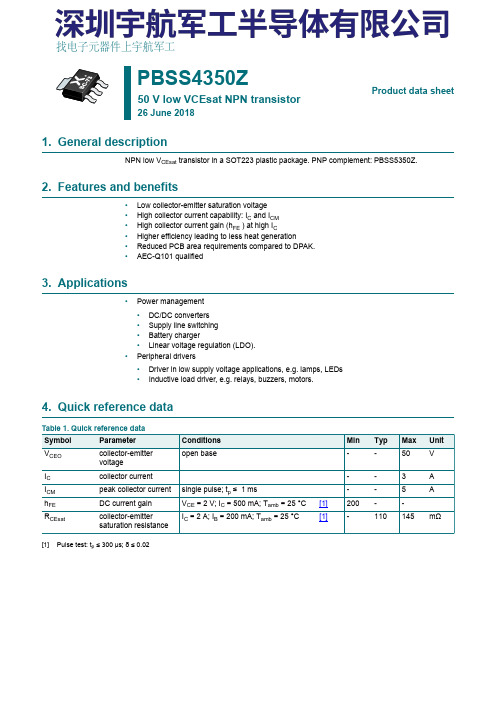

PBSS4350Z中文资料

HMC435MS8G_07中文资料

State Low High

Truth Table

Bias Condition* 0 Vdc @ 25 μA Typical +5 Vdc @ 25 μA Typical

Control Input

Signal Path State

ELECTROSTATIC SENSITIVE DEVICE

A

B

RFC to:

SWITCHES - SMT

9 - 256

Electrical Specifications, TA = +25° C, Vctl = 0/+5 Vdc, 50 Ohm System

Insertion Loss

Parameter

Isolation (RFC to RF1/RF2)

Return Loss (On State)Fra bibliotekUnits

dB dB dB

dB dB dB dB dB

dB dB dB

dB

dBm

dBm

ns ns

For price, delivery, and to place orders, please contact Hittite Microwave Corporation: 20 Alpha Road, Chelmsford, MA 01824 Phone: 978-250-3343 Fax: 978-250-3373 Order On-line at

+25 C

+85 C

56

-40 C

54

52

50

48

46

44

42

40 0 0.5 1 1.5 2 2.5 3 3.5 4

PBSS5350Z中文资料

Philips Semiconductors

Product specification

50 V low VCEsat PNP transistor

PBSS5350Z

handbook, halfpage

1000

MGW167

handbook, halfpage

− 1.2

MGW168

hFE 800

(1)

VBE (V) − 0.8

元器件交易网

DISCRETE SEMICONDUCTORS

DATA SHEET

handbook, halfpage

M3D087

PBSS5350Z 50 V low VCEsat PNP transistor

Product specification Supersedes data of 2003 Jan 20 2003 May 13

Fig.4

Collector-emitter saturation voltage as a function of collector current; typical values.

Fig.5

Base-emitter saturation voltage as a function of collector current; typical values.Leabharlann −1−10−102

−103 −104 I C (mA)

−1

−10

−102

−103 −104 I C (mA)

IC/IB = 10. (1) Tamb = 150 °C. (2) Tamb = 25 °C. (3) Tamb = −55 °C.

IC/IB = 10. (1) Tamb = −55 °C. (2) Tamb = 25 °C. (3) Tamb = 150 °C.

ADSP-21262SBBCZ150资料

aSHARC and the SHARC logo are registered trademarks of Analog Devices, Inc.SHARC®Embedded ProcessorADSP-21262Rev. BInformation furnished by Analog Devices is believed to be accurate and reliable. However, no responsibility is assumed by Analog Devices for its use, nor for anyinfringements of patents or other rights of third parties that may result from its use. Specifications subject to change without notice. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices. Trademarks and registered trademarks are the property of their respective owners.One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A. Tel: FAX: 781.461.3113 © 2005 Analog Devices, Inc. All rights reserved.SUMMARYHigh performance 32-bit/40-bit floating-point processor Code compatibility—at assembly level, uses the same instruction set as other SHARC DSPsSingle-instruction multiple-data (SIMD) computational archi-tecture—two 32-bit IEEE floating-point/32-bit fixed-point/ 40-bit extended precision floating-point computational units, each with a multiplier, ALU, shifter, and register file High bandwidth I/O—a parallel port, an SPI® port, six serial ports, a digital applications interface (DAI), and JTAGDAI incorporates two precision clock generators (PCGs), an input data port (IDP) that includes a parallel data acquisi-tion port (PDAP), and three programmable timers, all under software control by the signal routing unit (SRU) On-chip memory—2M bit of on-chip SRAM and a dedicated 4M bit of on-chip mask-programmable ROMThe ADSP-21262 is available in commercial and industrial temperature grades. For complete ordering information, see Ordering Guide on Page46.KEY FEATURESSerial ports offer left-justified sample-pair and I2S support via 12 programmable and simultaneous receive or trans-mit pins, which support up to 24 transmit or 24 receive I2S channels of audio when all six serial ports (SPORTs) are enabled or six full duplex TDM streams of up to 128 channels per frameAt 200 MHz (5 ns) core instruction rate, the ADSP-21262 operates at 1200 MFLOPS peak/800 MFLOPS sustained performance whether operating on fixed- or floating-point data400 MMACS sustained performance at 200 MHzSuper Harvard Architecture—three independent buses for dual data fetch, instruction fetch, and nonintrusive, zero-overhead I/OTransfers between memory and core at up to four 32-bit floating- or fixed-point words per cycle, sustained2.4G byte/s bandwidth at 200 MHz core instruction rate and 900M byte/sec is available via DMAFigure 1.Functional Block DiagramADSP-21262 ADDITIONAL KEY FEATURES2M bit on-chip dual-ported SRAM (1M bit block 0, 1M bit block 1) for simultaneous access by core processor and DMA4M bit on-chip dual-ported mask-programmable ROM(2M bit in block 0 and 2M bit in block 1)Dual data address generators (DAGs) with modulo and bit-reverse addressingZero-overhead looping with single-cycle loop setup, providing efficient program sequencingSingle-instruction multiple-data (SIMD) architecture provides:Two computational processing elementsConcurrent execution—each processing element executes the same instruction, but operates on different data Parallelism in buses and computational units allows single cycle executions (with or without SIMD) of a multiplyoperation; an ALU operation; a dual memory read orwrite; and an instruction fetchAccelerated FFT butterfly computation through a multiply with add and subtract instructionDMA controller supports:22 zero-overhead DMA channels for transfers between theADSP-21262 internal memory and serial ports (12), the input data port (IDP) (eight), the SPI-compatible port(one), and the parallel port (one)32-bit background DMA transfers at core clock speed, inparallel with full-speed processor executionJTAG background telemetry for enhanced emulation featuresIEEE 1149.1 JTAG standard test access port and on-chip emulationDual voltage: 3.3 V I/O, 1.2 V coreAvailable in 136-ball BGA and 144-lead LQFP packagesAlso available in lead-free packagesDigital applications interface includes six serial ports, two precision clock generators, an input data port, three pro-grammable timers, and a signal routing unit Asynchronous parallel/external port provides:Access to asynchronous external memory16 multiplexed address/data lines that can support 24-bitaddress external address range with 8-bit data or 16-bit address external address range with 16-bit data66M byte/sec transfer rate for 200 MHz core rate50M byte/sec transfer rate for 150 MHz core rate256 word page boundariesExternal memory access in a dedicated DMA channel8-bit to 32-bit and 16-bit to 32-bit word packing options Programmable wait state options: 2 to 31 CCLK Serial ports provide:Six dual data line serial ports that operate at up to50M bit/sec for a 200 MHz core and up to 37.5M bit/sec for a 150 MHz core on each data line—each has a clock, frame sync, and two data lines that can be configured as either a receiver or transmitter pairLeft-justified sample-pair and I2S support, programmable direction for up to 24 simultaneous receive or transmit channels using two I2S-compatible stereo devices perserial portTDM support for telecommunications interfaces including 128 TDM channel support for newer telephony inter-faces such as H.100/H.110Up to 12 TDM stream support, each with 128 channelsper frameCompanding selection on a per channel basis in TDM mode Input data port provides an additional input path to the SHARC core configurable as either eight channels of I2S or serial data or as seven channels plus a single 20-bit wide synchronous parallel data acquisition portSupports receive audio channel data in I2S, left-justifiedsample pair, or right-justified modeSignal routing unit (SRU) provides configurable and flexible connections between all DAI components, six serial ports, two precision clock generators, three timers, an input data port/parallel data acquisition port, 10 interrupts, six flag inputs, six flag outputs, and 20 SRU I/O pins (DAI_Px) Serial peripheral interface (SPI)Master or slave serial boot through SPIFull-duplex operationMaster-slave mode multimaster supportOpen drain outputsProgrammable baud rates, clock polarities, and phases3 Muxed Flag/IRQ lines1 Muxed Flag/Timer expired lineROM-based security features:JTAG access to memory permitted with a 64-bit key Protected memory regions that can be assigned to limitaccess under program control to sensitive codePLL has a wide variety of software and hardware multi-plier/divider ratiosRev. B|Page 2 of 48|August 2005ADSP-21262Rev. B |Page 3 of 48|August 2005TABLE OF CONTENTSGeneral Description ................................................. 4ADSP-21262 Family Core Architecture ...................... 4ADSP-21262 Memory and I/O Interface Features ......... 6Target Board JTAG Emulator Connector .................... 8Development Tools ............................................... 9Evaluation Kit ..................................................... 10Designing an Emulator-CompatibleDSP Board (Target) ........................................... 10Additional Information ......................................... 10Pin Function Descriptions ........................................ 11Address Data Pins as Flags ..................................... 14Core Instruction Rate to CLKIN Ratio Modes ............. 14Address Data Modes ............................................. 14ADSP-21262 Specifications ....................................... 15Recommended Operating Conditions ....................... 15Electrical Characteristics ........................................ 15Absolute Maximum Ratings ................................... 16ESD Sensitivity .................................................... 16Timing Specifications ........................................... 17Output Drive Currents .......................................... 38Test Conditions ................................................... 38Capacitive Loading ............................................... 38Environmental Conditions ..................................... 39Thermal Characteristics ........................................ 39136-Ball BGA Pin Configurations ............................... 41144-Lead LQFP Pin Configurations ............................. 44Package Dimensions ................................................ 45Ordering Guide (46)REVISION HISTORY8/05—Rev. A to Rev. BMiscellaneous Format Updates..........................Universal Changed “Digital Audio Interface” to “DigitalApplications Interface”........................................Global Deleted ROM-Based Security from Page 8Applied Corrections and Additional Information to:Summary ............................................................ 1Key Features ........................................................ 1Additional Key Features .......................................... 2General Description ............................................... 4ADSP-21262 Family Core Architecture ...................... 4Serial Ports .......................................................... 6Parallel Port ......................................................... 8Power Supplies ..................................................... 8Evaluation Kit .................................................... 10Pin Function Descriptions ..................................... 11Recommended Operating Conditions ...................... 15Clock Signals ...................................................... 19Precision Clock Generator (Direct Pin Routing) ......... 23Output Drive Currents ......................................... 38Capacitive Loading .............................................. 38Environmental Conditions .................................... 39Thermal Characteristics ........................................ 39Package Dimensions ............................................ 45Ordering Guide .. (46)ADSP-21262 GENERAL DESCRIPTIONThe ADSP-21262 SHARC DSP is a member of the SIMDSHARC family of DSPs featuring Analog Devices Super Har-vard Architecture. The ADSP-21262 is source code compatible with the ADSP-2126x, ADSP-21160, and ADSP-21161 DSPs as well as with first generation ADSP-2106x SHARC processors in SISD (single-instruction, single-data) mode. Like other SHARC DSPs, the ADSP-21262 is a 32-bit/40-bit floating-point proces-sor optimized for high performance signal processing applica-tions with its dual-ported on-chip SRAM, mask-programmable ROM, multiple internal buses to eliminate I/O bottlenecks, and an innovative digital applications interface.As shown in the Functional Block Diagram on Page 1, the ADSP-21262 uses two computational units to deliver a five to ten times performance increase over previous SHARC proces-sors on a range of DSP algorithms. Fabricated in a state-of-the-art, high speed, CMOS process, the ADSP-21262 DSP achieves an instruction cycle time of 5 ns at 200 MHz or 6.6 ns at 150 MHz. With its SIMD computational hardware, the ADSP-21262 can perform 1200MFLOPS running at 200 MHz or 900 MFLOPS running at 150 MHz.Table1 shows performance benchmarks for the ADSP-21262. The ADSP-21262 continues SHARC’s industry-leading stan-dards of integration for DSPs, combining a high performance 32-bit DSP core with integrated, on-chip system features. These features include 2M bit dual-ported SRAM memory, 4M bit dual-ported ROM, an I/O processor that supports 22 DMA channels, six serial ports, an SPI, external parallel bus, and digi-tal applications interface.The block diagram of the ADSP-21262 on Page1 illustrates the following architectural features:•Two processing elements, each containing an ALU, multi-plier, shifter, and data register file•Data address generators (DAG1, DAG2)•Program sequencer with instruction cache•PM and DM buses capable of supporting four 32-bit data transfers between memory and the core at every core pro-cessor cycle•Three programmable interval timers with PWM genera-tion, PWM capture/pulse width measurement, andexternal event counter capabilities•On-chip dual-ported SRAM (2M bit)•On-chip dual-ported, mask-programmable ROM(4M bit)•JTAG test access port•8- or 16-bit parallel port that supports interfaces to off-chip memory peripherals•DMA controller•Six full-duplex serial ports•SPI-compatible interface•Digital applications interface that includes two precisionclock generators (PCG), an input data port (IDP), six serial ports, eight serial interfaces, a 20-bit synchronous parallel input port, 10 interrupts, six flag outputs, six flag inputs,three programmable timers, and a flexible signal routingunit (SRU)Figure2 shows one sample configuration of a SPORT using the precision clock generator to interface with an I2S ADC and an I2S DAC with a much lower jitter clock than the serial port would generate itself. Many other SRU configurations are possible.ADSP-21262 FAMILY CORE ARCHITECTUREThe ADSP-21262 is code compatible at the assembly level with the ADSP-21266, ADSP-2136x, ADSP-2116x, and the first gen-eration ADSP-2106x SHARC DSPs. The ADSP-21262 shares architectural features with the ADSP-2126x, ADSP-2136x, and ADSP-2116x SIMD SHARC family of DSPs, as detailed in the following sections.SIMD Computational EngineThe ADSP-21262 contains two computational processing ele-ments that operate as a single-instruction multiple-data (SIMD) engine. The processing elements are referred to as PEX and PEY and each contains an ALU, multiplier, shifter, and register file. PEX is always active, and PEY may be enabled by setting the PEYEN mode bit in the MODE1 register. When this mode is enabled, the same instruction is executed in both processing ele-ments, but each processing element operates on different data. This architecture is efficient at executing math intensive DSP algorithms.Entering SIMD mode also has an effect on the way data is trans-ferred between memory and the processing elements. When in SIMD mode, twice the data bandwidth is required to sustain computational operation in the processing elements. Because of this requirement, entering SIMD mode also doubles the band-width between memory and the processing elements. When using the DAGs to transfer data in SIMD mode, two data values are transferred with each access of memory or the register file.Table 1.ADSP-21262 Benchmarks (at 200 MHz)Benchmark Algorithm Speed(at 200 MHz)1024 Point Complex FFT (Radix 4, with reversal)61.3 µsFIR Filter (per tap)11Assumes two files in multichannel SIMD mode.3.3 nsIIR Filter (per biquad)113.3 ns Matrix Multiply (pipelined)[3×3] × [3×1] [4×4] × [4×1]30 ns 53.3 nsDivide (y/×)20 nsInverse Square Root30 nsRev. B|Page 4 of 48|August 2005ADSP-21262Rev. B |Page 5 of 48|August 2005Independent, Parallel Computation UnitsWithin each processing element is a set of computational units. The computational units consist of an arithmetic/logic unit (ALU), multiplier, and shifter. These units perform all opera-tions in a single cycle. The three units within each processing element are arranged in parallel, maximizing computational throughput. Single multifunction instructions execute parallel ALU and multiplier operations. In SIMD mode, the parallel ALU and multiplier operations occur in both processing ele-ments. These computation units support IEEE 32-bit single precision floating-point, 40-bit extended precision floating-point, and 32-bit fixed-point data formats.Data Register FileA general-purpose data register file is contained in eachprocessing element. The register files transfer data between the computation units and the data buses, and store intermediate results. These 10-port, 32-register (16 primary, 16 secondary) register files, combined with the ADSP-2126x enhanced Har-vard architecture, allow unconstrained data flow between computation units and internal memory. The registers in PEX are referred to as R0–R15 and in PEY as S0–S15.Single-Cycle Fetch of Instruction and Four Operands The ADSP-21262 features an enhanced Harvard architecture in which the data memory (DM) bus transfers data and the pro-gram memory (PM) bus transfers both instructions and data (see Figure 1 on Page 1). With the ADSP-21262’s separate pro-gram and data memory buses and on-chip instruction cache, the processor can simultaneously fetch four operands (two over each data bus) and one instruction (from the cache), all in a single cycle.Instruction CacheThe ADSP-21262 includes an on-chip instruction cache that enables three-bus operation for fetching an instruction and four data values. The cache is selective—only the instructions whose fetches conflict with PM bus data accesses are cached. This cache allows full-speed execution of core, looped operations such as digital filter multiply-accumulates, and FFT butterfly processing.Data Address Generators with Zero-Overhead Hardware Circular Buffer SupportThe ADSP-21262’s two data address generators (DAGs) are used for indirect addressing and implementing circular data buffers in hardware. Circular buffers allow efficient program-ming of delay lines and other data structures required in digital signal processing, and are commonly used in digital filters andFigure 2.ADSP-21262 System Sample ConfigurationADSP-21262Fourier transforms. The two DAGs of the ADSP-21262 contain sufficient registers to allow the creation of up to 32 circular buff-ers (16 primary register sets, 16 secondary). The DAGs automatically handle address pointer wraparound, reduce over-head, increase performance, and simplify implementation. Circular buffers can start and end at any memory location. Flexible Instruction SetThe 48-bit instruction word accommodates a variety of parallel operations for concise programming. For example, theADSP-21262 can conditionally execute a multiply, an add, and a subtract in both processing elements while branching and fetch-ing up to four 32-bit values from memory—all in a single instruction.ADSP-21262 MEMORY AND I/O INTERFACE FEATURESThe ADSP-21262 adds the following architectural features to the SIMD SHARC family core:Dual-Ported On-Chip MemoryThe ADSP-21262 contains two megabits of internal SRAM and four megabits of internal mask-programmable ROM. Each block can be configured for different combinations of code and data storage (see memory map, Figure3). Each memory block is dual-ported for single-cycle, independent accesses by the core processor and I/O processor. The dual-ported memory, in com-bination with three separate on-chip buses, allows two data transfers from the core and one from the I/O processor, in a sin-gle cycle.The ADSP-21262’s SRAM can be configured as a maximum of 64K words of 32-bit data, 128K words of 16-bit data, 42K words of 48-bit instructions (or 40-bit data), or combinations of differ-ent word sizes up to two megabits. All of the memory can be accessed as 16-bit, 32-bit, 48-bit, or 64-bit words. A 16-bit float-ing-point storage format is supported that effectively doubles the amount of data that may be stored on-chip. Conversion between the 32-bit floating-point and 16-bit floating-point for-mats is performed in a single instruction. While each memory block can store combinations of code and data, accesses are most efficient when one block stores data using the DM bus for transfers, and the other block stores instructions and data using the PM bus for transfers.Using the DM bus and PM buses, with one dedicated to each memory block, assures single-cycle execution with two data transfers. In this case, the instruction must be available inthe cache.DMA ControllerThe ADSP-21262’s on-chip DMA controller allows zero-over-head data transfers without processor intervention. The DMA controller operates independently and invisibly to the processor core, allowing DMA operations to occur while the core is simul-taneously executing its program instructions. DMA transfers can occur between the ADSP-21262’s internal memory and its serial ports, the SPI-compatible (serial peripheral interface) port, the IDP (input data port), parallel data acquisition port (PDAP), or the parallel port. Twenty-two channels of DMA are available on the ADSP-21262—one for the SPI, 12 via the serial ports, eight via the input data port, and one via the processor’s parallel port. Programs can be downloaded to the ADSP-21262 using DMA transfers. Other DMA features include interrupt generation upon completion of DMA transfers, and DMA chaining for automatic linked DMA transfers.Digital Applications Interface (DAI)The digital applications interface provides the ability to connect various peripherals to any of the SHARC’s DAI pins(DAI_P20–1).Connections are made using the signal routing unit (SRU, shown in the block diagram on Page1).The SRU is a matrix routing unit (or group of multiplexers) that enables the peripherals provided by the DAI to be intercon-nected under software control. This allows easy use of the DAI associated peripherals for a much wider variety of applications by using a larger set of algorithms than is possible with noncon-figurable signal paths.The DAI also includes six serial ports, two precision clock gen-erators (PCGs), an input data port (IDP), six flag outputs and six flag inputs, and three timers. The IDP provides an additional input path to the ADSP-21262 core, configurable as either eight channels of I2S or serial data, or as seven channels plus a single 20-bit wide synchronous parallel data acquisition port. Each data channel has its own DMA channel that is independent from the ADSP-21262’s serial ports.For complete information on using the DAI, see theADSP-2126x SHARC DSP Peripherals Manual.Serial PortsThe ADSP-21262 features six full duplex synchronous serial ports that provide an inexpensive interface to a wide variety of digital and mixed-signal peripheral devices such as the Analog Devices AD183x family of audio codecs, ADCs, and DACs. The serial ports are made up of two data lines, a clock, and frame sync. The data lines can be programmed to either transmit or receive and each data line has its own dedicated DMA channel. Serial ports are enabled via 12 programmable and simultaneous receive or transmit pins that support up to 24 transmit or 24 receive channels of serial data when all six SPORTs are enabled, or six full duplex TDM streams of 128 channels per frame.The serial ports operate at up to one-quarter of the DSP core clock rate, providing each with a maximum data rate of50M bit/sec for a 200 MHz core and 37.5M bit/sec for a150MHz core. Serial port data can be automatically transferred to and from on-chip memory via a dedicated DMA. Each of the serial ports can work in conjunction with another serial port to provide TDM support. One SPORT provides two transmit sig-nals while the other SPORT provides the two receive signals. The frame sync and clock are shared.Serial ports operate in four modes:•Standard DSP serial mode•Multichannel(TDM)modeRev. B|Page 6 of 48|August 2005ADSP-21262Rev. B|Page 7 of 48|August 2005•I 2S mode•Left-justified sample pair modeLeft-justified sample pair mode is a mode where in each frame sync cycle two samples of data are transmitted/received—one sample on the high segment of the frame sync, the other on the low segment of the frame sync. Programs have control over var-ious attributes of this mode.Each of the serial ports supports the left-justified sample pair and I 2S protocols (I 2S is an industry-standard interface com-monly used by audio codecs, ADCs, and DACs), with two data pins, allowing four left-justified sample pair or I 2S channels (using two stereo devices) per serial port, with a maximum of upto 24 audio channels. The serial ports permit little-endian or big-endian transmission formats and word lengths selectable from 3 bits to 32 bits. For the left-justified sample pair and I 2S modes, data-word lengths are selectable between 8 bits and 32 bits. Serial ports offer selectable synchronization and transmit modes as well as optional µ-law or A-law companding selection on a per channel basis. Serial port clocks and frame syncs can be internally or externally generated.Serial Peripheral (Compatible) InterfaceSerial peripheral interface is an industry-standard synchronous serial link, enabling the ADSP-21262 SPI-compatible port to communicate with other SPI-compatible devices. SPI is anFigure 3.ADSP-21262 Memory MapADSP-21262interface consisting of two data pins, one device select pin, and one clock pin. It is a full-duplex synchronous serial interface, supporting both master and slave modes. The SPI port can operate in a multimaster environment by interfacing with up to four other SPI-compatible devices, either acting as a master or slave device. The ADSP-21262 SPI-compatible peripheral implementation also features programmable baud rates up to 37.5 MHz, clock phases, and polarities. The ADSP-21262 SPI-compatible port uses open drain drivers to support a multimas-ter configuration and to avoid data contention.Parallel PortThe parallel port provides interfaces to SRAM and peripheral devices. The multiplexed address and data pins (AD15–0) can access 8-bit devices with up to 24 bits of address, or 16-bit devices with up to 16 bits of address. In either mode, 8- or 16-bit, the maximum data transfer rate is one-third the core clock speed. As an example, a clock rate of 200 MHz is equivalent to 66M byte/sec, and a clock rate of 150 MHz is equivalent to50M byte/sec.DMA transfers are used to move data to and from internal memory. Access to the core is also facilitated through the paral-lel port register read/write functions. The RD, WR, and ALE (address latch enable) pins are the control pins for the parallel port.TimersThe ADSP-21262 has a total of four timers: a core timer able to generate periodic software interrupts, and three general-pur-pose timers that can generate periodic interrupts and be independently set to operate in one of three modes:•Pulse waveform generation mode•Pulse width count/capture mode•External event watchdog modeThe core timer can be configured to use FLAG3 as a timer expired output signal, and each general-purpose timer has one bidirectional pin and four registers that implement its mode of operation: a 6-bit configuration register, a 32-bit count register, a 32-bit period register, and a 32-bit pulse width register. A sin-gle control and status register enables or disables all three general-purpose timers independently.Program BootingThe internal memory of the ADSP-21262 boots at system power-up from an 8-bit EPROM via the parallel port, an SPI master, an SPI slave, or an internal boot. Booting is determined by the boot configuration (BOOTCFG1–0) pins. Selection of the boot source is controlled via the SPI as either a master or slave device, or it can immediately begin executing from ROM. Phase-Locked LoopThe ADSP-21262 uses an on-chip phase-locked loop (PLL) to generate the internal clock for the core. On power-up, the CLKCFG1-0 pins are used to select ratios of 16:1, 8:1, and 3:1. After booting, numerous other ratios can be selected via soft-ware control. The ratios are made up of software configurable numerator values from 1 to 32 and software configurable divi-sor values of 1, 2, 4, 8, and 16.Power SuppliesThe ADSP-21262 has separate power supply connections for the internal (V DDINT), external (V DDEXT), and analog (A VDD/A VSS) power supplies. The internal and analog supplies must meet the 1.2 V requirement. The external supply must meet the 3.3 V requirement. All external supply pins must be connected to the same power supply.Note that the analog supply pin (A VDD) powers the processor’s internal clock generator PLL. To produce a stable clock, it is rec-ommended that PCB designs use an external filter circuit for the A VDD pin. Place the filter components as close as possible to the A VDD/A VSS pins. For an example circuit, see Figure4. (A recom-mended ferrite chip is the muRata BLM18AG102SN1D). To reduce noise coupling, the PCB should use a parallel pair of power and ground planes for V DDINT and GND. Use wide traces to connect the bypass capacitors to the analog power (A VDD) and ground (A VSS) pins. Note that the A VDD and A VSS pins specified in Figure4 are inputs to the processor and not the analog ground plane on the board—the A VSS pin should connect directly to digital ground (GND) at the chip.TARGET BOARD JTAG EMULATOR CONNECTOR Analog Devices DSP Tools product line of JTAG emulators uses the IEEE 1149.1 JTAG test access port of the ADSP-21262 pro-cessor to monitor and control the target board processor during emulation. Analog Devices DSP Tools product line of JTAG emulators provides emulation at full processor speed, allowing inspection and modification of memory, registers, and proces-sor stacks. The processor’s JTAG interface ensures that the emulator will not affect target system loading or timing.For complete information on Analog Devices’ SHARC DSP Tools product line of JTAG emulator operation, see the appro-priate emulator hardware user’s guide.Figure 4.Analog Power Filter CircuitRev. B|Page 8 of 48|August 2005。

PBSS4350Z中文规格书

Package

Name

PBSS4350Z

SC-73

Description

plastic surface-mounted package with increased heatsink; 4 leads

Version SOT223

7. Marking

Table 4. Marking codes Type number PBSS4350Z

2 / 12

Nexperia

PBSS4350Z

50 V low VCEsat NPN transistor

12. Soldering

1.3 1.2 (4×) (4×)

7 3.85 3.6 3.5

0.3

4

3.9 6.1 7.65

1

2

3

2.3

2.3

1.2 (3×)

1.3 (3×)

6.15

Fig. 9. Reflow soldering footprint for SC-73 (SOT223)

8.9

6.7

1.9 4

6.2

8.7

1

2

3

1.9 (3×)

2.7

2.7

1.1

1.9 (2×)

Fig. 10. Wave soldering footprint for SC-73 (SOT223)

solder lands solder resist solder paste occupied area Dimensions in mm

4. Quick reference data

Table 1. Quick reference data

Symbol

Parameter

PBSS4140T中文资料

MLD662

102 handbook, halfpage RCEsat (Ω)

MLD663

102

10

(2)

(3) (1) (2)

10

1

(3)

1

1

10

102

103

IC (mA)

104

10−1 10−1

1

10

10−2

10−3 10−4 IC (mA)

IC/IB = 10. (1) Tamb = 150 °C. (2) Tamb = 25 °C. (3) Tamb = −55 °C.

DISCRETE SEMICONDUCTORS

DATA SHEET

PBSS4140T 40 V, 1A NPN low VCEsat (BISS) transistor

Product specification Supersedes data of 2001 Jul 13 2004 Mar 16

Philips Semiconductors

Product specification

40 V, 1A NPN low VCEsat (BISS) transistor

FEATURES • Low collector-emitter saturation voltage • High current capabilities. • Improved device reliability due to reduced heat generation. APPLICATIONS • General purpose switching and muting • LCD backlighting • Supply line switching circuits • Battery driven equipment (mobile phones, video cameras and hand-held devices). DESCRIPTION NPN low VCEsat transistor in a SOT23 plastic package. PNP complement: PBSS5140T. MARKING TYPE NUMBER PBSS4140T Note 1. * = p: made in Hong Kong. * = t: made in Malaysia. * = W: made in China. ORDERING INFORMATION TYPE NUMBER PBSS4140T PACKAGE NAME − DESCRIPTION plastic surface mounted package; 3 leads MARKING CODE(1) ZT*

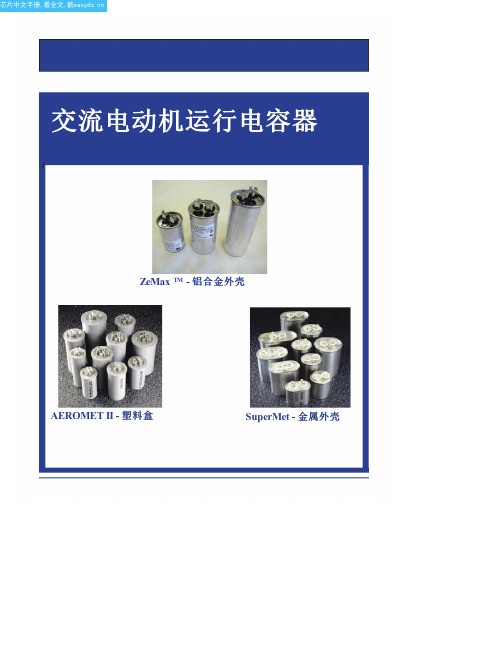

Z64S4440M中文资料(Aerovox)中文数据手册「EasyDatasheet - 矽搜」

交流电动机运行电容器

ZeMax TM - 铝合金外壳

AEROMET II - 塑料盒

SuperMet - 金属外壳

芯片中文手册,看全文,戳

目录

AEROMET II规格(系列M型).......................................... .................................... 3 SuperMet & ZeMax TM 规格(系列Z型)............................................ .................. 4 部分编号系统.............................................................................................................五 AEROMET II评分表(单台容量)系列M型....................................... ........... 6 AEROMET II评分表(双功能)系列型号M ....................................... ............. 8 SuperMet评分表(单台容量)系列Z型........................................ ............... 9 SuperMet评分表(双容量)系列Z型........................................ .............. 11 ZeMax TM 评分表(单台容量)系列Z型......................................... ........... 13 AEROMET II机械尺寸.............................................. .......................................... 15 SuperMet机械尺寸............................................... ........................................... 16 ZeMax TM 机械Dimensions............................................................................................17 附件 - 安装硬件.............................................. ............................................ 18

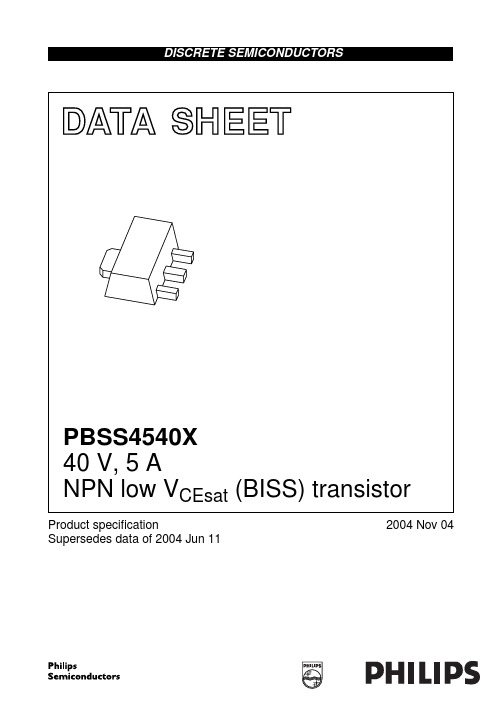

PBSS4540X中文资料

Fig.2 Power derating curves.

2004 Nov 04

4

Philips Semiconductors

Product specification

40 V, 5 A NPN low VCEsat (BISS) transistor

THERMAL CHARACTERISTICS SYMBOL Rth(j-a) PARAMETER from junction to ambient in free air notes 1 and 2 note 2 note 3 note 4 note 5 Rth(j-s) Notes 1. Operated under pulsed conditions; pulse width tp ≤ 10 ms; duty cycle δ ≤ 0.2. from junction to soldering point CONDITIONS

Philips Semiconductors

Product specification

40 V, 5 A NPN low VCEsat (BISS) transistor

FEATURES • High hFE and low VCEsat at high current operation • High collector current capability: IC maximum 4 A • High efficiency leading to less heat generation. APPLICATIONS • Medium power peripheral drivers (e.g. fan and motor) • Strobe flash units for DSC and mobile phones • Inverter applications (e.g. TFT displays) • Power switch for LAN and ADSL systems • Medium power DC-to-DC conversion • Battery chargers. DESCRIPTION NPN low VCEsat transistor in a medium power SOT89 (SC-62) package. PNP complement: PBSS5540X. MARKING TYPE NUMBER PBSS4540X Note 1. * = p: made in Hong Kong. * = t: made in Malaysia. * = W: made in China. ORDERING INFORMATION PACKAGE TYPE NUMBER NAME PBSS4540X SC-62 DESCRIPTION MARKING CODE(1) *1B

ADF4351中文资料代替4350

概述

ADF4351结合外部环路滤波器和外部参考频率使用时,可 实现小数N分频或整数N分频锁相环(PLL)频率合成器。

ADF4351具有一个集成电压控制振荡器(VCO),其基波输 出频率范围为2200 MHz至4400 MHz。此外,利用1/2/4/8/ 16/32/64分频电路,用户可以产生低至35 MHz的RF输出频 率。对于要求隔离的应用,RF输出级可以实现静音。静音 功能既可以通过引脚控制,也可以通过软件控制。同时提 供辅助RF输出,且不用时可以关断。

RFOUTA+ RFOUTA– PDBRF RFOUTB+ RFOUTB–

MULTIPLEXER

09800-001

MULTIPLEXER

ADF4351

CE

AGND

DGND

CPGND

SDGND AGNDVCO

图1.

Rev. 0

Information furnished by Analog Devices is believed to be accurate and reliable. However, no responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other rightsofthirdpartiesthatmayresultfromitsuse.Speci cationssubjecttochangewithoutnotice.No license is granted by implication or otherwise under any patent or patent rights of Analog Devices. Trademarks and registered trademarks are the property of their respective owners.

PBSS5350T,215;中文规格书,Datasheet资料

Product data sheet Supersedes data of 2002 Aug 082004 Jan 09DISCRETE SEMICONDUCTORS50 V; 3 A NPN low V CEsat(BISS) transistorPBSS4350TFEATURES•Low collector-emitter saturation voltage V CEsat and corresponding low R CEsat•High collector current capability•High collector current gain•Improved efficiency due to reduced heat generation.APPLICATIONS•Power management applications•Low and medium power DC/DC convertors •Supply line switching•Battery chargers•Linear voltage regulation with low voltage drop-out (LDO).DESCRIPTIONNPN low V CEsat transistor in a SOT23 plastic package. PNP complement: PBSS5350T.MARKINGNote1.* = p: Made in Hong Kong.* = t: Made in Malaysia.* = W: Made in China.QUICK REFERENCE DATA PINNINGTYPE NUMBER MARKING CODE(1) PBSS4350T ZC*SYMBOL PARAMETER MAX.UNIT V CEO collector-emitter voltage50VI C collector current (DC)2AI CRP repetitive peak collectorcurrent3AR CEsat equivalent on-resistance130mΩPIN DESCRIPTION1base2emitter3collectorORDERING INFORMATIONTYPE NUMBERPACKAGENAME DESCRIPTION VERSIONPBSS4350T−plastic surface mounted package; 3 leads SOT2350 V; 3 A NPN low V CEsat (BISS) transistorPBSS4350TLIMITING VALUESIn accordance with the Absolute Maximum Rating System (IEC 60134).Notes1.Operated under pulsed conditions: pulse width t p ≤ 100 ms; duty cycle δ ≤ 0.25.2.Device mounted on a printed-circuit board; single sided copper; tinplated; standard footprint.3.Device mounted on a printed-circuit board; single sided copper; tinplated; mounting pad for collector 1 cm 2.4.Device mounted on a printed-circuit board; single sided copper; tinplated; mounting pad for collector 6 cm 2.THERMAL CHARACTERISTICS Notes1.Device mounted on a printed-circuit board; single sided copper; tinplated; standard footprint.2.Device mounted on a printed-circuit board; single sided copper; tinplated; mounting pad for collector 1 cm 2.3.Device mounted on a printed-circuit board; single sided copper; tinplated; mounting pad for collector 6 cm 2.4.Operated under pulsed conditions: pulse width t p ≤ 100 ms; duty cycle δ ≤ 0.25.SYMBOL PARAMETERCONDITIONSMIN.MAX.UNITV CBO collector-base voltage open emitter −50V V CEO collector-emitter voltage open base −50V V EBO emitter-base voltage open collector−5V I C collector current (DC)−2A I CRP repetitive peak collector current note 1−3A I CM peak collector current single peak−5A I B base current (DC)−0.5AP tottotal power dissipationT amb ≤ 25 °C; note 2−300mW T amb ≤ 25 °C; note 3−480mW T amb ≤ 25 °C; note 4−540mW T amb ≤ 25 °C; notes 1 and 2− 1.2W T stg storage temperature −65+150°C T j junction temperature−150°C T amb operating ambient temperature−65+150°CSYMBOL PARAMETERCONDITIONSVALUE UNIT R th(j-a)thermal resistance from junction to ambientin free air; note 1417K/W in free air; note 2260K/W in free air; note 3230K/W in free air; notes 1 and 4104K/W50 V; 3 A NPN low V CEsat (BISS) transistorPBSS4350TCHARACTERISTICST amb = 25 °C unless otherwise specified.Note1.Pulse test: t p ≤ 300 μs; δ ≤ 0.02.SYMBOL PARAMETERCONDITIONSMIN.TYP.MAX.UNIT I CBO collector-base cut-off current I E = 0; V CB = 50 V−−100nA I E = 0; V CB = 50 V; T j = 150 °C−−50μA I EBO emitter-base cut-off current I C = 0; V EB = 5 V −−100nAh FEDC current gainI C = 100 mA; V CE = 2 V 300−−I C = 500 mA; V CE = 2 V 300−−I C = 1 A; V CE = 2 V; note 1300−−I C = 2 A; V CE = 2 V; note 1200−−I C = 3 A; V CE = 2 V; note 1100−−V CEsatcollector-emitter saturation voltageI C = 500 mA; I B = 50 mA −−80mV I C = 1 A; I B = 50 mA −−160mV I C = 2 A; I B = 100 mA; note 1−−280mV I C = 2 A; I B = 200 mA; note 1−−260mV I C = 3 A; I B = 300 mA; note 1−−370mV R CEsat equivalent on-resistance I C = 2 A; I B = 200 mA; note 1−100130m ΩV BEsat base-emitter saturation voltageI C = 2 A; I B = 100 mA; note 1−− 1.1V I C = 3 A; I B = 300 mA; note 1−− 1.2V V BEon base-emitter turn-on voltage I C = 1 A; V CE = 2 V; note 1 1.2−−V f T transition frequency I C = 100 mA; V CE = 5 V; f = 100 MHz100−−MHz C c collector capacitanceI E = I e = 0; V CB = 10 V; f = 1 MHz−−25pF50 V; 3 A NPN low V CEsat (BISS) transistor PBSS4350T50 V; 3 A NPN low V CEsat (BISS) transistor PBSS4350T50 V; 3 A NPN low V CEsat (BISS) transistor PBSS4350T50 V; 3 A NPN low V CEsat (BISS) transistor PBSS4350T PACKAGE OUTLINE50 V; 3 A NPN low V CEsat (BISS) transistorPBSS4350TDATA SHEET STATUSNotes1.Please consult the most recently issued document before initiating or completing a design.2.The product status of device(s) described in this document may have changed since this document was publishedand may differ in case of multiple devices. The latest product status information is available on the Internet at URL . DOCUMENT STATUS (1)PRODUCT STATUS (2)DEFINITIONObjective data sheet Development This document contains data from the objective specification for product development.Preliminary data sheet Qualification This document contains data from the preliminary specification. Product data sheet ProductionThis document contains the product specification.DISCLAIMERSGeneral ⎯ Information in this document is believed to be accurate and reliable. However, NXP Semiconductors does not give any representations or warranties,expressed or implied, as to the accuracy or completeness of such information and shall have no liability for the consequences of use of such information.Right to make changes ⎯ NXP Semiconductors reserves the right to make changes to informationpublished in this document, including without limitation specifications and product descriptions, at any time and without notice. This document supersedes and replaces all information supplied prior to the publication hereof.Suitability for use ⎯ NXP Semiconductors products are not designed, authorized or warranted to be suitable for use in medical, military, aircraft, space or life support equipment, nor in applications where failure or malfunction of an NXP Semiconductors product can reasonably be expected to result in personal injury, death or severe property or environmental damage. NXP Semiconductors accepts no liability for inclusion and/or use of NXP Semiconductors products in such equipment orapplications and therefore such inclusion and/or use is at the customer’s own risk.Applications ⎯ Applications that are described herein for any of these products are for illustrative purposes only. NXP Semiconductors makes no representation or warranty that such applications will be suitable for the specified use without further testing or modification.Limiting values ⎯ Stress above one or more limiting values (as defined in the Absolute Maximum Ratings System of IEC 60134) may cause permanent damage to the device. Limiting values are stress ratings only and operation of the device at these or any other conditions above those given in the Characteristics sections of this document is not implied. Exposure to limiting values for extended periods may affect device reliability.Terms and conditions of sale ⎯ NXP Semiconductors products are sold subject to the general terms and conditions of commercial sale, as published at /profile/terms, including those pertaining to warranty, intellectual property rightsinfringement and limitation of liability, unless explicitly otherwise agreed to in writing by NXP Semiconductors. In case of any inconsistency or conflict between information in this document and such terms and conditions, the latter will prevail.No offer to sell or license ⎯ Nothing in this document may be interpreted or construed as an offer to sell products that is open for acceptance or the grant, conveyance or implication of any license under any copyrights, patents or other industrial or intellectual property rights.Export control ⎯ This document as well as the item(s) described herein may be subject to export controlregulations. Export might require a prior authorization from national authorities.Quick reference data ⎯ The Quick reference data is an extract of the product data given in the Limiting values and Characteristics sections of this document, and as such is not complete, exhaustive or legally binding.NXP SemiconductorsCustomer notificationThis data sheet was changed to reflect the new company name NXP Semiconductors, including new legal definitions and disclaimers. No changes were made to the technical content, except for package outlinedrawings which were updated to the latest version.Contact informationFor additional information please visit: For sales offices addresses send e-mail to: salesaddresses@© NXP B.V. 2009All rights are reserved. Reproduction in whole or in part is prohibited without the prior written consent of the copyright owner.The information presented in this document does not form part of any quotation or contract, is believed to be accurate and reliable and may be changed without notice. No liability will be accepted by the publisher for any consequence of its use. Publication thereof does not convey nor imply any license under patent- or other industrial or intellectual property rights.Printed in The Netherlands R75/02/pp10 Date of release: 2004 Jan 09 Document order number: 9397 750 12437分销商库存信息: NXPPBSS5350T,215。

零件喷漆性能要求

GM4350 零件喷漆性能要求1.范围1.1材料描述:这个标准包括实验室对喷漆的各种等级的检测要求,通常用于汽车零部件表面喷漆。

这个标准不包括表面要求和加工参数(不包括:3.1.1部分),而在材料规格(998XXXX)里面有规定,并且不包括电泳后用于连接真空堆积金属涂料和热处理涂料。

对电泳塑料件的化学成分,表面处理和喷漆都应该按照通用批准的零件表面处理要求(APOPS),当对电泳做测试的时候,至少要对3个样品进行检测,从每一个零件中获得不同的数据。

来自装配车间的初始和最终电泳零件必须能够接受规定的高层表面电泳要求和符合所有的检测要求和标准1.2特殊运用以下几个例子表明了一些过去使用的等级标准和现在使用的标准。

咨询你们的材料工程师,请求帮助指出适用的等级。

特殊运用等级如下:A336-xxx*. 通常用于汽车底盘&外观零件腐蚀,例如:没有电镀的冷扎钢,预涂层钢,压铸锌、铝、镁。

有时用在金属引擎零件上。

A96. 以前用于汽车外观的零件都在明亮的表面上喷漆就像不锈钢,阳极电镀的铝,镀铬金属或塑胶件。

但值得注意的是在明亮的表面上镀上去的漆通常不能保持太久,所以通过了A96的要求并不能保证满足这方面的性能要求。

因此,指定在明亮的底层镀漆是不可取的。

A0. 通常用在汽车外观的零件上,包括塑料件和其它非金属物质.C96-xxx*. 通常用在汽车尾部行李箱的一些可看得见的金属零件和一些暴露在潮湿空气中的零件.C24.通常用在汽车内部的不易暴露在潮湿空气中的金属件.C0.通常用在汽车内部的塑料件和其它非金属件.注:xxx*关于检验等级,在表格4里面有标明.1.3备注1.3.1这里的检验规范用于定期质量管理(第3部分)和电泳过程(第3部分和附录A).附加的检测要求必须在等级编码后面加Z后缀,并且附加的检测要求必须在技术图纸上或材料规格上说明.在表1里面进行举例说明.表格1:加“Z”字尾的例子在有后缀Z的所有等级里面,相近材料的兼容性检测要求必须在技术图纸上说明。

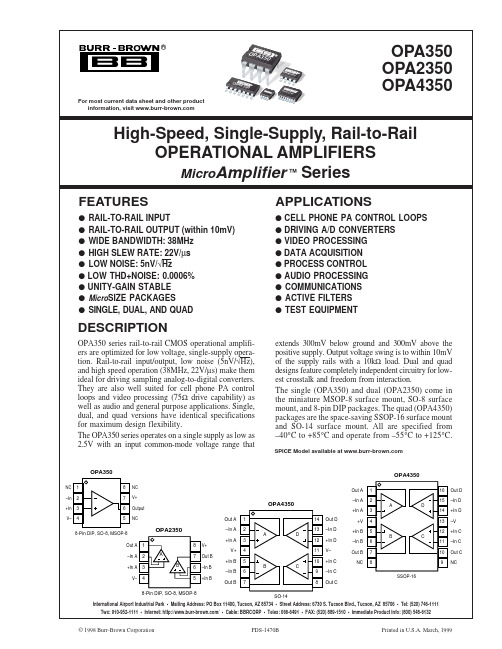

OPA4350UA中文资料

SO-14

International Airport Industrial Park • Mailing Address: PO Box 11400, Tucson, AZ 85734 • Street Address: 6730 S. Tucson Blvd., Tucson, AZ 85706 • Tel: (520) 746-1111

TA = –40°C to +85°C IO = 0 IO = 0

±150

±4 40

0.15

±500 ±1

150 175

±0.5

±10

See Typical Performance Curve

±0.5

±10

4 7 5 4

–0.1

(V+)+0.1

66

84

76

90

74

1013 || 2.5 1013 || 6.5

100

122

100

100

120

100

38 22 0.22 0.5 0.1 0.0006 0.17 0.17

TA = –40°C to +85°C

TA = –40°C to +85°C Output Current Short-Circuit Current Capacitive Load Drive

POWER SUPPLY Operating Voltage Range Minimum Operating Voltage Quiescent Current (per amplifier)

High-Speed, Single-Supply, Rail-to-Rail OPERATIONAL AMPLIFIERS MicroAmplifier ™ Series

FUJI XEROX DocuPrint C4350打印机 说明书

本小册子中提及的其他名称都是相应公司的商标。

尽管所载信息在打印时正确无误,富士施乐亚太区保留随时更改所述机器规格参数而不另外通知的权利。

视产品购买所在国家或地区,规格参数、选件名称和供货情况可能会不尽相同。

“xerox”及连接的球体图形是施乐公司在美国和/或其它国家的标识或注册商标。

FXCL 1003富士施乐在华分支机构富士施乐全国服务热线:800-820-5146 400-820-5146/北京 北京市朝阳区建国路甲92号世茂大厦904室 电话:010-********上海 上海市卢湾区淮海中路300号香港新世界大厦29F/30F/32F 电话:021-********广州 广州市东风中路410-412号时代地产中心15楼 电话:020-********成都 成都市锦江区滨江东路9号B 座香格里拉中心写字楼6层 电话:028-********沈阳 沈阳市和平区和平南大街2号东宇大厦1305、1306室 电话:024-********哈尔滨 哈尔滨市南岗区民益街76号网通广场20楼 电话:0451-********杭州 杭州市江干区杭海路238号森禾商务广场A 座1903室、1904室 电话:0571-********武汉 武汉市建设大道568号新世界国贸大厦I 座21层2105-2107室 电话:027-********长沙 长沙市芙蓉区燕山路鸿飞大厦1202、1209号 电话:0731-********郑州 郑州市中原中路220号裕达国际贸易中心A 座22层2212 电话:0371-********南京 南京市汉中路89号金鹰国际商城21层B2-C1座 电话:025-********福州 福州市五四路国贸广场29层C1 电话:0591-********西安 西安市南关正街88号长安国际广场B 座1006室 电话:029-********DocuPrintC4350DocuPrint C4350彩色激光打印机实力超群,技高一筹,非同寻常的打印机功能,提供完善的公司内部打印和装订解决方案DocuPrint C4350彩色激光打印机规格参数规格打印速度预热时间首页输出时间最大月打印负荷输出分辨率色阶纸张尺寸介纸类型介纸输入容量介纸输出容量双面功能处理器内存容量内置硬盘PDL(页面描述语言)支持的操作系统接口网络协议电源运行噪音功耗尺寸重量服务彩色:35页/分 双面打印时28面/分黑白:45页/分 双面打印时36面/分<45秒(连接电源时,室温20˚C)彩色:<9.7秒 黑白:<6.9秒150,000页/月标准、高质量:600dpi x 600dpi ,高分辨率:1200dpi x 1200dpi 图像增强各色256色阶 (1670万色)标准纸盘:A3, B4, A4, B5, A5, 11 x 17", 8.5 x 14", 8.5 x 13", 8.5 x 11", 8 x 10", 5.5 x 8.5", 八开, 十六开,用户自定义纸张(宽140~297mm x 长148~432mm)选配件:纸盘1/纸盘3:A3, B4, A4, B5, A5, 11 x 17", 8.5 x 14", 8.5 x 13", 8.5 x 11", 8 x 10", 5.5 x 8.5", 八开,十六开,自定义尺寸(宽148~297mm x 长210~432mm) 大容量纸盘2:A3, B4, A4, B5, A5, 11 x 17", 8.5 x 14", 8.5 x 13", 8.5 x 11", 8 x 10", 5.5 x 8.5", 八开,十六开,自定义尺寸(宽148~297mm x 长210~432mm) 大容量纸盘3/4:A4, 8.5 x 11", B5旁路纸盘:A3, B4, A4, B5, A5, A6, 11 x 17", 8.5 x 14", 8.5 x 13", 8.5 x 11", 8 x 10", 5.5 x 8.5", 八开,十六开,12 x 18", 12 x 19", 12.6 x 17.7"(SRA3),官制明信片,定制信封(长形3号),用户自定义纸张(宽100~305mm x 长140~1,200mm)双面打印:A3, B4, A4, B5, A5, 11 x 17", 8.5 x 14", 8.5 x 13", 8.5 x 11", 8 x 10", 5.5 x 8.5", 八开, 十六开,自定义尺寸(宽140~297mm x 长148~432mm)标准纸盘:普通纸/再生纸(64~98g/m 2)、薄纸(55~63g/m 2)、厚纸1 (99~169g/m 2)、 涂布纸1 (99~169g/m 2)、标签(99~169g/m 2)、OHP 透明胶片选配纸盘:纸盘1/纸盘3/大容量纸盘:普通纸/再生纸(64~98g/m 2)、薄纸(55~63g/m 2)、 厚纸1 (99~169g/m 2)、涂布纸1 (99~169g/m 2)、标签纸(99~169g/m 2)、 OHP 透明胶片旁路纸盘:普通纸/再生纸(64~98g/m 2)、薄纸(55~63g/m 2)、厚纸1 (99~169g/m 2)、 厚纸2 (170~220g/m 2)、涂布纸1 (99~169g/m 2)、标签 (99~169g/m 2)、 OHP 透明胶片、明信片、信封双面打印:普通纸/再生纸(64~98g/m 2)、厚纸1 (99~169g/m 2)、涂布纸1 (99~169g/m 2)标准:标准纸盘:500张;手动纸盘:100张选配纸盘:纸盘1:500张(500张 x 1路)、纸盘3:1,500张(500张 x 3路)、 大容量纸盘:2,520张(500 张+875张+1,145张)标准:400 张(正面朝下)选配件:装订器:2,000 张(正面朝下)、旁路纸盘:200 张标准PowerPC G3-600MHz标准:256MB 、内存插槽2个(1个空置)选配件:256MB 、512MB 加装内存(最大768MB)选配件:40GB标准:PostSoript Level 3、PCL5、PCL6、ESC/P :欧文81字体、PS3:欧文136字体、PDF 、 TIFF 、HPGL 、HPGL2、ESCP/K 选配件:PS3:日语2字体(平成)Windows ® 95/98/98SE/Me 、Windows NT ® 4.0、Windows ® 2000、Windows ® XP 、Windows Server ® 2003、Mac OS ® X ,LinuxEthernet 100BASE-TX/10BASE-T 、双向并口(IEEE1284标准)、USB1.1、USB2.0(High Speed)TCP/IP(lpd 、SMB 、Port9100、IPP)、IPX/SPX(NetWare ®)、EtherTalk ®AC220-240V±10%、10A 、50/60Hz 共用启动时:(仅本体)7.0B ,53dB(A)以下,待机时:(仅本体) 4.9B ,32dB(A)以下最大:1,320W ;睡眠模式时:8W ;平均:待机时247W ,启动时855W 632宽 x 717深 x 493高 mm 91kg (含随机耗材)2年上门服务EC100641EC100642EC100643EC100645EC100646EC100647EC100648EC100649EC100650EC100651EC100652选配件购买信息550页A3/A4通用进纸盒1650页A3/A4通用进纸盒2520页进纸盒(2个A4加一个A3纸盒)40GB 内置硬盘256MB 内存512MB 内存正面朝上接收盘日文字库条(HEISEI)中文字库条(PCL 字库) 长条幅纸盘专业完成装订器打印机耗材防伪标签说明富士施乐打印机耗材包装上采用新型激光防伪技术和数码查询系统,没有标贴的可能为非原装耗材。

OZ964S中文资料

ORDERING INFORMATION

Part Number OZ964S OZ964SN OZ964IS OZ964ISN OZ964G OZ964GN OZ964IG OZ964IGN OZ964D OZ964DN Temp Range

0° C to 70° C 0° C to 70° C -40° C to +85°C -40° C to +85°C 0° C to 70° C 0° C to 70° C -40° C to +85°C -40° C to +85°C 0° C to 70° C 0° C to 70° C

元器件交易网

OZ964

Change Summary

Controlled Recipient #101461 printed on 10/25/2004. Updates will be provided to registered recipients.

CHANGES

No. 1 2 3 4 5 6 7 Applicable Section Title Ordering Information General Description Functional Block Diagram Description Reference Application Circuit Package information Throughout data sheet Description Change the title to read ‘Phase-Shift PWM Controller’ Add OZ964GN, OZ964IG, OZ964IGN, OZ964D & OZ964DN st Add 1 paragraph ‘OZ964 is a high…LCD.’ Add 1 paragraph 1 sentence ‘Specific DC/CD…’ Add DC/DC Reference Application Circuit Correct 20 Pin SOIC 300mil drawing Miscellaneous corrections

Fabrication Guidelines- RO4400 series prepregs. RO4350B , RO4350F prepregs

Processing Guidelines for RO4450B ™ and RO4450F ™ PrepregsPROCESSING GUIDELINES:STORAGE:Upon receipt, all prepreg should be immediately moved from the receiving area into a controlledenvironment. Proper storage conditions would include temperatures between 10°C and 30°C (50°Fand 85°F) and protection against exposure to catalytic conditions such as high radiation and ultraviolet light. The prepreg should not be stored under vacuum. It is best to store the prepreg in its heat sealedpackaging, partially used packages should be resealed with tape.When properly stored, prepreg properties will be maintained for 12 months from the shipment date.A “fi rst-in, fi rst-out” inventory system is recommended.UNPACKING:RO4400™ prepregs are packaged in a dust-free environment, but will collect dust and debris from counter tops. We recommend counter tops be cleaned prior to unpackaging the prepreg. Plastic slip-sheeting has been provided to ease separation of individual plies and to shield the prepreg from contamination until it is ready for use.TOOLING:Tooling holes can be punched, drilled, or cut. Thin entry and exit materials may be needed to support the prepreg through the tooling hole formation process. The slip-sheeting should remain in place through tool-ing as it will shield the prepreg from contamination and should eliminate the risk of individual plies fusing together as the tooling holes are formed.MULTI-LAYER PREPARATION:Each ply of RO4450B™ and RO4450F™ 4-mil prepregwill bond to a nominal 0.004” (0.101mm) thickness,and each ply of RO4450B 3.6-mil prepreg will bond toa nominal 0.0036” (0.091mm) when recommendedbonding parameters are used. The actual thicknesseach ply will add to a multi-layer construction isdependent upon the weight and distribution ofcopper on the innerlayer surfaces.Rogers recommends the use of two or more plies ofprepreg between metal layers, and that the properpress cycle parameters are used per our guidelines.Processing Guidelines RO4400 Processing Guidelines Advanced Circuit Materials Division 100 S. Roosevelt Avenue Chandler, AZ 85226Tel: 480-961-1382, Fax: The world runs better with Rogers.®Any deviation from these recommendations can lead to poor fi ll performance or electrical failures, especially in high-speed digital/high density designs. If the design requires single-ply usage between metal layers, the user must ensure the proper testing protocol is in place to evaluate fi ll/fl ow and electrical performance. Contact your local technical services representative for questions or assistance with these guidelines.Also contact your local technical services representative for designs using more than six metal layers, or 35 micron foil on both sides, or when bonding against FR-4 cores.Etched dielectric surfaces should not be mechanically or chemically altered prior to multilayer bonding. Innerlayer metal surfaces should be oxide treated to promote improved mechanical adhesion. Reduced black oxide, brown oxide, and additive or subtractive oxide alternatives have been successfully applied. Inner-layers should be baked for 15 to 30 minutes at 115°C (239°F) to 125°C (257°F) just prior to preparing the multi-layer package for bonding.Core bonded constructions are preferred, but foil bonded outer-layers are an option with RO4400 prepregs. Rogers’ qualifi ed and recommended copper foil is HTE-TWS available from Circuit Foils. Sheeted foils are available through the manufacturers or through the sheeting service listed below:Circuit Foil America 625 rue du Luxembourg Granby J2J 2S9 - Canada Phone (+1) 450-770-8558 Fax: (+1) 450-770-8022 Contact Information:USA CustomersCopper Rolls - petey.decarlo@(fax # +1-215-887-6911)(USA)Copper Sheets - carmen.pignon@ (fax # +1-450-405-4622)(Canada)Europe and AsiaCopper Rolls and sheets - paul.jung@ (fax # +11 352 95 75 51 249)(Luxembourg)RO4450B and RO4450F prepregs allow a rapid ramp to 107°C (225°F), a 2.8°C - 4.0°C/Min (5°F-7°F) ramp rate between 107°C (225°F) and 121°C (250°F), and a maximum 2.2°C/Min (4°F/min) from 121°C (250°F) to 177°C (350°F). The full pressure of 400 psi should be used regardless of vacuum assistance potential, and lengthy (>5 minutes) draw downs should be avoided. Pressure should be applied before package temperature exceeds 38°C (100°F). Transfer to a cooling press is allowed after a 60 minute dwell at 177°C (350°F). The graph shown provides an optimum temperature and pressure profi le for bonding RO4450B and RO4450F prepregs. The tem-perature profi le can be matched using an in-hot process. Time vs. temperature trials may be required to defi ne requirements for lagging materials.Special Bonding Note: The RO4450B and RO4450F prepreg resin system is at its lowest viscosity at temperatures between 100°C (210°F) and 120°C (250°F). High layer count MLB’s, designs with buried metal layers thicker than ½ oz. copper, and constructions using single plies of RO4450B and RO4450F prepreg will benefi t by spending 20 minutes in the reduced viscosity window. This can be accomplished by ramping at a rate of 1°C/Min ( 2°F/Min) or by dwelling at 115°C (240°F) for 20 minutes. Should the latter approach be chosen, the ramp rates from RTto 115°C (240°F) and from 115°C-175°C (240°F to 350°F) can be 2.8°C-4.0°C/Min (5°F-7°F/Min). Care should be taken to not exceed 120°C (250°F) during the 20 minute dwell.Page 2 of 4Page 3 of 4Cycle time:2 hoursOuterlayer and PTH Processing: Processing guidelines for RO4003C ™, RO4350B ™, RO4360™ and RO4000® LoPro ™ double-sided circuits are applicable to RO4000 multi-layer boards. However, the multi-layer constructions will require desmear. CF4/O2 plasma and alkaline-permanganate processes used to desmear high Tg(170°C/338°F) FR-4 materials have been found to work well with RO4000 multi-layers. While desmear may berequired, etchback of the resin system is not recommended.Expected visual appearance in a cross section of RO4000 LoPro Laminates.Visual comparison of RO4000 LoPro laminates and traditional RO4000 cores in multi-layer constructions.The information contained in this data sheet and processing guide is intended to assist you in designing with Rogers’ circuit materials and prepreg. It is not intended to and does not create any warranties, express or implied, including any warranty of merchantability or fi tness for a particular purpose or that the results shown on this data sheet and processing guide will be achieved by a user for a particular purpose. The user is responsible for determining the suitability of Rogers’ circuit materials and prepreg for each application. Prolonged exposure in an oxidative environment may cause changes to the dielectric properties of hydrocarbon ba sed materials. The rate of change increases at higher temperatures and is highly dependent on the circuit design. Although Roger s’ high frequency materials have been used successfully in innumerable applications and reports of oxidation resulting in performanc e problems are extremely rare, Rogers recommends that the customer evaluate each material and design combination to determin e fi tness for use over the entire life of the end productThese commodities, technology and software are exported from the United States in accordance with the Export A dministration regu-lations. Diversion contrary to U.S. law prohibited.The world runs better with Rogers. and the Rogers’ logo are licensed trademarks of Rogers Corporation.RO4000, RO4400, RO4003C, RO4350B, RO4360 RO4450B, RO4450F and LoPro are licensed trademarks of Rogers Corp oration.© 1999, 2003, 2004, 2005, 2006, 2007, 2008, 2009, 2010, 2011 Rogers Corporation, Printed in U.S.A, All rights reserved.Revised 02/14/2011 0937-0211-CC Publication #92-005。

NXP Semiconductors PBSS5350SS 数据手册

1.Product profile1.1General descriptionPNP/PNP double low V CEsat Breakthrough In Small Signal (BISS) transistor in a medium power Surface-Mounted Device (SMD) plastic package.1.2FeaturesI Low collector-emitter saturation voltage V CEsat I High collector current capability I C and I CM I High collector current gain (h FE ) at high I C I High efficiency due to less heat generationISmaller required Printed-Circuit Board (PCB) area than for conventional transistors1.3ApplicationsI Dual low power switches (e.g. motors, fans)I Automotive1.4Quick reference data[1]Pulse test: t p ≤300µs;δ≤0.02.PBSS5350SS50 V , 2.7 A PNP/PNP low V CEsat (BISS) transistorRev. 01 — 3 April 2007Product data sheetTable 1.Product overviewType numberPackage NPN/PNP complement NPN/NPN complement NXPName PBSS5350SSSOT96-1SO8PBSS4350SPNPBSS4350SSTable 2.Quick reference dataSymbol Parameter Conditions Min Typ Max Unit Per transistor V CEO collector-emitter voltage open base --−50V I C collector current --−2.7A I CM peak collector current single pulse;t p ≤1ms --−5A R CEsatcollector-emittersaturation resistanceI C =−2A;I B =−200mA[1]-95140m Ω查询PBSS4350SPN供应商2.Pinning information3.Ordering information4.Marking5.Limiting valuesTable 3.PinningPin Description Simplified outline Symbol1emitter TR12base TR13emitter TR24base TR25collector TR26collector TR27collector TR18collector TR14518006aaa97687651234TR1TR2Table 4.Ordering informationType numberPackage NameDescriptionVersion PBSS5350SSSO8plastic small outline package; 8leads; body width 3.9mmSOT96-1Table 5.Marking codesType number Marking code PBSS5350SS5350SSTable 6.Limiting valuesIn accordance with the Absolute Maximum Rating System (IEC 60134).Symbol ParameterConditions Min Max Unit Per transistorV CBO collector-base voltage open emitter -−50V V CEO collector-emitter voltage open base -−50V V EBO emitter-base voltage open collector -−5V I C collector current -−2.7A I CM peak collector current single pulse;t p ≤1ms-−5A I B base current-−0.5A P tottotal power dissipationT amb ≤25°C[1]-0.55W [2]-0.87W [3]-1.43W[1]Device mounted on an FR4PCB, single-sided copper, tin-plated and standard footprint.[2]Device mounted on an FR4PCB, single-sided copper, tin-plated, mounting pad for collector 1cm 2.[3]Device mounted on a ceramic PCB, Al 2O 3, standard footprint.Per device P tottotal power dissipationT amb ≤25°C[1]-0.75W [2]- 1.2W [3]-2W T j junction temperature -150°C T amb ambient temperature −65+150°C T stgstorage temperature−65+150°C(1)Ceramic PCB, Al 2O 3, standard footprint (2)FR4PCB, mounting pad for collector 1cm 2(3)FR4PCB, standard footprintFig 1.Per device: Power derating curvesTable 6.Limiting values …continuedIn accordance with the Absolute Maximum Rating System (IEC 60134).Symbol Parameter Conditions Min Max Unit T amb (°C)−751751252575−25006aaa9671.01.50.52.02.5P tot (W)0(1)(2)(3)6.Thermal characteristics[1]Device mounted on an FR4PCB, single-sided copper, tin-plated and standard footprint.[2]Device mounted on an FR4PCB, single-sided copper, tin-plated, mounting pad for collector 1cm 2.[3]Device mounted on a ceramic PCB, Al 2O 3, standard footprint.Table 7.Thermal characteristics Symbol ParameterConditions Min Typ Max Unit Per transistorR th(j-a)thermal resistance from junction to ambientin free air[1]--227K/W [2]--144K/W [3]--87K/W R th(j-sp)thermal resistance from junction to solder point --40K/WPer device R th(j-a)thermal resistance from junction to ambientin free air[1]--167K/W [2]--104K/W [3]--63K/WFR4PCB, standard footprintFig 2.Per transistor: Transient thermal impedance from junction to ambient as a function of pulse duration;typical values006aaa809101102103Z th(j-a)(K/W)10−110−51010−210−410210−1t p (s)10−310310.0100.020.050.10.20.330.50.751.0duty cycle =FR4PCB, mounting pad for collector 1cm 2Fig 3.Per transistor: Transient thermal impedance from junction to ambient as a function of pulse duration;typical valuesCeramic PCB, Al 2O 3, standard footprintFig 4.Per transistor: Transient thermal impedance from junction to ambient as a function of pulse duration;typical values006aaa810101102103Z th(j-a)(K/W)10−110−51010−210−410210−1t p (s)10−31031duty cycle =0.010.020.050.10.20.330.50.751.0006aaa811t p (s)10−410210310110−310−110−210210103Z th(j-a)(K/W)10.020.050.10.20.330.50.751.000.01duty cycle =7.Characteristics[1]Pulse test: t p ≤300µs;δ≤0.02.Table 8.CharacteristicsT amb =25°C unless otherwise specified.Symbol Parameter Conditions Min Typ Max Unit Per transistor I CBOcollector-base cut-off current V CB =−50V; I E =0A --−100nA V CB =−50V; I E =0A;T j =150°C --−50µA I CES collector-emitter cut-off current V CE =−50V; V BE =0V --−100nA I EBO emitter-base cut-off current V EB =−5V; I C =0A --−100nAh FEDC current gainV CE =−2V; I C =−100mA 200340-V CE =−2V; I C =−500mA [1]200290-V CE =−2V; I C =−1A [1]180250-V CE =−2V; I C =−2A [1]130180-V CE =−2V; I C =−2.7A[1]95135-V CEsatcollector-emitter saturation voltage[1]I C =−0.5A; I B =−50mA -−60−90mV I C =−1A; I B =−50mA -−125−180mV I C =−2A; I B =−100mA -−225−320mV I C =−2A; I B =−200mA -−190−280mV I C =−2.7A; I B =−270mA-−255−370mV R CEsat collector-emitter saturation resistance I C =−2A; I B =−200mA [1]-95140m ΩV BEsatbase-emittersaturation voltage[1]I C =−2A; I B =−100mA -−0.95−1.1V I C =−2.7A; I B =−270mA-−1−1.2V V BEon base-emitter turn-on voltage V CE =−2V; I C =−1A [1]-−0.8−1.2V t d delay time V CC =−10V; I C =−2A;I Bon =−100mA;I Boff =100mA-9-ns t r rise time -54-ns t on turn-on time -63-ns t s storage time -190-ns t f fall time -50-ns t off turn-off time-240-ns C ccollector capacitance V CB =−10V; I E =i e =0A;f =1MHz-2535pFV CE =−2V (1)T amb =100°C (2)T amb =25°C (3)T amb =−55°CT amb =25°CFig 5.DC current gain as a function of collectorcurrent; typical valuesFig 6.Collector current as a function ofcollector-emitter voltage; typical valuesV CE =−2V (1)T amb =−55°C (2)T amb =25°C (3)T amb =100°CI C /I B =20(1)T amb =−55°C (2)T amb =25°C (3)T amb =100°CFig 7.Base-emitter voltage as a function of collectorcurrent; typical values Fig 8.Base-emitter saturation voltage as a function ofcollector current; typical values006aaa977200400600h FE0I C (mA)−10−1−104−103−1−102−10(1)(2)(3)V CE (V)0−2.0−1.6−0.8−1.2−0.4006aaa978−2−3−1−4−5I C (A)0I B (mA) = −140−126−112−98−84−70−56−14−28−42006aaa979−0.4−0.8−1.2V BE (V)0I C (mA)−10−1−104−103−1−102−10(1)(2)(3)006aaa980−0.6−1.0−1.4V BEsat (V)−0.2I C (mA)−10−1−104−103−1−102−10(1)(2)(3)I C /I B =20(1)T amb =100°C (2)T amb =25°C (3)T amb =−55°CT amb =25°C (1)I C /I B =100(2)I C /I B =50(3)I C /I B =10Fig 9.Collector-emitter saturation voltage as afunction of collector current; typical valuesFig 10.Collector-emitter saturation voltage as afunction of collector current; typical valuesI C /I B =20(1)T amb =100°C (2)T amb =25°C (3)T amb =−55°CT amb =25°C (1)I C /I B =100(2)I C /I B =50(3)I C /I B =10Fig 11.Collector-emitter saturation resistance as afunction of collector current; typical values Fig 12.Collector-emitter saturation resistance as afunction of collector current; typical values006aaa981−10−1−10−2−1V CEsat (V)−10−3I C (mA)−10−1−104−103−1−102−10(1)(2)(3)006aaa982−10−1−10−2−1V CEsat (V)−10−3I C (mA)−10−1−104−103−1−102−10(1)(2)(3)I C (mA)−10−1−104−103−1−102−10006aaa983110−110210103R CEsat (Ω)10−2(1)(2)(3)I C (mA)−10−1−104−103−1−102−10006aaa984110−110210103R CEsat (Ω)10−2(1)(2)(3)8.Test informationFig 13.BISS transistor switching time definitionV CC =−10V; I C =−2A; I Bon =−100mA; I Boff =100mAFig 14.Test circuit for switching times006aaa266−I Bon (100 %)−I B input pulse(idealized waveform)−I Boff90 %10 %−I C (100 %)−I C t dt on90 %10 %t routput pulse(idealized waveform)t ftt st offR CR2R1DUTmgd624V oR B(probe)450 Ω(probe)450 ΩoscilloscopeoscilloscopeV BBV IV CC9.Package outline10.Packing information[1]For further information and the availability of packing methods, see Section 14.Fig 15.Package outline SOT96-1 (SO8)03-02-18Dimensions in mm1.00.41.75pin 1 index0.490.360.250.195.04.84.03.86.25.81.27Table 9.Packing methodsThe indicated -xxx are the last three digits of the 12NC ordering code.[1]Type number Package DescriptionPacking quantity 10002500PBSS5350SSSOT96-18mm pitch, 12mm tape and reel-115-11811.SolderingFig 16.Reflow soldering footprint SOT96-1 (SO8)Fig 17.Wave soldering footprint SOT96-1 (SO8)sot096-1_froccupied areasolder lands Dimensions in mm placement accuracy ± 0.25 1.300.60 (8×)1.27 (6×)4.00 6.605.507.00sot096-1_fwsolder resistoccupied areasolder lands Dimensions in mm board directionplacement accurracy ± 0.25 4.005.50 1.300.3 (2×)0.60 (6×)1.20 (2×)1.27 (6×)7.006.60enlarged solder land12.Revision historyTable 10.Revision historyDocument ID Release date Data sheet status Change notice Supersedes PBSS5350SS_120070403Product data sheet--13.Legal information13.1Data sheet status[1]Please consult the most recently issued document before initiating or completing a design.[2]The term ‘short data sheet’ is explained in section “Definitions”.[3]The product status of device(s)described in this document may have changed since this document was published and may differ in case of multiple devices.The latest product status information is available on the Internet at URL .13.2DefinitionsDraft —The document is a draft version only. The content is still under internal review and subject to formal approval, which may result in modifications or additions. NXP Semiconductors does not give any representations or warranties as to the accuracy or completeness ofinformation included herein and shall have no liability for the consequences of use of such information.Short data sheet —A short data sheet is an extract from a full data sheet with the same product type number(s)and title.A short data sheet is intended for quick reference only and should not be relied upon to contain detailed and full information. For detailed and full information see the relevant full data sheet, which is available on request via the local NXP Semiconductors sales office. In case of any inconsistency or conflict with the short data sheet, the full data sheet shall prevail.13.3DisclaimersGeneral —Information in this document is believed to be accurate andreliable.However,NXP Semiconductors does not give any representations or warranties,expressed or implied,as to the accuracy or completeness of such information and shall have no liability for the consequences of use of such information.Right to make changes —NXP Semiconductors reserves the right to make changes to information published in this document, including withoutlimitation specifications and product descriptions, at any time and without notice.This document supersedes and replaces all information supplied prior to the publication hereof.Suitability for use —NXP Semiconductors products are not designed,authorized or warranted to be suitable for use in medical, military, aircraft,space or life support equipment, nor in applications where failure ormalfunction of a NXP Semiconductors product can reasonably be expected to result in personal injury, death or severe property or environmental damage.NXP Semiconductors accepts no liability for inclusion and/or use of NXP Semiconductors products in such equipment or applications and therefore such inclusion and/or use is at the customer’s own risk.Applications —Applications that are described herein for any of these products are for illustrative purposes only. NXP Semiconductors makes no representation or warranty that such applications will be suitable for the specified use without further testing or modification.Limiting values —Stress above one or more limiting values (as defined in the Absolute Maximum Ratings System of IEC 60134)may cause permanent damage to the device.Limiting values are stress ratings only and operation of the device at these or any other conditions above those given in theCharacteristics sections of this document is not implied. Exposure to limiting values for extended periods may affect device reliability.Terms and conditions of sale —NXP Semiconductors products are sold subject to the general terms and conditions of commercial sale,as published at /profile/terms , including those pertaining to warranty,intellectual property rights infringement and limitation of liability, unless explicitly otherwise agreed to in writing by NXP Semiconductors. In case of any inconsistency or conflict between information in this document and such terms and conditions, the latter will prevail.No offer to sell or license —Nothing in this document may be interpreted or construed as an offer to sell products that is open for acceptance or the grant,conveyance or implication of any license under any copyrights,patents or other industrial or intellectual property rights.13.4TrademarksNotice:All referenced brands,product names,service names and trademarks are the property of their respective owners.14.Contact informationFor additional information, please visit:For sales office addresses, send an email to:**********************Document status [1][2]Product status [3]DefinitionObjective [short] data sheet Development This document contains data from the objective specification for product development.Preliminary [short] data sheet Qualification This document contains data from the preliminary specification.Product [short] data sheetProductionThis document contains the product specification.15.Contents1Product profile. . . . . . . . . . . . . . . . . . . . . . . . . . 11.1General description. . . . . . . . . . . . . . . . . . . . . . 11.2Features . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11.3Applications . . . . . . . . . . . . . . . . . . . . . . . . . . . 11.4Quick reference data. . . . . . . . . . . . . . . . . . . . . 12Pinning information. . . . . . . . . . . . . . . . . . . . . . 23Ordering information. . . . . . . . . . . . . . . . . . . . . 24Marking. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 25Limiting values. . . . . . . . . . . . . . . . . . . . . . . . . . 26Thermal characteristics. . . . . . . . . . . . . . . . . . . 47Characteristics. . . . . . . . . . . . . . . . . . . . . . . . . . 68Test information. . . . . . . . . . . . . . . . . . . . . . . . . 99Package outline . . . . . . . . . . . . . . . . . . . . . . . . 1010Packing information. . . . . . . . . . . . . . . . . . . . . 1011Soldering . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1112Revision history. . . . . . . . . . . . . . . . . . . . . . . . 1213Legal information. . . . . . . . . . . . . . . . . . . . . . . 1313.1Data sheet status . . . . . . . . . . . . . . . . . . . . . . 1313.2Definitions. . . . . . . . . . . . . . . . . . . . . . . . . . . . 1313.3Disclaimers. . . . . . . . . . . . . . . . . . . . . . . . . . . 1313.4T rademarks. . . . . . . . . . . . . . . . . . . . . . . . . . . 1314Contact information. . . . . . . . . . . . . . . . . . . . . 1315Contents. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 14Please be aware that important notices concerning this document and the product(s)described herein, have been included in section ‘Legal information’.© NXP B.V.2007.All rights reserved.For more information, please visit: Forsalesofficeaddresses,pleasesendanemailto:**********************Date of release: 3 April 2007。

PBSS4350Z,135;中文规格书,Datasheet资料