ECE-C 471 Introduction to VLSI Design Baris Taskin Bossone 413F

微电子经典书籍

文章出处:虎踞龙盘发信人: detective (超级侦探), 信区: METech标 题: 微电子经典书籍---->Must have!!!发信站: BBS 水木清华站 (Sat May 11 11:43:46 2002)下面的书全是经典,最好全有,你全有了吗??;)TitleAuthorPublisher(see below)ISBN# CommentsAnalog Circuit Design: Art, Science, and PossibilitiesWilliams (editor)BH0-7506-9166-2Lots of good stories here. Every new IC designer should read Derek Bowers chapte r.Art and Science of Analog Circuit DesignWilliams (editor)BH0-7506-9505-6More good stories. Eric Swanson’s view of digital vs. analog resonated with me.Analysis and Design of Analog Integrated Circuits - 3rd Ed.Gray and MeyerWI0-471-57495-3A popular introductory text. I used the first edition for guidance on my first c ustom IC (a bipolar array)Analogue IC design: The Current-Mode ApproachTomazou, Lidgey, & Haigh (editors)IEE0-86341-215-7Great reference for current mirrors, translinear circuits, MOS transconductors, current-conveyors.Analog MOS Integrated Circuits for Signal ProcessingGregorian & TemesWI0-471-09797-7Best introduction to switched-capacitor circuit design.CMOS Analog Circuit DesignAllen & HolbergHRW0-03-006587-9Probably the best introductory book for analog designers unfamiliar with CMOS te chniques.Design of MOS VLSI Circuits for TelecommunicationsTsividis & Antongnetti (editors)PH0-13-200643-XReplaced by the 2nd edition. Get this one too, if you can find it, for some mate rial that was replaced on digital filter mechanization.Design of Analog-Digital VLSI Circuits for Telecommunications & Signal Processin g- 2nd Ed.Franca & Tsividis (editors)PH0-13-203639-8 A ?“must have”.Switched Capacitor CircuitsAllen & Sanchez-SinencioVNR0-442-20873-1I confess that I haven’t used it much, but it appears to be a very comprehensiv ereference on whole field.Analog Interfaces for Digital Signal Processing SystemsOp’t Eynde & SansenKAP0-7923-9348-1Very readable. Lots of material on the “nuts-and-bolts” of putting delta-sigma data converters togetherIntegrated Analog-to-Digital and Digital-to-Analog ConvertersVan de PlasscheKAP0-7923-9436-4Plenty of high-speed bipolar stuff here, too.Signal Recovery from Noise in Electronic InstrumentationWilmshurstAH0-85274-783-7Excellent introduction to the basic principles involved.Photodiode AmplifiersGraemeMcG-H0-07-024247-XThere is a lot more to this topic than meets the eye. This is a complete treatme nt of all the subtleties.Video Demystified: A Handbook for the Digital EngineerJackHT1-878707-09-4Very useful and not just for digital types. A good one-stop source for digital v ideo information.Low-Noise Electronic System DesignMotchenbacher & ConnellyWI 0-471-57742-1 A ?"must have”. Someday you will need it.Communications ReceiversRohde & BucherMcG-H0-07-053570-1I always wanted to build one of these from scratch. Maybe someday...Principles of Communications SystemsTaub & SchillingMcG-H 0-07-062955-2A standard college-type text.Analog Circuit Design: Low-Noise, Low-Power, Low-Voltage; Mixed-Mode Design with CAD Tools; Voltage, Current and Time ReferencesHuijsing, van de Plassche, Sansen (editors)KAP0-7923-9659-6Outstanding classic section by Barrie Gilbert on bandgapvoltage reference design is worth more than the price of the book.More on folding A/D converters, autozeroing, etc.Analog Circuit Design: Low-Power Low-Voltage, Integrated Filters, and Smart Powe rvan de Plassche, Sansen, & Huijsing (editors)KAP0-7923-9513-1Another set of seminars.Analog Circuit Design: Mixed A/D Circuit Design, Sensor Interface Circuits, and Communication Circuits Sansen,Huijsing, van de Plassche (editors)KAP0-7923-9408-9Another set of seminars.VNR Concise Encyclopedia of MathematicsGellert, Kustner, Hellwich, KastnerVNR0-442-22646-2A jewel. The panorama of mathematics is clearly laid out. Several people have tr ied to find it but tell me it’s unavailable now. Scream at them to put it back inprint!Circuits and Systems TutorialsTomazou (editor)IEEE0-7803-1170-1Tutorials on unusual topics like: chaos, image coding, nonlinear DSP. Good delta -sigma tutorial, too.Oversampling Delta-Sigma Data ConvertersCandy & TemesIEEE0-87942-285-8A “must have” collection of the earlier papers on this topic. A new collection is out now, but I’m still back-ordered.Integrated Continuous-Time FiltersTsividis & Voorman (editors)IEEE0-7803-0425-XI haven’t done much with this type of filter, but I find this reference useful for design of linear transconductors.Analog CMOS Filters for Very High FrequenciesNauta KAPnext time Design methodology for the ultimate in CMOS linear circuit speed.Monolithic Phase-Locked Loops and Clock Recovery CircuitsRazavi (editor)IEEE0-7803-1149-3A collection of journal papers that is a “must have” if you design these.Phase-Locked Loops - 2nd Ed.BestMcG-H0-07-911386-9The most accessible introduction to the topic.Digital PLL Frequency Synthesizers - Theory and DesignRohdePH0-13-214239-2 Out of print.You might still be able to get a copy at Compact Software.Frequency Synthesis by Phase-LockEganKrieger0-89464-456-4One of the few places that phase-frequency detector “dead-zone” and sampled-da ta effects on the loop stability are treated.Phase-Locked Loop Circuit DesignWolaverPH0-13-662743-9My personal favorite of the PLL books. Wolaver has a clear approach. There’s so me good stuff on data recovery here, too.Phaselock TechniquesGardnerWI0-471-04294-3For many, the standard reference. I haven’t found it as useful.Discrete-Time Signal ProcessingOppenheim & SchaferPH0-13-216292-XThe standard textbook.A “must have”.Handbook of Digital Signal ProcessingMitra & KaiserWI0-471-61995-7Must have.Digital Filter DesignParks & BurrusWI0-471-82896-3Practical with not too much math in the presentation. Contains some source codeDigital Filters and Signal ProcessingJacksonKAP0-89838-276-9Good chapter on quantization effects.Multirate Digital Signal ProcessingFliegeWI0-471-93976-5Very clear presentation. Good explanation of interpolated FIR filter design.Principles of Digital Audio - 3rd Ed.PohlmannMcG-H0-07-050468-7Good overview of audio CD coding, error correction, and compression techniques.Advanced Digital AudioPohlmannSams0-672-22768-1Not quite as good as his "Principles..", IMHO. Probably too broad.Digital MOS Integrated Circuits IIElmasry (editor)IEEE0-87942-275-0Collection of papers. Good intro to the topic.Modern Active Filter DesignSchaumann, Soderstrand & Laker (editors)IEEE0-471-09733-0Contains an especially good paper by Fleischer and Laker on SC biquads.Electronic Filter Design HandbookWilliams & TaylorMcG-H0-07-070434-1Probably the standard “working engineer” reference.Handbook of Engineering FundamentalsEshbachWI0-471-24553-4For the times when you are confronted with problems that are “outside the box”.Electrical Noise, Fundamentals & SourcesGuptaIEEE0-471-03117-8Like it says...the fundamentalsSemiconductor Device Modeling with SPICEMassobrio & AntongnettiMcG-H0-07-002469-3Just what do the parameters in those models mean anyway?Inside SPICE - Overcoming the Obstacles of Circuit SimulationKielkowskiMcG-H0-07-911525-XJust what is that simulator doing anyway? A “must have”.Nonlinear Circuits Handbook Sheingold Analog Devices n/a A treasurechest of analog techniques that will soon be lost, crushed byhundreds-of-thousands of sub-micron digital transistors operatingat high speeds.Publisher Decoder AH Adam HilgerPublisher Decoder AH Adam HilgerHRW Holt, Rinehart & WinstonHT HighText PublicationsIEE Institute of Electrical EngineersIEEE IEEE PressKAP Kluwer Academic PublishersMcG McGraw-HillPH Prentice HallSams Howard SamsVNR (now Wiley) Van Nostrand Reinhold WI Wiley-Interscience--。

国家科技公司National Instruments的LabVIEW认证系列文档第一部分说明书

LabVIEW Certification OverviewThe National Instruments LabVIEW Certification Program consists of the following three certification levels:-Certified LabVIEW Associate Developer (CLAD)-Certified LabVIEW Developer (CLD)-Certified LabVIEW Architect (CLA)Each level is a prerequisite for the next level of certification.A CLAD demonstrates a broad and complete understanding of the core features and functionality available in the LabVIEW Full Development System and possesses the ability to apply that knowledge to develop, debug, and maintain small LabVIEW modules. The typical experience level of a CLAD is approximately 6 to 9 months in the use of the LabVIEW Full Development System.A CLD demonstrates experience in developing, debugging, deploying, and maintaining medium-to-large scale LabVIEW applications. A CLD is a professional with an approximate cumulative experience of 12 to 18 months developing medium-to-large applications in LabVIEW.A CLA not only possesses the technical expertise and software development experience to break a project specification into manageable LabVIEW components but has the experience to see the project through by effectively utilizing project and configuration management tools. A CLA is a professional with an approximate cumulative experience of 24 months in developing medium-to-large applications in LabVIEW.Note The CLAD certification is a prerequisite to taking the CLD exam. The CLDcertification is a prerequisite to taking the CLA exam. There are no exceptions to this requirement for each exam.CLA Exam OverviewA CLA demonstrates mastery in analyzing and interpreting customer requirements for the development of scalable application architectures in LabVIEW, organized in a modular project hierarchy with the intent to be fully developed later by a multi-developer team. The architecture meets the requirements using a software simulation with interfaces to abstracted hardware modules. To ensure successful integration, the Architect enables completion by a developer team with modules designed with consistent, well defined interfaces, data structures, module design patterns, messaging, and documented developer instructions with specific design requirements. The CLA is a professional with an approximate cumulative experience of 24 months in developing medium-to-large applications in LabVIEW.Product: Your test computer will have the latest LabVIEW Full or Professional Development System installed for developing your application. Contact your proctor or testing center prior to the exam to get the details and familiarize yourself with the LabVIEW version that you will use to develop your application.Refer to /labview/how_to_buy.htm for details on the features available in the LabVIEW Full / Professional Development System.Please note that you will not receive extra exam time to compensate for non-familiarity with the LabVIEW environment. If you need time to customize the environment, please make arrangements with your proctor to hold off on giving you the exam packet until you are ready to start the exam.The use of resources available in LabVIEW, such as the LabVIEW Help, examples, and templates are allowed during the exam. Externally developed VIs or resources are prohibited.The CLA exam consists of a project that is very similar to the project that you worked on the CLD exam.Your exam submissions should be transferred to a USB memory stick and turned in to your proctor.Note Do not detach the binding staple, copy, or reproduce / retain any section of the exam document or solution of the exam. Failure to comply will result infailure.CLA Exam Topics1.Project Requirements2.Project Organization and Hierarchy3.Project Architecture and Design4.Team-Based Design, Development, and Standardization Practices5.Reusable Tools / Component DesignNote The CLA exam is cumulative and includes CLAD and CLD exam topics.Topic Subtopic1.Project Requirements a.Technical requirementsb.Requirements trackingc.GUI Developmentd.Hardware Interfacee.Error Handling2.Project Organization and Hierarchy bVIEW project hierarchyb.Disk hierarchybVIEW pathsd.Modular hierarchy3.Project Architecture and Design a.Main VI architectureb.Module / SubVI architecturec.Messaging Architectured.Error Modulee.File and Database I/Of.Simulation architectureer interface designh.Advanced design methodsi.Documentation of requirements4.Team-Based Design, Development,and Standardization Practices bVIEW development practicesb.Modular functionalityc.Documentation for Developercompletiond.Clear Modular APIs5.Reusable Tools / Component Design bVIEW technologiesb.API designc.Design patternsCLA Exam Topic Details1.Project Requirementsa.Technical requirementsDetermine and list the following requirements from the project specification:1.Application requirements—Goal and purpose of the applicationer interface requirements—Presentation and behavior of controls thatinteract with users3.Functional requirements—The functionality of the components and theirinteraction within the system4.Timing requirements—Hardware / software, event-based data overflow,daylight savings5.Error handling requirements—Warning, errors, critical errors, shutdownsequence6.Hardware or simulation requirements—Interface and operational requirementsfor switching to field devices7.Input/output requirements—Console, databases8.Initialization, shutdown requirements—User interface and program behaviorduring startup, error conditions, and shutdown9.Non-functional requirements—Accuracy, performance, modifiability10.Assumptions and constraintsa) A functional assumption is an issue that is unclear in the specificationb) A functional constraint is a design decision that is imposed by thespecificationb.Requirements tracking1.Identify and fulfill requirementsa)Determine detail level of requirementsb)Locate requirements tags in architecture only where requirements arefulfilled2.Methods or (utilization of) software tools to track requirementsa)Use specified format for requirements tags for Requirements Gatewaytrackingb)Utilize provided tag filec.GUI Development1.Build GUI based on specificationa)Determine the appropriate control type based on functional specificationsb)Use Type Definitions2.Design interface that meets functional requirementsa)Utilize the LabVIEW Development Guidelinesb)Organize, modularize, or group user interface components to follow aprocess, or logical sequencec)Utilize advanced LabVIEW development techniquesd.Hardware Interfacee abstraction to separate simulation and hardware modulesa)Develop API to interface with the controller moduleb)Design a scalable interface that enables transition from simulation tohardwarec)Develop method to select hardware or simulation modules2.Develop simulation architecture based on hardwarea)Select a modular architecture that simulates external hardwareb)Select user interface components that closely mimic the function of thehardwaree.Error Handling1.Develop centralized error handlinga)Demonstrate methods to handle warning, critical errors, and shutdownerror conditions as defined in the specificationb)Develop architecture that integrates the error module in the main VI andwithin other modules2.Design a shut down method that is responsive to the error module and isabstracted from the functional modules2.Project Organization and HierarchybVIEW Project hierarchy1.Develop a LabVIEW Project hierarchy for team-based developmenta)Modules and their hierarchyb)Shared subVIs, custom controlsc)Plug-in VIsd)LabVIEW Project librariese)Support files (documentation, configuration, and log files)2.Utilize a naming conventionb.Disk hierarchy1.Mimic project hierarchy on diske auto-populating foldersanize project and disk hierarchy by module or other functional basedschemec.Paths1.Utilize and require developer to use relative pathsd.Modular Hierarchyanize by module or other functional based scheme2.Sub folders based on code artifacts such as controls or module subVIs3.Project Architecture and Designa.Main VI architecture1.Select an advanced, scalable, and modular architecture that enables thefollowing:a)Handling of user interface events and user eventsb)Asynchronous and parallel processing of eventsc)Initialization, shutdown, state persistence, and restorationd)Effective error (logic and run-time) handlinge)Timing (event or poll-based)f)Team-based development of functional modules2.Develop data and event messaging structures3.Develop architecture to handle configuration data4.Develop interfaces for simulation and other modules5.Utilize the LabVIEW Development Guidelines for memory optimizationb.Module / subVI architecture1.Select a cohesive architecture and design pattern for modules and subVIs2.Define and develop a clear API3.Define a consistent connector pane and iconc.Messaging Architecture1.Modularize messaging scheme for initialization, use, and shutdown2.Demonstrate method for messaging for developers to complete3.Demonstrate loose coupling of messaging moduled.Error Module1.Modularize centralized error handling for clear initialization, use, andshutdown2.Demonstrate error handling integration with functional modules3.Integrate for shutdown as specified4.Demonstrate file logging5.Discriminate actions for different types of error severitye.File and Database I/O1.Modularize I/O for clear initialization, use, and shutdownmunicate access methods for developers to complete3.Specify data formats and conversion to application data structures4.Integrate for Configuration data and Error loggingf.Simulation module architecture1.Select a modular architecture that simulates external hardware2.Design a scalable interface that can ease transition from simulation tohardware3.Select user interface components that closely mimic the function of thehardwareer interface design1.Utilize the LabVIEW Development Guidelinesanize, modularize, or group user interface components to follow a process,or logical sequence3.Utilize advanced LabVIEW development techniquesh.Advanced design methods1.Develop an architecture for a modular, scalable, and maintainable application2.Implement, develop, and enhance standard design patterns to suit projectrequirements3.Utilize an event-based design for user interface events and define usergenerated events for timing, error, signaling, and so on4.Abstract functionality and develop a clear and consistent interface API formodules and subVIs5.Utilize and standardize scalable data types and data structures6.Utilize object oriented design, recursion, VI Server, and advanced file I/Otechniquesi.Documentation of Requirements1.Utilize the LabVIEW Development Guidelines2.Document the following:a)Main architecture for module integrationb)Data structures and data and message communication mechanismc)Modules, subVIs, and interfaces (API)d)Simulation module, interfaces, and requirements for transitioning fromsimulation to hardware module4.Team-Based Design, Development, and Standardization PracticesbVIEW development practices1.Establish and use consistent development style—Utilize the LabVIEWDevelopment Guidelines as well as company developed standardse templates as a starting point for development3.Document VI Properties, the block diagram, and the user interface (tip strips,and so on)4.Develop reusable modules and tools to standardize developmentb.Architecture for modular development1.Select a cohesive architecture and design for modules and subVIs2.Define a consistent connector pane and icon3.Define error handling and ensure critical errors are handled appropriately4.Develop major structures and messaging5.Develop sufficient detail for the developer to implement the specificrequirements.c.Documentation instructions for the developer to complete the application1.Document coding completion of algorithms, transactions, and logic for adeveloper team to complete functionality2.Document multiple similar steps by completing a first step with detailedrequirements and subsequent steps referring to the technique of the first stepe LabVIEW code on the block diagram to demonstrate technique andcompliment this with developer instruction documentationd.Clear modular APIs1.Define the APIs for modules and subVIs2.Develop APIs for functional modules to enable modularity and abstraction3.Develop Architecture with APIs for error handling, initialization, andshutdown5.Reusable Tools / Component DesignbVIEW technologies1.Determine the optimal method for developing a reusable component or aproductivity enhancement tool from the following technologies:a)Custom controlsb)Merge VIc)SubVId)XControlse)VI templateb.API design1.Develop a simplified API to wrap advanced LabVIEW functions2.Develop manager VIs to handle common tasks, such as reference managementof queues, user events, and so on3.Utilize project access options to restrict or allow access to components oflibrariesc.Design Patterns1.Select appropriate design patters for modules and subVIs based on functionalrequirementse documentation to describe the completion of routine design patternelementsCLA ExamIn the CLA exam you will be required to design an architecture that covers the requirements given in a project specification.Exam Duration: 4 hoursStyle of exam: Application architecture developmentPassing grade: 70%Application Architecture Development:You must develop an application framework consisting of a main VI, modules, supporting subVIs, and custom controls (type definitions). A module is a subVI or group of subVIs that performs a set of functions. A module may have it own hierarchy of subVIs.Note You are not required to submit a functional application. The functional details of the requirements should be documented in the main VI, modules, and subVIs.You must provide this documentation in the architecture to enable developers on your team to develop the functionality.The architecture has the following minimum requirements:a.Develop a project hierarchyb.Develop a main VI. The main VI should include the following:i.Modular User interfaceii.Driving architectureiii.Major data structuresiv.Event, data, timing, and error communication method(s)v.Error handlingvi.Fully connected modules and /or subVIsc.Develop shell (stub) modules and subVIs, which should not include detailedfunctional logic, but should include the following:i.Inputs, outputs, icon, and connector paneii.Architecture and APIiii.Major internal data structuresiv.Error handling and error communicationv.Instructions or comments listing the functional details, which are sufficient for a developer to complete the functionality of the VId.Develop an interface for hardware simulation as a separate module or as part of themain VI or any other module, depending on your design.e.Develop inter-process communication mechanismf.Develop an error handling and shutdown strategyRequirements TrackingThe project specification will detail requirements identified by a unique identifier. In order to demonstrate coverage of a requirement, you must include the ID of the requirement in the documentation of your architecture. Requirements can be covered in any part of the architecture’s documentation, including:∙VI Documentation Property∙Control Documentation Property∙Project or Library Documentation Property∙Comments on the front panel or block diagramA single requirement may be covered by multiple sections of code if all of those sections are necessary to fulfill the requirement.To cover a requirement, the following text should be in the in the documentation of the code: [Covers: ID] Example: [Covers: CD1]The provided USB memory stick contains a text file that has all of the Tags. This file is provided as a convenience for use in placing the tags in the application code.Note A requirements tracking tool (Requirements Gateway) will be used to verify the requirements coverage, hence adherence to the above syntax is crucial.Please refer to the CLA sample exams to see the how the coverage is documented in the VI and the instruction / comments that need to be included in the VI for a developer to complete the implementation.Grading:The point allocation for the CLA exam consists is as follows: (Total: 100 points)∙User interface and block diagram style : 10 points∙Documentation : 20 points∙Requirements coverage : 30 points∙Architecture development : 40 pointsCertified LabVIEW Architect Preparation Guide100500-01CLA Exam Preparation ResourcesUse the following resources for additional exam preparation:∙Managing Software Engineering in LabVIEW∙Advanced Architectures for LabVIEWo Instructor-led trainingo Self-paced training using the course manuals∙CLA Sample Exams:o /claprepCLA Exam ScenariosThe following table lists possible exam scenarios that you may receive to develop a solution for your CLA exam. This list is intended to give a general idea of what exams will be administered, and there may be variations within each exam.Exam Scenario DescriptionCoffee Machine The coffee machine simulates ingredient storage, andperforms grinding, brewing and dispensing operations toprepare hot water, coffee and latte.Pizza Machine The Pizza Machine simulates creating a customized pizzarecipe and then making, baking and cutting the pizza. Security System The multi-zoned security system simulates the arming,disarming, tamper, bypass and alarm functions. Thermostat The thermostat simulates scheduled programmatic heatingand cooling control for heating, ventilation and air-conditioning (HVAC) system.© 2014 National Instruments Page 11 of 11。

ECE 17中文版

ECE关于车辆座椅、座椅固定装置及头枕认证的统一规定UNIFORM PROVISIONS CONCERING THE APPROVAL OF VEHICLES WITHREGARD TO THE SEATS,THEIR ANCHORAGESAND ANY HEAD RESTAINTS奇瑞汽车有限公司汽研院NO.17 关于车辆座椅、座椅固定装置以及头枕认证的统一规定1 适用范围1.1 本法规适用于M1 和N 类车辆座椅、头枕及其固定装置强度方面的认证,也适用于M2和M3 类车辆座椅、头枕及其固定装置强度方面的认证,且不受第80 号法规01 修正系列的限制(1)。

1.2 本法规也适用于座椅靠背后面部分(2)的设计,以及M1 类车辆行李前冲位移的乘员防护装置。

本法规不适用于折叠式座椅、侧向座椅、后向座椅以及此类座椅的头枕。

2 定义在本法规中:2.1 “车辆认证”是指座椅及其固定装置强度,座椅靠背后部设计以及头枕性能方面的车辆型式认证。

2.2 “车辆型式”是指在下列主要方面没有差异的车辆:2.2.1 座椅的结构、形状、尺寸、材料以及质量,允许座椅蒙皮和颜色不同;允许质量差在批准座椅型式的座椅质量的5%范围内;2.2.2 座椅、座椅靠背及其组成部件的调节装置、位移装置及锁止装置的型式和尺寸;2.2.3 座椅固定装置的型式和尺寸;2.2.4 头枕的尺寸、构架、材料和衬垫,允许其蒙皮和颜色不同;2.2.5 头枕附件的型式和尺寸,若头枕为分体式头枕还包括头枕连接部件的特性。

2.3 “座椅”是指供一个成年乘员乘坐且有完整装饰并与车辆结构为一体或分体的乘坐设施。

它包括单独的座椅或长条座椅的一个座位。

2.4 “长条座椅”是指供一个以上成年乘员乘坐且具有完整装饰的乘坐设施。

2.5 “固定装置”是指将座椅总成固定到车辆结构上的装置,包括车身上受影响的部件。

2.6 “调节装置”是指能将座椅或其部件的位置调整到适应乘员乘坐姿态的装置。

VLSI测试与可测性设计第一讲

2002年9月16日

Testing Principle

2002年9月16日

Automatic Test Equipment Components

Consists of:

Powerful computer Powerful 32-bit Digital Signal Processor (DSP) for analog testing Test Program (written in high-level language) running on the computer Probe Head (actually touches the bare or packaged chip to perform fault detection experiments) Probe Card or Membrane Probe (contains electronics to measure signals on chip pin or pad)

2002年9月16日

Motivation

Need to understand some Automatic Test Equipment (ATE)

technology

Influences what tests are possible Serious analog measurement limitations at high digital frequency or in the analog domain Need to understand capabilities for digital logic, memory, and analog test in System-on-a-Chip (SOC) technology

现代VLSI设计-基于IP核的设计第四版课程设计

现代VLSI设计-基于IP核的设计第四版课程设计一、背景介绍现代集成电路设计是电子信息工程学科体系中重要的一环,在现代电子信息领域有着广泛的应用。

随着技术的不断进步,集成度的要求越来越高,逐渐从单个器件转向系统级芯片设计,为此,设计人员要对现代VLSI设计有深入的了解和掌握。

本课程设计基于IP核的设计,旨在通过具体的实际案例,提高学生对现代VLSI设计的理解,并学习如何利用常见IP核优化系统性能,达到减少设计成本、提高设计效率、提高设计可维护性的目的。

二、设计目标本次课程设计的主要目标是掌握VLSI设计的基本原理和流程,学习如何使用IP核进行设计,理解如何对电路进行优化。

三、课程内容3.1 VLSI设计基本原理VLSI(Very Large Scale Integration)是指超大规模集成电路。

VLSI设计主要包括从设计到工艺、测试等多个环节,本部分将学习VLSI设计的基本流程、器件结构、工艺和测试方法等基本知识。

3.2 IP核简介IP核(Intellectual Property)是指独立的设计模块,可以被其他不同的电路利用。

IP核的设计和应用可以大大简化电路设计,提高设计效率和可维护性。

本部分将学习IP核的基本原理、分类和应用场景。

3.3 IP核的设计本部分将围绕基于IP核的设计开展实际操作,涉及IP核的设计和应用。

具体包括如何使用Vivado软件进行IP核的设计和如何利用IP核完成特定功能的设计。

3.4 IP核的优化本部分将介绍如何使用IP核进行电路优化,旨在提高系统设计的性能和可靠性。

具体包括如何对IP核进行定制化、如何进行IP核的性能评估以及如何评估系统的功耗等。

四、课程实践本课程设计将通过实践案例学习VLSI设计、IP核的设计与优化。

4.1 实践案例1:基于IP核的数字信号处理系统设计本案例将指导学生利用IP核进行一个简单的数字信号处理系统设计,包括数据输入输出模块、FIR滤波器模块、FFT模块。

VLSI设计基础第三版课程设计

VLSI设计基础第三版课程设计一、概述VLSI(Very Large-Scale Integration)是指集成电路技术中的一种技术,这种技术可以使几千个甚至几百万个电子元件集成在一个芯片上。

VLSI的发展使得集成电路的组织、设计、制造变得更加简单和经济。

因此,本课程旨在让学生了解VLSI的基础概念、设计方法和制造流程,同时通过实践,帮助学生掌握VLSI设计的基础知识和技能。

二、教学目标1. 理论目标•掌握VLSI设计的基本概念、原理和方法;•了解VLSI设计流程和制造工艺;•理解芯片设计中的时序、布局和布线等内容;•熟悉ASIC和FPGA的原理和应用。

2. 实践目标•熟悉VLSI设计工具的使用;•学会使用一些流行的VLSI仿真工具;•实现一个小型VLSI设计项目,加深对VLSI设计过程的理解。

第一部分:VLSI设计原理1.VLSI概述2.VLSI设计流程3.VLSI芯片设计的基本概念4.芯片布局设计5.芯片布线设计6.阵列设计基础7.数字信号处理器的设计8.软件定义电台的设计9.ASIC设计基础10.FPGA的基本原理和应用第二部分:VLSI设计实践1.FPGA的简单应用2.Verilog HDL及其模块化设计方法3.VHDL语言及其模块化设计方法4.门级元件的设计和实现5.组合逻辑和时序逻辑的设计6.测试的方法和技巧7.系统级仿真本课程将采用以下教学方法:1.理论授课:讲解VLSI设计的基本概念、原理和方法;2.实验实践:通过一些实践操作,将理论知识具体化;3.设计实践:要求学生进行一些小型VLSI设计项目。

五、教学要求1. 学生要求本课程面向电子信息类等专业的学生,建议先修读模拟电子技术、数字电子技术等课程。

因为本课程需要学生具备一定的电路基础知识和编程能力。

2. 教师要求本课程需要教师具备丰富的VLSI设计经验,熟悉VLSI设计流程和常用工具,能够灵活运用各种学习资源,耐心指导学生进行设计项目。

模拟电路推荐书籍

McGraw Hill, 1994

ISBN 0-07-032386-0

Design of Analog/Digital VLSI Circuits for Telecommunications and Signal Processing

J. Franca, Y. Tsividi

VLSI Design Techniques for Analog and Digital Circuits

R.L.Geiger, P.E.Allen, N.R.Strader

McGraw-Hill 1989

ISBN: 0070232539

Analog Design Text Books

Addison-Wesley Publishing Company

ISBN 0-201-12580-3

Computer Aids of VLSI Design

Steven Rubin

Addison-Wesley Publishing Company

ISBN 0-201-05824-3

P.R. Gray, R.G.Meyer

John Wiley & Sons, 1992

ISBN: 0471574953

Neil Weste and Kamran Eshraghian

Addison-Wesley Publishing Company

ISBN 0-201-08222-5

The Design and Analysis of VLSI Circuits

Lance Glasser and Daniel Dobberphuhl

VLSI设计课程

课程安排

1. 2. 3. 4. 5. 6. 电路仿真(一部分) : 20学时 VHDL设计(二部分): 25学时 VSLI系统设计(三部分): 10学时 HDL设计综合(三部分): 5学时 VSLI自动布局布线(三部分): 10学时 VSLI物理验证(三部分): 10时 共80学时

学习VLSI设计工具

1. 电路仿真工具Cadence -spectre 2. VHDL编译及仿真工具ALTER- MaxPlusII

3. 应用软件设计工具-Keil51 4. 数字系统功能验工具-Mento Modelsim

5. 设计综合工具-Synopsys dc(Design Compiler) 6. 自动布局布线工具- Cadence SE(Silicon Ensemble) 7. VLSI物理验证工具Cadence Dracula

4.

5.

6.

SOC的芯片实现 -基于M210core的例子

《VLSI设计》教材

1. 主要教材:

《超大规模集成电路设计技术》三册 电路模拟spectre仿真; 《超大规模集成电路设计技术》四册 VSLI设计系列;

2. 建议参考书:

《IC设计基础》任艳颖等 西安电子科技出版社2009; 《现代VLSI电路设计》 Wayn.e 科学出版社2012; 《数学集成电路设计》 Ven.Martin 电子工业2012; 《电子系统-集成电路设计技术》李玉山等 电子工2012;

《超大规模集成电路 (VLSI)设计》

《VLSI设计》课程简介

1. 2. 3. 课程主要讲授数字超大规模集成电路(VSLI)设计的概念 及方法。 课程以一个0.18微米工艺30万门规模的数字系统芯片设计 项目为实例. 学习电路仿真; VHDL设计; VSLI系统软硬件协同设计; 设计 综合; 时序分析;VSLI自动布局布线; VSLI物理验证;全芯 片后仿真。 学习spectre电路模拟工具、数字电路仿真工具Modelsim、 DC设计综合工具及SE自动布局布线工具的使用。 课程采取课堂教学和实验相结合的方式,含盖超大规模集 成电路(VSLI)设计全流程.。 通过学习和实验,要求完成30万门的数/字系统芯片项目设 计,从而具备VSLI芯片设计基本能力。

VLSI设计与制造技术概述

VLSI设计与制造技术概述随着科技的不断发展,半导体行业在过去几十年中取得了巨大的进步。

VLSI(Very Large Scale Integration,超大规模集成电路)设计与制造技术作为半导体行业的核心,起到了决定性的作用。

本文将对VLSI 设计与制造技术进行概述,介绍其基本概念、发展历程和关键技术。

一、VLSI设计的基本概念VLSI设计是指在单个芯片上集成大量的电子元件,将复杂的电路系统等设计信息转化为实际可制造的芯片。

VLSI设计的关键目标是提高集成度和功能密度,从而实现更高性能和更小尺寸的芯片。

二、VLSI设计的发展历程VLSI设计技术起源于20世纪60年代末,当时人们开始研究如何在一块硅片上集成多个晶体管。

随着摩尔定律的提出,VLSI设计技术逐渐成为半导体行业的核心竞争力之一。

在过去的几十年中,VLSI设计技术经历了几个主要的发展阶段,从SSI(Small Scale Integration,小规模集成)到MSI(Medium Scale Integration,中规模集成)再到LSI (Large Scale Integration,大规模集成)和VLSI。

如今,VLSI设计已经进入到SOC(System-on-a-Chip,片上系统)和多核心时代。

三、VLSI设计的关键技术1. 逻辑设计:逻辑设计是VLSI设计的基础,它通过使用HDL (Hardware Description Language,硬件描述语言)描述电路功能,并系统地进行功能验证和仿真。

2. 物理设计:物理设计主要包括芯片布局和电路布线两个方面。

芯片布局决定电路元件的相对位置,而电路布线则是将逻辑电路转化为物理电路的过程。

3. 高级封装技术:高级封装技术是将VLSI芯片封装成可直接使用的模块或器件的过程。

常用的封装技术包括BGA(Ball Grid Array,球栅阵列)、CSP(Chip Scale Package,芯片尺寸封装)等。

数字集成电路可测性设计(DFT)讲义第1讲

Good chip appears to be faulty (fails test)

EE141 VLSI Test Principles and Architectures

11

Introduction

Electronic System Manufacturing

A

system consists of

Moore’s Law: scale of ICs doubles every 18 months

Growing size and complexity poses many and new testing challenges

VLSI M LSI

1960s 1970s 1980s 1990s 2000s

EE141 VLSI Test Principles and Architectures

5

Introduction

Importance of Testing

Moore’s Law results from decreasing feature size (dimensions)

from 10s of µm to 10s of nm for transistors and interconnecting wires

8

Introduction

Testing During VLSI Development

Design verification targets design errors

Corrections made prior to fabrication

Design Specification Design Fabrication Packaging Quality Assurance Design Verification Wafer Test Package Test Final Testing

vlsi design

Group III: missing electron, called hole (p-type)

60

80

ECE Department, University of Texas at Austin

Lecture 2: Transistors, Fabrication, Layout

40 120

60

80

ECE Department, University of Texas at Austin

Lecture 2: Transistors, Fabrication, Layout

J. A. Abraham, August 29, 2011

1 / 43

The Elements (Periodic Table)

August 29, 2011

80

ECE Department, University of Texas at Austin

Lecture 2: Transistors, Fabrication, Layout

J. A. Abraham, August 29, 2011

1 / 43

Conductivity in Silicon Lattice

Body (bulk) is commonly tied to Ground (0 V)

mm When the gate is 40 a low voltage at 60 P-type body is at low voltage 80 100 120

Source-body and drain-body diodes are OFF No current flows, transistor is OFF

版VLSI系统设计.ppt

VLSI系统设计-7 .1 (3)

东南大学电子科学与工程学院

7.1 VLSI可测试性的重要性

测试的基本考虑:

转变测试思想,直接对电路内各个节点的测试; 分块测试,降低测试的复杂性,利用模块化设计的特 点; 增加附加逻辑和电路,改进其可控制性和可观察性, 覆盖全部的硬件节点; 添加自检测模块,使测试具有智能化和自动化。 这些技术和方法的应用就是系统的可测试性设计。

端点号i 11 12 13 14 15 16 17 18 19

CC0(i) 5 8 16 3 3 15 23 16 24

CC1(i) 7 6 14 3 3 13 21 14 22

VLSI系统设计-7.2 (27)

东南大学电子科学与工程学院

8号节点的可控制性最差

修改后,8号节点的0值可 控制性函数值为9。

VLSI系统设计-7 .1 (4)

东南大学电子科学与工程学院

7.2 测试基础

内部节点测试方法的测试思想

通过对系统输入一定的测试矢量,在系统的输出端观察 到所测节点的状态。这时的测试矢量的作用是控制被测试节 点的状态,并且将该节点的状态效应传送到输出观察点。

对节点的测试方法(对比法): 假设在待测试节点存在一个故障状态,然后反映和传送 这个故障到输出观察点(假设)。 实测中如果在输出观察点测到该故障效应,则说明该节 点确实存在假设的故障,如果不是故障效应则说明该节点不 存在假设的故障(实测)。

7.2 测试基础

测试矢量生成

生成测试矢量包括三个环节:

为了能够反映在电路内部节点所存在的故障,必须对该节 点设置正常逻辑值,设置的正常逻辑值应为假设的故障值的非 量。

为了能够将故障效应传播到某个原始输出,则沿着故障传 播路径的所有逻辑门必须被选通,这被称为敏化。

Introduction to VLSI Design

Mask costs (tooling needed to create IC) NRE fabrication charges (fabs are VERY expensive)

The Bad News

Although the cost of manufacturing IC„s remained approximately constant, the design cost did not. In fact, while designer productivity has improved with time, it has not increased a the same rate as the complexity of the chips. So the cost of the chip design is growing exponentially with the complexity of the circuit. The integrating of a system on a piece of silicon has an attractive manufacturing cost but frightening design cost and risk. Need to build very complex stuff. Many chip costs are dominated by amortized design cost and not fabrication cost. ASIC design is $10-20M/chip, custom design is larger than that.

Invention of IC

VIAVI Solutions 光纤连接器端面质量检查最佳实践指南说明书

Executive SummaryIt is widely known in the fiber optic industry that scratches, defects, and dirt on fiber optic connector end faces negatively impact network performance. As bandwidth requirements continue to grow and fiber penetrates further into the network, dirty and damaged optical connectors increasingly impact the network. If dirty and damaged end faces are not dealt with systematically, these defects can degrade network performance and eventually take down an entire link.In the effort to guarantee a common level of performance from the connector, the International Electrotechnical Commission (IEC) created Standard 61300-3-35, which specifies pass/fail requirementsfor end face quality inspection before connection. Designed to be a common reference of product quality, use of the IEC Standard supports product quality throughout the entire fiber optic life cycle, but only when compliance to the standard occurs at each stage. In response, current best practices recommend systematic proactive inspection of every fiber optic connector end face before connection. While current research shows that this practice is eliminating the installation of contaminated fibers and improving network performance, the uncontrollable variables of technician eyesight and expertise, ambient lighting, and display conditions keep manual inspectionand analysis from being a 100-percent reliable and repeatable method of assuring IEC compliance. In addition, because manual inspection does not create a record of the inspection process, certification of quality at the point of installation is not practical.Because compliance to the IEC Standard is the onlyway to achieve the promise of today’s fiber-rich, high-connectivity networks, this white paper proposesthe automation of the inspection process throughthe addition of analysis software programmed to the Standard’s pass/fail criteria to the practice of systematic proactive inspection.Automation of the systematic proactive inspection process using software programmed to the IEC Standard eliminates the variables associated with manual inspection, provides a documentable record of the quality of the connector end face at the point of installation, and provides a 100-percent repeatable and reliable process.White PaperAchieving IEC Standard Compliance for Fiber Optic Connector Quality through Automation of the Systematic Proactive End Face Inspection ProcessCombined, these benefits make automated end face inspection the most effective method available to assure and certify compliance to the IEC Standard throughout the fiber optic product life cycle, and achieve the promise of next-generation networks.IEC Standard 61300-3-35IEC Standard 61300-3-35 is a global common set of requirements for fiber optic connector end face quality designed to guarantee insertion loss and return loss performance. The Standard contains pass/fail requirements for inspection and analysis of the end face of an optical connector, specifying separate criteria for different types of connections (for example, SM-PC, SM-UPC, SM-APC, MM, and multi-fiber connectors). For more detail onthe Standard, copies of the copyrighted document are available for purchase at by searching for “61300-3-35”.These criteria are designed to guarantee a common level of performance in an increasingly difficult environment where fiber is penetrating deeper into the network and being handled by more technicians, many of whom may be unfamiliar with the criticality of fiber optical connector end face quality or possess the experience and technical knowledge required to properly assess it.Figure 1. Fiber Optic Product Life CycleThe standard is designed to be used as a common quality reference between supplier and customer, and between work groups in several ways:y As a requirement from the customer to the supplier (for example, integrator to component supplier or operator to contractor)y As a guarantee of product quality and performance from the supplier to the customer (for example, manufacturer to customer, contractor to network owner, or between work groups within an organization)y As a guarantee of network quality and performance within an organizationAs more stages in the fiber optic product life cycle, shown in Figure 1, are outsourced to disparate vendors, the standard takes on renewed importance in ensuring the optimized performance of today’s fiber-dense networks.The Development of the IEC StandardThe quality values used in the IEC standard are the result of years of extensive testing of scratched, damaged,or dirty optical connectors conducted by a coalition of industry experts including component suppliers, contract manufacturers, network equipment vendors, test equipment vendors, and service providers. This work has been published previously in a number of papers as noted in the References section of this paper.Understanding the variables and limitations of manual visual inspection, fiber optic test and measurement manufacturer VIAVI contributed its automated objective inspection and analysis software FiberChek2™, as illustrated in Figure 2, to the IEC for use in the development of the 61300-3-35 visual inspection standard. Automating the pass/fail process using research-based parameters extracted from testing conducted by the aforementioned industry coalition provided the IEC with a repeatable standard of quality that would guarantee a common level of performance, creating a positive impact on both product and network performance.More than 8 years of testing on a constantly expanding database of fibers and fiber devices (for example, SM, MM, Ribbon, E2000, SFP/XFP, Bend-insensitive fibers, Lenses, and other interfaces), combined with widespread use in the industry by component manufacturers, integrators/CMs, OEMs, third-party installers, and service providers, makes the VIAVI software program the only proven automated objective inspection software program that assures compliance to the IEC standard at every step of the fiber optic life cycle.Testament to this is the fact that this software program is currently used by three of the top five U.S. cable assembly manufacturers, along with six of the largest optical component manufacturers, five of the largest network equipment vendors, and five of the top Network Service Providers (NSPs) in the world, making VIAVI FiberChek2 software the current worldwide industry standard for automated objective fiber optic connector end face inspection.Figure 2. Example of the Proven Inspection and Analysis Software Program FiberChek2 from VIAVIThe criteria in the IEC Standard requires the user to know the exact location and size of surface defects (for example, scratches, pits, and debris) on the fiber optic connector end face. As a result, it is only through the use of automated inspection and analysis software that compliance to the IEC Standard (or customer specification) can be tested and certified.The combination of common requirements (the IEC Standard) and automated inspection and analysis (FiberChek2) have measurably impacted product quality through the supply chain. This is providing improved repeatability and stability of inspection analysis throughout the fiber optic product life cycle, ensuring consistent product performance regardless of the number and expertise of vendors and technicians involved in the manufacture, installation, and network administration processes.Proactive Inspection Model: Step One Toward Achieving IEC ComplianceDespite its role in the development of the IEC Standard and usage by industry leaders, automated inspection and analysis software is not yet in widespread use across the fiber optic industry. In an effort to enable compliance to the Standard even when using manual visual inspection equipment alone, IEC and industry leaders are supporting the promotion of fiber handling best practices. An example of one such educational effort is the proactive inspection model developed and promoted by fiber optic test equipment manufacturer VIAVI, “Inspect Before You Connect” (IBYC), as illustrated in Figure 3.The simple four-step IBYC model, which supports and is mandated by the IEC Standard, effectively guides technicians of varying levels of expertise in the proper implementation of systematic proactive inspection. y Step 1 Inspect: Use the microscope to inspect the fiber. If the fiber is dirty , go to Step 2. If the fiber is clean, go to Step 4.y Step 2 Clean: If the fiber is dirty , use a cleaning tool to clean the fiber end face.y Step 3 Inspect: Use the microscope to re-inspect and confirm the fiber is clean. If the fiber is still dirty , go back to Step 2. If the fiber is clean, go to Step 4.y Step 4 Connect: If both the male and female connectors are clean, they are ready to connect.Consistent use of the IBYC model ensures that proactive inspection is performed correctly every time and that fiber optic end faces are clean prior to mating connectors, eliminating the installation of dirty or damaged fibers into the network and optimizing network performance. As a result, IBYC has been incorporated intomanufacturing procedures for the majority of the world’s leading organizations using fiber, increasing knowledge of this process and helping it become routine practice around the world.Automated Inspection and Analysis: Achieving and Certifying IEC ComplianceEven with the aid of the IBYC model, manual inspection using only a video microscope can be difficult depending on the technician’s expertise and can result in variable connector quality and network performance. Reliant on technician eyesight and expertise along with variable display settings and ambient lighting, manual inspection and analysis is not 100 percent reliable, repeatable, or certifiable. Because it produces no visual record of the end face condition in the manual inspection process, certifying compliance at the point of installation through images or reporting is both unreliable and impractical, as Figure 4a shows.To ensure IEC compliance is achieved, automated inspection of fiber optic connector end faces using inspection and analysis software built on the IEC Standard’s pass/fail criteria is the most effective method available. With it technicians of all skill levels can effectively accomplish both compliance and certification through images andreports, as Figure 4b shows.PASSFigure 4b. Automated Inspection gives technicians a pass or fail result.Figure 4a. Manual Inspection requires technicians to judge whether the connector complies with the IEC Standard.Using the software, automated inspection and analysis can produce a visual record of the end face condition as shown in Figure 5, which can be used in reports and archived for future reference.)As a result, automated inspection and analysis presents several clear advantages over subjective inspection:y Eliminates variation in resultsy Certifies and records product quality at time of inspectionFigure 5. Automated inspection enables the technician to certify compliance to the standard byproducing a date stamped test report.y Enables technicians of all skill levels to certify quality reliably and systematicallyy Makes advanced pass/fail criteria simple to usey Improves product and network performance and yieldsUsing a fiber optic inspection and analysis software program that is preloaded with the IEC Standard specifications, such as VIAVI FiberChek2 software, any technician can effectively:y Inspect and certify compliance with IEC 61300-3-35 or other customer-specified standards at every stage of the fiber optic product life cycle at the push of a buttony Implement simple pass/fail acceptance testing; no skill in quality judgment is necessaryy Generate detailed analysis reports that can be archivedConclusion: Business Impact of Automated End Face AnalysisThe combination of common requirements (the IEC Standard) and automated fiber optic inspection and analysis software (FiberChek2) has positively impacted product quality across the supply chain. The business impacts of reliable, repeatable automated fiber optic connector inspection and certification include:y Insured and repeatable product quality through the quantification of connector end face condition at installationy Assurance of customer satisfaction and supplier protection through the reliable documentation of connector end face qualityy Competitive advantage for component and system vendors, and for installation contractors who can cost-effectively document end face qualityy A common, repeatable system provides correlation through the supply chainy Easy deployment of custom requirements analysisCombined, these benefits make automated end face inspection the most effective method available to assure and certify compliance to the IEC Standard throughout the fiber optic product life cycle, and achieve the promise of next-generation networks.© 2021 VIAVI Solutions Inc. Product specifications and descriptions in this document are subject to change without notice.Patented as described at /patents iecinspect-wp-fit-tm-ae 30168245 900 1010C ontact Us +1 844 GO VIAVI (+1 844 468 4284)To reach the VIAVI office nearest you, visit /contact VIAVI Solutions References1. “Qualification of Scattering from Fiber Surface Irregularities,” Journal of Lightwave T echnology , V .20, N 3, April 2002,pp. 634−637.2. “Optical Connector Contamination/Scratches and its Influence on Optical Signal Performance,” Journal of SMTA, V .16, Issue 3, 2003, pp. 40−49.3. “At the Core: How Scratches, Dust, and Fingerprints Affect Optical Signal Performance,” Connector Specifier, January2004, pp. 10−11.4. “Degradation of Optical Performance of Fiber Optics Connectors in a Manufacturing Environment,” Proceedings ofAPEX2004, Anaheim, California, February 19−Feb 26, 2004, pp. PS-08-1-PS-08-4.5. “Cleaning Standard for Fiber Optics Connectors Promises to Save Time and Money”, Photonics Spectra, June 2004,pp. 66−68.6. “Analysis on the effects of fiber end face scratches on return loss performance of optical fiber connectors”, Journalof Lightwave T echnology , V .22, N 12, December 2004, pp. 2749−2754.7. “Development of Cleanliness Specification for Single-Mode Connectors,” Proceedings of APEX2005, Anaheim,California, February 21−26, 2005, pp. S04-3-1, 16.8. “Keeping it clean: A cleanliness specification for single-mode connectors,” Connector Specifier, August 2005, pp.8−10.9. “Contamination Influence on Receptacle T ype Optical Data Links,” Photonics North, 2005, T oronto, Canada,September 2005.10. “Development of Cleanliness Specifications for 2.5 mm and 1.25 mm ferrules Single-Mode Connectors,” Proceedingsof OFC/NFOEC, Anaheim, California, March 5−10, 2006.11. “Standardizing cleanliness for fiber optic connectors cuts costs, improves quality ,” Global SMT & Packaging, June/July 2006, pp. 10−12.12. “Accumulation of Particles Near the Core during Repetitive Fiber Connector Matings and De-matings,” Proceedingsof OFC/NFOEC2007, Anaheim, CA, March 25−29, 2007, NThA6, pp.1−11.13. “Development of Cleanliness Specifications for Single-Mode, Angled Physical Contact MT Connectors,” Proceedingof OFC/NFOEC2008, San Diego, February 24−28, 2008, NThC1, pp. 1−10.14. “Correlation Study between Contamination and Signal Degradation in Single-Mode APC Connectors,” Proc. SPIE, Vol.7386, 73861W (2009); doi:10.1117/12.837545.。

vlsi_精品文档

VLSIIntroductionVLSI (Very Large Scale Integration) refers to the process of miniaturizing electronic circuits through the integration of thousands, millions, or even billions of transistors onto a single chip. This integration allows for the production of complex and powerful electronic devices, such as microprocessors, memory chips, and digital signal processors. In this article, we will explore the key concepts and advancements in VLSI technology.Evolution of VLSIVLSI technology has rapidly evolved since its inception in the 1970s. The early developments in VLSI focused on reducing the size of individual transistors, which led to the production of microprocessors and memory chips. As the technology progressed, the number of transistors that could be integrated onto a single chip increased significantly. This led to the rise of complex systems-on-chip (SoCs) that contain multiple components, including processors, memory, and peripherals.Manufacturing ProcessThe manufacturing process of VLSI chips involves several key steps. The process begins with the design of the circuit using a hardware description language (HDL) such as Verilog or VHDL. The designed circuit is then divided into several layers, each representing a specific component or function. These layers are transferred onto a silicon wafer through a process called photolithography.Once the layers are transferred, the silicon wafer goes through a series of etching and deposition steps to create the transistors and interconnects. This is followed by the application of various materials to form the gate insulation, metal layers, and contacts. Finally, the wafer is cut into individual chips, and each chip undergoes testing to ensure its functionality.Advancements in VLSIThe advancements in VLSI technology have been driven by Moore’s Law, which states that the number of transistors on a chip doubles approximately every two years. This trend has enabled the production of higher-performance and lower-power chips. Some of the key advancements in VLSI include:1. Shrinking Transistor SizesAs technology has progressed, the size of transistors has continued to shrink. This allows for more transistors to be integrated onto a single chip, resulting in increased processing power and efficiency.2. Introduction of FinFET TechnologyFinFET is a transistor design that provides better control over the flow of current. Compared to traditional planar transistors, FinFETs offer improved performance and power efficiency, making them ideal for modern VLSI chips.3. Integration of System-on-Chip (SoC)SoCs are integrated circuits that contain multiple components, such as processors, memory, and peripherals, on a single chip. This integration enables the production of compact and efficient devices, including smartphones, tablets, and IoT devices.4. Advanced Packaging TechniquesTo accommodate the increasing complexity of VLSI chips, advanced packaging techniques have been developed. These techniques, such as 3D stacking and system-in-package (SiP), allow for the integration of multiple chips, sensors, and other components into a single package, improving performance and reducing size.Applications of VLSIVLSI technology finds its applications in various sectors, including:1. Consumer ElectronicsVLSI chips are used in consumer electronics devices such as smartphones, tablets, televisions, and gaming consoles. These chips enable the high-performance computing and advanced features found in modern gadgets.2. Automotive IndustryVLSI chips are used in the automotive industry for various applications, including engine control units, driver-assistance systems, infotainment systems, and vehicle connectivity.3. Medical DevicesVLSI chips play a crucial role in medical devices such as pacemakers, implantable sensors, and medical imaging equipment. These chips enable the processing and transmission of data in real-time, enhancing the efficiency and effectiveness of medical procedures.4. Communication SystemsVLSI technology is essential in the telecommunications industry for the development of high-speed data communication systems, such as routers, switches, and network processors.Future TrendsAs VLSI technology continues to advance, several future trends are expected to shape its development:1. More MiniaturizationThe constant drive for miniaturization will continue, enabling the integration of even more transistors onto a single chip. This will lead to the development of highly powerful and efficient electronic devices.2. Emergence of AI HardwareWith the increasing demand for artificial intelligence (AI) applications, specialized hardware for AI processing, such as AI accelerators and neural network processors, will become more prevalent in VLSI designs.3. Advanced Packaging TechniquesThere will be further advancements in packaging techniques, enabling the integration of chips and components with heterogeneous technologies. This will facilitate the development of highly integrated and complex systems.4. Focus on Power EfficiencyAs power consumption remains a critical concern, VLSI designs will continue to focus on reducing power consumption while maintaining high performance. This will involve the incorporation of power-management techniques and low-power design methodologies.ConclusionVLSI technology has revolutionized the electronics industry by enabling the production of powerful and complex electronic devices. With advancements in transistor technology, packaging techniques, and system integration, VLSI chips have become indispensable in various applications. As the technology continues to evolve, we can expect further miniaturization, the emergence of specialized AI hardware, and a focus on power efficiency in future VLSI designs.。

VLSI设计基础4

4.4.3 门阵列在VLSI设计中的应用形式

门阵列是一种规则阵列形式的版图,与前面介绍 的晶体管规则阵列所不同的是,在前述的晶体管规则 阵列中,版图和电路形式是相关的,运用什么样的版 图必须有配套的电路设计方法。门阵列版图对电路设 计没有严格的要求,可以完全按照人们习惯的设计方 式构造电路,不必考虑逻辑的表达式应是什么形式。

动态NMOS或非结构ROM

4.1.2 ROM版图

1. NMOS或非结构ROM版图

2. NMOS与非结构ROM版图

例题:按照真值表,用NMOS或非ROM结构电路实现逻辑。

4.2 MOS晶体管开关逻辑

MOS开关晶体管逻辑是建立在“传输晶体管” 或“传输门”基础上的逻辑结构,所以又称为传输 晶体管逻辑。信号的传输是通过导通的MOS器件, 从源传到漏或从漏传到源。这时的信号接受端的逻 辑值将同时取决于信号的发送端和MOS器件栅极的 逻辑值。

4.3.2 “或非-或非”阵列结构

Z abcacd bd

当用“或非-或非”结构PLA实现逻辑时必须输入取反、 输出取反。

4.3.3 多级门阵列(MGA)

MGA是在PLA基础上变化而成的多级门结构,虽然 它被称为门阵列,实际上它是多级PLA的组合,一个最明 显的标志是它对输入、输出位置的限制。

因为在每块PLA中,“与平面”只能外部输入,内部 输出,“或平面”只能内部输入,外部输出。

固定门阵列采用预加工技术,就是说,在工厂里预先 就加工了一些规格化的门阵列母片,这些母片已完成了 主要的工艺流程,母片上已沉积了金属层。所谓固定就 是固定大小、固定结构、固定I/O数量的门阵列。

固定大小就是对某一个预先制作的母片,它的门数是 固定的,如500门、1000门、5000门,等等。

TL471标准-中文-老版本

安全带系统总成及高度调节装置材料及功能要求(TL 471)安全带系统总成及高度调节装置注意:首次供货及修改的批准,按照1、原理草图、定义1.1 安全腰带(图)1.2 带缩卷器的安全腰带(图)1.3 三点式安全带(图)1.4 带缩卷器的三点式安全带1.5 大众自动安全带(VW-RA)1.6 ELRA(电控自动安全带)2、总则2.1 结构型式:按图纸;如果图纸要求与供货技术条件不一致则以图纸为准2.2 适用范围:前座及后座的按第1节的所有安全带2.3 使用范围:采用ECE、EG、或US(美国)要求的国家2.4 安全带要求:按TL-4702.5开关、安全带报警系统按TL-904及TL-820632.6 标记2.6.1 零件:按照图纸2.6.2 安全带2.6.2.1法定标记每种安全带必须具有耐久而清晰的安全带符号和符合法规的标记2.6.2.2商标、零件号除法定标记外,还要以标出商标和零件号。

2.7 有关的法律和规章USA(美国):美国法规571.209;571.208ECE(欧经会):R16.04EG(欧共体):77/541,81/576,82/319澳大利亚:4/00如果图纸中TL编号上标有秃宝盖记号或有图纸中出现有相应的TLD编号,则有秃宝盖记号的章节需要提出证明,文件应保存10年。

2.8 试验次序必须绝对按照下面的章节编号次序来进行试验,此外还须明确地说明这一点。

2.9试验设备如无其他规定,应有采用符合法规和规章的试验设备2.10禁镉要求按VW501152.11禁止石棉要求不得以任何形式使用石棉3、附件及塑料件定义:所谓附件是指安全带系统的所有零件,它们直接固定有汽车车身上,并包括闭锁和缩卷器。

3.1耐腐蚀性(金属件)在金属件上不得出现红锈,锌腐蚀允许最多达到表面的5%。

在试验之后,按照本供货技术条件的有关章节的功能还必须保证良好,对于缩卷宗器,在本试验之前,应进行按照5.1节有室温下的试验,以及按第5.3节和第5.4节的试验。

VLSI测试方法学和可测性设计

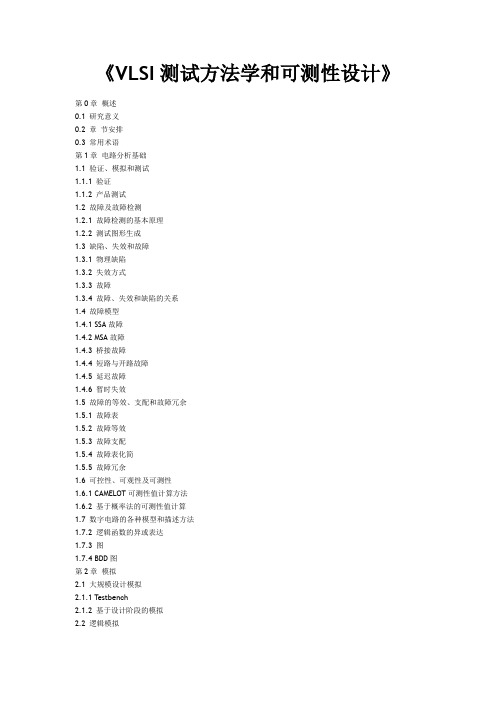

《VLSI测试方法学和可测性设计》第0章概述0.1 研究意义0.2 章节安排0.3 常用术语第1章电路分析基础1.1 验证、模拟和测试1.1.1 验证1.1.2 产品测试1.2 故障及故障检测1.2.1 故障检测的基本原理1.2.2 测试图形生成1.3 缺陷、失效和故障1.3.1 物理缺陷1.3.2 失效方式1.3.3 故障1.3.4 故障、失效和缺陷的关系1.4 故障模型1.4.1 SSA故障1.4.2 MSA故障1.4.3 桥接故障1.4.4 短路与开路故障1.4.5 延迟故障1.4.6 暂时失效1.5 故障的等效、支配和故障冗余1.5.1 故障表1.5.2 故障等效1.5.3 故障支配1.5.4 故障表化简1.5.5 故障冗余1.6 可控性、可观性及可测性1.6.1 CAMELOT可测性值计算方法1.6.2 基于概率法的可测性值计算1.7 数字电路的各种模型和描述方法1.7.2 逻辑函数的异或表达1.7.3 图1.7.4 BDD图第2章模拟2.1 大规模设计模拟2.1.1 T estbench2.1.2 基于设计阶段的模拟2.2 逻辑模拟2.2.1 编译模拟2.2.2 事件驱动模拟2.2.3 延迟模型2.3 故障模拟2.3.1 并行故障模拟2.3.2 演绎故障模拟2.3.3 并发性故障模拟2.3.4 故障模型结果分析第3章组合电路的测试3.1 简介3.2 异或法3.2.1 异或法3.2.2 不可检测故障3.2.3 多输出电路3.3 布尔差分3.3.1 对原始输入节点的布尔差分3.3.2 布尔差分的性质3.3.3 对电路内部节点的布尔差分3.4 路径敏化法3.4.1 确定性算法的基本过程3.4.2 无扇出分支的路径敏化法3.4.3 有扇出分支的路径敏化法3.5 D算法3.5.1 D算法关键术语3.5.2 D算法的基本步骤3.5.3 D算法举例3.6 PODEM算法3.6.1 PODEM算法思路3.6.2 PODEM算法流程3.6.3 PODEM算法举例3.7 其他测试生成算法3.7.1 FAN算法3.7.2 其他算法第4章时序电路的测试4.1 时序电路测试的概念4.2 时序电路的功能测试4.2.1 时序电路的检查序列4.2.2 时序电路功能测试4.3 时序电路的确定性测试生成4.3.1 时序电路的模型4.3.2 时序电路的测试生成模型4.3.3 扩展的向后驱赶算法4.3.4 扩展的向后驱赶算法举例4.4 时序电路的其他测试生成方法4.4.1 FASTEST算法4.4.2 CONTEST算法第5章专用可测性设计5.1 概述5.2 可测性分析5.2.1 可控性值的估计5.2.2 可观性值5.2.3 SCOAP算法描述5.2.4 可测性度量的应用5.3 可测性的改善方法5.3.1 插入测试点5.3.2 电路分块5.4 容易测试的电路5.4.1 C可测性5.4.2 变长测试5.5 组合电路的可测性设计5.5.1 用Reed-Muller模式设计组合电路5.5.2 异或门插入法5.5.3 组合电路的其他可测性设计方法5.6 时序电路可测性设计中的问题5.6.1 时序电路的初始化设计问题5.6.2 时间延迟效应的最小化5.6.3 逻辑冗余问题5.6.4 避免设计中非法状态5.6.5 增加逻辑以控制振荡第6章扫描路径法6.1 简介6.2 扫描路径设计6.2.1 基本的扫描路径设计6.2.2 部分扫描设计6.2.3 隔离的串行扫描设计6.2.4 非串行的扫描设计6.3 扫描路径的测试方法6.3.1 组合电路部分的测试生成6.3.2 测试施加6.3.3 扫描路径测试举例6.4 扫描路径设计及测试举例6.5 扫描路径的结构6.5.1 双口触发器和电平敏化锁存器6.5.2 电平敏化扫描设计6.5.3 随机编址的存储单元第7章边界扫描法7.1 边界扫描法的基本结构7.2 测试存取通道及控制7.2.1 测试存取通道的信号7.2.2 TAP控制器7.2.3 TAP控制器的操作7.3 寄存器及指令7.3.1 指令寄存器7.3.2 测试数据寄存器7.3.3 指令7.4 操作方式7.4.1 正常操作7.4.2 测试方式操作7.4.3 测试边界扫描寄存器7.5 边界扫描描述语言7.5.1 主体7.5.2 BSDL描述器件举例第8章随机测试和伪随机测试8.1 随机测试8.1.1 随机测试的概念8.1.2 故障检测率的估算8.1.3 测试图形长度的计算8.1.4 输入变量的优化8.2 伪随机序列8.2.1 同余伪随机序列8.2.2 反馈移位寄存器和异或门构成的伪随机序列生成电路8.3 LFSR的数学基础8.3.1 根据本原多项式优化伪随机序列发生电路8.3.2 LFSR的运算8.3.3 M序列的特性8.4 伪随机测试序列生成电路8.4.1 外接型PRSG8.4.2 内接型PRSG8.4.3 混合连接型PRSG8.5 与M序列相关的序列的生成方法8.5.1 Ford序列8.5.2 De Bruijn序列8.6 低功耗测试序列8.6.1 RSIC序列生成原理8.6.2 RSIC序列的数学表达8.6.3 RSIC序列的特性第9章内建自测试9.1 内建自测试的概念9.1.1 内建自测试简介9.1.2 内建自测试的结构9.1.3 内建自测试的测试生成9.2 响应数据压缩9.2.2 "1"计数9.2.3 跳变次数压缩9.3 特征分析法9.3.1 特征分析原理9.3.2 串行输入特征寄存器9.3.3 多输入的特征分析9.4 内建自测试的结构9.4.1 内建自测试9.4.2 自动测试9.4.3 循环内建自测试9.4.4 内建逻辑块观测器9.4.5 随机测试组合块9.4.6 STUMPS第10章电流测试10.1 简介10.2 IDDO测试机理10.2.1 基本概念10.2.2 无故障电路的电流分析10.2.3 转换延迟10.3 IDDO测试方法10.3.1 片外测试10.3.2 片内测试10.4 故障检测10.4.1 桥接10.4.2 栅氧10.4.3 开路故障10.4.4 泄漏故障10.4.5 延迟故障10.5 测试图形生成10.5.1 基于电路级模型的测试图形生成10.5.2 基于泄漏故障模型的测试图形生成10.6 深亚微米技术对电流测试的影响第11章存储器测试11. 1 存储器电路模型11.1.1 功能模型11.1.2 存储单元11.1.3 RAM组成11.2 存储器的缺陷和故障模型11.2.1 缺陷11.2.2 阵列故障模型11.2.3 周边逻辑11.3 存储器测试的类型11.3.1 性能测试11.3.3 功能测试11.3.4 电流测试11.4 存储器测试算法11.4.1 MSCAN算法11.4.2 GALPAT算法11.4.3 算法型测试序列11.4.4 Checkerboard测试11.4.5 Marching图形序列11.4.6 March测试的表达方法11.4.7 各种存储器测试算法的分析11.5 存储器测试方法11.5.1 存储器直接存取测试11.5.2 存储器内建自测试11.5.3 宏测试11.5.4 各种存储器测试方法比较11.6 存储器的冗余和修复第12章SoC测试12.1 SoC测试的基本问题12.1.1 SoC核的分类12.1.2 SoC测试问题12.1.3 存取、控制和隔离12.2 概念性的SoC测试结构12.2.1 测试源和测试收集12.2.2 测试存取机构12.2.3 测试壳12.3 测试策略12.3.1 核的非边界扫描测试12.3.2 核的边界扫描测试策略12. 4 IEEE P1500标准12. 5 SoC测试再探索。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

ECE-C471Introduction to VLSI Design Syllabus Baris Taskin Lecture:Mon10:00am-12:00pm Bossone413F Lab:Fri11:00am-1:00pm

Course Information

Course Title:Introduction to VLSI Design

Course Type:Undergraduate–Senior

Credits:3credits

Duration:Fall Quarter

Meeting Times:Lectures:Once a week for2hours

Laboratory:Once a week for2hours

Prerequisites

This course is intended for senior-level ECE undergraduate students.

Knowledge of digital logic design(ECE200)and introductory eletronics(ECE-L301-302) is required.Previous exposure to transistors and semiconductor devices would be useful,but not required.These introductory topics will be discussed in early stages of the course to provide necessary technical background to all students from EE and CE.

Course Description

This is an introductory course in thefield of Very Large Scale Integration(VLSI)circuit and systems design.Systematic understanding,design and analysis of VLSI integrated circuits will be covered.This course will focus exclusively on digital CMOS VLSI systems design,although some issues in mixed-signal mode will also be addressed.

The course will begin with a review of CMOS transistor operation and semiconductor man-ufacturing process.Logic design with CMOS transistors and circuit families will be described. Specifically,layout,design rules,and circuit simulation will be addressed.

Course objectives include:

•To learn the basic concepts of modern VLSI circuit design by studying logic design,physical structure and fabrication of semiconductor devices,

•To analyze the electrical and design characteristics of transistors and gates,

•To observe the integration of these devices into complicated high-performance systems,•To understand the role of computer-aided design(CAD)tools in automating the designflow and providing improved productivity in VLSI systems design,

•To understand the relationship between semiconductor technology,transistors and architec-ture,addressing all levels of hierarchy in VLSI system designflow.

1

Course Structure

Laboratory:Once a week for2hours,five(5)assignments

Exam(s):One(1)final examination.

Homework(s):Two(2)homeworks will be assigned.

Project(s):None

This is a senior level undergraduate level class and the evaluation criteria is established accord-ingly.The evaluation process will encompass the monitoring of not the quality of individual work but also participation in group projects and lectures.Thefinal grade will be calculated as follows:

Final→30%

Homework(s)→30%

Lab assignment(s)→40%

Total100%

Textbook

Following is a list of suggested textbooks for this course,starting with the required textbook by J.M.Rabaey,A.Chandrakasan and B.Nikolic.The additional textbooks1through3provide much additional information and can be quite useful.

Required Textbook:J.M.Rabaey,A.Chandrakasan and B.Nikolic,Digital Integrated Cir-

cuits,Prentice Hall,2003,ISBN:0130909963.

Additional Reading: 1.John P.Uyemura,Introduction to VLSI Circuits and Systems:A

Design Perspective Prentice-Hall,Inc.,2002.

2.N.H.Weste and D.Harris,CMOS VLSI Design:A Circuits and

Systems Perspective,Addison-Wesley,2nd ed.,2004.

3.S.M.Kang and Y.Leblebici,CMOS Digital Integrated Circuits Anal-

ysis&Design,McGraw-Hill Inc.,2002.

Laboratory

Weekly design and simulation assignments using Cadence CAD tools.Specifically,Cadence Virtuoso tool for layout,Analog Artist using simulators Spice and Spectre for simulation and Diva for DRC will be used.

Weekly assignments will include:

•CMOS Inverter

•CMOS NAND and NOR gates

•XOR and MUX gates

•Learning about data paths:A simple combinational circuit(i.e.2-bit adder)

2

Tentative Schedule

Week Lecture Lab

1Introduction to VLSI Systems

2CMOS Fabrication

3HSPICE Simulation SPICE assignment 4Layout Design:Rules,Models,CAD CMOS inverter design 5Interconnect Wires HW#1

6Static CMOS Inverter:Speed,Power,Area,Scaling CMOS NAND and NOR 7Layout Techniques for Complex Gates CMOS XOR and MUX 8Power Consumption

9Combinational Logic1:Standard Cells,Circuit Families2-bit Adder

10Combinational Logic2:Low Power CMOS

11Sequential Logic1:Registers,Clock,Timing HW#2

12Sequential Logic2:Clock,Timing

Final Examination(Date TBA)

3。