CCM1648中文资料

货物贸易外汇监测系统(企业版)

货物贸易外汇监测系统(企业版)访问设置手册一、系统使用要求为能正常使用货物贸易外汇监测系统提供的功能,货物贸易外汇监测系统对系统用户的计算机环境要求如下:●Windows操作系统;●IE浏览器,支持IE6、IE7和IE8;●Java运行环境,需要jre1.4.2及以上版本,建议从本系统下载;●Microsoft Office Excel ,支持Excel 2003和Excel2007;●能够访问互联网。

二、浏览器设置通过国家外汇管理局应用服务平台(以下简称“应用服务平台”)登录和使用货物贸易外汇监测系统(企业版),首先需要对用户客户端的浏览器进行必要的设置。

浏览器版本要求为IE6.0及以上,以下操作均以WINDOWS XP操作系统,浏览器IE8.0为例。

(一)受信站点设置1、打开IE浏览器,选择菜单“工具”,点击“Internet 选项”,如图2-1所示:图2-12、在“Internet 选项”弹出窗口中,选择“安全”页,单击选中“可信站点”,然后点击右下“默认级别(D)”按钮,设置受信任站点的安全级别为“低”。

如图2-2所示:图2-23、点击“站点(S)”按钮,在可信站点维护窗口中添加国家外汇管理局应用服务平台地址、货物贸易外汇监测系统地址和。

具体操作参见图2-3和图2-4。

点击确定保存设置并返回“Internet 选项”窗口。

图2-3注意:该选项不能选中图2-44、最后在“Internet 选项”窗口点击确定按钮保存所有设置。

(二)兼容性视图设置如果浏览器是IE8版本,还应设置兼容模式,具体如下:1、打开IE 8浏览器后,点击浏览器“工具(T)”菜单,勾选“兼容性视图”,如图2-5所示:图2-52、然后点击“兼容性视图设置”,在设置窗口中勾选“在兼容性视图中显示所有网站”。

如图2-6所示:图2-6(三)弹出窗口设置打开IE浏览器,点击“工具”—“弹出窗口阻止程序”,在下一级菜单中选择“关闭弹出窗口阻止程序”,如图2-7所示:图2-7(四)cookie设置1、打开IE浏览器,选择菜单“工具”,点击“Internet 选项”。

UCP600的中英文版下载

ICC UNIFORM CUSTOMS AND PRACTICE FOR DOCUMENTARY CREDITSUCP 600英文FOREWORD (3)INTRODUCTION (5)ARTICLE 1 APPLICATION OF UCP (10)ARTICLE 2 DEFINITIONS (10)ARTICLE 3 INTERPRETATIONS (11)ARTICLE 4 CREDITS V. CONTRACTS (13)ARTICLE 5 DOCUMENTS V. GOODS, SERVICES OR PERFORMANCE (13)ARTICLE 6 AV AILABILITY, EXPIRY DATE AND PLACE FOR PRESENTATION (14)ARTICLE 7 ISSUING BANK UNDERTAKING (14)ARTICLE 8 CONFIRMING BANK UNDERTAKING (15)ARTICLE 9 ADVISING OF CREDITS AND AMENDMENTS (16)ARTICLE 10 AMENDMENTS (18)ARTICLE 11 TELETRANSMITTED AND PRE-ADVISED CREDITS AND AMENDMENTS19ARTICLE 12 NOMINATION (19)ARTICLE 13 BANK-TO-BANK REIMBURSEMENT ARRANGEMENTS (20)ARTICLE 14 STANDARD FOR EXAMINATION OF DOCUMENTS (21)ARTICLE 15 COMPLYING PRESENTATION (23)ARTICLE 16 DISCREPANT DOCUMENTS, W AIVER AND NOTICE (23)ARTICLE 17 ORIGINAL DOCUMENTS AND COPIES (25)ARTICLE 18 COMMERCIAL INVOICE (26)ARTICLE 19 TRANSPORT DOCUMENT COVERING AT LEAST TWO DIFFERENT MODES OF TRANSPORT (26)ARTICLE 20 BILL OF LADING (28)ARTICLE 21 NON-NEGOTIABLE SEA W AYBILL (31)ARTICLE 22 CHARTER PARTY BILL OF LADING (33)ARTICLE 23 AIR TRANSPORT DOCUMENT (34)ARTICLE 24 ROAD, RAIL OR INLAND W ATERW AY TRANSPORT DOCUMENTS (36)ARTICLE 25 COURIER RECEIPT, POST RECEIPT OR CERTIFICATE OF POSTING (38)ARTICLE 26 "ON DECK", "SHIPPER'S LOAD AND COUN T", “SAID BY SHIPPER TO CONTAIN〞AND CHARGES ADDITIONAL TO FREIGHT (38)ARTICLE 27 CLEAN TRANSPORT DOCUMENT (39)ARTICLE 28 INSURANCE DOCUMENT AND COVERAGE (39)ARTICLE 29 EXTENSION OF EXPIRY DATE OR LAST DAY FOR PRESENTATION (41)ARTICLE 30 TOLERANCE IN CREDIT AMOUNT, QUANTITY AND UNIT PRICES (41)ARTICLE 31 PARTIAL DRAWINGS OR SHIPMENTS (42)ARTICLE 32 INSTALMENT DRA WINGS OR SHIPMENTS (43)ARTICLE 33 HOURS OF PRESENTATION (43)ARTICLE 34 DISCLAIMER ON EFFECTIVENESS OF DOCUMENTS (43)ARTICLE 35 DISCLAIMER ON TRANSMISSION AND TRANSLATION (43)ARTICLE 36 FORCE MAJEURE (44)ARTICLE 37 DISCLAIMER FOR ACTS OF AN INSTRUCTED PARTY (45)ARTICLE 38 TRANSFERABLE CREDITS (45)ARTICLE 39 ASSIGNMENT OF PROCEEDS (48)UCP600中文版UCP600第一条UCP的适用范围 (48)第二条定义 (49)第三条解释 (50)第四条信用证与合同 (50)第五条单据与货物、效劳或履约行为 (51)第六条兑用方式、截止日和交单地点 (51)第七条开证行责任 (51)第八条保兑行责任 (52)第九条信用证及其修改的通知 (53)第十条修改 (53)第十一条电讯传输的和预先通知的信用证和修改 (54)第十二条指定 (54)第十三条银行之间的偿付安排 (54)第十四条单据审核标准 (55)第十五条相符交单 (56)第十六条不符单据、放弃及通知 (56)第十七条正本单据及副本 (57)第十八条商业发票 (57)第十九条涵盖至少两种不同运输方式的运输单据 (58)第二十条提单 (59)第二十一条不可转让的海运单 (60)第二十二条租船合同提单 (61)第二十三条空运单据 (62)第二十四条公路、铁路或内陆水运单据 (62)第二十五条快递收据、邮政收据或投邮证明 (63)第二十六条“货装舱面〞、“托运人装载和计数〞、“内容据托运人报称〞及运费之外的费用。

LCD12864液晶显示器中文说明(DOC)知识交流

一、液晶显示模块概述12864A-1汉字图形点阵液晶显示模块,可显示汉字及图形,内置8192个中文汉字(16X16点阵)、128个字符(8X16点阵)及64X256点阵显示RAM(GDRAM)。

主要技术参数和显示特性:电源:VDD 3.3V~+5V(内置升压电路,无需负压);显示内容:128列× 64行显示颜色:黄绿显示角度:6:00钟直视LCD类型:STN与MCU接口:8位或4位并行/3位串行配置LED背光多种软件功能:光标显示、画面移位、自定义字符、睡眠模式等二、外形尺寸1.外形尺寸图2.主要外形尺寸项目标准尺寸单位模块体积113.0×65.0×12.8mm定位尺寸105.0×55.0mm视域73.4×38.8 mm行列点阵数128×64dots点距离0.52×0.52 mm点大小0.48×0.48 mm二、模块引脚说明引脚号引脚名称方向功能说明1 VSS - 模块的电源地2 VDD - 模块的电源正端3 V0 - LCD驱动电压输入端4 RS(CS) H/L 并行的指令/数据选择信号;串行的片选信号5 R/W(SID) H/L 并行的读写选择信号;串行的数据口6 E(CLK) H/L 并行的使能信号;串行的同步时钟7 DB0 H/L 数据08 DB1 H/L 数据19 DB2 H/L 数据210 DB3 H/L 数据311 DB4 H/L 数据412 DB5 H/L 数据513 DB6 H/L 数据614 DB7 H/L 数据715 PSB H/L 并/串行接口选择:H-并行;L-串行16 NC 空脚17 /RET H/L 复位低电平有效18 NC 空脚19 LED_A - 背光源正极(LED+5V)20 LED_K - 背光源负极(LED-OV)逻辑工作电压(VDD):4.5~5.5V电源地(GND):0V工作温度(Ta):0~60℃(常温) / -20~75℃(宽温)三、接口时序模块有并行和串行两种连接方法(时序如下):8位并行连接时序图MPU写资料到模块MPU从模块读出资料2、串行连接时序图串行数据传送共分三个字节完成:第一字节:串口控制—格式11111ABCA为数据传送方向控制:H表示数据从LCD到MCU,L表示数据从MCU到LCDB为数据类型选择:H表示数据是显示数据,L表示数据是控制指令C固定为0第二字节:(并行)8位数据的高4位—格式DDDD0000第三字节:(并行)8位数据的低4位—格式0000DDDD串行接口时序参数:(测试条件:T=25℃VDD=4.5V)四、用户指令集指令指令码说明执行时间(540KHZ)RSRWDB7DB6DB5DB4DB3DB2DB1DB清除显示0 0 0 0 0 0 0 0 0 1将DDRAM填满“20H”,并且设定DDRAM的地址计数器(AC)到“00H”4.6ms地址归位0 0 0 0 0 0 0 0 1 X设定DDRAM的地址计数器(AC)到“00H”,并且将游标移到开头原点位置;这个指令并不改变DDRAM的内容4.6ms进入点设定0 0 0 0 0 0 0 1 I/D S指定在资料的读取与写入时,设定游标移动方向及指定显示的移位72us显示状态开/关0 0 0 0 0 0 1 D C BD=1:整体显示ONC=1:游标ONB=1:游标位置ON72us游标或显示移位控制0 0 0 0 0 1S/CR/LX X设定游标的移动与显示的移位控制位元;这个指令并不改变DDRAM的内容72us功能设定0 0 0 0 1 DL XREX XDL=1 (必须设为1)RE=1:扩充指令集动作72us备注:1、当模块在接受指令前,微处理顺必须先确认模块内部处于非忙碌状态,即读取BF标志时BF需为0,方可接受新的指令;如果在送出一个指令前并不检查BF标志,那么在前一个指令和这个指令中间必须延迟一段较长的时间,即是等待前一个指令确实执行完成,指令执行的时间请参考指令表中的个别指令说明。

CCM-16用户手册(V2[1].1)-200712

![CCM-16用户手册(V2[1].1)-200712](https://img.taocdn.com/s3/m/d8772ff8fab069dc5022011e.png)

神州数码网络有限公司 2007年12月目录前言 (2)安全性需知 (3)CCM产品的电气安全性 (3)CCM系列产品的操作安全性 (3)产品特点 (4)硬件特性 (4)软件特征 (4)安全特性 (6)硬件安装 (7)串口连接 (7)电源连接 (7)网络连接 (7)指示灯 (8)驱动程序的安装 (8)WINDWS平台驱动的安装 (9)SCO UNIX平台驱动的安装 (11)终端服务器的配置 (13)通过WEB方式进行配置 (13)通过TELNET方式进行配置 (32)通过终端方式进行配置 (50)终端服务器的快速安装 (52)UPGRADE(CCM升级和查找程序.EXE)的使用 (52)T ELNET下配置快速配置相关参数 (54)常见问题解答 (56)UPGRADE(CCM升级和查找程序)使用问题 (56)有关终端服务器数据接收不正常的原因分析 (57)C ONSOLE问题 (58)如果忘记了CCM产品密码 (58)R EAL PORT 模式问题:串口程序不能打开串口 (58)TCP/UDP S OCKET模式的问题 (59)PPP模式的问题 (59)附录 (61)前言欢迎使用神州数码的CCM系列产品。

CCM产品是异步串行口(RS-232、RS-422/485)和以太网RJ45接口间的一个转换器。

是一个带有CPU和嵌入式OS及完整TCP/IP协议栈的独立智能设备。

完成RS-232/422/485格式和以太网传输的IP包之间的数据转换,从而给传统的串行设备增加联网功能。

为了使您能更好的了解、使用及日常维护CCM产品,我们特编写了本使用手册,希望您能在使用和配置前仔细阅读一下本使用手册,以免损坏或影响正常使用。

在此,感谢您选择和购买了神州数码网络(北京)有限公司出品的系列网络产品,希望我们的产品和服务能让您满意,让“中国网络普遍成功”!安全性需知CCM产品的电气安全性z为避免可能的电击造成严重损害,在搬动CCM系列产品之前,请先将CCM系列产品的电源适配器暂时从电源插座中拔出;z当您要将某个终端加入到CCM系列产品中或者要去除CCM系列产品中的某个终端时,请务必在安装之前先拔掉CCM系列产品的电源适配器或关闭电源;z如果CCM系列产品的电源已损坏,请不要尝试自行修复,请将之邮寄回我公司,由我们的专业技术服务人员来处理;CCM系列产品的操作安全性z在您安装CCM系列产品以及加入终端设备之前,请务必详加阅读本手册所提供的相关信息;z在使用CCM系列产品之前,请确定所有的排线,电源适配器都已正确地连接好,若您发现有任何重大的瑕疵,请尽速联络我们;z灰尘、湿气以及剧烈的温度变化都会影响CCM系列产品的使用寿命,因此请尽量避免将CCM系列产品放置在这些地方;z若在CCM系列产品的使用上有任何的技术性问题,请和经过检定或有经验的技术人员联络;产品特点CCM产品是神州数码面向行业用户推出的一款调试控制器,配备具有强大运算能力的专用CPU 以及独立开发的嵌入式操作系统,并且拥有全面的功能以及人性化的交互界面,可以很方便地配置和使用,为您的工作带来很大的方便。

MC1648中文资料

1 VCC

2 NC

3 OUT

4 NC

5 AGC

6 NC

7 VEE P SUFFIX 14–LEAD PLASTIC PACKAGE CASE 646–06

Pin assignment is for Dual–in–Line Package. For PLCC pin assignment, see the MC1648 Non–Standard Pin Conversion Table below.

1. This measurement guarantees the dc potential at the bias point for purposes of incorporating a varactor tuning diode at this point. 2. Frequency variation over temperature is a direct function of the ∆C/∆ Temperature and ∆L/∆ Temperature.

MC1648 NON–STANDARD PIN CONVERSION DATA

Package 8D 14 L,P TANK 1 12 VCC 2 14 VCC 3 1 OUT 4 3 AGC 5 5 8 VEE 6 7 10 VEE 7 8 12 BIAS 8 10 14

D SUFFIX 8–PIN PLASTIC SOIC PACKAGE CASE 751–05

20FN 18 20 2 4 *NOTE – All unused pins are not connected. Supply Voltage +5.0Vdc –5.2Vdc GND Pins 7,8 1,14

信捷plc编程手册[1]

![信捷plc编程手册[1]](https://img.taocdn.com/s3/m/20948a2a192e45361066f5b9.png)

XC 系列可编程控制器

1 编程方式概述............................................................................................................................... 1

1-1.可编程控制器的特点 ................................................................................................................. 3 1-2.编程语言 .................................................................................................................................... 4 1-2-1.种类 ..................................................................................................................................... 4 1-2-2.互换性 ................................................................................................................................. 4 1-3.编程方式 .................................................................................................................................... 5

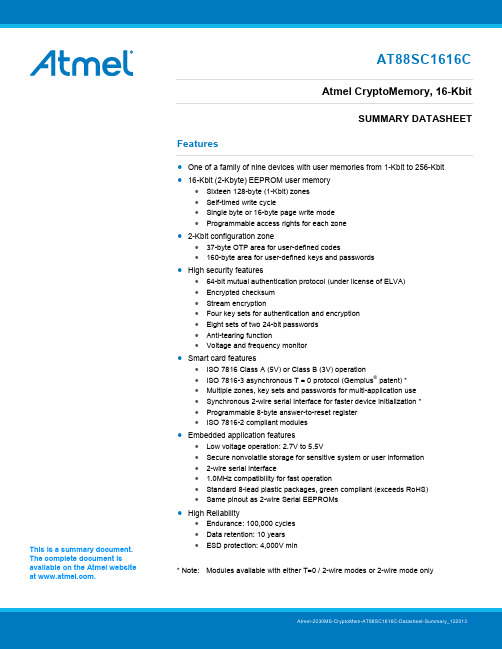

AT88SC1616C Atmel CryptoMemory 16K 位安全电器记忆晶体管数据手册说

AT88SC1616CAtmel CryptoMemory, 16-KbitSUMMARY DATASHEETFeatures • One of a family of nine devices with user memories from 1-Kbit to 256-Kbit •16-Kbit (2-Kbyte) EEPROM user memory• Sixteen 128-byte (1-Kbit) zones • Self-timed write cycle• Single byte or 16-byte page write mode • Programmable access rights for each zone• 2-Kbit configuration zone• 37-byte OTP area for user-defined codes• 160-byte area for user-defined keys and passwords •High security features• 64-bit mutual authentication protocol (under license of ELVA) • Encrypted checksum • Stream encryption• Four key sets for authentication and encryption • Eight sets of two 24-bit passwords • Anti-tearing function• Voltage and frequency monitor•Smart card features• ISO 7816 Class A (5V) or Class B (3V) operation• ISO 7816-3 asynchronous T = 0 protocol (Gemplus ®patent) * • Multiple zones, key sets and passwords for multi-application use • Synchronous 2-wire serial interface for faster device initialization * • Programmable 8-byte answer-to-reset register •ISO 7816-2 compliant modules•Embedded application features• Low voltage operation: 2.7V to 5.5V• Secure nonvolatile storage for sensitive system or user information • 2-wire serial interface• 1.0MHz compatibility for fast operation• Standard 8-lead plastic packages, green compliant (exceeds RoHS) •Same pinout as 2-wire Serial EEPROMs•High Reliability• Endurance: 100,000 cycles• Data retention: 10 years • ESD protection: 4,000V min* Note: Modules available with either T=0 / 2-wire modes or 2-wire mode onlyT his is a summary document. The complete document is available on the Atmel website at .AT88SC1616C [SUMMARY DATASHEET]Atmel-2030MS-CryptoMem-AT88SC1616C-Datasheet-Summary_1220132Table 1. Pin AssignmentFigure 1.Pin Configuration1. DescriptionThe Atmel ®AT88SC1616C member of the Atmel CryptoMemory ®family is a high-performance secure memory providing 16-Kbits of user memory with advanced security and cryptographic features built in. The user memory is divided into 16 128-byte zones, each of which may be individually set with different security access rights or effectively combined together to provide space for 1 to 16 data files.1.1 Smart Card ApplicationsThe AT88SC1616C provides high security, low cost, and ease of implementation without the need for a microprocessor operating system. The embedded cryptographic engine provides for dynamic and symmetric mutual authentication between the device and host, as well as performing stream encryption for all data and passwords exchanged between the device and host. Up to four unique key sets may be used for these operations. The AT88SC1616C offers the ability to communicate with virtually any smart card reader using the asynchronous T = 0 protocol (Gemplus patent) defined in ISO 7816-3.1.2 Embedded ApplicationsThrough dynamic and symmetric mutual authentication, data encryption, and the use of encrypted checksums, theAT88SC1616C provides a secure place for storage of sensitive information within a system. With its tamper detection circuits, this information remains safe even under attack. A 2-wire serial interface running at 1.0MHz is used for fast and efficientcommunications with up to 15 devices that may be individually addressed. The AT88SC1616C is available in industry standard 8-lead packages with the same familiar pinout as 2-wire serial EEPROMs.V CC =C1RST=C2SCL/CLK=C3NC=C4ISO Smart Card ModuleC5=GND C6=NC C7=SDA/IO C8=NCNC NC NCGND123487658-lead SOIC, PDIP V CC NC SCL SDAV CC =C1NC=C2SCL/CLK=C3NC=C4TWI Smart Card Module C5=GND C6=NC C7=SDA/IO C8=NCAT88SC1616C [SUMMARY DATASHEET]Atmel-2030MS-CryptoMem-AT88SC1616C-Datasheet-Summary_1220133Figure 1-1. Block Diagram2.Pin Descriptions2.1Supply Voltage (V CC )The V CC input is a 2.7V to 5.5V positive voltage supplied by the host.2.2 Clock (SCL/CLK)In the asynchronous T = 0 protocol, the SCL/CLK input is used to provide the device with a carrier frequency f . The nominal length of one bit emitted on I/O is defined as an “elementary time unit” (ETU) and is equal to 372/f . When the synchronous protocol is used, the SCL/CLK input is used to positive edge clock data into the device and negative edge clock data out of the device.2.3 Reset (RST)The AT88SC1616C provides an ISO 7816-3 compliant asynchronous answer to reset sequence. When the reset sequence is activated, the device will output the data programmed into the 64-bit answer-to-reset register. An internal pull-up on the RST input pad allows the device to be used in synchronous mode without bonding RST. The AT88SC1616C does not support the synchronous answer-to-reset sequence.2.4 Serial Data (SDA/IO)The SDA pin is bidirectional for serial data transfer. This pin is open-drain driven and may be wired with any number of other open drain or open collector devices. An external pull-up resistor should be connected between SDA and V CC . The value of this resistor and the system capacitance loading the SDA bus will determine the rise time of SDA. This rise time will determine the maximum frequency during read operations. Low value pull-up resistors will allow higher frequency operations while drawing higher average power. SDA/IO information applies to both asynchronous and synchronous protocols.When the synchronous protocol is used, the SCL/CLK input is used to positive edge clock data into the device and negative edge clock data out of the device.V CCAT88SC1616C [SUMMARY DATASHEET]Atmel-2030MS-CryptoMem-AT88SC1616C-Datasheet-Summary_12201343.*Notice:Stresses beyond those listed under “AbsoluteMaximum Ratings” may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other condition beyond those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods of time may affect device reliability.Table 3-1.DC CharacteristicsNotes: 1. V IL min and V IH max are reference only and are not tested2. To prevent latch up conditions from occurring during power up of the AT88SCxxxxC, V CC must be turned onbefore applying V IH . For powering down, V IH must be removed before turning V CC offAT88SC1616C [SUMMARY DATASHEET]Atmel-2030MS-CryptoMem-AT88SC1616C-Datasheet-Summary_1220135Table 3-2.AC CharacteristicsApplicable over recommended operating range from V CC = +2.7 to 5.5V, T AC = -40°C to +85°C, CL = 30pF4. Device Operation for Synchronous ProtocolsClock and Data Transitions:The SDA pin is normally pulled high with an external device. Data on the SDA pin may change only during SCL low time periods (see Figure 4-3 on page 7). Data changes during SCL high periods will indicate a start or stop condition as defined below.Start Condition:A high-to-low transition of SDA with SCL high is a start condition which must precede any other command (see Figure 4-4 on page 7).Stop Condition:A low-to-high transition of SDA with SCL high is a stop condition. After a read sequence, the stop command will place the EEPROM in a standby power mode (see Figure 4-4 on page 7).Acknowledge:All addresses and data words are serially transmitted to and from the EEPROM in 8-bit words. The EEPROM sends a zero to acknowledge that it has received each word. This happens during the ninth clock cycle (see Figure 4-5 on page 7). Memory Reset:After an interruption in protocol, power loss or system reset, any 2-wire part can be reset by following these steps: 1. Clock up to nine cycles2. Look for SDA high in each cycle while SCL is high3. Create a start conditionAT88SC1616C [SUMMARY DATASHEET] Atmel-2030MS-CryptoMem-AT88SC1616C-Datasheet-Summary_1220136 Figure 4-1. Bus Timing for 2-wire CommunicationsSCL: Serial Clock, SDA – Serial Data I/OFigure 4-2. Write Cycle Timing: SCLSerial Clock, SDA – Serial Data I/ONote: The write cycle time t WR is the time from a valid stop condition of a write sequence to the end of the internalclear/write cycleSCLSDA INSDA OUTSTOPCONDITIONSTARTCONDITIONSCLSDAAT88SC1616C [SUMMARY DATASHEET]Atmel-2030MS-CryptoMem-AT88SC1616C-Datasheet-Summary_1220137Figure 4-3. Data ValidityFigure 4-4. Start and Stop DefinitionsFigure 4-5. Output AcknowledgeDATA CHANGE ALLOWEDDATA STABLEDATA STABLESDASCLSDASCLSTART STOPSCLDAT A INDAT A OUTEG D E L W O N K C A T R A T S 981AT88SC1616C [SUMMARY DATASHEET]Atmel-2030MS-CryptoMem-AT88SC1616C-Datasheet-Summary_12201385.Device Architecture5.1User ZonesThe EEPROM user memory is divided into 16 zones of 1024 bits each. Multiple zones allow for different types of data or files to be stored in different zones. Access to the user zones is allowed only after security requirements have been met. These security requirements are defined by the user during the personalization of the device in the configuration memory. If the same security requirements are selected for multiple zones, then these zones may effectively be accessed as one larger zone.6. Control LogicAccess to the user zones occurs only through the control logic built into the device. This logic is configurable through access registers, key registers and keys programmed into the configuration memory during device personalization. Also implemented in the control logic is a cryptographic engine for performing the various higher-level security functions of the device.AT88SC1616C [SUMMARY DATASHEET]Atmel-2030MS-CryptoMem-AT88SC1616C-Datasheet-Summary_12201397. Configuration MemoryThe configuration memory consists of 2048 bits of EEPROM memory used for storing passwords, keys and codes and for defining security levels to be used for each user zone. Access rights to the configuration memory are defined in the control logic and may not be altered by the user.AT88SC1616C [SUMMARY DATASHEET]Atmel-2030MS-CryptoMem-AT88SC1616C-Datasheet-Summary_122013108. Security FusesThere are three fuses on the device that must be blown during the device personalization process. Each fuse locks certain portions of the configuration memory as OTP memory. Fuses are designed for the module manufacturer, card manufacturer and card issuer and should be blown in sequence, although all programming of the device and blowing of the fuses may be performed at one final step.9. Protocol SelectionThe AT88SC1616C supports two different communication protocols.• Smart Card Applications:The asynchronous T = 0 protocol defined by ISO 7816-3 is used for compatibility with the industry’s standard smart card readers• Embedded Applications:A 2-wire serial interface is used for fast and efficient communication with logic or controllersThe power-up sequence determines which of the two communication protocols will be used.9.1 Asynchronous T = 0 ProtocolThis power-up sequence complies with ISO 7816-3 for a cold reset in smart card applications.• V CC goes high; RST, I/O-SDA and CLK-SCL are low • Set I/O-SDA in receive mode • Provide a clock signal to CLK-SCL •RST goes high after 400 clock cyclesThe device will respond with a 64-bit ATR code, including historical bytes to indicate the memory density within theCryptoMemory family. Once the asynchronous mode has been selected, it is not possible to switch to the synchronous mode without powering off the device.Figure 9-1. Asynchronous T = 0 Protocol (Gemplus Patent)V cc I/O-SDARSTCLK-SCL9.2 Synchronous 2-wire Serial InterfaceThe synchronous mode is the default after powering up V CC due to an internal pull-up on RST. For embedded applications using CryptoMemory in standard plastic packages, this is the only communication protocol.• Power-up V CC , RST goes high also• After stable V CC , CLK-SCL and I/O-SDA may be drivenFigure 9-2. Synchronous 2-wire ProtocolNote:Five clock pulses must be sent before the first command is issued10. Communication Security ModesCommunications between the device and host operate in three basic modes. Standard mode is the default mode for the device after power-up. Authentication mode is activated by a successful authentication sequence. Encryption mode is activated by a successful encryption activation following a successful authentication. Table 10-1. Communication Security Modes (1)Notes: 1. Configuration data include viewable areas of the configuration zone except the passwords:• MDC: Modification Detection Code •MAC: Message Authentication CodeV cc I/O-SDARST CLK-SCL1234511. Security Options11.1 Anti-tearingIn the event of a power loss during a write cycle, the integrity of the device’s stored data may be recovered. This function is optional – the host may choose to activate the anti-tearing function, depending on application requirements. When anti-tearing is active, write commands take longer to execute, since more write cycles are required to complete them, and data are limited to eight bytes.Data are written first to a buffer zone in EEPROM instead of the intended destination address, but with the same accessconditions. The data are then written in the required location. If this second write cycle is interrupted due to a power loss, the device will automatically recover the data from the system buffer zone at the next power-up.In 2-wire mode, the host is required to perform ACK polling for up to 8mS after write commands when anti-tearing is active. At power-up, the host is required to perform ACK polling, in some cases for up to 2mS, in the event that the device needs to carry out the data recovery process.11.2 Write LockIf a user zone is configured in the write lock mode, the lowest address byte of an 8-byte page constitutes a write access byte for the bytes of that page.Example: The write lock byte at $080 controls the bytes from $080 to $087Table 11-1. Write Lock ExampleThe write lock byte may also be locked by writing its least significant (rightmost) bit to “0”. Moreover, when write lock mode is activated, the write lock byte can only be programmed – that is, bits written to “0” cannot return to “1”. In the write lockconfiguration, only one byte can be written at a time. Even if several bytes are received, only the first byte will be taken into account by the device.12. Password VerificationPasswords may be used to protect read and/or write access of any user zone. When a valid password is presented, it ismemorized and active until power is turned off, unless a new password is presented or RST becomes active. There are eight password sets that may be used to protect any user zone. Only one password is active at a time, but write passwords give read access also.12.1 Authentication ProtocolThe access to a user zone may be protected by an authentication protocol. Any one of four keys may be selected to use with a user zone.The authentication success is memorized and active as long as the chip is powered, unless a new authentication is initialized or RST becomes active. If the new authentication request is not validated, the card loses its previous authentication and itshould be presented again. Only the last request is memorized.Note: Password and authentication may be presented at any time and in any order. If the trials limit has been reached (after four consecutive incorrect attempts), the password verification or authentication process will not be takeninto accountFigure 12-1. Password and Authentication Operations12.2 ChecksumThe AT88SC1616C implements a data validity check function in the form of a checksum, which may function in standard,authentication or encryption modes.In the standard mode, the checksum is implemented as a Modification Detection Code (MDC), in which the host may read an MDC from the device in order to verify that the data sent was received correctly.In the authentication and encryption modes, the checksum becomes more powerful since it provides a bidirectional dataintegrity check and data origin authentication capability in the form of a Message Authentication Code (MAC). Only thehost/device that carried out a valid authentication is capable of computing a valid MAC. While operating in the authentication or encryption modes, the use of a MAC is required. For an ingoing command, if the device calculates a MAC different from the MAC transmitted by the host, not only is the command abandoned but the mode is also reset. A new authentication and/or encryption activation will be required to reactivate the MAC.12.3 EncryptionThe data exchanged between the device and the host during read, write and verify password commands may be encrypted to ensure data confidentiality.The issuer may choose to require encryption for a user zone by settings made in the configuration memory. Any one of four keys may be selected for use with a user zone. In this case, activation of the encryption mode is required in order to read/write data in the zone and only encrypted data will be transmitted. Even if not required, the host may elect to activate encryption provided the proper keys are known.12.4 Supervisor ModeEnabling this feature allows the holder of one specific password to gain full access to all eight password sets, including the ability to change passwords.12.5 Modify ForbiddenNo write access is allowed in a user zone protected with this feature at any time. The user zone must be written during device personalization prior to blowing the security fuses.12.6 Program OnlyFor a user zone protected by this feature, data within the zone may be changed from a “1” to a “0”, but never from a “0” to a “1”.13. Initial Device ProgrammingTo enable the security features of CryptoMemory, the device must first be personalized to set up several registers and load in the appropriate passwords and keys. This is accomplished through programming the configuration memory of CryptoMemory using simple write and read commands. To gain access to the configuration memory, the secure code must first besuccessfully presented. For the AT88SC1616C device, the secure code is $20 0C E0. After writing and verifying data in the configuration memory, the security fuses must be blown to lock this information in the device. For additional information on personalizing CryptoMemory, please see the application notes Programming CryptoMemory for Embedded Applications and Initializing CryptoMemory for Smart Card Applications (at ).Notes: 1. Formal drawings may be obtained from an Atmel sales office2. Both the J and P module packages are used for either ISO (T=0 / 2-wire mode) or TWI (2-wire mode only)Ordering Code: MJ or MJTG Ordering Code: MP or MPTGModule Size: M2Dimension*: 12.6 x 11.4 [mm] Glob Top: Round - ∅ 8.5 [mm] Thickness: 0.58 [mm]Pitch: 14.25mm Module Size: M2Dimension*: 12.6 x 11.4 [mm]Glob Top: Square - 8.8 x 8.8 [mm] Thickness: 0.58 [mm]Pitch: 14.25mmNote: *The module dimensions listed refer to the dimensions of the exposed metal contact area. The actual dimensions of the module after excise or punching from the carrier tape are generally 0.4mm greater in both directions(i.e., a punched M2 module will yield 13.0 x 11.8mm)15.1 Atmel AT88SC1616C Package Marking Information8S1 – 8-lead JEDEC SOIC8P3 – 8-lead PDIP16. Revision History。

形状记忆合金双程记忆效应训练机[发明专利]

![形状记忆合金双程记忆效应训练机[发明专利]](https://img.taocdn.com/s3/m/442d0a254028915f804dc2fa.png)

专利名称:形状记忆合金双程记忆效应训练机专利类型:发明专利

发明人:张博明,于东,梁军,赵海涛,解维华

申请号:CN200710071855.3

申请日:20070309

公开号:CN101020948A

公开日:

20070822

专利内容由知识产权出版社提供

摘要:本发明提供了一种可以对形状记忆合金型材进行高效双程记忆效应训练的自动设备。

它包括机架,设置在机架上的传动机构、限位器,连接传动机构的电机,设置在机架下方的风机和控制器,控制器分别与电机、限位器、直流电源和风机相连,在控制器与直流电源之间连接有定时器,直流电源带有与形状记忆合金相连的输出线,传动机构包括安装在机架上的导轨和丝杠,丝杠和导轨上安装有滑动螺母,电机与丝杠相连。

本发明可以实现对形状记忆合金双程记忆效应进行高效自动训练,适用于批量地进行记忆合金的训练。

申请人:哈尔滨工业大学

地址:150001 黑龙江省哈尔滨市南岗区西大直街92号

国籍:CN

代理机构:哈尔滨市哈科专利事务所有限责任公司

代理人:刘娅

更多信息请下载全文后查看。

EQMS-氯酚类化合物(CPs)

氯酚类化合物(CPs)xx一、物质简介氯酚类化合物(CPs)是一类广泛存在于水环境中的有机污染物,这类化合物具有环境稳定性、生物累积性和生物毒性,水体中普遍存在的氯酚类化合物主要有以下七种[1]:二、监测分析方法气相色谱法质谱联机测定酚类化合物是在酸性条件下萃取,然后净化和测定,对酚类化合物不进行衍生。

该法由于氯酚类化合物极性大,当色谱柱性能降低时,往往容易严重拖尾[2]。

固相萃取采用高效、高选择性的固定相较传统的液液萃取显著减少溶剂用量,简化样品处理程序[3]。

故可采用乙酸酐衍生化,固相萃取盘全自动萃取和GCMS联用的方法建立水中氯酚类的快速分析方法。

1 仪器与试剂1.1仪器:Trace DSQII GCMS气质联用仪,EI离子源(美国热电公司);OPTIMA delta-6(30m伊0.25mm伊0.25滋m)色谱柱(德国MACHEREY-NAGEL公司);SPE-DEX 4790 自动固相萃取仪(四通道)(美国Horizon公司)。

1.2试剂:氯酚类的混标,4-氯酚(4-CP)、2,4-二氯酚(2,4-DCP)、2,6- 二氯酚(2,6-DCP)、2,4,5-三氯酚(2,4,5-TCP)、2,4,6-三氯酚(2,4,6-TCP)、2,3,4,6-四氯酚(2,3,4,6-TeCP)、五氯酚(PCP)等7种物质,其浓度分别为:101.4 、98.9、101.0、100.2、100.1、100.32. 样品的采集因氯酚类见光分解,使用棕色瓶采集。

每100 mL水样加入1 mL 10% 的硫酸溶液和0.5g 的硫酸铜,置暗处,4 o C可闭光保存24 h[4],相同条件下准备空白试样一份用以对照。

3. 样品的处理在萃取之前要对样品进行衍生化处理,生成相应的氯苯类乙酸酯。

取900ml的样品于1L 的样品瓶中,加入20 o C饱和硼砂溶液调节pH至9,滴加3ml乙酸酐,混匀水样并室温放置5min。

用铝箔封好瓶口并架上SPE-DEX 4790,启动程序自动萃取,浓缩至1ml进样。

MC1648

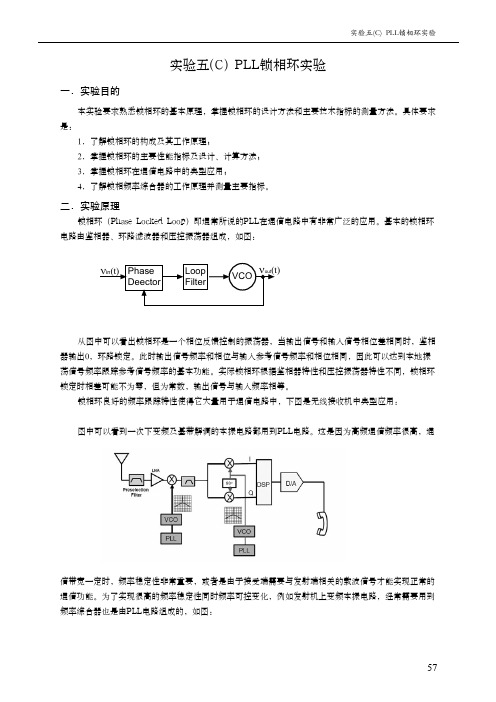

实验五(C) PLL锁相环实验一.实验目的本实验要求熟悉锁相环的基本原理,掌握锁相环的设计方法和主要技术指标的测量方法。

具体要求是:1.了解锁相环的构成及其工作原理;2.掌握锁相环的主要性能指标及设计、计算方法;3.掌握锁相环在通信电路中的典型应用;4.了解锁相频率综合器的工作原理并测量主要指标。

二.实验原理锁相环(Phase Locked Loop)即通常所说的PLL在通信电路中有非常广泛的应用。

基本的锁相环电路由鉴相器、环路滤波器和压控振荡器组成,如图:从图中可以看出锁相环是一个相位反馈控制的振荡器,当输出信号和输入信号相位差相同时,鉴相器输出0,环路锁定。

此时输出信号频率和相位与输入参考信号频率和相位相同,因此可以达到本地振荡信号频率跟踪参考信号频率的基本功能。

实际锁相环根据鉴相器特性和压控振荡器特性不同,锁相环锁定时相差可能不为零,但为常数,输出信号与输入频率相等。

锁相环良好的频率跟踪特性使得它大量用于通信电路中,下图是无线接收机中典型应用:图中可以看到一次下变频及基带解调的本振电路都用到PLL电路。

这是因为高频通信频率很高,通信带宽一定时,频率稳定性非常重要,或者是由于接受端需要与发射端相关的载波信号才能实现正常的通信功能。

为了实现很高的频率稳定性同时频率可控变化,例如发射机上变频本振电路,经常需要用到频率综合器也是由PLL电路组成的,如图:图中主要增加了两个1/R和1/N的分频器,以实现对固定参考频率源输出可变的输出频率的功能。

有关系式:N f R f out ref =即f R N f out ref=,此关系式为频率综合器的基本关系式。

锁相环路的特点 1.具有良好的带通滤波性能 2.具有准确的频率跟踪性能3.具有较好的低门限特性锁相环路分析一般锁相环路是由鉴相器、环路滤波器和压控振荡器组成的相位反馈系统,常用反馈控制理论来分析锁相环路。

一般来讲鉴相器的鉴相特性是非线性的,锁相环路的电路方程是一个非线性微分方程,需要用非线性理论进行分析。

MC1648_PLL 高频信号发生器

FM调制器(MC1648 + MC12022 + MC145152)摘要:本设计是基于数字频率合成技术,采用单片机来完成控制的FM调制器。

利用锁相环式频率合成器,由单片机实现对PLL频率合成芯片MC145152的控制。

可自动改变频率,步进达100KHz;可实时测量压控振荡器输出频率,并用液晶显示器显示;采用了AGC电路来稳定输出电压;功率放大选用三极管S 9018,提高了放大器的效率。

同时系统还实现了频率扩展、立体声编码等实用性功能。

程序设计采用C语言,在单片机AT89C52芯片上编程实现,经测试,整机功能齐全,发射信号正常;输出频率稳定度优于10-5;输出功率≥100mW;输出阻抗为50Ω。

关键词:压控振荡器数字频率合成单片机 MC1648The modulate of FM TransmitterAbstact:The system adopting microcontrollers 51 to design the Frequency Modulation Transmitter is base d on the digital frequency synthesize technical. The system is made up of Voltage Control LC Oscillator, Phase Locked Loop, AGC circuit, Dual–Modulus Prescaler, microcontrollers circuit , peak to peak voltag e value measure circuit, LCD module and keyboard.The digital PLL circuit is made up of some integrate circuits,they are MC145152、MC1648、MC12022.it can improve stability of frequency. It can automatical ly change and measure the frequency of Transmitter with a step of 5 kHz and P out and display it by LC D. Meantime it realizes the functions of expanding the frequency, stereo coding, amplify the power etc.M ocrocontrollers adopts AT89C51 which is produced by Corp Atmel , it belong to the catena of 51,adaptin g to designing the program with C. It is proved to be well functioning, the output frequency is stable,the sine wave is beautiful and lubricity. because of adopting the digital PLL frequency synthesize technical, the stability of frequency add to 10-6; when the signal pass filter.The Signal-to-Noise attain the standard of A , promulgated by nation.Keywords:VCO digital frequency synthesize singlechip MC1648目录第一章系统设计 (3)1.1 总体设计方案 (3)1.1.1 设计要求 (3)1.1.2 设计思路 (3)1.1.3 方案论证与比较 (3)1.1.4 系统组成 (6)第二章单元电路设计 (6)2.1 压控振荡器的设计 (6)2.2 锁相环路的设计 (9)2.2.1 PLL频率合成电路设计 (10)2.2.2 前置分频器 (11)2.2.3 鉴相器 (12)2.2.4 环路滤波器 (13)2.2.5 电源电路 (14)2.3 功率放大电路的设计 (14)2.4 立体声编码器的设计 (15)2.5 输出功率测量的设计 (16)2.6 控制电路设计和频率计算 (16)第三章软件设计 (18)3.1 MC145152的控制和显示部分的设计 (18)3.2 测频计的设计 (19)3.3 TLC549的控制程序设计 (20)3.4 液晶显示驱动的设计 (20)第四章系统测试 (21)4.1 测试使用的仪器 (21)4.2指标测试和测试结果 (21)4.2.1输出频率范围和稳定度的测试 (21)4.2.2输出功率的测试 (21)4.2.3 VCO可实现的功能 (21)第五章结束语 (22)第六章参考文献 (22)附录 (22)第一章系统设计1.1总体设计方案1.1.1 设计要求1.基本要求(1)载波的频率范围68Mhz~88Mhz;(2)步进100Khz,随时可调;(3)载波频率稳定度优于10-3;(4)最大频偏:75Khz;(5)频率响应:100hz~10Khz, ±6dB;(6)失真度:100hz~10Khz,≤3%dB;(7)信噪比:20lgS/N≥40dB;(8)残波辐射:10lgP0/PN≥40dB;(9)射频输出功率:100mW,负载50Ω;(10)能显示载频频率和输出载波功率。

ADIS16488A Silicon Anomaly List说明书

Tactical Grade,Ten Degrees of Freedom Inertial Sensor Silicon Anomaly ADIS16488ARev. 0Document FeedbackInformation furnished by Analog Devices is believed to be accurate and reliable. However, noresponsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other rights of third parties that may result from its use. Specifications subject to change without notice. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices. T rademarks and registered trademarks are the property of their respective owners. One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A. Tel: 781.329.4700 ©2017 Analog Devices, Inc. All rights reserved. Technical Support This anomaly list describes the known bugs, anomalies, and workarounds for the ADIS16488A.Analog Devices, Inc., is committed, through future silicon revisions, to continuously improve silicon functionality. Analog Devices tries to ensure that these future silicon revisions remain compatible with your present software/systems by implementing the recommended workarounds outlined within this document.PERFORMANCE ISSUESTable 1. Error in Soft Iron Correction Factors [er001]Background The signal chain for the tri-axis magnetometer in the ADIS16488A includes a user-configurable, 3 × 3 soft iron correction matrix. Users configure each value in the soft iron correction matrix by writing to its corresponding register. For example,the SOFT_IRON_S12 register contains the value for correction factor S12. In these registers, 1 LSB = 100/215.Issue On units that have firmware Revision 1.07 (or earlier), 1 LSB = 12.5/215, which is eight times lower than the correct value, on the following registers: SOFT_IRON_S12, SOFT_IRON_S13, SOFT_IRON_S21, SOFT_IRON_S31, and SOFT_IRON_S32. Workaround Read FIRM_REV to determine the firmware revision of a unit. If FIRM_REV < 0x0108, clear all soft iron correction values (write 0x0000 to each SOFT_IRON_Sxy register) and perform the soft iron correction outside of the ADIS16488A. Related Issues None.Table 2. User Offset Addition Error [er002]Background The ADIS16488A provides user-configurable bias correction values for each gyroscope and accelerometer(x, y, and z), through the following registers: XG_BIAS_HIGH, XG_BIAS_LOW, YG_BIAS_HIGH, YG_BIAS_LOW, ZG_BIAS_HIGH,ZG_BIAS_LOW, XA_BIAS_HIGH, XA_BIAS_LOW, YA_BIAS_HIGH, YA_BIAS_LOW, ZA_BIAS_HIGH, and ZA_BIAS_LOW.Issue On units that have firmware Revision 1.07 (or earlier), there is a computation error that results in a small error in the bias of each sensor (for example, less than 0.02°/sec for the gyroscopes).Workaround Read FIRM_REV to determine the firmware revision of a unit. If FIRM_REV < 0x0108, write 0x0000 to XG_BIAS_HIGH, XG_BIAS_LOW, YG_BIAS_HIGH, YG_BIAS_LOW, ZG_BIAS_HIGH, ZG_BIAS_LOW, XA_BIAS_HIGH, XA_BIAS_LOW,YA_BIAS_HIGH, YA_BIAS_LOW, ZA_BIAS_HIGH, and ZA_BIAS_LOW. Apply the bias correction factors to the gyroscope andaccelerometer signals outside of the ADIS16488A.Related Issues None.Table 3. Temperature Compensation Error [er003]Background The ADIS16488A leverages internal temperature sensors as control inputs for the compensation of gyroscope and accelerometer measurements.Issue On units that have firmware Revision 1.08 (or earlier), one of the three temperature sensors can be corrupted when using an external clock to drive the sampling. The external clock causes elevated levels of sensitivity to variation in temperature. Workaround Read FIRM_REV to determine the firmware revision of a unit. If FIRM_REV < 0x0109, use the internal sample clock if the best temperature sensitivity is necessary.Related Issues None.Table 4. Real-Time Clock (RTC) Functional Issues [er004]Background The ADIS16488A provides a RTC function that keeps track of time (seconds, minutes, hours, days, months, and years) while the main processor function is not operating (sleep, powered off).Issue On units that have firmware Revision 1.08 (or earlier), the days information in TIME_DH_OUT can experience an overflow condition when the device recovers from sleep mode.Workaround Read FIRM_REV to determine the firmware revision of a unit. If FIRM_REV < 0x0109, do not use sleep mode if the RTC function is critical for the application.Related Issues None.ADIS16488ASilicon AnomalyRev. 0 | Page 2 of 3Table 5. Erroneous Barometer Self Test Result in DIAG_STS [er005]Background The DIAG_STS register provides an error flag for the self test function in Bit 11.IssueOn units that have firmware Revision 1.08 (or earlier), Register DIAG_STS, Bit 11 may remain in a low state, even if the barometer is failing its self test routine.WorkaroundRead FIRM_REV to determine the firmware revision of a unit. If FIRM_REV < 0x0109, do not use Register DIAG_STS, Bit 11 to determine the health of the barometer for mission critical functions.Related Issues None.Table 6. Barometer New Data Bit Continues Updating After Failure [er006]Background Register SYS_E_FLAG, Bit 9 indicates that there is new barometer data in the BAROM_OUT register when it is in a high state. IssueOn units that have firmware Revision 1.08 (or earlier), Register SYS_E_FLAG, Bit 9 still indicates that new data is available, even if the barometer has experienced a failure.WorkaroundRead FIRM_REV to determine the firmware revision of a unit. If FIRM_REV < 0x0109, do not use Register SYS_E_FLAG, Bit 9 to determine the operational state of the barometer function.Related Issues None.Table 7. Sleep Mode Recovery Causes Barometer Failure [er007]Background The ADIS16488A provides a sleep mode that has a faster recovery time than a complete restart (power-on or reset recovery). IssueOn units that have firmware Revision 1.08 (or earlier), recovery from sleep mode can cause failure in the barometer function. WorkaroundRead FIRM_REV to determine the firmware revision of a unit. If FIRM_REV < 0x0109, do not use sleep mode if the barometer is important for the application.Related Issues None.Table 8. Writing to Register FNCTIO_CTRL Causes Barometer Failure [er008]Background The FNCTIO_CTRL register provides a number of user configurations for the input/output lines (DIO1, DIO2, DIO3, and DIO4). IssueOn units that have firmware Revision 1.08 (or earlier), writing to the FNCTIO_CTRL register can cause the barometer measurement function to lock up.WorkaroundRead FIRM_REV to determine the firmware revision of a unit. If FIRM_REV < 0x0109 and the barometer function is important for the application, reset the operation after writing to Register FNCTIO_CTRL and after backing up those settings in the flash.Related Issues NoneTable 9. Writing to Register GLOB_CMD, Bit 1 Causes Barometer Failure [er009]BackgroundThe Register GLOB_CMD, Bit 1 provides a trigger bit for running the self test function on all of the sensors inside of the ADIS16488A .IssueOn units that have firmware Revision 1.08 (or earlier), running the self test routine by setting Register GLOB_CMD, Bit 1 equal to 1 can cause the barometer measurement function to lock up.WorkaroundRead FIRM_REV to determine the firmware revision of a unit. If FIRM_REV < 0x0109 and the barometer function is important for the application, reset the operation after running the self test function.Related Issues NoneTable 10. Daylight Savings Time Error in Real-Time Clock [er010]BackgroundThe ADIS16488A provides a RTC function that keeps track of time (seconds, minutes, hours, days, months, and years) while the main processor function is not operating (sleep, powered off). Register CONFIG, Bit 1 provides a control for managing against daylight savings time.IssueOn units that have firmware Revision 1.08 (or earlier), turning daylight savings time on by setting Register CONFIG, Bit 1 equal to 1 causes a malfunction in the tracking of the RTC.WorkaroundRead FIRM_REV to determine the firmware revision of a unit. If FIRM_REV < 0x0109, do not use the daylight savings time setting of Register CONFIG, Bit 1 equal to 1.Related Issues NoneSilicon AnomalyADIS16488ARev. 0 | Page 3 of 3Table 11. Flash Memory Corruption From Power Loss During Manual Flash Updates [er011]Background Setting Register GLOB_CMD, Bit 3 equal to 1 causes an update of the flash memory, which takes 375 ms to execute.IssueOn units that have firmware Revision 1.09 (or earlier), power loss during manual flash execution has a 1 in 1000 chance of causing corruption in the flash memory, which destroys the device.WorkaroundRead FIRM_REV to determine the firmware revision of a unit. If FIRM_REV < 0x0109, keep VDD > 3.0 V during manual flash update process. Not that this best practice has broader application; however, it does address this specific sensitivity.Related Issues NoneANOMALY STATUSReference Number DescriptionStatus Date Code er001 Error in soft iron correction factors Fixed1438 er002 User offset addition errorFixed 1438 er003 Temperature compensation errorFixed 1514 er004 Real-time clock (RTC) functional issuesFixed 1514 er005 Erroneous barometer self test result in DIAG_STSFixed 1514 er006 Barometer new data bit continues updating after failure Fixed 1514 er007 Sleep mode recovery causes barometer failureFixed 1514 er008 Writing to Register FNCTIO_CTRL causes barometer failure Fixed 1514 er009 Writing to Register GLOB_CMD, Bit 1 causes barometer failure Fixed 1514 er010 Daylight savings time error in real-time clockFixed 1514 er011Flash memory corruption from power loss during manual flash updatesFixed1526©2017 Analog Devices, Inc. All rights reserved. Trademarks and registered trademarks are the property of their respective owners. S11855-0-1/17(0)。

西门子程控器中文说明

Page 2/20/2006CC1N7696en

Siemens Building Technologies HVAC Products

使用 警告

专门为气体阀验证(泄漏测试)设计的 LDU11 是基于以下的压力检测原理。 它可以用于带或不带放散管的气体燃烧装置。 对于符合 EN 标准不带放散管的装置,《无排气管的连接案例》里的注意事项必须被遵 守。I

t3 填满测试空间 Filling the test space t4 清除测试空间 Evacuating the test space

¹) 阀门的开启时间不用与 EN1643 的一致

阀门验证装置 LDU11... (不带插入式底座) 插入式底座不包含在运输的货物中,必须分开订购!

中等容量的燃烧控制器连接附件

在锁定阶段,除了端子 13 LDU11…的所有电源端子都处于断开状态,端子 13 是用来指示 锁定的。

复位以后,逻辑控制程序会自动将其回归当启动位置并且立即开始一个新的验证测试。

不要按住复位按钮超过 10 秒的时间。

在测试区域排气之前的失电不会引起控制程序的改变。.

在开始排气后失电,当电恢复后阀门验证测试不会继续,逻辑控制程序会先将其回归到启 动位置然后再开始完整的阀门验证测试。

LDU11.323A17 AC 100...110 V

LDU11.323A27 AC 220...240 V

LDU11.523A17 ¹) AC 100...110 V

LDU11.523A27 ¹) AC 220...240 V

t3 t4 2.5 s 2.5 s 2.5 s 2.5 s 5s 5s 5s 5s

单片机控制的宽频带频率合成器

单片机控制的宽频带频率合成器

周思宁;汪文革

【期刊名称】《电子技术应用》

【年(卷),期】1995(000)012

【摘要】介绍单片机控制的宽频带频率合成器的总体结构和性能,着重对其中的数字式高频锁相环和单片机控制部分的设计思想进行了讨论,并给出了具体的原理图。

【总页数】3页(P11-13)

【作者】周思宁;汪文革

【作者单位】不详;不详

【正文语种】中文

【中图分类】TN74

【相关文献】

1.锁相环频率合成器的单片机控制 [J], 王烨

2.锁相环频率合成器的单片机控制 [J], 王烨

3.基于单片机控制的ADF4106锁相频率合成器的设计与实现 [J], 李垒;

4.基于单片机控制的直接频率合成器的设计 [J], 朱思敏; 陈娟; 易清泗

5.基于单片机控制的LMX2572锁相频率合成器的设计与实现 [J], 李垒

因版权原因,仅展示原文概要,查看原文内容请购买。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

14

5

Medical

5

Gen. Purpose

4 1

No

98.55 84.33 29.0 74.2 55.63 CCM1012-ND

No

86.11 72.14 29.0 62.0 55.63 CCM1020-ND

Insulating Boot for M1 Version . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . CCM1066-ND NEW!

EOP Series: A general purpose filter which is effective in removing both common and differential-mode noise for susceptibility applications.

EP Series: The EP/VP series of RFI filters has been developed to reduce conducted noise to acceptable limits for equipment that must comply with requirements of CISPAR in Europe and the FCC specifications in the USA.

Flange Flange Snap-In Snap-In Flange

Male Male Male Female Female

Dimensions (mm)

DigiHale Waihona Puke KeyABC

D

Part No.

Series SR — AC Connector

50.01 40.01 28.19 26.70

CCM1400-ND

Corcom Part No.

6ESRM-P 6ESRM-3 6ESRMC2 6ESRFC3 6ESRF-3

220-240

Fig. 11

C

D B

Fig. 12 A B

C

220-240

Fig. 13

A

DVE

D

C

D B A

Note: Picture shown with switch. Fig. 14

E

EDP Series: These RFI power line filters provide enhanced differential-mode performance for applications requiring more line-to-line protection.

EJT Series: The EJT Series is a power inlet filter designed to attenuate noise up to 1 GHz. This inlet uses an IEC 320/C14 input connector. This product was designed to address the demand for more noise attenuation at higher frequencies in a compact inlet.

10B

D

6 10 3

Faston Faston Faston

50.29 50.29 50.29

54.10 54.10 54.10

58.67 58.67 58.67

28.50 28.50 28.50

55.91 55.91 55.91

40.01 40.01 40.01

CCM1383-ND CCM1384-ND CCM1385-ND

11.24 9.27 8.69 9.35 9.38

196.50 162.50 151.75 163.50 164.00

657.00 542.00 507.00 547.00 548.00

9

20

Straight

79.375 34.29 29.99 37.08 36.07 — CCM1257-ND

17.54 306.75 1024.00

Rated Current 120V Fig. (Amps)

RFI Filter Type

Available

Voltage DPST

Selection On/Off

Position Switch

A

Dimensions (mm)

B

C

DE

Digi-Key Part No.

Series J — Power Entry Modules

10

Faston

31.50 49.02 58.67 26.92 55.91 — CCM1372-ND*

16.38 286.25

956.00

10

Faston

31.50 49.02 58.67 26.92 55.91 — CCM1373-ND*

12.77 223.50

746.00

10

Faston

31.50 54.10 58.67 26.92 55.91 — CCM1374-ND

DVE

DB A

Fig. 15

D Note: Picture shown with mounting flange.

C E

Ø3.40 C

B A

DVE

+ S

RF Line Filters

B Series: These general purpose common-mode RFI power line filters effectively provide RFI control of line-to-ground noise in a small size at a low cost.

50.22 40.01 22.76 31.09

CCM1401-ND

30.40 — 22.66 30.61

CCM1402-ND

35.31 — 28.19 35.71

CCM1403-ND

50.01 40.01 29.31 35.71

CCM1404-ND

Pricing

1

25

100

3.23 56.50 189.00 2.35 41.00 137.00 2.47 43.00 144.00 2.86 50.00 167.00 2.86 50.00 167.00

Series H - Power Entry Modules

2

6

Faston, Straight 55.90 30.20 20.60 40.01 —

— CCM1607-ND

16.41 287.00

958.00

Series P, Chameleon — For General or Medical Applications (See chart for part number break down)

84.50

944.00 6VJ1 1687.00 6J4

3190.01 5EFLA2S

1221.00 1425.00 1425.00 1811.00 1781.00 1985.00

1757.00 1527.00

282.23

6VM1S 6VM2S 6VM4S 5EHM1S 5EFM1S 5EFM4S

5EHM4 5EFM1

6

Unfiltered

4

11

6

Gen. Purpose

4

—

68.07 38.61 29.72 31.24 — CCM1200-ND

—

69.85 47.50 29.73 40.13 — CCM1201-ND

Series LA — Power Entry Modules

12

5

Gen. Purpose

2

—

元器件交易网

Power Entry Modules (Cont.)

Rated Current Fig. 120V (Amps)

Termination

Dimensions (mm)

Digi-Key

A

B

C

D

E

F Part No.

Pricing

1

25

100

Series EJS — Enhanced Performance Snap-In Compact RFI Filter IEC Connector Package

10A

6

10

10

6

6

6

Faston Faston Faston Faston Faston Faston

31.50 54.10 58.67 26.92 55.91 — CCM1378-ND 31.50 54.10 58.67 28.50 55.91 — CCM1379-ND 31.50 54.10 58.67 28.50 55.91 — CCM1380-ND 31.50 54.10 58.67 26.92 55.91 — CCM1381-ND 31.50 54.10 58.67 28.50 55.91 — CCM1382-ND 31.50 54.10 58.67 26.92 55.91 — CCM1600-ND

MA604

Rated Current 125V Fig. (Amps)

15

15

15

15

15

15

Output Terminals

Mounting Input Style Config.

PC Terminals Quick Disconnect Quick Disconnect Quick Disconnect Quick Disconnect