CDCLVC1112PW;中文规格书,Datasheet资料

VCS1026中文资料

622.080MHz VCSO FEATURES• Industry Standard 5x7mm SMTFootprint• +3.3 Vdc Supply Voltage• -40°C to 85°C Temp. Range• LVPECL differential outputs• ± 50ppm Absolute Pull Range (APR)• Output Enable/Disable Function• SAW resonator• Extremely Low Jitter• Tape & Reel Packaging• RoHS CompliantDESCRIPTIONSurface mount 5x7mm VCSO operating at3.3V supply with complementary LVPECLoutputs for use in datacom & telecomapplications.ELECTRICAL SPECIFICATIONSParameter Conditions&RemarksMinTypicalMaxUnit Operating ConditionsNominal Frequency f NOM- 622.080 - MHz Operating Temperature Range -40 - 85 °C Storage Temperature Range -55 - 125 °C Supply Voltage V CC; ±5% 3.135 3.300 3.465 VdcSupply Current I cc; Max. V CC; T A = 25°Cload = 50Ω to V CC – 2V- 60 70 mALoad output to V CC – 2V - 50 - ΩFrequency StabilityFrequency vs. Temperature ref to T A = 25°C; V C = constant +20 - -150 ppm Electronic Frequency ControlInput Impedance Z i50 100 - kΩControl Voltage Range V C ; positive monotonic transfer 0.3 - 3.0 Vdc Gain Transfer - 180 - ppm/V Absolute Pull Range APR; all causes (see note 1) ± 50 - - ppm Modulation Bandwidth -3dB ref. 100Hz - 50 - kHz Linearity Deviation from best linear fit - 2 10 % NOTE 1: Minimum guaranteed frequency shift (∆f/f NOM) under all conditions (temperature, aging, supply voltage, load) for 15 years at an average effective operating temperature of +55°C622.080MHz VCSO ELECTRICAL SPECIFICATIONS (Continued)Parameter Conditions&RemarksMinTypicalMaxUnit Output ParametersOutput Signal LVPECLV OL- -V CC-1.620AmplitudeV OH V CC-1.025 - -VdcRise/Fall Times 20% to 80% - 250 400 ps Duty Cycle @ 50% of output signal 45 50 55 % Start up time to reach 90% of final amplitude - - 10 ms100Hz - -85 -75 dBc/Hz1kHz - -110 -100 dBc/Hz10kHz - -140 -130 dBc/Hz100kHz - -143 -140 dBc/Hz Phase Noise1MHz - -143 -140 dBc/Hz12kHz to 20MHz (calculated from Phase Noise) - 0.16 0.3 psRMSPhase Jitter50kHz to 80MHz (calculated from Phase Noise) - 0.16 0.3 psRMSLVPECL OUTPUT WAVEFORM TEST CIRCUIT, LVPECL LOADOUTPUT ENABLE/DISABLE LOGICPad 2 Pad 4 Pad 5Low ”0” outputs disabled HI Z HI ZOpen outputs enabled Output Comp. OutputHigh ”1” outputs enabled Output Comp. Output622.080MHz VCSO622.080MHz VCSOMAXIMUM SOLDERING PROFILETemperature217°C 260°C (Absolute max temperature) Time60-150 sec 10 sec. maxNote: Part is not designed to be reflowed in an inverted position.MSL Level: 1This product is fully compliant to RoHS Directive 2002/95/EC。

1117-_datasheet线性电源LDO

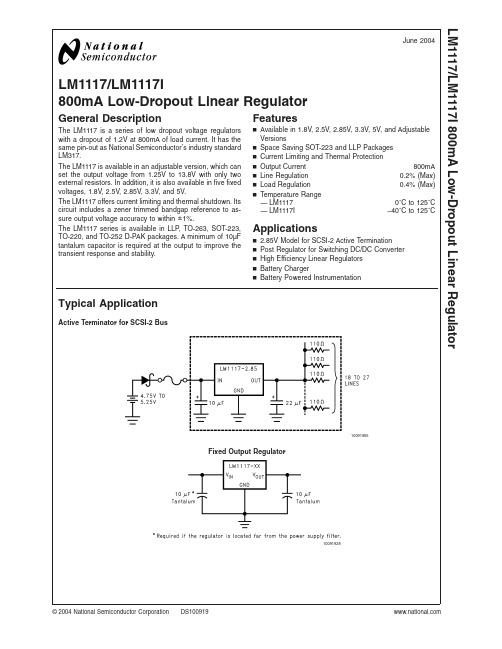

LM1117/LM1117I800mA Low-Dropout Linear RegulatorGeneral DescriptionThe LM1117is a series of low dropout voltage regulators with a dropout of 1.2V at 800mA of load current.It has the same pin-out as National Semiconductor’s industry standard LM317.The LM1117is available in an adjustable version,which can set the output voltage from 1.25V to 13.8V with only two external resistors.In addition,it is also available in five fixed voltages,1.8V,2.5V,2.85V,3.3V,and 5V.The LM1117offers current limiting and thermal shutdown.Its circuit includes a zener trimmed bandgap reference to as-sure output voltage accuracy to within ±1%.The LM1117series is available in LLP ,TO-263,SOT-223,TO-220,and TO-252D-PAK packages.A minimum of 10µF tantalum capacitor is required at the output to improve the transient response and stability.Featuresn Available in 1.8V,2.5V,2.85V,3.3V,5V,and Adjustable Versionsn Space Saving SOT-223and LLP Packages n Current Limiting and Thermal Protection n Output Current 800mA n Line Regulation 0.2%(Max)n Load Regulation 0.4%(Max)n Temperature Range —LM11170˚C to 125˚C —LM1117I −40˚C to 125˚CApplicationsn 2.85V Model for SCSI-2Active Termination n Post Regulator for Switching DC/DC Converter n High Efficiency Linear Regulators n Battery ChargernBattery Powered InstrumentationTypical ApplicationActive Terminator for SCSI-2Bus10091905Fixed Output Regulator10091928June 2004LM1117/LM1117I 800mA Low-Dropout Linear Regulator©2004National Semiconductor Corporation Ordering InformationPackage TemperatureRange Part Number Packaging MarkingTransport Media NSC Drawing 3-lead SOT-2230˚C to +125˚CLM1117MPX-ADJ N03A Tape and Reel MP04ALM1117MPX-1.8N12A Tape and Reel LM1117MPX-2.5N13A Tape and Reel LM1117MPX-2.85N04A Tape and Reel LM1117MPX-3.3N05A Tape and Reel LM1117MPX-5.0N06A Tape and Reel −40˚C to +125˚CLM1117IMPX-ADJ N03B Tape and Reel LM1117IMPX-3.3N05B Tape and Reel LM1117IMPX-5.0N06B Tape and Reel3-lead TO-2200˚C to +125˚CLM1117T-ADJ LM1117T-ADJ Rails T03B LM1117T-1.8LM1117T-1.8Rails LM1117T-2.5LM1117T-2.5Rails LM1117T-2.85LM1117T-2.85Rails LM1117T-3.3LM1117T-3.3Rails LM1117T-5.0LM1117T-5.0Rails 3-lead TO-2520˚C to +125˚CLM1117DTX-ADJ LM1117DT-ADJ Tape and Reel TD03B LM1117DTX-1.8LM1117DT-1.8Tape and Reel LM1117DTX-2.5LM1117DT-2.5Tape and Reel LM1117DTX-2.85LM1117DT-2.85Tape and Reel LM1117DTX-3.3LM1117DT-3.3Tape and Reel LM1117DTX-5.0LM1117DT-5.0Tape and Reel −40˚C to +125˚CLM1117IDTX-ADJ LM1117IDT-ADJ Tape and Reel LM1117IDTX-3.3LM1117IDT-3.3Tape and Reel LM1117IDTX-5.0LM1117IDT-5.0Tape and Reel 8-lead LLP0˚C to +125˚CLM1117LDX-ADJ 1117ADJ Tape and Reel LDC08A LM1117LDX-1.81117-18Tape and Reel LM1117LDX-2.51117-25Tape and Reel LM1117LDX-2.851117-28Tape and Reel LM1117LDX-3.31117-33Tape and Reel LM1117LDX-5.01117-50Tape and Reel −40˚C to 125˚CLM1117ILDX-ADJ 1117IAD Tape and Reel LM1117ILDX-3.31117I33Tape and Reel LM1117ILDX-5.01117I50Tape and Reel TO-2630˚C to +125˚CLM1117SX-ADJ LM1117SADJ Tape and Reel TS3B LM1117SX-2.85LM1117S2.85Tape and Reel LM1117SX-3.3LM1117S3.3Tape and Reel LM1117SX-5.0LM1117S5.0Tape and ReelL M 1117/L M 1117I 2Block Diagram10091901Connection DiagramsSOT-22310091904Top ViewTO-22010091902Top ViewTO-25210091938Top ViewTO-26310091944Top View10091945Side ViewLLP10091946When using the LLP packagePins2,3&4must be connected together andPins5,6&7must be connected togetherTop ViewLM1117/LM1117I3Absolute Maximum Ratings (Note 1)If Military/Aerospace specified devices are required,please contact the National Semiconductor Sales Office/Distributors for availability and specifications.Maximum Input Voltage (V IN to GND)20VPower Dissipation (Note 2)Internally LimitedJunction Temperature (T J )(Note 2)150˚CStorage Temperature Range -65˚C to 150˚CLead TemperatureTO-220(T)Package 260˚C,10sec SOT-223(IMP)Package 260˚C,4secESD Tolerance (Note 3)2000VOperating Ratings (Note 1)Input Voltage (V IN to GND)15VJunction Temperature Range (T J )(Note 2)LM11170˚C to 125˚C LM1117I−40˚C to 125˚CLM1117Electrical CharacteristicsTypicals and limits appearing in normal type apply for T J =25˚C.Limits appearing in Boldface type apply over the entire junc-tion temperature range for operation,0˚C to 125˚C.Symbol Parameter ConditionsMin (Note 5)Typ (Note 4)Max (Note 5)UnitsV REFReference VoltageLM1117-ADJI OUT =10mA,V IN -V OUT =2V,T J =25˚C 10mA ≤I OUT ≤800mA,1.4V ≤V IN -V OUT ≤10V1.2381.2251.2501.2501.2621.270V VV OUTOutput VoltageLM1117-1.8I OUT =10mA,V IN =3.8V,T J =25˚C 0≤I OUT ≤800mA,3.2V ≤V IN ≤10V 1.7821.746 1.8001.800 1.8181.854V V LM1117-2.5I OUT =10mA,V IN =4.5V,T J =25˚C 0≤I OUT ≤800mA,3.9V ≤V IN ≤10V 2.4752.450 2.5002.500 2.5252.550V V LM1117-2.85I OUT =10mA,V IN =4.85V,T J =25˚C 0≤I OUT ≤800mA,4.25V ≤V IN ≤10V 0≤I OUT ≤500mA,V IN =4.10V 2.8202.7902.790 2.8502.8502.850 2.8802.9102.910V V V LM1117-3.3I OUT =10mA,V IN =5V T J =25˚C 0≤I OUT ≤800mA,4.75V ≤V IN ≤10V 3.2673.235 3.3003.300 3.3333.365V V LM1117-5.0I OUT =10mA,V IN =7V,T J =25˚C 0≤I OUT ≤800mA,6.5V ≤V IN ≤12V4.9504.9005.0005.000 5.0505.100V V ∆V OUTLine Regulation (Note 6)LM1117-ADJI OUT =10mA,1.5V ≤V IN -V OUT ≤13.75V 0.0350.2%LM1117-1.8I OUT =0mA,3.2V ≤V IN ≤10V 16mV LM1117-2.5I OUT =0mA,3.9V ≤V IN ≤10V 16mVLM1117-2.85I OUT =0mA,4.25V ≤V IN ≤10V 16mV LM1117-3.3I OUT =0mA,4.75V ≤V IN ≤15V 16mV LM1117-5.0I OUT =0mA,6.5V ≤V IN ≤15V110mVL M 1117/L M 1117I 4LM1117Electrical Characteristics(Continued)Typicals and limits appearing in normal type apply for T J=25˚C.Limits appearing in Boldface type apply over the entire junc-tion temperature range for operation,0˚C to125˚C.Symbol Parameter ConditionsMin(Note5)Typ(Note4)Max(Note5)Units∆V OUT Load Regulation(Note6)LM1117-ADJV IN-V OUT=3V,10≤I OUT≤800mA0.20.4% LM1117-1.8V IN=3.2V,0≤I OUT≤800mA110mVLM1117-2.5V IN=3.9V,0≤I OUT≤800mA110mVLM1117-2.85V IN=4.25V,0≤I OUT≤800mA110mV LM1117-3.3V IN=4.75V,0≤I OUT≤800mA110mV LM1117-5.0V IN=6.5V,0≤I OUT≤800mA115mVV IN-V OUT Dropout Voltage(Note7)I OUT=100mA 1.10 1.20V I OUT=500mA 1.15 1.25V I OUT=800mA 1.20 1.30VI LIMIT Current Limit V IN-V OUT=5V,T J=25˚C80012001500mAMinimum Load Current(Note8)LM1117-ADJV IN=15V 1.75mAQuiescent Current LM1117-1.8V IN≤15V510mALM1117-2.5V IN≤15V510mALM1117-2.85V IN≤10V510mALM1117-3.3V IN≤15V510mALM1117-5.0V IN≤15V510mA Thermal Regulation T A=25˚C,30ms Pulse0.010.1%/W Ripple Regulation f RIPPLE=120Hz,V IN-V OUT=3V V RIPPLE=1V PP6075dB Adjust Pin Current60120µAAdjust Pin Current Change 10≤I OUT≤800mA,1.4V≤V IN-V OUT≤10V0.25µATemperature Stability0.5% Long Term Stability T A=125˚C,1000Hrs0.3% RMS Output Noise(%of V OUT),10Hz≤f≤10kHz0.003%Thermal Resistance Junction-to-Case 3-Lead SOT-22315.0˚C/W 3-Lead TO-220 3.0˚C/W 3-Lead TO-25210˚C/WThermal Resistance Junction-to-Ambient (No air flow)3-Lead SOT-223(No heat sink)136˚C/W3-Lead TO-220(No heat sink)79˚C/W3-Lead TO-252(Note9)(No heat sink)92˚C/W3-Lead TO-26355˚C/W8-Lead LLP(Note10)40˚C/WLM1117/LM1117I5LM1117I Electrical CharacteristicsTypicals and limits appearing in normal type apply for T J =25˚C.Limits appearing in Boldface type apply over the entire junc-tion temperature range for operation,−40˚C to 125˚C.Symbol Parameter ConditionsMin (Note 5)Typ (Note 4)Max (Note 5)UnitsV REFReference VoltageLM1117I-ADJI OUT =10mA,V IN -V OUT =2V,T J =25˚C 10mA ≤I OUT ≤800mA,1.4V ≤V IN -V OUT ≤10V1.2381.2001.2501.2501.2621.290V VV OUTOutput VoltageLM1117I-3.3I OUT =10mA,V IN =5V,T J =25˚C 0≤I OUT ≤800mA,4.75V ≤V IN ≤10V 3.2673.168 3.3003.300 3.3333.432V V LM1117I-5.0I OUT =10mA,V IN =7V,T J =25˚C 0≤I OUT ≤800mA,6.5V ≤V IN ≤12V4.9504.8005.0005.000 5.0505.200V V ∆V OUTLine Regulation (Note 6)LM1117I-ADJI OUT =10mA,1.5V ≤V IN -V OUT ≤13.75V 0.0350.3%LM1117I-3.3I OUT =0mA,4.75V ≤V IN ≤15V 110mV LM1117I-5.0I OUT =0mA,6.5V ≤V IN ≤15V115mV ∆V OUTLoad Regulation (Note 6)LM1117I-ADJV IN -V OUT =3V,10≤I OUT ≤800mA 0.20.5%LM1117I-3.3V IN =4.75V,0≤I OUT ≤800mA 115mV LM1117I-5.0V IN =6.5V,0≤I OUT ≤800mA120mV V IN -V OUTDropout Voltage (Note 7)I OUT =100mA 1.10 1.30V I OUT =500mA 1.15 1.35V I OUT =800mA1.20 1.40V I LIMITCurrent Limit V IN -V OUT =5V,T J =25˚C 80012001500mA Minimum Load Current (Note 8)LM1117I-ADJ V IN =15V 1.75mA Quiescent CurrentLM1117I-3.3V IN ≤15V 515mA LM1117I-5.0V IN ≤15V515mA Thermal Regulation T A =25˚C,30ms Pulse0.010.1%/W Ripple Regulation f RIPPLE =120Hz,V IN -V OUT =3V V RIPPLE =1V PP6075dBAdjust Pin Current 60120µA Adjust Pin Current Change10≤I OUT ≤800mA,1.4V ≤V IN -V OUT ≤10V 0.210µA Temperature Stability 0.5%Long Term Stability T A =125˚C,1000Hrs0.3%RMS Output Noise (%of V OUT ),10Hz ≤f ≤10kHz 0.003%Thermal Resistance Junction-to-Case 3-Lead SOT-22315.0˚C/W 3-Lead TO-25210˚C/W Thermal Resistance Junction-to-Ambient No air flow)3-Lead SOT-223(No heat sink)136˚C/W 3-Lead TO-252(No heat sink)(Note 9)92˚C/W 8-Lead LLP(Note 10)40˚C/WNote 1:Absolute Maximum Ratings indicate limits beyond which damage to the device may occur.Operating Ratings indicate conditions for which the device is intended to be functional,but specific performance is not guaranteed.For guaranteed specifications and the test conditions,see the Electrical Characteristics.L M 1117/L M 1117I 6Note 2:The maximum power dissipation is a function of T J(max),θJA ,and T A .The maximum allowable power dissipation at any ambient temperature is P D =(T J(max)–T A )/θJA .All numbers apply for packages soldered directly into a PC board.Note 3:For testing purposes,ESD was applied using human body model,1.5k Ωin series with 100pF.Note 4:Typical Values represent the most likely parametric norm.Note 5:All limits are guaranteed by testing or statistical analysis.Note 6:Load and line regulation are measured at constant junction room temperature.Note 7:The dropout voltage is the input/output differential at which the circuit ceases to regulate against further reduction in input voltage.It is measured when the output voltage has dropped 100mV from the nominal value obtained at V IN =V OUT +1.5V.Note 8:The minimum output current required to maintain regulation.Note 9:Minimum pad size of 0.038in 2Note 10:Thermal Performance for the LLP was obtained using JESD51-7board with six vias and an ambient temperature of 22˚C.For information about improved thermal performance and power dissipation for the LLP ,refer to Application Note AN-1187.Typical Performance CharacteristicsDropout Voltage (V IN -VOUT )Short-Circuit Current1009192210091923Load Regulation LM1117-ADJ Ripple Rejection1009194310091906LM1117/LM1117I7Typical Performance Characteristics(Continued)LM1117-ADJ Ripple Rejection vs.CurrentTemperature Stability1009190710091925Adjust Pin Current LM1117-2.85Load Transient Response1009192610091908LM1117-5.0Load Transient Response LM1117-2.85Line Transient Response1009190910091910L M 1117/L M 1117I 8Typical Performance Characteristics(Continued) LM1117-5.0Line Transient Response10091911Application Note1.0External Capacitors/Stability1.1Input Bypass CapacitorAn input capacitor is recommended.A10µF tantalum on theinput is a suitable input bypassing for almost all applications.1.2Adjust Terminal Bypass CapacitorThe adjust terminal can be bypassed to ground with a by-pass capacitor(C ADJ)to improve ripple rejection.This by-pass capacitor prevents ripple from being amplified as theoutput voltage is increased.At any ripple frequency,theimpedance of the C ADJ should be less than R1to prevent theripple from being amplified:1/(2π*f RIPPLE*C ADJ)<R1The R1is the resistor between the output and the adjust pin.Its value is normally in the range of100-200Ω.For example,with R1=124Ωand f RIPPLE=120Hz,the C ADJ should be>11µF.1.3Output CapacitorThe output capacitor is critical in maintaining regulator sta-bility,and must meet the required conditions for both mini-mum amount of capacitance and ESR(Equivalent Series Resistance).The minimum output capacitance required by the LM1117is10µF,if a tantalum capacitor is used.Any increase of the output capacitance will merely improve the loop stability and transient response.The ESR of the output capacitor should range between0.3Ω-22Ω.In the case of the adjustable regulator,when the C ADJ is used,a larger output capacitance(22µf tantalum)is required.2.0Output VoltageThe LM1117adjustable version develops a1.25V reference voltage,V REF,between the output and the adjust terminal. As shown in Figure1,this voltage is applied across resistor R1to generate a constant current I1.The current I ADJ from the adjust terminal could introduce error to the output.But since it is very small(60µA)compared with the I1and very constant with line and load changes,the error can be ig-nored.The constant current I1then flows through the output set resistor R2and sets the output voltage to the desired level.For fixed voltage devices,R1and R2are integrated inside the devices.3.0Load RegulationThe LM1117regulates the voltage that appears between itsoutput and ground pins,or between its output and adjustpins.In some cases,line resistances can introduce errors tothe voltage across the load.To obtain the best load regula-tion,a few precautions are needed.Figure2,shows a typical application using a fixed outputregulator.The Rt1and Rt2are the line resistances.It isobvious that the V LOAD is less than the V OUT by the sum ofthe voltage drops along the line resistances.In this case,theload regulation seen at the R LOAD would be degraded fromthe data sheet specification.To improve this,the load shouldbe tied directly to the output terminal on the positive side anddirectly tied to the ground terminal on the negative side.10091917FIGURE1.Basic Adjustable RegulatorLM1117/LM1117I9Application Note(Continued)When the adjustable regulator is used (Figure 3),the best performance is obtained with the positive side of the resistor R1tied directly to the output terminal of the regulator rather than near the load.This eliminates line drops from appearing effectively in series with the reference and degrading regu-lation.For example,a 5V regulator with 0.05Ωresistance between the regulator and load will have a load regulation due to line resistance of 0.05Ωx I L .If R1(=125Ω)is con-nected near the load,the effective line resistance will be 0.05Ω(1+R2/R1)or in this case,it is 4times worse.In addition,the ground side of the resistor R2can be returned near the ground of the load to provide remote ground sens-ing and improve load regulation.4.0Protection DiodesUnder normal operation,the LM1117regulators do not need any protection diode.With the adjustable device,the internal resistance between the adjust and output terminals limits the current.No diode is needed to divert the current around the regulator even with capacitor on the adjust terminal.The adjust pin can take a transient signal of ±25V with respect to the output voltage without damaging the device.When a output capacitor is connected to a regulator and the input is shorted to ground,the output capacitor will discharge into the output of the regulator.The discharge current de-pends on the value of the capacitor,the output voltage of the regulator,and rate of decrease of V IN .In the LM1117regu-lators,the internal diode between the output and input pins can withstand microsecond surge currents of 10A to 20A.With an extremely large output capacitor (≥1000µF),and with input instantaneously shorted to ground,the regulator could be damaged.In this case,an external diode is recommended between the output and input pins to protect the regulator,as shown in Figure 4.5.0Heatsink RequirementsWhen an integrated circuit operates with an appreciable current,its junction temperature is elevated.It is important to quantify its thermal limits in order to achieve acceptable performance and reliability.This limit is determined by sum-ming the individual parts consisting of a series of tempera-ture rises from the semiconductor junction to the operating environment.A one-dimensional steady-state model of con-duction heat transfer is demonstrated in Figure 5.The heat generated at the device junction flows through the die to the die attach pad,through the lead frame to the surrounding case material,to the printed circuit board,and eventually to the ambient environment.Below is a list of variables that may affect the thermal resistance and in turn the need for a heatsink.R θJC (ComponentVariables)R θCA (ApplicationVariables)Leadframe Size &Material Mounting Pad Size,Material,&Location No.of Conduction Pins Placement of Mounting PadDie SizePCB Size &Material Die Attach Material Traces Length &Width Molding Compound Size and MaterialAdjacent Heat Sources Volume of Air Ambient Temperatue Shape of Mounting Pad10091918FIGURE 2.Typical Application using Fixed OutputRegulator 10091919FIGURE 3.Best Load Regulation using AdjustableOutput Regulator 10091915FIGURE 4.Regulator with Protection Diode L M 1117/L M 1117I10Application Note(Continued)The LM1117regulators have internal thermal shutdown to protect the device from over-heating.Under all possible operating conditions,the junction temperature of the LM1117must be within the range of 0˚C to 125˚C.A heatsink may be required depending on the maximum power dissipation and maximum ambient temperature of the application.To deter-mine if a heatsink is needed,the power dissipated by the regulator,P D ,must be calculated:I IN =I L +I GP D =(V IN -V OUT )I L +V IN I GFigure 6shows the voltages and currents which are present in the circuit.The next parameter which must be calculated is the maxi-mum allowable temperature rise,T R (max):T R (max)=T J (max)-T A (max)where T J (max)is the maximum allowable junction tempera-ture (125˚C),and T A (max)is the maximum ambient tem-perature which will be encountered in the application.Using the calculated values for T R (max)and P D ,the maxi-mum allowable value for the junction-to-ambient thermal resistance (θJA )can be calculated:θJA =T R (max)/P DIf the maximum allowable value for θJA is found to be ≥136˚C/W for SOT-223package or ≥79˚C/W for TO-220package or ≥92˚C/W for TO-252package,no heatsink is needed since the package alone will dissipate enough heat to satisfy these requirements.If the calculated value for θJA falls below these limits,a heatsink is required.As a design aid,Table 1shows the value of the θJA of SOT-223and TO-252for different heatsink area.The copper patterns that we used to measure these θJA s are shown at the end of the Application Notes Section.Figure 7and Figure 8reflects the same test results as what are in the Table 1Figure 9and Figure 10shows the maximum allowable power dissipation vs.ambient temperature for the SOT-223and TO-252device.Figures Figure 11and Figure 12shows the maximum allowable power dissipation vs.copper area (in 2)for the SOT-223and TO-252devices.Please see AN1028for power enhancement techniques to be used with SOT-223and TO-252packages.*Application Note AN-1187discusses improved thermal per-formance and power dissipation for the LLP .TABLE 1.θJA Different Heatsink AreaLayout Copper AreaThermal ResistanceTop Side (in 2)*Bottom Side (in 2)(θJA ,˚C/W)SOT-223(θJA ,˚C/W)TO-25210.0123013610320.0660*******.30846040.530755450.76069526106647700.211584800.49870900.689631000.8825711017957120.0660.06612589130.1750.175937210091937FIGURE 5.Cross-sectional view of Integrated Circuit Mounted on a printed circuit board.Note that the case temperature is measured at the point where the leadscontact with the mounting pad surface 10091916FIGURE 6.Power Dissipation DiagramLM1117/LM1117IApplication Note(Continued)TABLE 1.θJA Different Heatsink Area (Continued)Layout Copper AreaThermal Resistance140.2840.2848361150.3920.3927555160.50.57053*Tab of device attached to topside copperL M 1117/L M 1117IApplication Note(Continued)10091913 FIGURE7.θJA vs.1oz Copper Area for SOT-22310091934 FIGURE8.θJA vs.2oz Copper Area for TO-25210091912 FIGURE9.Maximum Allowable Power Dissipation vs.Ambient Temperature for SOT-22310091936FIGURE10.Maximum Allowable Power Dissipation vs.Ambient Temperature for TO-25210091914FIGURE11.Maximum Allowable Power Dissipation vs.1oz Copper Area for SOT-22310091935FIGURE12.Maximum Allowable Power Dissipation vs.2oz Copper Area for TO-252LM1117/LM1117IApplication Note(Continued)10091941FIGURE 13.Top View of the Thermal Test Pattern in Actual ScaleL M 1117/L M 1117IApplication Note(Continued)10091942FIGURE14.Bottom View of the Thermal Test Pattern in Actual Scale LM1117/LM1117ITypical Application Circuits10091930Adjusting Output of Fixed Regulators10091931Regulator with Reference100919291.25V to 10V Adjustable Regulator with ImprovedRipple Rejection100919275V Logic Regulator with Electronic Shutdown*L M 1117/L M 1117ITypical Application Circuits(Continued)10091932Battery Backed-Up Regulated Supply10091933Low Dropout Negative Supply LM1117/LM1117IPhysical Dimensionsinches (millimeters)unless otherwise noted3-Lead SOT-223NS Package Number MP04A3-Lead TO-220NS Package Number T03BL M 1117/L M 1117IPhysical Dimensions inches(millimeters)unless otherwise noted(Continued)3-Lead TO-263NS Package Number TS3B LM1117/LM1117IPhysical Dimensionsinches (millimeters)unless otherwise noted (Continued)3-Lead TO-252NS Package Number TD03B8-Lead LLPNS Package Number LDC08AL M 1117/L M 1117INotesLIFE SUPPORT POLICYNATIONAL’S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF THE PRESIDENT AND GENERAL COUNSEL OF NATIONAL SEMICONDUCTOR CORPORATION.As used herein:1.Life support devices or systems are devices orsystems which,(a)are intended for surgical implant into the body,or(b)support or sustain life,and whose failure to perform when properly used in accordance with instructions for use provided in the labeling,can be reasonably expected to result in a significant injury to the user.2.A critical component is any component of a lifesupport device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system,or to affect its safety or effectiveness.BANNED SUBSTANCE COMPLIANCENational Semiconductor certifies that the products and packing materials meet the provisions of the Customer Products Stewardship Specification(CSP-9-111C2)and the Banned Substances and Materials of Interest Specification (CSP-9-111S2)and contain no‘‘Banned Substances’’as defined in CSP-9-111S2.National Semiconductor Americas CustomerSupport CenterEmail:new.feedback@ Tel:1-800-272-9959National SemiconductorEurope Customer Support CenterFax:+49(0)180-5308586Email:europe.support@Deutsch Tel:+49(0)6995086208English Tel:+44(0)8702402171Français Tel:+33(0)141918790National SemiconductorAsia Pacific CustomerSupport CenterEmail:ap.support@National SemiconductorJapan Customer Support CenterFax:81-3-5639-7507Email:jpn.feedback@Tel:81-3-5639-7560 LM1117/LM1117I 800mA Low-Dropout Linear RegulatorNational does not assume any responsibility for use of any circuitry described,no circuit patent licenses are implied and National reserves the right at any time without notice to change said circuitry and specifications.。

SC1112中文资料

V S µA mV V V V S S µA

VTTINTH DeltaTRACK VIN = 3.30V, IO = 0A

1.45

1.52 200

1.55

V mV

2001 Semtech Corp.

2

元器件交易网

SC1112

POWER MANAGEMENT Electrical Characteristics (Cont.)

500 500

AGP Gate Current

IsourceAGPgate IsinkAGPgate

5VSTBY = 4.75V, Vgate = 3.0V

500 500

ADJ Gate Current

IsourceADJgate IsinkADJgate

5VSTBY = 4.75V, Vgate = 3.0V

500 500

Load Regulation Line Regulation Gain (AOL)(2)

LOADREG LINEREG GAINLDO

VTTIN = 3.30V, IO = 0 to 2A VTTIN = 3.13V to 3.47V, Io = 2A LDOS Output to GATE

V mA

1.5 (Cdelay*SCTH)/ISC 16 650 1.450 1.060 1.330 22 700 1.500 1.085 1.350 (Cdelay*PGTH_1.2)/IPG (Cdelay*PGTH_1.5)/IPG 16 22 28 28 750 1.550 1.110 1.390

GND AGPGATE AGPSEN VTTGATE VTTSEN AGPSEL VTTSEL VTTIN

CDCLVP1212RHAT;CDCLVP1212RHAR;CDCLVP1212EVM;中文规格书,Datasheet资料

VVV V V V VCDCLVP1212 SCAS886B–AUGUST2009–REVISED AUGUST2011 12LVPECL Output,High-Performance Clock BufferCheck for Samples:CDCLVP1212FEATURES DESCRIPTIONThe CDCLVP1212is a highly versatile,low additive •2:12Differential Bufferjitter buffer that can generate12copies of LVPECL •Selectable Clock Inputs Through Control Pin clock outputs from one of two selectable LVPECL,•Universal Inputs Accept LVPECL,LVDS,and LVDS,or LVCMOS inputs for a variety of LVCMOS/LVTTL communication applications.It has a maximum clockfrequency up to2GHz.The CDCLVP1212features •12LVPECL Outputsan on-chip multiplexer(MUX)for selecting one of two •Maximum Clock Frequency:2GHz inputs that can be easily configured solely through a•Maximum Core Current Consumption:88mA control pin.The overall additive jitter performance isless than0.1ps,RMS from10kHz to20MHz,and •Very Low Additive Jitter:<100fs,rms in10-kHzoverall output skew is as low as25ps,making the to20-MHz Offset Rangedevice a perfect choice for use in demanding • 2.375-V to3.6-V Device Power Supply applications.•Maximum Propagation Delay:550psThe CDCLVP1212clock buffer distributes one of two •Maximum Output Skew:25ps selectable clock inputs(IN0,IN1)to12pairs of •LVPECL Reference Voltage,V AC_REF,Available differential LVPECL clock outputs(OUT0,OUT11)with minimum skew for clock distribution.The for Capacitive-Coupled InputsCDCLVP1212can accept two clock sources into an •Industrial Temperature Range:–40°C to+85°Cinput multiplexer.The inputs can be LVPECL,LVDS,•ESD Protection Exceeds2kV(HBM)or LVCMOS/LVTTL.•Available in6-mm×6-mm QFN-40(RHA)The CDCLVP1212is specifically designed for driving Package50-Ωtransmission lines.When driving the inputs insingle-ended mode,the LVPECL bias voltage APPLICATIONS(VAC_REF)should be applied to the unused negativeinput pin.However,for high-speed performance up to •Wireless Communications2GHz,differential mode is strongly recommended.•Telecommunications/NetworkingThe CDCLVP1212is packaged in a small40-pin,•Medical Imaging6-mm x6-mm QFN package and is characterized for •Test and Measurement Equipment operation from–40°C to+85°C.Please be aware that an important notice concerning availability,standard warranty,and use in critical applications of TexasInstruments semiconductor products and disclaimers thereto appears at the end of this data sheet.All trademarks are the property of their respective owners.PRODUCTION DATA information is current as of publication date.Copyright©2009–2011,Texas Instruments Incorporated Products conform to specifications per the terms of the TexasInstruments standard warranty.Production processing does notnecessarily include testing of all parameters.CDCLVP1212SCAS886B–AUGUST2009–REVISED This integrated circuit can be damaged by ESD.Texas Instruments recommends that all integrated circuits be handled with appropriate precautions.Failure to observe proper handling and installation procedures can cause damage.ESD damage can range from subtle performance degradation to complete device failure.Precision integrated circuits may be more susceptible to damage because very small parametric changes could cause the device not to meet its published specifications.AVAILABLE OPTIONS(1)T A PACKAGED DEVICES FEATURESCDCLVP1212RHAT40-pin QFN(RHA)package,small tape and reel –40°C to+85°CCDCLVP1212RHAR40-pin QFN(RHA)package,tape and reel(1)For the most current specifications and package information,see the Package Option Addendum located at the end of this data sheet orrefer to our web site at .ABSOLUTE MAXIMUM RATINGS(1)Over operating free-air temperature range(unless otherwise noted).CDCLVP1212UNITV CC Supply voltage range(2)–0.5to4.6VV IN Input voltage range(3)–0.5to V CC+0.5VV OUT Output voltage range(3)–0.5to V CC+0.5VI IN Input current20mAI OUT Output current50mAT A Specified free-air temperature range(no airflow)–40to+85°CT STG Storage temperature range–65to+150°CT J Maximum junction temperature+125°CESD Electrostatic discharge(HBM)2kV (1)Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device.These are stress ratingsonly,and functional operation of the device at these or any other conditions beyond those indicated is not implied.Exposure toabsolute-maximum-rated conditions for extended periods may affect device reliability.(2)All supply voltages must be supplied simultaneously.(3)The input and output negative voltage ratings may be exceeded if the input and output clamp-current ratings are observed. RECOMMENDED OPERATING CONDITIONSOver operating free-air temperature range(unless otherwise noted).CDCLVP1212PARAMETER MIN TYP MAX UNITV CC Supply voltage 2.375 2.50/3.30 3.60VT A Ambient temperature–40+85°C PACKAGE DISSIPATION RATINGS(1)(2)VALUETEST4×4VIASPARAMETER CONDITIONS ON PAD UNIT0LFM36.1°C/WθJA Thermal resistance,junction-to-ambient150LFM30.2°C/W400LFM28.2°C/WθJP(3)Thermal resistance,junction-to-pad 3.58°C/W(1)The package thermal resistance is calculated in accordance with JESD51and JEDEC2S2P(high-K board).(2)Connected to GND with16thermal vias(0.3-mm diameter).(3)θJP(junction-to-pad)is used for the QFN package,because the primary heat flow is from the junction to the GND pad of the QFNpackage.2Submit Documentation Feedback Copyright©2009–2011,Texas Instruments IncorporatedProduct Folder Link(s):CDCLVP1212CDCLVP1212 SCAS886B–AUGUST2009–REVISED AUGUST2011ELECTRICAL CHARACTERISTICS:LVCMOS Input(1)At V CC=2.375V to3.6V and T A=–40°C to+85°C(unless otherwise noted).CDCLVP1212PARAMETER TEST CONDITIONS MIN TYP MAX UNITf IN Input frequency200MHzExternal threshold voltage applied toV th Input threshold voltage 1.1 1.8Vcomplementary inputV IH Input high voltage V th+0.1V CC VV IL Input low voltage0V th–0.1VI IH Input high current V CC=3.6V,V IH=3.6V40μAI IL Input low current V CC=3.6V,V IL=0V–40μAΔV/ΔT Input edge rate20%to80% 1.5V/nsI CAP Input capacitance5pF(1)Figure3and Figure4show dc test setup.ELECTRICAL CHARACTERISTICS:Differential Input(1)At V CC=2.375V to3.6V and T A=–40°C to+85°C(unless otherwise noted).CDCLVP1212PARAMETER TEST CONDITIONS MIN TYP MAX UNITf IN Input frequency Clock input2000MHzf IN≤1.5GHz0.1 1.5VV IN,DIFF,PP Differential input peak-peak voltage1.5GHz≤f IN≤2GHz0.2 1.5VV ICM Input common-mode level 1.0V CC–0.3VI IH Input high current V CC=3.6V,V IH=3.6V40μAI IL Input low current V CC=3.6V,V IL=0V–40μAΔV/ΔT Input edge rate20%to80% 1.5V/nsI CAP Input capacitance5pF(1)Figure5and Figure6show dc test setup.Figure7shows ac test setup.Copyright©2009–2011,Texas Instruments Incorporated Submit Documentation Feedback3Product Folder Link(s):CDCLVP1212CDCLVP1212SCAS886B–AUGUST2009–REVISED ELECTRICAL CHARACTERISTICS:LVPECL Output(1)At V CC=2.375V to2.625V and T A=–40°C to+85°C(unless otherwise noted).CDCLVP1212PARAMETER TEST CONDITIONS MIN TYP MAX UNITV OH Output high voltage V CC–1.26V CC–0.9VV OL Output low voltage V CC–1.7V CC–1.3VV OUT,DIFF,PP Differential output peak-peak voltage f IN≤2GHz0.5 1.35VV AC_REF Input bias voltage(2)I AC_REF=2mA V CC–1.6V CC–1.1VV IN,DIFF,PP=0.1V550pst PD Propagation delayV IN,DIFF,PP=0.3V550pst SK,PP Part-to-part skew150pst SK,O Output skew25psCrossing-point-to-crossing-point distortion,t SK,P Pulse skew(with50%duty cycle input)–5050psf OUT=100MHzf OUT=100MHz,V IN,SE=V CC,V th=1.25V,0.11ps,RMS10kHz to20MHzf OUT=100MHz,V IN,SE=0.9V,0.128ps,RMSV th=1.1V,10kHz to20MHzRandom additive jitter(with50%duty f OUT=2GHz,V IN,DIFF,PP=0.2V,t RJIT0.053ps,RMS cycle input)V ICM=1V,10kHz to20MHzf OUT=100MHz,V IN,DIFF,PP=0.15V,0.093ps,RMSV ICM=1V,10kHz to20MHzf OUT=100MHz,V IN,DIFF,PP=1V,0.092ps,RMSV ICM=1V,10kHz to20MHzt R/t F Output rise/fall time20%to80%200psI EE Supply internal current Outputs unterminated88mAI CC Output and internal supply current All outputs terminated,50Ωto V CC–2468mA(1)Figure8and Figure9show dc and ac test setup.(2)Internally generated bias voltage(V AC_REF)is for3.3-V operation only.It is recommended to apply externally generated bias voltage forV CC<3.0V.4Submit Documentation Feedback Copyright©2009–2011,Texas Instruments IncorporatedProduct Folder Link(s):CDCLVP1212CDCLVP1212 SCAS886B–AUGUST2009–REVISED AUGUST2011ELECTRICAL CHARACTERISTICS:LVPECL Output(1)At V CC=3.0V to3.6V and T A=–40°C to+85°C(unless otherwise noted).CDCLVP1212PARAMETER TEST CONDITIONS MIN TYP MAX UNITV OH Output high voltage V CC–1.26V CC–0.9VV OL Output low voltage V CC–1.7V CC–1.3VV OUT,DIFF,PP Differential output peak-peak voltage f IN≤2GHz0.65 1.35VV AC_REF Input bias voltage I AC_REF=2mA V CC–1.6V CC–1.1VV IN,DIFF,PP=0.1V550pst PD Propagation delayV IN,DIFF,PP=0.3V550pst SK,PP Part-to-part skew150pst SK,O Output skew25psCrossing-point-to-crossing-point distortion,t SK,P Pulse skew(with50%duty cycle input)–5050psf OUT=100MHzf OUT=100MHz,V IN,SE=V CC,V th=1.65V,0.101ps,RMS10kHz to20MHzf OUT=100MHz,V IN,SE=0.9V,0.130ps,RMSV th=1.1V,10kHz to20MHzRandom additive jitter(with50%duty f OUT=2GHz,V IN,DIFF,PP=0.2V,t RJIT0.069ps,RMS cycle input)V ICM=1V,10kHz to20MHzf OUT=100MHz,V IN,DIFF,PP=0.15V,0.094ps,RMSV ICM=1V,10kHz to20MHzf OUT=100MHz,V IN,DIFF,PP=1V,0.094ps,RMSV ICM=1V,10kHz to20MHzt R/t F Output rise/fall time20%to80%200psI EE Supply internal current Outputs unterminated88mAI CC Output and internal supply current All outputs terminated,50Ωto V CC–2468mA(1)Figure8and Figure9show dc and ac test setup.Copyright©2009–2011,Texas Instruments Incorporated Submit Documentation Feedback5Product Folder Link(s):CDCLVP1212CDCLVP1212Thermal Pad(1)12345678910I N _S E LI N P 1I N N 1N CV C CV C CV A C _R E FI N N 0I N P 0OUTN3OUTP3OUTN2OUTP2OUTN1OUTP1OUTN0OUTP0V CCV CC 20191817161514131211O U T P 7O U T P 5G N DO U T P 6O U T P 4O U T N 6O U T N 4O U T N 7O U T N 5G N D 30292827262524232221V CC OUTP8OUTN8OUTP9OUTN9OUTP10OUTN10OUTP11OUTN11V CC31323334353637383940N C CDCLVP1212SCAS886B –AUGUST 2009–REVISED AUGUST 2011PIN CONFIGURATIONRHA PACKAGEQFN-40(TOP VIEW)(1)Thermal pad must be soldered to ground.6Submit Documentation FeedbackCopyright ©2009–2011,Texas Instruments IncorporatedProduct Folder Link(s):CDCLVP1212CDCLVP1212 SCAS886B–AUGUST2009–REVISED AUGUST2011 PIN DESCRIPTIONSCDCLVP1212Pin DescriptionsTERMINAL TERMINAL PULL-UP/NAME NO.TYPE PULLDOWN DESCRIPTION5,6,11,20,V CC Power— 2.5-V/3.3-V supplies for the device31,40GND21,30Ground—Device groundsINP0,INN09,8Input—Differential input pair or single-ended input.Unused input pair can be left floating.Redundant differential input pair or single-ended input.Unused input pair can be INP1,INN12,3Input—left floating.OUTP11,38,39Output—Differential LVPECL output pair no.11.Unused output pair can be left floating.OUTN11OUTP10,36,37Output—Differential LVPECL output pair no.10.Unused output pair can be left floating.OUTN10OUTP9,34,35Output—Differential LVPECL output pair no.9.Unused output pair can be left floating.OUTN9OUTP8,32,33Output—Differential LVPECL output pair no.8.Unused output pair can be left floating.OUTN8OUTP7,28,29Output—Differential LVPECL output pair no.7.Unused output pair can be left floating.OUTN7OUTP6,26,27Output—Differential LVPECL output pair no.6.Unused output pair can be left floating.OUTN6OUTP5,24,25Output—Differential LVPECL output pair no.5.Unused output pair can be left floating.OUTN5OUTP4,22,23Output—Differential LVPECL output pair no.4.Unused output pair can be left floating.OUTN4OUTP3,18,19Output—Differential LVPECL output pair no.3.Unused output pair can be left floating.OUTN3OUTP2,16,17Output—Differential LVPECL output pair no.2.Unused output pair can be left floating.OUTN2OUTP1,14,15Output—Differential LVPECL output pair no.1.Unused output pair can be left floating.OUTN1OUTP012,13Output—Differential LVPECL output pair no.0.Unused output pair can be left floating.OUTN0PulldownIN_SEL1Input MUX select input for input choice(see Table2)(see Table1)Bias voltage output for capacitive coupled inputs.Do not use V AC_REF at V CC< V AC_REF7Output— 3.0V.If used,it is recommended to use a0.1-μF capacitor to GND on this pin.The output current is limited to2mA.NC4,10——Do not connectTable1.Pin CharacteristicsPARAMETER MIN TYP MAX UNITSR PULLDOWN Input pulldown resistor150kΩTable2.Input Selection TableIN_SEL ACTIVE CLOCK INPUT0INP0,INN01INP1,INN1Copyright©2009–2011,Texas Instruments Incorporated Submit Documentation Feedback7Product Folder Link(s):CDCLVP12120.20.40.60.81.01.21.41.62.01.8Frequency (GHz)1.00.90.80.70.60.50.4D i f f e r e n t i a l O u t p u t P e a k -t o -P e a k V o l t a g e (V)0.20.40.60.81.01.21.41.62.01.8Frequency (GHz)1.11.21.31.00.90.80.70.60.50.4D i f f e r e n t i a l O u t p u t P e a k -t o -P e a k V o l t a g e (V )CDCLVP1212SCAS886B –AUGUST 2009–REVISED AUGUST 2011TYPICAL CHARACTERISTICSAt T A =–40°C to +85°C (unless otherwise noted).DIFFERENTIAL OUTPUT PEAK-TO-PEAK VOLTAGEvs FREQUENCYFigure 1.DIFFERENTIAL OUTPUT PEAK-TO-PEAK VOLTAGEvs FREQUENCYFigure 2.8Submit Documentation FeedbackCopyright ©2009–2011,Texas Instruments IncorporatedProduct Folder Link(s):CDCLVP1212VV V thV IHmaxV ILmaxV IHminV ILminV IHV ILV th V V V GNDV CCV V CDCLVP1212SCAS886B –AUGUST 2009–REVISED AUGUST 2011TEST CONFIGURATIONSThis section describes the function of each block for the CDCLVP1212.Figure 3through Figure 9illustrate how the device should be set up for a variety of test configurations.Figure 3.DC-Coupled LVCMOS Input During Device TestFigure 4.V th Variation over LVCMOS LevelsFigure 5.DC-Coupled LVPECL Input During Device TestCopyright ©2009–2011,Texas Instruments Incorporated Submit Documentation Feedback9Product Folder Link(s):CDCLVP1212CDCLVP1212SCAS886B–AUGUST2009–REVISED Figure6.DC-Coupled LVDS Input During Device TestV VFigure7.AC-Coupled Differential Input to DeviceFigure8.LVPECL Output DC Configuration During Device TestFigure9.LVPECL Output AC Configuration During Device Test10Submit Documentation Feedback Copyright©2009–2011,Texas Instruments IncorporatedProduct Folder Link(s):CDCLVP1212分销商库存信息:TICDCLVP1212RHAT CDCLVP1212RHAR CDCLVP1212EVM。

AG6200-MCQ中文规格书

AG6200-MCQHDMI转VGA转换器中文数据表V1.3 QQ176490316 TEL136七023 2221变更历史PS:本中文规格书由第三方翻译软件自动翻译,权威信息请以原厂英文版规格书为准。

索引1.特点和功能描述 (2)管脚映射 (2)管脚说明 (3)2.电气特性 (4)直流规范 (5)交流规格 (6)3.包装和标记规范 (6)标记 (6)包装尺寸 (7)4.参考文献 (7)图片列表图1 HDMI到VGA桥接器的应用程序 (1)图2系统框图 (2)图3 48引脚映射 (2)表格列表表1引脚说明 (4)表2正常运行条件 (4)表3直流电源典型电源特性 (5)表4直流规范 (5)表5数字I/O规范 (5)表6 TMDS输入时间 (6)AG6200-MCQ特征将HDMI 1.4b转换为VGAAG6200支持高达1920x1200@60Hz的视频分辨率:AG6200支持热插拔检测内置晶体,无需外挂晶体。

内置5V至1.2V稳压器核心电压1.2V符合HDCP 1.4规范的片上HDCP引擎集成片上HDCP密钥AG6200支持2通道IIS音频接口AG6200支持1080i分辨率AG6200-MCQ封装(QQ176490316 TEL136********)AG6200-MCQ封装尺寸:48-pin QFN,6 mm x 6 mmAG6200-MCQ温度范围(0℃~+85℃)AG6200-MCQ应用电缆适配器扩展底座、扩展坞AG6200-MCQ概述Algoltek AG6200-MCQ芯片是一个HDMI(高清多媒体接口)到VGA桥接芯片。

它将HDMI信号转换为标准VGA信号它可以在适配器、智能电缆等设备中设计图1 HDMI到VGA网桥的应用1、AG6200-MCQ系统框图和功能描述图2系统框图AG6200-MCQ引脚映射图3 48引脚映射AG6200-MCQ管脚说明Tabl表1引脚说明2、AG6200-MCQ电气特性正常工作条件表2正常运行条件直流规范表3直流电源典型电源规格表4直流电源最大供电规范表5数字I/O规交流规格表6 TMDS输入时间3、AG6200-MCQ包装和标记规范AG6200-MCQ标记AG6200-MCQHDMI 转VGA 转换器 11 / 112020-02-08 AG6200-MCQ 包装尺寸QFN48 QFN48注1。

TPS2412PW中文资料

DEVICE TPS2412 TPS2413

ORDERING INFORMATION(1)

TEMPERATURE

PACKAGE (2)

ORDERING CODE

–40°C to 85°C

PW (TSSOP - 8)

TPS2412PW TPS2413PW

MARKING TPS2412 TPS2413

(1) Add an R suffix to the device type for tape and reel. (2) For the most current package and ordering information, see the Package Option Addendum at the end

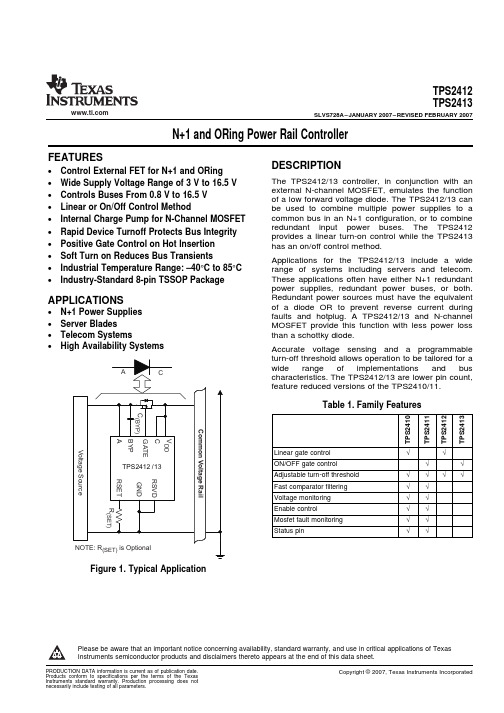

Accurate voltage sensing and a programmable turn-off threshold allows operation to be tailored for a wide range of implementations and bus characteristics. The TPS2412/13 are lower pin count, feature reduced versions of the TPS2410/11.

VALUE –0.3 to 18

7.5 18 –0.3 to 30 –0.3 to 13 0.3 –0.3 to 7 Indefinite 2 500 Internally liited –65 to 150

UNIT V V V V V V V

kV V °C °C

(1) Stresses beyond those listed under absolute maximum ratings may cause permanent damage to the device. These are stress ratings only and functional operation of the device at these or any other conditions beyond those indicated under recommended operating conditions is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

HLW8110 HLW8112智能计量IC用户手册说明书

REV 1.191 / 68HLW8110/HLW8112用户手册REV 1.19REV 1.192 / 68智能计量IC1应用领域 ⏹ 智能家电设备 ⏹ 漏电检测设备 ⏹ 计量电表⏹ 计量插座 ⏹ WIFI 插座 ⏹ 充电桩 ⏹ PDU 设备 ⏹ LED 照明 ⏹ 交通路灯REV 1.193 / 682修订历史时间 修改记录版本 2018-03-16 初始版本 REV 1.00 2018-04-10 增加图表附录 REV 1.01 2018-05-25 增加协议资料 REV 1.02 2018-09-26 修改PIN 脚说明 REV 1.05 2018-09-28 重新排版 REV 1.06 2018-12-25 增加相角计算公式 REV 1.07 2019-02-13 修改字体REV 1.08 2019-02-18 更正输入通道信号输入范围值 REV 1.09 2019-02-20 增加B 通道比较器描述 REV 1.10 2019-05-21 电气特性参数修改REV 1.12 2019-10-03 增加UART 复位条件,删除uart 4800bps 设置选项 REV 1.16 2020-03-02 修改漏电检测电路 REV 1.17 2020-08-28 修订版本REV 1.18 2020-11-20 修改原理图,1K 和33NF 变更为100R 和330NF REV 1.19REV 1.194 / 68目录1 应用领域 .........................................................................................................................................2 2 修订历史 .........................................................................................................................................3 3 特性 ................................................................................................................................................. 74 概述 ................................................................................................................................................. 85 功能框图 ......................................................................................................................................... 8 6引脚配置和功能描述 (9)6.1 HLW8110芯片管脚描述 ............................................................................................................ 9 6.2 HLW8110典型应用 .................................................................................................................. 10 6.3 HLW8112芯片管脚描述 .......................................................................................................... 10 6.4HLW8112典型应用 (12)7电气特性 (12)7.1 推荐工作条件 ......................................................................................................................... 12 7.2 模拟特性 ................................................................................................................................. 13 7.3 数字特性 ................................................................................................................................. 14 7.4 极限额定值 ............................................................................................................................. 15 7.5可靠性 (15)8功能概述 (16)8.1 复位系统 ................................................................................................................................. 16 8.2 时钟系统 ................................................................................................................................. 17 8.3 模数转换 ................................................................................................................................. 17 8.4 通道切换 ................................................................................................................................. 18 8.5 有功功率 ................................................................................................................................. 18 8.6 有效值 ..................................................................................................................................... 19 8.7 视在功率和功率因素 ............................................................................................................. 20 8.8 能量计算 ................................................................................................................................. 20 8.9 过零检测、相角、电压频率测量 ......................................................................................... 21 8.10 峰值检测 ................................................................................................................................. 23 8.11 过流、过压、有功功率过载检测 ......................................................................................... 25 8.12 电压聚降检测 ......................................................................................................................... 27 8.13 均值信号 ................................................................................................................................. 29 8.14 瞬时信号和采样波形 ............................................................................................................. 30 8.15 温度传感器 ............................................................................................................................. 30 8.16比较器 (31)9寄存器说明 (32)REV 1.195 / 689.1.1 系统控制寄存器 ............................................................................................................. 34 9.1.2 计量控制寄存器 ............................................................................................................. 35 9.1.3 计量控制寄存器2 .......................................................................................................... 36 9.1.4 脉冲频率寄存器 ............................................................................................................. 37 9.1.5 无负载有功功率(潜动与启动)阈值寄存器PstartPA 、PstartPB ......................... 38 9.1.6 有功功率和视在功率增益校正寄存器 ......................................................................... 38 9.1.7 相位校正寄存器 .............................................................................. 错误!未定义书签。

CDCLVC1310RHBR;CDCLVC1310-EVM;中文规格书,Datasheet资料

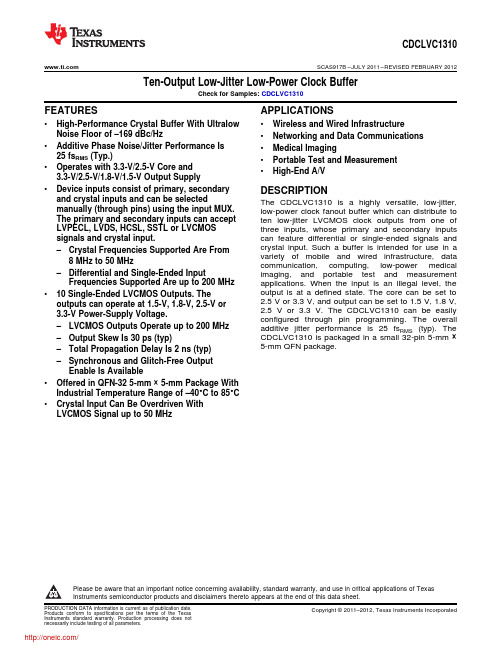

CDCLVC1310 SCAS917B–JULY2011–REVISED FEBRUARY2012 Ten-Output Low-Jitter Low-Power Clock BufferCheck for Samples:CDCLVC1310FEATURES APPLICATIONS•High-Performance Crystal Buffer With Ultralow•Wireless and Wired Infrastructure Noise Floor of–169dBc/Hz•Networking and Data Communications •Additive Phase Noise/Jitter Performance Is•Medical Imaging25fs RMS(Typ.)•Portable Test and Measurement•Operates with3.3-V/2.5-V Core and•High-End A/V3.3-V/2.5-V/1.8-V/1.5-V Output Supply•Device inputs consist of primary,secondary DESCRIPTIONand crystal inputs and can be selected The CDCLVC1310is a highly versatile,low-jitter, manually(through pins)using the input MUX.low-power clock fanout buffer which can distribute to The primary and secondary inputs can accept ten low-jitter LVCMOS clock outputs from one of LVPECL,LVDS,HCSL,SSTL or LVCMOS three inputs,whose primary and secondary inputscan feature differential or single-ended signals and signals and crystal input.crystal input.Such a buffer is intended for use in a –Crystal Frequencies Supported Are Fromvariety of mobile and wired infrastructure,data 8MHz to50MHz communication,computing,low-power medical–Differential and Single-Ended Input imaging,and portable test and measurement Frequencies Supported Are up to200MHz applications.When the input is an illegal level,theoutput is at a defined state.The core can be set to •10Single-Ended LVCMOS Outputs.The2.5V or3.3V,and output can be set to1.5V,1.8V,outputs can operate at1.5-V,1.8-V,2.5-V or2.5V or3.3V.The CDCLVC1310can be easily3.3-V Power-Supply Voltage.configured through pin programming.The overall–LVCMOS Outputs Operate up to200MHz additive jitter performance is25fsRMS (typ).TheCDCLVC1310is packaged in a small32-pin5-mm×–Output Skew Is30ps(typ)5-mm QFN package.–Total Propagation Delay Is2ns(typ)–Synchronous and Glitch-Free OutputEnable Is Available•Offered in QFN-325-mm×5-mm Package WithIndustrial Temperature Range of–40°C to85°C•Crystal Input Can Be Overdriven WithLVCMOS Signal up to50MHzPlease be aware that an important notice concerning availability,standard warranty,and use in critical applications of TexasInstruments semiconductor products and disclaimers thereto appears at the end of this data sheet.PRODUCTION DATA information is current as of publication date.Copyright©2011–2012,Texas Instruments Incorporated Products conform to specifications per the terms of the TexasInstruments standard warranty.Production processing does notnecessarily include testing of all parameters.XTAL LVCMOSOEDifferential/LVCMOSIN_SEL0/IN_SEL1CDCLVC1310SCAS917B –JULY 2011–REVISED FEBRUARY 2012These devices have limited built-in ESD protection.The leads should be shorted together or the device placed in conductive foam during storage or handling to prevent electrostatic damage to the MOS gates.BLOCK DIAGRAMFigure 1.High-Level Block Diagram of CDCLVC13102Submit Documentation FeedbackCopyright ©2011–2012,Texas Instruments IncorporatedProduct Folder Link(s):CDCLVC1310P0048-18CDCLVC1310RHB Package (Top View)Y9Y0G N DG N DVDDO O EY8I N _S E L 0GND I N _S E L 1Y7S E C _I N PVDDO S E C _I N NY6G N DY5G N DVDDOV D DY1X I NGND X O U TY2P R I _I N PVDDOP R I _I N NY3G N DY4G N DCDCLVC1310SCAS917B –JULY 2011–REVISED FEBRUARY 2012PINOUT DIAGRAMCopyright ©2011–2012,Texas Instruments Incorporated Submit Documentation Feedback3Product Folder Link(s):CDCLVC1310CDCLVC1310SCAS917B–JULY2011–REVISED PIN FUNCTIONSPINI/O TYPE DESCRIPTIONNAME NO(s)4,9,15,16,21,GND PWR Analog Power supply ground25,26,32IN_SEL0,30,29I Digital Input clock selection(pulldown of150kΩ)IN_SEL1OE31I Digital LVCMOS output enable(pulldown of150kΩ)Inverting differential primary reference input,internally biased to Vdd/2(pullup/pulldown PRI_INN14I Analogof150kΩ)PRI_INP13I Analog Non-inverting differential/single-ended primary reference input(pulldown of150kΩ)Inverting differential secondary reference input,internally biased to Vdd/2SEC_INN27I Analog(pullup/pulldown of150kΩ)SEC_INP28I Analog Non-inverting differential/single-ended secondary reference input(pulldown of150kΩ) VDD10PWR Analog Power supply pins2,6,19,VDDO PWR Analog I/O power supply pins23XIN11I Analog Crystal Oscillator Input or XTAL Bypass modeXOUT12I Analog Crystal Oscillator OutputY01O Analog LVCMOS output0Y13O Analog LVCMOS output1Y25O Analog LVCMOS output2Y37O Analog LVCMOS output3Y48O Analog LVCMOS output4Y517O Analog LVCMOS output5Y618O Analog LVCMOS output6Y720O Analog LVCMOS output7Y822O Analog LVCMOS output8Y924O Analog LVCMOS output9Table1.Input SelectionIN_SEL1IN_SEL0INPUT CHOSEN00PRI_IN01SEC_IN10XTAL/overdrive(1)11XTAL bypass(2)(1)This mode can be used to overdrive the XTAL oscillator with anLVCMOS input.For characteristics;see LVCMOS OUTPUTCHARACTERISTICS.(2)This mode is only XTAL bypass.For characteristics,see LVCMOSOUTPUT CHARACTERISTICS.Table2.INPUT/OUTPUT OPERATION(1)INPUT STATE OUTPUT STATEPRI_INx,SEC_INx open Logic LOWPRI_INP/SEC_INP=HIGH,Logic HIGHPRI_INN/SEC_INN=LOWPRI_INP/SEC_INP=LOW,Logic LOWPRI_INN/SEC_INN=HIGH(1)Device must have switching edge to obtain output states.4Submit Documentation Feedback Copyright©2011–2012,Texas Instruments IncorporatedProduct Folder Link(s):CDCLVC1310CDCLVC1310 SCAS917B–JULY2011–REVISED FEBRUARY2012Table3.OE FunctionOE Yx0High-impedance1EnabledABSOLUTE MAXIMUM RATINGS(1)over operating free-air temperature range(unless otherwise noted)VALUE UNIT VDD,VDDO Supply voltage range–0.5to4.6VV IN Input voltage range–0.5to VDD+0.5VV OUT Output voltage range–0.5to VDDO+0.5VI IN Input current±20VI OUT Output current±50VT stg Storage temperature range–65to150°CT J Junction temperature125°C(1)Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device.These are stress ratingsonly,and functional operation of the device at these or any other conditions beyond those indicated under Recommended Operating Conditions is not implied.Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability. RECOMMENDED OPERATING CONDITIONSover operating free-air temperature range(unless otherwise noted)MIN NOM MAX UNIT3.135 3.3 3.4652.375 2.5 2.625VDDO Output supply voltage V1.6 1.821.35 1.5 1.653.135 3.3 3.465VDD Core supply voltage V2.375 2.5 2.625I OH High-level output current,LVCMOS–24mAI OL Low-level output current,LVCMOS24mAT A Ambient temperature–4085°CCopyright©2011–2012,Texas Instruments Incorporated Submit Documentation Feedback5Product Folder Link(s):CDCLVC1310CDCLVC1310SCAS917B–JULY2011–REVISED THERMAL INFORMATIONCDCLVC1310THERMAL METRIC(1)RHB UNIT32PINSθJA Junction-to-ambient thermal resistance(2)41.7°C/WθJCtop Junction-to-case(top)thermal resistance(3)34.1°C/WθJB Junction-to-board thermal resistance(4)14.4°C/WψJT Junction-to-top characterization parameter(5)0.9°C/WψJB Junction-to-board characterization parameter(6)14.4°C/WθJCbot Junction-to-case(bottom)thermal resistance(7) 6.2°C/W(1)For more information about traditional and new thermal metrics,see the IC Package Thermal Metrics application report,SPRA953.(2)The junction-to-ambient thermal resistance under natural convection is obtained in a simulation on a JEDEC-standard,high-K board,asspecified in JESD51-7,in an environment described in JESD51-2a.(3)The junction-to-case(top)thermal resistance is obtained by simulating a cold plate test on the package top.No specificJEDEC-standard test exists,but a close description can be found in the ANSI SEMI standard G30-88.(4)The junction-to-board thermal resistance is obtained by simulating in an environment with a ring cold plate fixture to control the PCBtemperature,as described in JESD51-8.(5)The junction-to-top characterization parameter,ψJT,estimates the junction temperature of a device in a real system and is extractedfrom the simulation data for obtainingθJA,using a procedure described in JESD51-2a(sections6and7).(6)The junction-to-board characterization parameter,ψJB,estimates the junction temperature of a device in a real system and is extractedfrom the simulation data for obtainingθJA,using a procedure described in JESD51-2a(sections6and7).(7)The junction-to-case(bottom)thermal resistance is obtained by simulating a cold plate test on the exposed(power)pad.No specificJEDEC standard test exists,but a close description can be found in the ANSI SEMI standard G30-88.INPUT CHARACTERISTICSover recommended ranges of supply voltage(VDDO≤VDD),load and ambient temperature(unless otherwise noted) PARAMETER TEST CONDITIONS MIN TYP MAX UNIT DC Characteristic(OE,IN_SEL0,IN_SEL1,PRI_IN,SEC_IN)I IH Input high current VDD=3.465V,V IH=3.465V40µAI IL Input low current VDD=3.465V,V IL=0V–40µAΔV/ΔT Input edge rate20%–80%2V/nsR Pullup/down Pullup/down resistance150kΩC IN Input capacitance2pF Single-Ended DC Characteristic(PRI_INP,SEC_INP)(1)VDD=3.3V±5%2VDD+0.3V IH Input high voltage VVDD=2.5V±5% 1.6VDD+0.3VDD=3.3V±5%–0.3 1.3V IL Input low voltage VVDD=2.5V±5%–0.30.9Single-Ended DC Characteristic(OE,IN_SEL0,IN_SEL1)V IH Input high voltage0.7×VDD VV IL Input low voltage0.3×VDD V Differential DC Characteristic(PRI_IN,SEC_IN)V I,DIFF Differential input voltage swing(2)0.15 1.3VVDD–V ICM Input common-mode voltage(3)0.5V0.85AC Characteristic(PRI_IN,SEC_IN)f IN Input frequency DC200MHzidc Input duty cycle40%60%(1)PRI/SEC_INN biased to VDD/2(2)V IL should not be less than–0.3V(3)Input common-mode voltage is defined as V IH(see Figure19).6Submit Documentation Feedback Copyright©2011–2012,Texas Instruments IncorporatedProduct Folder Link(s):CDCLVC1310CDCLVC1310 SCAS917B–JULY2011–REVISED FEBRUARY2012CRYSTAL CHARACTERISTICSover recommended ranges of supply voltage,load and ambient temperature(unless otherwise noted)PARAMETER TEST CONDITIONS MIN TYP MAX UNIT Equivalent series resistance(ESR)50ΩMaximum shunt capacitance7pF Drive level100µWCRYSTAL OSCILLATOR CHARACTERISTICSover recommended ranges of supply voltage,load and ambient temperature(unless otherwise noted)PARAMETER TEST CONDITIONS MIN TYP MAX UNIT Mode of oscillation FundamentalFrequency850MHz Frequency in overdrive mode(1)50MHz Frequency in bypass mode(2)50MHzOn-chip load capacitance12pF(1)Input signal swing(max)=2V;input signal t r/t f(max)=10ns;functional,but ac parameters may not be met.(2)Input signal swing(max)=V DD;input signal t r/t f(max)=10ns;functional,but ac parameters may not be met.Copyright©2011–2012,Texas Instruments Incorporated Submit Documentation Feedback7Product Folder Link(s):CDCLVC1310CDCLVC1310SCAS917B–JULY2011–REVISED LVCMOS OUTPUT CHARACTERISTICSover recommended ranges of supply voltage(VDDO≤VDD),load(50Ωto VDDO/2),and ambient temperature(unless otherwise noted)PARAMETER TEST CONDITIONS MIN TYP MAX UNITf OUT200MHzVDDO=3.135V 2.5VDDO=2.375V 1.8V OH Output high voltage VVDDO=1.6V 1.15VDDO=1.35V0.95VDDO=3.135V0.5VDDO=2.375V0.4V OL Output low voltage VVDDO=1.6V0.4VDDO=1.35V0.4VDDO=3.3V15VDDO=2.5V20R OUT Output impedanceΩVDDO=1.8V25VDDO=1.5V30t SLEW-RATE Output rise/fall slew rate20%to80%5V/nst SK Output skew3050pst SK,PP Part-to-part skew(1)2nst DELAY Propagation delay2nsSingle-ended input,VDD=3.3V,25VDDO=3.3VSingle-ended input,VDD=2.5V/3.3V,VDDO=1.5V/1.8V/2.5V,f IN/OUT30=125MHzt RJIT System-level additive jitter(2)f S,RMSDifferential input,VDD=3.3V,30VDDO=3.3VDifferential input,VDD=2.5V/3.3V,VDDO=1.5V/1.8V/2.5V,f IN/OUT=30125MHz10-kHz offset(3)–145100-kHz offset(3)–1561-MHz offset(3)–16310-MHz offset(3)–16420-MHz offset(3)–164NF Noise floor dBc/Hz10-kHz offset(4)–145100-kHz offset(4)–1551-MHz offset(4)–16010-MHz offset(4)–16120-MHz offset(4)–162odc Output duty cycle f IN/OUT=125MHz,idc=50%(5)45%55%t EN Output enable/disable time2CycleMUX ISOLATMUX isolation(6)125MHz55dBION(1)Part-to-part skew is calculated as the difference between the fastest and the slowest t pd across multiple devices.(2)Integration range:12kHz–20MHz;input source see Application Information(3)Single-ended input,f IN/OUT=125MHz,VDD=VDDO=3.3V(4)Differential input,f IN/OUT=125MHz,VDD=VDDO=3.3V(5)Stable V IH,V IL,and V CM(6)See Figure18.8Submit Documentation Feedback Copyright©2011–2012,Texas Instruments IncorporatedProduct Folder Link(s):CDCLVC1310CDCLVC1310 SCAS917B–JULY2011–REVISED FEBRUARY2012PHASE NOISE WITH XTAL(1)SELECTEDVDD=VDDO=2.5V/3.3V,f XTAL=25MHz,T A=25°C(unless otherwise noted)PARAMETER TEST CONDITIONS MIN TYP MAX UNITIB=12kHz to5MHz,VDD=VDDO80=3.3VJrms RMS phase jitter ps rmsIB=12kHz to5MHz,VDD=VDDO115=2.5Vf offset=100Hz,VDD=VDDO=3.3–92Vf offset=1kHz,VDD=VDDO=3.3V–137f offset=10kHz,VDD=VDDO=3.3–163Vf offset=100kHz,VDD=VDDO=3.3–168Vf offset=1MHz,VDD=VDDO=3.3–168Vf offset=5MHz,VDD=VDDO=3.3–169VPN Phase noise(see Figure15)dBc/Hzf offset=100Hz,VDD=VDDO=2.5–91Vf offset=1kHz,VDD=VDDO=2.5V–136f offset=10kHz,VDD=VDDO=2.5–159Vf offset=100kHz,VDD=VDDO=2.5–164Vf offset=1MHz,VDD=VDDO=2.5–165Vf offset=5MHz,VDD=VDDO=2.5–165V(1)Crystal specification:C L=18pF;ESR=35Ω(max);C0=7pF;drive level=100µW(max)DEVICE CURRENT CONSUMPTIONover recommended ranges of supply voltage,load and ambient temperature(unless otherwise noted)PARAMETER TEST CONDITIONS MIN TYP MAX UNIT OVERALL PARAMETERS FOR ALL VERSIONSOE=0V or V DD;Ref.input(PRI/SEC)=0V or V DD;14I O=0mA;V DD/V DDO=3.3VI DD Static device current(1)mAOE=0V or V DD;Ref.input(PRI/SEC)=0V or V DD;8I O=0mA;V DD/V DDO=2.5VI DD,XTAL Device current with XTAL input(1)20mAVDDO=3.465V;f=100MHz8.8VDDO=2.625V;f=100MHz7.7 Power dissipation capacitance perC PD pFoutput(2)VDDO=2V;f=100MHz7.3VDDO=1.65V;f=100MHz 6.9(1)I DD and I DD,XTAL is the current through V DD;outputs on or in the high-impedance state;no load.(2)This is the formula for the power dissipation calculation(see Power Consideration section)I DD,Total=I DD+I DD,Cload+I DD,dyn[mA]I DD,dyn=C PD×V DDO×f×n[mA]I DD,Cload=C load×V DDO×f×n[mA]n=Number of switching output pinsCopyright©2011–2012,Texas Instruments Incorporated Submit Documentation Feedback9Product Folder Link(s):CDCLVC1310R=50from measurement equipmentWCDCLVC1310SCAS917B –JULY 2011–REVISED FEBRUARY 2012TEST CONFIGURATIONSFigure 2through Figure 8illustrate how the device should be set up for a variety of test configurations.Figure 2.LVCMOS Output DC Configuration;Test Load CircuitFigure 3.LVCMOS Input DC Configuration During Device TestFigure 4.LVPECL Input Configuration During Device Test10Submit Documentation FeedbackCopyright ©2011–2012,Texas Instruments IncorporatedProduct Folder Link(s):CDCLVC1310分销商库存信息:TICDCLVC1310RHBR CDCLVC1310-EVM。

IRMCK311TR;中文规格书,Datasheet资料

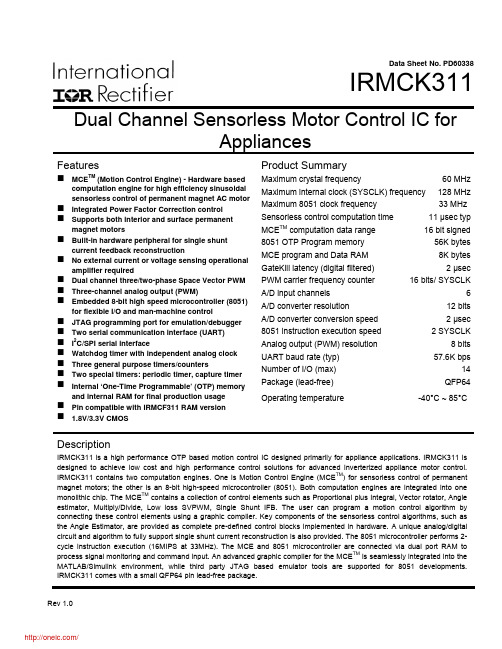

Data Sheet No. PD60338IRMCK311 Dual Channel Sensorless Motor Control IC forAppliancesFeaturesMCE TM (Motion Control Engine) - Hardware based computation engine for high efficiency sinusoidal sensorless control of permanent magnet AC motor Integrated Power Factor Correction controlSupports both interior and surface permanent magnet motorsBuilt-in hardware peripheral for single shunt current feedback reconstructionNo external current or voltage sensing operational amplifier requiredDual channel three/two-phase Space Vector PWM Three-channel analog output (PWM)Embedded 8-bit high speed microcontroller (8051) for flexible I/O and man-machine controlJTAG programming port for emulation/debugger Two serial communication interface (UART)I2C/SPI serial interfaceWatchdog timer with independent analog clockThree general purpose timers/countersTwo special timers: periodic timer, capture timer Internal ‘One-Time Programmable’ (OTP) memory and internal RAM for final production usagePin compatible with IRMCF311 RAM version1.8V/3.3V CMOS Product SummaryMaximum crystal frequency 60 MHz Maximum internal clock (SYSCLK) frequency 128 MHz Maximum 8051 clock frequency 33 MHz Sensorless control computation time 11 μsec typ MCE TM computation data range 16 bit signed 8051 OTP Program memory 56K bytes MCE program and Data RAM 8K bytes GateKill latency (digital filtered) 2 μsec PWM carrier frequency counter 16 bits/ SYSCLK A/D input channels 6 A/D converter resolution 12 bits A/D converter conversion speed 2 μsec 8051 instruction execution speed 2 SYSCLK Analog output (PWM) resolution 8 bits UART baud rate (typ) 57.6K bps Number of I/O (max) 14 Package (lead-free) QFP64 Operating temperature -40°C ~ 85°CDescriptionIRMCK311 is a high performance OTP based motion control IC designed primarily for appliance applications. IRMCK311 is designed to achieve low cost and high performance control solutions for advanced inverterized appliance motor control. IRMCK311 contains two computation engines. One is Motion Control Engine (MCE TM) for sensorless control of permanent magnet motors; the other is an 8-bit high-speed microcontroller (8051). Both computation engines are integrated into one monolithic chip. The MCE TM contains a collection of control elements such as Proportional plus Integral, Vector rotator, Angle estimator, Multiply/Divide, Low loss SVPWM, Single Shunt IFB. The user can program a motion control algorithm by connecting these control elements using a graphic compiler. Key components of the sensorless control algorithms, such as the Angle Estimator, are provided as complete pre-defined control blocks implemented in hardware. A unique analog/digital circuit and algorithm to fully support single shunt current reconstruction is also provided. The 8051 microcontroller performs 2-cycle instruction execution (16MIPS at 33MHz). The MCE and 8051 microcontroller are connected via dual port RAM to process signal monitoring and command input. An advanced graphic compiler for the MCE TM is seamlessly integrated into the MATLAB/Simulink environment, while third party JTAG based emulator tools are supported for 8051 developments. IRMCK311 comes with a small QFP64 pin lead-free package.TABLE OF CONTENTS1 Overview (5)2 IRMCK311 Block Diagram and Main Functions (6)3 Pinout (8)4 Input/Output of IRMCK311 (9)4.1 8051 Peripheral Interface Group (10)4.2 Motion Peripheral Interface Group (10)4.3 Analog Interface Group (11)4.4 Power Interface Group (11)4.5 Test Interface (12)5 Application Connections (13)6 DC Characteristics (14)6.1 Absolute Maximum Ratings (14)6.2 System Clock Frequency and Power Consumption (14)6.3 Digital I/O DC Characteristics (15)6.4 PLL and Oscillator DC Characteristics (15)6.5 Analog I/O DC Characteristics (16)6.6 Under Voltage Lockout DC Characteristics (17)6.7 AREF Characteristics (17)7 AC Characteristics (18)7.1 PLL AC Characteristics (18)7.2 Analog to Digital Converter AC Characteristics (19)7.3 Op Amp AC Characteristics (19)7.4 SYNC to SVPWM and A/D Conversion AC Timing (20)7.5 GATEKILL to SVPWM AC Timing (21)7.6 Interrupt AC Timing (21)7.7 I2C AC Timing (22)7.8 SPI AC Timing (23)7.8.1 SPI Write AC timing (23)7.8.2 SPI Read AC Timing (24)7.9 UART AC Timing (25)7.10 CAPTURE Input AC Timing (26)7.11 JTAG AC Timing (27)7.12 OTP Programming Timing (28)8 I/O Structure (29)9 Pin List (32)Dimensions (35)10 Package11 Part Marking Information (36)Information (36)12 OrderingTABLE OF FIGURESFigure 1. Typical Application Block Diagram Using IRMCK311 (5)Figure 2. IRMCK311 Internal Block Diagram (6)Figure 3. IRMCK311 Pin Configuration (8)Figure 4. Input/Output of IRMCK311 (9)Figure 5. Application Connection of IRMCK311 (13)Figure 6. Clock Frequency vs. Power Consumption (14)Figure 7 Crystal oscillator circuit (18)Figure 8 Voltage droop of sample and hold (19)Figure 9 SYNC to SVPWM and A/D conversion AC Timing (20)Figure 10 GATEKILL to SVPWM AC Timing (21)Figure 11 Interrupt AC Timing (21)Figure 12 I2C AC Timing (22)Figure 13 SPI AC Timing (23)Figure 14 SPI Read AC Timing (24)Figure 15 UART AC Timing (25)Figure 16 CAPTURE Input AC Timing (26)Figure 17 JTAG AC Timing (27)Figure 18 OTP Programming Timing (28)Figure 19 All digital I/O except motor PWM output (29)Figure 20 RESET, GATEKILL I/O (29)Figure 21 Analog input (30)Figure 22 Analog operational amplifier output and AREF I/O structure (30)Figure 23 VPP programming pin I/O structure (30)Figure 24 VSS and AVSS pin structure (31)Figure 25 VDD1 and VDDCAP pin structure (31)Figure 26 XTAL0/XTAL1 pins structure (31)TABLE OF TABLESTable 1. Absolute Maximum Ratings (14)Table 2. System Clock Frequency (14)Table 3. Digital I/O DC Characteristics (15)Table 4. PLL DC Characteristics (15)Table 5. Analog I/O DC Characteristics (16)Table 6. UVcc DC Characteristics (17)Table 7. AREF DC Characteristics (17)Table 8. PLL AC Characteristics (18)Table 9. A/D Converter AC Characteristics (19)Table 10. Current Sensing OP Amp AC Characteristics (19)Table 11. SYNC AC Characteristics (20)Table 12. GATEKILL to SVPWM AC Timing (21)Table 13. Interrupt AC Timing (21)Table 14. I2C AC Timing (22)Table 15. SPI Write AC Timing (23)Table 16. SPI Read AC Timing (24)Table 17. UART AC Timing (25)Table 18. CAPTURE AC Timing (26)Table 19. JTAG AC Timing (27)Table 20. OTP Programming Timing (28)Table 21. Pin List (32)1 OverviewIRMCK311 is a new International Rectifier integrated circuit device primarily designed as a one-chip solution for complete inverter controlled appliance dual motor control applications. Unlike a traditional microcontroller or DSP, the IRMCK311 provides a built-in closed loop sensorless control algorithm using the unique Motion Control Engine (MCE TM) for permanent magnet motors. The MCE TM consists of a collection of control elements, motion peripherals, a dedicated motion control sequencer and dual port RAM to map internal signal nodes. IRMCK311 also employs a unique single shunt current reconstruction circuit to eliminate additional analog/digital circuitry and enables a direct shunt resistor interface to the IC. The sensorless control is the same for both motors with a single shunt current sensing capability. Motion control programming is achieved using a dedicated graphical compiler integrated into the MATLAB/Simulink TM development environment. Sequencing, user interface, host communication, and upper layer control tasks can be implemented in the 8051 high-speed 8-bit microcontroller. The 8051 microcontroller is equipped with a JTAG port to facilitate emulation and debugging tools. Figure 1 shows a typical application schematic using IRMCK311.IRMCK311 is intended for volume production purpose and contains 64K bytes of OTP (One Time Programming) ROM, which can be programmed through a JTAG port. For a development purpose use, IRMCF311 contains a 48k byte of RAM in place of program OTP to facilitate an application development work. Both IRMCF311 and IRMCK311 come in the same 64-pin QFP package with identical pin configuration to facilitate PC board layout and transition to mass productionFigure 1. Typical Application Block Diagram Using IRMCK3112 IRMCK311 Block Diagram and Main FunctionsM o t i o n C o n t r o l B u sFigure 2. IRMCK311 Internal Block DiagramIRMCK311 contains the following functions for sensorless AC motor control applications:• Motion Control Engine (MCE TM )o Proportional plus Integral block o Low pass filtero Differentiator and lag (high pass filter) o Ramp o Limito Angle estimate (sensorless control) o Inverse Clark transformation o Vector rotator o Bit latch o Peak detect o Transitiono Multiply-divide (signed and unsigned)o Divide (signed and unsigned)o Addero Subtractoro Comparatoro Countero Accumulatoro Switcho Shifto ATAN (arc tangent)o Function block (any curve fitting, nonlinear function)o16-bit wide Logic operations (AND, OR, XOR, NOT, NEGATE)o MCE TM program and data memory (6K byte). Note 1o MCE TM control sequencer• 8051 microcontrollero Three 16-bit timer/counterso16-bit periodic timero16-bit analog watchdog timero16-bit capture timero Up to 36 discrete I/Oso Eleven-channel 12-bit A/DFive buffered channels (0 – 1.2V input)One unbuffered channel (0 – 1.2V input)o JTAG port (4 pins)o Up to three channels of analog output (8-bit PWM)o Two UARTo I2C/SPI porto 64K byte Note 1program One-Time Programmable memoryo2K byte data RAM. Note 2Note 1: Total size of OTP memory is 64K byte, however MCE program occupiesmaximum 8K byte which will be loaded into internal RAM at a powerup/bootprocess. Therefore only 56K byte OTP memory area is usable for 8051microcontroller.Note 2: Total size of RAM is 8K byte including MCE program, MCE data, and 8051data. Different sizes can be allocated depending on applications.3 PinoutXTAL0XTAL1P1.1/RXD P1.2/TXDVDD1VSS VDD2P1.3/SYNC/SCKP1.4/CAPP 3.6/R X D 1P 3.7/T X D 1FPWMVL FPWMUL V S SV D D 2A V D DA V S SA I N 0A R E FP 2.7/A O P W M 1P 2.6/A O P W M 0CPWMUH CPWMVH CPWMWH CPWMUL CPWMVL CPWMWL CGATEKILL VDD1VSS I F B C OI F B C +I F B C -P L L V S SP L L V D DR E S E TN CT C KP 5.3/T D IP 5.2/T D OP 5.1/T M SS D A /C S 0S C L /S O -S I /V P PP 5.0/P F C G K I L LP F C P W M V S SFGATEKILL FPWMWL VAC-VAC+VACO IPFCO IPFC+IPFC-I F B F OI F B F +I F B F -P3.0/INT2/CS1C M E X TFPWMVH FPWMUHFPWMWH A I N 1P 3.2/I N T 0Figure 3. IRMCK311 Pin Configuration4 Input/Output of IRMCK311All I/O signals of IRMCK311 are shown in Figure 4. All I/O pins are 3.3V logic interface except A/D interface pins.Figure 4. Input/Output of IRMCK3114.1 8051 Peripheral Interface GroupUART InterfaceP1.1/RXD Input, Receive data to IRMCK311, can be configured as P1.1P1.2/TXD Output, Transmit data from IRMCK311, can be configured as P1.22nd channel Receive data to IRMCK311, can be configured as P3.6 P3.6/RXD1 Input,P3.7/TXD1 Output,2nd channel Transmit data from IRMCK311, can be configured as P3.7Discrete I/O InterfaceP1.3/SYNC/SCK Input/output port 1.3, can be configured as SYNC output or SPI clock P1.4/CAP Input/output port 1.4, can be configured as Capture Timer inputP3.0/INT2/CS1 Input/output port 3.0, can be configured as external interrupt 2 or SPIchip select 1P3.2/INT0 Input/output port 3.2, can be configured as external interrupt 0Analog Output InterfaceP2.6/AOPWM0 Input/output, can be configured as 8-bit PWM output 0 withprogrammable carrier frequencyP2.7/AOPWM1 Input/output, can be configured as 8-bit PWM output 1 withprogrammable carrier frequencyCrystal InterfaceXTAL0 Input, connected to crystalXTAL1 Output, connected to crystalReset InterfaceRESET Inout, system reset, needs to be pulled up to VDD1 but doesn’t requireexternal RC time constantI2C/SPI InterfaceSCL/SO-SI/VPP Output, I2C clock output, SPI SO-SII2C Data line, Chip Select 0 of SPISDA/CS0 Input/output,P3.0/INT2/CS1 Input/output port 3.0, can be configured as external interrupt 2 or SPIchip select 1P1.3/SYNC/SCK Input/output port 1.3, can be configured as SYNC output or SPI clock 4.2 Motion Peripheral Interface GroupPWMCPWMUH Output, motor 1 PWM phase U high side gate signalCPWMUL Output, motor 1 PWM phase U low side gate signalCPWMVH Output, motor 1 PWM phase V high side gate signalCPWMVL Output, motor 1 PWM phase V low side gate signalCPWMWH Output, motor 1 PWM phase W high side gate signalCPWMWL Output, motor 1 PWM phase W low side gate signalFPWMUH Output, motor 2 PWM phase U high side gate signalFPWMUL Output, motor 2 PWM phase U low side gate signal分销商库存信息: IRIRMCK311TR。

MIW1123中文资料