FM1182_parameters_1.1

maxwell 电磁仿真 rmxport 参数定义

题目:Maxwell电磁仿真RMXprt参数定义随着科技的不断进步,电磁仿真技术在工程设计和研发中发挥着越来越重要的作用。

Maxwell电磁仿真软件是一款功能强大的电磁场分析工具,能够帮助工程师们快速准确地进行电磁场仿真分析。

在Maxwell软件中,RMXprt是其中一个重要的参数定义工具,它能够帮助工程师定义和分析电磁仿真中的参数,从而为设计和研发工作提供重要的支持。

本文将对Maxwell电磁仿真RMXprt参数定义进行详细介绍,希望能够帮助读者更好地了解和掌握这一工具。

一、RMXprt参数定义的基本概念1.1 RMXprt的作用RMXprt是Maxwell电磁仿真软件中的一个重要工具,它主要用于定义和分析电磁仿真中的参数。

在电磁场分析中,各种参数的定义和分析是十分重要的,它们直接影响着电磁场的分布和特性。

通过RMXprt工具对参数进行准确的定义和分析,可以有效地帮助工程师们进行电磁场仿真分析,为设计和研发工作提供重要的支持。

1.2 RMXprt参数定义的基本原理RMXprt工具的参数定义是建立在Maxwell电磁场理论基础之上的,它通过对电磁场的特性进行分析和计算,从而确定各种参数的定义。

在进行参数定义时,工程师们可以根据实际需求,对各种参数进行灵活的设置和调整,以满足不同应用场景的需求。

熟练掌握RMXprt工具的参数定义原理,对于工程师们进行电磁场仿真分析具有重要的意义。

二、RMXprt参数定义的具体操作步骤2.1 打开RMXprt工具工程师们需要打开Maxwell电磁仿真软件,并选择RMXprt工具进行参数定义。

在打开RMXprt工具之后,工程师们可以看到一个界面,界面中包含了各种参数定义的选项和设置。

2.2 选择参数定义的类型在打开RMXprt工具之后,工程师们需要根据实际需求选择参数定义的类型。

Maxwell软件提供了多种参数定义的类型,包括线圈定义、磁路定义、绕组定义等。

工程师们可以根据实际需求选择相应的参数定义类型,并进行后续的操作。

KSZ8851-16MLL DEMO BOARD 48-PIN ETHERNET CONTROLLE

SD13

SD7 40

CPU_D14 3

6

SD14

SD8 39

CPU_D15 4

5

SD15

SD9 36

SD10 35

33

SD11 34

CPU_CMD

33

SD12 33

R10

SD13 32

CPU_CSN

33

SD14 31

R12

SD15 30

CPU_WRN

33

CMD

11

R14

CPU_RDN

33

CSN

12

R16

5 6 7 8

TANT

C27

R28 10uF

470pF 2.49K

Power 3.3V 0.1uF (red LED)

CSN CMD

4.7K R27 4.7K R29

GBLC03C_0 D3

GND 2 GND

VR 5 3.3VA

INTRN 4.7K R30

VOUT = 1.24 X [ 1 + ( 2.49k/ 1.5K ) ]

5

4

3

KSZ8851-16MLL (48-pin) Demo Board Black Diagram

D

Headers 20x2

RJ45

LAN1 T

KSZ8851-16MLL

Reset

Power

+1.8V

+2.5V

+3.3V

STATUS LEDs

OSC

EEPROM

C

MIC5209YM

25 MHz

AT93C46

x2

2

1

DATE:

JMT1808R 微控制器用户手册说明书

JMT1808R MCU用户手册江苏宏云技术有限公司*************Dec. 2016 V1.12微控制器JMT1808R 1产品概述 (20)1.1功能描述 (20)1.2主要特性 (20)1.3框图 (22)1.4应用范围 (22)1.5引脚配置 (23)1.5.1 LQFP48L引脚图 (23)1.5.2 LQFP32L引脚图 (24)1.5.3 QFN32L引脚图 (25)1.5.4 TSSOP28L引脚图 (26)1.5.5 引脚说明 (27)2电源管理(PMU) (30)2.1概述 (30)2.2低功耗控制 (30)2.2.1 降低系统时钟频率 (31)2.2.2 外设时钟门控 (32)2.2.3 关闭模拟模块 (32)2.2.4 四种低功耗模式 (32)2.2.5 OSC开关说明 (34)2.3寄存器 (34)2.3.1 低功耗控制寄存器(PMUCTR) [0xA1] (35)3时钟复位管理(CRM) (36)3.1时钟管理 (36)3.1.1 概述 (36)3.1.2 框图 (36)3.1.3 功能描述 (37)3.1.4 寄存器描述 (42)3.2复位管理 (52)3.2.1 概述 (52)3.2.2 框图 (53)3.2.3 功能描述 (53)3.2.4 寄存器 (56)1微控制器JMT1808R4JMT51 MCU核 (61)4.1概述 (61)4.2指令集 (61)5JMT018 DSP核 (67)5.1概述 (67)5.1.1 框图 (67)5.1.2 系统总线 (67)5.1.3 运算单元(ALU) (68)5.1.4 乘累加单元(MAC) (68)5.1.5 除法单元(DIV) (68)5.1.6 硬件循环(HW loop) (69)5.1.7 数据传输 (69)5.1.8 存储单元 (69)5.2指令集 (69)5.2.1 数据传输指令 (69)5.2.2 算术运算指令 (71)5.2.3 移位运算指令 (72)5.2.4 逻辑运算指令 (73)5.2.5 乘法运算指令 (73)5.2.6 并行运算指令 (74)5.2.7 程序控制指令 (77)5.3数据运算器 (78)5.3.1 通用寄存器 (78)5.3.2 累加器A (79)5.3.3 乘法 (83)5.3.4 乘加运算 (84)5.3.5 加减运算 (86)5.3.6 移位运算 (86)5.3.7 四舍五入方法 (87)5.4DSP存储空间 (87)5.4.1 数据存储空间 (87)5.4.2 程序存储空间 (88)5.5DSP工作配置 (89)2微控制器JMT1808R 5.6DSP代码生成与下载 (89)5.6.1 DSP代码生成 (89)5.6.2 DSP代码下载 (89)5.7DSP内部寄存器 (90)5.7.1 DSP通用寄存器R0 (90)5.7.2 DSP通用寄存器R1 (91)5.7.3 DSP通用寄存器R2 (91)5.7.4 DSP通用寄存器R3 (91)5.7.5 DSP通用寄存器R4 (91)5.7.6 DSP通用寄存器R5 (91)5.7.7 DSP通用寄存器R6 (91)5.7.8 DSP通用寄存器R7 (91)5.7.9 X数据空间指针寄存器DP0 (92)5.7.10 Y数据空间指针寄存器DP1 (92)5.7.11 DSP程序地址指针寄存器PC (92)5.7.12 乘法及乘加结果寄存器A (92)5.7.13 LINK寄存器 (92)5.7.14 状态寄存器PSR (92)5.7.15 模式寄存器PMR (93)5.7.16 硬件循环次数寄存器LOOP (93)5.7.17 硬件循环指令个数寄存器LIR (94)5.8JMT51访问DSP寄存器 (94)5.8.1 DSP配置寄存器(DSP_CFG) [0xD4] (95)5.8.2 DSP运行状态寄存器(DSP_STA) [0xD1] (95)5.8.3 PC寄存器低字节(DSP_PCL) [0xD2] (96)5.8.4 PC寄存器高字节(DSP_PCH) [0xD3] (96)5.8.5 R0寄存器低字节(DSP_R0L) [0xD9] (96)5.8.6 R0寄存器高字节(DSP_R0H) [0xDA] (96)5.8.7 R1寄存器低字节(DSP_R1L) [0xDB] (96)5.8.8 R1寄存器高字节(DSP_R1H) [0xDC] (97)5.8.9 R2寄存器低字节(DSP_R2L) [0xDD] (97)5.8.10 R2寄存器高字节(DSP_R2H) [0xDE] (97)5.8.11 R3寄存器低字节(DSP_R3L) [0xDF] (97)5.8.12 R3寄存器高字节(DSP_R3H) [0xE1] (97)5.8.13 R4寄存器低字节(DSP_R4L) [0xE2] (97)3微控制器JMT1808R45.8.14 R4寄存器高字节(DSP_R4H) [0xE3] (97)5.8.15 R5寄存器低字节(DSP_R5L) [0xE4] (98)5.8.16 R5寄存器高字节(DSP_R5H) [0xE5] (98)5.8.17 R6寄存器低字节(DSP_R6L) [0xE6] (98)5.8.18 R6寄存器高字节(DSP_R6H) [0xE7] (98)5.8.19 R7寄存器低字节(DSP_R7L) [0xE9] (98)5.8.20 R7寄存器高字节(DSP_R7H) [0xEA] (98)5.8.21 DP0寄存器低字节(DSP_DP0L) [0xEB] (98)5.8.22 DP0寄存器高字节(DSP_DP0H) [0xEC] (99)5.8.23 DP1寄存器低字节(DSP_DP1L) [0xED] (99)5.8.24 DP1寄存器高字节(DSP_DP1H) [0xEE] (99)5.8.25 A寄存器7~0比特(DSP_A0L) [0xEF] (99)5.8.26 A寄存器15~8比特(DSP_A0H) [0xF1] (99)5.8.27 A寄存器23~16比特(DSP_A1L) [0xF2] (99)5.8.28 A寄存器31~24比特(DSP_A1H) [0xF3] (99)5.8.29 A寄存器39~32比特(DSP_A2) [0xF4] (100)5.8.30 LNKR寄存器低字节(DSP_LNKRL) [0xF5] (100)5.8.31 LNKR寄存器高字节(DSP_LNKRH) [0xF6] (100)5.8.32 PSR寄存器低字节(DSP_PSRL) [0xF7] (100)5.8.33 PSR寄存器高字节(DSP_PSRH) [0xF9] (101)5.8.34 PMR寄存器低字节(DSP_PMRL) [0xFA] (101)5.8.35 PMR寄存器高字节(DSP_PMRH) [0xFB] (101)5.8.36 LOOP寄存器低字节(DSP_LOOPL) [0xFC] (101)5.8.37 LOOP寄存器高字节(DSP_LOOPH) [0xFD] (101)5.8.38 LIR寄存器低字节(DSP_LIRL) [0xFE] (102)5.8.39 LIR寄存器高字节(DSP_LIRH) [0xFF] (102)6中断 (103)6.1概述 (103)6.2外部中断(INT0/INT1) (105)6.3中断优先级 (105)6.4中断处理过程 (106)6.5中断响应时间 (106)6.6中断寄存器 (107)微控制器JMT1808R6.6.1 中断使能寄存器0(IEN0) [0xA8] (107)6.6.2 中断使能寄存器1(IEN1) [0xB8] (108)6.6.3 中断使能寄存器2 (IEN2) [0xC0] (109)6.6.4 中断优先级寄存器0 (IP0) [0xB9] (109)6.6.5 中断优先级寄存器1(IP1) [0xBA] (110)6.6.6 中断优先级寄存器2(IP2) [0xBB] (111)7存储器 (112)7.1JMT51存储器 (112)7.1.1 程序存储器 (112)7.1.2 外部数据存储器 (113)7.1.3 内部数据存储器 (113)7.1.4 特殊功能寄存器 (115)7.2JMT018存储器 (120)7.3存储器访问冲突说明 (121)7.4JMT51核寄存器 (122)7.4.1 ACC寄存器(A) [0xE0] (122)7.4.2 B寄存器(B) [0xF0] (122)7.4.3 堆栈指针(SP) [0x81] (122)7.4.4 程序状态字寄存器(PSW) [0xD0] (123)7.4.5 数据指针低字节(DPL) [0x82] (124)7.4.6 数据指针高字节(DPH) [0x83] (124)7.4.7 MOVX指令设置寄存器(MOVXCON) [0x86] (124)7.5P AGE堆栈寄存器 (125)7.5.1 SFR PAGE寄存器(SFRPAGE) [0x84] (125)7.5.2 PAGE堆栈使能寄存器(SFRPGEN) [0x85] (126)7.5.3 PAGE堆栈寄存器0(PGSTACK0) [0x91] (126)7.5.4 PAGE堆栈寄存器1(PGSTACK1) [0x92] (126)7.5.5 PAGE堆栈寄存器2(PGSTACK2) [0x93] (126)7.5.6 PAGE堆栈寄存器3(PGSTACK3) [0x94] (127)8Flash存储器 (128)8.1概述 (128)8.2FLASH操作 (128)8.2.1 FLASH数据读取 (128)5微控制器JMT1808R68.2.2 FLASH扇区擦除 (129)8.2.3 FLASH编程 (129)8.3FLASH寄存器 (130)8.3.1 FLASH控制寄存器(FLSC) [0xF9] (130)8.3.2 FLASH关键字寄存器(FLSK) [0xFA] (130)9看门狗定时器(WDT) (131)9.1概述 (131)9.2功能描述 (131)9.3寄存器 (131)9.3.1 看门狗分频系数寄存器(WDTCKDIV) [0xD9] (131)9.3.2 看门狗比较值寄存器(WDTINT) [0xDA] (132)9.3.3 看门狗中断标志寄存器(WDTINTF) [0xDB] (132)9.3.4 看门狗喂狗寄存器(WDTLD) [0xDC] (133)9.3.5 看门狗启停寄存器(WDTST) [0xDD] (133)10实时时钟(RTC) (134)10.1概述 (134)10.2实时时钟 (134)10.3闹钟 (136)10.4RTC时钟调校 (136)10.5实时时钟寄存器更新 (137)10.6实时时钟寄存器读取 (137)10.7RTC中断 (137)10.8RTC寄存器 (138)10.8.1 RTC控制寄存器0(RTCCON0) [0xA9] (138)10.8.2 RTC控制寄存器1(RTCCON1) [0xAA] (139)10.8.3 RTC时标控制寄存器(RTCTMC) [0xAB] (140)10.8.4 RTC秒寄存器(RTCSEC) [0xAC] (140)10.8.5 RTC分钟寄存器(RTCMIN) [0xAD] (141)10.8.6 RTC小时寄存器(RTCHOUR) [0xAE] (141)10.8.7 RTC星期寄存器(RTCWEEK) [0xAF] (141)10.8.8 RTC日寄存器(RTCDAY) [0xB1] (141)10.8.9 RTC月寄存器(RTCMON) [0xB2] (141)微控制器JMT1808R10.8.10 RTC年寄存器(RTCYEAR) [0xB3] (142)10.8.11 闹钟0秒寄存器(AL0SEC) [0xB4] (142)10.8.12 闹钟0分钟寄存器(AL0MIN) [0xB5] (142)10.8.13 闹钟0小时寄存器(AL0HOUR) [0xB6] (142)10.8.14 闹钟0星期寄存器(AL0WEEKS) [0xB7] (142)10.8.15 闹钟1分钟寄存器(AL1MIN) [0xB9] (143)10.8.16 闹钟1小时寄存器(AL1HOUR) [0xBA] (143)10.8.17 闹钟1日寄存器(AL1DAY) [0xBB] (143)10.8.18 闹钟1月寄存器(AL1MON) [0xBC] (144)10.8.19 RTC时钟调校寄存器0(RTCADJ0) [0xBD] (144)10.8.20 RTC时钟调校寄存器1(RTCADJ1) [0xBE] (144)10.8.21 RTC中断使能寄存器(RTCIE) [0xBF] (144)10.8.22 RTC中断标志寄存器(RTCIF) [0xC7] (145)11定时器/计数器(TIMER) (146)11.1概述 (146)11.2TIMER管脚配置 (146)11.3Timer0工作模式 (146)11.3.1 模式0(13位定时器/计数器) (146)11.3.2 模式1(16位定时器/计数器) (147)11.3.3 模式2(8位自动重装定时器/计数器) (147)11.3.4 模式3(两个8比特定时器) (148)11.4Timer1工作模式 (149)11.4.1 模式0(13位定时器/计数器) (149)11.4.2 模式1(16位定时器/计数器) (149)11.4.3 模式2(8位自动重装定时器/计数器) (150)11.5Timer2工作模式 (150)11.5.1 模式0(13位定时器/计数器) (150)11.5.2 模式1(16位定时器/计数器) (151)11.5.3 模式2(16位自动重装定时器/计数器) (151)11.5.4 模式3(1个8比特定时器/计数器) (152)11.6TIMER寄存器 (152)11.6.1 Timer0/1控制寄存器(TCON) [0x88] (153)11.6.2 Timer0/1模式寄存器(TMOD) [0x89] (154)7微控制器JMT1808R811.6.3 Timer0低8位(TL0) [0x8A] (155)11.6.4 Timer1低8位(TL1) [0x8B] (155)11.6.5 Timer0高8位(TH0) [0x8C] (155)11.6.6 Timer1高8位(TH1) [0x8D] (155)11.6.7 Timer0/1预分频控制器(TPSC) [0x8E] (155)11.6.8 Timer2控制寄存器(T2CON) [0xD1] (156)11.6.9 Timer2重载寄存器低8位(RL2) [0xD2] (156)11.6.10 Timer2重载寄存器高8位(RH2) [0xD3] (156)11.6.11 Timer2低8位(TL2) [0xD4] (157)11.6.12 Timer2高8位(TH2) [0xD5] (157)11.6.13 Timer2预分频控制器(T2PSC) [0xD6] (157)12高级定时器(PWM) (158)12.1概述 (158)12.2特性 (158)12.3框图 (160)12.4输入输出引脚配置 (160)12.5功能描述 (160)12.5.1 计数器 (161)12.5.2 输入捕获功能 (173)12.5.3 从模式控制 (175)12.5.4 输出比较功能 (181)12.5.5 主模式控制 (207)12.5.6 中断 (209)12.5.7 高级定时器同步 (211)12.6寄存器描述 (216)12.6.1 TIMx控制寄存器0 (TIMx_CONR0) [TIM0:0xBB/TIM1:0xFB] (221)12.6.2 TIMx控制寄存器1 (TIMx_CONR1) [TIM0:0x89/TIM1:0xC9] (223)12.6.3 TIMx控制寄存器2 (TIMx_CONR2) [TIM0:0x8A/TIM1:0xCA] (224)12.6.4 TIMx控制寄存器3 (TIMx_CONR3) [TIM0:0x8B/TIM1:0xCB] (225)12.6.5 TIMx从模式控制寄存器0 (TIMx_TGICR0) [TIM0:0x8C/TIM1:0xCC] (226)12.6.6 TIMx从模式控制寄存器1 (TIMx_TGICR1) [TIM0:0x8D/TIM1:0xCD] (228)12.6.7 TIMx中断使能寄存器0 (TIMx_IER) [TIM0:0x8E/TIM1:0xCE] (230)12.6.8 TIMx中断使能寄存器1(TIMx_IER_NOCMP)[TIM0:0xB7/TIM7:0xF7] 23112.6.9 TIMx通道CC0输入捕获/输出比较模式控制寄存器(TIMx_CC0MR)[TIM0:0x8F/TIM1:0xCF] (231)12.6.10 TIMx通道CC1输入捕获/输出比较模式控制寄存器(TIMx_CC1MR)[TIM0:0x91/TIM1:0xD1] (236)12.6.11 TIMx通道CC2输入捕获/输出比较模式控制寄存器(TIMx_CC2MR)[TIM0:0x92/TIM1:0xD2] (241)12.6.12 TIMx通道CC3输入捕获/输出比较模式控制寄存器(TIMx_CC3MR)[TIM0:0x93/TIM1:0xD3] (245)12.6.13 TIMx通道使能控制寄存器(TIMx_CCENR) [TIM0:0x94/TIM1:0xD4] (249)12.6.14 TIMx通道极性控制寄存器(TIMx_CCPS) [TIM0:0x95/TIM1:0xD5] (251)12.6.15 TIMx死区时间寄存器(TIMx_DTG) [TIM0:0x96/TIM1:0xD6] (252)12.6.16 TIMx周期值自动装载寄存器的低8位(TIMx_ARRL) [TIM0:0x97/TIM1:0xD7]25212.6.17 TIMx周期值自动装载寄存器的高8位(TIMx_ARRH) [TIM0:0x99/TIM1: 0xD9]25312.6.18 TIMx预分频寄存器的低8位(TIMx_PSCL) [TIM0:0x9A/TIM1: 0xDA] (253)12.6.19 TIMx预分频寄存器的高8位(TIMx_PSCH) [TIM0:0x9B/TIM1:0xDB] (253)12.6.20 TIMx重复计数寄存器(TIMx_RCR) [TIM0:0x9C/TIM1:0xDC] (254)12.6.21 TIMx通道CC0捕获/向上计数比较寄存器的低8位(TIMx_CC0RUL)[TIM0:0x9D/ TIM1:0xDD] (254)12.6.22 TIMx通道CC0捕获/向上计数比较寄存器的高8位(TIMx_CC0RUH)[TIM0:0x9E/TIM1:0xDE] (255)12.6.23 TIMx通道CC0向下计数比较寄存器的低8位(TIMx_CC0RDL) [TIM0:0x9F/ TIM1:0xDF] (256)12.6.24 TIMx通道CC0向下计数比较寄存器的高8位(TIMx_CC0RDH) [TIM0:0xA1/ TIM1:0xE1] (257)12.6.25 TIMx通道CC1捕获/向上计数比较寄存器的低8位(TIMx_CC1RUL)[TIM0:0xA2/TIM1:0xE2] (258)12.6.26 TIMx通道CC1捕获/向上计数比较寄存器的高8位(TIMx_CC1RUH)[TIM0:0xA3/TIM1:0xE3] (259)12.6.27 TIMx通道CC1向下计数比较寄存器的低8位(TIMx_CC1RDL)[TIM0:0xA4/TIM1:0xE4] (260)12.6.28 TIMx通道CC1向下计数比较寄存器的高8位(TIMx_CC1RDH)[TIM0:0xA5/TIM1:0xE5] (260)12.6.29 TIMx通道CC2捕获/向上计数比较寄存器的低8位(TIMx_CC2RUL)[TIM0:0xA6/TIM1:0xE6] (261)12.6.30 TIMx通道CC2捕获/向上计数比较寄存器的高8位(TIMx_CC2RUH)[TIM0:0xA7/TIM1:0xE7] (262)12.6.31 TIMx通道CC2向下计数比较寄存器的低8位(TIMx_CC2RDL)[TIM0:0xA9/TIM0:0xE9] (263)12.6.32 TIMx通道CC2向下计数比较寄存器的高8位(TIMx_CC2RDH)[TIM0:0xAA/TIM1:0xEA] (264)12.6.33 TIMx通道CC3捕获/向上计数比较寄存器的低8位(TIMx_CC3RUL)[TIM0:0xAB/TIM1:0xEB] (265)12.6.34 TIMx通道CC3捕获/向上计数比较寄存器的高8位(TIMx_CC3RUH)[TIM0:0xAC/TIM1:0xEC] (266)12.6.35 TIMx通道CC3向下计数比较寄存器的低8位(TIMx_CC3RDL)[TIM0:0xAD/TIM1:0xED] (267)12.6.36 TIMx通道CC3向下计数比较寄存器的高8位(TIMx_CC3RDH)[TIM0:0xAE/TIM1:0xEE] (268)12.6.37 TIMx刹车控制寄存器(TIMx_BRKC) [TIM0:0xAF/TIM1:0xEF] (269)12.6.38 TIMx事件产生寄存器(TIMx_EGR) [TIM0:0xB1/TIM1:0xF1] (271)12.6.39 TIMx互补模式控制寄存器(TIMx_CMPLMTARY) [TIM0:0xB2/TIM1:0xF2]27312.6.40 TIMx中断标志寄存器0 (TIMx_ISR0) [TIM0:0xB3/TIM1:0xF3] (273)12.6.41 TIMx中断标志寄存器1 (TIMx_ISR1) [TIM0:0xB4/TIM1:0xF4] (274)12.6.42 TIMx中断标志寄存器2 (TIMx_ISR2) [TIM0:0xB9/TIM1:0xF9] (275)12.6.43 TIMx计数器的低8位(TIMx_CNTL) [TIM0:0xB5/TIM1:0xF5] (276)12.6.44 TIMx计数器的高8位(TIMx_CNTH) [TIM0:0xB6/TIM1:0xF6] (276)13CORDIC协处理器 (277)13.1概述 (277)13.2功能描述 (278)13.2.1 输入数据格式 (278)13.2.2 结果数据归一化 (278)13.2.3 CORDIC调度 (279)13.2.4 CORDIC中断 (280)13.2.5 CORDIC精度 (280)13.3CORDIC 寄存器 (281)13.3.1 JMT51 MCU调度寄存器 (281)13.3.2 JMT018 DSP指令调度寄存器 (284)14通用异步收发传输器(UART) (287)14.1概述 (287)14.2框图 (287)14.3UART管脚配置 (288)14.4UART工作模式 (288)14.4.1 标准UART工作模式0:同步移位寄存器 (288)14.4.2 标准UART工作模式1:8位UART,波特率可变 (289)14.4.3 标准UART工作模式2:9位UART,波特率固定 (290)14.4.4 标准UART工作模式3:9位UART,波特率可变 (290)14.4.5 38KHz红外调制发送 (291)14.4.6 IrDA(SIR)红外通信 (292)14.5UART多机通信 (292)14.6UART奇偶校验 (293)14.7UART波特率计算 (293)14.8UART寄存器 (302)14.8.1 UART0控制寄存器(S0CON) [0x98] (302)14.8.2 UART0数据缓冲寄存器(S0BUF) [0x99] (303)14.8.3 UART0波特率重载寄存器低8位(S0RELL) [0x9A] (303)14.8.4 UART0波特率重载寄存器高2位(S0RELH) [0x9B] (304)14.8.5 UART0红外控制寄存器(S0IRCON) [0x9C] (304)14.8.6 UART1控制寄存器(S1CON) [0xF1] (305)14.8.7 UART1数据缓冲寄存器(S1BUF) [0xF2] (305)14.8.8 UART1波特率重载寄存器低8位(S1RELL) [0xF3] (306)14.8.9 UART1波特率重载寄存器高2位(S1RELH) [0xF4] (306)14.8.10 UART1红外控制寄存器(S1IRCON) [0xF5] (306)15I2C接口 (308)15.1概述 (308)15.2框图 (308)15.3I2C管脚配置 (308)15.4I2C模块连接 (308)15.5I2C数据格式 (309)15.5.2 读写控制比特 (309)15.5.3 反馈(ACK) (310)15.5.4 起始条件和结束条件 (310)15.5.5 数据格式 (310)15.5.6 时钟同步 (311)15.5.7 仲裁 (311)15.6I2C时钟产生 (312)15.7I2C工作模式 (313)15.7.1 从机模式 (313)15.7.2 主机模式 (315)15.8I2C中断 (318)15.9I2C寄存器 (319)15.9.1 I2C控制寄存器(I2CCON) [0xE1] (319)15.9.2 I2C从机地址寄存器低8位(I2CSADDRL) [0xE2] (320)15.9.3 I2C从机地址寄存器高2位(I2CSADDRH) [0xE3] (320)15.9.4 I2C本机地址寄存器低8位(I2COADDRL) [0xE4] (321)15.9.5 I2C本机地址寄存器高2位(I2COADDRH) [0xE5] (321)15.9.6 I2C工作时钟分频控制寄存器(I2CDIV) [0xE6] (321)15.9.7 I2C时钟SCL低电平时间配置寄存器(I2CDUTYL) [0xE7] (322)15.9.8 I2C时钟SCL高电平时间配置寄存器(I2CDUTYH) [0xE9] (322)15.9.9 I2C数据SDA保持时间配置寄存器(I2CHOLD) [0xEA] (322)15.9.10 I2C数据写缓冲寄存器(I2CWBUF) [0xEB] (323)15.9.11 I2C数据读缓冲寄存器(I2CRBUF) [0xEC] (323)15.9.12 I2C状态寄存器(I2CSTS) [0xED] (323)15.9.13 I2C中断标志寄存器(I2CISC) [0xEE] (324)15.9.14 I2C中断使能寄存器(I2CIEN) [0xEF] (325)16串行外设接口(SPI) (326)16.1概述 (326)16.2框图 (326)16.3SPI管脚配置 (326)16.4SPI主/从机互连 (327)16.4.1 4线互连模式 (327)16.5SPI时序设置 (328)16.6数据发送和接收过程 (329)16.6.1 主机模式 (329)16.6.2 从机模式 (331)16.7SPI中断 (332)16.8SPI寄存器 (333)16.8.1 SPI控制寄存器(SPICON) [0xC9] (333)16.8.2 SPI中断使能寄存器(SPIIE) [0xCA] (334)16.8.3 SPI中断标志寄存器(SPIIF) [0xCB] (335)16.8.4 SPI波特率控制寄存器(SPIBR) [0xCC] (335)16.8.5 SPI数据缓冲寄存器(SPIBUF) [0xCD] (336)17模拟/数字转换(ADC)和可编程增益放大器(PGA) (337)17.1概述 (337)17.2ADC转换结果访问方式 (338)17.3ADC输入端口配置 (338)17.4可编程增益放大器(PGA)说明 (339)17.5ADC参考电压配置 (341)17.6ADC转换功能 (341)17.7ADC转换结果数据格式 (342)17.8ADC转换时序 (342)17.9模拟看门狗 (343)17.10外部触发事件 (344)17.11特殊通道序列管理 (346)17.12ADC工作模式 (347)17.12.1 单次转换+非扫描模式 (347)17.12.2 单次转换+扫描模式 (348)17.12.3 连续转换+非扫描模式 (350)17.12.4 连续转换+扫描模式 (351)17.13双ADC协同工作模式 (353)17.13.1 独立模式 (353)17.13.2 普通同步模式 (353)17.13.4 普通交叉模式 (355)17.13.5 特殊交替触发模式 (355)17.13.6 普通同步+特殊同步模式 (356)17.13.7 普通同步+特殊交替触发模式 (357)17.13.8 普通交叉+特殊同步模式 (358)17.14中断处理 (359)17.15ADC寄存器 (360)17.15.1 JMT51访问ADC寄存器 (360)17.15.2 JMT018访问ADC寄存器 (391)18模拟比较器(CMP) (393)18.1模拟比较器概述 (393)18.2低压检测 (394)18.2.1 低压检测保护程序示例 (395)18.3模拟比较器寄存器 (396)18.3.1 模拟比较器使能寄存器(CMPEN) [0x91] (396)18.3.2 模拟比较器中断寄存器(CMPINT) [0x92] (397)18.3.3 模拟比较器比较结果寄存器(CMPFLAG) [0x93] (397)18.3.4 模拟比较器滤波选择寄存器(CMPFT) [0x94] (398)18.3.5 模拟比较器VDD分压寄存器(CMPVDD) [0x95] (398)18.3.6 模拟比较器参考电压选择寄存器(CMPREF) [0x96] (398)19通用输入/输出(GPIO) (400)19.1管脚设置 (400)19.2管脚功能复用 (403)19.3PWM管脚特殊复用 (407)19.3.1 PWM输出复用 (407)19.3.2 PWM刹车复用 (407)19.4管脚数据寄存器读写 (408)19.5外设管脚复用配置 (408)19.6管脚滤波 (415)19.7INT0中断 (415)19.8INT1中断 (418)19.9P A0唤醒 (421)19.10GPIO寄存器 (421)19.10.1 PA0数字I/O控制寄存器(PA0CTRL) [0x99] (424)19.10.2 PA1数字I/O控制寄存器(PA1CTRL) [0x9A] (425)19.10.3 PA2数字I/O控制寄存器(PA2CTRL) [0x9B] (426)19.10.4 PA3数字I/O控制寄存器(PA3CTRL) [0x9C] (427)19.10.5 PA4数字I/O控制寄存器(PA4CTRL) [0x9D] (428)19.10.6 PA5数字I/O控制寄存器(PA5CTRL) [0x9E] (428)19.10.7 PA6数字I/O控制寄存器(PA6CTRL) [0x9F] (429)19.10.8 PA7数字I/O控制寄存器(PA7CTRL) [0xC3] (430)19.10.9 PB0数字I/O控制寄存器(PB0CTRL) [0xA1] (431)19.10.10 PB1数字I/O控制寄存器(PB1CTRL) [0xA2] (432)19.10.11 PB2数字I/O控制寄存器(PB2CTRL) [0xA3] (432)19.10.12 PB3数字I/O控制寄存器(PB3CTRL) [0xA4] (433)19.10.13 PB4数字I/O控制寄存器(PB4CTRL) [0xA5] (434)19.10.14 PB5数字I/O控制寄存器(PB5CTRL) [0xA6] (435)19.10.15 PB6数字I/O控制寄存器(PB6CTRL) [0xA7] (436)19.10.16 PB7数字I/O控制寄存器(PB7CTRL) [0xC4] (436)19.10.17 PC0数字I/O控制寄存器(PC0CTRL) [0xA9] (437)19.10.18 PC1数字I/O控制寄存器(PC1CTRL) [0xAA] (438)19.10.19 PC2数字I/O控制寄存器(PC2CTRL) [0xAB] (439)19.10.20 PC3数字I/O控制寄存器(PC3CTRL) [0xAC] (440)19.10.21 PC4数字I/O控制寄存器(PC4CTRL) [0xAD] (440)19.10.22 PC5数字I/O控制寄存器(PC5CTRL) [0xAE] (441)19.10.23 PC6数字I/O控制寄存器(PC6CTRL) [0xAF] (442)19.10.24 PC7数字I/O控制寄存器(PC7CTRL) [0xC5] (443)19.10.25 PD0数字I/O控制寄存器(PD0CTRL) [0xB1] (444)19.10.26 PD1数字I/O控制寄存器(PD1CTRL) [0xB2] (444)19.10.27 PD2数字I/O控制寄存器(PD2CTRL) [0xB3] (445)19.10.28 PD3数字I/O控制寄存器(PD3CTRL) [0xB4] (446)19.10.29 PD4数字I/O控制寄存器(PD4CTRL) [0xB5] (447)19.10.30 PD5数字I/O控制寄存器(PD5CTRL) [0xB6] (448)19.10.31 PD6数字I/O控制寄存器(PD6CTRL) [0xB7] (448)19.10.32 PD7数字I/O控制寄存器(PD7CTRL) [0xC6] (449)19.10.33 PE0数字I/O控制寄存器(PE0CTRL) [0xB9] (450)19.10.34 PE1数字I/O控制寄存器(PE1CTRL) [0xBA] (451)19.10.35 PE2数字I/O控制寄存器(PE2CTRL) [0xBB] (452)19.10.36 PE3数字I/O控制寄存器(PE3CTRL) [0xBC] (452)19.10.37 PE4数字I/O控制寄存器(PE4CTRL) [0xBD] (453)19.10.38 PE5数字I/O控制寄存器(PE5CTRL) [0xBE] (454)19.10.39 PE6数字I/O控制寄存器(PE6CTRL) [0xBF] (455)19.10.40 PE7数字I/O控制寄存器(PE7CTRL) [0xC7] (456)19.10.41 PG0数字I/O控制寄存器(PG0CTRL) [0xC1] (456)19.10.42 PG1数字I/O控制寄存器(PG1CTRL) [0xC2] (457)19.10.43 PA转换速率寄存器(PASR) [0xC9] (458)19.10.44 PB转换速率寄存器(PBSR) [0xCA] (459)19.10.45 PC转换速率寄存器(PCSR) [0xCB] (460)19.10.46 PD转换速率寄存器(PDSR) [0xCC] (461)19.10.47 PE转换速率寄存器(PESR) [0xCD] (461)19.10.48 PG转换速率寄存器(PGSR) [0xCE] (462)19.10.49 PA驱动能力寄存器(PADR) [0xD1] (463)19.10.50 PB驱动能力寄存器(PBDR) [0xD2] (464)19.10.51 PC驱动能力寄存器(PCDR) [0xD3] (464)19.10.52 PD驱动能力寄存器(PDDR) [0xD4] (465)19.10.53 PE驱动能力寄存器(PEDR) [0xD5] (466)19.10.54 PG驱动能力寄存器(PGDR) [0xD6] (467)19.10.55 模拟管脚使能寄存器0(AIOEN0) [0xCF] (467)19.10.56 模拟管脚使能寄存器1(AIOEN1) [0xD7] (469)19.10.57 复位管脚滤波选择寄存器(NRSTFQS) [0xD9] (470)19.10.58 唤醒使能寄存器(WKUPEN) [0xDB] (470)19.10.59 INT0上升沿中断使能寄存器(INT0PE) [0xDC] (471)19.10.60 INT0下降沿中断使能寄存器(INT0NE) [0xDD] (471)19.10.61 INT0中断使能寄存器(INT0EN) [0xDE] (472)19.10.62 INT0中断控制寄存器(INT0CON) [0xDF] (473)19.10.63 INT1上升沿中断使能寄存器(INT1PE) [0xE1] (474)19.10.64 INT1下降沿中断使能寄存器(INT1NE) [0xE2] (475)19.10.65 INT1中断使能寄存器(INT1EN) [0xE3] (476)19.10.66 INT1中断控制寄存器(INT1CON) [0xE4] (477)19.10.67 INT1中断管脚选择寄存器0(INT1SEL0) [0xE5] (478)19.10.68 INT1中断管脚选择寄存器1(INT1SEL1) [0xE6] (479)19.10.69 INT1中断管脚选择寄存器2(INT1SEL2) [0xE7] (480)19.10.70 INT1中断管脚选择寄存器3(INT1SEL3) [0xE9] (480)19.10.71 PWM刹车选择寄存器(PWMBKS) [0xEA] (481)19.10.72 PWM特殊复用输出分组选择寄存器(PWMOSEL) [0xF1] (481)19.10.73 PWM特殊复用输出选择寄存器0(PWMOSEL0) [0xF2] (482)19.10.74 PWM特殊复用输出选择寄存器1(PWMOSEL1) [0xF3] (483)19.10.75 PWM特殊复用输出选择寄存器2(PWMOSEL2) [0xF4] (483)19.10.76 PWM特殊复用输出使能寄存器0(PWMOMUX0) [0xF5] (484)19.10.77 PWM特殊复用输出使能寄存器1(PWMOMUX1) [0xF6] (485)19.10.78 PWM特殊复用输出使能寄存器2(PWMOMUX2) [0xF7] (486)19.10.79 PA输入缓冲使能寄存器(PAIE) [0xF9] (487)19.10.80 PB输入缓冲使能寄存器(PBIE) [0xFA] (488)19.10.81 PC输入缓冲使能寄存器(PCIE) [0xFB] (489)19.10.82 PD输入缓冲使能寄存器(PDIE) [0xFC] (489)19.10.83 PE输入缓冲使能寄存器(PEIE) [0xFD] (490)19.10.84 PG输入缓冲使能寄存器(PGIE) [0xFE] (491)19.10.85 PA数据寄存器(P0) [0x80] (492)19.10.86 PB数据寄存器(P1) [0x90] (492)19.10.87 PC数据寄存器(P2) [0xA0] (492)19.10.88 PD数据寄存器(P3) [0xB0] (492)19.10.89 PE数据寄存器(P4) [0xC8] (492)19.10.90 PG数据寄存器(P6) [0x98] (492)20电气特性 (493)20.1极限参数 (493)20.2工作条件 (493)20.2.1 芯片供电 (493)20.2.2 功耗特性 (493)20.2.3 I/O特性 (494)20.2.4 REGC引脚特性 (495)20.2.5 NRST引脚特性 (495)20.2.6 上电/掉电条件 (495)20.2.7 时钟特性 (496)20.2.8 通信接口 (498)20.2.9 FLASH特性 (501)20.2.10 ADC特性 (501)20.2.11 PGA特性 (502)20.2.12 CMP特性 (502)20.2.13 内部参考电压特性 (503)20.2.14 电气敏感性 (503)21封装特性 (504)21.1LQFP32L (504)21.2LQFP48L (505)21.3QFN32L (507)21.4TSSOP28L (508)1产品概述1.1功能描述JMT1808R是一款内置MCU和DSP的双核SOC芯片。

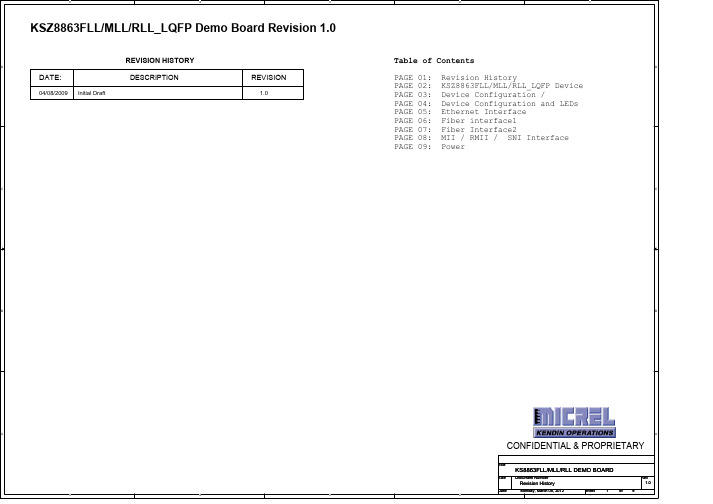

KS8863MLL_FLL_RLL_DEMO_BOARD_V1-201203

7 7

7 7

J13

1

2

3

4

CON4A

Test Mode,4V

Ext_V2 R12 4.7K

FXSD2

7

+3.3A

Force FX Mode R8

4.7K

JP77

FXSD2

1

2

3

4

5

6

7

8

R9

B

Do not populate

HEADER 4X2

TX Mode

1K

cap if pull down

is used

SCL_MDC INTRN SCRS3 SCOL3 VDDC GND

SMRXC3 SMRXD30 SMRXD31 SMRXD32 SMRXD33 SMRXDV3

C 6

3,4

SPIQ

3

SPISN

4

P1LED1

4

P1LED0

3,4

P2LED1

3,4

P2LED0

1-2 for FLL, 3-4 for MLL/RLL J12

SMRXDV3

2,8

R131 1K

+3.3V

+3.3V

JP103

1 2

B

3

3X1

R106 4.7K

P1LED1

R114 1K

2

JP104

1 2

3

3X1

R107 4.7K

P1LED0

2

R115 1K

PORT 2

+3.3V

+3.3V

JP201

1 2

3

3X1

R111 4.7K

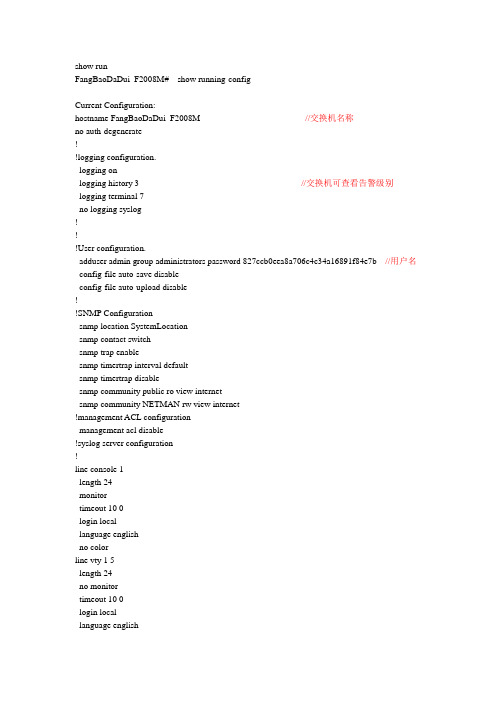

烽火2008脚本

show runFangBaoDaDui_F2008M# show running-configCurrent Configuration:hostname FangBaoDaDui_F2008M //交换机名称no auth-degenerate!!logging configuration.logging onlogging history 3 //交换机可查看告警级别logging terminal 7no logging syslog!!!User configuration.adduser admin group administrators password 827ccb0eea8a706c4c34a16891f84e7b //用户名config-file auto-save disableconfig-file auto-upload disable!!SNMP Configurationsnmp location SystemLocationsnmp contact switchsnmp trap enablesnmp timertrap interval defaultsnmp timertrap disablesnmp community public ro view internetsnmp community NETMAN rw view internet!management ACL configurationmanagement acl disable!syslog server configuration!line console 1length 24monitortimeout 10 0login locallanguage englishno colorline vty 1 5length 24no monitortimeout 10 0login locallanguage englishno color!!SGM Configurationsgmsgm role candidate!!Cos Configurationcoscos disablecos queue mode weighted-round-robincos queue 0 weight 1cos queue 1 weight 2cos queue 2 weight 4cos queue 3 weight 8cos priority 0 queue 0cos priority 1 queue 0cos priority 2 queue 1cos priority 3 queue 1cos priority 4 queue 2cos priority 5 queue 2cos priority 6 queue 3cos priority 7 queue 3cos priority remap disablecos priority 0 map-to 0cos priority 1 map-to 0cos priority 2 map-to 0cos priority 3 map-to 0cos priority 4 map-to 0cos priority 5 map-to 0cos priority 6 map-to 0cos priority 7 map-to 0!!!Vlan Configurationinterface vlan 1 //默认vlan member 1-9 untaggedinterface vlan 49 //划分vlan member 1 tagged //vlan 成员及类型member 2-3 untagged //vlan 成员及类型interface vlan 50member 1 taggedmember 4-8 untaggedinterface vlan 254member 1 tagged!!MAC Aging Configurationmac aging-time 300mac learn-mode independence!!System Configurationsystem //系统视图management vlan 254 //管理VLAN ip address 10.20.4.10/24 //管理IP地址gateway 10.20.4.1 //网关out-band ip address 192.168.2.1/24arp-request timer 0anti-attack enableigmp-snooping proxy vlan 1igmp-snooping max multicast-group 256!!Radius Configurationradiusradius disable!!Stp Configurationstpstp disable!!Loop Check configurationloop-check trap disableloop-check action isolationloop-check expire-time 0!!Dtag Configuration!!Dhcp Configuration!!Spnm Configurationspnmspnm disablespnm password switchspnm send-access-mac disablespnm community NETMAN!!Rmon configuration!!Anti-arp Configurationanti-arp disable!ftpd configurationno ftpd!!ESR Configurationesresr disable!!Ethernet Configurationinterface ethernet 1 //端口名称join vlan 49-50,254 tagged //端口VLAN信息及类型join vlan 1 untagged //端口VLAN信息及类型auto-neg 10M half enableauto-neg 10M full enableauto-neg 100M half enableauto-neg 100M full enableauto-neg pause disableduplex autoflow-ctrl disablepacket-limit broadcast 64packet-limit multicast 0packet-limit dlf 64stp disablestp priority 0no shutdownloop-check enableloop-check vlan 1dtag disablesecurity-mac disableuser-limit number 0interface ethernet 2join vlan 1,49 untaggedauto-neg 10M half enableauto-neg 10M full enableauto-neg 100M half enableauto-neg 100M full enableauto-neg pause disableduplex autoflow-ctrl disablepvid 49 //端口标签号packet-limit broadcast 64packet-limit multicast 0packet-limit dlf 64stp disablestp priority 0no shutdownloop-check enableloop-check vlan 1dtag disablesecurity-mac disableuser-limit number 0interface ethernet 3join vlan 1,49 untagged auto-neg 10M half enable auto-neg 10M full enable auto-neg 100M half enable auto-neg 100M full enable auto-neg pause disable duplex autoflow-ctrl disablepvid 49packet-limit broadcast 64 packet-limit multicast 0 loop-check vlan 1dtag disablesecurity-mac disableuser-limit number 0interface ethernet 4join vlan 1,50 untagged auto-neg 10M half enable auto-neg 10M full enable auto-neg 100M half enable auto-neg 100M full enable auto-neg pause disable duplex autoflow-ctrl disablepvid 50packet-limit broadcast 64 packet-limit multicast 0 packet-limit dlf 64stp disablestp priority 0no shutdownloop-check enableloop-check vlan 1dtag disablesecurity-mac disableuser-limit number 0interface ethernet 5join vlan 1,50 untagged auto-neg 10M half enable auto-neg 10M full enable auto-neg 100M half enable auto-neg 100M full enable auto-neg pause disable duplex autoflow-ctrl disablepvid 50packet-limit broadcast 64 packet-limit multicast 0 packet-limit dlf 64stp disablestp priority 0no shutdownloop-check enableloop-check vlan 1dtag disablesecurity-mac disableuser-limit number 0interface ethernet 6join vlan 1,50 untagged auto-neg 10M half enable auto-neg 10M full enable auto-neg 100M half enable auto-neg 100M full enable auto-neg pause disable duplex autoflow-ctrl disablepvid 50packet-limit broadcast 64 packet-limit multicast 0 packet-limit dlf 64stp disablestp priority 0no shutdownloop-check enableloop-check vlan 1dtag disablesecurity-mac disableuser-limit number 0interface ethernet 7join vlan 1,50 untagged auto-neg 10M half enable auto-neg 10M full enable auto-neg 100M half enable auto-neg 100M full enable auto-neg pause disable duplex autoflow-ctrl disablepvid 50packet-limit broadcast 64 packet-limit multicast 0 packet-limit dlf 64stp disablestp priority 0no shutdownloop-check enableloop-check vlan 1dtag disablesecurity-mac disableuser-limit number 0interface ethernet 8join vlan 1,50 untagged auto-neg 10M half enable auto-neg 10M full enable auto-neg 100M half enable auto-neg 100M full enable auto-neg pause disable duplex autoflow-ctrl disablepvid 50packet-limit broadcast 64 packet-limit multicast 0 packet-limit dlf 64stp disablestp priority 0no shutdownloop-check enableloop-check vlan 1dtag disablesecurity-mac disable user-limit number 0interface ethernet 9join vlan 1 untagged duplex autoflow-ctrl disablepacket-limit broadcast 64 packet-limit multicast 0 packet-limit dlf 64stp disablestp priority 0no shutdownloop-check enableloop-check vlan 1dtag disablesecurity-mac disable user-limit number 0!!endFangBaoDaDui_F2008M#。

蓝牙测试指标

一:介绍1. 范围2. 概况3. 参考文件二:RADIO FREQUENCY无线电频率测试1. 介绍2. 测试环境3. 测试项目3.1 Output power输出功率3.2 Power Control 功率控制3.3 Initial Carrier Frequency 最初的载波频率3.4 Carrier Frequency Drift 载波频率漂移3.5 Modulation Characteristic 调制特性3.6 Single Slot Sensitivity单插槽的敏感性3.7 Multi Slots Sensitivity 多槽灵敏度3.8 Maximum Input Level最大输入标准三:蓝牙耳机功能测试1. 耗电量静态及工作电流/待机电流2. 充电、充电连接、显示3. 频率调整4. 配对5. 音频连接6. 仿真音频7. 兼容性8. 通话距离9. 外观结构四:附件功能测试1. 火牛高压2. 火牛输出电压3. SPK功能4. MIC功能五:运行条件一:介绍1. 范围此文件概括说明所有蓝牙产品的初步测试计划2. 概况3.1~3.8项目主要描述射频测试,三项主要描述耳机实际使用功能测试,四项主要描述耳机附件的功能测试3. 参考文件[1]Bluetooth: Specification of the Bluetooth System, Volume 2: Core(Controller v1.2 )蓝牙:蓝牙系统的规范,卷2:核心(控制器v1.2)[2]Bluetooth: Specification of the Bluetooth System, Volume 3: Core (Hostv1.2 )[3]Bluetooth: Specification of the Bluetooth System, Volume 2: Core(Controller v2.0)[4]Bluetooth: Specification of the Bluetooth System, Volume 3: Core (Host v2.0)[5]Bluetooth: Headset Profile (v1.1) 蓝牙:耳机概要(v1.1[6]Bluetooth: Core System Package : RF Test Suite Structure (TSS) /TestPurpose(TP) (v2.0)蓝牙:核心系统方案:射频测试套件结构(TSS)/测试目的(TP)(v2.0)[7]Bluetooth: Core System Package : Baseband Test Suite Structure (TSS) /TestPurpose(TP) (v2.0) 蓝牙:核心系统方案:基带测试套件结构(TSS)/测试目的(TP)(v2.0)[8]Bluetooth: Core System Package : LM Test Suite Structure (TSS) /TestPurpose(TP) (v2.0)蓝牙:核心系统方案:LM测试套件结构(TSS)/测试目的(TP)(v2.0)[9]Bluetooth: Core System Package : General Access Profile Test SuiteStructure (TSS) /Test Purpose(TP) (v2.0) 蓝牙:核心系统方案:通用访问配置文件测试套件结构(TSS)/测试目的(TP)(v2.0[10]Bluetooth: Headset Profile Specification 1.1 Test Suite Structure (TSS)/Test Purpose(TP)牙:耳机概要文件规范1.1测试套件结构(TSS)/测试目的(TP)[11]CSR: BlueCore2-Audio Datasheet企业社会责任:BlueCore2-Audio数据表TP是可靠性测试二:RADIO FREQUENCY TEST射频测试1. 介绍这一个测试是确定蓝牙耳机的射频 (发射器和接收器) 基本功能是否符合或超过蓝牙标准要求2. 测试环境Bluetooth Tester-- Anritsu MT8852A/MT8852B or other 蓝牙测试仪,特制MT8852A / MT8852B或其他DUT(Device Under Test)- Linnking Bluetooth DUT(测试设备)——Linnking蓝牙3. 测试项目3.1 Output power 输出功率DUT 初始设置:DUT用loop back测试模式使用跳频测试程序及标准MT8850A 传输一个标准的数据包(DH5 , DH1,DH3 或Longest )给DUT. 此DUT 环向后将数据传送给Bluetooth tester ,MT8850A 测量其功率. 这一个测试在跳时运行,而且测试被重复。

Infoprint 250 導入と計画の手引き 第 7 章ホスト

SUBNETMASK

255.255.255.128

Type of service...............: TOS

*NORMAL

Maximum transmission unit.....: MTU

*LIND

Autostart.....................:

AUTOSTART

*YES

: xx.xxx.xxx.xxx

: xx.xxx.xxx.xxx

*

(

)

IEEE802.3

60 1500

: xxxx

48 Infoprint 250

31. AS/400

IP

MTU

1

1

IPDS TCP

CRTPSFCFG (V3R2)

WRKAFP2 (V3R1 & V3R6)

RMTLOCNAME RMTSYS

MODEL

0

Advanced function printing............:

AFP

*YES

AFP attachment........................:

AFPATTACH

*APPC

Online at IPL.........................:

ONLINE

FORMFEED

*CONT

Separator drawer......................:

SEPDRAWER

*FILE

Separator program.....................:

SEPPGM

*NONE

Library.............................:

H3C S5800 版本说明书

H3C S5800_5820X-CMW520-R1810P16 版本说明书Copyright © 2018新华三技术有限公司版权所有,保留一切权利。

非经本公司书面许可,任何单位和个人不得擅自摘抄、复制本文档内容的部分或全部,并不得以任何形式传播。

本文档中的信息可能变动,恕不另行通知。

目录1 版本信息 (1)1.1 版本号 (1)1.2 历史版本信息 (1)1.3 版本配套表 (4)1.4 ISSU版本兼容列表 (5)1.5 版本升级注意事项 (6)2 硬件特性变更说明 (6)2.1 R1810P16版本硬件特性变更说明 (6)2.2 R1810P13版本硬件特性变更说明 (6)2.3 R1810P12版本硬件特性变更说明 (6)2.4 R1810P10版本硬件特性变更说明 (6)2.5 R1810P08版本硬件特性变更说明 (7)2.6 R1810P06版本硬件特性变更说明 (7)2.7 R1810P05版本硬件特性变更说明 (7)2.8 R1810版本硬件特性变更说明 (7)2.9 R1809P11版本硬件特性变更说明 (7)2.10 R1809P10版本硬件特性变更说明 (7)2.11 R1809P09版本硬件特性变更说明 (7)2.12 R1809P06版本硬件特性变更说明 (7)2.13 R1809P05版本硬件特性变更说明 (7)2.14 R1809P03版本硬件特性变更说明 (7)2.15 R1809P01版本硬件特性变更说明 (7)2.16 R1808P27版本硬件特性变更说明 (8)2.17 R1808P25版本硬件特性变更说明 (8)2.18 R1808P23版本硬件特性变更说明 (8)2.19 R1808P22版本硬件特性变更说明 (8)2.20 R1808P21版本硬件特性变更说明 (8)2.21 R1808P17版本硬件特性变更说明 (8)2.22 R1808P15版本硬件特性变更说明 (8)2.23 R1808P13版本硬件特性变更说明 (8)2.24 R1808P11版本硬件特性变更说明 (8)2.25 R1808P08版本硬件特性变更说明 (8)2.26 R1808P06版本硬件特性变更说明 (8)i2.29 F1807P01版本硬件特性变更说明 (9)2.30 R1805P02版本硬件特性变更说明 (9)2.31 R1211P08版本硬件特性变更说明 (9)2.32 R1211P06版本硬件特性变更说明 (9)2.33 R1211P03版本硬件特性变更说明 (9)2.34 R1211P02版本硬件特性变更说明 (9)2.35 R1211版本硬件特性变更说明 (9)2.36 F1209P01版本硬件特性变更说明 (9)2.37 F1209版本硬件特性变更说明 (9)2.38 F1208版本硬件特性变更说明 (10)2.39 F1207版本硬件特性变更说明 (10)2.40 R1206版本硬件特性变更说明 (10)2.41 R1110P05版本硬件特性变更说明 (10)2.42 R1110P04版本硬件特性变更说明 (10)3 软件特性及命令行变更说明 (10)4 MIB变更说明 (10)5 操作方式变更说明 (16)5.1 R1810P16版本操作方式变更 (16)5.2 R1810P13版本操作方式变更 (16)5.3 R1810P12版本操作方式变更 (16)5.4 R1810P10版本操作方式变更 (16)5.5 R1810P08版本操作方式变更 (17)5.6 R1810P06版本操作方式变更 (17)5.7 R1810P05版本操作方式变更 (17)5.8 R1810版本操作方式变更 (17)5.9 R1809P11版本操作方式变更 (17)5.10 R1809P10版本操作方式变更 (17)5.11 R1809P09版本操作方式变更 (17)5.12 R1809P06版本操作方式变更 (17)5.13 R1809P05版本操作方式变更 (18)5.14 R1809P03版本操作方式变更 (18)5.15 R1809P01版本操作方式变更 (18)5.16 R1808P27版本操作方式变更 (18)5.17 R1808P25版本操作方式变更 (18)ii5.20 R1808P21版本操作方式变更 (18)5.21 R1808P17版本操作方式变更 (19)5.22 R1808P15版本操作方式变更 (19)5.23 R1808P13版本操作方式变更 (19)5.24 R1808P11版本操作方式变更 (19)5.25 R1808P08版本操作方式变更 (19)5.26 R1808P06版本操作方式变更 (19)5.27 R1808P02版本操作方式变更 (19)5.28 R1807P02版本操作方式变更 (20)5.29 F1807P01版本操作方式变更 (20)5.30 R1805P02版本操作方式变更 (20)5.31 R1211P08版本操作方式变更 (20)5.32 R1211P06版本操作方式变更 (21)5.33 R1211P03版本操作方式变更 (21)5.34 R1211P02版本操作方式变更 (21)5.35 R1211版本操作方式变更 (21)5.36 F1209P01版本操作方式变更 (21)5.37 F1209版本操作方式变更 (21)5.38 F1208版本操作方式变更 (21)5.39 F1207版本操作方式变更 (22)5.40 R1206版本操作方式变更 (22)5.41 R1110P05版本操作方式变更 (22)5.42 R1110P04版本操作方式变更 (23)6 版本使用限制及注意事项 (23)7 存在问题与规避措施 (23)8 解决问题列表 (24)8.1 R1810P16版本解决问题列表 (24)8.2 R1810P13版本解决问题列表 (24)8.3 R1810P12版本解决问题列表 (25)8.4 R1810P10版本解决问题列表 (26)8.5 R1810P08版本解决问题列表 (27)8.6 R1810P06版本解决问题列表 (28)8.7 R1810P05版本解决问题列表 (28)8.8 R1810版本解决问题列表 (28)iii8.11 R1809P09版本解决问题列表 (30)8.12 R1809P06版本解决问题列表 (31)8.13 R1809P05版本解决问题列表 (32)8.14 R1809P03版本解决问题列表 (33)8.15 R1809P01版本解决问题列表 (34)8.16 R1808P27版本解决问题列表 (36)8.17 R1808P25版本解决问题列表 (36)8.18 R1808P23版本解决问题列表 (38)8.19 R1808P22版本解决问题列表 (38)8.20 R1808P21版本解决问题列表 (39)8.21 R1808P17版本解决问题列表 (39)8.22 R1808P15版本解决问题列表 (40)8.23 R1808P13版本解决问题列表 (41)8.24 R1808P11版本解决问题列表 (42)8.25 R1808P08版本解决问题列表 (44)8.26 R1808P06版本解决问题列表 (44)8.27 R1808P02版本解决问题列表 (46)8.28 R1807P02版本解决问题列表 (49)8.29 F1807P01版本解决问题列表 (50)8.30 R1805P02版本解决问题列表 (50)8.31 R1211P08版本解决问题列表 (53)8.32 R1211P06版本解决问题列表 (53)8.33 R1211P03版本解决问题列表 (57)8.34 R1211P02版本解决问题列表 (57)8.35 R1211版本解决问题列表 (58)8.36 F1209P01版本解决问题列表 (62)8.37 F1209版本解决问题列表 (62)8.38 F1208版本解决问题列表 (63)8.39 F1207版本解决问题列表 (65)8.40 R1206版本解决问题列表 (65)8.41 R1110P05版本解决问题列表 (66)8.42 R1110P04版本解决问题列表 (68)9 相关资料 (70)9.1 相关资料清单 (70)iv10 技术支持 (70)附录 A 本版本支持的软、硬件特性列表 (71)A.1 版本硬件特性 (71)A.2 版本软件特性 (73)附录 B 版本升级操作指导 (84)B.1 简介 (84)B.2 软件加载方式简介 (84)B.3 BootRom界面加载 (85)B.3.1 BootRom界面介绍 (85)B.3.2 通过Console口利用XModem完成加载 (89)B.3.3 通过以太网口利用TFTP完成加载 (100)B.3.4 通过以太网口利用FTP完成加载 (103)B.4 命令行接口加载 (107)B.4.1 通过USB口实现软件加载 (107)B.4.2 通过FTP实现软件加载 (107)B.4.3 通过TFTP实现软件加载 (109)v表目录表1 历史版本信息表 (1)表2 版本配套表 (4)表3 ISSU版本兼容列表 (5)表4 MIB文件变更说明 (10)表5 S5800系列产品硬件特性 (71)表6 S5820X系列产品硬件特性 (72)表7 S5800系列产品软件特性 (73)表8 S5820X系列产品软件特性 (79)表9 交换机软件加载方式一览表 (84)表10 基本BOOT菜单说明 (86)表11 基本BOOT辅助菜单说明 (86)表12 扩展BOOT菜单说明 (87)表13 扩展BOOT辅助菜单说明 (89)表14 通过Console口利用XModem加载系统文件 (93)表15 BootRom升级选择菜单 (94)表16 协议选择及参数设置菜单 (95)表17 通过以太网口利用TFTP加载系统文件 (100)表18 TFTP协议相关参数的设置说明 (102)表19 通过以太网口利用FTP加载系统文件 (104)表20 FTP协议相关参数的设置说明 (105)vi本文介绍了H3C S5800_5820X-CMW520-R1810P16版本的特性、使用限制、存在问题及规避措施等,在加载此版本前,建议您备份配置文件,并进行内部验证,以避免可能存在的风险。

VAR-SOM-MX8M-PLUS based on NXP i.MX 8M Plus Evalua

VAR-SOM-MX8M-PLUS based on NXP i.MX 8M PlusEvaluation Kit Quick Start GuideFeatures:1. Power ON Switch (SW7)2. 12V DC In Jack (J24)3. USB Debug (J29)4. micro SD Card slot (J28)5. USB 3.0 OTG (J26)6. USB 2.0 Host (J23)7. Gigabit Ethernet #0 (J21) 8. Gigabit Ethernet #1 (J20)9. MIPI-CSI #1 Camera connector [optional] (J19) 10. Miscellaneous Header #1 (J17)11. HDMI/ MIPI-CSI #2 Camera connector[optional] (J13)12. Mini PCI Express Connector (J15) 13. Miscellaneous Header #2 (J3) 14. SOM Connector (J1) 15. LVDS#B Header (J5)16. LVDS#A/ DSI Header (J7) 17. Fan Power Connector (J9) 18. Digital Microphone (U1) 19. Resistive Touch (J10) 20. Capacitive Touch (J11)21. User Buttons (SW1, SW2, SW4) 22. Line-In Connector (J12)23. Headphones Connector (J14) 24. Boot Select Switch (SW3)25. SAI/I2C/SPI/CAN Header (J16) 26. Reset Button (SW5)27. PWR Select Switch (SW6) 28. UART/PWM Header (J18) 29. RTC Battery Holder (JBT1)Evaluation kit initial Setup1. Carefully remove the 7” LCD and Symphony-Board from the package.2. Connect the 7” LCD Display and Touch cablesto the Evaluation Kit connectors J7, J11 respectively.Note:connect the display cable with the red wire on pin 1. Connect the touch cable with the metal contacts facing down.3. Plug the USB type A to micro B cable betweenthe USB debug connector (J29) and a PC USB port.4. For heatsink assembly instructions, pleasefollow the VHP-VS8M documentation .Please note that the heatsink is mainly used for CPU/GPU intensive applications and may be required per your specific use case.P/N VSS0177AVAR-SOM-MX8M-PLUS based on NXP i.MX 8M PlusEvaluation Kit Quick Start GuideSetting the host PC for debug1. Download any PC terminal software (e.g. Putty ).2. Set the PC terminal software parameters as follows:- Baud Rate: 115200 - Data bits: 8 - Stop bits: 1 - Parity: None- Flow Control: NoneBooting from eMMC1. Set Boot select switch (SW3) to “Internal” position to boot from the VAR-SOM-MX8M-PLUS internal storage.2. Plug the wall adapter into the 12V power jack (J24) and to a 120VAC~240VAC power source.3. Set Power ON switch (SW7) to ON state.4. Boot messages are printed within the PC terminal window.Booting from a micro SD cardThe microSD card is supplied within the package. Updated SD card images can also be downloaded from the Variscite FTP server.See more details in the recovery SD card section in the Variscite Wiki pages.1. Set Power ON switch (SW7) to off state.2. Set Boot select switch (SW3) to “SD ” positionin order to boot from SD Card.3. Push microSD card into the microSD cardslot (J28) of the Symphony-Board.4. Set Power ON switch (SW7) to ON state.5. Boot messages are print ed within PC’sterminal window.(Re-)Installing the file system to eMMCPlease refer to the recovery SD card section in the Variscite Wiki pages.Linkso Wiki page:https:///index.php?title=VAR-SOM-MX8M-PLUSo VAR-SOM-MX8M-PLUS Evaluation kits:https:///product/evaluation-kits/var-som-mx8m-plus-evaluation-kits/o VAR-SOM-MX8M-PLUS System on Module:https:///product/system-on-module-som/cortex-a53-krait/var-som-mx8m-plus-nxp-i-mx-8m-plus/o Symphony carrier board:https:///product/single-board-computers/symphony-board/o Customer portal:https:///loginThank you for purchasing Variscite’s product.For additional assistance please contact: *******************。

STM32固件库使用手册【中文】

所有的驱动源代码都符合“Strict ANSI-C”标准(项目于范例文件符合扩充 ANSI-C 标准)。我们已经把驱动 源代码文档化,他们同时兼容 MISRA-C 2004 标准(根据需要,我们可以提供兼容矩阵)。由于整个固态 函数库按照“Strict ANSI-C”标准编写,它不受不同开发环境的影响。仅对话启动文件取决于开发环境。

1.3.1 变量 ................................................................................................................................................ 28 1.3.2 布尔型 ............................................................................................................................................ 28 1.3.3 标志位状态类型 ........................................................................................................................... 29 1.3.4 功能状态类型 ...............................................

全网站点参数设置

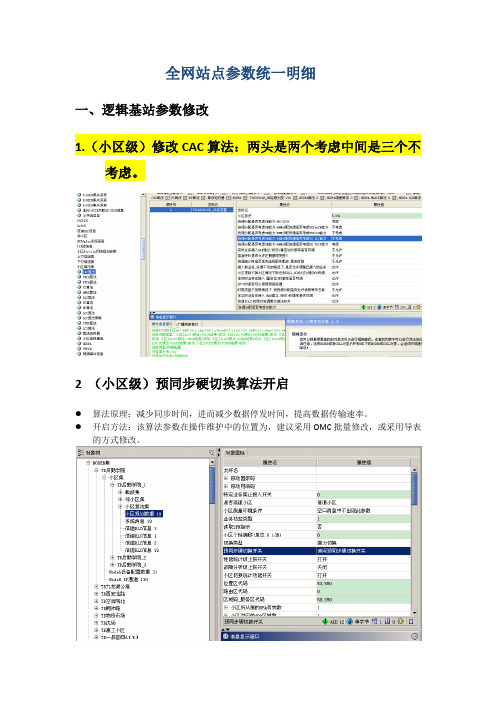

全网站点参数统一明细一、逻辑基站参数修改1.(小区级)修改CAC算法:两头是两个考虑中间是三个不考虑。

2 (小区级)预同步硬切换算法开启●算法原理:减少同步时间,进而减少数据停发时间,提高数据传输速率。

●开启方法:该算法参数在操作维护中的位置为,建议采用OMC批量修改,或采用导表的方式修改。

3.(小区级)PS算法定时器,市区基站修改为300.郊县暂时默认为10s。

二、超级基站参数修改三、HSDPA速率提升专项配置:以下参数是基于28及28补丁版本,且在之前的优化参数基础上做修改,具体修改参数如下:1.(小区级)QM使用的SEND类型控制帧发送最大周期由10设置为5,空口平均速率统计窗长修改为4图42.(小区级)HSDPA慢速功控功能打开。

图53.(小区级)CQI修正参数配置图64.(小区级)HARQ最大传输次数由4设置为6。

HARQ信息qpsk: 0/2/1/316qam: 0/1/2/3图7注意:LMT-B上qpsk和16qam是交叉出现的,因此修改时界面值显示如下:0-0-2-1-1-2-3-3—0-0-2-1-1-2-3-3(qpsk、16qam的1-4修改值为:0-0-2-1-1-2-3-3,5至8的重复配置。

)如果修改的时候下面有个数据是空格,就修改为2,如图:注:所有参数修改值以表格所列为准,图片只是示意修改项所在位置。

5.(RNC级) reorderingReleaseTimer T1定时器设置为300ms参数原理:增加重排序等待时间,设置到200ms以上后其实该值不起作用了。

图3.1涉及业务类型包括:背景类、流类、交互类。

6.(RNC级) MACHSDISCARDTIME由200ms设置为250ms参数原理:拉长mac对数据的丢弃时间,尽量不丢弃。

参见图3.1;涉及业务类型包括:背景类、流类、交互类参标中注:对于流业务,RAB指派消息中携带有Transfer delay,此参数应该小于Transfer delay。

llama-factory 训练参数 解释

Llama-Factory训练参数解释如下:

--quantization_bit4/8:启用QLoRA训练。

--lora_target:LoRA作用模块,默认模块应作为该参数的默认值,可使用--lora_targetall 参数指定全部模块。

--model_name_or_path:模型地址。

--do_train:表示进行训练。

--dataset:使用的数据集。

--finetuning_type:微调的方法。

--output_dir:断点保存,保存模型断点的位置。

--overwrite_cache:表示是否覆盖缓存文件。

--per_device_train_batch_size:批处理大小,每块GPU上处理的样本数量。

--gradient_accumulation_steps:梯度累积,梯度累积的步数(节省显存的方法)。

--lr_scheduler_type:学习率调节器,采用的学习率调节器名称。

--logging_steps:日志间隔,每两次日志输出间的更新步数。

--save_steps:保存间隔,每两次断点保存间的更新步数。

--learning_rate:学习率,AdamW优化器的初始学习率。

--num_train_epochs:训练轮数,需要执行的训练总轮数。

--plot_loss:绘制损失函数图。

--fp16:计算类型,是否启用fp16或bf16混合精度训练。

F820脚本(邵阳)

show onu unauthentication

在olt上,查看未注册的,记录mac地址和pon口号。

interface epon-olt_0/1/4

onu 1 type ZTE-F820 mac

onu 2 type ZTE-F820 mac b4b3.62e6.abc5

onu 3 type ZTE-F820 mac b4b3.62e6.b289

int fei_0/5/1

switchport vlan 2001 tag

exit

sho

voip 5

mg net 1 mode 0 ip-address 10.41.125.133 mask 255.255.255.0 gateway 10.41.125.1 vlan-option 1 vlan-id 2001 vlan-priority 6

mgmt-ip onu-ip 10.65.80.23 255.255.224.0 7 50 mgm-ip 0.0.0.0 0.0.0.0 10.65.80.1 status enable

c300配置脚本

pon-onu-mng epon-onu_0/2/2:6

auto-config

mgmt-ip 10.65.48.134 255.255.224.0 vlan 102 priority 7 route 0.0.0.0 0.0.0.0 10.65.48.1 status enable

F820到2012年5月的最新版本是 V1.1.0P1T6 EPUA 为v6.5或者V1.3.18或者 V1.4.3 2012年7月最新版本V1.1.0P1T6。

ZXAN(config)#nvram boot-server 218.76.199.136

无刷直流电机控制器的软件设计中英文翻译(精)

Commutation Torque Ripple Reduction in BLDC Motor Using PWM_ON_PWM ModeGuangwei Meng, Hao Xiong, Huaishu Li Department of Electrical Engineering, Naval University of Engineering, Wuhan, China.Abstrac t:The paper analyzes the steady commutation process of the BLDC motor using PWM mode, confirms the commutation time to keep noncommutation phase current amplitude constant during commutation period by way of PWM in the period to implement the compensation control to eliminate commutation torque ripple under both low speed and high speed operation, investigates the effect by PWM mode on a three-phase six-state 120°turn-on BLDC motor, and presents torque ripple compensation control in PWM_ON_PWM mode, which can not only entirelyeliminate torque ripple resulted from the current emerging in the turn-off phase during non-commutation period but also compensate torque ripple caused by the commutation current during commutation period.Index Terms—BLDC motor, commutation, PWM, torque ripple.I. INTRODUCTIONThe BLDC motors have been widely used due to its features - a simple structure, good speed adjusting performance,high power density, low noise and simple control, etc. It is a hotspot to suppress the torque ripple and improve the control performance of a BLDC motor with the trapezoidal back emf.BLDC motors usually operate in all kinds of PWM modes, which not only affect the dynamic loss of power switches and radiation uniformity, but also influence the torque ripple. It is an effective way to suppress the torque ripple through changing dc bus chopper control to remain non-commutation phase current amplitude constant, but it results into a more complex topology [1]-[3]. It is just fit for low speed applications tocontrol non-commutation phase current amplitude to regulate the commutation torque ripple . It is analyzed about the influence resulted from PWM ON mode on the torque ripple .The ideas in [1]-[3] are to adopt different suppression methods in different speed interval, but they don’t take t he effect by PWM mode s on the systemin account. The predictive current, neural network control and active disturbance rejection control etc are introduced to suppress the torque ripple , but the control algorithm is more complicated and harder for realization.Depending on the commutation process of BLDC motors and the effect by PWM modes on the system, thepaper presents a torque ripple com-pensation control inPWM_ON_PWM mode at different speeds by seeking different PWM modulation ratios during commutation period as motor runs at low speed and high speed.The method retains the original to-pology, improves the control performance of the system dramatically,and moreover is easy to realize.II. ELECTROMAGNETIC TORQUE OF BLDC MOTORDURING COMMUTATION PROCESSAssume that the BLDC motor is three-phase symmetrical and Y- connected, and neglect eddy currents and hysteresis losses, its equivalent circuit and main circuit are shown in Figure 1. r, L are the resistance andinductance of the stator windingsrespectively;C B A e e e ,, are the counter emfs of the corresponding phase windings respectively; C B A i i i ,, are the corresponding phase currents respectively.0=++C B A i i i (1The counter emf of every phase winding is a trapezoidal waveform with a flat-top width greater than or equal to 1200 electrical degree,and its flat-top amplitude is Em. When the motor works in three-phase six-state 1200 turn-on mode, the currents don’t commutates instantaneously as a result of the inductanceof the armature winding. Take the power switch 1T and 2T ’s turn-on to2T and 3T ’s turn -on for example. During the commutation, it is gained as follows m C B A E e e e =-== (2Suppose that the mechanical angular velocity of the rotor is Ω, the toque can be obtained as follows during the commutation process.Ω=Ω++=C m C C B B A A e i E i e i e i e T 2 (3 It is obvious from (3 that the toque is proportional to the non-commutation phase current during commutation,i.e. the commutation torque ripple can be eliminated so long as non-commutation phase current remains constant during commutation. III TORQUE RIPPLE REDUCTION IN PWM MODEa new PWM mode is presented -PWM _ON _PWM, i.e. using PWM mode in the first30°and the last 30° while keeping constant turn-onmode in the middle 60°. The mode can entirely eliminate the emerging current in the turn-off phase during non-commutation and thus reduce the torqueripple during non-commutation.PWM _ON _PWM is a bilateral modulation, but the dynamic losses of power switches in the mode are equal to those of unilateral modulation. Six switches are modulated in turn, so the power switches have a uniform radiation and the system has a higher reliability. The mode is employing PWM on the turn-on power switchesand thus it can suppress the torque ripple during commutation to a certain extent even if a compensation control is not applied at a low speed.In PWM _ON _PWM mode, it can not only eliminate the torque ripple during non-commutation but also suppress the commutation torque ripple at low speed operation by keeping dm BB U rI E D 034+= in the commutation compensation control time ⎪⎪⎭⎫⎝⎛++=m c E rI rI r L t 21ln 00 at low speed operation, i.e.d m U rI E ≤+034.At high speed operation i.e.d m U rI E ≥+034,overlapping commutation is used to keep the turn-on phase constantly on and make the control pulse duty cycle of the turn-off phase 1340-+=dm AA U rI E D in the commutation compensation control time⎪⎪⎭⎫⎝⎛----=0021ln rI E U rI r L t m d c ,which can not only eliminate the torque ripple during noncommutation but also suppress the commutation torque ripple at high speed operation.A simulation is carried out to verify the method.The parameters areN T m r n V U m kg J r mH L L N N 4.0,1600,48,0157.0,66.0,262===⋅=Ω==.In non-full-bridge modulation mode such as H_PWM-L_ON mode, power switches in the upper arms use PWM mode while the others in the lowerarms use constant turn-on mode in 1200 turn-on interval. The simulation waveform of phase current is shown in Fig. 3. It is obvious that a current emerges in the turn-off phase during non-turn-on period and its pulsating frequency is the same as the modulatingfrequency while its amplitude varies with the variation of back emf amplitude, whichproduces a reverse torque.Figure 2 H_ PWM - L_ ON phase current waveform Figure 3 PWM_ON_PWM phase current waveform The simulation waveform of phase current in PWM _ON _PWM mode is shown in Fig.4. It is obvious that no current emerges in the turn-off phase duringnon-turnon period, which reduces the torque ripple during noncommutation compared with other PWM mode.Fig.5 shows the waveforms of the phase current and torque at low speed with PWM pulse duty cycle DA=0.2 without compensation control. Fig. 6 shows thewaveforms of the phase current and torque at low speed with the control pulse duty cycle DBB=0.4 in the turn-on phase within the commutation time tc=0.0013 by a compensation control. The comparison indicates that the torque ripple caused by commutation can be almost eliminated by means of a commutation compensationcontrol at low speed application.It is found from Fig.3 to Fig.8 that using a commutation compensation control in PWM_ON_PWM mode can not only avoid the torque ripple caused by the emerging current in the turn-off phase during noncommutation but also effectively suppress the commutation torque ripple at both low speed and high speed applications.Figure4 phase current and torque waveform during Figure 5 when running at low speed by changing theLow speed running phase current and phase compensation torque waveformFigure 6under the speed of phase current and torque waveform Figure 7high-speed run through the compensation control ofphase current and torque waveformIV. CONCLUSIONSBased on the analysis of commutation process of BLDC motor and the effect by PWM mode on the control system, a commutation compensation control inPWM_ON_PWM mode is worked out, which can not only eliminate torque ripple resulted from the current emerging in the turn-off phase during non-commutation period but also compensate commutation torque ripple. A control system without torque ripple can be realized through the method under both low speed and high speed operation.REFERENCES[1] S. Wang, T. Li, and Z. Wang, “Commutation torque ripple reduction in brushless DC motor drives using a sin gle current sensor,” Electric Machines and Control, vol. 12,pp. 288-293, March. 2008.[2] X. Zhang and Z. Lü, “New BLDCM drive method to smooth the torque,” Power Electronics, vol. 41, pp. 102-104, Feb. 2007.[3] H.J. Song and C. Ick. “Commutation torque r ipple reduction in brushless DC motor drivers using a single DC current sensor,” IEEE Trans. On Power Electr, vol. 19,pp. 312-319, Feb. 2004.[4] G.H. Kim, J. Seog and S.W. Jong, “Analysis of the commutation torque ripple effect for BLDCM fed by HCRPWM-VSI,” Proc. of APEC’92, 1992, pp.277-284. [5] X. Zhang and B. Chen, “The different influences of four PWM modes on commutation torque ripples in brushless DC motor control system,” Electric Machines andControl,vol.7, pp. 87-91, Feb. 2003.[6] D. Chen, Z. Liu and J. Ren et al, « Analysis of effects onBLDCM torque ripple by PWM modes,”. Electrical Drivers, vol.35, pp. 18-20, April 2005.中文翻译用PWM_ON_PWM模式抑制无刷直流电机换相引起的脉动转矩中国武汉海军工程大学电机工程系蒙广伟、雄郝、李怀树编摘要:本文分析了无刷直流电动机采用PWM控制稳定换相的过程,证实了运用PWM模式,在换相时控制非换相相电流有稳定不变的幅度,并进行补偿以消除低速和高速工作下的换相转矩脉动;研究了运用三相六状态的PWM模式120°启动无刷直流电机的方法,并提出基于脉宽调制的PWM模式如何来抑制转矩脉动,PWM 控制不仅可以消除非换相期间由关断电流引起的转矩脉动,还可以补偿换相期间由换相电流引起的转矩脉动。

MAX31888评估系统说明书

One Analog Way, Wilmington, MA 01887 U.S.A. | Tel: 781.329.4700 | © 2021 Analog Devices, Inc. All rights reserved.© 2021 Analog Devices, Inc. All rights reserved. Trademarks and registered trademarks are the property of their respective owners.General DescriptionThe MAX31888 evaluation system (EV system) demon-strates the MAX31888 1-Wire ® temperature sensor withalarm function. The MAX31888 EV system includes theMAX31888 evaluation kit (EV kit) and the USB2PMB2module. Windows ® 7/8/8.1/10 -compatible software pro-vides a user-friendly interface that demonstrates the fea-tures of the MAX31888.The MAX31888 EV kit contains an on-board DS2484I 2C to 1-Wire converter and comes with the 6-pin µDFNMAX31888ALT+T installed.Features ●On-Board I 2C to 1-Wire Converter (DS2484) ●Proven PCB Layout ●Fully Assembled and Tested ●Windows 7/8/8.1/10-Compatible Software 319-100839; Rev 0; 11/21Ordering Information appears at end of data sheet.1-Wire is a registered trademark of Maxim Integrated Products, Inc.Windows is a registered trademark of Microsoft Corporation.Pmod™” is a trademark of Digilent Inc.Quick StartRequired Equipment●MAX31888 EV system (USB cable included)●Windows PC ●MAX31888GUISetup.msi file Note: In the following sections, software-related items are identified by bolding. Text in bold refers to items directly from the EV kit software. Text in bold and underlined refers to items from the Windows operating system.Procedure The EV system is fully assembled and tested. Follow the steps to verify board operation:Caution: Do not turn on the power supply until all connections are completed.1) Install the MAX31888GUISetup.msi software on a computer.2) Align the X2 connector of the USB2PMB2 with the J1 connector of the MAX31888 EV kit.3) Verify that the shunts are in the default position asshown in Table 1.4) Connect the USB cable from the computer to theUSB2PMB2 board.5) Open the EV kit GUI, MAX31888EvaluationKitTool.exe (Figure 1).6) Click the Scan Adapters button. Then select theoption PMODxxxxxx (where xxxxxx is numeric) andclick the Connect button.7) Click the Convert T button.8) Click the Read button. Figure 2 shows the measuredtemperature.FILEDECRIPTION MAX31888_uDFN_ EVKIT _A_SCHEMATI CEVKIT SCHEMATIC MAX31888_uDFN_ EVKIT _A _MARKETING_PCBEVKIT PCB LAYOUT BUILD_BOM_ MAX31888_uDFN_ EVKIT _AEVKIT BILL OF MATERIALS MAX31888_uDFN_ EVKIT _A _ODB EVKIT ODBMAX31888 EV Kit FilesFigure 1. MAX31888 Main WindowFigure 2. Measuring Temperature on the MAX31888The main window of the MAX31888 EV kit software con-tains controls to evaluate the MAX31888 IC.FIFO ControlsThe FIFO Controls groupbox allows the user to selectthe FIFO Status Clear , Almost Full Type , FIFO Rollover ,and Almost Full Setting . Click the checkbox to enablethem and click again to disable. The Data Countershows the quantity of the data stored in the FIFO andthe Overflow Counter shows the quantity the dataoverflowed.Click Set to apply the above settings.Click Read to confirm the settings.Click Flush to clear the FIFO data.Alarm Thresholds Adjust the High Threshold (Temperature High) and LowThreshold (Temperature Low) edit boxes to the desired temperature threshold. When the desired setting is set,click the Set button to apply. Click the Read button toconfirm they are set correctly.Status Register The High Temp or Low Temp fault status bit displays red when the Read button is clicked and the temperatureexceeds the threshold range.The Almost Full fault status bit displays red whenthe Read button is clicked and the FIFO data quantityexceeds 32 minus Almost Full Setting .The Temp Ready status bit displays green when theRead button is clicked and temp data has been converted.Convert T , Reset , Match ROM , and Skip ROM .Temperature The temperature is displayed in a graph. View hexadeci-mal code and converted temperature by clicking on the Read button.Logging Data The temperature and raw code can be saved to a file. Click the Export to *.CSV button before collecting data.General Description of Hardware The MAX31888 EV system demonstrates the MAX31888, a 1-Wire temperature sensor with alarm. The USB2PMB2module and the EV kit complete the system. The DS2484acts as the 1-Wire master for the MAX31888 and as anI 2C slave for the er-Supplied I 2C and I/O To evaluate the EV kit with a user-supplied I 2C bus, use connector J1 which is a PMod™-compatible connector. Ifthe master does not have a PMod-compatible connector,then make the connection directly to the SCL and SDAtest points. Make sure the return ground is the same asthe er-Supplied VPU The MAX31888 is powered through USB by default when a PMod-compatible master module is connected to the J1 connector of the EV kit. If the user-supplied VPU is used, change J6 jumper position from default to 2-3 andapply a voltage between +1.7V and +3.6V at the VPU testpoint and ensure that ground is connected at the GNDtest point.Table 1. Jumper Descriptions*Default position.JUMPERSHUNT POSITION DESCRIPTION J11-2*Connects VCC (onboard power supply)2-3Connects VPU (external power supply)SUPPLIER PHONE WEBSITE KEYSTONE(516) 328-7500https:///WURTH ELECTRONICS INC+1 877 6902207https://TDK+81 3 67 78 10 00https:/// KEMET+91-95131-45888https:///en/us.htmlAVX+1 (864) 967-2150https:///LITE-ON ELECTRONICS INC.*************https:///en-usSAMTEC1-800-726-8329https:///VISHAY1-800-344-4539https:///PANASONIC*************https:///BOURNS+1 951-781-5500https:///YAGEO+886 2 6629 9999https:///en/Home MAXIM408-601-1000https:///en.html Note: Indicate that you are using the MAX31888 when contacting these component suppliers.Ordering InformationPART TYPEMAX31888EVSYS#EV System (EV Kit + Master Board)MAX31888EVKIT#EV KitUSB2PMB2#Master Board#Denotes RoHS compliant.MAX31888 EV Kit–Silk Top MAX31888 EV Kit–TopMAX31888 EV Kit–BottomInformation furnished by Analog Devices is believed to be accurate and reliable. However, no responsibility isassumed by Analog Devices for its use, nor for any infringements of patents or other rights of third parties thatmay result from its use.Specifications subject to change without notice. No license is granted by implicationorotherwise under any patent or patent rights of Analog Devices. Trademarks andregistered trademarks are the property of their respective owners.REVISIONNUMBERREVISION DATE DESCRIPTION PAGES CHANGED 011/21Release for Market Intro —。

Kenwood TK-941 Conversion 33-centimeter Programmin

Ray Montagne - W7CIAThe frequency must be converted to a Kenwood Channel Number prior to programming. The following table, obtained from the KW900EZP program documentation by K2MCI, is used to obtain the channel number for the target frequencies:927 902919907920908921909926903 801602403200.00001811612413210.0125 2821622423220.0250 3831632433230.0375 4841642443240.0500 5851652453250.0625 6861662463260.0750 7871672473270.0875 8881682483280.1000 9891692493290.1125 10901702503300.1250 11911712513310.1375 12921722523320.1500 13931732533330.1625 14941742543340.1750 15951752553350.1875 16961762563360.2000 17971772573370.2125 18981782583380.2250 19991792593390.2375 201001802603400.2500 211011812613410.2625 221021822623420.2750 231031832633430.2875 241041842643440.3000 251051852653450.3125 261061862563460.3250 271071872573470.3375 281081882583480.3500 291091892593490.3625 301101902603500.3750 311111912613510.3875 321121922623520.4000 331131932633530.4125 341141942643540.4250 351151952653550.4375 361161962663560.4500 371171972673570.4625 381181982683580.4750 391191992693590.4875 401202002703600.5000 411212012713610.5125 421222022723620.5250 431232032733630.5375 441242042743640.5500 451252052753650.5625 461262062763660.5750 471272072773670.5875 481282082783680.6000 491292092793690.6125927 902919907920908921909926903501302102803700.6250511312112813710.6375521322122823720.6500531332132833730.6625541342142843740.6750551352152853750.6875561362162863760.7000571372172873770.7125581382182883780.7250591392192893790.7375601402202903800.7500611412212913810.7625621422222923820.7750631432232933830.7875641442242943840.8000651452252953850.8125661462262963860.8250671472272973870.8375681482282983880.8500691492292993890.8675701502303003900.8750711512313013910.8875721522323023920.9000731532333033930.9125741542343043940.9250751552353053050.9375761562363063960.9500771572373073970.9625781582383083980.9750791592393093990.9875The target frequency pairs of 927.2125 / 902.2125 and 927.2250 / 902.2250 use FCC channels 17 and 18 respectively.Programming ProcedureI. Launch KPG-25D.exe and start with an empty template by selecting New from the File menu.II. Set the Model to TK-941.III. Select Feature Option from the Edit menu.IV. Set the T.O.T. (Dispatch) parameter to 600. This is the transmission time limit, in dispatch mode, expressed in 15 seconds per step with a range of from 15 seconds to 600 seconds. The default is 60 seconds. These are set to 10 minutes (600 seconds) so that the timers in the repeater controller can be used.V. Set the T.O.T. (Tel)parameter to 600. This is the transmission time limit, in telephone mode, expressed in 15 seconds per step with a range of from 15 seconds to 600 seconds. The default is 180 seconds. These are set to 10 minutes (600 seconds) so that the timers in the repeater controller can be used.VI. Set the Drop out delay time parameter to 1. This sets the time between carrier detect drop out and the resumption of scanning. This parameter can be set from 0 to 254 seconds at 1 second per count. The default is 3 seconds.VII. Set the dwell time parameter to 1. This sets the time between the end of transmission and the resumption of scanning. This parameter can be set from 0 to 254 seconds at 1 second per count. The default is 15 seconds.VIII. Set the Transpond delay time parameter to 3. This sets the delay from the decode of a transpond enabled ID to the beginning of a transpond transmission. This parameter can be set from 0 to 254 seconds at 1 second per count. The default is 3 seconds. If this parameter is set to a value greater than the Drop out delay time then the Drop out delay time will be used as the Transpond delay time.IX. Set the TX inhibit time parameter to 5.0. This parameter sets the period of time that the transmitter is inhibited after an inhibited ID is detected. The value can be set from 0.5 seconds to 8.0 seconds in 0.5 second steps.X. Set the Aux switch parameter to N/A. This parameter toggles the following functions off:A. N/A: No functionB. Option Sig: Option signaling board reset switch.C. Manual Relay: Auxiliary output signal ON/OFF.D. Horn Alert: Horn Alert ON/OFFE. Telephone Search: Automatically searches for a vacant telephone channel (trunked system).F. ALP/Sys.Grp.: Toggle display between alphanumeric or the system & group number.G. Fixed Call: Reset radio to a pre-programmed system & group.H. Del/Add: Provides the user system Delete / Add button.XI. Set the Scan switch parameter to List scan. This parameter sets the scan type selection as follows:A. N/A:Disables the scan switch function and sounds an alert tone (if programmed) when the scan key ispressed.B. List Scan: Automatic roaming scan.C. Fix System Scan: Operator selectable system scan.XII. Set the Revert sys type parameter to Last Use. This parameter sets the programmable transmit destination system & group during scanning. Options include:A. Last Used: Last transmitted system & group.B. Last Called: Last received system & group.XIII. Set the Free System ring back parameter to No. This feature is only active during telephone use (trunked system). The radio will beep when the telephone interconnect line is not busy.XIV. Set the Clear to talk beep parameter to Yes. Upon successful access of a trunked system, this beep tone sounds to alert the user they can begin speaking.XV. Set the System search parameter to None. While a selected system is busy (the radio sounds an intercept tone) then release the PTT key, the radio will start to search for an available system automatically or manually. Options include:A. None: Disable system search.B. Auto: During the intercept tone, keep the PTT key held down and press the SCAN key. Upon release of theSCAN key, system search begins.C. Manual: During the intercept tone, releasing the PTT will initiate auto system search.XVI. Set the Display Character parameter to Grp Name. This parameter selects the display character Group name (Alphanumeric) or System & Group number. If you select the AUX switch as the display character, this selection will be just as default. Options include:A. Sys Grp: Set the display character as System & Group number.B. Grp Name: Set the display character as alphanumeric (pre-programing necessary).XVII. Set the Minimum volume parameter to 0. The minimum volume is the level which will be set automatically every time you turn on the radio. If the volume is adjusted below this level prior to turning the radio off, the volume will be set to this level the next time the radio is turned on. In order to ensure that the speaker is quiet at the repeater site, this value is set to zero. The default value is 8.XVIII. Set the Off hook scan parameter to Disable. The radio is able to scan, even with the mic off hook. Options include:A. Enable: Scan start & stop is independent of the mic hook switch.B. Disable: Mic must be on hook for scanning to start.XIX. Set the Off hook horn alt parameter to Disable. Horn alert is auto disabled when the microphone goes off hook Options include:A. Enable: Off hook auto disable.B. Disable: Manual disable only.XX. Set the Off hook decode parameter to Enable. The radio is still tone squelched, even though the mic is in the off hook condition (valid for QT, DQT and Option Signaling board decode). Options include:A. Enable: Decode signaling active even in the off hook condition.B. Disable: Decode signaling is disabled during off hook.Setting this parameter to Enable allows the radio to operate in decode without having to wire the off-hook signal to the on-hook position.XXI. Set the Access logic sig parameter to Sngl. Pulse. This logic signal is useful for external radio control unit (i.e. Mobile Data Terminal, Computer Aided Dispatch or Over The Air Re-Programming etc) that require a signal at the time of successful trunked repeater access. Options include:A. Continuous: Logic Level high during length of access.B. Sng. Pulse: Logic level high pulse at the time of a successful handshake.XXII. Set the Horn alt logic sig parameter to Pulse. The Horn Alert logic can be used to drive a vehicle horn relay, light or other device. The logic level signal can be set for a continuous (EX: light) or momentary pulse output (EX: vehicle horn relay). Options include:A. Continuous: Continuous logic level low output until reset.B. Pulse: Momentary logic level low output.XXIII.The options should now appear as:XXIV. Layout all of the repeater input frequencies in the first group. Setup each repeater output frequency in a separate system. Using the Kenwood3.exe program, the hexadecimal representation of each frequency can be determined (as seen in the table below).Group & System ConfigurationGroup 1Group 2Group 3Group 4Group 5Group 6Group 7Group 81KC7MCCTX A927.2125CarrierCH. 170xD197KC7MCCTX A927.2125EncodeCH. 170xD197KC7MCCRX A902.2125CarrierCH. 170x0190KC7MCCRX A902.2125EncodeCH. 170x0190KC7MCCTX B927.2250CarrierCH. 180xD297KC7MCCTX B927.2250EncodeCH. 180xD297KC7MCCRX B902.2250CarrierCH. 180x0290KC7MCCRX B902.2250EncodeCH. 180x0290The carrier access groups are not intended for active use but support test configurations, such as performing a -12 dB SINAD measurement on a receiver.XXV. Set the system configuration to Conventional.XXVI. Hit Enter to edit the system configuration.XXVII. Program each group as follows:A. Set the FCC field to 200.B. Set the transmit Encode field as appropriate.C. Set the receive Decode field as appropriate.D. Set the Grp-Name field as appropriate. Use unique text that will help you identify the group name whenusing the HxD program at a later step.E. Set the TlkArnd field to Yes.F. Leave all other fields at their default values.XXVIII. Save the KPG25D configuration file.XXIX. Exit the KPG25D.exe program.XXX. The KPG25D.exe program will have inserted a value of 0x089B, corresponding to channel 200 or 937.5000 MHz, into each of the frequency slots. The channel numbers are stored as a 16-bit word in little endian format. Endian swapping the default channel value results in a value of 0x9B08, which converts to a decimal value of 39688. The decimal channel value can be determined by subtracting the target frequency from 937.5000 MHz and then dividing by the channel frequency step size of 0.0125 MHz. The resulting value is then subtracted from a value of 38923, converted back to hexadecimal and then endian swapped into little endian format before storing the frequency. This is apparently what the Kenwood3.exe program does (except that the conversion to decimal and endian swapping is not required in programming since little endian is the native format for x86 processors).XXXI. Launch the HxD.exe program.XXXII. Open the KPG25D data file with the HxD program.XXXIII. Locate each frequency entry with a value of 0x089B and edit the value to the appropriate value obtained from the Kenwood3.exe program. The Grp-Name field data will be visible in the window and will help to locate the 0x089B value associated with a specific group name..XXXIV. Save the file and exit the Kenwood3.exe program.XXXV. Launch the KPG25D.exe program.XXXVI. Load the KPG25D data file.XXXVII. A view of the Feature option window will show the new channel data.XXXVIII. Program the radio.Filter InstallationTwo TK-941 radios are used to implement the full-duplex link back-bone, with one radio acting as the transmitter and the other radio acting as the receiver. The front-end filter on the receive radio must be swapped out with a filter that has the bandpass frequency having the receive frequency fall within the bandpass.A hot air SMD station was used to remove the pair of filters from the TK-941 receive radio front-end. 915 MHz filters were then installed using a standard soldering station. Note that the filter terminals did not align with the solder pads on the printed circuit board. The terminals had to be bent in to contact the pads prior to soldering. A check was made, using an Ohm meter, to verify that the terminals did not short to the ground traces surrounding the filter terminal pads.Upon completion of the filter installation, the VCO was adjusted to obtain VCO lock.Repeater Controller Interface - Receive RadioThe repeater controller interface requires access to the COS signal and de-emphasized audio. The signal driving the BASE of Q20 presents an Active LOW COS. Further, the COS signal carries only the COS when programmed for COS access or the logical NAND of COS and Tone Decode when programmed for tone or DCS access. The observed logic level on the COS signal shows 3.6 volts when HIGH.Squelch gated de-emphasized audio is available at the junction of C75 and IC6-13. The signal level of the audio, using a 1KHz tone with 3KHz deviation (as used for a -12 dB SINAD measurement), was observed to be 1.2 Vpp.The following annotated PCB view shows where to connect the COS and Gated Audio signals to interface to the repeater controller.The following image shows the repeater controller interface wires attached to the receive radio. The COS wire is blue. The squelch gated de-emphasized audio is orange. A black ground connection is made at emitter of Q20. A Dremel tool was used to grind a small slot to route the cable out of the RF shielded area where the interface signals are available. A Hot Glue gun was used to fasten down the wires, providing strain relief for the PCB pad connections.The power cable chassis strain relief can be lifted, exposing a small but removable plug. Removing this plug allows for routing of the repeater controller interface wires out of the radio chassis.Repeater Controller Interface - Transmit RadioThe transmit radio requires access to the PTT and Microphone input signals. The front panel was removed in preparation to route wires from under the power cable and on to through the chassis to the front panel PCB.The attachment points on the back of the front panel PCB are well marked as follows:1. PTT: Push-to-talk (Green Wire)2. ME: Microphone Return (audio-signal-ground - Black Wire)3. MI: Microphone Input (Red Wire)。

MAX14878-MAX14880 高速传输接收器的中文名字说明书