A Solution Type Indexed Serialization Combinators in Standard ML

PV Link

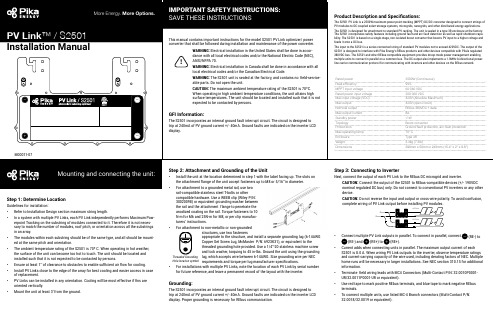

Step 1: Determine LocationGuidelines for installation:• Refer to Installation Design section maximum string length.• In a system with multiple PV Links, each PV Link independently performs Maximum Pow-erpoint Tracking on the substring of modules connected to it. Therefore it is not neces-sary to match the number of modules, roof pitch, or orientation across all the substrings in an array.• The modules within each substring should be of the same type, and all should be mount-ed at the same pitch and orientation.• The ambient temperature rating of the S2501 is 70º C. When operating in hot weather,the surface of the unit can become too hot to touch. The unit should be located and installed such that it is not expected to be contacted by persons.• Ensure at least 1” of clearance to obstacles to enable sufficient air flow for cooling.• Install PV Links close to the edge of the array for best cooling and easier access in caseof replacement.• PV Links can be installed in any orientation. Cooling will be most effective if fins areoriented vertically.• Mount the unit at least 3’ from the ground.rail-compatible stainless steel T-bolts or other compatible hardware. Use a WEEB clip (Wiley P/N: 30020098) or equivalent grounding washer between the rail and the attachment flange to penetrate the anodized coating on the rail. Torque fasteners to 10 N-m for M6 and 25N-m for M8, or per clip manufac-turers’ instructions.• For attachment to non-metallic or non-groundedstructures, use two fastenersappropriate to the structure, and install a separate grounding lug (6-14AWG Copper Set Screw Lug, McMaster P/N: 6923K31), or equivalent to the threaded grounding hole provided. Use a 1/4”-20 stainless machine screw and lock washer, torquing to 45 in-lbs. Ground the unit using the groundinglug, which accepts wire between 6-14AWG. Size grounding wire per NEC requirements and torque per lug manufacturer specifications.• For installations with multiple PV Links, note the location of each PV Link by serial numberfor future reference, and leave a permanent record of the layout with the inverter.Grounding:The S2501 incorporates an internal ground fault interrupt circuit. The circuit is designed to trip at 240mA of PV ground current +/- 40mA. Ground faults are indicated on the inverter LCD display. Proper grounding is necessary for REbus communication.device.CAUTION: Do not reverse the input and output or cross-wire polarity. To avoid confusion, complete wiring of PV Link output before installing PV modules.• Connect multiple PV Link outputs in parallel. To connect in parallel, connect (RE-) to (RE-) and (RE+) to (RE+).•Current adds when connecting units in parallel. The maximum output current of each S2501 is 8.0 A. When wiring PV Link outputs to the inverter, observe temperature ratings and current-carrying capacity of the wire used, including derating factors of NEC. Multiple home runs will be necessary in larger installations. See NEC section 310.15 for additional information.• Terminate field wiring leads with MC4 Connectors (Multi-Contact P/N: 32.0010P0001-UR/32.0011P0001-UR or equivalent).• Use red tape to mark positive REbus terminals, and blue tape to mark negative REbus terminals.•To connect multiple units, use listed MC-4 Branch connectors (Multi-Contact P/N:32.0018/32.0019 or equivalent).Threaded Grounding Hole location symbol REbus380VDC OUTPUTPVSUBSTRIN INPUTWARNING: ELECTRIC SHOCK HAZARD - THE DC CONDUCTORS OF THISPHOTOVOL TAIC SYSTEM ARE UNGROUNDED AND MAY BE ENERGIZED. ELECTRIC SHOCKHAZARD - DC OUTPUT CONDUCTORS MAY BE ENERGIZED REGARDLESS OF SUN EXPOSURE.CAUTION: RISK OF ELECTRIC SHOCK - WHEN THE PHOTOVOL TAIC ARRAY ISEXPOSED TO LIGHT, IT SUPPLIES A DC VOL TAGE TO EQUIPMENT. COVER PV MODULE INOPAQUE MATERIAL BEFORE CONNECTING OR DISCONNECTING THIS OPTIMIZER. DURING FAUL T, ZERO CURRENT IS SOURCED INTO DC ARRAY BY THIS CONVERTER. INSTALL IN。

芬士多(Festo Multi)型号为2GEx h IIC T4 Gb X的气体传输系统说明书

Translation of the original instructions 1Identification EXTab. 1 2Further applicable documentsTechnical data for the product can have different values in other documents. For operation in an explosive atmosphere, the technical data in this document alwayshave priority.All available documents for the product è /pk.3FunctionWhen the compressed air supply ports are pressurized reciprocally, the internal slide in the pipe moves back and forth. The movement is transferred to the external slide by a rigid connection.4Safety 4.1Safety instructions–The device can be used under the stated operating conditions in zone 1 ofexplosive gas atmospheres.–All work must be carried out outside of potentially explosive areas.–Extraction of the operating medium outside the potentially explosive area.–The device is not intended for use with other fluids.4.2Intended useThe pneumatic linear drive is intended for the transportation of loads.4.3Identification X: special conditions –Danger of electrostatic discharge.–Ambient temperature: –10°C £ T a £ +60°C 5CommissioningThe discharge of electrostatically charged parts can lead to ignitable sparks. •Prevent electrostatic charging by taking appropriate installation and cleaningmeasures.•Include the device in the system’s potential equalisation.•The slide is electrically insulated from the actuator. Include the slide separately in the system potential equalisation.Installation and commissioning may only be performed in accordance with the operating instructions and by qualified personnel.Strong chargegenerating processes can charge nonconductive layers and coatings on metal surfaces.Escaping exhaust air can swirl up dust and create an explosive dust atmosphere.Related type of ignition protection: c (constructional safety)Particulate matter in the compressed air can cause electrostatic charges.–Observe the product labelling.–Seal unused openings with blanking plugs or slot covers.When using PPV endposition cushioning or shock absorbers:–Adjust the cushioning so that the piston rod safely reaches the end positionsand that it does not strike hard against them or rebound.–Only load the shock absorber in the axial direction. Avoid the generation oftransverse loads.6Maintenance and care–Check the operational reliability of the device regularly. Interval: 2 million movement cycles or after 6 months at the latest.–Clean the device with a damp cloth.–Lubricate the guide at the lubrication nipples in intervals. Interval: 400 km –Roller bearing cartridges of guide systems of the DGPL...KF und DGPL...HDafter a distance of 4500 km.Repairs of this type must only be carried out by trained and authorised specialists.–Please contact your Festo technical consultant.7Fault clearanceTab. 2 8Technical dataOperating conditionsMax. operating pressure [bar]8Ambient temperature [°C]–10 … +60Operating medium Compressed air to ISO 85731:2010 [7:4:4]Mounting position AnyDesignDoubleacting, with magnetic coupling, without piston rodTab. 38102472DGPL-...-EX3-...Linear drive8102472201811c [8102474]Festo SE & Co. KG Ruiter Straße 82 73734 Esslingen Germany+49 711 347。

SequenceManager Logix Controller-based Batch和排队解决方

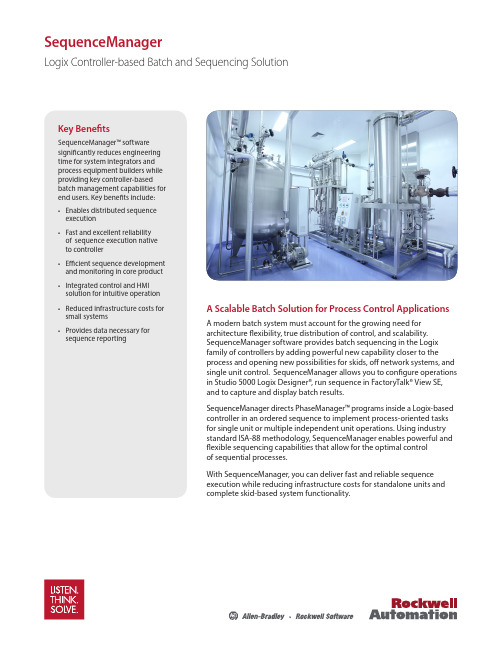

SequenceManagerLogix Controller-based Batch and Sequencing SolutionA Scalable Batch Solution for Process Control ApplicationsA modern batch system must account for the growing need for architecture flexibility, true distribution of control, and scalability. SequenceManager software provides batch sequencing in the Logix family of controllers by adding powerful new capability closer to the process and opening new possibilities for skids, off network systems, and single unit control. SequenceManager allows you to configure operations in Studio 5000 Logix Designer®, run sequence in FactoryTalk® View SE, and to capture and display batch results.SequenceManager directs PhaseManager™ programs inside a Logix-based controller in an ordered sequence to implement process-oriented tasks for single unit or multiple independent unit operations. Using industry standard ISA-88 methodology, SequenceManager enables powerful and flexible sequencing capabilities that allow for the optimal control of sequential processes.With SequenceManager, you can deliver fast and reliable sequence execution while reducing infrastructure costs for standalone units and complete skid-based system functionality.Key BenefitsSequenceManager™ software significantly reduces engineering time for system integrators and process equipment builders while providing key controller-based batch management capabilities for end users. Key benefits include:• Enables distributed sequence execution • Fast and excellent reliability of sequence execution native to controller • Efficient sequence development and monitoring in core product • Integrated control and HMI solution for intuitive operation • Reduced infrastructure costs for small systems • Provides data necessary for sequence reportingDistributed Batch Management Based on Proven TechnologyBuilt Upon Rockwell AutomationIntegrated ArchitectureSequenceManager was built using the standard control and visualization capabilities found in Rockwell Automation® Integrated Architecture® software. SequenceManager is a new capability that is builtinto Logix firmware that uses visualization through FactoryTalk® View SE to create an integrated sequencing solution. Combined with event and reporting tools, SequenceManager software is a complete batch solution for single unit and skid-based process applications.Scalable Controller-based Solution SequenceManager allows flexible design for skid-based equipment to be developed, tested and delivered asa fully functioning standalone solution but, if needed, seamlessly integrated into a larger control system. This strategy provides the end user with the option to integrate equipment without imposing design constraints on the OEM delivering the skid. Additionally, it enables the end user to deliver equipment as a standalone system without the constraint to scale to a larger process solution in the future. This batch solution offers scalability to help prevent costly redesign and engineering.Flexibility to Meet Process Needs SequenceManager enables you to expand your process control on skid based equipment that performs repetitive tasks and decision-making abilities. By using the ISA-88 methodology, SequenceManager allows for control design that can be adopted to fit the needs of the process industries without the constraints of custom application code. Built-in state model handling provides for fast and easy configuration while maintainingcontrol of the process.Editor and ViewerAs a brand new program type in Studio 5000 Logix Designer®, SequenceManager™ software gives the user the power and flexibility necessary to create dynamic recipes to maximize the effectiveness of the process control system.Without limitations on steps and parameters, and the ability to run parallel phases, to branch, and to loop back and rerun steps, SequenceManager removes the barriers in achieving effective batch within the controller.Sequence ExecutionProcedural sequences are executed through nativefunctions in the controller. With an integrated ISA-88 state model, the control and states of phases can be assured. Standard batch functionality, such as manual control and active step changes, are included to give the operational flexibility that is needed to respond toabnormal process conditions.Allowing for an Intuitive Batch ApplicationResponsive batch interactions between the controller and equipment, along with intuitive operator interfaces, provide the core of a truly distributed batching strategy that drives ISA-88 procedural models.Allen-Bradley, FactoryTalk Batch, FactoryTalk® View SE, Integrated Architecture, Listen.Think.Solve., PhaseManager, PlantPAx, Rockwell Automation, Rockwell Software, SequenceManager, and Studio 5000 Logix Designer are trademarks of Rockwell Automation, Inc. Trademarks not belonging to Rockwell Automation are property of their respective companies.Operator ViewerFactoryTalk® View SE and ActiveX controls monitor and interact with a running procedural sequence through the HMI. Advance ActiveX controls provide an intuitive interface for controlling sequences and changingparameters from the operational environment. Improved capabilities allow the user to perform manual step changes and acquire control easily.Reporting and AnalyticsSequenceManager data generates events that are used to produce batch reports and procedural analysis. A separate event client transfers the event data from the Logixcontroller to a historical database. SequenceManager uses the same data structure and reports as FactoryTalk Batch, which provides a consistent and intuitive batch reporting tool among Rockwell Automation® Batch Solutions.Additional InformationVisit us at /processPublication PROCES-PP001A-EN-E – June 2016Copyright © 2016 Rockwell Automation, Inc. All Rights Reserved. Printed in USA.。

未标记为可序列化

未标记为可序列化简介序列化是指将对象实例的状态存储到存储媒体的过程。

在此过程中,先将对象的公共字段和私有字段以及类的名称(包括类所在的程序集)转换为字节流,然后再把字节流写入数据流。

在随后对对象进行反序列化时,将创建出与原对象完全相同的副本。

在面向对象的环境中实现序列化机制时,必须在易用性和灵活性之间进行一些权衡。

只要您对此过程有足够的控制能力,就可以使该过程在很大程度上自动进行。

例如,简单的二进制序列化不能满足需要,或者,由于特定原因需要确定类中那些字段需要序列化。

以下各部分将探讨.NET 框架提供的可靠的序列化机制,并着重介绍使您可以根据需要自定义序列化过程的一些重要功能。

持久存储我们经常需要将对象的字段值保存到磁盘中,并在以后检索此数据。

尽管不使用序列化也能完成这项工作,但这种方法通常很繁琐而且容易出错,并且在需要跟踪对象的层次结构时,会变得越来越复杂。

可以想象一下编写包含大量对象的大型业务应用程序的情形,程序员不得不为每一个对象编写代码,以便将字段和属性保存至磁盘以及从磁盘还原这些字段和属性。

序列化提供了轻松实现这个目标的快捷方法。

公共语言运行时(CLR) 管理对象在内存中的分布,.NET 框架则通过使用反射提供自动的序列化机制。

对象序列化后,类的名称、程序集以及类实例的所有数据成员均被写入存储媒体中。

对象通常用成员变量来存储对其他实例的引用。

类序列化后,序列化引擎将跟踪所有已序列化的引用对象,以确保同一对象不被序列化多次。

.NET 框架所提供的序列化体系结构可以自动正确处理对象图表和循环引用。

对对象图表的唯一要求是,由正在进行序列化的对象所引用的所有对象都必须标记为Ref="tag-863-1.html">Serializable(请参阅基本序列化)。

否则,当序列化程序试图序列化未标记的对象时将会出现异常。

当反序列化已序列化的类时,将重新创建该类,并自动还原所有数据成员的值。

AssayMAP Bravo平台的使用说明书

This guide is intended for users who have been trained in the proper use of the AssayMAP Bravo Platform and understand the safety guidelines in the Bravo Platform Safety and Installation Guide. The procedures in this guide require the Protein Sample Prep Workbench and VWorks Automation Control software. See the user guide to verify the required software versions.Step 1. Design the Normalizationmethod Open the Normalization Method Setup T ool v2.0and follow the instructions on the screen to design and save a normalization method.To open the Normalization Method Setup Tool, locate the Normalization v2.0 banner in the Utility Library, and then click Method Setup T ool. Follow the instructions on the screen to design and save a method file.For in-depth assay development guidelines, see the Normalization v2.0 User Guide in the Literature Library of the Protein Sample Prep Workbench.A small sample and reagent volume excess is required in all labware types to ensure proper volume transfer. The Normalization Method Setup Tool automatically indicates the amount of excess volume recommended per plate type but this volume can be changed by the user.Step 2. Prepare Sample and Diluentplates Prepare the Sample plate to match the initial sample volumes and well positions specified in the method that you created in the Normalization Method Setup Tool. Prepare the Diluent plate by putting the volume calculated by the Normalization Method Setup Tool in position A12, as this is where all the diluent will be aspirated. To minimize evaporation, fill the Sample and Diluent plates immediately before run time or keep them covered until you run the protocol.Step 3. Prepare thesystem T o prepare the system:1Check the levels of the wash station source and waste carboys, and fill or empty as required.2If you have not already done so, turn on the AssayMAP Bravo Platform and accessories, and start the Protein Sample Prep Workbench.3Open the Utility Library, and then open the System Startup/Shutdown utility .AssayMAP Protein Sample Prep Workbench Normalization v2.0 Quick Start GuideStep 4. Run the utility4Click Run Startup to prepare the system for the run.The Bravo head and tie bar will move during the Bravo Startup protocol. To preventinjury, keep clear of the device while it is in motion.5During the Startup protocol, verify that all the wash station chimneys have liquidflowing through them. If liquid is not flowing through the chimneys, see the96 Channel Wash Station Maintenance Guide for troubleshooting guidelines.Step 4. Run theutility T o run the Normalization utility:1Open the Normalization utility.2Under Select and Load a Normalization Method, click and select the method.The default method storage location is C:/VWorks Workspace/Methods/AM Normalization Utility v2.0.3Click Display Bravo Layout to display the Method Loaded and the Deck Layout information.The probes of the Bravo 96AM Head are sharp and can scratch you if they brush across your hand. A probe scratch can expose you to any contaminants remaining on the probes. Be careful to avoid touching the probes.4Ensure that the following items are securely in place at their respective AssayMAP Bravo deck locations:•Bravo Plate Riser at deck locations 2 and 6.• A tip box full of fresh 250-µL pipette tips at deck location 3.•The empty 96AM Cartridge & Tip Seating Station at deck location 5.To prevent a potential collision, ensure that no thermal plate insert is on the Peltier Thermal Station installed at deck location 4.5Place the filled reagent plates at the assigned deck locations, as shown in the Deck Layout of the form.Improperly seated labware can cause a hardware collision, resulting in equipment damage. Ensure that all labware are properly seated within the alignment features of their respective platepads.6Ensure that all the labware on the deck exactly matches the Deck Layout in the form.Incorrect labware selections can cause a hardware collision, resulting in equipment damage. Ensure that the selections in the method exactly match the physical labware present on the Bravo deck.7Click Run Protocol to start the run.Step 5. Clean up after each run T o clean up after the run:1Remove used labware from the deck.2Discard the used pipette tips from the tip box at deck location 3.Step 6. Shut down at end of day3Transfer the unused pipette tips from the 96AM Cartridge & Tip Seating Station at deck location 5 to unused locations in the tip box.4Remove the Bravo Plate Risers from deck locations 2 and 6.5Discard any leftover reagents appropriately.6Optional. To conduct stringent washing of the syringes, run the Syringe Wash utility.Step 6. Shut down at end of day T o shut down at the end of the day:1Open the System Startup/Shutdown utility .2Remove everything from the deck except the 96AM Wash Station (deck location 1).3Place the 96AM Cartridge & Tip Seating Station at deck location 2, and then click Run Shutdown . 4After the Shutdown protocol has completed, turn off the power at the AssayMAP Bravo Platform and the accessories.5Close the Protein Sample Prep Workbench software.Utility overview The following figure shows the utility interface, and the following table provides anoverview of the basic movements of the AssayMAP Bravo Platform during theNormalization protocol.Table Automation movements during the protocolContactingAgilent Technologies Web: https://Contact page: https:///en/contact-us/page Documentation feedback: ************************************ProtocolprocessProcess name Process description1Syringe Wash Performs 1 external syringe wash at the wash station (decklocation 1).2Syringe Drying Performs 4 syringe aspirate-and-dispense cycles above the washstation (deck location 1) to cycle air in and out of the syringes. Thesyringes move over the chimneys after each cycle to remove anydroplets that were pushed out of the syringes during the cycle.3Initial Tip Transfer Transfers all 96 250-µL pipette tips from the tip box (deck location 3) tothe 96AM Cartridge & Tip Seating Station (deck location 5).4Single Tip Pickup Picks up the next available individual pipette tip from the 96AMCartridge & Tip Seating Station (deck location 5) using probe A12 ofthe Bravo 96AM Head.5Diluent Transfer Aspirates diluent (deck location 4, well A12) into the pipette tip, andthen dispenses the diluent into a specific well in the normalized plate(deck location 6).6Sample Transfer Aspirates sample (deck location 2) into the pipette tip, and thendispenses the sample into the same well in the normalized plate (decklocation 6) that was used for the Diluent Transfer process.7Single Tip Eject Ejects the used pipette tip into the tip box (deck location 3).The tip box well location matches the well location of the normalizedsample that the pipette tip was used to prepare.8Additional Transfers Repeats processes 2 through 5 for every sample in the sample plate(deck location 2).9Used Tip Pickup Presses on all the used pipette tips from the tip box (deck location 3).10Mixing Mixes all the samples in the normalized plate (deck location 6).11Final Tip Ejection Ejects the used pipette tips into the tip box (deck location 3).。

基于表面增强拉曼光谱的巴旦木氧化程度快速检测

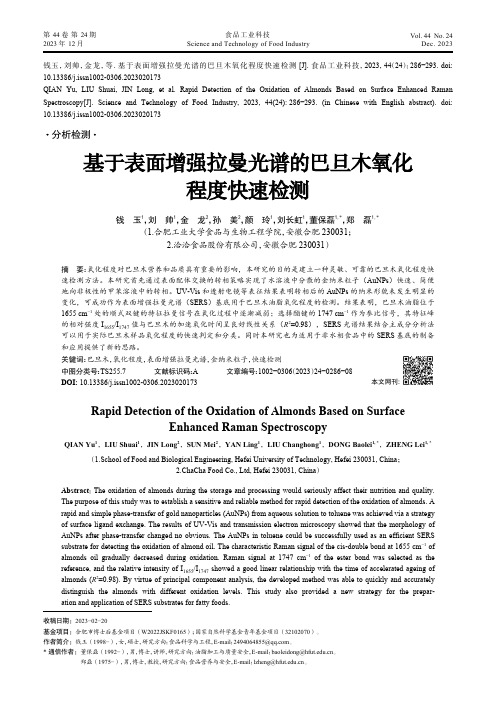

钱玉,刘帅,金龙,等. 基于表面增强拉曼光谱的巴旦木氧化程度快速检测[J]. 食品工业科技,2023,44(24):286−293. doi:10.13386/j.issn1002-0306.2023020173QIAN Yu, LIU Shuai, JIN Long, et al. Rapid Detection of the Oxidation of Almonds Based on Surface Enhanced Raman Spectroscopy[J]. Science and Technology of Food Industry, 2023, 44(24): 286−293. (in Chinese with English abstract). doi:10.13386/j.issn1002-0306.2023020173· 分析检测 ·基于表面增强拉曼光谱的巴旦木氧化程度快速检测钱 玉1,刘 帅1,金 龙2,孙 美2,颜 玲1,刘长虹1,董保磊1, *,郑 磊1,*(1.合肥工业大学食品与生物工程学院,安徽合肥 230031;2.洽洽食品股份有限公司,安徽合肥 230031)摘 要:氧化程度对巴旦木营养和品质具有重要的影响,本研究的目的是建立一种灵敏、可靠的巴旦木氧化程度快速检测方法。

本研究首先通过表面配体交换的转相策略实现了水溶液中分散的金纳米粒子(AuNPs )快速、简便地向非极性的甲苯溶液中的转相。

UV-Vis 和透射电镜等表征结果表明转相后的AuNPs 的纳米形貌未发生明显的变化,可成功作为表面增强拉曼光谱(SERS )基底用于巴旦木油脂氧化程度的检测。

结果表明,巴旦木油脂位于1655 cm −1处的顺式双键的特征拉曼信号在氧化过程中逐渐减弱;选择酯键的1747 cm −1作为参比信号,其特征峰的相对强度I 1655/I 1747值与巴旦木的加速氧化时间呈良好线性关系(R 2=0.98),SERS 光谱结果结合主成分分析法可以用于实际巴旦木样品氧化程度的快速判定和分类。

Redis使用redis存储对象反序列化异常SerializationFailedExce。。。

Redis使⽤redis存储对象反序列化异常SerializationFailedExce。

案例使⽤Redis进⾏对象存储,在处理业务逻辑的时候,丛Redis获取对象发现反序列化失败,抛出如下异常:Caused by: org.springframework.data.redis.serializer.SerializationException: Cannot deserialize; nested exception is org.springframework.core.serializer.support.SerializationFailedException: Failed to deserialize payload. Is the byte array a result of correspon at org.springframework.data.redis.serializer.JdkSerializationRedisSerializer.deserialize(JdkSerializationRedisSerializer.java:82)at org.springframework.data.redis.core.AbstractOperations.deserializeValue(AbstractOperations.java:318)at org.springframework.data.redis.core.AbstractOperations$ValueDeserializingRedisCallback.doInRedis(AbstractOperations.java:58)at org.springframework.data.redis.core.RedisTemplate.execute(RedisTemplate.java:207)at org.springframework.data.redis.core.RedisTemplate.execute(RedisTemplate.java:169)at org.springframework.data.redis.core.AbstractOperations.execute(AbstractOperations.java:91)at org.springframework.data.redis.core.DefaultValueOperations.get(DefaultValueOperations.java:43)at com.ppmoney.geedai.wechat.service.wechat.impl.GetAccessTokenServiceImpl.get(GetAccessTokenServiceImpl.java:37)at com.ppmoney.geedai.wechat.service.wechat.impl.CustomMsgServiceImpl.send(CustomMsgServiceImpl.java:32)... 82 common frames omittedCaused by: org.springframework.core.serializer.support.SerializationFailedException: Failed to deserialize payload. Is the byte array a result of corresponding serialization for DefaultDeserializer?; nested exception is java.io.InvalidClassException: weixin.popu at org.springframework.core.serializer.support.DeserializingConverter.convert(DeserializingConverter.java:78)at org.springframework.core.serializer.support.DeserializingConverter.convert(DeserializingConverter.java:36)at org.springframework.data.redis.serializer.JdkSerializationRedisSerializer.deserialize(JdkSerializationRedisSerializer.java:80)... 90 common frames omittedCaused by: java.io.InvalidClassException: weixin.popular.bean.token.Token; local class incompatible: stream classdesc serialVersionUID = -584152862903853930, local class serialVersionUID = 8841433872811285796at java.io.ObjectStreamClass.initNonProxy(ObjectStreamClass.java:616)at java.io.ObjectInputStream.readNonProxyDesc(ObjectInputStream.java:1623)at java.io.ObjectInputStream.readClassDesc(ObjectInputStream.java:1518)at java.io.ObjectInputStream.readOrdinaryObject(ObjectInputStream.java:1774)at java.io.ObjectInputStream.readObject0(ObjectInputStream.java:1351)at java.io.ObjectInputStream.readObject(ObjectInputStream.java:371)at org.springframework.core.serializer.DefaultDeserializer.deserialize(DefaultDeserializer.java:70)at org.springframework.core.serializer.support.DeserializingConverter.convert(DeserializingConverter.java:73)... 92 common frames omitted解决⽅案经排查,原因是存放的对象忘了添加序列化号,导致存储的序列化编号和反序列化编号不⼀致,所以反序列化异常。

JVM for a Heterogeneous Shared Memory System

JVM for a Heterogeneous Shared Memory SystemDeQing Chen,Chunqiang Tang,Sandhya Dwarkadas,and Michael L.ScottComputer Science Department,University of Rochester AbstractInterWeave is a middleware system that supports the shar-ing of strongly typed data structures across heterogeneouslanguages and machine architectures.Java presents spe-cial challenges for InterWeave,including write detection,data translation,and the interface with the garbage col-lector.In this paper,we discuss our implementation ofJ-InterWeave,a JVM based on the Kaffe virtual machineand on our locally developed InterWeave client software.J-InterWeave uses bytecode instrumentation to detectwrites to shared objects,and leverages Kaffe’s class ob-jects to generate type information for correct transla-tion between the local object format and the machine-independent InterWeave wire format.Experiments in-dicate that our bytecode instrumentation imposes lessthan2%performance cost in Kaffe interpretation mode,and less than10%overhead in JIT mode.Moreover,J-InterWeave’s translation between local and wire format ismore than8times as fast as the implementation of ob-ject serialization in Sun JDK1.3.1for double arrays.Toillustrate theflexibility and efficiency of J-InterWeave inpractice,we discuss its use for remote visualization andsteering of a stellar dynamics simulation system writtenin C.1IntroductionMany recent projects have sought to support distributedshared memory in Java[3,16,24,32,38,41].Manyof these projects seek to enhance Java’s usefulness forlarge-scale parallel programs,and thus to compete withmore traditional languages such as C and Fortran in thearea of scientific computing.All assume that applicationcode will be written entirely in Java.Many—particularlythose based on existing software distributed shared mem-ory(S-DSM)systems—assume that all code will run oninstances of a common JVM.has yet to displace Fortran for scientific computing sug-gests that Java will be unlikely to do so soon.Even for systems written entirely in Java,it is appealing to be able to share objects across heterogeneous JVMs. This is possible,of course,using RMI and object serial-ization,but the resulting performance is poor[6].The ability to share state across different languages and heterogeneous platforms can also help build scalable dis-tributed services in general.Previous research on var-ious RPC(remote procedure call)systems[21,29]in-dicate that caching at the client side is an efficient way to improve service scalability.However,in those sys-tems,caching is mostly implemented in an ad-hoc man-ner,lacking a generalized translation semantics and co-herence model.Our on-going research project,InterWeave[9,37],aims to facilitate state sharing among distributed programs written in multiple languages(Java among them)and run-ning on heterogeneous machine architectures.InterWeave applications share strongly-typed data structures located in InterWeave segments.Data in a segment is defined using a machine and platform-independent interface de-scription language(IDL),and can be mapped into the ap-plication’s local memory assuming proper InterWeave li-brary calls.Once mapped,the data can be accessed as ordinary local objects.In this paper,we focus on the implementation of In-terWeave support in a Java Virtual Machine.We call our system J-InterWeave.The implementation is based on an existing implementation of InterWeave for C,and on the Kaffe virtual machine,version1.0.6[27].Our decision to implement InterWeave support directly in the JVM clearly reduces the generality of our work.A more portable approach would implement InterWeave support for segment management and wire-format trans-lation in Java libraries.This portability would come,how-ever,at what we consider an unacceptable price in perfor-mance.Because InterWeave employs a clearly defined internal wire format and communication protocol,it is at least possible in principle for support to be incorporated into other JVMs.We review related work in Java distributed shared state in Section2and provide a brief overview of the Inter-Weave system in Section3.A more detailed description is available elsewhere[8,37].Section4describes the J-InterWeave implementation.Section5presents the results of performance experiments,and describes the use of J-InterWeave for remote visualization and steering.Sec-tion6summarizes our results and suggests topics for fu-ture research.2Related WorkMany recent projects have sought to provide distributed data sharing in Java,either by building customized JVMs[2,3,24,38,41];by using pure Java implementa-tions(some of them with compiler support)[10,16,32]; or by using Java RMI[7,10,15,28].However,in all of these projects,sharing is limited to Java applications. To communicate with applications on heterogeneous plat-forms,today’s Java programmers can use network sock-ets,files,or RPC-like systems such as CORBA[39].What they lack is a general solution for distributed shared state. Breg and Polychronopoulos[6]have developed an al-ternative object serialization implementation in native code,which they show to be as much as eight times faster than the standard implementation.The direct compari-son between their results and ours is difficult.Our exper-iments suggest that J-Interweave is at least equally fast in the worst case scenario,in which an entire object is mod-ified.In cases where only part of an object is modified, InterWeave’s translation cost and communication band-width scale down proportionally,and can be expected to produce a significant performance advantage.Jaguar[40]modifies the JVM’s JIT(just-in-time com-piler)to map certain bytecode sequences directly to na-tive machine codes and shows that such bytecode rewrit-ing can improve the performance of object serialization. However the benefit is limited to certain types of objects and comes with an increasing price for accessing object fields.MOSS[12]facilitates the monitoring and steering of scientific applications with a CORBA-based distributed object system.InterWeave instead allows an application and its steerer to share their common state directly,and in-tegrates that sharing with the more tightly coupled sharing available in SMP clusters.Platform and language heterogeneity can be supported on virtual machine-based systems such as Sun JVM[23] and [25].The Common Language Run-time[20](CLR)under framework promises sup-port for multi-language application development.In com-parison to CLR,InterWeave’s goal is relatively modest: we map strongly typed state across languages.CLR seeks to map all high-level language features to a common type system and intermediate language,which in turn implies more semantic compromises for specific languages than are required with InterWeave.The transfer of abstract data structures wasfirst pro-posed by Herlihy and Liskov[17].Shasta[31]rewrites bi-nary code with instrumentation for access checks forfine-grained S-DSM.Midway[4]relies on compiler support to instrument writes to shared data items,much as we do in the J-InterWeave JVM.Various software shared memory systems[4,19,30]have been designed to explicitly asso-ciate synchronization operations with the shared data they protect in order to reduce coherence costs.Mermaid[42] and Agora[5]support data sharing across heterogeneous platforms,but only for restricted data types.3InterWeave OverviewIn this section,we provide a brief introduction to the design and implementation of InterWeave.A more de-tailed description can be found in an earlier paper[8]. For programs written in C,InterWeave is currently avail-able on a variety of Unix platforms and on Windows NT. J-InterWeave is a compatible implementation of the In-terWeave programming model,built on the Kaffe JVM. J-InterWeave allows a Java program to share data across heterogeneous architectures,and with programs in C and Fortran.The InterWeave programming model assumes a dis-tributed collection of servers and clients.Servers maintain persistent copies of InterWeave segments,and coordinate sharing of those segments by clients.To avail themselves of this support,clients must be linked with a special In-terWeave library,which serves to map a cached copy of needed segments into local memory.The servers are the same regardless of the programming language used by clients,but the client libraries may be different for differ-ent programming languages.In this paper we will focus on the client side.In the subsections below we describe the application programming interface for InterWeave programs written in Java.3.1Data Allocation and AddressingThe unit of sharing in InterWeave is a self-descriptive data segment within which programs allocate strongly typed blocks of memory.A block is a contiguous section of memory allocated in a segment.Every segment is specified by an Internet URL and managed by an InterWeave server running at the host indi-cated in the URL.Different segments may be managed by different servers.The blocks within a segment are num-bered and optionally named.By concatenating the seg-ment URL with a block number/name and offset(delim-ited by pound signs),we obtain a machine-independent pointer(MIP):“/path#block#offset”. To create and initialize a segment in Java,one can ex-ecute the following calls,each of which is elaborated on below or in the following subsections:IWSegment seg=new IWSegment(url);seg.wl_acquire();MyType myobj=new MyType(seg,blkname);myobj.field=......seg.wl_release();In Java,an InterWeave segment is captured as an IWSegment object.Assuming appropriate access rights, the new operation of the IWSegment object communi-cates with the appropriate server to initialize an empty segment.Blocks are allocated and modified after acquir-ing a write lock on the segment,described in more detail in Section3.3.The IWSegment object returned can be passed to the constructor of a particular block class to al-locate a block of that particular type in the segment. Once a segment is initialized,a process can convert be-tween the MIP of a particular data item in the segment and its local pointer by using mip ptr and ptr mip where appropriate.It should be emphasized that mip ptr is primar-ily a bootstrapping mechanism.Once a process has one pointer into a data structure(e.g.the root pointer in a lat-tice structure),any data reachable from that pointer can be directly accessed in the same way as local data,even if embedded pointers refer to data in other segments.In-terWeave’s pointer-swizzling and data-conversion mech-anisms ensure that such pointers will be valid local ma-chine addresses or references.It remains the program-mer’s responsibility to ensure that segments are accessed only under the protection of reader-writer locks.3.2HeterogeneityTo accommodate a variety of machine architectures,In-terWeave requires the programmer to use a language-and machine-independent notation(specifically,Sun’s XDR[36])to describe the data types inside an InterWeave segment.The InterWeave XDR compiler then translates this notation into type declarations and descriptors appro-priate to a particular programming language.When pro-gramming in C,the InterWeave XDR compiler generates twofiles:a.hfile containing type declarations and a.c file containing type descriptors.For Java,we generate a set of Java class declarationfiles.The type declarations generated by the XDR compiler are used by the programmer when writing the application. The type descriptors allow the InterWeave library to un-derstand the structure of types and to translate correctly between local and wire-format representations.The lo-cal representation is whatever the compiler normally em-ploys.In C,it takes the form of a pre-initialized data struc-ture;in Java,it is a class object.3.2.1Type Descriptors for JavaA special challenge in implementing Java for InterWeave is that the InterWeave XDR compiler needs to gener-ate correct type descriptors and ensure a one-to-one cor-respondence between the generated Java classes and C structures.In many cases mappings are straight forward: an XDR struct is mapped to a class in Java and a struct in C,primitivefields to primitivefields both in Java andC,pointersfields to object references in Java and pointers in C,and primitive arrays to primitive arrays. However,certain“semantics gaps”between Java and C force us to make some compromises.For example,a C pointer can point to any place inside a data block;while Java prohibits such liberties for any object reference. Thus,in our current design,we make the following compromises:An InterWeave block of a single primitive data item is translated into the corresponding wrapped class for the primitive type in Java(such as Integer,Float, etc.).Embedded structfields in an XDR struct definition areflattened out in Java and mapped asfields in its parent class.In C,they are translated naturally into embeddedfields.Array types are mapped into a wrapped IWObject(including the IWacquire,wl acquire, and rlpublic class IWSegment{public IWSegment(String URL,Boolean iscreate);public native staticint RegisterClass(Class type);public native staticObject mip_to_ptr(String mip);public native staticString ptr_to_mip(IWObject Ob-ject obj);......public native int wl_acquire();public native int wl_release();public native int rl_acquire();public native int rl_release();......}Figure2:IWSegment Class4.1.1JNI Library for IWSegment ClassThe native library for the IWSegment class serves as an intermediary between Kaffe and the C InterWeave library. Programmer-visible objects that reside within the IWSeg-ment library are managed in such a way that they look like ordinary Java objects.As in any JNI implementation,each native method has a corresponding C function that implements its function-ality.Most of these C functions simply translate their pa-rameters into C format and call corresponding functions in the C InterWeave API.However,the creation of an In-terWeave object and the method RegisterClass need special explanation.Mapping Blocks to Java Objects Like ordinary Java objects,InterWeave objects in Java are created by“new”operators.In Kaffe,the“new”operator is implemented directly by the bytecode execution engine.We modi-fied this implementation to call an internal function new-Block in the JNI library and newBlock calls the Inter-Weave C library to allocate an InterWeave block from the segment heap instead of the Kaffe object heap.Before returning the allocated block back to the“new”operator, newBlock initializes the block to be manipulated cor-rectly by Kaffe.In Kaffe,each Java object allocated from the Kaffe heap has an object header.This header contains a pointer to the object class and a pointer to its own monitor.Since C InterWeave already assumes that every block has a header (it makes no assumption about the contiguity of separate blocks),we put the Kaffe header at the beginning of what C InterWeave considers the body of the block.A correctly initialized J-InterWeave object is shown in Figure3.Figure3:Block structure in J-InterWeaveAfter returning from newBlock,the Kaffe engine calls the class constructor and executes any user cus-tomized operations.Java Class to C Type Descriptor Before any use of a class in a J-InterWeave segment,including the creation of an InterWeave object of the type,the class object must befirst registered with RegisterClass.Register-Class uses the reflection mechanism provided by the Java runtime system to determine the following informa-tion needed to generate the C type descriptor and passes it to the registration function in the C library.1.type of the block,whether it is a structure,array orpointer.2.total size of the block.3.for structures,the number offields,eachfield’s off-set in the structure,and a pointer to eachfield’s type descriptor.4.for arrays,the number of elements and a pointer tothe element’s type descriptor.5.for pointers,a type descriptor for the pointed-to data.The registered class objects and their corresponding C type descriptors are placed in a hashtable.The new-Block later uses this hashtable to convert a class object into the C type descriptor.The type descriptor is required by the C library to allocate an InterWeave block so that it has the information to translate back and forth between local and wire format(see Section3).4.2KaffeJ-InterWeave requires modifications to the byte code in-terpreter and the JIT compiler to implementfine-grained write detection via instrumentation.It also requires changes to the garbage collector to ensure that InterWeave blocks are not accidentally collected.Figure4:Extended Kaffe object header forfine-grained write detection4.2.1Write DetectionTo support diff-based transmission of InterWeave segment updates,we must identify changes made to InterWeave objects over a given span of time.The current C ver-sion of InterWeave,like most S-DSM systems,uses vir-tual memory traps to identify modified pages,for which it creates pristine copies(twins)that can be compared with the working copy later in order to create a diff.J-InterWeave could use this same technique,but only on machines that implement virtual memory.To enable our code to run on handheld and embedded devices,we pursue an alternative approach,in which we instrument the interpretation of store bytecodes in the JVM and JIT. In our implementation,only writes to InterWeave block objects need be monitored.In each Kaffe header,there is a pointer to the object method dispatch table.On most architectures,pointers are aligned on a word boundary so that the least significant bit is always zero.Thus,we use this bit as theflag for InterWeave objects.We also place two32-bit words just before the Kaffe object header,as shown in Figure4.The second word—modification status—records which parts of the object have been modified.A block’s body is logically divided into32parts,each of which corresponds to one bit in the modification status word.Thefirst extended word is pre-computed when initializing an object.It is the shift value used by the instrumented store bytecode code to quickly determine which bit in the modification status word to set(in other words,the granularity of the write detection).These two words are only needed for In-terWeave blocks,and cause no extra overhead for normal Kaffe objects.4.2.2Garbage CollectionLike distributedfile systems and databases(and unlike systems such as PerDiS[13])InterWeave requires man-ual deletion of data;there is no garbage collection.More-over the semantics of InterWeave segments ensure that an object reference(pointer)in an InterWeave object(block) can never point to a non-InterWeave object.As a result, InterWeave objects should never prevent the collection of unreachable Java objects.To prevent Kaffe from acci-dentally collecting InterWeave memory,we modify the garbage collector to traverse only the Kaffe heap.4.3InterWeave C libraryThe InterWeave C library needs little in the way of changes to be used by J-InterWeave.When an existing segment is mapped into local memory and its blocks are translated from wire format to local format,the library must call functions in the IWSegment native library to initialize the Kaffe object header for each block.When generating a description of modified data in the write lock release operation,the library must inspect the modifi-cation bits in Kaffe headers,rather than creating diffs from the pristine and working copies of the segment’s pages.4.4DiscussionAs Java is supposed to be“Write Once,Run Anywhere”, our design choice of implementing InterWeave support at the virtual machine level can pose the concern of the portability of Java InterWeave applications.Our current implementation requires direct JVM support for the fol-lowing requirements:1.Mapping from InterWeave type descriptors to Javaobject classes.2.Managing local segments and the translation be-tween InterWeave wire format and local Java objects.3.Supporting efficient write detection for objects in In-terWeave segments.We can use class reflection mechanisms along with pure Java libraries for InterWeave memory management and wire-format translation to meet thefirst two require-ments and implement J-InterWeave totally in pure Java. Write detection could be solved using bytecode rewrit-ing techniques as reported in BIT[22],but the resulting system would most likely incur significantly higher over-heads than our current implementation.We didn’t do this mainly because we wanted to leverage the existing C ver-sion of the code and pursue better performance.In J-InterWeave,accesses to mapped InterWeave blocks(objects)by different Java threads on a single VM need to be correctly synchronized via Java object monitors and appropriate InterWeave locks.Since J-InterWeave is not an S-DSM system for Java virtual machines,the Java memory model(JMM)[26]poses no particular problems. 5Performance EvaluationIn this section,we present performance results for the J-InterWeave implementation.All experiments employ a J-InterWeave client running on a1.7GHz Pentium-4Linux machine with768MB of RAM.In experiments involving20406080100120_201_co mp r e s s _202_j e s s _205_ra y t r a c e _209_db _213_j a va c _222_m p e g a u d i o _227_m t r t _228_j a c kJVM98 BenchmarksT i m e (s e c .)Figure 5:Overhead of write-detect instrumentation in Kaffe’s interpreter mode01234567_201_c o mp r e s s _202_j e s s _205_r a y t r a c e _209_d b _213_j a v a c _222_m p e g a u d i o _227_m t r t _228_j a c k JVM98 Benchmarks T i m e (s e c .)Figure 6:Overhead of write-detect instrumentation inKaffe’s JIT3modedata sharing,the InterWeave segment server is running on a 400MHz Sun Ultra-5workstation.5.1Cost of write detectionWe have used SPEC JVM98[33]to quantify the perfor-mance overhead of write detection via bytecode instru-mentation.Specifically,we compare the performance of benchmarks from JVM98(medium configuration)run-ning on top of the unmodified Kaffe system to the per-formance obtained when all objects are treated as if they resided in an InterWeave segment.The results appear in Figures 5and 6.Overall,the performance loss is small.In Kaffe’s inter-preter mode there is less than 2%performance degrada-tion;in JIT3mode,the performance loss is about 9.1%.The difference can be explained by the fact that in inter-preter mode,the per-bytecode execution time is already quite high,so extra checking time has much less impact than it does in JIT3mode.The Kaffe JIT3compiler does not incorporate more re-cent and sophisticated technologies to optimize the gener-ated code,such as those employed in IBM Jalepeno [35]and Jackal [38]to eliminate redundant object referenceand array boundary checks.By applying similar tech-niques in J-InterWeave to eliminate redundant instrumen-tation,we believe that the overhead could be further re-duced.5.2Translation costAs described in Sections 3,a J-InterWeave application must acquire a lock on a segment before reading or writ-ing it.The acquire operation will,if necessary,ob-tain a new version of the segment from the InterWeaveserver,and translate it from wire format into local Kaffeobject format.Similarly,after modifying an InterWeavesegment,a J-InterWeave application must invoke a write lock release operation,which translates modified por-tions of objects into wire format and sends the changes back to the server.From a high level point of view this translation re-sembles object serialization ,widely used to create per-sistent copies of objects,and to exchange objects between Java applications on heterogeneous machines.In this sub-section,we compare the performance of J-InterWeave’stranslation mechanism to that of object serialization in Sun’s JDK v.1.3.1.We compare against the Sun im-plementation because it is significantly faster than Kaffe v.1.0.6,and because Kaffe was unable to successfully se-rialize large arrays in our experiments.We first compare the cost of translating a large array of primitive double variables in both systems.Under Sun JDK we create a Java program to serialize double arrays into byte arrays and to de-serialize the byte arrays backagain.We measure the time for the serialization and de-serialization.Under J-InterWeave we create a programthat allocates double arrays of the same size,releases (un-maps)the segment,and exits.We measure the releasetime and subtract the time spent on communication with the server.We then run a program that acquires (maps)the segment,and measure the time to translate the byte arrays back into doubles in Kaffe.Results are shown in Figure 7,for arrays ranging in size from 25000to 250000elements.Overall,J-InterWeave is about twenty-three times faster than JDK 1.3.1in serialization,and 8times faster in dese-rialization.5.3Bandwidth reduction To evaluate the impact of InterWeave’s diff-based wire format,which transmits an encoding of only those bytes that have changed since the previous communication,we modify the previous experiment to modify between 10and 100%of a 200,000element double array.Results appear in Figures 8and 9.The former indicates translation time,the latter bytes transmitted.20406080100120140250005000075000100000125000150000175000200000225000250000Size of double array (in elements)T i m e (m s e c .)Figure 7:Comparison of double array translation betweenSun JDK 1.3.1and J-InterWeave102030405060708090100100908070605040302010Percentage of changesT i m e (m s e c .)Figure 8:Time needed to translate a partly modified dou-ble arrayIt is clear from the graph that as we reduce the per-centage of the array that is modified,both the translationtime and the required communication bandwidth go down by linear amounts.By comparison,object serialization is oblivious to the fraction of the data that has changed.5.4J-InterWeave Applications In this section,we describe the Astroflow application,developed by colleagues in the department of Physics andAstronomy,and modified by our group to take advan-tage of InterWeave’s ability to share data across hetero-geneous platforms.Other applications completed or cur-rently in development include interactive and incremental data mining,a distributed calendar system,and a multi-player game.Due to space limitations,we do not present these here.The Astroflow [11][14]application is a visualization tool for a hydrodynamics simulation actively used in the astrophysics domain.It is written in Java,but employs data from a series of binary files that are generated sepa-rately by a computational fluid dynamics simulation sys-00.20.40.60.811.21.41.61.8100908070605040302010Percentage of changesT r a n s mi s s i o n s i z e (M B )Figure 9:Bandwidth needed to transmit a partly modified double array2040608010012014012416Number of CPUsT i m e (s e c .)Figure 10:Simulator performance using InterWeave in-stead of file I/Otem.The simulator,in our case,is written in C,and runs on a cluster of 4AlphaServer 41005/600nodes under the Cashmere [34]S-DSM system.(Cashmere is a two-level system,exploiting hardware shared memory within SMP nodes and software shared memory among nodes.InterWeave provides a third level of sharing,based on dis-tributed versioned segments.We elaborate on this three-level structure in previous papers [8].)J-InterWeave makes it easy to connect the Astroflow vi-sualization front end directly to the simulator,to create an interactive system for visualization and steering.The ar-chitecture of the system is illustrated in Figure 1(page 1).Astroflow and the simulator share a segment with one header block specifying general configuration parameters and six arrays of doubles.The changes required to the two existing programs are small and limited.We wrote an XDR specification to describe the data structures we are sharing and replaced the original file operations with shared segment operations.No special care is re-quired to support multiple visualization clients or to con-trol the frequency of updates.While the simulation data。

SparseVB:变分贝叶斯算法为线性和逻辑回归的稀疏高维回归模型的稀疏变量选择说明书

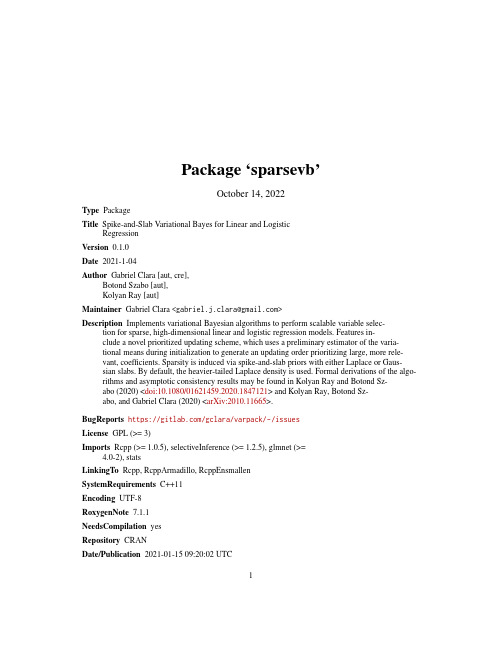

Package‘sparsevb’October14,2022Type PackageTitle Spike-and-Slab Variational Bayes for Linear and LogisticRegressionVersion0.1.0Date2021-1-04Author Gabriel Clara[aut,cre],Botond Szabo[aut],Kolyan Ray[aut]Maintainer Gabriel Clara<*************************>Description Implements variational Bayesian algorithms to perform scalable variable selec-tion for sparse,high-dimensional linear and logistic regression models.Features in-clude a novel prioritized updating scheme,which uses a preliminary estimator of the varia-tional means during initialization to generate an updating order prioritizing large,more rele-vant,coefficients.Sparsity is induced via spike-and-slab priors with either Laplace or Gaus-sian slabs.By default,the heavier-tailed Laplace density is used.Formal derivations of the algo-rithms and asymptotic consistency results may be found in Kolyan Ray and Botond Sz-abo(2020)<doi:10.1080/01621459.2020.1847121>and Kolyan Ray,Botond Sz-abo,and Gabriel Clara(2020)<arXiv:2010.11665>.BugReports https:///gclara/varpack/-/issuesLicense GPL(>=3)Imports Rcpp(>=1.0.5),selectiveInference(>=1.2.5),glmnet(>=4.0-2),statsLinkingTo Rcpp,RcppArmadillo,RcppEnsmallenSystemRequirements C++11Encoding UTF-8RoxygenNote7.1.1NeedsCompilation yesRepository CRANDate/Publication2021-01-1509:20:02UTC12sparsevb-package R topics documented:sparsevb-package (2)svb.fit (3)Index6 sparsevb-package sparsevb:Spike-and-Slab Variational Bayes for Linear and LogisticRegressionDescriptionImplements variational Bayesian algorithms to perform scalable variable selection for sparse,high-dimensional linear and logistic regression models.Features include a novel prioritized updating scheme,which uses a preliminary estimator of the variational means during initialization to generate an updating order prioritizing large,more relevant,coefficients.Sparsity is induced via spike-and-slab priors with either Laplace or Gaussian slabs.By default,the heavier-tailed Laplace density is used.Formal derivations of the algorithms and asymptotic consistency results may be found in Kolyan Ray and Botond Szabo(2020)<doi:10.1080/01621459.2020.1847121>and Kolyan Ray, Botond Szabo,and Gabriel Clara(2020)<arXiv:2010.11665>.DetailsFor details as they pertain to using the package,consult the svb.fit function help page.Detailed descriptions and derivations of the variational algorithms with Laplace slabs may be found in the references.Author(s)Maintainer:Gabriel Clara<*************************>Authors:•Botond Szabo•Kolyan RayReferences•Ray K.and Szabo B.Variational Bayes for high-dimensional linear regression with sparse priors.(2020).Journal of the American Statistical Association.•Ray K.,Szabo B.,and Clara G.Spike and slab variational Bayes for high dimensional logistic regression.(2020).Advances in Neural Information Processing Systems33.See AlsoUseful links:•Report bugs at https:///gclara/varpack/-/issuessvb.fit Fit Approximate Posteriors to Sparse Linear and Logistic ModelsDescriptionMain function of the sparsevb putes mean-field posterior approximations for both linear and logistic regression models,including variable selection via sparsity-inducing spike and slab priors.Usagesvb.fit(X,Y,family=c("linear","logistic"),slab=c("laplace","gaussian"),mu,sigma=rep(1,ncol(X)),gamma,alpha,beta,prior_scale=1,update_order,intercept=FALSE,noise_sd,max_iter=1000,tol=1e-05)ArgumentsX A numeric design matrix,each row of which represents a vector of covari-ates/independent variables/features.Though not required,it is recommendedto center and scale the columns to have norm sqrt(nrow(X)).Y An nrow(X)-dimensional response vector,numeric if family="linear"andbinary if family="logistic".family A character string selecting the regression model,either"linear"or"logistic".slab A character string specifying the prior slab density,either"laplace"or"gaussian".mu An ncol(X)-dimensional numeric vector,serving as initial guess for the varia-tional means.If omitted,mu will be estimated via ridge regression to initializethe coordinate ascent algorithm.sigma A positive ncol(X)-dimensional numeric vector,serving as initial guess for thevariational standard deviations.gamma An ncol(X)-dimensional vector of probabilities,serving as initial guess forthe variational inclusion probabilities.If omitted,gamma will be estimated viaLASSO regression to initialize the coordinate ascent algorithm.alpha A positive numeric value,parametrizing the beta hyper-prior on the inclusion probabilities.If omitted,alpha will be chosen empirically via LASSO regres-sion.beta A positive numeric value,parametrizing the beta hyper-prior on the inclusion probabilities.If omitted,beta will be chosen empirically via LASSO regres-sion.prior_scale A numeric value,controlling the scale parameter of the prior slab ed as the scale parameterλwhen prior="laplace",or as the standard deviationσif prior="gaussian".update_order A permutation of1:ncol(X),giving the update order of the coordinate-ascent algorithm.If omitted,a data driven updating order is used,see Ray and Szabo(2020)in Journal of the American Statistical Association for details.intercept A Boolean variable,controlling if an intercept should be included.NB:This feature is still experimental in logistic regression.noise_sd A positive numerical value,serving as estimate for the residual noise standard deviation in linear regression.If missing it will be estimated,see estimateSigmafrom the selectiveInference package for more details.Has no effect whenfamily="logistic".max_iter A positive integer,controlling the maximum number of iterations for the varia-tional update loop.tol A small,positive numerical value,controlling the termination criterion for max-imum absolute differences between binary entropies of successive iterates. DetailsSupposeθis the p-dimensional true parameter.The spike-and-slab prior forθmay be represented by the hierarchical schemew∼Beta(α,β),z j|w∼i.i.d.Bernoulli(w),θj|z j∼ind.(1−z j)δ0+z j g.Here,δ0represents the Dirac measure at0.The slab g may be taken either as a Laplace(0,λ)or N(0,σ2)density.The former has centered densityfλ(x)=λ2e−λ|x|.Givenαandβ,the beta hyper-prior has densityb(x|α,β)=xα−1(1−x)β−1 1tα−1(1−t)β−1d t.A straightforward integration shows that the prior inclusion probability of a coefficient isαα+β. ValueThe approximate mean-field posterior,given as a named list containing numeric vectors"mu", "sigma","gamma",and a value"intercept".The latter is set to NA in case intercept=FALSE.In mathematical terms,the conditional distribution of eachθj is given byθj|µj,σj,γj∼ind.γj N(µj,σ2)+(1−γj)δ0.Examples###Simulate a linear regression problem of size n times p,with sparsity level s### n<-250p<-500s<-5###Generate toy data###X<-matrix(rnorm(n*p),n,p)#standard Gaussian design matrixtheta<-numeric(p)theta[sample.int(p,s)]<-runif(s,-3,3)#sample non-zero coefficients in random locations pos_TR<-as.numeric(theta!=0)#true positivesY<-X%*%theta+rnorm(n)#add standard Gaussian noise###Run the algorithm in linear mode with Laplace prior and prioritized initialization### test<-svb.fit(X,Y,family="linear")posterior_mean<-test$mu*test$gamma#approximate posterior meanpos<-as.numeric(test$gamma>0.5)#significant coefficients###Assess the quality of the posterior estimates###TPR<-sum(pos[which(pos_TR==1)])/sum(pos_TR)#True positive rateFDR<-sum(pos[which(pos_TR!=1)])/max(sum(pos),1)#False discovery rateL2<-sqrt(sum((posterior_mean-theta)^2))#L_2-errorMSPE<-sqrt(sum((X%*%posterior_mean-Y)^2)/n)#Mean squared prediction errorIndexsparsevb,3sparsevb(sparsevb-package),2sparsevb-package,2svb.fit,2,36。

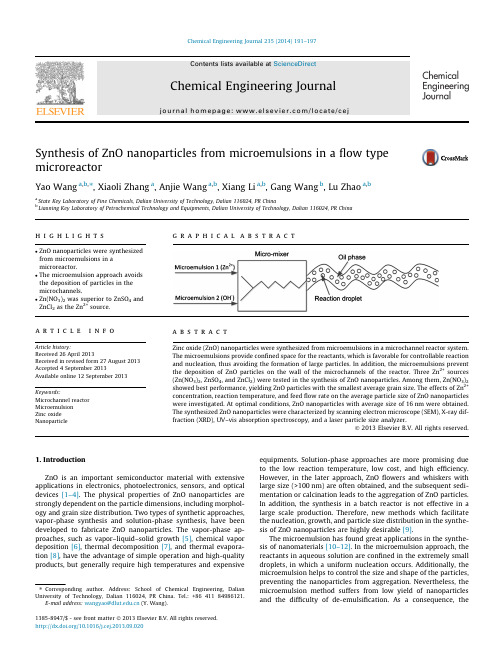

Synthesis of ZnO nanoparticles from microemulsions in a flow type microreactor