一种PowerPC指令集模拟器的设计与实现

基于PowerPC处理器的单板计算机设计和实现

结构框图如图 2

硬 件 电路设 计包 括监 控 电路 、 时钟 电路 、 电压转 换

电路 、 处理器 电路 、 MP C 1 0 7桥 控 制 器 、 存 储 器 电路 、 定

d e s i g n h a s t h e a d v a n t a g e s o f h i g h c a p a b i l i t y, l o w p o we r c o n s u mp t i o n, a n d g o o d le f x i b i l i t y, a n d in f d s p r a c t i c a l a p — p l i c a t i o n wi t h g o o d r e s u l t s .

a 叶弑 2 0 1 4 年 第 2 7 卷 第 6 期

El e c t r o n i c S c i . & Te c h . / J u n . 1 5.2 0 1 4

基于 P o w e r P C处 理 器 的单 板 计 算 机 设 计 和 实 现

刘 冰 ,孙爱 中

( 中航工业西安航空计算技术研究所 第 6研究室 ,陕西 西安

摘

7 1 0 0 6 8 )

要 为提 高现代 武器装备 中抗 恶劣环境 计算机 的处理 能力 ,提 出了一种基 于 P o w e r P C处理 器的计算模块设 计

方法。该 方法包括基 于 P o w e r P C处理器的计算模 块的主要硬 件设计思路和软件 实现过程 ,通过采 用 P o w e r P C 7 5 5处理器

基于PowerPCDSP总线通信软件的设计与实现

基于PowerPCDSP总线通信软件的设计与实现针对现代总线控制管理计算机系统的发展趋势,结合某型飞机航空通信总线控制管理的实际需求,设计了基于PowerPC + DSP的总线通信系统软件,主要是对RS422串行通信总线和ARINC429总线进行控制和管理。

该软件分为驱动软件和控制软件,驱动软件运行在PowerPC上,它实现DSP与主机应用软件间的接口控制和数据传递,可提供各类消息数据的读、写支持,并对DSP内程序进行调度。

控制软件运行在DSP上,它负责RS422串行通信总线和ARINC429总线通信的控制、数据接收和发送等。

PowerPC和DSP通过双口存储器进行数据通信。

该中还介绍了总线通信系统中PowerPC和DSP的故障管理功能。

本软件充分利用系统资源,实现了通信总线的控制与管理,满足航电系统总线通信与管理的要求。

PowerPC是IBM和Motorola公司共同开发的高性能、低功耗、开放架构的处理器,采用简单的指令集(RISC),同时集成了PCI -Express、千兆网络、RapidIO及CAN等多种网络通信控制器,支持DMA、I2C、UART等数据交换组件,具有处理能力强、网络通信接口多等优点,被广泛应用于汽车电子、航空航天、工业控制等要求高性能和高可靠性的领域[1-3]。

鉴于此,文中设计了一种基于PowerPC750配有VME总线的CPU模块,满足现代武器装备的需求。

TMS320F240系列DSP是美国TI公司于推出的,专为数字电机控制和其他控制应用系统而设计的16位定点数字信号处理器。

它将数字信号处理的高速运算功能与面向电机的强大控制能力结合在一起,从而成为传统的多微处理器单元和多片设计系统的理想替代品。

F240片内外设包括双10位A/D转换器,带有锁相环PLL时钟模块,带中断的看门狗定时器模块,串行通信接口SCI及串行外设接口SPI,另外,还集成了一个事件管理模块EVM。

因此,F240不仅具有高速数据处理能力,还具有控制和事件管理能力,可完成人机界面,与上位机进行串行通信[4-5]。

PowerPC-体系结构之指令集

PowerPC 体系结构之指令集1. 概述Book E 定义的PowerPC 指令集的指令可分为以下几类:分支跳转指令CR 指令整数指令浮点指令处理器控制指令存储管理相关指令CR 指令主要是对CR 内部位运算支持的一些指令,如crand, cror, crxor 等等。

2. 常用指令先看一个测试程序:------------------------------------------------------------------int test_call(int a, int b, int c){a =b + c;return a;}int test_if(int s){int i;if(s > 0)i = s;else if(s < 0)i = -s;elsei = s * 8;return i;}int test_cyc1(int c){int sum = 0;do {sum += c;c--;} while(c > 0);return c;}int test_cyc2(int c){int sum = 0;for(; c > 0; c--)sum += c;return c;}int main(){int a, b, c, d;a = test_if(5);b = test_cyc1(10);c = test_cyc2(10);d = test_call(1, 2, 3);return a + b + c + d;}------------------------------------------------------------------引入的目的在于查看判断、循环和过程调用这些基本结构在PowerPC 里怎么被支持。

-O2 参数编译后,objdump -S -d 反汇编,则:------------------------------------------------------------------1000040c <test_call>:int test_call(int a, int b, int c){a =b + c;return a;}1000040c: 7c 64 2a 14 add r3,r4,r5 ----> 对应a, b, c 三个参数,同时r3 又置返回值10000410: 4e 80 00 20 blr ----> 跳转到LR 所存放的地址处,即函数返回10000414 <test_if>:int test_if(int s){int i;if(s > 0)10000414: 7c 60 1b 79 mr.r0,r3 -----> r3 移到r0,若r0 小于、大于、等于0,则置CR0 的相应位。

powerPC架构及编程资料

返回

MPC8260处理器的结构与编程

MPC8260处理器是由Motorola提供的PowerPC系列处理器.它由两个内核即PowerPC 603e和通信处理模块CPM专用内核组成.由于CPM分担了嵌入式PowerPC核的外围工作 任务,这种双处理器体系结构功耗要低于传统的体系结构的处理器。

基本功能模块

此外,改进的VMX(Vector Multimedia Extensions矢量多媒体 扩展指令集)引擎较G4处理器有了更 高的执行效率,这个引擎与 Motorola的Altivec引擎一样,属于 IBM与Motorola共同开发的产物,都 具有162条SIMD指令。

IBM生产的PowerPC 970处理器

优势三:稳定性,可靠行 Powerpc架构具有很强稳定性能,高可靠性 更长的产品寿命周期(通常 10到 15年以上) 苛刻条件下,芯片具有很强健壮性,适合工业级应用

优势四:软件兼容性 软件可移植,从低端到高端器件,软件代码具有再使用能力 完整功能的组合:Ethernet, USB, PCI

优势五:芯片性能可选范围大 从低端到高端都有芯片可以选择 最低主频率50MHZ,133MHZ,266MHZ,最高可以达到几GHZ

提供的系统功能: (1) 保护:硬件和软件看门狗; (2) 复位:复位和监视; (3) 时钟同步:根据外部时钟振荡器产生内部时钟; (4) 电源管理; (5) JTAG:测试接入端口.

CPM的模块结构 MPC8260高性能通信处理模块(CPM)运行频率133MHz或166MHz,包括了 MPC8260中的所有通信组件,提供3个FCC,2个MCC,4个SCC,2个SMC,1个SPI和 一个I2C,其主要特点有: (1) PowerPC和CPM可以工作在不同频率; (2) 支持串行比特率710Mbit/s @ 133MHz; (3) 并行I/O寄存器; (4) 片内24KB双口RAM; (5) 两个多通道控制器(MCC),每个支持128条全双工的64kbit/s HDLC线; (6) 虚拟DMA功能; (7) 双总线结构:1个64位PowerPC和1个32位本地总线; (8) 2个UTOPIA二级主/从端口,均支持多PHY; (9) 3个MII接口; (10) 8个TDM接口(T1/E1),2个TDM口可以无缝链接到T3/E3; (11) 内部电压2.0V,I/O电平3.3V; (12) 133MHz 功耗位2.5W.

PowerPC

IBM推出可升级的POWER并行系统,这是第一款采用RS/6000技术,基于微处理器的超级计算机。

谢谢观看

系统接口单元SIU的功能是提供内部总线和外部总线的接口,该接口单元具有32位微处理器的几乎所有的通 用接口特性,尽管Power PC核内部总线为32位,但通过SIU可以将外部总线宽度动态地配置成8、16或32位,以 兼容数据总线宽度为8、 16或32位的外设或存储器。

SIU单元中的存储器控制器支持最多与高达8组存储器的无缝连接,每组的容量从32K字节到256M字节可变, 数据总线宽度可由4个独立的使能信号控制为8bits,16bits或32bits。支持的存储器类型包括SRAM、SSRAM、 EPOM、Flash ROM、DRAM,SDRAM等。存储器控制器为每一组存储器分别提供了可选的0到15个的等待状态以适应 不同速度的存储器。SIU也支持其它需要双时钟访问的外部SRAM和用突发方式访问的外部设备。

PowerPC处理器有 32个(32位或 64位)GPR(通用寄存器)以及诸如 PC(程序计数器,也称为 IAR/指令 寄存器或 NIP/下一指令指针)、LR(链接寄存器)、CR(条件寄存器)等各种其它寄存器。有些 PowerPC CPU 还有 32个 64位 FPR(浮点寄存器)。

PowerPC体系结构是 RISC(精简指令集计算)体系结构的一个示例。因此:

联盟运作

联盟运作

联盟三巨头,个个有来头,因此联盟采行的是松散制联盟。也就是说,联盟的目标一致,但彼此并没有隶属 关系,运作时也难以强制成员遵行。不过联盟负责制定规格、进行授权与认证等相关工作。

分工方面,摩托罗拉主司芯片设计、制造。苹果电脑则是负责操作系统,还有组装及销售。IBM不愧是信息 界的全能选手,他从上游的芯片设计、制造,到中游的系统整合、测试、操作系统,及下游的组装、销售,不但 能全面参与,向来亦是个中好手。

PowerPC简介及编程要点

PowerPC简介及编程一,PowerPC芯片PowerPC是早期Motorola和IBM联合为Apple的MAC机开发的CPU芯片,商标权同时属于IBM和Motorola,并成为他们的主导成品.IBM主要的PowerPC产品有PowerPC604s(深蓝内部的CPU),PowerPC750,PowerPCG3(1.1GHz).Motorola主要有MC和MPC系列.尽管他们产品不一样,但都采用PowerPC的内核.这些产品大都用在嵌入式系统中.Motorola的MPC860简介MPC860 PowerQUICC (Quad Integrated Communications Controller) 内部集成了微处理器和一些控制领域的常用外围组件, 特别适用于通信产品. 包括器件的适应性, 扩展能力和集成度等. MPC860 PowerQUICC集成了两个处理块.一个处理块是嵌入的PowerPC核, 另一个是通信处理模块( CPM, Communications Processor Module), 通信处理模块支持四个串行通信控制器(SCC, Serial Communication Controller), 实际上它有八个串行通道: 四个SCC,两个串行管理控制器(SMC, Serial Management Channels), 一个串行外围接口电路( SPI, Serial Peripheral Interface ) 和一个I2C( Inter-Integrated Circuit ) 接口. 由于CPM分担了嵌入式PowerPC核的外围工作任务, 这种双处理器体系结构功耗要低于传统的体系结构的处理器.单出口, 嵌入式PowerPC核32比特版本(与PowerPC结构定义完全兼容)32x32位通用寄存器(GPRs, General Purpose Registers)o4K数据Cache和4K指令Cache, 分别带有一个MMU.o存储管理单元(MMU)32-输入翻译后备缓冲器( TLBs )o32位数据,地址线∙存储控制器(八个存储体)o单线存储模块无逢接口,静态随即存取存储器(RAM), EPROM, FLASH MEMORY或DRAM等。

power pc指令类型特点

power pc指令类型特点

PowerPC(PPC)是一种RISC(精简指令集计算机)架构,其指令集具有一些特点,包括以下内容:

1.精简指令集:PowerPC采用了精简指令集(RISC)的设计原则,其指令集相对较小且精简。

这有助于提高指令执行速度和简化处理器的设计。

2.固定长度指令:PowerPC的指令长度通常是固定的,这使得指令的解码和执行更加高效。

指令通常是32位长,但也有64位版本。

3.多寄存器操作:PowerPC支持多寄存器操作,允许在一条指令中同时对多个寄存器执行操作。

这提高了并行性和性能。

4.延迟槽:PowerPC采用了延迟槽的设计,允许在分支指令之后执行前一个指令。

这可以提高分支指令的效率。

5.浮点运算支持:PowerPC架构具有强大的浮点运算支持,包括一组浮点寄存器和一套浮点指令。

6.立即数操作:PowerPC允许立即数操作,即在指令中直接指定常数值,而不需要从内存中加载。

7.负载/存储架构:PowerPC采用了典型的负载/存储架构,即大部分操作都是在寄存器之间进行,而内存访问需要专门的负载(Load)和存储(Store)指令。

8.大端序和小端序:PowerPC支持两种字节序,即大端序和小端序,这允许在不同体系结构之间进行数据交换。

这些特点使PowerPC成为一种高性能和灵活的架构,广泛用于多种应用领域,包括个人计算机、服务器、嵌入式系统和超级计算机。

不过,需要注意的是,随着时间的推移,一些基于PowerPC架构的产品逐渐被其他架构所取代。

机载PowerPC系列高性能处理器模块硬件设计

为代表 的公司较 早研制 出以 P o we r P C系列 处理 器为核心的高 速数据处理功 能模块 ,形成 了以 VME为主的底板总线 、结构 尺寸为 3 U、6 U 的标准 P o we r P C系列 高性 能处 理器 模块,并

模 块 的硬 件 实现 。

【 关键 词 】开发式综合化 ;可配置性 ;可测试性 【 中图分类号 】V 2 7 1 . 4 【 文献标识码 】A

【 文章编号 】1 0 0 8 . 1 1 5 1 ( 2 0 1 5 ) 0 5 . 0 0 0 we r PC s e r i e s hi g h- pe r f o r ma n c e pr o c e s s o r mo du l e ha r d wa r e de s i g n

Ab s t r a c t : Th i s p a p e r ir f s t i n t r o d u c e s t h e t y p i c a l h i g h p e r f o r ma n c e p r o c e s s o r a n d i n t r o d u c e d P o we r P C p r o c e s s o r s e r i e s ,a n d t h e n

i mp l e me n t a t i o n Ke y wo r d s : Op e n i n t e g r a t i o n ; c o n ig f nr a b i l i t y ; t e s t a b i l i t y

随着计算机技术 、 通 信 技术 的 飞 速 发 展 ,向 着 高 技 术 、 高

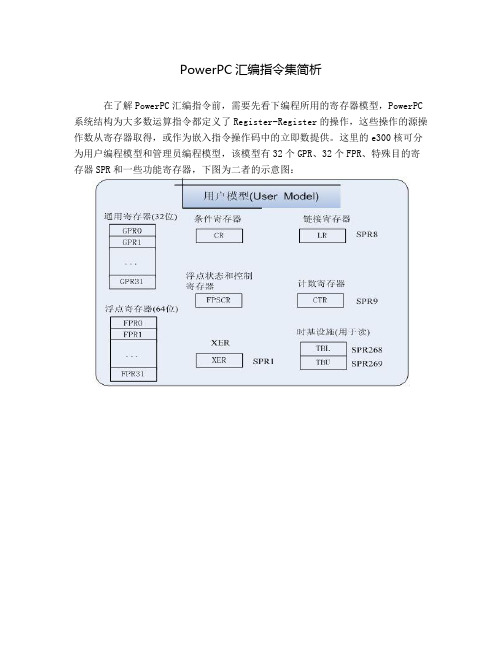

PowerPC汇编指令集简析

PowerPC汇编指令集简析在了解PowerPC汇编指令前,需要先看下编程所用的寄存器模型,PowerPC 系统结构为大多数运算指令都定义了Register-Register的操作,这些操作的源操作数从寄存器取得,或作为嵌入指令操作码中的立即数提供。

这里的e300核可分为用户编程模型和管理员编程模型,该模型有32个GPR、32个FPR、特殊目的寄存器SPR和一些功能寄存器,下图为二者的示意图:上面这些寄存器可能不太好理解,因为名字和Intel汇编不一样,其实,可以这样理解,GPR就相当于EAX/EBX/ECX,而CTR则完全就是ECX的功能,是吧?区别就是没有堆栈而已咯。

CR被分为8段,每段4位,分别代表LT、GT、EQ和SO(小于、大于、等于和溢出);LR用于记录跳转地址;特殊寄存器XER用于记录溢出和进位标志;FPSCR用于记录浮点运算类型和异常等。

再看下指令集,大部分的CPU指令集可分为:数据读写、数值计算、流程控制和设备管理四个部分,由于PowerPC使用RISC,指令字长为32bit,Endian一般是可调的,默认为大端,另外,PowerPC没有栈,所以程序需要自己实现相关操作。

首先为运算和逻辑指令,列举如下:它们与通用寄存器有关,源数据来自GPR 或16 位立即数,目的是GPR 寄存器,操作为32 位,GPR 中存放32 位更新数据。

大多数指令都可以根据字面意思理解其作用,注意还有一个“cntlzw”指令,意为计算字中的第一个0,用于在一个字中找到1时将一个指令中的0的数量找出,它在决定例外寄存器中最高优先服务时有用。

下面是数据读写指令,它们对数据在存储器中核通用寄存器中的传送很有用,若数据小于传送长度(单字,半字或字节),指令会使数据变位为32位,将不同位填0或符号扩展。

指令列举如下:这里需要注意的是上面列举的lbz和lhz两个指令并不完全等同于moval,[ebx]和mov ax,[ebx+10]这两个,因为前面两个是将字节和半字加载到r3时还清空了高位,而后两条指令只是加载数据到eax,并不会清空高位。

实验1 PowerPC 处理器简单的硬件设计

实验1 PowerPC 处理器简单的硬件设计信息14 李兰鑫 2110502077一、实验目的通过实验1、学会运用软件创建一个XPS工程;2、掌握如何使用BSB(Base System Builder)在XUP Virtex-II Pro开发板上建立一个目标系统;3、掌握如何下载测试程序并通过超级终端输出验证结果。

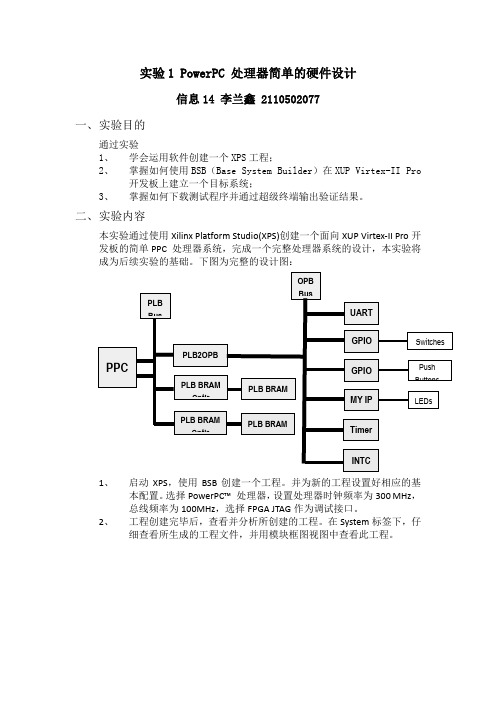

二、实验内容本实验通过使用Xilinx Platform Studio(XPS)创建一个面向XUP Virtex-II Pro开发板的简单PPC 处理器系统,完成一个完整处理器系统的设计,本实验将成为后续实验的基础。

下图为完整的设计图:1、启动XPS,使用BSB创建一个工程。

并为新的工程设置好相应的基本配置。

选择PowerPC™ 处理器,设置处理器时钟频率为300 MHz,总线频率为100MHz,选择FPGA JTAG作为调试接口。

2、工程创建完毕后,查看并分析所创建的工程。

在System标签下,仔细查看所生成的工程文件,并用模块框图视图中查看此工程。

3、使用PlatGen生成硬件网表。

4、下载测试应用程序并观察输出。

下载指定测试程序,将XUP开发板连上电源、下载电缆和串口电缆,通过超级终端观察输出结果。

三、实验结果实验结果如下图所示:在超级终端中,可显示相应的进入、退出语句。

同时可通过对程序的修改实现学号的输出。

四、结果分析本次实验,在XPS中,Base System Builder用于创建工程,也会创建一些文件,包括描述处理器系统的MHS文件和描述原理图的PBD文件。

定制好系统之后,就可以生成处理器系统的网表。

下载指定的测试程序后可实现在超级终端的输出,同时通过对可见程序的修改,添加学号输出的语句,在超级终端实现了学号的输出。

五、心得体会通过本次实验,我初步掌握了XPS的使用方法,可以创建工程并对其分析查看。

同时学会将程序下载至开发板中通过超级终端显示相应的结果,也掌握了在程序中添加自己的内容。

一种PowerPC数据处理模块设计

一种PowerPC数据处理模块设计

李晓蕊;李金山;李健一

【期刊名称】《电脑编程技巧与维护》

【年(卷),期】2023()2

【摘要】随着嵌入式系统功能的日益强大,嵌入式系统在航空电子系统中的应用也越来越广泛。

航空、航天、国防电子等关键领域对嵌入式硬件的功能、可靠性、成本、体积、功耗等方面都有着严格要求。

数据处理模块作为嵌入式硬件的核心部件,对它的性能也提出了更高的要求。

设计了一种基于HKSP6102处理器的PowerPC 数据处理模块,对各单元功能展开了详细的讲解。

该设计具通用性,在接口功能和处理性能等方面具有较大优势,为航空嵌入式电子系统提供了一种全系统单片解决方案。

【总页数】3页(P69-71)

【作者】李晓蕊;李金山;李健一

【作者单位】中国航空工业集团公司西安航空计算技术研究所

【正文语种】中文

【中图分类】TP3

【相关文献】

1.PowerPC数据处理模块的看门狗设计

2.PowerPC8270数据处理模块的异步总线接口设计

3.PowerPC8270数据处理模块的PCI接口设计

4.PowerPC 8270数

据处理模块的SPI接口设计5.一种基于PowerPC的FC网络交换模块的设计与验证

因版权原因,仅展示原文概要,查看原文内容请购买。

基于PowerPC的软件仿真调试系统的设计与实验

1 2 平 台工作 流 程 .

1 目标 层 : ) 目标 Pw rC平 台上 的运 行 环境 ; o eP

2 )虚拟 化层 : 整个 系统 的核 心 , 即运 行 在 主机

系 统 的虚拟机 进 程 ;

3 )主机 层 : 际宿 主机 的运行 环境 。 实

Pw rC虚 拟调 试平 台首 先分 析 带有 调 试 信息 o eP 的 E F文 件 , 析 出行 号 表 ( L 分 即执 行 指 令 对 应 的程 序地 址 ) 变 量 地 址 以及 对 应 的可 执 行 文 件 。 而后 ,

我们 将 分 析好 的 可 执 行 加 载进 虚 拟 机 中。 而后 虚

21 0 1年 8月 1 7日收到

的机器上 , 仿真一个 Pw rC平台, oe P 可以如真实的硬 件平台一样加 载运行相应 的 Pw rC的可执行文 oe P 件, 并提供更方便 的调试接 口。

第一作者 简介 : 孙胜杰 ( 9 6 ) 男 , 族 , 18 一 , 汉 陕西省 西安市人 , 士 硕

点则 暂停 运 行 , 制 权 交 由上层 的 图形 界 面操 作 。 控 最 后执 行 itpe 成 取 址 、 码 与 执行 。整 体 流 ne r r t完 译

程 如 图 3所示 。

主机层

@ 2 1 SiT c. nr. 0 1 c. eh E gg

基 于 P w r C的软 件 仿 真 调试 o eP 系统 的设 计与实验

孙 胜 杰 苗克 坚 曹晓 洁

( 西北工业大学计算 机学院 西安 7 0 2 ; , 1 19 上海海关学院基础部 上海 2 10 ) , 02 4

PowerPC 的仿真和交叉开发

即时编译

通过即时编译(Just In Time,JIT)这种方法,可以动态 地将解释的字节码(例如,一个仿真的指令流)翻译成本 地指令。这种方法不是简单地依次解释和仿真每条指令, 而是将整个指令序列转换成本地对应的指令序列,并将它 们缓存起来,这样,在随后执行指令序列时,就不需要再 进行翻译了。相应地,已解释代码的严格 CPU 限制循环 应该可以以接近本地的速度执行,因为本地代码被保存在 缓存中。另一方面,带有很少循环的代码的性能则得不到 太多的改善。JIT 编译器对于 Java™ 虚拟机来说非常常

PearPC

PearPC 是另一种新的仿真器,它可以使用 JIT 动态翻译,但只能和 PowerPC 目标一起在 见,这种编译器也可以用于提高仿真虚拟机的效率。 x86 主机上使用 —— 不过,本文使用的正好是这种环境。它的性能不如 qemu 好,大约要比 主机系统慢 15 倍。不幸的是,PearPC 不支持用户环境,因此还需要一个内核和一个基本文 件系统(Linux、Darwin 和 Mac OS X 目前都受支持)。 PearPC 不支持 GDB 连接,也不支持 AltiVec 向量处理指令(不过开发人员打算在未来

选择仿真器

由于上述原因,本文将使用 qemu。一些常见的基本问题也适用于其他仿真器,但就本文来说,qemu 是最易于构建的。请下载和解压 qemu tarball (请参阅 参考资料),然后: 清单 1: 构建 qemu

$. / c o n f i g u r et a r g e t l i s t = p p c u s e r $m a k e

64-位 PowerPC

虽然 crosstool 可以容易地产生 ppc64 toolchains ,但还没有用于 64-位 PowerPC 的开源仿真器,因此您需要使用真正的硬件来做实验。当然, ppc32 可执行文件在 ppc64 硬件上同样运行得很好(但反之则不然)。 回页首

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

邮局订阅号:82-946360元/年技术创新电子设计《PLC 技术应用200例》您的论文得到两院院士关注一种PowerPC 指令集模拟器的设计与实现A modelling and implementation method for PowerPC instruction set simulator(1.西北工业大学;2.广西工学院)孙利军1董云卫1周兵2SUN Li-jun DONG Yun-wei ZHOU Bing摘要:构建了基于PowerPC 处理器的SoC 软硬件协同验证平台。

该平台使用层次化设计方法,支持TLM 抽象层次的虚拟原型仿真,兼顾了仿真精度和速度的要求,并用软件编程的方法详细介绍了PowerPC 体系指令集模拟器(ISS)的设计与实现方法。

关键词:指令集;指令集模拟器;系统语言;事务级模型中图分类号:TP 311文献标识码:AAbstract:This article describes the design of a SoC hardware/software co -verification platform,which is based on the layered ap -proach.The platform can obtain high accuracy and simulation speed by transaction-level model (TLM)in an architecture.This pro -ject integrates instruction set simulators (ISS)as SystemC modules with TLM interfaces to the other platform components.It simulates the CPU hardware behaviour using C++program language.Key words:PowerPC instruction set;instruction set simulator;SystemC;TLM文章编号:1008-0570(2010)08-2-0161-031引言传统SoC 设计方法流程的主要弊端是:寄存器传输级(RTL)描述的层次较低,仿真速度不高;系统设计流程中存在着多种设计语言,不同的开发人员之间存在语义鸿沟;软硬件协同仿真点较晚,不利于在设计早期发现错误,这时候的重新开发将付出较大的代价。

所以提高设计的抽象层次,在流程中使用统一的建模语言室解决问题的关键。

针对上面提出的问题,Synopsys,Coware 和Frontier Design 等公司合作开发了一种新的系统建模语言SystemC,其目的是为系统设计提供一种单一的语言,即提供一个公共的平台来进行更好的软硬件协同设计和验证,提高设计效率。

目前PowerPCISS 如PearPC 、PSIM 及QEMU 都是用C 语言构建PowerPC 处理器内核。

但还存在着一些不足,一方面,这些模拟器代码没有统一的接口标准,全系统中外围设备代码无法重用,例如,QEMU 模拟器的外围设备模块无法在其它模拟器上使用。

另一方面,在全系统仿真中,进行交互操作和并行处理时不能很好的兼容第三方的模块。

基于上述问题,本文用SystemC 语言对模拟器进行建模,以C++作为处理器的硬件描述语言,详细介绍了在基于X86指令系统的PC 计算机平台上,设计一个PowerPC 指令集CPU 模拟器全部过程,最后用实例来说明设计的合理性。

2模拟器设计方案SystemC 是一种完成电子系统从软件到硬件的全部建模过程的语言,是一个支持多层设计抽象的建模平台,可以在RTL 抽象层之上建模系统,包括可能在软件中、硬件中或者是两者的组合中实现的系统。

SystemC 根据IEEE 标准定义,并且开源实施,它已经成为了代表硬件模型的标准。

SystemC 相对于普通C++主要增加了一个能对硬件不同抽象层次描述和仿真的C++类库,和一个不依赖任何硬件的仿真器的轻量级仿真内核。

SimSoC 是该模拟器的名称,它作为SystemC TLM(transac -tion-level model)模块的一个集合来实施,它的整体结构如图一所示。

它的硬件组件用TLM 模型作为原型,因此SimSoC 的模拟工作由SystemC 的内核驱动。

组件之间的互相联络通过抽象的总线,平台上模拟的每个处理器都被抽象为一个特殊的类。

事务处理级模型(TLM)是进行这种分析的理想模型,在片上系统(SoC)设计中使用事务处理级建模,可让设计从高效率协同仿真和高产出的分析与调试中受益。

事务是指在被建模和被模拟的系统中,两个模块之间的一次数据或者事件的传输。

同一建模对象的SystemC 事务级模型的模拟速度大约是SystemC RTL 级模型的100倍。

解决了目前IC 设计过程中遇到的仿真速度慢的缺点,也体现了事务级比RTL 级抽象层次更高的特点。

图1SimSoC 系统结构SimSoC 指令集模拟器的目的是通过模拟目标处理器的行为来验证其指令的准确性。

它效仿指令的执行、异常、中断和虚拟内存的映射。

该处理器驱动译文为二进制的代码。

当程序计数器指向的指令没有被翻译,则该翻译被调用;否则,缓存中已经翻译的代码将被执行。

该翻译实际上是基于存储页面的。

孙利军:硕士研究生基金项目:基金申请人:周兴社;项目名称:重点课题“高可靠构件化嵌入式软件设计与验证技术及其支撑环境研究”;基金颁发部门:国家自然科学基金委(60736017)161--技术创新《微计算机信息》(嵌入式与SOC)2010年第26卷第8-2期360元/年邮局订阅号:82-946《现场总线技术应用200例》电子设计SimSoC 模拟框架主要由两个部分组成:一部分是基于SystemC/TLM 的硬件组件的仿真,另一部分是处理器的模拟。

SimSoc 主要模拟了PowerPC 芯片、ARM 芯片以及MIPS 芯片中的指令集,CPU 的状态以及行为,内部部件的通信,MMU 总线以及存储器。

本文中主要介绍PowerPC 的模拟。

SimSoc 中各个模拟部件之间的关系如图2所示,每一个目标平台的硬件部件都是用SystemC 模块来实现模拟的。

CPU 模拟器以及MMU 是放在同一个SystemC 模块中。

MMU 和其它设备产生Sys -temC-TLM 通信是通过它的TLM 初始化端口,对于CPU 模拟器来说,它是通过一个函数来接收外设发出的中断请求的。

目标机内存是通过宿主机的内存来模拟实现的。

内存也是一个TLM 目标模块,它可以和系统中的其它模块通信,CPU 模拟器可以直接对内存进行操作。

我们假设虚拟内存是分页的,在SimSoc 目前的版本中暂时不支持分段的内存。

图2SimSoc 模拟器部件关系软件的角度来说,处理器主要包括指令集和对寄存器的操作,处理器建模主要是通过将实现指令集译码执行的各个部件封装为C++类的形式。

处理器建模过程就是精确指令集设计和实现的过程。

PowerPC 处理器的ISA 模型主要包括数据格式、处理器系统、存储器组织、寄存器组织、指令集译码系统及ELF 文件加裁。

各部分建模的基本方法如下:(1)在数据格式定义中主要定义硬件能直接识别和处理的数据类型和格式,包括字长、半字和字节。

(2)处理器系统的实现是通过PPC_Processor 类定义指令译码和执行过程中所涉及的所有部件及其操作。

在该类中声明了所有通用寄存器、堆栈指针、内存单元、中断异常及debug 端口等部件并实现对这些部件的操作。

(3)存储器系统主要是通过在PPC_MMU 和PPC_TLB 类中定义处理器的存储空间、编址单位、编址方式和大小端等。

首先,定义与数据、程序存储器对应的一个或多个数组,然后,定义一组访问函数实现地址转换、范围检查、大小端定义、字、半字和字节的访问。

(4)寄存器组织包括PC 、通用寄存器、状态寄存器等各种寄存器的数量、组织及使用方法。

对寄存器的处理采取的方案是,在PPC_Processor 类定义和实现PC 及所有的通用寄存器的访问。

(5)指令译码系统主要实现了对每条指令的译码和执行过程。

首先在PPC_Instruction 类定义各种指令类型的执行和显示,然后在decode 中对所有的指令进行解析,主要完成根据操作码和功能码查找指令并根据指令格式对操作数域进行解析的过程。

最后,将所有PPC 指令分为alu 、fpu 、load&store 和misc 四类,并在其中定义和实现具体的指令。

(6)模拟器在运行时首先调用Elf_loader 文件,经解析器解析后得到的程序和数据用于初始化内存。

仿真器执行指令并处理数据,并将结果打印在输出控制台。

Elf_loader 文件经解析后返回信息。

3指令译码及实现3.1PowerPC 指令格式PowerPC 采用定长操作码的指令字格式。

所有指令的指令长度都是32位单字长指令,且是对准的。

其中操作码占6位。

项目中设计的模拟器实现了PowerPC 指令集中所有指令的译码和执行,每条指令的具体含义见文献。

3.2指令译码指令译码主要包括两方面的内容,一方面是通过操作码(PowerPC 每条指令的操作码由基本码和扩展码组成)确定指令的具体操作类型;另一方面是通过对指令的译码,确定指令执行过程中操作数(立即数或偏移量)或操作数所在的寄存器。

3.2.1确定指令操作类型本方案中采用分级查找的方式实现了确定操作类型。

首先,将需要进行译码的所有指令按照操作码进行分类,将所有操作码相同的指令定义为同一个分组,如定义操作码为011111的所有指令放在group0中。

对于操作码唯一的指令可直接定义指令类型,如:ppc_tdi 等指令。

由于PowerPC 指令集的操作码统一为6位,即共有64种操作码,这样可将所有的PowerPC 指令分成64种分组或指令类型,每组指令的操作码的基本码都相同,并通过数组来实现具体的分组。

如将group0、group1、ppc_tdi 和ppc_ori 等放在数组ppc_table_main [64]中。

其次,再将各操作码相同的分组中按扩展码的指令进行二次分组,例如group0组中又可分为group00、group01等组,其中每组指令的操作码和功能码都相同。

最后在group00、group01中根据特殊标志位来确定具体的操作类型。

通过对以下六条二进制指令进行译码,来说明指令的译码过程:011111xxxxx yyyyy zzzzz 00000111000and 011111xxxxx yyyyy zzzzz 00000111001and_011111xxxxx yyyyy zzzzz x100001010x addx 010011xxxxx yyyyy zzzzz 010*******x crand 010011xxxxx yyyyy zzzzz 0011000001x crxor 000010xxxxx yyyyy zzzzzzzzzzzzzzzz tdi (1)定义分组由于本例中指令and 、and_和andx 的操作码中基本码相同,且指令and 和and_操作码中的扩展码也相同因此可将这三条指令放在group0中,再将指令and 和and_放入group00中,andx 指令放在group01中。