isplsi1016-mil CPLD

第二讲:Lattice公司的isp1016芯片

在系统编程接口——串行菊花链方式:

SDO SDI MODE SCLK ispEN

5线ISP编程接口

ispLSI 1016

ispGDS

在系统可编 程数字开关

ispGAL

ispLSI

返回目录

树立质量法制观念、提高全员质量意 识。20 .10.21 20.10 .21W ednes day, October 21, 2020

安全在于心细,事故出在麻痹。20.1 0.212 0.10.2 116:5 4:401 6:54: 40Oct ober 21, 2020

踏实肯干,努力奋斗。2020年10月2 1日下 午4时5 4分20. 10.21 20.10 .21

追求至善凭技术开拓市场,凭管理增 创效益 ,凭服 务树立 形象。 2020年 10月2 1日星 期三下 午4时5 4分40 秒16:5 4:402 0.10. 21

• 串行数据输出SDO(Serial Data Out);

• 串行时钟SCLK(Serial Clock);

• 模式选择Mode;

• 整个芯片的使能端ispEN。

当ispEN引脚加高电平时,器件处于正常模式。当 ispEN引脚加低电平时,器件处于编程状态,所有I/O端 的三态缓冲电路皆被禁止而处于高阻状态,从而割断了 芯片与外电路的联系,避免了编程芯片与外电路的互相 影响。

• 输出布线区ORP是介于GLB和IOC之间的可编程互 连阵列; • ORP的输入是8个GLB的32个输出端; • ORP的输出有16个,分别与该侧的16个IOC相连; • 通过对ORP编程,可以将任一个GLB输出灵活地送 到16个I/O端的任何一个; • 在ORP的旁边还有16条通向GRP的总线,I/O单元可 以使用,GLB的输出也可以通过ORP使用它,从而方便地 实现了I/O端复用的功能和GLB之间的互连。

ISP技术

ISP技术 ISP技术

ABEL-HDL语言 编程软件ispEXPERT

ISP技术

ISP技术

ISP技术的特点 ISP逻辑器件系列 ispLSI器件的结构 在系统编程原理和方法

ISP技术的特点

一、在系统编程

在系统编程(ISP):指用户具有在自己设计的线路板上为 重构逻辑而对逻辑器件进行反复编程改写的能力。 ISP技术是美国Lattice半导体公司首先提出来的一种能 在产品设计、制造过程中的每个环节具有对其器件、电路或 整个数字系统的逻辑和功能随时进行组态或重组能力的最新 技术。在可编程逻辑器件(Programming Logic Device, PLD)及其技术中,ISP是一种新的概念、新的标准。

ISP逻辑器件系列

目前,商品化的在系统可编程逻辑器件有 (1)ISPLSI (2)ISPGAL (3)ISPGDS(Generic Digital Switch).

ISP逻辑器件系列

一、ispLSI系列

美国Lattice公司是世界上第一片GAL诞生地.特别是九十年 代发明并率先推出的ISP技术,开拓了新一代的ttice公 司已将ISP技术应用到高密度可编程逻辑器件(HDPLD)中,形 成ispLSI系列高密度在系统可编程逻辑器件.

可变成逻辑器件厂商

随着可编程逻辑器件应用的赢利吸力和日益广泛,许多IC制 造厂家涉足PLD/FPGA领域。目前世界上有十几家生产 CPLD/FPGA的公司,最大的三家是:ALTERA,XILINX, Lattice,其中ALTERA和XILINX占有了60%以上的市场份额。 3、 Lattice:Lattice是ISP技术的发明者, ISP技术极大的 促进了PLD产品的发展,与ALTERA和XILINX相比,其开发 工具比ALTERA和XILINX略逊一筹。中小规模PLD比较有特 色,不过其大规模PLD、FPGA的竞争力还不够强 1999年 推出可编程模拟器件。99年收购Vantis(原AMD子公司), 成为第三大可编程逻辑器件供应商。2001年12月收购agere 公司(原Lucent微电子部)的FPGA部门。主要产品有 ispLSI2000/5000/8000, MACH4/5,ispMACH4000等

数字系统设计课件(自制)第4章

并口18-25是地线,其他线分成三类,8根数据线,可进行数据输出,5根状态线, 输入,四根控制线,输出。设置成JTAG口。

主系统通用 10针标准 配置/下载接口

PIN1

目标板10针标准 配置接口

OTP配置器件插座 配置器件插座 配置器件

将编程完毕的配置 器件插在相应的 电路系统上

4.2.4 PAL结构原理 结构原理

4.2 简单 简单PLD结构原理 结构原理

2.2.4 PAL结构原理 结构原理

4.2.5 GAL结构原理 结构原理

4.2 简单 简单PLD结构原理 结构原理

4.2.5 GAL结构原理 结构原理

(1)寄存器模式 )

4.2 简单 简单PLD结构原理 结构原理

(2)复合模式 ) 1、组合输出双向口结构 、

2.5.2 JTAG边界扫描测试 边界扫描测试

4.5 硬件测试

4.5.2 JTAG边界扫描测试 边界扫描测试

4.6 PLD产品概述 产品概述

4.6.1 Lattice公司的 公司的PLD器件 公司的 器件

1. ispLSI系列器件 系列器件 2. MACHXO系列 系列 3. MACH4000系列 系列 4. LatticeSC FPGA系列 系列 5. LatticeECP3 FPGA系列 系列

其他PLD公司: 公司: 其他 公司 ACTEL公司: ACT1/2/3、40MX 公司: 公司 、 ATMEL公司:ATF1500AS系列、40MX 公司: 系列、 公司 系列 CYPRESS公司 公司 QUIKLOGIC公司 公司

SO MUCH IC!

FPGA CPLD

三大可编程逻辑器件公司样片

封装形式 20 脚 PL 、32 脚 TQFP CC 8 脚 PDIP、20 脚PLCC 8 脚 PDIP、20 脚PLCC 8 脚 PDIP、20 脚PLCC、32 脚TQFP 8 脚 PDIP、20 脚PLCC、32 脚TQFP 8 脚 PDIP、20 脚PLCC、32 脚TQFP

课后习题答案第8章_存储器和可编程逻辑器件

第8章半导体存储器和可编程逻辑器件8-1存储器按读写功能以及信息的可保存性分别分为哪几类?并简述各自的特点。

解答:存储器按读写功能可分为只读存储器(ROM)和随机存储器(RAM)。

随机存取存储器在工作过程中,既可从其任意单元读出信息,又可以把外部信息写入任意单元。

因此,它具有读、写方便的优点,但由于具有易失性,所以不利于数据的长期保存。

只读存储器在正常工作时其存储的数据固定不变,只能读出,不能随时写入。

ROM为非易失性器件,当器件断电时,所存储的数据不会丢失。

存储器按信息的可保存性可分为易失性存储器和非易失性存储器。

易失性存储器在系统关闭时会失去存储的信息,它需要持续的电源供应以维持数据。

非易失存储器在系统关闭或无电源供应时仍能保持数据信息。

8-2什么是SRAM?什么是DRAM?它们在工作原理、电路结构和读/写操作上有何特点?解答:SRAM(Static Random Access Memory)为静态随机存储器,其存储单元是在静态触发器的基础上附加控制电路构成的。

DRAM(Dynamic Random Access Memory)为动态随机存储器,常利用MOS管栅极电容的电荷存储效应来组成动态存储器,为了避免存储信息的丢失,必须定时地对电路进行动态刷新。

SRAM的数据由触发器记忆,只要不断电,数据就能保存,但其存储单元所用的管子数目多,因此功耗大,集成度受到限制。

DRAM一般采用MOS管的栅极电容来存储信息,由于电荷保存时间有限,为避免存储数据的丢失,必须由刷新电路定期刷新,但其存储单元所用的管子数目少,因此功耗小,集成度高。

SRAM速度非常快,但其价格较贵;DRAM的速度比SRAM慢,不过它比ROM 快。

8-3若RAM的存储矩阵为256字⨯4位,试问其地址线和数据线各为多少条?解答:存储矩阵为256字⨯4位的RAM地址线为8根,数据线为4根。

8-4某仪器的存储器有16位地址线,8位数据线,试计算其最大存储容量是多少?解答:最大存储容量为216⨯8=524288=512k bit(位)8-5用多少片256⨯4位的RAM可以组成一片2K⨯8位的RAM?试画出其逻辑图。

(完整版)Xilinx+CPLD介绍

Xilinx CPLD系列产品1.1 简介Xilinx CPLD 系列器件包括XC9500系列器件、CoolRunner XPLA 和CoolRunner-Ⅱ系列器件。

Xilinx CPLD器件可使用Foundation或ISE开发软件进行开发设计,也可使用专门针对CPLD器件的Webpack开发软件进行设计。

1.1.1 XC9500系列CPLD器件Xilinx 公司的CPLD器件被广泛地应用在通信系统、网络、计算机系统及控制系统等电子系统中。

XC9500系列CPLD器件的t PD最快达3.5ns,宏单元数达288个,可用门数达6400个,系统时钟可达到200MHz。

XC9500系列器件采用快闪存储技术(FastFLASH),与E2CMOS 工艺相比,功耗明显降低。

XC9500系列产品均符合PCI总线规范;含JTAG测试接口电路,具有可测试性;具有在系统可编程(In System Programmable,ISP)能力。

XC9500系列器件分XC9500 5V器件、XC9500XL 3.3V器件和XC9500XV 2.5V器件3种类型,XC9500系列可提供从最简单的PAL综合设计到最先进的实时硬件现场升级的全套解决方案。

表1-1~表1-3分别列出了XC9500、XC9500XL和XC9500XV系列器件的基本特征。

表1-4~表1-6则分别列出了XC9500、XC9500XL和XC9500XV器件的封装和I/O引脚数。

其中f CNT代表16位计数器操作频率,f sys表示一般目标系统设计中生成多重功能块所需的内部操作频率。

表1-1 XC9500系列器件特征表1-2 XC9500XL系列器件特征表1-3 XC9500XV系列器件特征表1-4 XC9500 CPLD封装及I/O引脚数·7·表1-6 XC9500XV CPLD封装及I/O引脚数(不包括4个专用JTAG引脚)XC9500系列产品采用第二代“支持ISP”的引脚锁定结构,它拥有一个54bit输入函数块,使用户可以在进行多种改变的同时保持输出引脚固定。

采用ispLSI1016芯片设计数控系统的位置板

采用ispLSI1016芯片设计数控系统的位置板大连理工大学林乐忠王永青胡力耘摘要采用新型的大规模可编程集成芯片)))ispL SI1016设计数控系统中的位置板,与采用其它IC芯片设计的位置板相比,可改善整个位置环的逻辑和电气特性,对于提高整个数控系统的加工精度和可靠性,具有实用价值。

关键词:ispLSI1016计数器位置反馈Design of Position Feedback C ard of NC System with the ispLSI1016DeviceLin Lezhong Wang Yongqing Hu LiyunAbstract T he autho r desig ns and develops the position feedback card w ith the new insystem pro-gr ammable large scale integ ration device)paring with using the other g ener al IC de-vices,this card can improv e the logic and electr ic character i stics o f the whole position loop of N C system.T his design has a practical meaning for raising the pr ecisio n,reliability of the N C sytem.Key Words:ispLSI1016;counter;position feedback1引言位置板是实现闭环数控系统的关键硬件,其特性好坏直接影响整个数控系统的性能。

大型精密数控机床的运动部件行程较长,必须用位数多的位置板构成位置环,以实现位置闭环控制,这要求设计多位计数器。

用标准的IC芯片或一般的可编程逻辑器件PLD(如PAL、GAL等)可以完成这一设计,但是由于此类芯片的功能与管脚有限,而设计要求的逻辑较复杂,以致设计所用的芯片个数会过多,电路板的尺寸过大,同时电路的时延问题严重,时序难以保证,从而使设计难度增大。

MPU软件简介

一、软件简介在热处理、锻造前加热和熔炼热备存在大量的中频感应加热设备,这些设备大多采用晶闸管变频电源。

这类设备大多是工厂里的主要设备,一旦出现故障,会造成工厂的生产线停产,造成较大的经济损失。

维修这类设备需要专门的人员,设备控制线路有事整个设备的核心,它的好坏决定了设备整个工作性能,目前主要有以下几种方案:1、采用分立件的控制线路;这种线路接线复杂,控制板数量多需要10块以上的,调试复杂,对调试和维修人员有较高的要求。

2、采用集成电路的控制线路;这种线路控制板数量减少到3块以下,但由于采用的集成电路较多,参数的一致性差,控制线路维修复杂,升级和调试复杂。

3、采用单片机的控制线路;这种线路集成度高,但抗干扰性差,需要大量的光耦隔离,还需要专门的电源供电和布线,提高了设备的制造难度。

为了达到设备稳定,抗干扰性好、调试与维修简单,我们采用大规模可编程逻辑器件(CPLD)作为控制线路的核心芯片,实现了中频感应加热系统控制系统的升级。

该芯片主要完成了整流脉冲移相与和成;保护电路;逆变脉冲的产生和逆变同步鉴相器以及几个专用定时器。

此次设计选用了美国LITTICE公司生产的ISPLSI1016-60LJ作为控制线路的核心芯片,它有44个引脚,其中包括32个I/O引脚,4个专用引脚,2个电源引脚,2个地引脚。

集成密度位2000个门电路,引脚到引脚延迟位4.5---20nS,工作频率位60MHz,,工作电压位5v。

此芯片程序有VHD语言编写而成,主要有几个子程序和主程序组成。

子程序有8为计数器程序;16倍分频器,保护锁存器;整流同步信号处理程序和定时器组成。

有主程序调用相应的子程序和一些相关的语句,完成了芯片的全部功能。

二、芯片软件子程序详解1、8位计数器程序该程序实现了对信号240次计数器,当计到240次时,输出高电平。

设有复位端,复位时,输出低电平,主程序清单如下:library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_unsigned.all;//此为定义库文件entity jsq isport (clk,res,r: in std_logic;out1: out std_logic);end;//CLK 为计数器时钟信号,RES为计数器的复位信号R为脉冲处理信号以上均为输入信号OUT1为计数器输出信号以上为子程序传递信号;architecture jxq_arc of jsq issignal o:std_logic;//o 为条件信号beginprocess (res,clk)variable count:integer range 0 to 240;//count 计数器子程序内部信号技术次数beginif res='1' then //检测计数器复位信号count:=0; //计数器清0out1<='0'; //输出为低电平o<='0'; //条件信号为0elsif clk'event and clk='1' then //检测计数器时钟信号,电平上升沿有校if count=240 thenif r/='0' or o='1' then //检测条件信号,输出计数结果out1<='0';o<='1';elseout1<='1';o<='0';end if;elseout1<='0';count:=count+1;//计数器加1end if;end if;end process;end jxq_arc;计数器的原理:当复位信号(RES)为高电平时,输出为低电平,计数器清0,条件信号O为0。

EDA技术及应用—Verilog HDL版(第三版) (1)

第2章 大规模可编程逻辑器件

(4) 封装代码。如Altera公司的EPM7128SLC84中的LC, 表示采用PLCC封装(Plastic Leaded Chip Carrier,塑料方形扁 平封装)。PLD封装除PLCC外,还有BGA(Ball Grid Array, 球形网状阵列)、C/JLCC(Ceramic /J-Leaded Chip Carrier,)、 C/M/P/TQFP(Ceramic/Metal/Plastic/Thin Quard Flat Package)、 PDIP/DIP(Plastic Double In line Package)、PGA(Ceramic Pin Grid Array)等,多以其缩写来描述,但要注意各公司稍有差 别,如PLCC,Altera公司用LC描述,Xilinx公司用PC描述, Lattice公司用J来描述。

第2章 大规模可编程逻辑器件

2.1.1 PLD的发展进程

最早的可编程逻辑器件出现在20世纪70年代初,主要是 可编程只读存储器(PROM)和可编程逻辑阵列(PLA)。20世 纪70年代末出现了可编程阵列逻辑(Programmable Array Logic,简称PAL)器件。20世纪80年代初期,美国Lattice公 司推出了一种新型的PLD器件,称为通用阵列逻辑(Generic Array Logic,简称GAL),一般认为它是第二代PLD器件。 随着技术进步,生产工艺不断改进,器件规模不断扩大,逻 辑功能不断增强,各种可编程逻辑器件如雨后春笋般涌现, 如PROM、EPROM、EEPROM等。

第2章 大规模可编程逻辑器件

采用ISP技术之后,硬件设计可以变得像软件设计那样灵活 而易于修改,硬件的功能也可以实时地加以更新或按预定的 程序改变配置。这不仅扩展了器件的用途,缩短了系统的设 计和调试周期,而且还省去了对器件单独编程的环节,因而 也省去了器件编程设备,简化了目标系统的现场升级和维护 工作。

HQFC-B1教师实验指导书

目 录第一章HQFC-B1计算机组成和数字逻辑实验系统介绍 (3)一、HQFC-B1实验系统的特点 (3)二、HQFC-B1实验系统的组成 (5)三、HQFC-B1监控使用说明 (13)四、HQFC-B1教学软件使用说明 (17)五、USB-COM通讯线使用说明 (20)第二章计算机组成原理实验 (30)第一节、寄存器实验 (30)第二节、运算器组成实验 (33)第三节、双端口存储器原理实验 (37)第四节数据通路组成实验 (42)一、寄存器读写 (44)二、写寄存器内容到存储器 (46)三、写存储器到寄存器 (48)四、寄存器堆RF并行输入输出 (51)第五节常规型微过程控制器组成实验 (52)第六节CPU组成与机器指令执行实验 (66)第七节中断原理实验 (70)第三章可编程逻辑简介 (74)第一节可编程逻辑器件简介 (74)第二节VHDL语言简介 (77)第三节Q UARTUS II软件使用说明 (87)第四章硬布线控制器 (101)第一节硬布线控制器简介 (101)第二节硬布线控制设计 (106)第五章课程设计 (121)第一节流水微程序控制器的设计与调试 (121)第二节流水硬布线控制器的设计与调试 (129)第六章数字逻辑门和数字系统实验 (133)第一节基本逻辑门逻辑实验 (133)第二节TTL、HC和HCT器件的电压传输特性 (135)第三节三态门实验 (138)第四节数据选择器和译码器 (140)第五节全加器构成及测试 (141)第六节组合逻辑中的冒险现象 (143)第七节触发器 (144)第八节简单时序电路 (147)第九节计数器 (152)第十节四相时钟分配器 (155)第十一节可编程逻辑控制器CPLD (157)实验一、3-8译码器实验 (157)实验二、D触发器实验 (159)实验三、简易分频器实验 (161)实验四、简易交通灯控制实验 (162)实验五、七段LED数码管显示实验 (165)实验四、简易计数器实验 (168)附录 (172)附录一常用实验器件引脚图 (172)附录二CPLD管脚分配图 (175)附录三控制器与数据通路信号 (177)第一章HQFC-B1计算机组成和数字逻辑实验系统介绍HQFC-B1它适用于《计算机组成原理》、《计算机组织和结构》和《数字逻辑和数字系统》三门课程的实验教学,是一种多用仪器。

TPlink TL-SF1016D交换机说明书

表表表表表指示灯工作状态描述

2 16/24/48个10/100Mbps自适应RJ45端口 支持10Mbps或100Mbps速率自适应功能,支持自动翻转(Auto MDI/MDIX)功 能,每个端口对应有一组指示灯,即Link/Act和100Mbps指示灯。

TL-S F1016 D/ TL-S F1024D交换 机前面板由16/24个10/10 0 Mbps自适应RJ4 5端口和 相关的指示灯组成,如图1-2所示(以TL-SF1024D为例说明)。

I

声明

相关文档

除本安装手册外,如需获取最新产品资料,请登录。

文档名称 《百兆非网管交换机安装手册》

用途 介绍了该系列交换机的安装和启动过程

安装手册简介

《百兆非网管交换机安装手册》主要介绍了TL-SF1016S/ TL-SF1024S/ TLS F10 4 8S/ TL-S F1016 D/ TL-S F1024D交换 机的硬件特性、安装方法以及在安装过 程中应注意事项。 本手册包括以下章节: 第1章:产品介绍。简述交换机的基本功能特性并详细介绍外观信息。 第2章:产品安装。指导交换机的硬件安装方法以及注意事项。 第3章:硬件连接。指导交换机与其他设备之间的连接及注意事项。 附录A:技术参数规格。

该图标表示需引起重视的警告事项。

该图标表示提醒操作中应注意的事项,如果操作错误可能导致设 备损坏等不良后果。

该图标表示对操作内容的描述进行必要的补充和说明。

III 阅读对象

目录

第1章 产品介绍 —————————— 01

1.1 产品简介 ....................................................................01 1.2 产品外观 ....................................................................01

ISP在系统编程技术

谭 敏电子信息与电气工程系

ALTERA 的 ByteBlaster(MV)下载接口

此接口既可作编 程下载口, 程下载口,也可作 JTAG接口 接口

Joint Test Action Ggroup

谭 敏电子信息与电气工程系

3.2.编程方式 . .

1、计算机并口

七芯电缆

下载电缆

ISP器件(接插件RJ45)

IDCODE指令模式 指令模式

管芯尺寸比较

谭 敏电子信息与电气工程系

Altera EPF10K100E 相对管芯尺寸: 0.6 0.25 µ工艺 4,992个逻辑单元(LE) 12 个EAB

* 1个 CLB 相当于 2 两个LE

Altera EPF10K100A 相对管芯尺寸: 1.0 0.35 µ工艺 4,992个逻辑单元(LE) 12 个EAB

10芯下载口 芯下载口

接口各引脚信号名称

引脚 PS 模式 JATG 模式 1 DCK TCK 2 GND GND 3 CONF_DONE TDO 4 VCC VCC 5 nCONFIG TMS 6 7 nSTA TUS 8 9 DATA0 TDI 10 GND GND

PS: Passive Serial 被动串行模式 JTAG: Joint Test Action Group 20世纪80年代联合测试行动组开发的技术规范

3.5.1 内部逻辑测试 3.5.2 JTAG边界扫描测试 边界扫描测试

图3-41 边界扫描电路结构

谭 敏电子信息与电气工程系

4.2 JTAG边界扫描测试 边界扫描测试 边界扫描IO引脚功能 表4-1 边界扫描 引脚功能

引 脚 TDI 描 述 测试数据输入 (Test Data Input) TDO 测试数据输出 (Test Data Output) TMS 测试模式选择 (Test Mode Select) TCK 测试时钟输入 (Test Clock Input) TRST 测试复位输入 (Test Reset Input) 低电平有效,异步复位边界扫描电路(在 IEEE 规范中,该引脚可选)。 测试指令和编程数据的串行输出引脚,数据在 TCK 的下降沿移出。如果数据 没有被移出时,该引脚处于高阻态。 控制信号输入引脚,负责 TAP 控制器的转换。TMS 必须在 TCK 的上升沿到 来之前稳定。 时钟输入到 BST 电路,一些操作发生在上升沿,而另一些发生在下降沿。 功 能 测试指令和编程数据的串行输入引脚。数据在 TCK 的上升沿移入。

pld概述

硬件设计和软件设计

EDA技术

2.电子设计自动化(EDA)技术 Electronic Design Automation

即利用计算机完成电子系统设计。借助于 软件设计平台,自动完成数字系统的逻辑综合、 布局布线、仿真等工作。最后下载到芯片,实 现设计方案。设计者只需完成对系统功能的描 述,就可以由计算机软件进行处理,得到设计 结果。修改设计如同修改软件一样方便。

(3). 适配(Fit)

适配器也称结构综合器,它的功能是将由综合器产生的 网表文件配臵于指定的目标器件中,使之产生最终的下载文 件,如JEDEC、Jam格式的文件。适配所选定的目标器件 (FPGA/CPLD芯片)必须属于原综合器指定的目标器件系列。 逻辑综合通过后必须利用适配器将综合后网表文件针对某 一具体的目标器件进行逻辑映射操作,其中包括底层器件配 臵、逻辑分割、逻辑优化、逻辑布局布线操作。适配完成后 可以利用适配所产生的仿真文件作精确的时序仿真,同时产 生可用于编程的文件。

ALTERA

XILINX

4.FPGA/CPLD生产商

LATTICE VANTIS (AMD)

CPLD: ispLSI系列:1K、2K、3K、5K、 8K ispLSI1016 、ispLSI2032、 ispLSI1032E、ispLSI3256A MACH系列 ispPAC系列:

其它PLD公司: ACTEL公司: ACT1/2/3、40MX ATMEL公司:ATF1500AS系列、40MX CYPRESS公司: QUIKLOGIC公司:

• FPGA – 反熔丝(Actel) – RAM(Xillinx)

3.器件规模

CPLD 集成规模 小(最大数万门) 单元粒度 大(PAL结构) 互连方式 集总总线 编程工艺 EPROM、 EEROM、Flash 编程类型 ROM型 FPGA 大(最高达百万门) 小(PROM结构) 分段总线、长线、专 用互连 SRAM RAM型,须与存储 器连用

第3章常用EDA软件

元件符号;还可以在原理图编辑器中选择Add/New

Block Symbol,然后按提示输入符号的输入输出信号 名;输入完后,按Run键,会自动产生一个元件符号, 并放入元件库中;选择符号并移入原理图中;完成原 理图文件设计。

3.1 ISP Design Expert System

完成下层文件设计: 项目管理器中,源文件左边的“?”图标,提示这个 源文件还是未知数,而且可以看出源文件的层次结构;

3.1.2 原理图源文件输入

添加原理图输入源

3.1.2 原理图源文件输入添加元件符号:A源自D/Symbol,选择相应元件,将鼠标

移到图纸的适当位置,单击鼠标;

添加输入、输出符号(对应外部引脚时需要):从

IOPAD.LIB库选择G-INPUT、G-OUTPUT管脚放到图纸上;

连线:Add/Wire,单击开始画线,随后每次单击鼠

3.1.3 功能时序仿真

仿真分功能仿真和时间仿真 输入波形文件(*.wet)或测试向量文件(*.wdl)

启动仿真。

3.1.3 功能时序仿真

建立测试信号文件(*.wdl) 1.选择Source/New/Waveform Stimulus; 2.选择与测试文件关联的器件或设计文件; 3.输入波形文件名,进入波形编辑窗口。

3.1.4 器件编程(下载)

3.1 ISP Design Expert System

例2:触发器设计计数器 例3:调用宏单元: 计数器CBU14 显示译码器bin27

3.1 ISP Design Expert System 例4:图形层次设计法

建立顶层原理图文件,其中可以调用上面用户创建的

3、修改系统日期到2000年9月以前。

3.1.1 建立设计项目

(完整版)FPGA型号命名规则

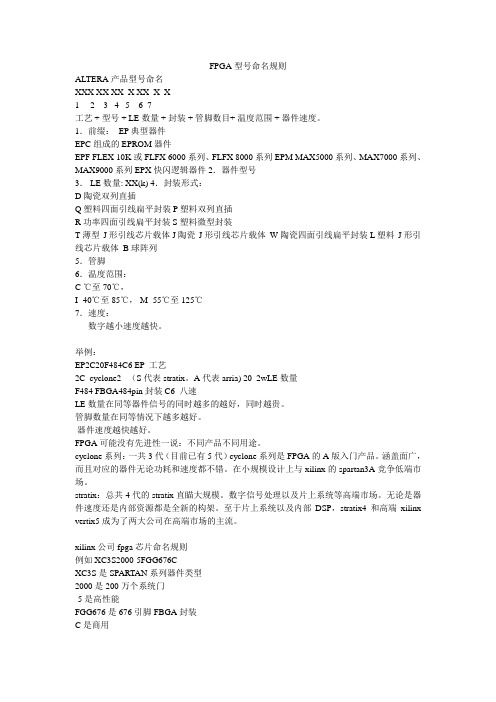

FPGA型号命名规则ALTERA产品型号命名XXX XX XX X XX X X1 2 3 4 5 6 7工艺 + 型号 + LE数量 + 封装 + 管脚数目+ 温度范围 + 器件速度。

1.前缀: EP 典型器件EPC 组成的EPROM 器件EPF FLEX 10K 或FLFX 6000 系列、FLFX 8000 系列 EPM MAX5000 系列、MAX7000 系列、MAX9000 系列 EPX 快闪逻辑器件 2.器件型号3. LE数量: XX(k) 4.封装形式:D 陶瓷双列直插Q 塑料四面引线扁平封装 P 塑料双列直插R 功率四面引线扁平封装 S 塑料微型封装T 薄型J 形引线芯片载体 J 陶瓷J 形引线芯片载体 W 陶瓷四面引线扁平封装 L 塑料J 形引线芯片载体 B 球阵列5.管脚6.温度范围:C ℃至70℃,I -40℃至85℃, M -55℃至125℃7.速度:数字越小速度越快。

举例:EP2C20F484C6 EP 工艺2C cyclone2 (S代表stratix。

A代表arria) 20 2wLE数量F484 FBGA484pin 封装 C6 八速LE数量在同等器件信号的同时越多的越好,同时越贵。

管脚数量在同等情况下越多越好。

器件速度越快越好。

FPGA可能没有先进性一说:不同产品不同用途。

cyclone系列:一共3代(目前已有5代)cyclone系列是FPGA的A版入门产品。

涵盖面广,而且对应的器件无论功耗和速度都不错。

在小规模设计上与xilinx的spartan3A竞争低端市场。

stratix:总共4代的stratix直瞄大规模。

数字信号处理以及片上系统等高端市场。

无论是器件速度还是内部资源都是全新的构架。

至于片上系统以及内部DSP,stratix4和高端xilinx vertix5成为了两大公司在高端市场的主流。

xilinx公司fpga芯片命名规则例如XC3S2000-5FGG676CXC3S是SPARTAN系列器件类型2000是200万个系统门-5是高性能FGG676是676引脚FBGA封装C是商用常用CPLD/FPGA 标识的含义CPLD/FPGA生产厂家多,系列、品种更多,各生产厂家命名、分类不一,给CPLD/FPGA 的应用带来了一定的困难,但其标识也是有一定的规律的。

第七讲 可编程逻辑器件结构与原理

可编程

可编程 可编程

可编程

固定 固定

固定

固定 可编程 OLMC

PAL器件的阵列结构

3、逻辑宏单元

PLD器件中的与-或阵列只能实现组合逻辑电路的功能,要实现 时序逻辑功能则需要有包含触发器或寄存器的逻辑宏单元 (OLMC)来实现 例:GAL16V8的OLMC可配置成4种工作模式(AC1(n) AC0): 专用输入、专用组合输出、选通组合输出、寄存器型输出P118

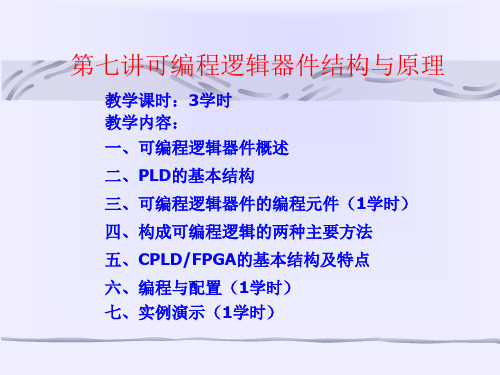

第七讲可编程逻辑器件结构与原理

教学课时:3学时 教学内容: 一、可编程逻辑器件概述 二、PLD的基本结构

三、可编程逻辑器件的编程元件(1学时)

四、构成可编程逻辑的两种主要方法 五、CPLD/FPGA的基本结构及特点

六、编程与配置(1学时) 七、实例演示(1学时)

一、可编程逻辑器件概述

可编程逻辑器件是ASIC的一个重要分支, 它是一种由用户编程以实现某种逻辑功 能的新型器件,故可编程逻辑器件也称 为可编程ASIC。

查找表原理

输入 A 0

0 0 0 0 0 0 1

输入 B 0

输入C 1

输入D 0 多路选择器

16x1 RAM

1 0 0 0 0 0 0 0 1 1

查 找 表 输 出 (0100)0

FPGA/CPLD生产商

FPGA: FLEX系列:10K、10A、10KE,EPF10K30E APEX系列:20K、20KE EP20K200E ACEX系列:1K系列 EP1K30、EP1K100 STRATIX系列:EP1系列 EP1S30、EP1S120 CPLD: MAX7000/S/A/B系列:EPM7128S MAX9000/A系列 FPGA: XC3000系列, XC4000系列, XC5000系列 Virtex系列 SPARTAN系列:XCS10、XCS20、XCS30 CPLD: XC9500系列:XC951清零 选择

256级灰度LED点阵屏显示原理及基于FPGA的电路设计

256级灰度LED点阵屏显⽰原理及基于FPGA的电路设计www.eaw.com.cn电⼦设计应⽤2004.151表1数据位点亮与关断的时间分配表3 分19场显⽰时各位的点亮与关断时间表2 00H到FFH时的不同点亮时间表4 19场显⽰时00H ̄FFH范围的总点亮时间引⾔256级灰度LED点阵屏在很多领域越来越显⽰出其⼴阔的应⽤前景,本⽂提出⼀种新的控制⽅式,即逐位分时控制⽅式。

随着⼤规模可编程逻辑器件的出现,由纯硬件完成的⾼速、复杂控制成为可能。

逐位分时点亮⼯作原理所谓逐位分时点亮,即从⼀个字节数据中依次提取出⼀位数据,分8次点亮对应的像素,每⼀位对应的每⼀次点亮时间与关断时间的占空⽐不同。

如果点亮时间从低位到⾼位依次递增,则合成的点亮时间将会有256种组合。

定义点亮时间加上关断时间为⼀个时间单位,设为T 。

表1列出了每⼀位的点亮与关断的时间分配。

如果定义数据位“1”有效(点亮),“0”⽆效(熄灭),则表2列出了数据从00H到FFH时的不同点亮时间。

由表2可知:数据每增1,点亮时间增加T/128。

根据点亮时间与亮度基本为线性关系的原理,从0 ̄255T/128的点亮时间则对应256级亮度。

当然,这个亮度是时间上的累加效果。

如果把⼀个LED点阵屏所有像素对应的同⼀数据位点亮⼀遍称为⼀场的话,那么8位数据共需8场显⽰完,称为“8场原理”。

理论上讲,8场即可显⽰出256级灰度,然⽽通过表2可看出,即使数据为FFH时,在8T时间内也只是点亮了255T/128时间。

关断时间可接近6T,点亮时间仅为总时间的约25%,因此,8场原理虽也能实现256级灰度显⽰,但亮度损失太⼤。

为了提⾼亮度,可采⽤“19场原理”,即8位数据分19场显⽰完,其中D7位数据连续显⽰8场,D6位连续显⽰4场,依次递减。

表3列出了各位的点亮与关断时间。

由表3可推导出数据从00H ̄FFH范围的总点亮时间,如表4所⽰。

在19T时间内,最⼤点亮时间可达近16T, 占总时间的84.21%,256级灰度LED点阵屏显⽰原理及基于FPGA的电路设计■郑州防空兵学院电⼦教研室魏银库陈建国狄国伟2004.1电⼦设计应⽤www.eaw.com.cn52图1FPGA内部电路远⼤于“8场原理”的25%。

tl-sf1016交换机说明书

第 3 章 配置软件的安装及使用 ........................................................ 6

3.1 配置软件RSSManager安装...........................................................................................6

2.3.1 2.3.2

前面板 ................................................................................................................3 后面板 ................................................................................................................4

2.2 产品特性 .......................................................................................................................3

2.3 交换机的外观 ................................................................................................................3

TL-SF1008L/TL-SF1016L/TL-SF1024L 8/16/24 口楼道交换机

物品清单

请小心打开包装盒,里面应有以 一张光盘 两个 L 型支架及其它配件 ᓖፀǖ

FPGA命名规则

Altera的命名规则如下的命名规则如下::工艺+版本+型号+LE数量+封装+器件速度。

举例:EP2C20F484C6EP 工艺2C cyclone2 (S代表stratix。

A代表arria)20 2wLE数量F484 FBGA484pin 封装C6 八速数字越小速度越快。

那么首先:LE数量在同等器件信号的同时越多的越好。

同时越贵管脚数量在同等情况下越多越好。

器件速度越快越好。

FPGA可能没有先进性一说:不同产品不同用途。

cyclone系列:一共3代cyclone系列是FPGA的A版入门产品。

涵盖面广,而且对应的器件无论功耗和速度都不错。

在小规模设计上与xilinx的spartan3A竞争低端市场。

stratix:总共4代的stratix直瞄大规模。

数字信号处理以及片上系统等高端市场。

无论是器件速度还是内部资源都是全新的构架。

至于片上系统以及内部DSP,stratix4和高端xilinx vertix5成为了两大公司在高端市场的主流。

ALTERA产品型号命名XXX XX XX X XX X X1 2 3 4 5 6 7工艺+ 型号+ LE数量+ 封装+ 管脚数目+ 温度范围+ 器件速度。

1.前缀:EP 典型器件EPC 组成的EPROM 器件EPF FLEX 10K 或FLFX 6000 系列、FLFX 8000 系列EPM MAX5000 系列、MAX7000 系列、MAX9000 系列EPX 快闪逻辑器件2.器件型号3.LE数量: XX(k)4.封装形式:D 陶瓷双列直插Q 塑料四面引线扁平封装P 塑料双列直插R 功率四面引线扁平封装S 塑料微型封装T 薄型J 形引线芯片载体J 陶瓷J 形引线芯片载体W 陶瓷四面引线扁平封装L 塑料J 形引线芯片载体B 球阵列5.管脚6.温度范围:C ℃至70℃,I -40℃至85℃,M -55℃至125℃7.速度:数字越小速度越快。

xilinx公司fpga芯片命名规则例如XC3S2000-5FGG676CXC3S是SPARTAN系列器件类型2000是200万个系统门-5是高性能FGG676是676引脚FBGA封装C是商用常用CPLD/FPGA 标识的含义CPLD/FPGA生产厂家多,系列、品种更多,各生产厂家命名、分类不一,给CPLD/FPGA 的应用带来了一定的困难,但其标识也是有一定的规律的。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

figure 1). The outputs of the eight GLBs are connected to GLBs and I/O cells. The Clock Distribution Network can

a set of 16 universal I/O cells by the ORP. The ispLSI also be driven from a special clock GLB (B0 on the ispLSI

— tpd = 20 ns Propagation Delay

B P — TTL Compatible Inputs and Outputs

— Electrically Erasable and Reprogrammable — Non-Volatile E2CMOS Technology — 100% Tested

ispLSI® 1016/883

In-System Programmable High Density PLD

Features

Functional Block Diagram

• HIGH-DENSITY PROGRAMMABLE LOGIC

— High-Speed Global Interconnect — 2000 PLD Gates — 32 I/O Pins, Four Dedicated Inputs

H U 1 • COMBINES EASE OF USE AND THE FAST SYSTEM - SPEED OF PLDs WITH THE DENSITY AND FLEX-

IBILITY OF FIELD PROGRAMMABLE GATE ARRAYS

E IN — Complete Programmable Device Can Combine Glue A Logic and Structured Designs

The basic unit of logic on the ispLSI 1016/883 device is the Generic Logic Block (GLB). The GLBs are labeled A0, A1 .. B7 (see figure 1). There are a total of 16 GLBs in the ispLSI 1016/883 device. Each GLB has 18 inputs, a programmable AND/OR/XOR array, and four outputs which can be configured to be either combinatorial or registered. Inputs to the GLB come from the GRP and

N — 96 Registers

— Wide Input Gating for Fast Counters, Sders, etc.

E — Small Logic Block Size for Random Logic R — Security Cell Prevents Unauthorized Copying E • HIGH PERFORMANCE E2CMOS® TECHNOLOGY E — fmax = 60 MHz Maximum Operating Frequency

January 2002

1016mil_02

1

Specifications ispLSI 1016/883

Functional Block Diagram

Figure 1. ispLSI 1016/883 Functional Block Diagram

Generic Logic Blocks

(GLBs)

dedicated inputs. All of the GLB outputs are brought back

into the GRP so that they can be connected to the inputs

of any other GLB on the device.

Copyright © 2002 Lattice Semiconductor Corp. All brand or product names are trademarks or registered trademarks of their respective holders. The specifications and information herein are subject to change without notice.

1016/883 device contains two of these Megablocks.

1016/883 device). The logic of this GLB allows the user

to create an internal clock from a combination of internal

Output Routing Pool Output Routing Pool

A0

B7

A1

DQ

B6

A2

DQ

B5

Logic

A3

Array D Q GLB

B4

A4

B3

DQ

A5

B2

A6

B1

A7 Global Routing Pool (GRP) B0

CLK

Description

The ispLSI 1016/883 is a High-Density Programmable Logic Device processed in full compliance to MIL-STD883. This military grade device contains 96 Registers, 32 Universal I/O pins, four Dedicated Input pins, three Dedicated Clock Input pins and a Global Routing Pool (GRP). The GRP provides complete interconnectivity between all of these elements. The ispLSI 1016/883 features 5Volt in-system programming and in-system diagnostic capabilities. It is the first device which offers non-volatile reprogrammability of the logic, as well as the interconnect to provide truly reconfigurable systems.

Clocks in the ispLSI 1016/883 device are selected using the Clock Distribution Network. Three dedicated clock

pins (Y0, Y1 and Y2) are brought into the distribution

TTL compatible voltages and the output drivers can

D source 4 mA or sink 8 mA.

The GRP has as its inputs the outputs from all of the GLBs and all of the inputs from the bi-directional I/O cells. All of these signals are made available to the inputs of the GLBs. Delays through the GRP have been equalized to minimize timing skew.

VIC NT #05 ispEN

Y0 Y1/RESET*

SCLK/Y2

*Note: Y1 and RESET are multiplexed on the same pin

0139B(1a)-isp.eps

E O N The device also has 32 I/O cells, each of which is directly

Input Bus Output Routing Pool (ORP)

Output Routing Pool (ORP) lnput Bus

EN R I/O0

I/O 1

E I/O 2 E I/O 3

I/O 4

B I/O 5 P I/O 6

I/O 7

I/O 8

S I/O 9 D I/O 10

I/O 11

S D • IN-SYSTEM PROGRAMMABLE — In-System Programmable™ (ISP™) 5-Volt Only A — Increased Manufacturing Yields, Reduced Time-toE 0 Market, and Improved Product Quality — Reprogram Soldered Devices for Faster Debugging

LATTICE SEMICONDUCTOR CORP., 5555 Northeast Moore Ct., Hillsboro, Oregon 97124, U.S.A. Tel. (503) 268-8000; 1-800-LATTICE; FAX (503) 268-8556;

— Three Dedicated Clock Input Pins

IC T 5 — Synchronous and Asynchronous Clocks