微机原理课件第8章

合集下载

微机原理第八章微型计算机的程序设计 ppt课件

mov ax, data

mov ds, ax

MOV AL, BYTE PTR W1

;AL=31H (+78H)

ADD AL, BYTE PTR W2 ;AL=A9H, CF=0,AF=0

DAA ;BCD数加法调整指令; AL=09H, CF=1

MOV SUM, AL

MOV AL, BYTE PTR W1+1 ; AL=89H (+56H)

MOV SUM, AL ;(SUM)=06H

MOV AL,AH; AL=09H

ADD AL, BYTE PTR W2+1 ; AL=09H+06H=0FH,属于第1种情况

MOV AH, 0

此句也可表达为MOV [SUM], AL; 见P151

AAA ; AL=05H, AH=01H

;第一种情况处理:AL=(AL+06H)&0FH, 因0FH+06H=15H,故 AL=05H,AH=AH+1=0+1=01H,所以AX=0105H

• W1

DW 8931H

• W2

DW 5678H

• SUM DB 3 DUP(0)

• data ends

• code segment

begin proc far

assume ss: stack, cs: code, ds:data

push ds

sub ax, ax

push ax

2020/9/18

10

2020/9/18

8

微机原理第八章微型计算机的程

序设计

AAA-----两个非压缩BCD数相加调 整指令

若(AL&0FH)>9或AF=1,则(AL+6)&0FH送AL,AH 加1且CF置1;

微机原理第八章 串行通信及串行接口

1. 可编程串行接口典型结构

✓状态寄存器

✓控制寄存器

✓数据输入寄存器--串行输入/并行 输出移位寄存器

✓数据输出寄存器--并行输入/串行 输出移位寄存器

2. 串行通信基本概念

在串行通信时,数据和联络信号使用同一条信号线 来传送,所以收发双方必须考虑解决如下问题: ❖ 波特率---双方约定以何种速率进行数据的发送和接收 ❖ 帧格式---双方约定采用何种数据格式 ❖ 帧同步---接收方如何得知一批数据的开始和结束 ❖ 位同步--- -接收方如何从位流中正确地采样到位数据 ❖ 数据校验--- -接收方如何判断收到数据的正确性 ❖差错处理---收发出错时如何处理 收发双方必须遵守一些共同的通信协议才能解决上述问题。

串行通信适于长距离、中低速通信

并行通信

将数据的各位同时在多根并行传输线上进行传输。

D0 0

D1 1

D2 0

源

D3 1

D4 D5

0 1

D6 1

D7 0

D0 D1 D2 D3 目 D4 的 D5 D6 D7

数据的各位同时由源到达目的地 → 快 多根数据线 → 短距离(远程费用高)

并行通信适于短距离、高速通信

工作方式下。

(8)错误检测 • 传输错误 • 覆盖错误

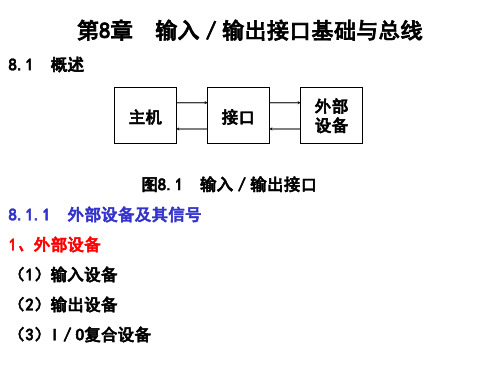

二、 接口与系统的连接

从结构上,可把接口分为两个部分,其中和 外设相连的接口结构与具体外设的传输要求及数 据格式相关,因此,各接口的该部分互不相同; 而与系统总线相连的部分,各接口结构类似,一 般都包括:

1. 总线收发器和相应的逻辑电路

2. 联络信号逻辑电路

接收端需要一个时钟来测定每一位的

时间长度。

波特率/位传输率---每秒传输的离散信号 的数目/每秒传输的位数。 波特率因子---

微机原理课件-第8章

ADC0809 IN0 IN1 IN2 IN3 IN4 ADDC ADDB ADDA

CPU用一条OUT指令把通道地址通过接口芯片送给ADC0809

ADC0809 IN0 IN1 IN2 IN3 IN4 ADDC ADDB ADDA 输 入

8255

DB

A1 A0

来自I/O 译码

D0-D7

74LS273

DX, start_port DX, AL DX, eoc_port AL, DX AL, 01H LL DX, oe_port AL, DX

;启动转换

;读入EOC状态 ;测试第0位(EOC状态位) ;未转换完,则循环检测 ;读入结果

主要技术指标

精度

量化间隔(分辨率) = Vmax/电平数(即满量程值)

例:某8位ADC的满量程电压为5V,则其分辨率为 5V/255=19.6mV

量化误差: 用数字(离散)量表示连续量时,由于数字 量字长有限而无法精确地表示连续量所造成的误差。 (字长越长,精度越高)

绝对量化误差 = 量化间隔/2 = (满量程电压/(2n-1))/2 相对量化误差 = 1/2 * 1/量化电平数目 * 100%

用延时等待的方法

…… MOV OUT CALL MOV IN …… DX, start_port DX, AL ;启动转换 DELAY_1MS ;延时1ms DX, oe_port AL, DX ;读入结果

用查询EOC状态的方法

…… MOV OUT LL: MOV IN AND JZ MOV IN ……A/D转 Nhomakorabea器的分类

根据A/D转换原理和特点的不同,可把ADC 分成两大类:直接ADC和间接ADC。

CPU用一条OUT指令把通道地址通过接口芯片送给ADC0809

ADC0809 IN0 IN1 IN2 IN3 IN4 ADDC ADDB ADDA 输 入

8255

DB

A1 A0

来自I/O 译码

D0-D7

74LS273

DX, start_port DX, AL DX, eoc_port AL, DX AL, 01H LL DX, oe_port AL, DX

;启动转换

;读入EOC状态 ;测试第0位(EOC状态位) ;未转换完,则循环检测 ;读入结果

主要技术指标

精度

量化间隔(分辨率) = Vmax/电平数(即满量程值)

例:某8位ADC的满量程电压为5V,则其分辨率为 5V/255=19.6mV

量化误差: 用数字(离散)量表示连续量时,由于数字 量字长有限而无法精确地表示连续量所造成的误差。 (字长越长,精度越高)

绝对量化误差 = 量化间隔/2 = (满量程电压/(2n-1))/2 相对量化误差 = 1/2 * 1/量化电平数目 * 100%

用延时等待的方法

…… MOV OUT CALL MOV IN …… DX, start_port DX, AL ;启动转换 DELAY_1MS ;延时1ms DX, oe_port AL, DX ;读入结果

用查询EOC状态的方法

…… MOV OUT LL: MOV IN AND JZ MOV IN ……A/D转 Nhomakorabea器的分类

根据A/D转换原理和特点的不同,可把ADC 分成两大类:直接ADC和间接ADC。

微机原理及接口技术课件 第八章_ppt课件

No Image

在输入时,保存外设发往 CPU 的数据 (输入寄存器) 在输出时,保存 CPU 发往外设 的数据 (输出寄存器)

任何接口电路均包括如下基本功能:

1. 作为微型机与外设间传递数据的中间缓冲站; 2.正确寻址与微机交换数据的外设 ;

3.提供微型机与外设间交换数据所需的控制逻辑 与状态信号。

No Image

采用间接寻址,则其指令格式为: 输入指令:IN AL,DX 输出指令:OUT DX,AL

这种间接寻址方式的端口地址为两个字节长, 由DX寄存器间接给出,可寻址64K个端口地址。

No Image

优点:

1. I/O口的地址空间独立,且不占用存储

器地址空间。

2.地址线较少,且寻址速度相对较快 。

3.专门I/O指令的使用,使编制的程序清

晰,便于理解和检查。

No Image

缺点:

1. I/O指令较少,导致程序设计的灵活 性较差;

2.需要存储器和I/O端口两套控制逻辑, 增加了控制逻辑的复杂性。

No Image

8.3 CPU与外设之间的数据传送方式

微机与外设间的数据传送,实际上是CPU 与 I/O 接口间的数据传送。 CPU 与外设间的数 据传送通常包括无条件传送、查询传送、

No Image

8086/8088等就采用了I/O端口单独寻址方式。 这些指令包含直接寻址和寄存器间接寻址两种

类型。

No Image

对以8086为CPU的PC系列机而言,如采用直接 寻址,则其指令格式为: 输入指令: IN AL,PORT 输出指令: OUT PORT, AL

这种直接寻址方式的端口地址为一个字节长, 可寻址256个端口

No Image

微机原理与接口技术第8章ppt课件

INTRB

8.2 并行接口

方式1输入端口控制信号与引脚关系

8.2 并行接口

(2) 方式1的输出端口的答信号

方式1输出端口的引脚定义

方式1输出端口A

方式1输出端口B

INTE A

图8.4 方式1输出端口的引脚定义

8.2 并行接口

方式1输出端口控制信号与引脚之间的关系总结

8.2 并行接口

3.方式2

第8章 串行和并行接口

8.1 通用接口及其功能

CPU访问外设,与外设进行数据交换,必须通过接口电路。接口 中数据的传送方式有无条件传送方式、状态查询传送方式、程序 中断传送方式和直接数据通道传送( DMA)等。

随着大规模集成电路的发展,将接口电路集成在一块芯片上,接口 芯片具有接口电路中的所有功能,即接口中含有输入输出数据的 通道,能对输入输出数据进行缓冲,能够协调CPU和输入输出设 备的数据传送,对输入输出设备进行选择和信息转换等。

8.2 并行接口

(1) 方式1输入端口的控制信号 图示给出了端口A和端口B输入

方式1(端口A)

方式1(端口B)

INTE A

PA7 ~

0

PC4 PC5

STBA

IBFA

INTE B

PB7~0 PC2 PC1

PC3

RD

PC6~7

INTRA RD

PC0

I/O

图8.3 方式1输入端口的引脚定义

STBB

IBFB

而通用接口芯片,顾名思义,此类芯片可作为多种外设 的接口。对于不同的外设所需的不同功能,可通过对 接口芯片的内部寄存器进行编程实现。

Intel 8251A和8255A就是通用的串行和并行接口芯片。

8.2 并行接口

8.2 并行接口

方式1输入端口控制信号与引脚关系

8.2 并行接口

(2) 方式1的输出端口的答信号

方式1输出端口的引脚定义

方式1输出端口A

方式1输出端口B

INTE A

图8.4 方式1输出端口的引脚定义

8.2 并行接口

方式1输出端口控制信号与引脚之间的关系总结

8.2 并行接口

3.方式2

第8章 串行和并行接口

8.1 通用接口及其功能

CPU访问外设,与外设进行数据交换,必须通过接口电路。接口 中数据的传送方式有无条件传送方式、状态查询传送方式、程序 中断传送方式和直接数据通道传送( DMA)等。

随着大规模集成电路的发展,将接口电路集成在一块芯片上,接口 芯片具有接口电路中的所有功能,即接口中含有输入输出数据的 通道,能对输入输出数据进行缓冲,能够协调CPU和输入输出设 备的数据传送,对输入输出设备进行选择和信息转换等。

8.2 并行接口

(1) 方式1输入端口的控制信号 图示给出了端口A和端口B输入

方式1(端口A)

方式1(端口B)

INTE A

PA7 ~

0

PC4 PC5

STBA

IBFA

INTE B

PB7~0 PC2 PC1

PC3

RD

PC6~7

INTRA RD

PC0

I/O

图8.3 方式1输入端口的引脚定义

STBB

IBFB

而通用接口芯片,顾名思义,此类芯片可作为多种外设 的接口。对于不同的外设所需的不同功能,可通过对 接口芯片的内部寄存器进行编程实现。

Intel 8251A和8255A就是通用的串行和并行接口芯片。

8.2 并行接口

微机原理课件第八章

A1

B1

┇┇ ┇┇ A8

┇ ┇

2Y1 2Y2 2Y3 2Y4 G DIR (b) 图8.2 数据缓冲器

B8

(a)单向缓冲器74LS244 单向缓冲器74LS244

(b)双向缓冲器74LS245 双向缓冲器74LS245

(3)锁存器 )锁存器74LS373 (4)译码器 )译码器74LS138

1D D Q C 1 O (1) A5 A4 A3 G1 G2A G2B Y0 Y1 Y2 Y3 Y4 8D D Q C 8 O (8) A2 A1 A0 C B A Y5 Y6 Y7 y0 y1 y2 y3 y4 y5 y6 y7 输入 A5A4A3A2A1A0 1 0 0 0 0 0 1 0 0 0 0 1 1 0 0 0 1 0 1 0 0 0 1 1 1 0 0 1 0 0 1 0 0 1 0 1 1 0 0 1 1 0 1 0 0 1 1 1 输出 y7y6y5y4y3y2y1y0 1 1 1 1 1 1 1 0 1 1 1 1 1 1 0 1 1 1 1 1 1 0 1 1 1 1 1 1 0 1 1 1 1 1 1 0 1 1 1 1 1 1 0 1 1 1 1 1 1 0 1 1 1 1 1 1 0 1 1 1 1 1 1 1

8.2.3

端口与CPU之间的接口 端口与CPU之间的接口 CPU

1、简单I/O接口的组成 简单I 简单I 简单I/O接口的组成:由地址译码、数据锁存与缓冲器、状态寄 接口的组成:由地址译码、数据锁存与缓冲器、 组成 存器、 存器、命令寄存器等 。 2、地址译码电路 地址译码电路是接口的重要组成部分。 地址译码电路是接口的重要组成部分。 地址译码电路分为两个部分:接口的选择和端口的选择。 地址译码电路分为两个部分:接口的选择和端口的选择。

微机原理第8章ppt

第8章

中断向量地址 与中断类型码的关系 中断向量地址 = 4*N ,其中N为中断类型码

如:中断类型码为13H的中断向量地址为: 4*13H=0004CH,则 (0004CH)=中断类型13H的处理程序的偏移地址, (0004EH)=中断类型13H处理程序的段地址。

第8章

MOV AX,DX INT 4AH MOV CX,0 …. …. IRET ….

中断处理程序 F000H:1805H 第一条指令

05H 18H 00H F0H 中断255偏址 中断255偏址 中断255段址 中断255段址

….

第8章

8.5.4、8086对中断的响应

8086中的各种中断的响应和处理过程是不同的, 主要区别在于如何获取相应的中断类型码。

第8章

1、硬件中断

CPU在当前指令周期的T状态采样中断请求输入 信号,如果有可屏蔽中断请求,且CPU处在开 中断状态(IF=1),则CPU在当前指令完成后, 转入两个连续的中断响应周期,在第二个中断 响应周期的T4状态前沿采样数据总线,获取由 外设输入的中断类型码;若是采样到的是非屏 蔽请求,则CPU不经过上述的两个中断响应周 期,而在内部自动产生中断类型码2。

;否,检查磁带是否有请求

;有,转到磁带服务程序

第8章 (二)移位法 IN AL,20H

RCL AL,1

JC PWF

RCL AL,1

JC DISS . . .

第8章 查询方法的优点: (1)优先次序:先被查询的优先级最高,后被查 询的优先级依次降低。 (2)省硬件。 查询方法的缺点: 由询问转入相应的服务程序入口的时间长。尤其 是在中断源较多的情况下。

中断向量表 00000H 1805H IP 00001H F000H CS 00002H 00003H

微机原理及接口技术课件第8章 常用可编程接口芯片

;执行锁存命令

MOV DX,CS+0

;计数器0端口地址

IN AL,DX 内容

;读计数输出锁存器中的低8位

MOV AH,AL

;保护

IN AL,DX 内容

;读计数疏忽锁存器中的高8位

XCHG AH,AL

;AX中是输出锁存命令瞬间,计数执行 单元中的计数值

13

8.2.3 8253的工作方式

8253 的工作方式:

在计数期间CPU又送来新的计数初值,不影响当前计数过程。计数器计数到0, OUT端输出高电平。一直等到下一次GATE信号的触发,才会将新的计数初值装入, 并以新的计数初值开始计数过程,如图8-4(c)所示。8253方式1下三种情况的时序 波形图,如图8-4所示。

18

8.2.3 8253的工作方式

8253方式1时序波形图

接口芯片的地址码经译码后接通芯片的片选端,对读操作而言,怎样使 输入端口的信息由数据总线进入CPU,数据何时读入CPU,这些都由读信号 控制。对于输出接口,当CPU对接口进行输出数据的操作时,发出写信号。 在PC系统中,对I/O接口的操作由IN、OUT指令完成。

3

8.1可编程接口芯片概述

3. 可编程 目前所用的接口芯片大部分是多通道、多功能的。所谓多通道就是指一

0:二进制计数 1:十进制计数

其中:D7 D6用于选择定时器;D5 D4用于确定时间常数的读/写格式;D3 D2用来 设定计数器的工作方式;D0用来设定计数方式。

11

8.2 可编程定时/计数器接口芯片8253

例题8.1 8253控制字写入示例

MOV DX,CS+3

;8253控制寄存器端口地址,设置8253内部寄存

输入

微机原理第八章PPT课件

双向 数据总线

数据 总线 缓冲器

RD WR

A1 A0 RESET

CS

读/写 控制 逻辑

CPU接口

A组控 制电路

8位内部数据总线

B组控 制电路

A组端口(8)

A组端口 C上半部(4)

B组端口 C下半部(4)

A组端口(8)

内部逻辑

பைடு நூலகம்

外设接口

P.301 图8-2 8255A内部逻辑结构图

I/O PA7 ~ PA0

第八章 可编程通用接口芯片

可编程接口芯片 并行I/O接口8255A 串行通信接口 可编程定时器/计数器8253/8254

可编程接口的组成及功能

功能

在CPU系统总线与外部 IO设备之间传输信息

组成

总线收发器 和控制逻辑

R/W

联络信号

数据、状 态、控制

使能 控制

状态、控制 寄存器

控制线

寻址 中断管理 DMA管理

8255A

PA7 ~ PA0 端口A

控制信号

8255A方式2控制信号

信号说明

STB(PC4) 、 IBF(PC5) OBF(PC7) 、 ACK(PC6)

INTR(PC3)

D7 D6 D5 D4 D3 D2 D1 D0

11

10 10 10

PC3

端口A双向方式

B组方式 1=方式1 0=方式0

PA7 ~ PA0

PC7

INTE

PC6

8255A的工作方式2

特点

仅适用于PA端口,可进行双向8位数据传送 PC提供5位控制信号,其余位可进行基本输入输出 用IN/OUT指令对PA端口进行操作,端口C用置位/复位 PB可以工作在方式0或1下

精品课件-微型计算机原理及接口技术-第8章_1

;AX:16bit,4个4bit数等待显示

;显示bit0~bit3

电路图

;右移4位 ;显示bit4~bit7

;显示bit8~bit11

;右移4位 ;显示bit12~bit15

;DLY1s为1s延迟程序

8.1.1 LED接口 三、动态显示的接口电路 1) 用通用接口芯片

15

锁 存 器

驱动器

驱动器 锁 存 器

减轻提供电流驱动器的负载; 增加吸收电流驱动器的负载。

共阴极LED数码管

8.1.1 LED接口 三、动态显示的接口电路 2) 用专用接口芯片:MM74C912/917

MM74C912/917:6位数字BCD/Hex显示控制驱动器 由Fairchild Semiconductor公司生产。 一个DM9368芯片只能驱动1个7段数码管;

2) 用专用接口芯片:MM74C912/917

引脚

显示字符格式

MM74C917 高阻

MM74C912 高阻

输入数据 A(20) × 0 1 0 1 0 0 0 1 0 1 0 1 0 1 0 1 1 B(21) × 0 0 1 1 0 1 1 1 0 0 1 1 0 0 1 1 1 C(22) × 0 0 0 0 1 1 1 1 0 0 0 0 1 1 1 1 1 D(23) × 0 0 0 0 0 0 0 0 1 1 1 1 1 1 1 1 1

三、动态显示的接口电路

2) 用专用接口芯片:MM74C912/917

电路图

上图电路中采用MM74C912芯片作为LED数码管接口,可实现十进 制数显示。

LED数码管动态显示电路 16

P D 7 LED1 P 5D 0 G 4 0 1G U34A7 D N GF 89F E 1E D 2D D N GC 3412C B 6B A 7A P D 7 LED2 P 5D 0 G 4 0 1G U34B7 D N GF 89F E 1E D 2D D N GC 3434C B 6B A 7A P D 7 LED3 P 5D 0 G 4 0 1G U34C7 D N GF 89F E 1E D 2D D N GC 3456C B 6B A 7A P D 7 LED4 P 5D 0 G 4 0 1G U34D7 D N GF 89F E 1E D 2D D N GC 3498C B 6B A 7A GFEDCBA P D 8642 11119753 1Y11Y21Y31Y42Y12Y22Y32Y4 GG 1A11A21A31A42A12A22A32A412 U3374LS240 13579 24681 11111

微机原理第八章:中断技术讲解

二、中断(zhōngduàn)源识别及中断(zhōngduàn) 判优

1.中断源识别

★ 软件查询法:

★ 中断矢量法:中断源提供中断类型号,CPU根据类型确定中断源 2.中断判优

★ 对同时产生的中断,首先处理优先级别较高的中断;

若优先级别相同,则按先来先服务的原则。

★ 对非同时产生的中断:

低优先级的中断程序允许被高优先级的中断源所中断

1.中断服务子程序的特点: 为“远过程”,用 IRET 指令返回

2.中断服务程序完成的工作

1)保护现场(通用寄存器的内容)

2)开中断(STI)

3)中断处理

4)关中断(CLI)

5)恢复现场 6)IRET

中断服务程序结构

保护有关寄存器内容 开中断

执行中断服务程序 关中断

恢复有关寄存器内容 执行IRET

精品资料

④ 执行 IRET 指令

4.退出中断(zhōngduàn) ① 关中断(zhōngduàn)

退

出

② 恢复现场中

③ 恢复断点 ④ 开中断(zhōngduàn) 断

精品资料

关中断 保存断点,保存现场

判别中断源 转入中断服务程序 保护寄存器、开中断 执行中断服务程序

IRET

关中断 恢复现场,恢复断点

开中断

STOSW

;串存储(字)

;AX→ES∶[DI]、 [DI+1]

MOV AX,SEG_INTR

;中断服务程序段基址送AX

STOSW

;串存储(字)

STI

;开中断

精品资料

2.用 MOV将直接(zhíjiē)中断向量写入中断向量表中

;将中断向量直接(zhíjiē)写入中断向量表中的程序段为

1.中断源识别

★ 软件查询法:

★ 中断矢量法:中断源提供中断类型号,CPU根据类型确定中断源 2.中断判优

★ 对同时产生的中断,首先处理优先级别较高的中断;

若优先级别相同,则按先来先服务的原则。

★ 对非同时产生的中断:

低优先级的中断程序允许被高优先级的中断源所中断

1.中断服务子程序的特点: 为“远过程”,用 IRET 指令返回

2.中断服务程序完成的工作

1)保护现场(通用寄存器的内容)

2)开中断(STI)

3)中断处理

4)关中断(CLI)

5)恢复现场 6)IRET

中断服务程序结构

保护有关寄存器内容 开中断

执行中断服务程序 关中断

恢复有关寄存器内容 执行IRET

精品资料

④ 执行 IRET 指令

4.退出中断(zhōngduàn) ① 关中断(zhōngduàn)

退

出

② 恢复现场中

③ 恢复断点 ④ 开中断(zhōngduàn) 断

精品资料

关中断 保存断点,保存现场

判别中断源 转入中断服务程序 保护寄存器、开中断 执行中断服务程序

IRET

关中断 恢复现场,恢复断点

开中断

STOSW

;串存储(字)

;AX→ES∶[DI]、 [DI+1]

MOV AX,SEG_INTR

;中断服务程序段基址送AX

STOSW

;串存储(字)

STI

;开中断

精品资料

2.用 MOV将直接(zhíjiē)中断向量写入中断向量表中

;将中断向量直接(zhíjiē)写入中断向量表中的程序段为

相关主题

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

4. 读/写控制部件

这是8255A内部完成读/写控制功能的部件,它能接收 CPU的控制命令,并根据它们向片内各功能部件发出 操作命令。可接收的控制命令如下: (1) CS——片选信号。由CPU输入,通常由端口的高位 地址码(A15~A2)译码得到,CS有效,表示该8255A被 选中。 (2) RD,WR——读、写控制信号。由CPU输入,RD有 效,表示CPU读8255A,应由8255A向CPU传送数据或 状态信息。WR有效,表示CPU写8255A,应由CPU将 控制字或数据写入8255A。 (3) RESET——复位信号。由CPU输入。RESET有效时, 清除8255A中所有控制字寄存器内容,并将各端口置成 输入方式。

(1) 无条件传送方式: 当外设已准备就绪,那就不必 查询外设的状态而进行信息传输,这就称为无条件 传送。这种信息传送方式只适用于简单的外设,如 开关和数码段显示器等。 当简单外设作为输入设备时,输入数据保持时间要 比CPU的处理速度慢得多,所以可直接使用三态缓 冲存储器与数据总线相连,如图8.1所示。CPU执 行输入指令时,读信号RD有效,选通信号M/IO= 0,因而三态缓冲存储器被选通,于是已准备好的 输入数据便可进入数据总线。

•典型的并行接口和外部设备连接如图8.4所示。图中 的并行接口用一个通道和输入设备相连,用另一个 通道和输出设备相连,每个通道中除数据线外均配 有一定的控制线和状态线。

图8.4

从图8.4中看到,并行接口中应该有一个控制寄存 器用来接收CPU对它的控制命令,有一个状态寄存 器提供各种状态位供CPU查询。为了实现输入和输 出,并行接口中还必定有相应的输入缓冲寄存器和 输出缓冲寄存器。 1. 并行接口的输入过程 外部设备首先将数据送给接口,并使状态线“数据 输入准备好”成为高电平。接口把数据接收到数据 输入缓冲寄存器的同时,使“数据输入回答”线变 为高电平,作为对外部设备的响应。外部设备接到 此信号,便撤除数据和“数据输入准备好”信号。 数据到达接口中后,接口会在状态寄存器中设置 “输入准备好”状态位,以便CPU对其进行查询, 接口也

图8.1

当简单外部设备作为输出设备时,一般都需要锁存 器。这是因为CPU送出的数据应在接口电路的输出 端保持一段时间。在图8.1中,当CPU执行输出指 令时,M/IO=0及WR=0,于是接口中的输出锁存 器被选中,CPU输出的信息经过数据总线送入输出 锁存器。 (2) 条件传送方式: CPU通过执行程序不断读取并测 试外部设备状态,如果输入外部设备处于已准备好 状态或输出外部设备为空闲状态时,则CPU执行传 送信息指令。由于条件传送方式是CPU在不断调查 外部设备的当前状态后才进行信息传送,所以也称 为“查询式传送”。因此,条件传送方式的接口电 路应包括:传送数据端口及传送状态端口。当输入 信

可以在此时向CPU发一个中断请求。所以,CPU 既可以用软件查询方式,也可以用中断方式来设法 读取接口中的数据。CPU从并行接口中读取数据后, 接口会自动清除状态寄存器中的“输入准备好”状 态位,并且使数据总线处于高阻状态。此后,又可 以开始下一个输入过程。 2. 并行接口的输出过程 每当外部设备从接口取走一个数据之后,接口就会 将状态寄存器中的“输出准备好”状态位置“1”, 以表示CPU当前可以往接口中输出数据,这个状态 位可供CPU进行查询。此时,接口也可以向CPU发 一个中断请求。所以,CPU既可以用软件查询方式, 也可以用中断方式设法往接口中输出一个数据。当

8.3.1 8255A芯片内部结构及其功能 • 由图8.5和图8.6可见,8255A由以下几部分组成:

图8.5

图8.6

1. 并行输入/输出端口A,B,C 8255A芯片内部包含3个8位端口,其中:端口A包 含一个8位数据输出锁存/缓冲存储器和一个8位数 据输入锁存器;端口B包含一个8位数据输入/输出、 锁存/缓冲存储器和一个8位数据输入缓冲存储器; 端口C包含一个输出锁存/缓冲存储器和一个输入缓 冲存储器。必要时端口C可分成两个4位端口,分 别与端口A和端口B配合工作,通常将端口A和端口 B定义为输入/输出的数据端口,而端口C可作为状 态或控制信息的传送端口。 2. A组和B组控制部件 端口A与端口C的高4位(PC7~PC4)构成A组,由A 组控制部件实现控制功能,端口B与端口C的低4位

IOP后,86系列CPU必须工作在最大工作模式。当 CPU需要进行输入或输出操作时,只需在存储器中 建立一个规定格式的信息块,设置好需要执行的操 作和有关参数,然后把这些参数送入8089,IOP即 会执行输入/输出操作。如果在数据传送过程出现 差错,8089会进行重复传送或做必要的处理。在整 个数据块的传送过程中,CPU可去完成其他作业。 在微型计算机系统中,通常是用各种类型的输入/ 输出接口芯片来完成CPU与其外部设备之间的信息 交换。下面介绍几种常用接口芯片及号。 当A1A0=00,选择端口A; 当A1A0=01,选择端口B; 当A1A0=10,选择端口C; 当A1A0=11,选择控制字寄存器。

8.3 可编程并行通信接口芯片8255A

8255A是Intel86系列微处理机的配套并行 接口芯片,它可为86系列CPU与外部设备之间 提供并行输入/输出的通道。由于它是可编程的, 可以通过软件来设置芯片的工作方式,所以, 用8255A连接外部设备时,通常不用再附加外 部电路,给使用者带来很大方便。

8.1 微型计算机的输入/输出接口 8.1.1 输入/输出接口的交换信号

计算机I/O接口电路与外部设备间交换的信号, 通常有以下4种类型: (1) 数字量: 二进制形式的数据,或是已经过编码的 二进制形式的数据。最小单位为“位”(bit),8位 称为一个字节(BYTE)。 (2) 模拟量: 用模拟电压或模拟电流幅值大小表示的 物理量。模拟量信号不能直接进入计算机,必须 经过A/D(模拟/数字)转换器,把模拟量转换成某种 形式的数字量,才能输入计算机。当外部设备需 要模拟量信号控制时,I/O接口电路D/A(数字/模拟) 转换器又能把数字量转换成模拟量信号。

(3) 开关量: 开关量信号只有两种状态,即“开”或 “闭”。这样,只要用一位二进制数就可表示。 (4) 脉冲量: 在计算机控制系统中还经常用到计数脉 冲、定时脉冲或控制脉冲。脉冲量信号是以脉冲形 式表示的一种信号。

8.1.2 输入/输出的控制方式

在微机系统中,可采用的输入/输出控制 方式一般有4种:程序控制方式、中断控制方 式、直接存储器存取方式(DMA方式)和输入/ 输出处理机方法。 1. 程序控制方式 这是指在程序控制下进行信息传送。

向CPU发出总线请求;若CPU响应DMA的请求把 总线使用权赋给DMA控制器,数据不通过CPU, 可直接在DMA控制器操纵下进行。当这批数据传 送完毕后,DMA控制器再向CPU发出“结束中断 请求”,CPU响应这一中断请求,即可收回总线使 用权。因此,采用DMA控制方式,CPU只需在数 据传送结束时响应一次中断,减轻了CPU的负担, 但DMA控制器一般只能对一台或几台同类型的外 部设备完成控制功能。 4. 输入/输出处理机控制方式 对于有大量输入/输出设备的微机系统,DMA控制 方式已不能满足这种需要。Intel公司生产与86系列 配套的输入/输出处理机(IOP)8089。系统中设置了

(PC3~PC0)构成B组,由B组控制部件实现控制功 能。它们各有一个控制单元,可接收来自读/写控 制部件的命令和CPU通过数据总线(D7~D0)送来 的控制字,并根据它们来定义各个端口的操作方式。 3. 数据总线缓冲存储器 这是一个三态双向8位数据缓冲存储器,它是 8255A与8086CPU之间的数据接口。CPU执行输出 指令时,可将控制字或数据通过数据总线缓冲存储 器传送给8255A。CPU执行输入指令时,8255A可 将状态信息或数据通过总线缓冲存储器向CPU输入。 因此它是CPU与8255A之间交换信息的必经之路。

存器的对应标志位置“1”,告诉CPU;当前外部 设备处于“忙”状态,从而阻止CPU输出新的数据。 当外部设备从接口中取走数据后,通常也会送出一 个应答信号ACK,ACK使接口中的D触发器置“0”, 从而使状态寄存器中的对应标志位置“0”,这样便 可开始下一个数据的输出过程。

图8.3

2. 中断控制方式 中断控制方式一般用来传送低速外部设备与CPU之 间的信息交换。当外部设备需要与CPU进行数据交 换时,由接口部件的CPU发出一个中断请求信号, CPU响应这一中断请求,便可在中断服务程序中完 成一个字节或一个字的信息交换。这样每操作一次, CPU要打断原来执行的程序去执行一般中断服务程 序,对速度较高的外部设备会产生信息丢失,因此 不能采用。 3. DMA控制方式 DMA控制方式是一种成块传送数据的方式。当某 一外部设备需要输入/输出一批数据时,向DMA控 制器发出请求,DMA控制器接收到这一请求后,

息时,查询到外部设备准备好后,则使接口的 “准备好”标志位置1。当输出信息时,外部设备 取走一个数据后,传送状态端口使标志为“空闲” 状态,可以接收下一个数据。 图8.2为查询式输入的接口电路。输入设备在数据 准备好后便往接口发出一个选通信号。

图8.2

这个选通信号起两个作用,一是把外部设备的数据 送到接口的锁存器中;另一方面,它使接口中的一 个D触发器置1,从而使三态缓冲存储器的READY =1。在查询输入过程中,CPU先从外部设备输入 数据中读取状态字,检查“准备好”标志位是否为 “1”。若已准备好,这时数据已进入接口锁存器, 则执行输入传送指令。同时把“准备好”标志位清 “0”,接着便可开始下一个数据传输过程。 图8.3为查询式输出接口电路。CPU执行输出指令 时,由选择信号M/IO及写信号WR产生的选通信号 把数据送入数据锁存器,同时使D触发器输出“1”。 此信号一方面告诉外部设备在接口中已有数据要输 出,另一方面D触发器的输出信号使状态寄

8.2 并行通信与并行接口 8.2.1 并行通信 并行通信是把一个字符的各数位用几条线 同时进行传输,传输速度快,信息率高。但它 比串行通信所用的电缆多,因此,并行通信常 用在传输距离较短(几米至几十米)和数据传输 率较高的场合。