2812寄存器

hello第四课(二)f2812存储器映射及cmd详解-日志-eyes417-

hello第四课(二):f2812存储器映射及cmd详解-日志-eyes417-...2812存储器映射2812具有32位的数据地址和22位的程序地址,总地址空间可以达到4M的数据空间和4M的程序空间。

32位的数据地址,就是能访问2的32次,是4G,而22位的程序地址,就是能访问2的22次,是4M。

其实,2812可寻址的数据空间最大是4G,但是实际线性地址能达到的只有4M,原因是2812的存储器分配采用的是分页机制,分页机制采用的是形如0xXXXXXXX的线性地址,所以数据空间能寻址的只有4M。

2812的存储器被划分成了下面的几个部分:1. 程序空间和数据空间。

2812所具有的RAM、ROM和FLASH都被统一编址,映射到了程序空间和数据空间,这些空间的作用就是存放指令代码和数据变量。

2. 保留区。

数据空间里面某些地址被保留了,作为CPU的仿真寄存器使用,这些地址是不向用户开放的。

3. CPU中断向量。

在程序空间里也保留了64个地址作为CPU 的32个中断向量。

通过CPU的一个寄存器ST1中的VMAP位来将这一段地址映射到程序空间的底部或者顶部。

映射和空间的统一编址 F2812内部的映射空间 2812CMD详解CMD:command 命令,顾名思义就是命令文件指定存储区域的分配.2812的CMD采用的是分页制,其中PAGE0用于存放程序空间,而PAGE1用于存放数据空间。

1.)#pragma ,CODE_SECTION和DATA_SECTION伪指令#pragma DATA_SECTION(funcA,"dataA"); ------ 函数外声明将funcA数据块定位于用户自定义的段"dataA"中------ 需要在CMD中指定dataA段的物理地址2.)MEMORY和SECTIONS是命令文件中最常用的两伪指令。

F2812寄存器速查手册

007+2004821074(149259898)015+zhengjunfe031_yangyansky(287817962)050+ywnwa(109264732)067+chaosming(276907343)084_suary(122757250)115 dandan112由衷感谢以上几位抽出宝贵的时间整理各模块的相关寄存器!限于水平,整理过程中难免存在错误或不当之处,恳请大家批评指正。

在奋斗中前行!事件管理器寄存器 (2)GPIO MUX 寄存器 (14)eCAN部分 (18)WDRST时钟、锁相环、看门狗和低功耗模式寄存器 (33)片内外设的中断扩展(PIE)寄存器 (38)串行通信接口 (42)ADC模块相关寄存器 (46)SPI模块寄存器 (54)事件管理器寄存器名称地址 占用地址空间(16bit)EVA描述GPTCONA 0x7400 1 通用定时器全局控制寄存器A T1CNT 0x7401 1 定时器1计数寄存器T1CMPR 0x7402 1 定时器1比较寄存器 T1PR 0x7403 1 定时器1周期寄存器T1CON 0x7404 1 定时器1控制寄存器T2CNT 0x7405 1 定时器2计数寄存器T2CMPR 0x7406 1 定时器2比较寄存器 T2PR 0x7407 1 定时器2周期寄存器T2CON 0x7408 1 定时器2控制寄存器 EXTCONA 0x7409 1 扩展控制寄存器A COMCONA 0x7411 1 比较控制寄存器A ACTRA 0x7413 1 比较操作控制寄存器A DBTCONA 0x7415 1 死区定时器控制寄存器A CMPR1 0x7417 1 比较寄存器1 CMPR2 0x7418 1 比较寄存器2 CMPR3 0x7419 1 比较寄存器3 CAPCONA 0x7420 1 捕捉单元控制寄存器A CAPFIFOA 0x7422 1 捕捉单元FIFO状态寄存器A CAP1FIFO 0x7423 1 2极深度FIFO1堆栈 CAP2FIFO 0x7424 1 2极深度FIFO2堆栈 CAP3FIFO 0x7425 1 2极深度FIFO3堆栈 CAP1FBOT 0x7427 1 FIFO1栈底寄存器 CAP2FBOT 0x7428 1 FIFO2栈底寄存器 CAP3FBOT 0x7429 1 FIFO3栈底寄存器 EVAIFRA 0x742C 1 中断标志寄存器A EVAIFRB 0x742D 1 中断标志寄存器B EVAIFRC 0x742E 1 中断标志寄存器C EVAIMRA 0x742F 1 中断屏蔽寄存器A EVAIMRB 0x7430 1 中断标志寄存器B EVAIMRC 0x7431 1 中断标志寄存器CEVBGPTCONB 0x7500 1 通用定时器全局控制寄存器B T3CNT 0x7501 1 定时器3计数寄存器T3CMPR 0x7502 1 定时器3比较寄存器 T3PR 0x7503 1 定时器3周期寄存器T3CON 0x7504 1 定时器3控制寄存器T4CNT 0x7505 1 定时器4计数寄存器T4CMPR 0x7506 1 定时器4比较寄存器T4PR 0x7507 1 定时器4周期寄存器T4CON 0x7508 1 定时器4控制寄存器EXTCONB 0x7509 1 扩展控制寄存器BCOMCONB 0x7511 1 比较控制寄存器BACTRB 0x7513 1 比较操作控制寄存器BDBTCONB 0x7515 1 死区定时器控制寄存器BCMPR4 0x7517 1 比较寄存器4CMPR5 0x7518 1 比较寄存器5CMPR6 0x7519 1 比较寄存器6CAPCONB 0x7520 1 捕捉单元控制寄存器BCAPFIFOB 0x7522 1 捕捉单元FIFO状态寄存器B CAP4FIFO 0x7523 1 2极深度FIFO4堆栈CAP5FIFO 0x7524 1 2极深度FIFO5堆栈CAP6FIFO 0x7525 1 2极深度FIFO6堆栈CAP4FBOT 0x7527 1 FIFO4栈底寄存器CAP5FBOT 0x7528 1 FIFO5栈底寄存器CAP6FBOT 0x7529 1 FIFO6栈底寄存器EVBIFRA 0x752C 1 中断标志寄存器AEVBIFRB 0x752D 1 中断标志寄存器BEVBIFRC 0x752E 1 中断标志寄存器CEVBIMRA 0x752F 1 中断屏蔽寄存器AEVBIMRB 0x7530 1 中断屏蔽寄存器BEVBIMRC 0x7531 1 中断屏蔽寄存器CGPTCONA(通用定时器全局控制寄存器A)15 14 13 12 11 10 9 8Reserved T2STAT T1STAT T2CTRIPE T1CTRIPE T2TOADC T1TOADC7 6 5 4 3 2 1 0T1TOADC TCOMPOE T2CMPOE T1CMPOE T2PIN T1PIN GPTCONA功能定义名称 功能描述位(Bit)15 Reserved Reserved14 T2STAT 通用定时器2的状态 0- 递减计数 1- 递增计数13 T1STAT 通用定时器1的状态 0- 递减计数 1- 递增计数12 T2CTRIPE T2CTRIP使能位,使能或禁止定时器2的比较输出。

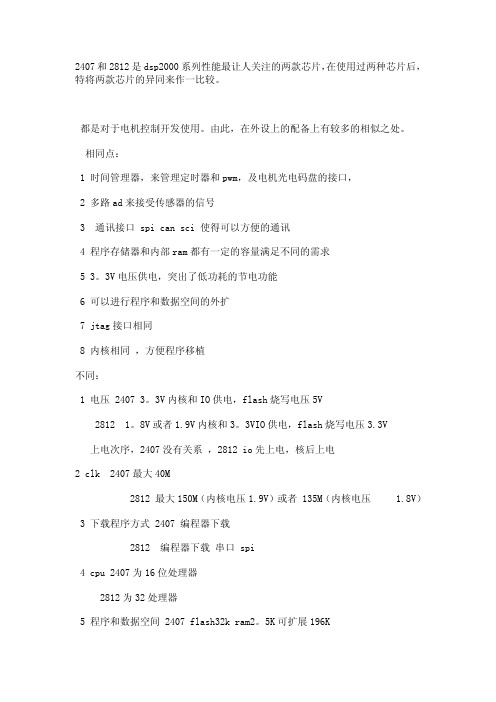

dsp2407与2812的区别

2407和2812是dsp2000系列性能最让人关注的两款芯片,在使用过两种芯片后,特将两款芯片的异同来作一比较。

都是对于电机控制开发使用。

由此,在外设上的配备上有较多的相似之处。

相同点:1 时间管理器,来管理定时器和pwm,及电机光电码盘的接口,2 多路ad来接受传感器的信号3 通讯接口 spi can sci 使得可以方便的通讯4 程序存储器和内部ram都有一定的容量满足不同的需求5 3。

3V电压供电,突出了低功耗的节电功能6 可以进行程序和数据空间的外扩7 jtag接口相同8 内核相同,方便程序移植不同:1 电压 2407 3。

3V内核和IO供电,flash烧写电压5V2812 1。

8V或者1.9V内核和3。

3VIO供电,flash烧写电压3.3V 上电次序,2407没有关系,2812 io先上电,核后上电2 clk 2407最大40M2812 最大150M(内核电压1.9V)或者 135M(内核电压 1.8V) 3 下载程序方式 2407 编程器下载2812 编程器下载串口 spi4 cpu 2407为16位处理器2812为32处理器5 程序和数据空间 2407 flash32k ram2。

5K可扩展196K2812 flash 16×128K ram 16×18K可扩展4M空间6 时间管理器 2407 定时器16位一个光电码盘接口2812 定期器32位有两个光电码盘接口7 ad 2407 10位 2812 12位8 sci 2407 1个没有缓冲单元 2812 两个具有缓冲单元8 can 2407标准can符合2。

0B协议 2812增强can和标准can 符合2。

0B9 mcbsp 2407 没有 2812 有10 语言 2407 汇编 c 2812 汇编 c c++11 TI支持 2407没有提供较多的例程支持 2812 提供完整的模块例程支持12 编程风格 2407倾向于模块编程 2812 类编程,并且结构性更强13 寄存器的保护。

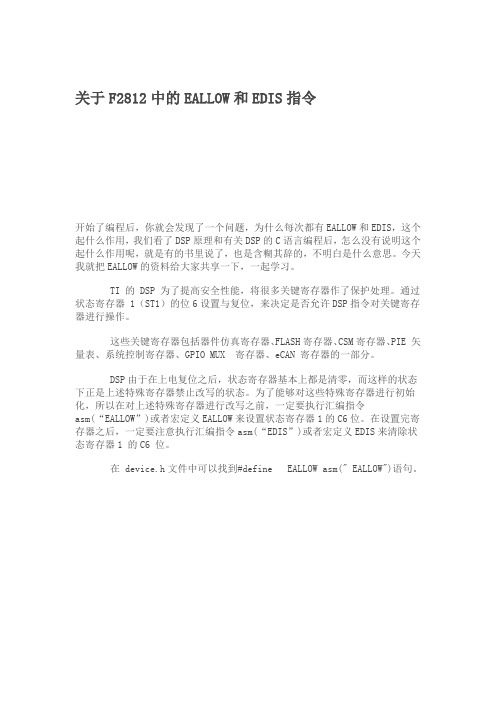

关于F2812中的EALLOW和EDIS指令

关于F2812中的EALLOW和EDIS指令

开始了编程后,你就会发现了一个问题,为什么每次都有EALLOW和EDIS,这个起什么作用,我们看了DSP原理和有关DSP的C语言编程后,怎么没有说明这个起什么作用呢,就是有的书里说了,也是含糊其辞的,不明白是什么意思。

今天我就把EALLOW的资料给大家共享一下,一起学习。

TI 的 DSP 为了提高安全性能,将很多关键寄存器作了保护处理。

通过状态寄存器 1(ST1)的位6设置与复位,来决定是否允许DSP指令对关键寄存器进行操作。

这些关键寄存器包括器件仿真寄存器、FLASH寄存器、CSM寄存器、PIE 矢量表、系统控制寄存器、GPIO MUX 寄存器、eCAN 寄存器的一部分。

DSP由于在上电复位之后,状态寄存器基本上都是清零,而这样的状态下正是上述特殊寄存器禁止改写的状态。

为了能够对这些特殊寄存器进行初始化,所以在对上述特殊寄存器进行改写之前,一定要执行汇编指令asm(“EALLOW”)或者宏定义EALLOW来设置状态寄存器1的C6位。

在设置完寄存器之后,一定要注意执行汇编指令asm(“EDIS”)或者宏定义EDIS来清除状态寄存器1 的C6 位。

在 device.h文件中可以找到#define EALLOW asm(" EALLOW")语句。

14-2812DSP-07XINTF及GPIO

具有多达56个独立 可编程复用的通用 双向的数字 I/O端 2 口

如果是数字I/O模式,方向控制寄存器 (GPxDIR)用来配置引脚的信号传输 方向,并通过限制寄存器( GPxQUAL)限制输入信号的脉冲宽 度以消除噪声

当DSP复位时,所有的GPIO引脚被配 置为输入引脚

电气与信息工程学院

C28x GPIO Pin Assignment

GPIO F

GPIOF0 / GPIOF1 / GPIOF2 / GPIOF3 / GPIOF4 / GPIOF5 / GPIOF6 / GPIOF7 / GPIOF8 / GPIOF9 / GPIOF10 / GPIOF11 / GPIOF12 / GPIOF13 / GPIOF14 /

GPIO G

• • •

1

MUX Control Bit 0 = I/O Function 1 = Primary Function GPxMUX

Pin

15 - 8

7-0

Some digital I/O and peripheral I/O input signals include an Input Qualification feature

•时基由内部时钟XTIMCLK 决定;

•XINTF 配置参数的改变可以引起处理时间的变化,所以用于配 置参数的代码不能放在XINTF 区域中执行。 电气与信息工程学院

F2812 外部 接口分区示 意图

DSP技术及应用

281x XINTF及GPIO

XINTF时钟

所有的XINTF 总线周期都从XCL KOUT 的上升沿开始,所有的定 时和事件都是从XTIMCLK 的上 升沿开始。

GPIO D

GPIOD0 GPIOD1 GPIOD5 GPIOD6 / / / / T1CTRIP_PDPINTA T2CTRIP / EVASOC T3CTRIP_PDPINTB T4CTRIP / EVBSOC

TMS320F2812中FLASH寄存器的配置问题解答

TMS320F2812中FLASH寄存器的配置问题解答问:我使用的是TI 2000系列芯片中的2812!我使用的是汇编语言对其进行开发,目前主程序已经完成,需要烧写到FLASH中运行,但烧写过后发现在FLASH中运行的速度和在RAM中用仿真器仿真的速度差不多!这样就太慢了,我设置的PLL倍频到150MHZ,后来发现是有关FLASH的一些配置寄存器没有进行配置,我想在FLASH中运行速度过慢的原因可能是这个造成的吧!我查看了TI的说明文档,其中关于FLASH寄存器的介绍中,有如下的一段:Note: Flash configuration registers should not be accessed while anaccess is in progress in flash or OTP memoryThe flash registers should not be accessed from code that is running fromOTP or flash memory or while an access may be in progress. All register accessesto the flash registers should be made from code executing outsideof flash/OTP memory and an access should not be attempted until all activityon the flash/OTP has completed. No hardware is included to protect for this.You can read the flash registers from code executing in flash/OTP; however,do not write to the registers.从上面的一段看出,如果需要配置FLASH的寄存器,必须执行FLASH以外存储空间的程序才可以实现,我又发现这些寄存器是受EALLOW和CSM保护的,所以我按照以下步骤试图重新配置寄存器:1,在执行存放于FLASH中的主程序段时,将一段存于FLASH中的初始化flash配置寄存器的程序完全复制到片内L0SARAM中,该初始化程序如下:MOVW DP,#DP_FLASH ;指向FLASH寄存器所在的页面EALLOWMOV AL,#01HMOV @FOPT,AL ;使能FLASH流水线模式MOV AL,#03HMOV @FPWR,ALMOV AL,#0FFHMOV @FSTDBYWAIT,ALMOV AL,#0FFHMOV @FACTIVEWAIT,ALMOV AL,#0203HMOV @FBANKWAIT,ALMOV AL,#06HMOV @FOTPWAIT,ALEDISLB FLASH_RET ;FLASH_RET 是我这段程序需要返回到的地址2,我配置了CSM模块的寄存器,使得器件不受CSM的保护3,用MOVL XAR7,#8300H ;200H是初始化程序复制到RAM中的地址LB *XAR7从FLASH跳转到RAM中执行该段初始化FLASH的程序4,从RAM中返回到FLASH中的主程序继续执行但发现这段程序烧写到片子里面后,不能按照我的意图执行,FLASH寄存器没有得到重新配置,请问这是什么原因呢?我上述的几个步骤对不对呢?请问,如果在程序烧写到片内FLASH中,在执行该程序时,想调到RAM中执行另一段程序,这种情况应该如何实现呢?应该有哪些需要注意的地方呢?如果那位有配置FLASH寄存器的例子的话,请发给我一份做一下参考吧!======================================================== 答:在flash中怎么能运行配置属于flash的寄存器呢?自己改变自己是不行的。

DSP 2812中文手册

第1章芯片结构及性能概述TMS320C2000系列是美国TI公司推出的最佳测控应用的定点DSP芯片,其主流产品分为四个系列:C20x、C24x、C27x和C28x。

C20x可用于通信设备、数字相机、嵌入式家电设备等;C24x主要用于数字马达控制、电机控制、工业自动化、电力转换系统等。

近年来,TI公司又推出了具有更高性能的改进型C27x和C28x系列芯片,进一步增强了芯片的接口能力和嵌入功能,从而拓宽了数字信号处理器的应用领域。

TMS320C28x系列是TI公司最新推出的DSP芯片,是目前国际市场上最先进、功能最强大的32位定点DSP芯片。

它既具有数字信号处理能力,又具有强大的事件管理能力和嵌入式控制功能,特别适用于有大批量数据处理的测控场合,如工业自动化控制、电力电子技术应用、智能化仪器仪表及电机、马达伺服控制系统等。

本章将介绍TMS320C28x 系列芯片的结构、性能及特点,并给出该系列芯片的引脚分布及引脚功能。

1.1 TMS320C28x系列芯片的结构及性能C28x系列的主要片种为TMS320F2810和TMS320F2812。

两种芯片的差别是:F2812内含128K×16位的片内Flash存储器,有外部存储器接口,而F2810仅有64K×16位的片内Flash存储器,且无外部存储器接口。

其硬件特征如表1-1所示。

表1-1 硬件特征TMS320C28x系列DSP的CPU与外设(上)·2·注:‡“S”是温度选择(-40℃~ +125℃)的特征化数据,仅对TMS是适用的。

‡‡产品预览(PP):在开发阶段的形成和设计中与产品有关的信息,特征数据和其他规格是设计的目标。

TI保留了正确的东西,更换或者终止了一些没有注意到的产品。

高级信息(AI):在开发阶段的取样和试制中与新产品有关的信息,特征数据和其他规格用以改变那些没有注意到的东西。

产品数据(PD):是当前公布的数据信息,产品遵守TI的每项标准保修规格,但产品加工不包括对所有参数的测试。

TMS320F2812寄存器定义(完整版)

=0 XREADY输入为同步方式=1 XREADY输入为异步方式

确定对区的访问是进行采样还是忽略XREADY =0区访问时忽略XREADY

读周期的建立周期=00无效=01 1个XTIMCLK周期(X2TIMING1=1加倍) =10 2个XTIMCLK周期=11 3个XTIMCLK周期

读周期的激活周期n*(X2TIMING1+1)*XTIMCLK周期(总的激活时间为(1+XRDACTIVE))

0x7040---0x704F

16

非EALLOW保护

SPI寄存器

0x7050---0x705F

16

非EALLOW保护

SCI A寄存器

0x7070---0x707F

16

非EALLOW保护

外部中断寄存器

0x70C0---0x70DF

32

EALLOW保护

GPIO多路选择寄存器

0x70E0---0x70FF

HOLD.9 (R/W/0)

MP/MC.8 (R/W/X) |

WLEVEL.(7-6) (R/W/0

CLKOFF.3 (R/W/0)

CLKMODE.2 (R/W/1)

WRBUFF.(1-0) (R/W/0)

0x0B34

设定XTIMCLK时钟比例000 XTIMCLK=SYSCLKOUT其它保留001 XTIMCLK=SYSCLKOUT/2

FBANKWAIT

读访问等待周期寄存器

PAGEWAIT.(11-8)(R/W/1)

RANDWAIT.(3-0) (R/W/1)

0x0A86

FLASH页读操作等待状态。(0--15 SYSCLKOUT周期)

FLASH随机读操作等待状态。(0--15 SYSCLKOUT周期)

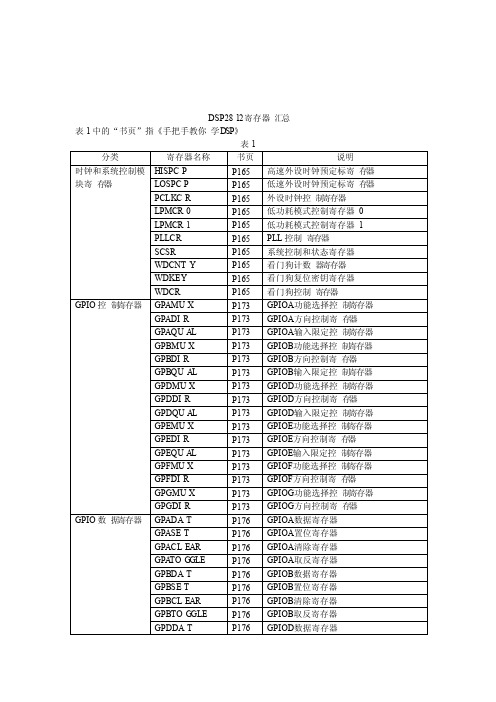

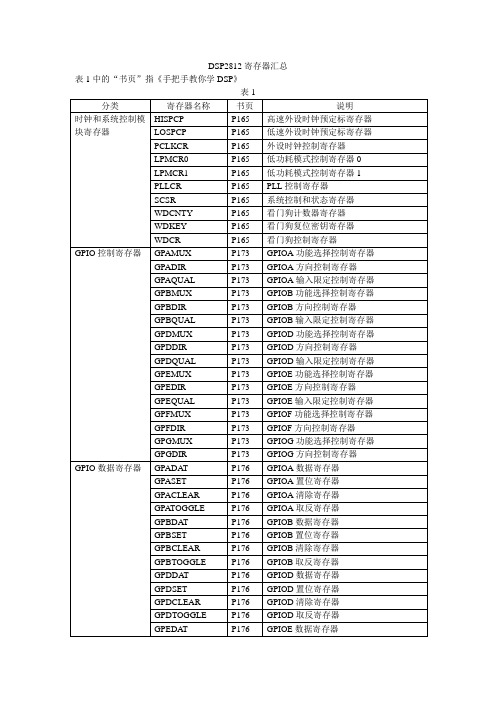

手把手教你学DSP2812-寄存器

比较寄存器 1 比较寄存器 2 比较寄存器 3 比较控制寄 存器 B 比较行为控 制寄存器 B 死区定时器控制寄存器 B 比较寄存器 4 比较寄存器 5 比较寄存器 6 捕获单元控 制寄存器 A 捕获单元 F IFO 状态 寄存器 A CAP1 的 FIFO 堆栈顶层寄存 器 CAP2 的 FIFO 堆栈顶层寄存 器 CAP3 的 FIFO 堆栈顶层寄存 器 CAP1 的 FIFO 堆栈底层寄存 器 CAP2 的 FIFO 堆栈底层寄存 器 CAP3 的 FIFO 堆栈底层寄存 器 捕获单元控 制寄存器 B 捕获单元 F IFO 状态 寄存器 B CAP4 的 FIFO 堆栈顶层寄存 器 CAP5 的 FIFO 堆栈顶层寄存 器 CAP6 的 FIFO 堆栈顶层寄存 器 CAP4 的 FIFO 堆栈底层寄存 器 CAP5 的 FIFO 堆栈底层寄存 器 CAP6 的 FIFO 堆栈底层寄存 器 EVA 中断标志寄存器 A EVA 中断屏蔽寄存器 A EVA 中断标志寄存器 B EVA 中断屏蔽寄存器 B EVA 中断标志寄存器 C EVA 中断屏蔽寄存器 C EVB 中断标志寄存器 A EVB 中断屏蔽寄存器 A EVB 中断标志寄存器 B EVB 中断屏蔽寄存器 B EVB 中断标志寄存器 C EVB 中断屏蔽寄存器 C ADC 控制 寄存器 1 ADC 控制 寄存器 2 ADC 最大转换通道寄 存器 ADC 通道选额控制寄 存器 1 ADC 通道选额控制寄 存器 2 ADC 通道选额控制寄 存器 3

TIMER 2TIMH TIMER 2PRD

F2812性能及引脚简介

//设置B组端口为GPIO功能 // 设置B组端口为输出端口 //设置F组端口为GPIO功能 // 设置F组端口为输出端口

需要注意:

• EALLOW—— 在DSP28_Device.h头文件中,通过“#define EALLOW asm (" EALLOW ") 在C语言主函数中嵌入汇编语言指令,汇编指令 “EALLOW”其含义为开放存储器映像寄存器,设置该命令后,可以 对MMR内容进行修改。当需要配置或修改MMR内容时,必须先写入 EALLOW汇编指令。反之,如果不首先写入EALLOW汇编指令,无 法完成对相应MMR内容的修改。 • EDIS:为结束修改MMR的汇编命令。当MMR配置完成后,需要写入 该命令。

微处理器监控器MAX690/692/703—709/813L(美国 MAXIM公司产品)

• 微机控制系统中,为了保证微处理器稳定可靠运行,需要配置电 压监控电路;为了实现掉电数据保护,需备用电池及切换电路; 为了使微处理器尽快摆脱干扰而陷入死循环,需要配置Watchdog 电路,将完成这些功能的电路集成到一个芯片中,称为微处理器 监控器。 • 实现功能: 1)在上电、掉电以及低压供电时,产生一个复位输出信号。 2)具有备用电池切换电路,备用电池可供给CMOS RAM芯片或 其他低功耗逻辑电路。 3)具有看门狗电路,该电路的外触发脉冲的时间间隔超过1.6S 时,将产生一个复位输出。 4)可用于低压检测 5)复位脉冲宽度Trs 200ms,复位门限电平 MAX690:4.65V,MAX692:4.40V

看门狗功能的软件配置

// Disable watchdog module SysCtrlRegs.WDCR= 0x0068; • • • • • • • • • • • // This function resets the watchdog timer. // Enable this function for using KickDog in the application /* void KickDog(void) { EALLOW; SysCtrlRegs.WDKEY = 0x0055; SysCtrlRegs.WDKEY = 0x00AA; EDIS; } */

DSP2812寄存器汇总

PIE, INT9组使能寄存器

PIEIFR9

P201

PIE, INT9组标志寄存器

PIEIER10

P201

PIE, INT10组使能寄存器

PIEIFR10

P201

PIE, INT10组标志寄存器

PIEIER11

P201

PIE, INT11组使能寄存器

PIEIFR11

P201

PIE, INT11组标志寄存器

P187

CPU定时器2控制寄存器

TIMER2TPR

P187

CPU定时器2预定标寄存器低位

TIMER2TPRH

P187

CPU定时器2预定标寄存器高位

CPU中断寄存器

IER

P196

CPU中断使能寄存器

IFR

P196

CPU中断标志寄存器

INTM

P196

CPU全局中断标志位

PIE(外设中断控制器)中断寄存器

EVAIFRA

P257

EVA中断标志寄存器A

EVAIMRA

P257

EVA中断屏蔽寄存器A

EVAIFRB

P257

EVA中断标志寄存器B

EVAIMRB

P257

EVA中断屏蔽寄存器B

EVAIFRC

P257

EVA中断标志寄存器C

EVAIMRC

P257

EVA中断屏蔽寄存器C

EVBIFRA

P257

EVB中断标志寄存器A

P293

ADC自动序列状态寄存器

ADCRESULT0

P293

ADC转换结果缓冲寄存器0

ADCRESULT1

P293

ADC转换结果缓冲寄存器1

TMS320F2812处理器特性

TMS320F2812处理器特性1.高性能静态CMOS(Static CMOS)技术●150MHz(时钟周期6.67ns)●低功耗(核心电压1.8V,I/O口电压3.3V)●Flash编程电压3.3V2.JTAG边界扫描(Boundary Scan)支持3.高性能的32位中央处理器(TMS320C28x)●16位*16位和32位*32位乘且累加操作●16位*16位的两个乘且累加●哈佛总线结构●强大的操作能力●快速的中断响应和处理●统一的寄存器编码模式●可达4兆字的线性程序地址●可达4兆字的数据地址●代码高效(用C/C++或汇编语言)●与TMS320F24/LF240x处理器的源代码兼容4.片内存储器●128K*16位的Flash存储器●1K*16位的OTP型只读存储器●L0和L1:两块4K**16位的单口随机存储器(SARAM)●H0:一块8K*16位的单口随机存储器●M0和M1:两块1K**16位的单口随机存储器5.引导存储器(Boot ROM)4K*16位●带有软件的Boot模式●标准数学表6.外部存储器接口(部分型号拥有,且标准不一)●最多1MB的存储器●可编程等待状态数●可编程读/写选通计数器(Strobe Timing)●三个独立的片选7.时钟与系统控制●支持动态的改变锁相环的频率●片内振荡器●看门狗定时器模块8.三个外部中断9.外部中断扩展(PIE)模块。

可支持96个外部中断,2812仅使用了45个外部中断。

10.128位的密匙(Security Key/Lock)●保护Flash/OTP和L0/L1 SARAM●防止ROM中的程序被盗11.3个32位的CPU定时器●12.马达控制外围设备●两个事件管理器(EVA、EVB)●与C240兼容的器件●13.串口外围设备●串行外围接口(SPI)●两个串行通信接口(SCIs),标准UART●增强型局域网络(eCAN)●多通道缓冲串行接口(McBSP)14.12位ADC,16通道●2*8通道的输入多路选择器●两个采样保持器●单一/同步转换●最快转换时间:80ns/12.5MSPS15.最多有56个独立的可编程、多用途通用输入/输出(GPIO)引脚16.高级的仿真特性●分析和设置断点的功能●实时的硬件调试17.开发工具●ANSI C/C++编译器/汇编程序/连接器●支持TMS320C24x/240x的指令●CCS集成开发环境●DSP/BIOS●JTAG扫描控制器(TI或第三方提供)●硬件评估板18.低功耗模式和节能模式●支持空闲模式、等待模式、挂起模式●停止单个外围的时钟19.封装方式●带外部存储器接口的179球型触点BGA封装●带外部存储器接口的176引脚低剖面四芯线扁平LQFP封装●没有外部存储器接口的128引脚贴片正方扁平PBK封装。

2812芯片

2812芯片

2812芯片是一种高性能、低功耗的单片机芯片,主要用于嵌入式应用领域。

它采用了Cortex-M3内核,拥有更高的处理能力和更低的功耗。

2812芯片的主要特点有以下几个方面:

1. 高性能:2812芯片采用了Cortex-M3内核,拥有72MHz的主频,具备较强的处理能力。

同时,它还支持硬件浮点运算和DSP指令集,能够满足更高级别的应用需求。

2. 低功耗:2812芯片在低功耗方面表现出色,通过灵活的功耗管理技术,能够在不同的休眠模式之间快速切换,从而减少功耗。

此外,它还采用了精简的电源管理电路,有效降低了功耗。

3. 多种接口:2812芯片支持多种常用的接口,包括UART、SPI、I2C等,以满足不同应用场景的需求。

同时,它还具备丰富的外设资源,如定时器、ADC、DAC等,可用于实现各种功能。

4. 强大的存储容量:2812芯片内置了较大的Flash存储器和RAM存储器,可用于存储程序代码和数据。

其中,Flash存储器的容量可达到数十KB甚至更大。

5. 多种封装形式:2812芯片提供了多种封装形式,如QFN、LQFP等,以适应不同的应用需求。

同时,它还支持工业级温

度范围,适合在各种环境条件下工作。

在实际应用中,2812芯片被广泛用于各种嵌入式系统,如消费电子产品、工业自动化设备、智能家居等。

它具备高性能、低功耗、丰富的接口和强大的存储容量等优势,可以实现复杂的控制和处理任务,满足不同应用的要求。

总之,2812芯片是一种性能出众的单片机芯片,通过其优秀的处理能力、低功耗和多种接口等特点,能够广泛应用于各种嵌入式领域,为用户提供高效、可靠的解决方案。

第2章TMS320F2812DSP内部结构

内容摘要

TMS320C2000概述 2.1 TMS320F2812中央处理单元 2.2 TMS320F2812存储器配置 2.3 TMS320F2812的引导加载方式 2.4 TMS320F2812的低功耗模式

2

TMS320C2000概述

TMS320C2000是TI公司继第二代定点DSP 处理器TMS320C2X和第三代定点DSP处理器 TMS320C5X之后出现的一种低价格、高性能的 定点DSP芯片。 主要包括: TMS320C24X、TMS320C28X两个子系列。

EVA/EVB

16通道

12位ADC

XRS

X1/XCLKIN X2 XF_XPLLDIS

系统控制 (振荡器、 PPL、外设时 钟、低功耗模 式、看门狗)

RS

CLKIN 存储器总线 外设总线

26

代码保护的模块

2.1.1 TMS320F2812CPU内部结构

TMS320F2812中包含一个高性能低功耗的32位 定点CPU内核,它主要负责DSP内部指令的控制和 数据的处理,主要由CPU内部寄存器、总线及相应 控制逻辑组成: 1.32位中央算术逻辑单元(CALU) 2.32位累加器(ACC) 3.能进行16bit×16bit或32bit×32bit定点乘法运 算的硬件乘法器(MUL) 4.桶形移位器 5.辅助寄存器算术单元(ARAU)及地址产生逻辑 6. 程序地址产生器及控制逻辑

Register Bus / Result Bus Data/Program-write Data Bus (32) Data-write Address Bus (32)

乘法器

Program Bus Data Bus

32 16 32

操作数1

F2812-GPIO详细资料说课讲解

F2812-G P I O详细资料F2812 I/O配置与应用GPIO,英文全称为General-Purpose IO ports,也就是通用IO口。

嵌入式系统中常常有数量众多,但是结构却比较简单的外部设备/电路,对这些设备/电路有的需要CPU为之提供控制手段,有的则需要被CPU用作输入信号。

而且,许多这样的设备/电路只要求一位,即只要有开/关两种状态就够了,比如灯亮与灭。

对这些设备/电路的控制,使用传统的串行口或并行口都不合适。

所以在微控制器芯片上一般都会提供一个“通用可编程IO接口”,即GPIO。

接口至少有两个寄存器,即“通用IO控制寄存器”与“通用IO数据寄存器”。

数据寄存器的各位都直接引到芯片外部,而对这种寄存器中每一位的作用,即每一位的信号流通方向,则可以通过控制寄存器中对应位独立的加以设置。

这样,有无GPIO接口也就成为微控制器区别于微处理器的一个特征。

一、 F2812 I/O端口概述F2812提供了56个多功能引脚,这些引脚的第一功能是作为通用意义数字I/O口(GPIO),而第二功能则可以作为片内外设的输入/输出引脚。

F2812通过专门的多路选择器(MUX)进行引脚功能的选择。

如果作为通用数字I/O 口,有专门的方向寄存器用于配置引脚作为输入还是输出,另外还有专门的数据寄存器、置位寄存器、清零寄存器以及触发寄存器用于对I/O口的状态进行读取或配置。

GPIO 引脚分配GPIO AGPIOA0 / PWM1 GPIOA1 / PWM2 GPIOA2 / PWM3 GPIOA3 / PWM4 GPIOA4 / PWM5 GPIOA5 / PWM6 GPIOA6 / T1PWM_T1CMP GPIOA7 / T2PWM_T2CMP GPIOA8 / CAP1_QEP1 GPIOA9 / CAP2_QEP2 GPIOA10 / CAP3_QEPI1 GPIOA11 / TDIRA GPIOA12 / TCLKINA GPIOA13 / C1TRIP GPIOA14 / C2TRIP GPIOA15 / C3TRIPGPIO BGPIOB0 / PWM7 GPIOB1 / PWM8 GPIOB2 / PWM9 GPIOB3 / PWM10 GPIOB4 / PWM11GPIOB5 / PWM12GPIOB6 / T3PWM_T3CMPGPIOB7 / T4PWM_T4CMPGPIOB8 / CAP4_QEP3GPIOB9 / CAP5_QEP4GPIOB10 / CAP6_QEPI2GPIOB11 / TDIRBGPIOB12 / TCLKINBGPIOB13 / C4TRIPGPIOB14 / C5TRIPGPIOB15 / C6TRIPGPIO DGPIOD0 /T1CTRIP_PDPINTAGPIOD1 / T2CTRIP / EVASOCGPIOD5 /T3CTRIP_PDPINTBGPIOD6 / T4CTRIP / EVBSOCGPIO EGPIOE0 / XINT1_XBIOGPIOE1 / XINT2_ADCSOCGPIOE2 / XNMI_XINT13 GPIO FGPIOF0 / SPISIMOA GPIOF1 / SPISOMIA GPIOF2 / SPICLKAGPIOF3 / SPISTEAGPIOF4 / SCITXDAGPIOF5 / SCIRXDAGPIOF6 / CANTXAGPIOF7 / CANRXAGPIOF8 / MCLKXAGPIOF9 / MCLKRAGPIOF10 / MFSXAGPIOF11 / MFSRAGPIOF12 / MDXAGPIOF13 / MDRAGPIOF14 / XFGPIO GGPIOG4 / SCITXDBGPIOG5 / SCIRXDBNote: GPIO are pinfunctions at reset GPIO A, B, D, E include Input Qualification feature二、GPIO寄存器控制2、1 GPxMUX寄存器通用输入输出多路选择寄存器I/O是工作在通用数字IO还是外围IO信号引脚就有GPxMUX决定。

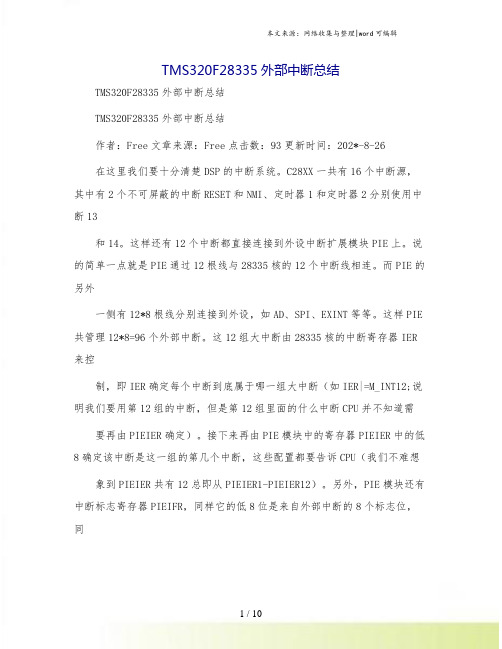

TMS320F28335外部中断总结

TMS320F28335外部中断总结TMS320F28335外部中断总结TMS320F28335外部中断总结作者:Free文章来源:Free点击数:93更新时间:202*-8-26在这里我们要十分清楚DSP的中断系统。

C28XX一共有16个中断源,其中有2个不可屏蔽的中断RESET和NMI、定时器1和定时器2分别使用中断13和14。

这样还有12个中断都直接连接到外设中断扩展模块PIE上。

说的简单一点就是PIE通过12根线与28335核的12个中断线相连。

而PIE的另外一侧有12*8根线分别连接到外设,如AD、SPI、EXINT等等。

这样PIE 共管理12*8=96个外部中断。

这12组大中断由28335核的中断寄存器IER 来控制,即IER确定每个中断到底属于哪一组大中断(如IER|=M_INT12;说明我们要用第12组的中断,但是第12组里面的什么中断CPU并不知道需要再由PIEIER确定)。

接下来再由PIE模块中的寄存器PIEIER中的低8确定该中断是这一组的第几个中断,这些配置都要告诉CPU(我们不难想象到PIEIER共有12总即从PIEIER1-PIEIER12)。

另外,PIE模块还有中断标志寄存器PIEIFR,同样它的低8位是来自外部中断的8个标志位,同样CPU的IFR寄存器是中断组的标志寄存器。

由此看来,CPU的所有中断寄存器控制12组的中断,PIE的所有中断寄存器控制每组内8个的中断。

除此之外,我们用到哪一个外部中断,相应的还有外部中断的寄存器,需要注意的就是外部中断的标志要自己通过软件来清零。

而PIE和CPU的中断标志寄存器由硬件来清零。

EALLOW;//ThisisneededtowritetoEALLOWprotectedregistersPieVectTable.XINT2=&ISRExint;//告诉中断入口地址EDIS;//ThisisneededtodisablewritetoEALLOWprotectedregisters PieCtrlRegs.PIECTRL.bit.ENPIE=1;//EnablethePIEblock使能PIE PieCtrlRegs.PIEIER1.bit.INTx5=1;//使能第一组中的中断5IER|=M_INT1;//EnableCPU第一组中断EINT;//EnableGlobalinterruptINTMERTM;//EnableGlobalrealtimeinterruptDBGM也就是说,12组中的每个中断都要完成上面的相同配置,剩下的才是去配置自己的中断。

1 TMS320F2812简介

1 TMS320F2812简介TMS320F2812是TI公司的一款用于控制的高性能、多功能、高性价比的32位定点DSP芯片。

该芯片兼容TMS320LF2407指令系统最高可在150MHz主频下工作,并带有18k×16位0等待周期片上SRAM和128k×16位片上FLASH(存取时间36ns)。

其片上外设主要包括2×8路12位ADC(最快80ns转换时间)、2路SCI、1路SPI、1路McBSP、1路eCAN等,并带有两个事件管理模块(EVA、EVB),分别包括6路PWM/CMP、2路QEP、3路CAP、2路16位定时器(或TxPWM/TxCMP)。

另外,该器件还有3个独立的32位CPU定时器,以及多达56个独立编程的GPIO引脚,可外扩大于1M×16位程序和数据存储器。

TMS320F2812采用哈佛总线结构,具有密码保护机制,可进行双16×16乘加和32×32乘加操作,因而可兼顾控制和快速运算的双重功能。

通过对TMS320F2812定点DSP芯片合理的系统配置和编程可实现快速运算,本文着重对此加以说明。

2 TMS320F2812基本系统配置2.1TMS320F2812时钟TMS320F2812的片上外设按输入时钟可分为如下4个组:(1)SYSOUTCLK组:包括CPU定时器和eCAN总线,可由PLLCR寄存器动态地修改;(2)OSCCLK组:主要是看门狗电路,由WDCR寄存器设置分频系数;(3)低速组:有SCI、SPI、McBSP,可由LOSPCP寄存器设置分频系数;(4)高速组:包括EVA/B、ADC,可由HISPCP寄存器设置分频系数。

为了使系统具有较快的工作速度,除了定时器和SCI等少数需要低速时钟的地方,其它外设均可以150MHz时钟工作。

图12.2存储空间图1所示是TMS320F2812的内部存储空间映射图。

TMS320F2812为哈佛(Harvard)结构的DSP,即在同一个时钟周期内可同时进行一次取指令、读数据和写数据的操作。

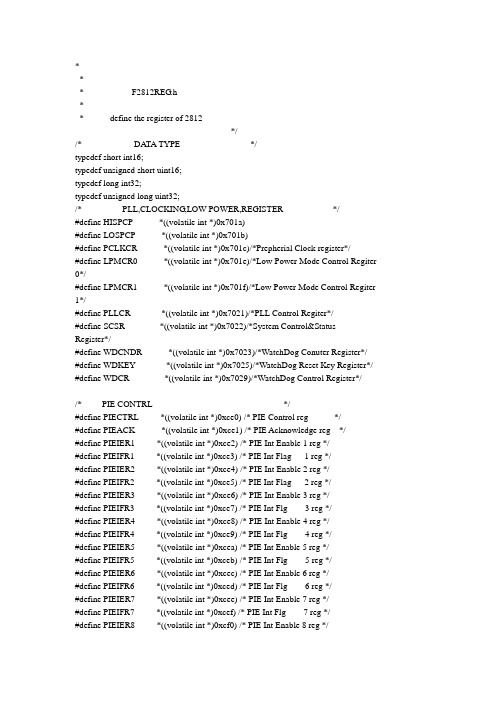

2812内部寄存器

*--------------------------------------------------** F2812REG.h** define the register of 2812----------------------------------------------------*//*------------------DATA TYPE------------------------*/typedef short int16;typedef unsigned short uint16;typedef long int32;typedef unsigned long uint32;/*--------------PLL,CLOCKING,LOW POWER,REGISTER-----------------*/#define HISPCP *((volatile int *)0x701a)#define LOSPCP *((volatile int *)0x701b)#define PCLKCR *((volatile int *)0x701c)/*Prepherial Clock register*/#define LPMCR0 *((volatile int *)0x701e)/*Low Power Mode Control Regiter 0*/#define LPMCR1 *((volatile int *)0x701f)/*Low Power Mode Control Regiter 1*/#define PLLCR *((volatile int *)0x7021)/*PLL Control Regiter*/#define SCSR *((volatile int *)0x7022)/*System Control&StatusRegister*/#define WDCNDR *((volatile int *)0x7023)/*WatchDog Conuter Register*/ #define WDKEY *((volatile int *)0x7025)/*WatchDog Reset Key Register*/ #define WDCR *((volatile int *)0x7029)/*WatchDog Control Register*//*-------PIE CONTRL---------------------------------------------*/#define PIECTRL *((volatile int *)0xce0) /* PIE Control reg */#define PIEACK *((volatile int *)0xce1) /* PIE Acknowledge reg */#define PIEIER1 *((volatile int *)0xce2) /* PIE Int Enable 1 reg */#define PIEIFR1 *((volatile int *)0xce3) /* PIE Int Flag 1 reg */#define PIEIER2 *((volatile int *)0xce4) /* PIE Int Enable 2 reg */#define PIEIFR2 *((volatile int *)0xce5) /* PIE Int Flag 2 reg */#define PIEIER3 *((volatile int *)0xce6) /* PIE Int Enable 3 reg */#define PIEIFR3 *((volatile int *)0xce7) /* PIE Int Flg 3 reg */#define PIEIER4 *((volatile int *)0xce8) /* PIE Int Enable 4 reg */#define PIEIFR4 *((volatile int *)0xce9) /* PIE Int Flg 4 reg */#define PIEIER5 *((volatile int *)0xcea) /* PIE Int Enable 5 reg */#define PIEIFR5 *((volatile int *)0xceb) /* PIE Int Flg 5 reg */#define PIEIER6 *((volatile int *)0xcec) /* PIE Int Enable 6 reg */#define PIEIFR6 *((volatile int *)0xced) /* PIE Int Flg 6 reg */#define PIEIER7 *((volatile int *)0xcee) /* PIE Int Enable 7 reg */#define PIEIFR7 *((volatile int *)0xcef) /* PIE Int Flg 7 reg */#define PIEIER8 *((volatile int *)0xcf0) /* PIE Int Enable 8 reg */#define PIEIFR8 *((volatile int *)0xcf1) /* PIE Int Flg 8 reg */ #define PIEIER9 *((volatile int *)0xcf2) /* PIE Int Enable 9 reg */ #define PIEIFR9 *((volatile int *)0xcf3) /* PIE Int Flg 9 reg */ #define PIEIER10 *((volatile int *)0xcf4) /* PIE Int Enable 10 reg */ #define PIEIFR10 *((volatile int *)0xcf5) /* PIE Int Flg 10 reg */ #define PIEIER11 *((volatile int *)0xcf6) /* PIE Int Enable 11 reg */ #define PIEIFR11 *((volatile int *)0xcf7) /* PIE Int Flg 11 reg */ #define PIEIER12 *((volatile int *)0xcf8) /* PIE Int Enable 12 reg */ #define PIEIFR12 *((volatile int *)0xcf9) /* PIE Int Flg 12 reg */ /*-------EVENT MANAGER REGISTER-------------------*//*-------------EVA Register-------------------------------*/#define GPTCONA *((volatile int *)0x7400)#define T1CNT *((volatile int *)0x7401)#define T1CMPR *((volatile int *)0x7402)#define T1PR *((volatile int *)0x7403)#define T1CON *((volatile int *)0x7404)#define T2CNT *((volatile int *)0x7405)#define T2CMPR *((volatile int *)0x7406)#define T2PR *((volatile int *)0x7407)#define T2CON *((volatile int *)0x7408)#define EXTCONA *((volatile int *)0x7409)#define COMCONA *((volatile int *)0x7411)#define ACTRA *((volatile int *)0x7413)#define DBTCONA *((volatile int *)0x7415)#define CMPR1 *((volatile int *)0x7417)#define CMPR2 *((volatile int *)0x7418)#define CMPR3 *((volatile int *)0x7419)#define CAPCONA *((volatile int *)0x7420)#define CAPFIFOA *((volatile int *)0x7422)#define CAP1FIFO *((volatile int *)0x7423)#define CAP2FIFO *((volatile int *)0x7424)#define CAP3FIFO *((volatile int *)0x7425)#define CAP1FBOT *((volatile int *)0x7427)#define CAP2FBOT *((volatile int *)0x7428)#define CAP3FBOT *((volatile int *)0x7429)#define EV AIMRA *((volatile int *)0x742c)#define EV AIMRB *((volatile int *)0x742d)#define EV AIMRC *((volatile int *)0x742e)#define EV AIFRA *((volatile int *)0x742f)#define EV AIFRB *((volatile int *)0x7430)#define EV AIFRC *((volatile int *)0x7431)/*-------------EVB Register-------------------------------*/#define GPTCONB *((volatile int *)0x7500)#define T3CNT *((volatile int *)0x7501)#define T3PR *((volatile int *)0x7503)#define T3CON *((volatile int *)0x7504) #define T4CNT *((volatile int *)0x7505)#define T4CMPR *((volatile int *)0x7506) #define T4PR *((volatile int *)0x7507)#define T4CON *((volatile int *)0x7508) #define EXTCONB *((volatile int *)0x7509) #define COMCONB *((volatile int *)0x7511) #define ACTRB *((volatile int *)0x7513) #define DBTCONB *((volatile int *)0x7515) #define CMPR4 *((volatile int *)0x7517) #define CMPR5 *((volatile int *)0x7518) #define CMPR6 *((volatile int *)0x7519) #define CAPCONB *((volatile int *)0x7520) #define CAPFIFOB *((volatile int *)0x7522) #define CAP4FIFO *((volatile int *)0x7523)#define CAP5FIFO *((volatile int *)0x7524) #define CAP6FIFO *((volatile int *)0x7525)#define CAP4FBOT *((volatile int *)0x7527) #define CAP5FBOT *((volatile int *)0x7528) #define CAP6FBOT *((volatile int *)0x7529) #define EVBIMRA *((volatile int *)0x752c) #define EVBIMRB *((volatile int *)0x752d) #define EVBIMRC *((volatile int *)0x752e) #define EVBIFRA *((volatile int *)0x752f)#define EVBIFRB *((volatile int *)0x7530) #define EVBIFRC *((volatile int *)0x7531) /*----------------GPIO----------------------------*//*----------------MUX REGISTER------------------*/ #define GPAMUX *((volatile int *)0x70c0) #define GPADIR *((volatile int *)0x70c1)#define GPAQUAL *((volatile int *)0x70c2) #define GPBMUX *((volatile int *)0x70c4) #define GPBDIR *((volatile int *)0x70c5)#define GPBQUAL *((volatile int *)0x70c6) #define GPDMUX *((volatile int *)0x70cc) #define GPDDIR *((volatile int *)0x70cd) #define GPDQUAL *((volatile int *)0x70ce) #define GPEMUX *((volatile int *)0x70d0) #define GPEDIR *((volatile int *)0x70d1)#define GPEQUAL *((volatile int *)0x70d2) #define GPFMUX *((volatile int *)0x70d4) #define GPFDIR *((volatile int *)0x70d5)#define GPGDIR *((volatile int *)0x70d9)/*-----------------DATA REGISTER-----------------*/#define GPADAT *((volatile int *)0x70e0)#define GPASET *((volatile int *)0x70e1)#define GPACLEAR *((volatile int *)0x70e2)#define GPATOGGLE *((volatile int *)0x70e3)#define GPBDAT *((volatile int *)0x70e4)#define GPBSET *((volatile int *)0x70e5)#define GPBCLEAR *((volatile int *)0x70e6)#define GPBTOGGLE *((volatile int *)0x70e7)#define GPDDAT *((volatile int *)0x70ec)#define GPDSET *((volatile int *)0x70ed)#define GPDCLEAR *((volatile int *)0x70ee)#define GPDTOGGLE *((volatile int *)0x70ef)#define GPEDAT *((volatile int *)0x70f0)#define GPESET *((volatile int *)0x70f1)#define GPECLEAR *((volatile int *)0x70f2)#define GPETOGGLE *((volatile int *)0x70f3)#define GPFDAT *((volatile int *)0x70f4)#define GPFSET *((volatile int *)0x70f5)#define GPFCLEAR *((volatile int *)0x70f6)#define GPFTOGGLE *((volatile int *)0x70f7)#define GPGDAT *((volatile int *)0x70f8)#define GPGSET *((volatile int *)0x70f9)#define GPGCLEAR *((volatile int *)0x70fa)#define GPGTOGGLE *((volatile int *)0x70fb)/*--------------ADC REGUSTER---------------------*/ #define ADCTRL1 *((volatile int *)0x7100)#define ADCTRL2 *((volatile int *)0x7101)#define ADCMAXCONV *((volatile int *)0x7102) #define ADCCHSELSEQ1 *((volatile int *)0x7103) #define ADCCHSELSEQ2 *((volatile int *)0x7104) #define ADCCHSELSEQ3 *((volatile int *)0x7105) #define ADCCHSELSEQ4 *((volatile int *)0x7106) #define ADCASEQSR *((volatile int *)0x7107) #define ADCRESULT0 *((volatile int *)0x7108)#define ADCRESULT1 *((volatile int *)0x7109)#define ADCRESULT2 *((volatile int *)0x710a)#define ADCRESULT3 *((volatile int *)0x710b)#define ADCRESULT4 *((volatile int *)0x710c)#define ADCRESULT5 *((volatile int *)0x710d)#define ADCRESULT6 *((volatile int *)0x710e)#define ADCRESULT8 *((volatile int *)0x7110)#define ADCRESULT9 *((volatile int *)0x7111)#define ADCRESULT10 *((volatile int *)0x7112)#define ADCRESULT11 *((volatile int *)0x7113)#define ADCRESULT12 *((volatile int *)0x7114)#define ADCRESULT13 *((volatile int *)0x7115)#define ADCRESULT14 *((volatile int *)0x7116)#define ADCRESULT15 *((volatile int *)0x7117)#define ADCTRL3 *((volatile int *)0x7118)#define ADCST *((volatile int *)0x7119)/*-----------------SCI MODULE REGISTER-----------*/ /*-----------------SCIA--------------------------*/#define SCICCRA *((volatile int *)0x7050)#define SCICTL1A *((volatile int *)0x7051)#define SCIHBAUDA *((volatile int *)0x7052) #define SCILBAUDA *((volatile int *)0x7053) #define SCICTL2A *((volatile int *)0x7054)#define SCIRXSTA *((volatile int *)0x7055)#define SCIRXEMUA *((volatile int *)0x7056) #define SCIRXBUFA *((volatile int *)0x7057)#define SCITXBUFA *((volatile int *)0x7059)#define SCIFFTXA *((volatile int *)0x705a)#define SCIFFRXA *((volatile int *)0x705b)#define SCIFFCTA *((volatile int *)0x705c)#define SCIPRIA *((volatile int *)0x705f)/*-----------------SCIB--------------------------*/#define SCICCRB *((volatile int *)0x7750)#define SCICTL1B *((volatile int *)0x7751)#define SCIHBAUDB *((volatile int *)0x7752) #define SCILBAUDB *((volatile int *)0x7753) #define SCICTL2B *((volatile int *)0x7754)#define SCIRXSTB *((volatile int *)0x7755)#define SCIRXEMUB *((volatile int *)0x7756) #define SCIRXBUFB *((volatile int *)0x7757)#define SCITXBUFB *((volatile int *)0x7759)#define SCIFFTXB *((volatile int *)0x775a)#define SCIFFRXB *((volatile int *)0x775b)#define SCIFFCTB *((volatile int *)0x775c)#define SCIPRIB *((volatile int *)0x775f)/*-----------------XINTF-------------------------*/#define XTIMING0 *((volatile long *)0x0b20) #define XTIMING1 *((volatile long *)0x0b22) #define XTIMING2 *((volatile long *)0x0b24)#define XTIMING7 *((volatile long *)0x0b2e) #define XINTCNF2 *((volatile long *)0x0b34) #define XBANK *((volatile long *)0x0b38) #define XREVISION *((volatile long *)0x0b3a) /*-----------------FLASH-------------------------*/#define FOPT *((volatile int *)0x0a80)#define FPWR *((volatile int *)0x0a82) #define FSTATUS *((volatile int *)0x0a83) #define FSTDBYW AIT *((volatile int *)0x0a84) #define FACTIVEW AIT *((volatile int *)0x0a85) #define FBANKWAIT *((volatile int *)0x0a86) #define FOPTW AIT *((volatile int *)0x0a87) /*----------------- DA -------------------------*/#define DAF *((volatile int *)0x2ff0)#define DAH *((volatile int *)0x3ff0)/*--------------External Interrupt---------------*/#define XINT1CR *((volatile int *)0x7070) #define XINT2CR *((volatile int *)0x7071) #define XNMICR *((volatile int *)0x7077) #define XINT1CTR *((volatile int *)0x7078) #define XINT2CTR *((volatile int *)0x7079) #define XNMICTR *((volatile int *)0x707f) /*-----------------TIMER-------------------------*/ typedef struct{uint32 Timer; // Timer Counteruint32 Period; // Timer Perioduint16 Control; // Timer Controluint16 Rsvd; // Reserveduint32 Prescale; // Timer Pre-Scale} C28X_TIMER;/*-----------------------------------------------*//*EOF*/。

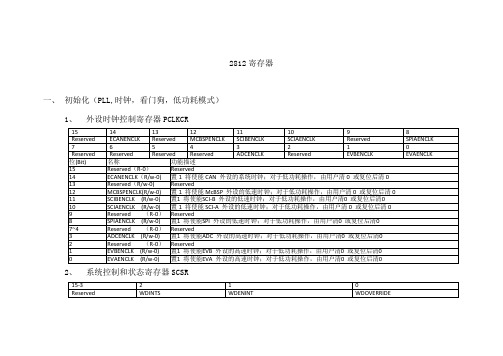

2812寄存器

2812寄存器一、初始化(PLL,时钟,看门狗,低功耗模式)1、外设时钟控制寄存器PCLKCR2、系统控制和状态寄存器SCSR3、高速外设时钟设置寄存器HISPCP4、低速外设时钟设置寄存器LOSPCP5、锁相环PLL控制寄存器PLLCR6、低功耗模式控制寄存器0(LPMCR0)7、低功耗模式控制寄存器1(LPMCR1)如果各个位都置1,将使选择的信号从备用方式唤醒器件;如果各个位都置0,信号无效8、看门狗计数寄存器WDCNTR9、看门狗复位寄存器WDKEY10、看门狗控制寄存器WDCR二、 PIE1、PIE中断配置寄存器PIECTRL2、PIE中断响应寄存器PIEACKx3、PIE中断标志寄存器PIEIFRx4、PIE中断使能寄存器PIEIERx5、CPU中断标志寄存器IFR6、CPU中断使能寄存器IER7、调试中断使能寄存器DBGIER(仅当CPU暂停实时仿真时使用该寄存器)8、外部中断1控制寄存器XINT1CR9、外部中断2控制寄存器XINT2CR10、外部NMI中断控制寄存器XNMICR11、外部中断1计数寄存器XINT1CTR12、外部中断2计数寄存器XINT2CTR13、外部NMI中断计数控制寄存器XNMICTCR三、 GPIO1、GPIO功能控制寄存器GPxMUXGPxMUX.位=0,配置为I/O功能GPxMUX.位=1,配置为外设功能2、GPIO方向控制寄存器GPxDIRGPxDIR.位=0,引脚配置为数字输入GPxDIR.位=1,引脚配置为数字输出3、GPIO数据寄存器GPxDATGPxDAT.位=0,且设置为输出功能,将相应的引脚拉低GPxDAT.位=1,且设置为输出功能,将相应的引脚拉高4、GPIO设置寄存器GPxSETGPxSET.位=0,无影响GPxSET.位=1,且设置为输出功能,将相应的引脚置成高电平5、GPIO清除寄存器GPxCLEARGPxCLEAR.位=0,无影响GPxCLEAR.位=1,且设置为输出功能,将相应的引脚置成低电平6、GPIO反转触发寄存器GPxTOGGLEGPxTOGGLE.位=0,无影响GPxTOGGLE.位=1,且设置为输出功能,将相应的引脚取反。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

2812寄存器

一、初始化(PLL,时钟,看门狗,低功耗模式)

1、外设时钟控制寄存器PCLKCR

2、系统控制和状态寄存器SCSR

3、高速外设时钟设置寄存器HISPCP

4、低速外设时钟设置寄存器LOSPCP

5、锁相环PLL控制寄存器PLLCR

6、低功耗模式控制寄存器0(LPMCR0)

7、低功耗模式控制寄存器1(LPMCR1)

如果各个位都置1,将使选择的信号从备用方式唤醒器件;如果各个位都置0,信号无效8、看门狗计数寄存器WDCNTR

9、看门狗复位寄存器WDKEY

10、看门狗控制寄存器WDCR

二、 PIE

1、PIE中断配置寄存器PIECTRL

2、PIE中断响应寄存器PIEACKx

3、PIE中断标志寄存器PIEIFRx

4、PIE中断使能寄存器PIEIERx

5、CPU中断标志寄存器IFR

6、CPU中断使能寄存器IER

7、调试中断使能寄存器DBGIER(仅当CPU暂停实时仿真时使用该寄存器)

8、外部中断1控制寄存器XINT1CR

9、外部中断2控制寄存器XINT2CR

10、外部NMI中断控制寄存器XNMICR

11、外部中断1计数寄存器XINT1CTR

12、外部中断2计数寄存器XINT2CTR

13、外部NMI中断计数控制寄存器XNMICTCR

三、 GPIO

1、GPIO功能控制寄存器GPxMUX

GPxMUX.位=0,配置为I/O功能

GPxMUX.位=1,配置为外设功能

2、GPIO方向控制寄存器GPxDIR

GPxDIR.位=0,引脚配置为数字输入

GPxDIR.位=1,引脚配置为数字输出

3、GPIO数据寄存器GPxDAT

GPxDAT.位=0,且设置为输出功能,将相应的引脚拉低

GPxDAT.位=1,且设置为输出功能,将相应的引脚拉高

4、GPIO设置寄存器GPxSET

GPxSET.位=0,无影响

GPxSET.位=1,且设置为输出功能,将相应的引脚置成高电平5、GPIO清除寄存器GPxCLEAR

GPxCLEAR.位=0,无影响

GPxCLEAR.位=1,且设置为输出功能,将相应的引脚置成低电平6、GPIO反转触发寄存器GPxTOGGLE

GPxTOGGLE.位=0,无影响

GPxTOGGLE.位=1,且设置为输出功能,将相应的引脚取反。

7、GPIO限制寄存器GPxQUAL

GPIO F 及GPIO G 端口不需要采样周期限制寄存器

四、 EV

1、通用定时器全局控制寄存器A/B (GPTCONA/B)

2、通用定时器计数、比较、周期寄存器

3、定时器控制寄存器TxCON

4、比较控制寄存器COMCONA/B

5、比较操作寄存器ACTRA/B

6、死区定时器控制寄存器DBTCONA/B

7、EV扩展控制寄存器EXTCONA/B

8、捕捉单元控制寄存器CAPCONA/B

9、捕捉单元结果及状态寄存器CAPFIFOA

10、EVA中断标志寄存器A(EVAIFRA)

11、EVA中断标志寄存器B(EVAIFRB)

12、EVA中断标志寄存器C(EVAIFRC)

13、EVA中断屏蔽寄存器A(EVAIMRA)

14、EVA中断屏蔽寄存器B(EVAIMRB)

15、EVA中断屏蔽寄存器C(EVAIMRC)

五、 ADC

1、ADC控制寄存器1(ADCTRL1)

2、ADC控制寄存器2(ADCTRL2)

3、ADC控制寄存器3(ADCTRL3)

4、最大转换通道寄存器MAXCONV

5、自动排序状态寄存器AUTO_SEQ_SR

6、ADC状态和标志寄存器ADC_ST_FLG

7、ADC输入通道选择排序寄存器ADCCHSELSEQ[4..1]

8、ADC转换结果缓冲寄存器RESULTn

六、 SPI

1、配置控制寄存器SPICCR

2、操作控制寄存器SPICTL

3、状态寄存器SPIST

4、波特率选择寄存器SPIBRR

5、仿真缓冲寄存器SPIEMU

6、串行接收缓冲寄存器SPIRXBUF

7、串行发送缓冲寄存器SPITXBUF

8、串行数据寄存器SPIDAT

9、SPI FIFO发送寄存器SPIFFTX

10、SPI FIFO接收寄存器SPIFFRX

11、SPI FIFO 控制寄存器SPIFFCT

12、优先级控制寄存器SPIPRI

七、 SCI

1、SCI通信控制寄存器

2、SCI控制寄存器1(SCICTL1)

3、SCI控制寄存器2(SCICTL2)

4、SCI接收状态寄存器SCIRXST

5、接收数据缓冲寄存器SCIRXBUF

6、SCI优先级控制寄存器SCIPRI

八、 ECAN

1、邮箱使能寄存器CANME

2、邮箱数据方向寄存器CANMD

3、发送请求置位寄存器CANTRS

4、发送请求复位寄存器CANTRR

5、发送相应寄存器CANTA

6、异常中断相应寄存器CANAA

7、接收消息挂起寄存器CANRMP

8、接收消息丢失寄存器RML

9、远程帧挂起寄存器CANRFP

10、全局接收屏蔽寄存器CANGAM

11、主控寄存器CANMC

12、位定时配置寄存器CANBTC

13、错误和状态寄存器CANES

14、发送错误计数寄存器(CANTEC)

15、接收错误计数寄存器(CANREC)

16、全局中断标志寄存器(CANGIF0/CANGIF1)

17、全局中断屏蔽寄存器(CANGIM)

18、邮箱中断屏蔽寄存器(CANMIM)

19、邮箱中断级别寄存器(CANMIL)

20、覆盖保护控制寄存器(CANOPC)

21、TXIO 控制寄存器(CANTIOC)

22、RXIO 控制寄存器(CANRIOC)

23、超时控制寄存器(CANTOC)

24、超时状态寄存器(CANTOS)

九、 XINTF

1、XINTF时序寄存器XTIMING0/1/2/6/7

2、XINTF配置寄存器XINTCNF2

3、XBANK寄存器。