以ARM和DSP为核心的实时仿真平台的开发

基于ARM+FPGA+多DSP的嵌入式实时图像处理系统

基于ARM+FPGA+多DSP的嵌入式实时图像处理系统关键字:实时图像处理FPGA FIFO实时图像处理、高速数据运算处理要求其系统具有对数据处理速度快、数据吞吐率高以及多任务处理功能。

目前大多数方案都是采用HPI数据传输方式,将ARM和DSP进行组合完成一些图像处理,DSP处理器只是完成图像采集、压缩、编码等简单的处理[1]工作,不能满足实时的智能识别或大数据量运算的视频处理要求。

在应用领域方面也会因其处理速度问题受到一定的限制。

例如,胎儿性别屏蔽项目中,要对实时视频进行性别部位的检测和屏蔽,若采用单DSP则会出现漏帧或视频不流畅;应用于高速运动物体跟踪时,单DSP无法实现实时运动物体跟踪,例如汉王科技的运动检测和海康威视运动检测,都不能实时检测,即使检测也会出现漏检现象和视频不流畅。

当处理4CIF或者更大图像时,单DSP的处理能力又会下降,虽然可以将图像缩小进行处理,但是缩小图像则会丢失一些重要的图像信息,使得智能识别准确率下降。

针对上述情况,设计一种能够实现进行快速信号处理和数据交换的实时图像处理系统很有必要。

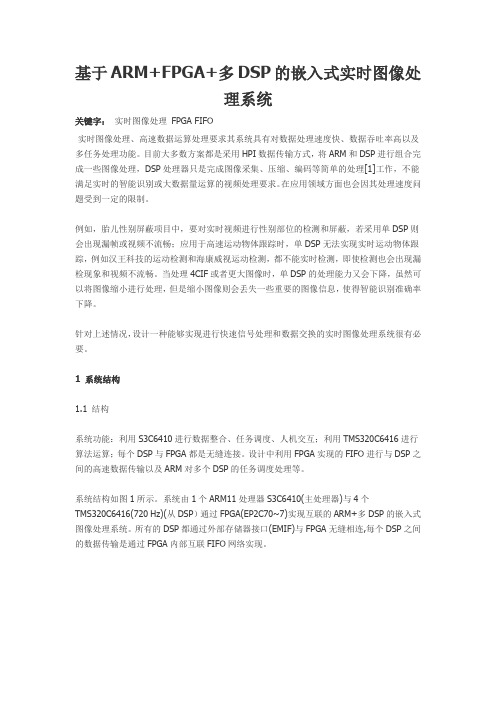

1 系统结构1.1 结构系统功能:利用S3C6410进行数据整合、任务调度、人机交互;利用TMS320C6416进行算法运算;每个DSP与FPGA都是无缝连接。

设计中利用FPGA实现的FIFO进行与DSP之间的高速数据传输以及ARM对多个DSP的任务调度处理等。

系统结构如图1所示。

系统由1个ARM11处理器S3C6410(主处理器)与4个TMS320C6416(720 Hz)(从DSP)通过FPGA(EP2C70~7)实现互联的ARM+多DSP的嵌入式图像处理系统。

所有的DSP都通过外部存储器接口(EMIF)与FPGA无缝相连,每个DSP之间的数据传输是通过FPGA内部互联FIFO网络实现。

图2所示是一种互联的FIFO网络结构和高速数据传输网络结构。

主处理器通过DMA数据访问模式与FPGA的双口FIFO连接,从而实现与FPGA通过FIFO连接的所有从DSP进行通信,所有FIFO都是双向的,FIFO及其读写控制逻辑都在FPGA内部实现。

ARM加DSP嵌入式双架构系统的设计与实现

兰

州

交

通

大

学

学

报

Vo 1 No 3 L3 .

Jun l f az o ioo gUnvri o r a o n h uJ tn iest L a y

J n 0 2 u e2 1

文章编号 :0 14 7 (0 2 0 —1 80 10 —3 3 2 1 )30 3—4

式多媒体应用程序平台 ( MA , pnMut ei O P O e lm d i a A pi t n l f m) T 公司推 出的专 门为支 plaos a o 是 I c i P tr 持第 3 (G 无线终端应用而设计的应用处理器 代 3) 体系结构 , 但这类芯片价格昂贵, 不适合完成某些特

定专 业领 域 的处理 . 了适 合 用户 自己的应用 需求 , 为

研究 基 于 AR 加 DS M P双 处理 器 的 架构 , 充 分 的 能

公司的高性能产 品. 系统设计采用 T 的高性 能数 I 字信 号处理 器 T 30 6 1T。芯 片 , 的核 心 主 MS 2C 4 6 [ ] 它 频能达到 1G , HZ 并且具有 丰富的片上 资源, 能够

ARM 加 D P嵌 入式 双 架构 系统 的设计 与 实现 S

赵 晶 , 王新 楼

70 7 ) 3 0 0

( 兰州交通大学 电子与信 息工程学 院, 甘肃 兰州

摘

要 : ¥C 40 在 3 2 4 A与 ¥ 2 C 4 6 30 6 1T芯 片为处理核心的基础上 , 出了一种基 于 AR 加 DS 提 M P双 架构 系统的软硬

件解决方案 , 为嵌 入 式信 号 处理 提 供 了新 的 设 计 理 念 和 实现 方 法 , 于 此 系统 可 以扩 展 开 发 出其 他 各 种 复 杂 的 信 基

基于ARM和DSP的嵌入式智能仪器系统设计.

基于ARM和DSP的嵌入式智能仪器系统设计1 引言随着智能仪器及控制系统对实时性信号处理的要求不断提高和大规模集成电路技术的迅速发展。

越来越迫切的要求有一种高性能的设计方案与之相适应,将DSP技术和ARM技术结合起来应用于嵌入式系统中,将会充分发挥两者优势以达到智能控制系统中对数据的实时性、高效性的通信要求。

该嵌入式系统要求实时响应,具有严格的时序性。

其工作环境可能非常恶劣,如高温、低温、潮湿等,所以系统还要求非常高的稳定性。

2 嵌入1 引言随着智能仪器及控制系统对实时性信号处理的要求不断提高和大规模集成电路技术的迅速发展。

越来越迫切的要求有一种高性能的设计方案与之相适应,将DSP技术和ARM技术结合起来应用于嵌入式系统中,将会充分发挥两者优势以达到智能控制系统中对数据的实时性、高效性的通信要求。

该嵌入式系统要求实时响应,具有严格的时序性。

其工作环境可能非常恶劣,如高温、低温、潮湿等,所以系统还要求非常高的稳定性。

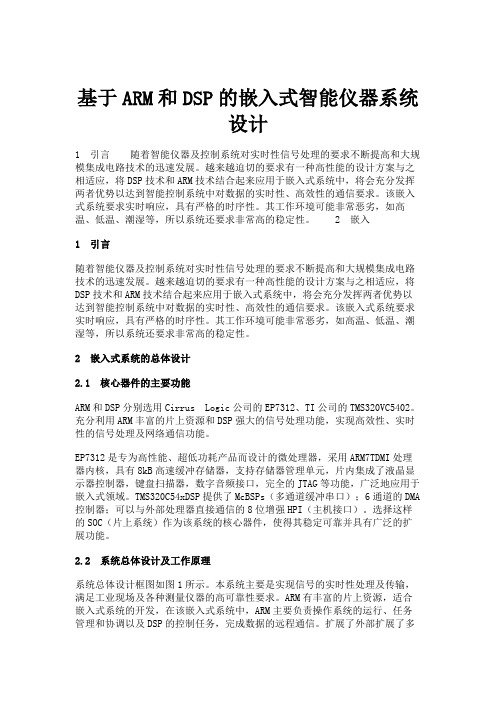

2 嵌入式系统的总体设计2.1 核心器件的主要功能ARM和DSP分别选用Cirrus Logic公司的EP7312、TI公司的TMS320VC5402。

充分利用ARM丰富的片上资源和DSP强大的信号处理功能,实现高效性、实时性的信号处理及网络通信功能。

EP7312是专为高性能、超低功耗产品而设计的微处理器,采用ARM7TDMI处理器内核,具有8kB高速缓冲存储器,支持存储器管理单元,片内集成了液晶显示器控制器,键盘扫描器,数字音频接口,完全的JTAG等功能,广泛地应用于嵌入式领域。

TMS320C54xDSP提供了McBSPs(多通道缓冲串口);6通道的DMA 控制器;可以与外部处理器直接通信的8位增强HPI(主机接口)。

选择这样的SOC(片上系统)作为该系统的核心器件,使得其稳定可靠并具有广泛的扩展功能。

2.2 系统总体设计及工作原理系统总体设计框图如图1所示。

本系统主要是实现信号的实时性处理及传输,满足工业现场及各种测量仪器的高可靠性要求。

基于ARM_DSP架构的新型智能仪器开发

在 Linux 中以模块的形式来加载设备, 在加载 模 块 时 , 需 要

调 用 入 口 函 数 init_mod ule , 而 在 卸 载 模 块 时 , 需 要 调 用 e x-

it_mod ule 。设备驱动程序通过 file _op e ra tions 数据结构提供访

问设备驱动的函数, 对于 SPI 这种字符型设备, 需要在驱动中实

r_SPCON0 = iore ma p (0x59000000,4)V

/ /SPI re g is te r

r_SPSTA0 = iore ma p (0x59000004,4)V

r_SPPIN0 = iore ma p (0x59000008,4)V

r_SPPRE0 = iore ma p (0x5900000C,4)V

备接口, 可用于外扩 USB 打印 机 等 USB 主 机 设 备 ; 片 内 包 括 3

个 UART, 通 过 电 平 转 换 芯 片 SIPEX3232 扩 展 串 口 ; 为 了 实 现

大容量数据的存储, 可以借助于片内的 SD 卡接口扩展 SD 卡,

或者通过 S3C2410A 开放的数据和地址总线结合通用片选信

无 相 位 延 时 的 下 降 沿 、有 相 位 延 时 的 下 降 沿 、无 相 位 延 迟 的 上 升

ห้องสมุดไป่ตู้

沿和有相位延迟的上升沿。图 4 为无相位延时的下降沿的 SPI

时序图。

图 4 无相位延时的下降沿的 SPI 时序

主从机通信的基本流程如下: 主机通过发出 SPICLK 信 号

来启动数据传输, 此时从机发送伪数据, 从机通过中断方式来接

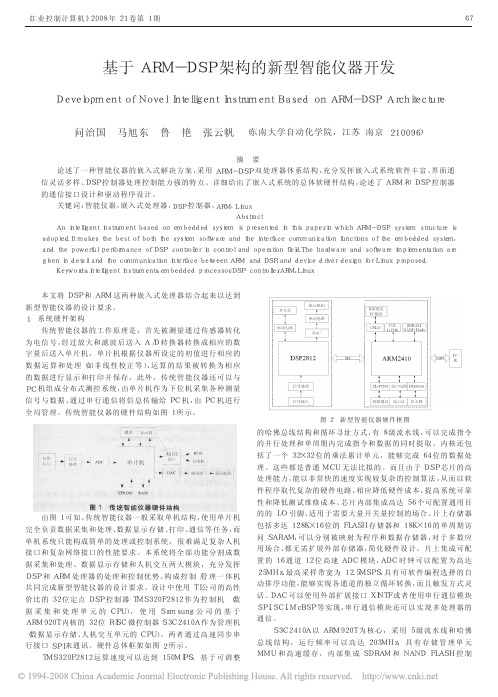

本文将 DSP 和 ARM 这两种嵌入式处理器结合起来以达到 新型智能仪器的设计要求。 1 系统硬件架构

基于MATLAB和DSP的滤波器硬件在环实时仿真

基于MAT LAB 和DSP 的滤波器硬件在环实时仿真3肖 兵 蔡一波 梁瑛琳(华南理工大学自动化科学与工程学院 广州 510641)摘 要:本文介绍了一种设计滤波器的新方法。

该方法基于硬件在环实时仿真系统,通过MA TL AB 对DSP 的滤波输出信号进行跟踪分析,实现了滤波器的快速设计。

该滤波器准确度高,具有较强的实用性与灵活性。

关键词:硬件在环;实时仿真;滤波中图分类号:TN713+.7 文献标识码:AFilter hardw are 2in 2loop real 2time simulationbased on MAT LAB and DSPXiao Bing Cai Y ibo Liang Y inglin(College of Automation Science and Engineering ,Sout h China University of Technology ,Guangzhou 510641)Abstract :This paper presented a new method of designing a filter.By tracing and analyzing the filter output signals of DSP on the platform of Matlab ,a fast realization of filter can be achieved on the basis of a hardware 2in 2loop real 2time simulation system.Simulation test indicates that this filter has high accuracy and the feature of flexibility and practicability.K eyw ords :hardware 2in 2loop ;real 2time simulation ;filter3基金项目:国家自然科学基金(60474042),广东省自然科学基金(04020000)作者简介:肖兵(19642),男,副研究员,主要从事汽车发动机控制、模式识别与故障诊断等方向的研究。

基于ARMDSP嵌入式系统ARM模块软件设计.

第16卷第1期2006年3月湖南工程学院学报Vo1.16.No.1Mar.2006 JournalofHunanInstituteofEngineering基于ARM/DSP嵌入式系统ARM模块软件设计聂建成,刘斌Ξ(湖南师范大学新闻与传播学院,湖南长沙410006)摘要:ARM/DSP平台是采用ARM7和DSP双CPU构建的嵌入式系统开发平台.ARM模块部分是其一个重要的组成部分.在系统中ARM模块主要负责系统控制部分,由于ARM的接口丰富,因而其接口电路驱动软件设计复杂,详细介绍了嵌入式系统中ARM.关键词:ARM;Microwindows;接口中图分类号:TP391.41文献标识码:A:0061-03.中间层则是可移,提供画线,区域填充,多边形绘制,裁切等操作及设置不同的颜色模式.在最上层,通过不同的API为程序员提供不同的图形应用实现.目前,Microwindows支持WindowsWin32,WinCEGDI,以及Nano-XAPI编程方式,这些API提供了与Win32及XWindows系统较为接近的兼容性,因此,使得其他环境下的应用程序能很容易地移植到Microwindows平台.1.2Microwindows的设备驱动Microwindows至少应连接一个显示屏,一个鼠标以及一个键盘入系统,然后层中与设备无关的例程将通过核心图形引擎调用设备驱动,进而执行特定硬件平台的操作[3].这种设计使得在Microwin2dows平台中可以挂接不同的硬件设备,且不会影响整个系统的工作方式.1.3MicroGUI,设备无关的图形引擎Microwindows的核心功能依赖于设备无关的0引言ARM部分PA的ARMLINUXVersion2.[1],并在此基础之上移植LINUX标准库GLIBC;图形支持库:LIB2JPG,LIBPNG;图形加载库:IMLIB,网页HTML,XML语法分析库LIBWWW,FLASH插件库:LIBFLASH,及汉字库.图形界面以Microwindows0.9及其控件库FLNX提供嵌入式图形界面平台. 本系统平台具有强大的网络通信功能,通过平台WEBSERVER,FTP,TELNET,INETD等网络工具和应用程序能方便开发基于INTERNET的网络终端,远程控制,远程数据采集、远程数据处理产品.在应用程序层上,系统平台集成窗口管理程序,全中文化网络浏览器(支持HTML,XML),FLASH 播放器(支持FLASH4,FLASH5,FLASH6),文本编辑器,游戏等用于PDA开发,机顶盒上网解决方案,以及可用于嵌入式数据采集、处理的虚拟示波器.1Microwindows的结构1.1Microwindows的分层设计Microwindows为分层结构设计[2],因此用户可图形引擎,通过这个引擎来调用底层屏幕,鼠标及键盘驱动的硬件接口.由于一系列的原因,图形引擎与用户程序是分离的,用户程序不直接调用中间层的图形引擎,而通过调用API来实现.其核心函数都使用类似于GdXXX()的名字,并于图形的输出有关,而不是与窗口管理有关.另外,所有的裁切及着色变换都在这个层中完在,其中,表1中的文件是Microwindows核心模块的组成文件:devdraw.c包含画线,画圆,多边形及绘制及填充,文本位图绘制及着色变换的核心函数.以在不同的层上使用Microwindows,用户也可以根据自己的需要对其中的某层或多层进行改写.在Microwindows各层中,最底层提供了屏幕,鼠标或触摸屏及键盘驱动,因些通过这层可以访问实际的Ξ收稿日期:2005-08-18作者简介:聂建成(1968-),男,硕士研究生,讲师,研究方向:计算机图形图像及应用.© 1994-2006 China Academic Journal Electronic Publishing House. All rights reserved. 62湖南工程学院学报2006年表1Microwindows核心模块组成文件(3)如果连接成功,通过write()开始传送.(4)使用完后则通过close()关闭连接.2)接收端的设计接收端的命令格式为:文件名devclip.cdevrgn.cdevmouse.cdevkbd.cdevpalX.c功能核心图形裁切例程区域交,并,差及异或的动态分配例程更新鼠标位置的核心例程,及屏幕裁切核心键盘处理例程静态连接1,2,4,8位色的调色板系统接收程序文件存放目录我们通过以下几个骤来处理接收端程序(1)调用socket()返回一个Socket.(2)调用bind()将Socket与端口之类的信息进行绑定(3)调用listen()进行端口监听(4)调用accept()(5)如果完成,()关闭连接2.Microwindows支持两种不同的应用程序接口,通过这些接口来处理Client/Server事件,以及比如画工具栏,关窗口等等之类的窗口管理活动,同时也包括程序员的图形输出请求.两种类型的API都运行于核心图形引擎和设备驱动之上.Microwidows之上的API始化屏幕,键盘,鼠标驱动,.当事件发生,事件,paint事件等.,然后参数被GdXXX()函数引擎.而窗口操作及图形操作都是在这个API层上完成的.这就是API所定义的窗口概念,窗口坐标等.然后所有的坐标被转换成屏幕坐标,再传入核心GdXXX()函数引擎来完成实际工作.在这个层中,同时也定义了图形及显示上下文并把这些信息传递到核心引擎例程.,.从该桌面可以方便ARM系统中的各个应用程序,从而实现可视化的系统操作接口,方便管理,且使系统管理更加人性化.并且在启动ARM的图形化程序界面之前.会先启动一个Logo画,显示一些辅助的信息.图1Microwindows与用户的程序结构框图图2管理程序的界面2.3嵌入虚拟仪器设计2基于Microwindows的接口软件开发2.1网络文件传送程序的设计1)发送端的设计发送端的命令格式为:发送程序收方的IP地址文件或选项(可以为文件或目录,且可有多个)我们通过以下几个步骤来与接收端来建立连接:(1)通过调用socket()取得一个Socket文件描运行于ARM开发板上的波形采样程序的程序界面图如图3所示.波形采样程序是与DSP联系在一起的一个虚拟仪器程序,其工作过程如下所述:DSP提供硬件支持,对输入波形进行采样,然后将采集的信号量化成8位的数据送去ARM板上的HPI口,HPI口的驱动程序处于DSP采集系统与虚拟仪器程序之间,做为中间桥梁,将采集的数据送入应用程序,并可将程序对DSP的控制信号送入DSP系统.从而实现ARM系统板与DSP采集系统之间的交互.述符.(2)通过调用connect()试图与接收方连接.© 1994-2006 China Academic Journal Electronic Publishing House. All rights reserved. 第1期聂建成等:基于ARM/DSP嵌入式系统ARM模块软件设计633结束语本文给出了基于Microwindows的嵌入式系统开发软件设计原理,给出了基于Microwindows的具体系统接口程序设计.系统具有较强的可扩展性,在系统的现有基础上很容易构建出各种嵌入式系统.参考文献[1][[2]http://kernelnewbies.kdoc[WZ].[3]K.LINUX编程权威指龙华乔..,基础与应用系统设计[M].北京航空,2002.图3ARMModuleSoftwareDesignBasedonARM/DSPEmbeddedSystemNIEJian-cheng,LIUBin(CollegeofJournalismandCommunication,HunanNormalUniversity,Changsha410006,Ch ina)Abstract:TheARM/DSPPlatformisaembeddedsystembasedonARM7andDSPprocessors. TheplatformcontainsaARMsubsystem.Thesubsystemisanimportantpartoftheembeddedsy stemandARMsubsystemworksassystemcontrolpartwithcomplexinterfacesoftwaredesign. ThisarticleintroducestheARMsubsysteminterfacesoftwaredesign.Keywords:ARM;Microwindows;interface© 1994-2006 China Academic Journal Electronic Publishing House. All rights reserved. 。

一种基于arm及dsp双核开发板的制作方法

一种基于arm及dsp双核开发板的制作方法一种基于arm及dsp双核开发板的制作方法本实用新型提供了一种基于ARM及DSP双核开发板,包括底板、处理器、实验操作面板,所述处理器包括ARM处理器和DSP处理器,ARM处理器与DSP处理器互相连接,所述ARM处理器的输出端连接在显示屏上,DSP的处理器的输出端连接在电机控制模块上,所述ARM处理器和DSP处理器的串口连接在IO扩展口上,所述实验操作面板包括有第一实验操作面板和第二实验操作面板,所述第一实验操作面板与ARM处理器互连,第二实验操作面板与DSP处理器互连。

【专利说明】【技术领域】[0001] 本实用新型涉及实验设备【技术领域】,尤其涉及一种基于DSP及ARM 双内核开发板 -种基于ARM及DSP双核开发板【背景技术】[0002] ARM与DSP是嵌入式系统应用最广泛的两类型的微处理器,ARM主要指采用ARM内核的各种嵌入式微处理器和微控制器,DSP主要指具有针对高速运算而进行各种优化处理的数字信号处理器。

[0003] 传统的微处理器开发板,基本是一个处理器内核,开发模式也比较单纯。

无法满足当前应用的复杂性,为了更好能能满足应用和媒体的需求,集成众多接口,需要一种的双核架构开发板,使微处理器的学习爱好者迅速掌握这门技术。

实用新型内容[0004] 本实用新型提供了一种基于ARM及DSP双核开发板,以其结构简单,设计合理,使用灵活方便,有利于学生迅速掌握当前飞速发展的ARM及DSP双核处理器技术。

[0005] 为了解决上述问题,本实用新型提供了一种基于ARM及DSP双核开发板,包括底板、处理器、实验操作面板,所述处理器包括ARM处理器和DSP 处理器,ARM处理器与DSP处理器互相连接,所述ARM处理器的输出端连接在显示屏上,DSP的处理器的输出端连接在电机控制模块上,所述ARM处理器和DSP处理器的串口连接在10扩展口上,所述实验操作面板包括有第一实验操作面板和第二实验操作面板,所述第一实验操作面板与ARM处理器互连,第二实验操作面板与DSP处理器互连。

ARM+DSP开发详解

一、绪言针对当前应用的复杂性,SOC芯片更好能能满足应用和媒体的需求,集成众多接口,用ARM做为应用处理器进行多样化的应用开发和用户界面和接口,利用DSP进行算法加速,特别是媒体的编解码算法加速,既能够保持算法的灵活性,又能提供强大的处理能力。

德州仪器(TI)继第一系列Davinci芯片DM644x之后,又陆续推出了DM643x,DM35x/36x,DM6467,OMAP35x,OMAPLx等一系列ARM+DSP或ARM+视频协处理器的多媒体处理器平台。

众多有很强DSP开发经验的工程师,以及应用处理开发经验的工程师都转到使用达芬奇或OMAP平台上开发视频监控、视频会议及便携式多媒体终端等产品。

基于ARM+DSP的芯片架构,如何进行开发实现做期望的嵌入式应用呢?传统的芯片,基本是一个处理器内核,或者是通用处理器如ARM,或者是DSP。

对于控制和用户接口,一般用通用处理器实现,算法处理或者媒体处理则依赖于DSP或者硬件芯片,很多系统都是双芯片的架构。

开发模式也比较单纯,比如ARM芯片,有ARM的的仿真工具,基于OS之上进行应用开发;DSP有DSP的开发工具,如TI的CCS以及510、560的仿真器,可以进行算法的移植、优化、跟踪、调试等。

这时,所需要的经验也比较单一。

基于ARM+DSP的双核架构,很多工程师不知道如何入手进行开发,提出了很多的疑问,比如对ARM工程师,很困惑的是如何使用DSP的资源?如何进行数据的交互?如何保持双核之间的同步?对DSP工程师,则问到如何进行ARM调试?如何启动DSP?如果进行媒体加速,如何操作外设获取或发送数据等二、芯片介绍基于不同的开发经验和基础,ARM工程师和DSP工程师会从完全不同的角度来看SOC的芯片,以至于拿到SOC的芯片根本不知道如何入手,这里就本人的经验与大家分享一下。

首先ARM+DSP的芯片,他是一个双核的,对应ARM和DSP分别是不同的指令集和编译器,可以把SOC的芯片看成是两个单芯片的合成,需要两套不同的开发工具,CCS3.3可以进行芯片级的调试和仿真,但是对应ARM和DSP需要选择不同的平台。

深入了解DSP和ARM的关系(相同与区别)

深入了解DSP和ARM的关系(相同与区别)DSP:DSP(digital singnal processor)是一种独特的微处理器,有自己的完整指令系统,是以数字信号来处理大量信息的器件。

一个数字信号处理器在一块不大的芯片内包括有控制单元、运算单元、各种寄存器以及一定数量的存储单元等等,在其外围还可以连接若干存储器,并可以与一定数量的外部设备互相通信,有软、硬件的全面功能,本身就是一个微型计算机。

DSP采用的是哈佛设计,即数据总线和地址总线分开,使程序和数据分别存储在两个分开的空间,允许取指令和执行指令完全重叠。

也就是说在执行上一条指令的同时就可取出下一条指令,并进行译码,这大大的提高了微处理器的速度。

另外还允许在程序空间和数据空间之间进行传输,因为增加了器件的灵活性。

其工作原理是接收模拟信号,转换为0或1的数字信号,再对数字信号进行修改、删除、强化,并在其他系统芯片中把数字数据解译回模拟数据或实际环境格式。

它不仅具有可编程性,而且其实时运行速度可达每秒数以千万条复杂指令程序,源源超过通用微处理器,是数字化电子世界中日益重要的电脑芯片。

它的强大数据处理能力和高运行速度,是最值得称道的两大特色。

DSP芯片,由于它运算能力很强,速度很快,体积很小,而且采用软件编程具有高度的灵活性,因此为从事各种复杂的应用提供了一条有效途径。

其主要应用是实时快速地实现各种数字信号处理算法。

根据数字信号处理的要求,DSP芯片一般具有如下主要特点:(1)在一个指令周期内可完成一次乘法和一次加法;(2)程序和数据空间分开,可以同时访问指令和数据;(3)片内具有快速RAM,通常可通过独立的数据总线在两块中同时访问;(4)具有低开销或无开销循环及跳转的硬件支持;(5)快速的中断处理和硬件I/O支持;(6)具有在单周期内操作的多个硬件地址产生器;(7)可以并行执行多个操作;(8)支持流水线操作,使取指、译码和执行等操作可以重叠执行。

基于ARM和DSP的运动控制平台设计及驱动程序开发

机床与液压

MACH INE TOOL & HYDRAULICS

Jan 2010 V ol 38 N o 1

DO I: 10. 3969 / j issn 1001 - 3881 2010 01 017

基于 ARM 和 DSP的运动控制平台设计及驱动程序开发

杨代华, 刘俊, 张盼盼

W indows CE把设 备 驱动 程序 分成 2 类: 本机 设 备驱动程序和流式接口驱动程序。本机驱动程序适合 于集成到基于 CE平台的设 备, 是专门为 底层硬 件而 设计的, 如键盘、屏幕等。流驱动程序, 是一般类型 的设备驱动程序, 支持的设备非常广泛。任何在逻辑 上可以看作为数据源的设备都可以为其实现流驱动程 序 [ 4]。流驱动把外设抽象成一个文件, 当应用程序使 用文件 API函 数对 设备 进 行访 问时, 操作 系 统接 受 AP I函 数并 调 用 F ileSys exe, 转 到 Dev ice exe, 调 用 流接口与硬件交互。

理等, 所有的 流驱 动函 数以 DLL 的输出 函数 形 式被 下文介绍的 AP I函数调用。

在 对 设 备 进 行 读 操作 之 前 , 首 先 要通 过 执 行

( 下转第 74页 )

& 74&

机床与液压

第 38卷

3% 。学习训练 6 600 次后, 结果 如表 2 所 示。再 用 经训练后的神经网络对余下的 3组数据进行计算, 以 检查网络的外推性能, 检验结果如表 3所示。

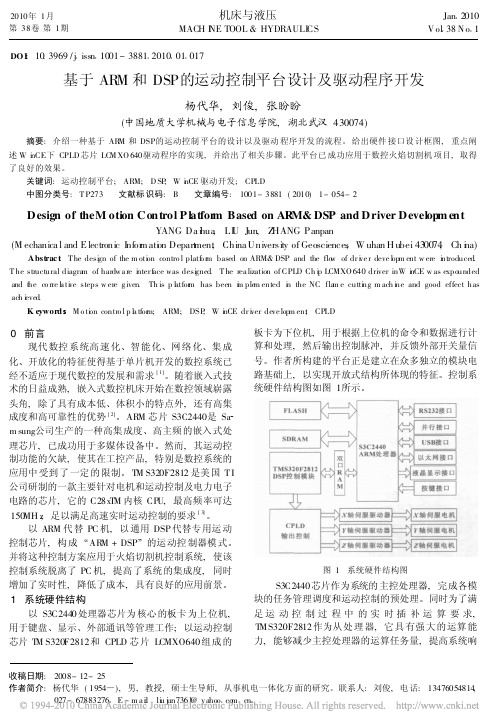

图 1 系统硬件结构图

S3C2440 芯片作为系统的 主控处理器, 完 成各模 块的任务管理调度和运动控制的预处理。同时为了满 足 运 动 控 制 过 程 中 的 实 时 插 补 运 算 要 求, TM S320F2812 作为从 处 理 器, 它 具 有强 大 的 运算 能 力, 能够减少主控处理器的运算任务量, 提高系统响

基于ARM与DSP的切绘机运动控制平台的设计.

3.43级中断服务程序3级中断主要完成CRT 显示处理,如果没有其它各级中断,系统就进行CRT 显示处理。

CRT 显示器的显示内容有各轴绝对位置和相对位置、零件程序、系统参数、I/O 接口状态数据、故障号等。

根据最近一次显示方式键操作的记忆状态,选择相应的内容显示。

4系统特点(1采用时间分割法的插补运算方法,具有多象限圆弧插补的功能。

理论上其快速移动速度、直线和圆弧插补速度均可达到步进电机驱动装置所允许的最大速度,且插补精度在1个脉冲当量范围内。

当脉冲当量为0.01mm ,1.6kg-m 步进电机空载时,最大直线和圆弧(R=250mm 时插补速度均可达到4.8m/min 。

步进电机安装到激光加工机后,最大直线和圆弧插补速度均可达3.2m/min 。

(2系统的数控指令格式、零件程序格式都符合ISO 国际标准。

若有格式错误,系统可进行自动诊断。

(3进给速度极限值、手动快速值、点位进给速度值等均作系统参数由用户设定,以获得适合具体控制对象的最佳运动参数。

(4经过输入、输出接口板的输入、输出信号,可操作诊断方式键进行诊断,以确定故障部位出自机床强电部分还是系统部分。

系统有20多种报警信息,当系统发生故障停机时,自动发出报警信息,操作有关按键,CRT 说明发生故障的原因。

(5该系统是针对激光加工机的控制要求设计的,只要系统的硬件和软件稍加扩充,也适用于其它数控机床,经过中间试验、工业试验和现场使用,证明系统设计是合理的。

5测试结果样机经过对不同厚度的钢板进行切割和焊接试验,测试结果令人满意。

在厚为2mm 的普通钢板上进行半圆、整圆、凸轮、巨型圆形的切割,切缝为0.2mm ,切割速度最高达1700mm/min ,加工误差±0.2mm ,曲率半径误差在±0.25mm 之内。

又在厚8mm 的钢板上切割整圆和矩形圆形,切缝为0.45mm ,最大切割速度达600mm/min 。

加工误差在±0.4mm 之内,曲率半径误差在±0.45mm 之内。

基于ARM+DSP进行应用开发 - 经验共享

有不足和不完善的,请各位批评指正针对当前应用的复杂性,SOC芯片更好能能满足应用和媒体的需求,集成众多接口,用ARM 做为应用处理器进行多样化的应用开发和用户界面和接口,利用DSP进行算法加速,特别是媒体的编解码算法加速,既能够保持算法的灵活性,又能提供强大的处理能力。

德州仪器(TI)继第一系列Davinci芯片DM644x之后,又陆续推出了DM643x,DM35x/36x,DM6467,OMAP35x,OMAPLx等一系列ARM+DSP或ARM+视频协处理器的多媒体处理器平台。

众多有很强DSP开发经验的工程师,以及应用处理开发经验的工程师都转到使用达芬奇或OMAP平台上开发视频监控、视频会议及便携式多媒体终端等产品。

基于ARM+DSP的芯片架构,如何进行开发实现做期望的嵌入式应用呢?传统的芯片,基本是一个处理器内核,或者是通用处理器如ARM,或者是DSP。

对于控制和用户接口,一般用通用处理器实现,算法处理或者媒体处理则依赖于DSP或者硬件芯片,很多系统都是双芯片的架构。

开发模式也比较单纯,比如ARM芯片,有ARM的的仿真工具,基于OS之上进行应用开发;DSP有DSP的开发工具,如TI的CCS以及510、560的仿真器,可以进行算法的移植、优化、跟踪、调试等。

这时,所需要的经验也比较单一。

基于ARM+DSP的双核架构,很多工程师不知道如何入手进行开发,提出了很多的疑问,比如对ARM工程师,很困惑的是如何使用DSP的资源?如何进行数据的交互?如何保持双核之间的同步?对DSP工程师,则问到如何进行ARM调试?如何启动DSP?如果进行媒体加速,如何操作外设获取或发送数据等。

基于不同的开发经验和基础,ARM工程师和DSP工程师会从完全不同的角度来看SOC的芯片,以至于拿到SOC的芯片根本不知道如何入手,这里就本人的经验与大家分享一下。

首先ARM+DSP的芯片,他是一个双核的,对应ARM和DSP分别是不同的指令集和编译器,可以把SOC的芯片看成是两个单芯片的合成,需要两套不同的开发工具,CCS3.3可以进行芯片级的调试和仿真,但是对应ARM和DSP需要选择不同的平台。

基于DSP和ARM的远程视频监控系统的设计

A 9 R 90是完全围绕A M90 R hm 处理器构建的系统 , T 1 M 20 R 2T A M T u b 拥有丰富的硬件资源及标准的外部接 口,工作主频高达20 M z 0 H ,是一款高性能 、低功耗 、低成本的处理器 .以太网控制器采用D 9 6E M 11 , D 11  ̄一  ̄ 1/( p快 速 以太 网物 理层 单芯 片 收发器 ,用 它作 为A M9 M96E 一'0lo Mbs ) R 的外设 与其 相连 ,再 通过 R4 接 口与以太网相连,同时采用一个大容量I E J5 D 硬盘同A M 相连 ,实现本地必要数据的存储 , R 9 其硬件结 构见 图4 .

Ma 2 v 0ll

文章编号 :10 —8 l( 0 )0 — 0 2 0 07 93 2 1 1 3 05 — 3

基 于 D P和 A M 的远程视频 监控 系统 的设计 S R

胥伟 ,王亮 ,王军

( .中国联通 齐齐 哈尔市 分公 司 信 息化 支撑 中心 ,黑龙 江 齐齐 哈尔 110 1 60 3 2 齐 齐哈 尔大学 计算机 与控 制工程 学院 ,黑 龙江 齐齐 哈尔 110 . 606)

基于ARM与DSP的机器视觉硬件平台设计与研究

目录

01 一、硬件平台设计

03 三、实验结果与分析

02 二、软件平台研究 04 参考内容

机器视觉是领域的一个重要分支,被广泛应用于自动化生产线、智能交通、 医疗诊断等领域。随着技术的不断发展,以ARM和DSP为核心的嵌入式系统逐渐成 为机器视觉硬件平台的主流选择。本次演示将介绍一种基于ARM与DSP的机器视觉 硬件平台的设计与研究。

二、硬件平台调试

1、硬件调试

在硬件平台调试中,首先应该对硬件进行调试。这包括对处理器、存储器以 及其他外围电路进行调试。通常可以采用示波器、逻辑分析仪等工具来进行调试。

2、软件调试

在硬件调试完成后,应该对软件进行调试。在多DSP硬件平台中,软件调试 可以采用交叉调试的方法来实现。常用的调试工具有Code Composer Studio、 Visual Studio等。

参考内容

随着数字信号处理技术的发展,多数字信号处理器(DSP)硬件平台在各种 应用领域中得到了广泛的应用。这种技术可以实现高效的并行处理和计算能力, 从而提高处理复杂算法和大数据量的能力。本次演示将介绍基于多DSP的硬件平 台设计与调试。

一、硬件平台设计

1、处理器选择

在多DSP硬件平台中,处理器的选择至关重要。处理器应该具有高效的并行 处理能力,同时应该满足应用领域的计算需求。目前,常用的处理器包括 TMS320C674x系列、TMS320F系列等。

图像处理算法是机器视觉系统的核心部分。本设计在DSP处理器上实现了一 种基于卷积神经网络的图像分类算法。该算法能够对输入的图像进行分类,并输 出分类结果。同时,为了提高算法效率,我们在算法实现过程中采用了许多优化 策略,如数据量压缩、计算过程优化等。

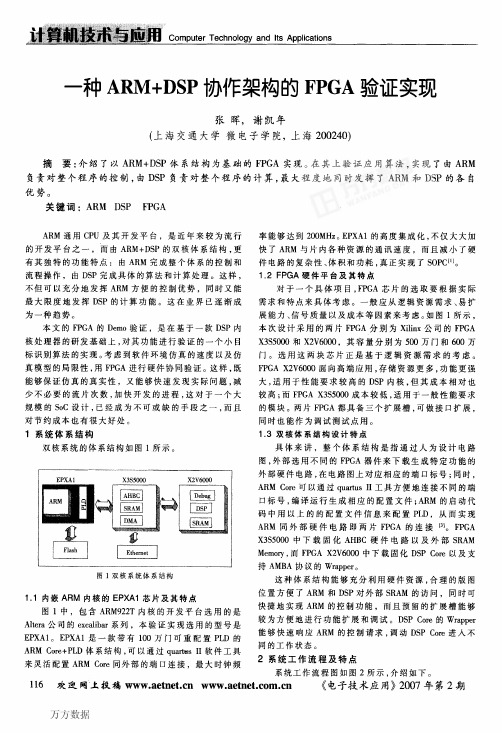

一种ARMDSP协作架构的FPGA验证实现

ARM Core可以通过quaItus II工具方便地连接不同的端

口标号,编译运行生成相应的配置文件;ARM的启动代

码中用以上的的配置文件信息来配置PLD,从而实现

ARM同外部硬件电路即两片FPGA的连接【3】。FPGA

X3S5000中下载固化AHBC硬件电路以及外部SRAM

Memory,而FPGA X2V6000中下载固化DSP Core以及支

门。选用这两块芯片正是基于逻辑资源需求的考虑。 FPGA X2V6000面向高端应用,存储资源更多,功能更强 大,适用于性能要求较高的DSP内核,但其成本相对也

少不必要的流片次数,加快开发的进程,这对于一个大

较高;而FPGA X3S5000成本较低,适用于一般性能要求

规模的SoC设计,已经成为不可或缺的手段之一,而且

件电路的复杂性、体积和功耗,真正实现了SOPC【11。 1.2 FPGA硬件平台及其特点

不但可以充分地发挥ARM方便的控制优势,同时又能

对于一个具体项目,FPGA芯片的选取要根据实际

最大限度地发挥DSP的计算功能。这在业界已逐渐成 需求和特点来具体考虑。一般应从逻辑资源需求、易扩

为一种趋势。

展能力、信号质量以及成本等因素来考虑。如图1所示,

《电子技术应用》2007年第2期

万方数据

复位 从Flash引导 配置PLDr和FpGA

≮:爹 卜面Y甚l 瓜

Debug Sub—Module实现对DSP Core的复位、启 动、暂停、断点设置、单步运行、读写内部SRAM、 读DSP Core寄存器等一系列功能,大大方便了 调试工作,同时也非常便捷地实现了ARM和 DSP的交互运行。

容量大的FPGA的成本同样也会比较高,所以在研 发需要和成本之间必须找到一个比较好的平衡点,这在 整个电路设计阶段就要预测得比较好,但这不太容易做 到,需要经验的积累。 3.2观测点的预留

ARM+DSP结构设计与实现

ARM+DSP结构设计与实现关键词:ARM处理器,嵌入式系统,DSP1 引言ARM(Advanced RISC Machine)是英国ARM公司设计开发的通用32位RISC微处理器体系结构,其主要优势在于简单的设计和高效的指令集。

ARM的设计目标是微型化、低功耗、高性能的微处理器实现[1]。

ARM 已经成为嵌入式系统主控制器的首选。

DSP(Digital Signal Processor)具有运算速度高、功耗低和智能化外设等特点,在数字信号处理方面显示了强大的实力。

由于ARM与DSP所具有的微型化、低功耗、高效性等共同特点和各自的独特优势,以ARM+DSP结构为核心的嵌入式系统在PDA、STB、DVD等消费类电子产品以及GPS、航空、勘探、测量等军方产品中得到了广泛的应用。

本文设计了基于ARM S3C2410与TMS320C5510 DSP的ARM+DSP结构的接口电路,并给出了其软件实现。

ARM+DSP结构以ARM为主控制器,DSP为协处理器,方案如图1所示。

ARM完成系统的流程调度、任务处理、中断处理以及提供显示、通信、远程控制等人机接口;DSP主要完成数字滤波、编码解码、数字调制解调等功能。

ARM与DSP利用了DSP提供的HPI口的进行通信,方便、灵活,接口电路设计简单。

ARM+DSP结构把ARM处理器和DSP处理器有机地结合起来,既能满足信号数据实时性要求,又便于系统的控制操作与升级,提高了系统的整体性能。

ARM+DSP结构具有很强的通用性,几乎不修改硬件和修改少量软件代码就可以轻松实现不同系统间的移植。

3 ARM S3C2410与TMS320C5510 DSP硬件接口设计TMS320C5510 DSP提供了一个16位宽的并行端口HPI(host port interface),通过HPI口,主机可以直接访问TMS320C5510 DSP的存储器,有关TMS320C5510 DSP的HPI口详细情况请参考资料[2][3]。

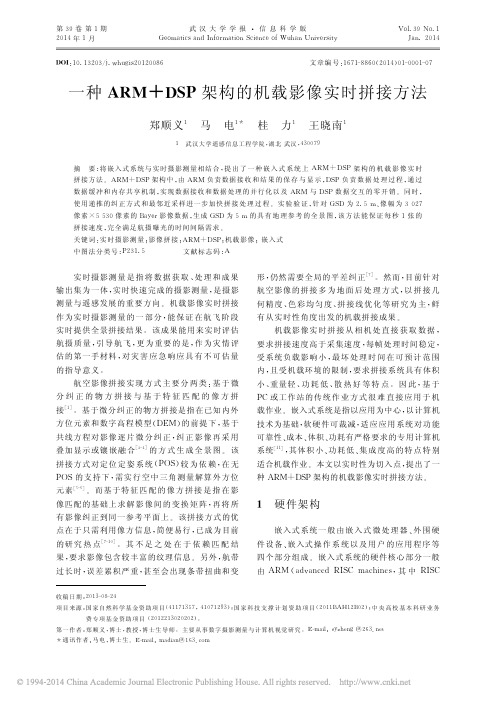

一种ARM_DSP架构的机载影像实时拼接方法

帧数据已经 到 来,会 导 致 数 据 丢 失。 为 解 决 传 输 耗时问题和应对 突 发 数 据,本 文 引 入 数 据 缓 冲 机 制 ,其 示 意 图 如 图 2 所 示 。

图 2 缓 冲 机 制 示 意 图 Fig.2 Diagram of Buffering

在数据接 收 和 数 据 处 理 之 间 建 立 内 存 缓 冲 区 ,当 缓 冲 区 处 于 “未 满 ”状 态 时 ,数 据 接 收 模 块 将 每帧数据按 照 A-B-C-A 的 顺 序 依 次 放 入 缓 冲 区 中 ;当 缓 冲 区 处 于 “未 空 ”状 态 时 ,数 据 处 理 模 块 按 照 A-B-C-A 的顺 序 依 次 从 缓 冲 区 中 取 出 影 像 数 据进行拼接 处 理。 时 序 意 义 上,数 据 被 先 接 收 再 处 理 依 次 顺 序 执 行 ,但 是 在 连 续 意 义 上 ,数 据 接 收 和数据处理并行执行。设每帧数据的传输时间为 Tt,处理时间为 Tp,平 均 每 帧 数 据 处 理 完 成 时 间 为 Ti。采用接收 -处理-接收的方 式,则 Ti=Tt+ Tp;而采用多 帧 缓 冲 的 方 式,则 有 Ti=max{Tt, Tp}。当 Tt<Tp 时,数 据 传 输 时 间 将 会 被 忽 略, 这为数据处 理 准 备 了 更 多 的 工 作 时 间。 此 外,采 用多帧缓冲,突发 数 据 将 会 被 置 入 缓 冲 区 而 不 会 丢 失 ,保 证 了 实 时 处 理 的 稳 定 性 。 1.2 内 存 共 享

图1 ARM+DSP 处理架构 Fig.1 Architecture of ARM+DSP

1.1 数 据 缓 冲 数据缓冲的目的是使数据接收和数据处理并

行化,同 时 缓 存 突 发 数 据,保 证 数 据 接 收 的 完 整 性。航空影 像 幅 面 大,则 单 帧 影 像 在 30 MB 以 上,假 设 接 收 速 率 为 250 MB/s,则 单 帧 影 像 传 输 耗 时 120 ms以 上 。 飞 机 航 摄 过 程 中 ,若 采 用 一 般 接收-处理-接收 的 方 式,数 据 接 收 则 相 对 占 据 大 量 时 间 ,制 约 了 数 据 处 理 的 实 时 性 。 另 外 ,在 航 摄 阶段,相邻航片的 拍 摄 时 间 间 隔 具 有 轻 微 的 不 确 定性,在 极 限 情 况 下,当 前 数 据 正 在 处 理,而 下 一

ARM实时在线仿真器的设计与实现

东南大学硕士学位论文ARM实时在线仿真器的设计与实现姓名:钱德俊申请学位级别:硕士专业:微电子与固体电子指导教师:胡晨20070416第二章嵌入式系统调试原理X86的INT3),而另一些机器没有类似的指令,就用任意一条不能被解释执行的非法(保留)指令代替。

目标操作系统添加的这些模块统称为‘锸桩”(见图2.1)。

驻留在ROM中的插桩称为ROMmonitor。

图2.1“插桩”示意图运行于目标平台的被调试程序(Debugge*)要在入口处调用设置断点的函数以产生异常,异常处理程序调用调试端口通信模块,等待主机(Host)上的调试器(Debugger)发送信息。

双方建立连接后调试器便等待用户发出调试命令,目标系统等待调试器根据用户命令生成的指令,如图2.2所示。

运行调试器◆旨定调试通信端口可目标系统发消息JL………日标操作系统初始化至应用系统入口●主动触发异常◆异常处理程序转入调试端口通信▲主机目标平台图2.2主机与目标平台调试示意图“插桩”能完成被调试程序的下载,目标机内存和寄存器的读写,设置断点,单步执行被调试程序等功能。

一些高级的“插桩”能完成代码分析(CodeProfiling),系统分析(SystemProfiling),ROM空间的写操作,以及设置各种非常复杂的断点等功能。

利用“插桩”方式作为调试手段时,开发应用程序的步骤如下:1、编写代码。

2、编译应用代码。

3、将代码下载到目标上的RAM空间。

4、用户使用调试器进行调试。

5、如果程序正常转到第8步。

6、发现程序有问题,在调试器的帮助下定位错误。

7、修改错误,重复2-7步。

8、将程序固化到目标机上。

这一方案的实质是用软件接管目标系统的全部异常处理(Exceptionhandler)及部分中断处理,在其中插入调试端口通信模块,与主机的调试器交互。

这种调试方式的最大好处就是:简单、方便。

还可以支持许多高级的调试功能,并且可扩展性强,成本低廉,基本上不需要专门的调试硬件支持。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

以ARM和DSP为核心的实时仿真平台的开发摘要:针对复杂的船舶推进系统仿真实时性的提高和精确度的需要,设计了以ARM+DSP嵌入式系统为核心的实时仿真平台,并分别详细论述了嵌入式仿真平台的硬件结构和技术特点,介绍了ARM,C5000和C2000核心软件结构以及芯片之间的内部通信,提供了具体实现高速运算和实时精确控制的新颖技术方案以及通用的仿真平台。

关键词:仿真;ARM+DSP;核心软件;内部通信引言一个大型的船舶轮机模拟器蕴含着30多个全物理摘要:针对复杂的船舶推进系统仿真实时性的提高和精确度的需要,设计了以ARM+DSP嵌入式系统为核心的实时仿真平台,并分别详细论述了嵌入式仿真平台的硬件结构和技术特点,介绍了ARM,C5000和C2000核心软件结构以及芯片之间的内部通信,提供了具体实现高速运算和实时精确控制的新颖技术方案以及通用的仿真平台。

关键词:仿真;ARM+DSP;核心软件;内部通信引言一个大型的船舶轮机模拟器蕴含着30多个全物理过程的数学模型,涉及千余个实时参变量,通常采用功能分散的DCS网络来实现。

即便如此,个别仿真工作站由于模型复杂、任务繁重,难以满足实时仿真的要求。

例如,动力推进系统的仿真是一个半实物在环的仿真系统,其中既有虚拟的动力装置即仿真计算机上运行的数学模型,又有真实的控制盘台、物理显示设备,是一种集实时控制和高速运算功能于一体的典型系统。

早期开发成功的SMSC2000型轮机模拟器采用工控机作为仿真计算机,所有数据的处理和输入输出的控制都经过它的数据采集卡来完成。

推进系统仿真的精确度与实时性无法两全。

近期航运仿真中心在开展多模式机舱仿真实验的同时,针对I/O点最多(200多个)、半实物环境最复杂的船舶推进系统进行了剖析,研制了嵌入式微机的新颖仿真平台。

船舶推进系统仿真平台的选取船舶推进系统仿真平台需要有很强的控制接口(输入输出)能力和高速的数字运算处理能力。

TI公司的DSPC2000系列率先为电机的实时控制开拓了应用领域,但并不适合于具有众多I/O的复杂机电模型的仿真。

由于市场上无现成的仿真装置可购,只能针对机舱模拟器的对象自行探索。

实际上,当代嵌入式芯片既提供了高速的数字信号处理器(DSP),也提供了有强大控制功能的微控制器(MCU)。

采用MCU+DSP架构,就可兼备两者的长处。

基于ARM核的32位RISC微控制器在监视控制、人机接口方面的功能非常完善,数字信号处理器(DSP)对各种数字信号或数据处理的能力十分强大。

因此,许多嵌入式实时应用系统采用ARM+DSP的结构组合来充分发挥两种处理器的优势,从每个处理器中获得最大益处,以获得更高性能。

其中,ARM作为主处理器,负责任务管理、输入输出接口、对外部设备的控制,甚至运行嵌入式操作系统;而DSP作为从处理器,仅仅负责快速的数据运算处理。

两个处理器核之间通过共用一部分存储器等方式进行通信。

以ARM+DSP为核心的嵌入式系统具有很强的控制接口能力和高速数字处理能力,用来代替以工控机为核心的仿真系统,可以达到实时运行精确的船舶推进系统的数学模型、实时控制外围物理设备的目的,从而实现精确实时的半物理实物在环的船舶推进仿真系统。

ARM+DSP嵌入式船舶推进系统仿真平台的硬件结构ARM+DSP嵌入式仿真平台主要由以ARM,C5000DSP,C2000DSP3个处理器为中心的功能部分构成。

其中ARM部分的ARM核微控制器是主处理器,是整个系统的控制中心。

ARM部分带有自己的FLASH,RAM,A/D,D/A转换器等外围设备,主要负责上电后完成整个系统的自举加载和系统的任务分配、从物理设备输入和向物理设备输出信号、通过CAN总线与上位计算机通信等。

C5000DSP部分主要运行船舶推进系统的数学模型,并将仿真所得的转速和转矩的数据传递给C2000DSP部分的电机控制单元,以在电动机上表达出推进系统的实时状态,即用电动机来模拟推进主机。

C2000DSP部分的功能是接收C5000DSP部分数学模型的运算结果,按照该结果控制电动机达到仿真的转速和转矩,最终实现用电动机来模拟推进主机。

这3个部分按一定的方式组合在一起,构成一个整体,共同完成推进系统仿真的任务。

其基本组织结构如图1所示。

图1 ARM+DSP嵌入式微机系统的基本组成[next]实际上,从可靠性角度考虑,对于ARM部分和C5000DSP部分,采用一块ARM7+C54x的双核芯片(TI的TMS320VC5470)把两部分的核心集成到一起。

这两部分的主要外围设备有ARM侧的FLASH,SRAM,SDRAM,键盘,LCD,CAN总线接口,A/D,D/A转换器(用于模拟量的输入输出),光耦电路(用于数字量或开关量的输入输出),用于编程调试用的JTAG接口及DSP侧的程序空间外扩SRAM,数据空间外扩SRAM,及I/O空间的FIFO(用于向C2000DSP部分传递数据)。

这两部分的硬件组织结构如图2所示。

图2 ARM和C5000DSP的硬件结构C2000DSP部分为任选部分。

若省略这部分,则仿真结果仅显示在LCD,LED状态指示灯上。

加上这部分后,仿真推进系统的各种动静态转速及转矩特性可在C2000DSP部分控制的仿真电机上反映出来,达到用电机模拟推进系统主机的目的。

图3所示的C2000DSP子系统实际上是一个电机的闭环控制系统,由DSP控制器、功率驱动放大电路、电机和转速检测环节(光电编码盘)4个子部分构成。

可见,ARM+DSP嵌入式船舶推进系统仿真平台的硬件资源丰富,且有很大的可扩展空间。

该系统平台在硬件方面有以下一些特点。

(1)从处理器的速度上看,ARM最大为47.5MHz,C5000DSP最大为100MHz,C2000DSP最大为40MHz,属于较高速处理器。

图3 C2000DSP部分的硬件结构[next](2)FLASH的容量很大。

在ARM和C5000DSP(即TMS320VC5470)部分有8MB 的外部FLASH;在C2000DSP(TMS320LF2407)部分有32KW的在片FLASH,而且还可以进行外扩。

这样,该系统就可以固化大量的程序代码,适合开发大型的程序。

(3)SRAM的容量也很大。

在ARM部分有16KB的在片高速SRAM和2MB的外部SRAM;在C5000DSP部分有72KW高速在片SRAM和64KW外扩程序SRAM和64KW 外扩数据SRAM;在C2000DSP(TMS320LF2407)部分有2.5KW的在片SRAM,而且还有64KW外扩程序SRAM和64KW外扩数据SRAM。

这样,大量的SRAM可以保证处理器在SRAM中读取程序,以保证程序快速运行。

(4)系统的I/O端口资源丰富。

既有数字量的输入输出,也有模拟量的输入输出;既提供了串行方式,也提供了并行方式。

为数据采集、控制指令输出、与上位机通信等奠定了硬件基础。

(5)C2000DSP的处理器TMS320LF2407是专用来进行电机控制的芯片,用来产生PWM信号和捕获转速反馈信号很容易,而且运算速度快,可以实现对电机的各种高效复杂的控制。

(6)各部分间需要实时交换数据,其硬件上都采用了共享存储器的方式(ARM与C5000DSP之间的ARMPortInterface,简称API,C5000DSP与C2000DSP之间的FIFO)。

这样,通信速度很快,从硬件上满足了实时要求。

(7)因为器件数量较多且速度相对较高,有些芯片采用的是先进的BGA(BallGridArray)封装技术,所以在设计印刷电路板时,采用了6层板,布线充分考虑了器件的高速性和封装技术。

(8)该系统平台提供了很多可扩展的接口,用户可针对具体对象扩充硬件、添加新的功能。

对于构成SMSC2000轮机模拟器的其他工作站,无须扩展任何I/O接口,可见该系统具有通用性。

ARM+DSP嵌入式仿真平台的软件结构ARM部分中的软件ARM部分是整个系统的控制中心,其运行的主要是系统软件,包括自举加载程序、指令响应程序、键盘扫描程序、LCD显示驱动程序、A/D与D/A转换控制程序、直接数字量/开关量输入输出程序、CAN总线通信控制程序及与C5000DSP 部分进行内部实时数据交换的控制程序。

自举加载程序是上电或复位后首要实现的任务。

它先对ARM的一些关键寄存器(如时钟、中断等)进行初始化(即部分初始化);之后将ARM部分中要运行的主程序和各个子程序(如指令响应程序、键盘扫描、LCD显示驱动等)从片外的非易失性存储器FLASH中加载到片内或片外的SRAM中,以增加程序的运行速度;接着,开始负责对C5000DSP部分进行复位初始化,再把数学模型程序通过API控制加载到C5000DSP中。

这样,自举加载程序就完成了两个部分的自举加载工作。

自举加载完成后,ARM部分开始执行系统的全部初始化,然后便进入系统的主程序(该主程序是一个无限循环等待程序),在主程序中再以中断方式反复运行键盘扫描、LCD显示驱动、指令解释响应、A/D与D/A转换控制、数字量/开关量的输入输出及与C5000DSP部分通讯的程序。

其中,指令解释的响应程序是一个核心程序,类似于操作系统的内核程序,接受来自输入处理子程序(键盘扫描、数字量/开关量的输入等)的接口数据,并根据它们的值启动相应的任务,如果需要将任务执行的结果作为接口数据(指令)输出给显示或控制处理子程序,则经由各输出子程序再进行处理。

该部分的软件组织结构如图4所示。

[next]图4 ARM部分的软件组织结构C5000DSP部分的软件C5000DSP部分主要用来运行推进系统的数学模型,该推进系统可以是传统的柴油主机推动系统,也可以是新型的电力推动系统,关键在于不同的推动类型对应不同的数学模型。

C5000DSP程序实质上是以实时循环迭代求解微分方程组为主的程序,该微分方程组即推进系统的数学模型,并且每循环求解一次,要确定有没有从ARM部分传递来的指令及参数更改的信息。

如果有,就改变相应状态及参数再求解微分方程组;如果没有,则仍按上一次的状态和参数求解。

在每个循环中,方程组完整求解一次,从而得到推动系统在该时刻的仿真数据。

在每个循环的最后,把仿真数据结果传送给ARM部分及C2000DSP部分(通过FIFO),用于显示和控制。

这部分的软件程序结构如图5所示。

图5 C5000DSP部分的软件组织结构[next]C2000DSP部分的软件结构C2000DSP部分的主要任务就是读取FIFO接收来自C5000DSP部分的仿真结果中的转速和转矩信号,并将之表达为电动机的相应转速和转矩。

该部分实际上是独立构成的一个专门控制交流电机的子系统。

其中,C2000DSP处理器TMS320LF2407为该控制子系统的核心。