IC原理习题

差动保护练习题

差动保护练习题差动保护是电力系统中常用的一种保护方式,用于检测电力系统中的相间故障,如电气短路、接地故障等。

差动保护装置通过对比电流差值来判断是否存在故障,并及时采取保护动作来防止故障扩大。

下面是一些差动保护练习题,帮助大家更好地理解和掌握差动保护的原理和应用。

练习题一:电力系统中有一台变压器,变压器二次侧有两个开关 K1 和 K2 分别连接两个线路。

变压器二次侧总电流为 Ic,分闸开关 K1 和 K2 后,线路 1 和线路 2 的电流分别为 I1 和 I2。

若差动保护装置的设置值为 I Δ =0.05*Ic,求差动保护装置的动作条件及动作方程。

解答:差动保护的动作条件是ΔI = I1 - I2 ≠ 0。

所以当线路 1 或线路 2 发生故障时,差动保护将会动作。

动作方程为ΔI = I1 - I2 - I Δ = 0。

练习题二:电力系统中有一台发电机,发电机的定子绕组和励磁绕组由两个开关K1和K2连接。

发电机定子绕组电流为Ic,分闸开关K1和K2后,定子绕组和励磁绕组的电流分别为I1和I2。

若差动保护的设置值为IΔ=0.1*Ic,求差动保护装置的动作条件及动作方程。

解答:差动保护的动作条件是ΔI=I1-I2≠0。

因此,当发电机定子绕组或励磁绕组发生故障时,差动保护将会动作。

动作方程为ΔI=I1-I2-IΔ=0。

练习题三:电力系统中有一台变压器,变压器的一次侧和二次侧都有差动保护装置。

当变压器二次侧发生短路故障时,差动保护装置将会动作。

现在已知变压器的一次侧电流为Ip,二次侧电流为Is,差动保护装置的设置值为IΔ=0.05*Is,求动作条件及动作方程。

解答:差动保护的动作条件是ΔI = Ip - Is ≠ 0。

所以当变压器二次侧发生故障时,差动保护将会动作。

动作方程为ΔI=Ip-Is-IΔ=0。

练习题四:电力系统中有两台变压器,变压器一次侧和变压器二次侧都有差动保护装置。

当变压器一次侧或二次侧发生短路故障时,差动保护装置将会动作。

微机组成原理练习题有答案

《微机组成原理》练习题第一章计算机系统概论5、动态RAM存储信息的原理是电容存储电荷,因此一般在2ms时间内必须刷新依次,刷新是按行进行的。

6、主存可以和CPU、CACHE、辅存交换信息。

7、 I/O编辑方式可以分为统一编址、分开编址两大类,前者需有独立的I/O指令后者可通过访存指令和设备交换信息。

8、条件转移、无条件转移、子程序调用、中断返回指令都属于跳转类指令,这类指令字的地址码字段指出的地址不是操作数的地址,而是下一条指令的地址9、动态RAM的刷新一般有集中刷新、分散刷新、异步刷新三种方式,之所以刷新是因为存储电容的电荷会放电。

1、总线管理包括哪些内容?简要说明几种查询方式。

链式查询方式只需很少的几根线就能按一定的优先顺序实现总线的优先控制,并且很容易扩充设备,但对电路故障敏感。

且优先级低的设备可能很难获得请求。

计数器查询方式的总线请求(BR)和忙线(BS)线是各设备共用的,单还需log2N(N为设备数)根设备地址线实现查询,设备的优先级可以不固定控制此链式查询复杂,电路故障不如链式查询方式敏感。

独立请求方式响应速度快,优先次序灵活,但控制线数量多,总线控制更复杂。

2、比较静态RAM和动态RAMa.在同样大小的芯片中,动态RAM的集成度远高于静态RAMb.动态RAM行列地址按显瘦顺序输送,减少了芯片引脚,封装尺寸也减少c.动态RAM的功耗比静态RAM小d.动态RAM的价格比静态RAM便宜3、在什么条件和什么时间,CPU可以响应I/O的中断请求?条件和时间是:当中断允许状态为1,且至少有一个中断请求被查到,则在一条指令执行完成时,响应中断。

4、存储器-寄存器三类指令中哪类指令的执行时间长/短?为什么?存储器-存储器型的指令执行时间最长,寄存器-寄存器型的指令执行时间最短;寄存器一般是集成在CPU的内部,而存储器是在CPU的外部,寄存器的存取时间短,而存储器的存取时间长,所以。

5、根据CPU访存性质的不同,可将CPU的工作周期分为哪几类?分为取址周期,间址周期,执行周期和中断周期一、选择题1、冯.诺依曼机工作方式的基本特点是( B )A.多指令流单数据流B.按地址访问并顺序执行指令C.堆栈操作D.存储器按内容选择地址2、电子计算机的算术/逻辑单元、控制单元及主存储器合称为(C )A、CPUB、ALUC、主机D、CU3、完整的计算机系统应包括(D )A、运算器、存储器、控制器B、外部设备和主机C、主机和实用程序D、配套的硬件设备和软件系统4、计算机系统中的存储系统是指(D )A、RAM存储器B、ROM存储器C、主存D、主存和辅存5、用以指定待执行指令所在地址的是( C )A、指令寄存器B、数据计数器C、程序计数器D、累加器6、微型计算机的发展以( B )技术为标志。

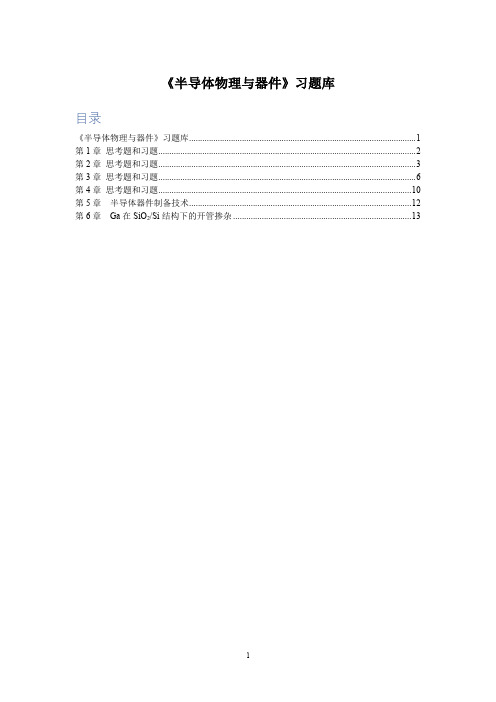

《半导体物理与器件》习题库

《半导体物理与器件》习题库目录《半导体物理与器件》习题库 (1)第1章思考题和习题 (2)第2章思考题和习题 (3)第3章思考题和习题 (6)第4章思考题和习题 (10)第5章半导体器件制备技术 (12)第6章Ga在SiO2/Si结构下的开管掺杂 (13)第1章思考题和习题1. 300K时硅的晶格常数a=5.43Å,求每个晶胞内所含的完整原子数和原子密度为多少?2. 综述半导体材料的基本特性及Si、GaAs的晶格结构和特征。

3. 画出绝缘体、半导体、导体的简化能带图,并对它们的导电性能作出定性解释。

4. 以硅为例,简述半导体能带的形成过程。

5. 证明本征半导体的本征费米能级E i位于禁带中央。

6. 简述迁移率、扩散长度的物理意义。

7. 室温下硅的有效态密度Nc=2.8×1019cm-3,κT=0.026eV,禁带宽度Eg=1.12eV,如果忽略禁带宽度随温度的变化,求:(a)计算77K、300K、473K 3个温度下的本征载流子浓度。

(b) 300K本征硅电子和空穴的迁移率分别为1450cm2/V·s和500cm2/V·s,计算本征硅的电阻率是多少?8. 某硅棒掺有浓度分别为1016/cm3和1018/cm3的磷,求室温下的载流子浓度及费米能级E FN的位置(分别从导带底和本征费米能级算起)。

9. 某硅棒掺有浓度分别为1015/cm3和1017/cm3的硼,求室温下的载流子浓度及费米能级E FP的位置(分别从价带顶和本征费米能级算起)。

10. 求室温下掺磷为1017/cm3的N+型硅的电阻率与电导率。

11. 掺有浓度为3×1016cm-3的硼原子的硅,室温下计算:(a)光注入△n=△p=3×1012cm-3的非平衡载流子,是否为小注入?为什么?(b)附加光电导率△σ为多少?(c)画出光注入下的准费米能级E’FN和E’FP(E i为参考)的位置示意图。

电路原理习题集(上册)

1-1 求题1-1图各分图中的待求电压、电流值(设电流表内阻为零)。

题1-1 图1-2 解答题1-2图中的各个分题(设电流表内阻为零)。

1-3 试求题1-3图所示部分电路中的电压U gf、U ag、U d b 和电流I cd。

1-4 根据基尔霍夫定律求出各元件的未知电流或电压,并计算各元件吸收的功率。

题1-2 图题1-3 图(a) (b)题1-4 图1-5 写出题1-5图所示各电路的U = f(I)和I = f(U)两种形式的端口特性方程。

1-6 试求题1-6图所示电路中的电压U ac和U ad。

1-7 试求题1-7图所示电路中的节点电位V1、V2和V3(图中接地点为零电位点)。

(a) (b) (c)题1-5 图1-8 在题1-8图所示电路中,电阻R1、R2、R3和R4的电压、电流额定值是6.3V、0.3A,R5的电压、电流额定值是6.3V、0.45A。

为使上述各电阻元件均处于其额定工作状态,问应当选配多大的电阻R x和R y?题1-6 图题1-7 图题1-8 图1-9 题1-9图所示电路是从某一电路中抽出的受控支路,试根据已知条件求出控制变量。

1-10 求题1-10图各分图所示电路中的电流I和电压U。

(a)(b)(a) (b) (c) (d)题1-9 图(c) (d)题1-10 图1-11 求题1-11图所示电路中的电压U和U1之值。

1-12 已知电路如题1-12图所示,求:(a) 电流I x、I y和电压U I;(b) 将电流控电流源的控制电流I x改为I y、再求I x、I y和U I。

(a) (b)题1-11 图题1-12 图1-13 在题1-13图所示电路中,若U i1=U i2=U i3=1 mV, A1=A2=4000, 求输出电压U01、U02。

1-14 设题1-14图中所示运算放大器是一个理想模型,试求输出电压U0 = -(U i1 + 2U i2 + 3U i3) 时,电路中电阻R1、R2、R3之间的关系。

[资料]信息传输原理习题部分参考答案

![[资料]信息传输原理习题部分参考答案](https://img.taocdn.com/s3/m/827c65d7a0c7aa00b52acfc789eb172ded63994d.png)

第一章 习题题(1.1)英文字母中e 的出现概率为0.105,c 的出现概率为0.023,o 的出现概率为0.001,试分别计算它们的自信息量(以比特为单位)。

解:由题意可得Ie= -log0.105=3.25bitIo= -log0.001=9.97bitIc= -log0.023=5.44bit∴字母e 的自信息量是3.25bit ,字母c 的自信息量是5.44bit ,字母o 的自信息量是9.97bit 。

题(1.2)某个消息由字符A,B,C,D 组成,已知它们的出现概率为83)(=A P ,41)(=B P ,41)(=C P ,81)(=D P ,试求由60个字符所构成的消息,其平均自信息量是多少比特。

解:由题意可得H (x )= -(38log 38+14*2*log 14+18log 18)=1.906bit∴由60个字符构成的消息的平均自信息量是1.906*60=114.36bit题(1.3)在二进制信道中信源消息集为}1,0{=X ,且已知出现概率)1()0(P P =。

信宿消息集为}1,0{=Y ,信道传输概率为41)0|1(=P 和81)1|0(=P 。

试求该信道所能提供的平均互信息量),(Y X I 等于多少?解: ∵ P Y/X =13,4471,88⎡⎤⎢⎥⎢⎥⎢⎥⎢⎥⎣⎦,P X =11,22⎡⎤⎢⎥⎣⎦∴P Y = P X *P Y/X =11,22⎡⎤⎢⎥⎣⎦*13,4471,88⎡⎤⎢⎥⎢⎥⎢⎥⎢⎥⎣⎦=97,1616⎡⎤⎢⎥⎣⎦∴H (Y )=-(916log 916+716log 716)=0.989bitH (Y/X )=12H (14,34)+12H (78,18)=0.678bit∴I (X ,Y )=H (Y )-H (Y/X )=0.989-0.678=0.311bit题(1.4)在二进制对称信道中传输消息}1,0{=X ,接收到的消息为}1,0{=Y 。

电路原理练习题第一部分填空题对于理想电压源而言,不允许路,但

电路原理练习题第一部分填空题1.对于理想电压源而言,不允许路,但允许路。

2.当取关联参考方向时,理想电容元件的电压与电流的一般关系式为。

3.当取非关联参考方向时,理想电感元件的电压与电流的相量关系式为。

4.一般情况下,电感的不能跃变,电容的不能跃变。

5.两种实际电源模型等效变换是指对外部等效,对内部并无等效可言。

当端子开路时,两电路对外部均不发出功率,但此时电压源发出的功率为,电流源发出的功率为;当端子短路时,电压源发出的功率为,电流源发出的功率为。

6.对于具有n个结点b个支路的电路,可列出个独立的KCL方程,可列出个独立的KVL方程。

7.KCL定律是对电路中各支路之间施加的线性约束关系。

8.理想电流源在某一时刻可以给电路提供恒定不变的电流,电流的大小与端电压无关,端电压由来决定。

9.两个电路的等效是指对外部而言,即保证端口的关系相同。

10.RLC串联谐振电路的谐振频率 = 。

11.理想电压源和理想电流源串联,其等效电路为。

理想电流源和电阻串联,其等效电路为。

12.在一阶RC电路中,若C不变,R越大,则换路后过渡过程越。

13.RLC串联谐振电路的谐振条件是 =0。

14.在使用叠加定理适应注意:叠加定理仅适用于电路;在各分电路中,要把不作用的电源置零。

不作用的电压源用代替,不作用的电流源用代替。

不能单独作用;原电路中的不能使用叠加定理来计算。

15.诺顿定理指出:一个含有独立源、受控源和电阻的一端口,对外电路来说,可以用一个电流源和一个电导的并联组合进行等效变换,电流源的电流等于一端口的 电流,电导等于该一端口全部 置零后的输入电导。

16. 对于二阶电路的零输入相应,当R=2C L /时,电路为欠阻尼电路,放电过程为 放电。

17. 二阶RLC 串联电路,当R 2CL时,电路为振荡放电;当R = 时,电路发生等幅振荡。

18. 电感的电压相量 于电流相量π/2,电容的电压相量 于电流相量π/2。

19. 若电路的导纳Y=G+jB ,则阻抗Z=R+jX 中的电阻分量R= ,电抗分量X= (用G 和B 表示)。

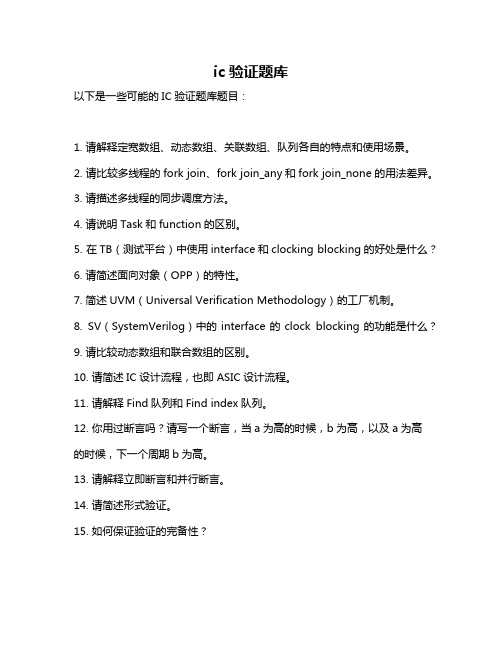

ic验证题库

ic验证题库

以下是一些可能的IC验证题库题目:

1. 请解释定宽数组、动态数组、关联数组、队列各自的特点和使用场景。

2. 请比较多线程的fork join、fork join_any和fork join_none的用法差异。

3. 请描述多线程的同步调度方法。

4. 请说明Task和function的区别。

5. 在TB(测试平台)中使用interface和clocking blocking的好处是什么?

6. 请简述面向对象(OPP)的特性。

7. 简述UVM(Universal Verification Methodology)的工厂机制。

8. SV(SystemVerilog)中的interface的clock blocking的功能是什么?

9. 请比较动态数组和联合数组的区别。

10. 请简述IC设计流程,也即ASIC设计流程。

11. 请解释Find队列和Find index队列。

12. 你用过断言吗?请写一个断言,当a为高的时候,b为高,以及a为高

的时候,下一个周期b为高。

13. 请解释立即断言和并行断言。

14. 请简述形式验证。

15. 如何保证验证的完备性?

以上题目主要涉及到了SystemVerilog数据类型、Verilog时序电路、SV 线程通信、覆盖率等方面的知识,仅供参考,建议查阅专业书籍或咨询专业人士获取更准确的信息。

晶体管原理 (部分习题讲解)

x W 2 9 3 2 VB ' =VB 1 dB =144 1 = 80V xdB 9

34、 、

已知 对于 单边突 变结 , εsqN0 K CT = A = 1 2(Vbi V ) (Vbi V ) 2 K 当 Vbi = 0.6V, V = 3V时 CT = , =10 pF, 由此 可得 3.6 K =10 3.6, 因此 V = 0.2V时 当 , 10 3.6 CT = =10 9 = 30 (pF) 0.4

20、 、

已 : 知 由 于

σp qp NA p NA = = >>1 σn qn ND n ND

qDpni2 qV Jdp = exp kT 1 Lp ND qDnni2 Jdn = Ln NA qV exp kT 1 Ln Dp NA Ln p NA = = >>1 Lp Dn ND Lp n ND

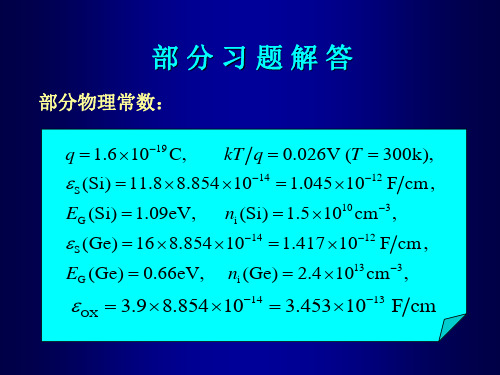

部分习题解答

部分物理常数: 部分物理常数:

q = 1.6 × 10 19 C, E G (Si) = 1.09eV, E G (Ge) = 0.66eV, kT q = 0.026V (T = 300k), ni (Si) = 1.5 × 1010 cm 3 , ni (Ge) = 2.4 × 1013 cm 3 ,

1

1

9、

qDBni2 qVBE IC = A JnC = A β JnE = A β exp E E E W NB kT B W2 1 W B 式 , =1 B =1 中 β = 0.9986 2 LB 2DBτB 将 A =104 m2 , = 0.9986, q =1.6×1019 C, β E DB =18cm2 s1, ni =1.5×1010 cm3, W = 0.7×104 cm, B NB =10 cm , VBE = 0.7V,

计算机体系结构习题答案

一、(5分)计算机系统设计中经常使用的4个定量原理是什么?请简要说明它们的含义。

答:(1)以经常性事件为重点。

在计算机系统的设计中,对经常发生的情况,赋予它优先的处理权和资源使用权,以得到更多的总体上的改进。

(2)Amdahl 定律。

加快某部件执行速度所获得的系统性能加速比,受限于该部件在系统中所占的重要性。

(3)CPU 性能公式。

执行一个程序所需的CPU 时间 = IC ×CPI ×T 。

(4)程序的局部性原理。

程序在执行时所访问地址的分布不是随机的,而是相对地簇聚。

二、(15分)假设某应用程序中有4类操作,通过改进各类操作的功能部件,可(2)各类操作单独改进后,程序获得的加速比分别是多少? (3)4类操作均改进后,整个程序的加速比是多少? 答:根据Amdahl 定律aff S n +-=)1(1,其中f 是可改进部分在总运行时间中所占比例,a 是可改进部分的加速比,可得4类操作均改进后,整个程序的加速比:11.77(1)n ii iS FF S =≈-+∑∑三、(5分)请简述指令之间数据冲突的类型。

答:指令之间的数据冲突有3种类型:真相关、反相关、输出相关。

真相关(数据依赖,有时候也称为数据相关):考虑两条指令i 和j ,i 在j 的前面,指令k 在指令i 和指令j 之间。

如果下述条件之一成立,则称指令j 与指令i 真相关:(1)指令j 使用指令i 产生的结果(写后读);(2)指令j 与指令k 真相关,而指令k 又与指令i 真相关。

(真相关的传递性) 反相关:考虑两条指令i 和j ,i 在j 的前面,如果指令j 所写的名与指令i 所读的寄存器名或存储地址相同,则称指令i 和j 发生了反相关。

(读后写)输出相关:考虑两条指令i 和j ,i 在j 的前面,如果指令j 和指令i 所写的寄存器名或存储地址相同,则称指令i 和j 发生了输出相关。

(写后写) 其中反相关和输出相关又合称名相关。

电路原理各章习题

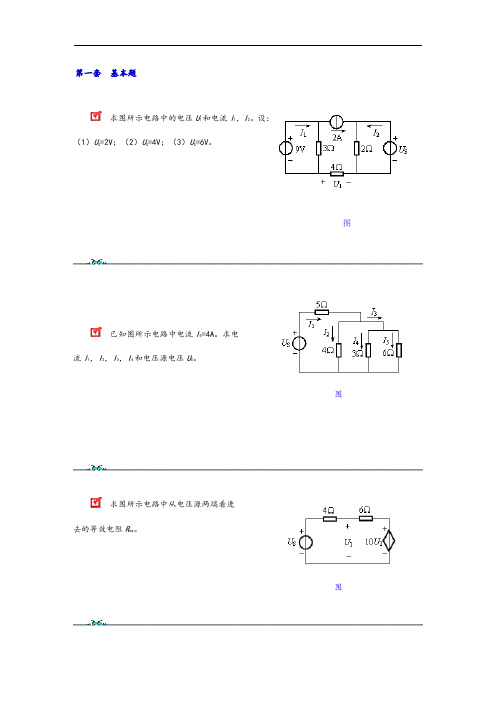

第一套基本题求图所示电路中的电压U1和电流I1,I2。

设:(1)U S=2V;(2)U S=4V;(3)U S=6V。

图已知图所示电路中电流I5=4A。

求电流I1,I2,I3,I4和电压源电压U S。

图求图所示电路中从电压源两端看进去的等效电阻R eq。

图求图所示电路中各元件的功率,并校验功率守恒。

图第二套提高题已知图所示电路中电压U=3V。

求由电源端看进去的电阻R eq和电阻R1的值。

图图所示电路中,已知3A电流源两端电压为40V。

求负载吸收的功率。

图已知图所示电路中,R1=40W,R e=27W,R b=150W ,R L=1500W,=。

求电压增益u2/u1和功率增益p2/p1。

其中p1是u1供出的功率,p2是R L吸收的功率。

图第一套基本题求图所示各电路的入端电阻R AB、R ab。

图图试将图所示电路化成最简单形式。

图图所示电路中,设输入电压为U i,试求U o/ U i。

图第二套提高题求图所示各电路的入端电阻R AB,R ab。

图中各电阻值均为1。

图答案:求图所示电路中的电压U L。

设I S,R,R L为已知。

图求图所示电路中的电流i。

图图所示电路由许多单元构成,每个单元包含R1和图R2两个电阻。

设单元数极多,视作无穷大。

(1)设R1=2,R2=1。

求A,B处的入端电阻。

(2)以B点为电位参考点,若每个节点电压是前一个节点电压的一半,问此时R1/R2是多少第一套基本题在图所示电路中,试用支路电流法求图示电路的各支路电流。

图流源两端电压U S。

图试用节点法求图所示电路中的电流I和电流源两端电压U。

图求图所示电路中各独立源发出的功率。

图第二套提高题试用回路电流法求图所示电路中电压U。

图试用回路电流法求图所示电路中1A电流源发出的功率。

图用节点电压法求图所示电路中电压表的读数。

图求图所示电路中各节点的电压U 1,U2,U3和U4。

图第一套基本题用叠加定理计算图所示电路中的电流I。

图求图所示电路的戴维南等效电路和诺顿等效电路。

通信电路原理习题课1-4章

波在负载上产生压降,因此对于二次谐波 L1

L2

要求 L2与C构成串联谐振,而对于基频L1 、

L2与C则构成并联谐振,在负载上能构产 生压降,因此:

R1

C R2

1 2

L2C

L1

1

C

L2

计算结果:

L1 =375μH, L2 =125μH

第1-4章

【习题】

2.有一并联回路在某频段内工作,频段最低频率为535kHz,最高 频率为1605kHz。现有两个可变电容器,一个电容器的最小电容 量是12pF,最大电容量是100pF;另一个电容器的最小电容量是 15pF,最大电容量是450pF。试问:

1.15 p 1 3.45 q p

q p

则可以得下列组合,满足条件:

p=1

p=2

p=2

q=2 ,

q=3 ,

代入 fs=

p 1 q p

fi

q=4

得在697. 5、930、1395kHz频率附近会 产生组合干扰哨声

第1-4章

fk pf0 qfs

fk pf0 qfs fi fi f0 fs

3、并联谐振回路如图示,已知:fp=10MHz,Qp=100,Rs=12.8KΩ, R大L功=1率K的Ω条,C件=4为0pFpR,2接L2 入R1系p 数Rp1S2p1,= 试NN12求33=接0.8入,系p数2=p2NN和1435,负回载路R通L频获带得B最W0.7

14

Is

Rs

C

Rp

2 L1

L2

pf0 qfs fi

pf0 qfs fi pf0 qfs fi pf0 qfs fi

p 1 fs q p fi

《电路原理》作业以及答案

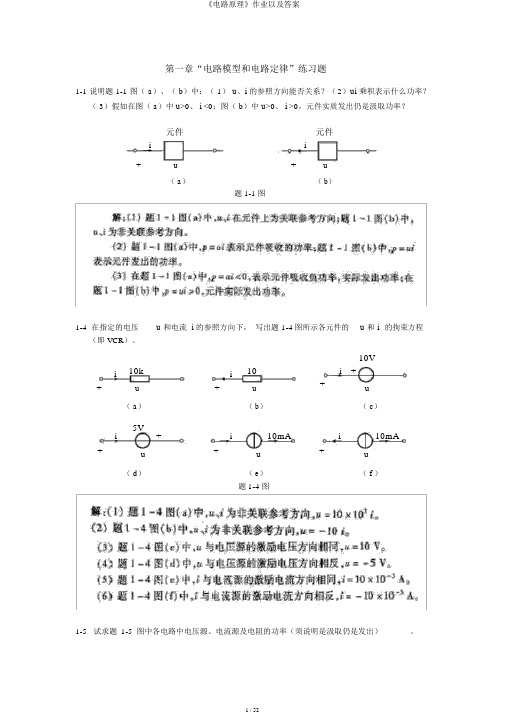

第一章“电路模型和电路定律”练习题1-1 说明题 1-1 图( a)、( b)中:( 1)u、i的参照方向能否关系?(2)ui乘积表示什么功率?( 3)假如在图( a)中u>0、i <0;图( b)中u>0、i >0,元件实质发出仍是汲取功率?元件元件i i+u+u( a)( b)题1-1图1-4 在指定的电压u 和电流 i 的参照方向下,写出题1-4图所示各元件的u 和 i的拘束方程(即 VCR)。

10k10i 10Vi i+++u+u u ( a)( b)( c)i 5V+i10mA i10mA+u+u+u( d)( e)( f )题1-4图1-5试求题1-5图中各电路中电压源、电流源及电阻的功率(须说明是汲取仍是发出)。

52A++15V515V 2A( a)(b)题1-5图1-16电路如题1-16 图所示,试求每个元件发出或汲取的功率。

2I12+++U2U2V(a)题 1-16 图+515V2A( c)A2I11I 2(b)1-20试求题1-20图所示电路中控制量u1及电压 u。

1k10k++++u1u10u12V题 1-20 图第二章“电阻电路的等效变换”练习题2-1电路如题2-1和电流 i 2、 i图所示,已知3:(1)R3=8ku S=100V,R1=2k,R2=8k。

试求以下 3 种状况下的电压;( 2)R3=(R3处开路);(3)R3=0(R3处短路)。

u2R1i2+i3+R2u2R3 u S题2-1 图2-5 用△— Y 等效变换法求题2-5 图中 a、b 端的等效电阻:(1)将结点①、②、③之间的三个 9 电阻组成的△形变换为 Y 形;(2)将结点①、③、④与作为内部公共结点的②之间的三个 9 电阻组成的 Y 形变换为△形。

①a999②③99b④题 2-52-11利用电源的等效变换,求题2-11 图所示电路的电流i 。

1A4424i+++1010 10V4V6V题 2-11 图2-13 题 2-13图所示电路中R1 R3 R4, R22R1,CCVS的电压u c4R1i1,利用电源的等效变换求电压u10。

集成电路原理答案

集成电路原理答案1. CMOS工艺是目前集成电路制造中使用广泛的一种工艺。

CMOS是互补型金属氧化物半导体的缩写,它由P型和N型晶体管组成。

P型晶体管通过控制基极电压进行工作,而N型晶体管则通过控制栅极电压进行工作。

CMOS工艺具有低功耗、高浮点性能和抗干扰等优点。

2. 集成电路的制造过程通常包括晶片制备、晶圆切割、芯片封装和测试等环节。

晶片制备是指将半导体材料(通常是硅)加工成具有特定功能的晶片。

晶圆切割是将大片的晶圆切割成一颗颗独立的芯片。

芯片封装是将芯片封装在塑料或陶瓷封装体中,以便安装在电路板上。

测试是对芯片进行功能和质量的检测,确保芯片能正常工作。

3. 集成电路的原理是基于电子器件的原理。

常见的电子器件包括二极管、三极管和晶体管等。

二极管是一种具有两个电极的电子器件,它能够只允许电流在一个方向上通过。

三极管是一种具有三个电极的电子器件,由两个PN结构组成。

晶体管是一种能够控制电流的电子器件,它通过调节输入电压来改变输出电流的大小。

4. 集成电路的设计中,逻辑门是最基本的组成单元。

逻辑门用于实现不同的逻辑功能,如与门、或门和非门等。

与门输出只有在所有输入都为高电平时才为高电平,或门输出只要有一个输入为高电平就为高电平,非门的输出与输入相反。

通过逻辑门的组合,可以构建复杂的电路功能,如加法器、多路选择器和计数器等。

5. 集成电路的应用非常广泛,涵盖了电子设备的各个领域。

常见的应用包括计算机、通信、医疗设备、汽车电子和消费电子等。

计算机中的处理器、存储器和各种接口芯片都是集成电路的应用。

在通信领域,集成电路用于实现无线通信、数据传输和网络设备等。

医疗设备中的心脏起搏器、血压计和体温计等也需要集成电路来完成各种功能。

6. 集成电路技术的发展是随着摩尔定律的提出而加速的。

摩尔定律指出,集成电路中的晶体管数量将每隔18-24个月翻一番,而成本将减少一半。

摩尔定律的实现需要不断提升晶体管的集成度和性能,以及改进制造工艺和材料。

电路原理习题期末复习例题

解:(1) 由 t = 0-电路求 uC(0–)、iL (0–) 换路前电路已处于稳态:电容元件视为开路; 由 t = 0-电路可求得:电感元件视为短路。

iL (0 )

R1 R1 R3

R

U R1R3

4

4

4

2

U 4

4

1A

R1 R3

44

(1) iL (0 ) 1 A

uC (0 ) R3iL (0 ) 4 1 4 V

I1

解:

I2

E1 R1 R2

1A

I3=0

VA =R3I3-E2+R2I2

=0-4+2 ×1= -2V

或

VA=R3I3-E2-R1I1+E1 =0-4-4 ×1+6=-2V

7. 计算 A 点的电位 VA

8. 电路如图。U1=10V,IS=2A,R1=1Ω,R2=2Ω,R3=5 Ω ,R=1 Ω。求电阻 R 中的电流 I;(2)计算理想电压源 U1 中的电流 IU1 和理想电流 源 IS 两端的电压 UIS;(3)分析功率平衡。 解: (1)

1.2A

I 34

E R3 R4

12 10 5

0.8A

UO I12R2 I34R4 1.25 0.85 2V

(2) 求等效电源的内阻 R0

R0 R1 // R2 R3

R4

(3) 画出等效电路求电流

IG

UO RO RG

2 5.8 10

0.126A

17.

18. 用诺顿原理计算图中电阻 R3 上的电流 I3.已知 R1=6Ω,R2=2 Ω,R3=3Ω,Is=10A,E=6V 解:(1) 求短路电流

(b) E 单独作用 将 IS 断开

I 2

数字ic笔试题——接口转换电路

数字ic笔试题——接口转换电路接口转换电路是用于连接不同电气特性或信号类型的两个设备或系统的电路。

它可以将一个设备的信号转换为另一个设备可以理解和处理的信号。

在数字IC领域中,接口转换电路通常用于将一种数字信号转换为另一种数字信号。

这些信号可以具有不同的电平、协议或时序要求。

下面是几个与数字IC接口转换相关的笔试题:1. 什么是接口转换电路?为什么需要进行接口转换?答:接口转换电路是用于连接不同电气特性或信号类型的两个设备或系统的电路。

它将一个设备的信号转换为另一个设备可以理解和处理的信号。

接口转换通常需要进行的原因包括: - 设备之间使用不同的电平标准(如TTL、CMOS、LVDS 等)。

- 设备之间使用不同的通信协议(如UART、SPI、I2C等)。

- 设备之间使用不同的数据格式(如并行、串行、并行/串行转换)。

- 设备之间使用不同的时序要求(如时钟频率、数据传输速率等)。

2. 请简要描述一种数字信号的电平转换电路。

答:数字信号的电平转换电路通常使用电平转换器来实现。

它将一个设备输出的数字信号从一种电平标准(例如TTL或CMOS)转换为另一种电平标准(例如LVDS或RS-232)。

电平转换电路通常包括电平转换芯片,该芯片具有适当的输入和输出接口以及电平转换功能。

3. 请简要描述一种串行通信协议的接口转换电路。

答:串行通信协议的接口转换电路通常使用串行通信接口芯片来实现。

例如,UART接口转换电路可以将串行数据发送和接收线路的电平转换为与目标设备兼容的电平标准。

该电路还可能涉及波特率转换、数据位数调整等功能,以确保正确的数据传输。

4. 什么是时钟域转换电路?为什么在数字系统中需要进行时钟域转换?答:时钟域转换电路用于在不同的时钟域之间进行数据传输。

在数字系统中,不同的模块可能使用不同的时钟频率或时钟相位,因此可能需要进行时钟域转换。

时钟域转换电路通常包括时钟提取、频率除法、时钟缓冲等组件,以确保数据在不同时钟域之间的正确传输和同步。

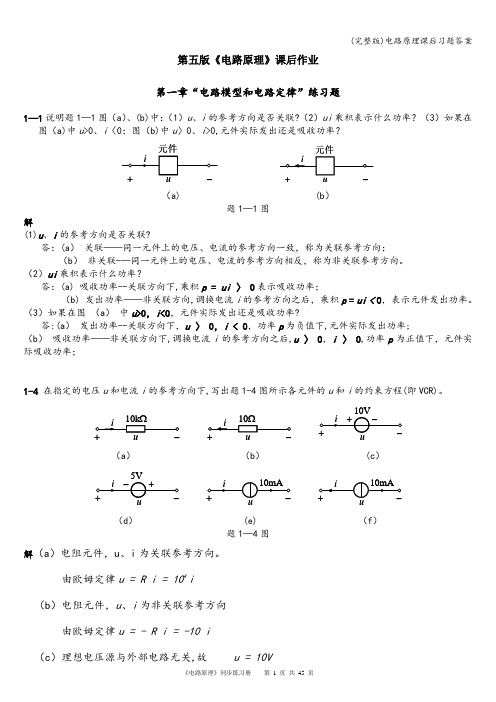

(完整版)电路原理课后习题答案

因此, 时,电路的初始条件为

t〉0后,电路的方程为

设 的解为

式中 为方程的特解,满足

根据特征方程的根

可知,电路处于衰减震荡过程,,因此,对应齐次方程的通解为

式中 。由初始条件可得

解得

故电容电压

电流

7-29RC电路中电容C原未充电,所加 的波形如题7—29图所示,其中 , 。求电容电压 ,并把 :(1)用分段形式写出;(2)用一个表达式写出。

题4-17图

解:首先求出 以左部分的等效电路.断开 ,设 如题解4-17图(a)所示,并把受控电流源等效为受控电压源。由KVL可得

故开路电压

把端口短路,如题解图(b)所示应用网孔电流法求短路电流 ,网孔方程为

解得

故一端口电路的等效电阻

画出戴维宁等效电路,接上待求支路 ,如题解图(c)所示,由最大功率传输定理知 时其上获得最大功率。 获得的最大功率为

(a)(b)

题3—1图

解:(1)每个元件作为一条支路处理时,图(a)和(b)所示电路的图分别为题解3-1图(a1)和(b1)。

图(a1)中节点数 ,支路数

图(b1)中节点数 ,支路数

(2)电压源和电阻的串联组合,电流源和电阻的并联组合作为一条支路处理时,图(a)和图(b)所示电路的图分别为题解图(a2)和(b2)。

电容电流

t=2 ms时

电容的储能为

7—20题7—20图所示电路,开关合在位置1时已达稳定状态,t=0时开关由位置1合向位置2,求t0时的电压 .

题7-20图

解:

用加压求流法求等效电阻

7-26题7—26图所示电路在开关S动作前已达稳态;t=0时S由1接至2,求t0时的 .

题7-26图

解:由图可知,t>0时

IC测试原理解析(1-4)

IC测试原理解析(第一部分)第一章数字集成电路测试的基本原理第一节不同测试目标的考虑•CMOS•NMOS•Others通常的测试项目种类:•功能测试:真值表,算法向量生成。

•直流参数测试:开路/短路测试,输出驱动电流测试,漏电电源测试,电源电流测试,转换电平测试等。

•交流参数测试:传输延迟测试,建立保持时间测试,功能速度测试,存取时间测试,刷新/等待时间测试,上升/下降时间测试。

第二节直流参数测试直流测试是基于欧姆定律的用来确定器件电参数的稳态测试方法。

比如,漏电流测试就是在输入管脚施加电压,这使输入管脚与电源或地之间的电阻上有电流通过,然后测量其该管脚电流的测试。

输出驱动电流测试就是在输出管脚上施加一定电流,然后测量该管脚与地或电源之间的电压差。

通常的DC测试包括:•接触测试(短路-开路):这项测试保证测试接口与器件正常连接。

接触测试通过测量输入输出管脚上保护二极管的自然压降来确定连接性。

二级管上如果施加一个适当的正向偏置电流,二级管的压降将是0.7V左右,因此接触测试就可以由以下步骤来完成:1.所有管脚设为0V,2.待测管脚上施加正向偏置电流”I”,3.测量由”I”引起的电压,4.如果该电压小于0.1V,说明管脚短路,5.如果电压大于1.0V,说明该管脚开路,6.如果电压在0.1V和1.0V之间,说明该管脚正常连接。

•漏电(IIL,IIH,IOZ):理想条件下,可以认为输入及三态输出管脚和地之间是开路的。

但实际情况,它们之间为高电阻状态。

它们之间的最大的电流就称为漏电流,或分别称为输入漏电流和输出三态漏电流。

漏电流一般是由于器件内部和输入管脚之间的绝缘氧化膜在生产过程中太薄引起的,形成一种类似于短路的情形,导致电流通过。

•三态输出漏电IOZ是当管脚状态为输出高阻状态时,在输出管脚使用VCC(VDD)或GND(VSS)驱动时测量得到的电流。

三态输出漏电流的测试和输入漏电测试类似,不同的是待测器件必须被设置为三态输出状态•转换电平(VIL,VIH)。

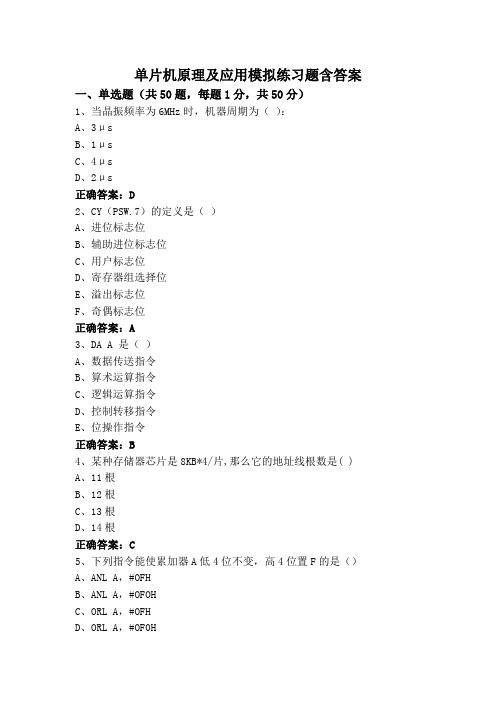

单片机原理及应用模拟练习题含答案

单片机原理及应用模拟练习题含答案一、单选题(共50题,每题1分,共50分)1、当晶振频率为6MHz时,机器周期为():A、3μsB、1μsC、4μsD、2μs正确答案:D2、CY(PSW.7)的定义是()A、进位标志位B、辅助进位标志位C、用户标志位D、寄存器组选择位E、溢出标志位F、奇偶标志位正确答案:A3、DA A 是()A、数据传送指令B、算术运算指令C、逻辑运算指令D、控制转移指令E、位操作指令正确答案:B4、某种存储器芯片是8KB*4/片,那么它的地址线根数是( )A、11根B、12根C、13根D、14根正确答案:C5、下列指令能使累加器A低4位不变,高4位置F的是()A、ANL A,#OFHB、ANL A,#OFOHC、ORL A,#OFHD、ORL A,#OF0H6、子程序返回指令的操作数有几个():A、0B、3C、1D、2正确答案:A7、执行下列程序后,内部RAM 30H单元的内容是()。

MOV 30H,#00H MOV R0,#30H MOV A, 30H ADD A, #05H MOVC A, @A+PC MOV @R0, A SJMP $ TDB:DB 00H ,01H ,02H,03H,05HA、00HB、02HC、05HD、30H正确答案:B8、以下标号正确的是():A、LOOPB、MOV:C、ST1:D、1ABC:正确答案:C9、一个机器周期内含有多少个状态周期():A、8B、2C、6D、4正确答案:C10、执行程序:MOV DPTR,#8000H MOVX A,@DPTR ADD A,20H MOV R0,#00H MOVx @R0,A INC R0 CLR A ADDC A,#00H MOVx @R0,A RET 之后则DPTR是()A、8003HB、7900HC、8001HD、8000H11、地址总线的缩写是():A、ABB、DBC、CBD、KB正确答案:A12、下列指令能使R0高4位不变,低4位置F的是()。

IC工艺原理习题

第一章外延思考题1.外延是___________________________________________________________________。

2.名词解释:同质结外延,异质结外延正外延,反外延SOS,SOI结构软误差,3.埋层外延中的图形漂移与滑移原因及解决办法。

4.分析外延中的自掺杂效应,讨论解决办法。

5.分析外延中的可能产生的几种缺陷,讨论解决办法。

6.总结影响外延生长速率的几种因素,如何提高外延层质量。

7.根据两种硅气相外延的原理,比较两种硅气相外延的特点。

8.外延技术在双极及MOS电路的主要用途第二章氧化工艺10001. 根据硅和二氧化硅的密度和分子量,说明生长厚度为x0的氧化层,计算要消耗厚度为___ x0的硅层,二氧化硅的密度用2.27g/cm3,硅的密度用2.33g/cm3,硅的原子量为28,氧的原子量为16。

选择题10002. 氧化层厚度和氧化时间的关系式为x0=A tA B21412++-⎛⎝⎫⎭⎪τ/,请化简,当氧化时间很短时,即()BAt4/2<<+τ, 则X0=_____A.BAt()+τ B. B t()+τ C.2BAt()+τ D.2B t()+τ10004 .氧化层厚度和氧化时间的关系式为X0=A tA B21412++-⎛⎝⎫⎭⎪τ/,当氧化时间很短时,即()BAt4/2<<+τ,它属于()A. 表面反应控制B. 扩散控制10006在温度相同的情况下,制备相同厚度的氧化层,分别用干氧,湿氧和水汽氧化,哪个需要的时间最长?()A.干氧B.湿氧C.水汽氧化10008. 二氧化硅膜能有效的对扩散杂质起掩蔽作用的基本条件有哪些______1.杂质在硅中的扩散系数大于在二氧化硅中的扩散系数2.杂质在硅中的扩散系数小于在二氧化硅中的扩散系数3.二氧化硅的厚度大于杂质在二氧化硅中的扩散深度4.二氧化硅的厚度小于杂质在二氧化硅中的扩散深度A.2,4 B.1,3 C.1,4 D.2,310010. 半导体器件生产中所制备的二氧化硅薄膜属于()A.结晶形二氧化硅 B. 无定形二氧化硅10011. 二氧化硅薄膜在半导体器件生产上的应用有:()1.对杂质的掩蔽作用2.对器件表面的保护和钝化作用3.用于器件的电绝缘和电隔离4.作为电容器的介质材料5.作为MOS场效应晶体管的绝缘栅材料A.1,2 B. 1,2,3 C. 1,2,4,5 D.1,2,3,4,510012. 扩散系数与下列哪些因素一定成增函数关系()1杂质的浓度梯度 2 温度3 扩散过程的激活能4 杂质的迁移率 A. 1,2 B. 2,3 C. 2,4 D.1,410013. 硅平面制造工艺的硼、磷扩散都属于_____ A. 代位式扩散 B.间隙式扩散填空题:20001. 在硅-二氧化硅系统中存在______电荷、可动电荷、界面态电荷和氧化层陷阱电荷。

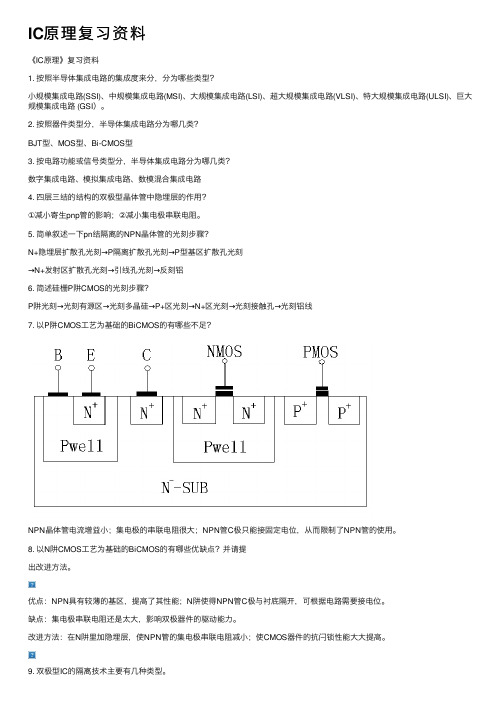

IC原理复习资料

IC原理复习资料《IC原理》复习资料1. 按照半导体集成电路的集成度来分,分为哪些类型?⼩规模集成电路(SSI)、中规模集成电路(MSI)、⼤规模集成电路(LSI)、超⼤规模集成电路(VLSI)、特⼤规模集成电路(ULSI)、巨⼤规模集成电路 (GSI)。

2. 按照器件类型分,半导体集成电路分为哪⼏类?BJT型、MOS型、Bi-CMOS型3. 按电路功能或信号类型分,半导体集成电路分为哪⼏类?数字集成电路、模拟集成电路、数模混合集成电路4. 四层三结的结构的双极型晶体管中隐埋层的作⽤?①减⼩寄⽣pnp管的影响;②减⼩集电极串联电阻。

5. 简单叙述⼀下pn结隔离的NPN晶体管的光刻步骤?N+隐埋层扩散孔光刻→P隔离扩散孔光刻→P型基区扩散孔光刻→N+发射区扩散孔光刻→引线孔光刻→反刻铝6. 简述硅栅P阱CMOS的光刻步骤?P阱光刻→光刻有源区→光刻多晶硅→P+区光刻→N+区光刻→光刻接触孔→光刻铝线7. 以P阱CMOS⼯艺为基础的BiCMOS的有哪些不⾜?NPN晶体管电流增益⼩;集电极的串联电阻很⼤;NPN管C极只能接固定电位,从⽽限制了NPN管的使⽤。

8. 以N阱CMOS⼯艺为基础的BiCMOS的有哪些优缺点?并请提出改进⽅法。

优点:NPN具有较薄的基区,提⾼了其性能;N阱使得NPN管C极与衬底隔开,可根据电路需要接电位。

缺点:集电极串联电阻还是太⼤,影响双极器件的驱动能⼒。

改进⽅法:在N阱⾥加隐埋层,使NPN管的集电极串联电阻减⼩;使CMOS器件的抗闩锁性能⼤⼤提⾼。

9. 双极型IC的隔离技术主要有⼏种类型。

pn结隔离、绝缘介质隔离及性能更优越的pn结隔离、绝缘介质隔离混合的隔离⼯艺--混合隔离(等平⾯隔离)。

其中最重要的是典型的pn 结隔离的⼯艺内容,这仍然是双极型逻辑集成电路制造中最最常⽤的隔离⼯艺,因为该⼯艺与常规平⾯制造⼯艺相容性最好。

pn结隔离-利⽤反向pn结的⼤电阻特性实现集成电路中各元器件间电性隔离⽅法;介质隔离-使⽤绝缘介质取代反向pn结,实现集成电路中各元器件间电性隔离⽅法;混合隔离-在实现集成电路中各元器件间电性隔离时,既使⽤了反向pn结的⼤电阻特性⼜使⽤了绝缘介质电性绝缘性质的⽅法。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

2007 / 2008 学年第_二学期期{末}考试卷A一、填空(1分×15=15分)1、双极型半导体IC以()作为有源器件,MOS型IC以MOS场效应晶件管作为有源器件。

把双极和CMOS相容工艺称为()工艺。

2、集成度提高的三个主要技术因素是器件尽寸缩小,()及芯片集成效率(结构和工艺设计改进)提高。

3、衡量一个TTL电路静态特性好坏的参数主要有噪声容限、负载能力、()。

4、增强型NMOS管其UGS( ), 则该管截止;增强型PMOS管其UGS( ), 则该管导通。

5、N沟器件的好处是电子表面迁移率比空穴表面迁移率(),所以NMOS电路的工作速度比PMOS电路()6、带缓冲级的CMOS门电路,输出驱动能力仅由该输出端的()决定,与各输入端所处的()。

7、在模拟IC的横向PNP管中,基区宽度减小会使β(),使CE之间的穿通电压VPT(),基区宽度的选择要首先保证()对基区宽度的要求。

8、差模放大器放大有用的()信号,对各种共模信号具有良好的共模抑制作用。

β、V BE、,I CEO随温度的变化会造成零点漂移及噪声,这些变化均是()信号。

二问答题(56分)1、图1为双极逻辑集成电路中NPN晶体管结构图,(1)简述寄生晶体管对NPN管的影响(4分)(3)工艺上如何减小有源寄生效应(5分)。

(共9分)图12、(1)画出标准TTL与非门逻辑电路图(3分)。

(2)简述当输入为高电平时的工作原理(要说明各个管子的工作状态并标出每个基极和集电极的电位)(6分)。

(3)5管单元TTL与非门电路比标准TTL与非门做了那些改进,提高了那些性能(5分)。

(共14分)3、肖特基嵌位晶体管与普通晶体管相比有什么特点(5分)?STTL与非门电路比6管单元TTL与非门电路作了那些改进(2分)?提高了电路的什么性能(2分)?带来了那两个缺点(4分)? (共13分)4、(1)画出互补CMOS反相器电路图(2分)(2)简述其工作原理(6分)。

(3)要使反相器噪容最大、输出波形对称需满足什么条件(2分)(共10分5、模拟IC中对扩散电阻器的要求是什么?(3分)6、说出差分放大器输入失调电流的定义。

(3分)三综合题(29分)1、设计一个互补CMOS逻辑电路,实现逻辑功能并设计每个器件的宽长比使输出波形对称。

(14分)与之匹配的基本反相器器件尺寸为:n= NMOS(W/L)=1.5, p= NMOS(W/L)=32、写出图2电路的节点1和2的逻辑表达式F1和F2(6分),并填写下表(5分)。

VDDVDDF2....3、图3为CMOS电流源电路,当(W/L)2::(W/L)1 =2:1,计算Io:Ir (4分)....图3 MOS恒流源2008 / 2009 学年第_一学期期{末}考试卷A一.填空(1分×15=15分)1、集成度提高的三个主要技术因素是器件尽寸缩小,()及芯片集成效率结构和工艺设计改进提高。

2、衡量一个TTL电路静态特性好坏的参数主要有噪声容限、负载能力、()。

3、增强型NMOS管其UGS和UGD满足( )时, 则该管饱和。

4、带缓冲级的CMOS门电路,输出驱动能力仅由该输出端的MOS晶体管特性决定,与各输入端所处的()。

5、齐纳二极管反向击穿电压具有()温度系数。

6、在模拟IC的横向PNP管中,基区宽度减小会使β增大,使CE之间的穿通电压VPT()。

7、差模放大器放大有用的()信号,对各种共模信号具有良好的共模抑制作用。

β、V BE、,I CEO随温度的变化会造成零点漂移及噪声,这些变化均是()信号。

8、影响双极差模放大器的输入失调电压的主要因素是( ),其输入失调电压的温漂与失调电压本身成()。

二问答题(53分)1、图1为双极逻辑集成电路中NPN晶体管结构图,(1)简述寄生晶体管对NPN管的影响(4分)(3)工艺上如何减小有源寄生效应(5分)。

(共9分)图12、(1)画出标准TTL与非门逻辑电路图(3分)。

(2)简述当输入为高电平时的工作原理(要说明各个管子的工作状态并标出每个基极和集电极的电位)(6分)。

(3)5管单元TTL与非门电路比标准TTL与非门做了那些改进,提高了那些性能(5分)。

(共14分)3、肖特基嵌位晶体管与普通晶体管相比有什么特点(6分)?STTL与非门电路比6管单元TTL与非门电路作了那些改进(2分)?提高了电路的什么性能(2分)?带来了那两个缺点(4分)? (共14分)4、(1)画出互补CMOS反相器电路图(2分)(2)简述其工作原理(6分)。

(3)要使反相器噪容最大、输出波形对称需满足什么条件(2分)(共10分5、模拟IC中对扩散电阻器的要求是什么?(3分)6、说出差分放大器输入失调电流的定义。

(3分)三综合题(32分)1、设计一个互补CMOS逻辑电路,实现逻辑功能并设计每个器件的宽长比使输出波形对称。

(12分)与之匹配的基本反相器器件尺寸为:n= NMOS(W/L)=1.5, p= NMOS(W/L)=32、写出图2电路的节点1和2的逻辑表达式F1和F2(6分),并填写下表(4分)。

.. Array F2..(图2)3、图3为CMOS电流源电路,假设两个管子的工艺参数相同,(1)推导Io:Ir的关系(8分);(2)计算当(W/L)2::(W/L)1 =5:1时Io:Ir的值(2分)。

(10分)图3 MOS恒流源2008 / 2009 学年第_二学期期{末}考试卷B一.填空(1分×15=15分)1、互补MOS逻辑集成电路由下拉网络和上拉网络组成,其中上拉网络为()器件,下拉网络为()器件。

2、双极型半导体IC以()作为有源器件,MOS型IC以MOS场效应晶件管作为有源器件。

把双极和CMOS相容工艺称为()工艺。

3、集成度提高的三个主要技术因素是(),()及芯片集成效率(结构和工艺设计改进)提高。

4、衡量一个TTL电路静态特性好坏的参数主要有噪声容限、负载能力、()。

5、增强型NMOS管其UGS( ), 则该管截止;增强型PMOS管其UGS( ), 则该管导通。

6、N沟器件的好处是电子表面迁移率比空穴表面迁移率(),所以NMOS电路的工作速度比PMOS电路()7、带缓冲级的CMOS门电路,输出驱动能力仅由该输出端的()决定,与各输入端所处的()。

8、差模放大器放大有用的()信号,对各种共模信号具有良好的共模抑制作用。

β、V BE、I CEO随温度的变化会造成零点漂移及噪声,这些变化均是()信号。

二问答题(56分)1、图1为双极逻辑集成电路中NPN晶体管结构图,(1)画出其中的寄生晶体管位置、寄生晶体管和NPN晶体管的电连接电路图。

(4分),(2)简述寄生晶体管对NPN管的影响(6分)(3)工艺上如何减小有源寄生效应(5分)。

(共15分)图12、(1)画出标准TTL与非门逻辑电路图(6分)。

(2)5管单元TTL与非门电路比标准TTL与非门做了那些改进,提高了那些性能(6分)。

(共12分)3、肖特基嵌位晶体管与普通晶体管相比有什么特点(8分)?STTL与非门电路比6管单元TTL与非门电路作了那些改进(2分)?提高了电路的什么性能(2分)?带来了那两个缺点(4分)? (共16分)4、(1)画出互补CMOS反相器电路图(3分)(2)要使反相器噪容最大、输出波形对称需满足什么条件(4分)(共7分5、模拟IC中对扩散电阻器的要求是什么?(3分)6、说出差分放大器输入失调电流的定义。

(3分)三综合题(29分)1、设计一个互补CMOS逻辑电路,实现逻辑功能并设计每个器件的宽长比使输出波形对称。

(14分)与之匹配的基本反相器器件尺寸为:n= NMOS(W/L)=1.5, p= NMOS(W/L)=32、写出图2电路的节点1和2的逻辑表达式F1和F2(6分),并填写下表(5分)。

VDD VDDF 2....3、图3为CMOS 电流源电路,当 (W/L)2::(W/L)1 =2:1,计算 Io :Ir (4分 )....图3 MOS 恒流源2009 / 2010 学年第_一学期期{末}考试卷A一、填空(每空一分,共20分)1、集成度提高的三个主要技术因素是(),()及芯片集成效率结构和工艺设计改进提高。

2、双极型半导体IC以()作为有源器件,MOS型IC以MOS场效应晶件管作为有源器件。

把双极和CMOS相容工艺称为()工艺。

3、互补MOS逻辑集成电路由下拉网络和上拉网络组成,其中上拉网络为()器件,下拉网络为()器件。

4、衡量一个TTL电路静态特性好坏的参数主要有噪声容限、负载能力、()。

5、增强型PMOSFET满足( ), 则该管饱和;增强型NMOSFET管满足( ), 则该管工作在可变电阻区,沟道两头都是()的,其沟道电阻与其宽长比成()比。

6、N沟器件的好处是电子表面迁移率比空穴表面迁移率(),所以NMOS电路的工作速度比PMOS电路()7、带缓冲级的CMOS门电路,输出驱动能力仅由该输出端的()决定,与各输入端所处的()。

8、差模放大器放大有用的()信号,对各种共模信号具有良好的共模抑制作用。

β、V BE、I CEO随温度的变化会造成零点漂移及噪声,这些变化均是()信号。

差模放大器输入失调电压的温漂与输入失调电压本身成()比9、模拟IC对元件参数的精度和()要求较高,因此在版图和工艺设计中需重视对元件的()设计二问答题(50分)1、图1为双极逻辑集成电路中NPN晶体管结构图,(1)画出其中的寄生晶体管位置、寄生晶体管和NPN晶体管的电连接电路图。

(4(2)当NPN管工作于饱和区时寄生晶体管工作在什么区?简述理由。

对集成电路有影响吗?(6分)(3)工艺上如何减小有源寄生效应(4分)。

(共14分)图12、(1)画出标准TTL与非门逻辑电路图(3分)。

(2)简述当输入为高电平时的工作原理(要说明各个管子的工作状态并标出每个基极和集电极的电位)(6分)。

(3)STTL与非门电路比6管单元TTL与非门电路作了那些改进(2分)?提高了电路的什么性能(2分)? (共13 分)3、(1)画出互补CMOS反相器电路图(2分)(2)简述其工作原理(6分)。

(3)要使反相器噪容最大、输出波形对称需满足什么条件?设计最小特征尺寸为0.5微米,µn/µP=2时器件尺寸(4分)(共 12 分)4、如何提高差分放大器的共模抑制比?(6分)5、模拟IC中对扩散电阻器的要求是什么?(3分)6、说出差分放大器输入失调电流的定义。

(2分)三综合题(30)1、设计一个互补CMOS逻辑电路,实现逻辑功能并设计每个器件的宽长比使输出波形对称。

(12分)与之匹配的基本反相器器件尺寸为:n= (W/L)NMOS=1.5, p= (W/L)PMOS=32、写出图2电路的节点1和2的逻辑表达式F1和F2(6分),并填写下表(4分)。