GE电口速率自协商问题(SGMII SERDES)

GE电口速率自协商问题-经典问题解析

GE电口速率自协商问题案例来源:单板调试关键词:GE电口、自协商1、问题描述在某上行扣板的调试过程中,发现上行GE电口与其它GE电口设备对接时,速率都为1000M时,电口可以正常link;但是当与速率强制为100/10M设备对接时,电口不能正确协商,端口link不上。

2、原因分析电口使用已比较成熟,与以前使用过的单板设计架构也没有太大差异,但是为何会出现此问题呢?开始的时候,大家一致认为是软件配置将速率强制成了1000M,但是经过核对,排除了“软件配置问题”。

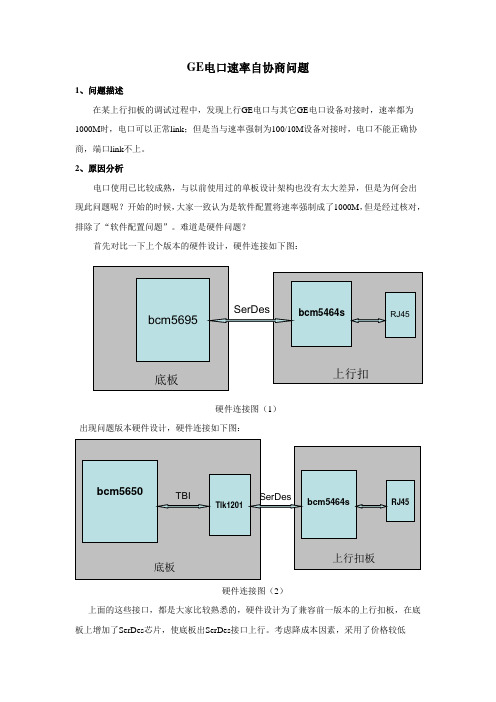

难道是硬件问题?首先对比一下上个版本的硬件设计,硬件连接如下图:硬件连接图(1)出现问题版本硬件设计,硬件连接如下图:硬件连接图(2)上面的这些接口,都是大家比较熟悉的,硬件设计为了兼容前一版本的上行扣板,在底板上增加了SerDes芯片,使底板出SerDes接口上行。

考虑降成本因素,采用了价格较低TLK1201芯片。

分别分析TLK1201的对外接口。

首先分析SerDes接口,SerDes接口是大家所较熟悉的,“SerDes”接口自协商大家看来是没有任何问题,但是学习了一下“SerDes”接口,却发现和我们平时的理解有些差异。

查阅bcm5464芯片资料,描述如下:SerDes: 1000 Mbps operation。

The SerDes interface shares the same differential data pin as the SGMII interface. The BCM5464S can act as a 1-GHz。

media converter by both supporting SerDes fiber and copper line interfaces simultaneously.很显然SerDes接口仅仅具备1000Mbps数据收发功能,不支持速率的自适应,那么上一版本我们认为的“SerDes”接口是如何进行速率协商的呢?结果发现是我们没有正确的区分SerDes和SGMII,SGMII接口才是支持10/100/1000M速率自协商的。

GE电口速率自协商问题(SGMII SERDES)

GE电口速率自协商问题1、问题描述在某上行扣板的调试过程中,发现上行GE电口与其它GE电口设备对接时,速率都为1000M时,电口可以正常link;但是当与速率强制为100/10M设备对接时,电口不能正确协商,端口link不上。

2、原因分析电口使用已比较成熟,与以前使用过的单板设计架构也没有太大差异,但是为何会出现此问题呢?开始的时候,大家一致认为是软件配置将速率强制成了1000M,但是经过核对,排除了“软件配置问题”。

难道是硬件问题?首先对比一下上个版本的硬件设计,硬件连接如下图:硬件连接图(1)出现问题版本硬件设计,硬件连接如下图:硬件连接图(2)上面的这些接口,都是大家比较熟悉的,硬件设计为了兼容前一版本的上行扣板,在底板上增加了SerDes芯片,使底板出SerDes接口上行。

考虑降成本因素,采用了价格较低TLK1201芯片。

分别分析TLK1201的对外接口。

首先分析SerDes接口,SerDes接口是大家所较熟悉的,“SerDes”接口自协商大家看来是没有任何问题,但是学习了一下“SerDes”接口,却发现和我们平时的理解有些差异。

查阅bcm5464芯片资料,描述如下:SerDes: 1000 Mbps operation。

The SerDes interface shares the same differential data pin as the SGMII interface. The BCM5464S can act as a 1-GHz。

media converter by both supporting SerDes fiber and copper line interfaces simultaneously.很显然SerDes接口仅仅具备1000Mbps数据收发功能,不支持速率的自适应,那么上一版本我们认为的“SerDes”接口是如何进行速率协商的呢?结果发现是我们没有正确的区分速率自协商的。

GE端口之SerDes和SGMII模式

GE端⼝之SerDes和SGMII模式

在以太⽹交换机中,上联GE端⼝通常可以配置为SerDes模式和SGMII模式两种。

硬件连接

SerDes模式和SGMII模式在硬件连线上是完全兼容的,都是⼀对接收、发送差分信号。

SGMII模式另外有接收数据参考时钟信号,如果MAC和PHY各⾃拥有独⽴的参考时钟,则可以忽略。

以BCM56820芯⽚为例,SGMII模式下:

SerDes模式下:

实际使⽤过程中,通过配置MAC相关寄存器,配置GE端⼝模式为SerDes模式或者SGMII模式。

应⽤范围

SGMII模式通常⽤来连接GE电模块,⽀持10/100/1000BASE-T电模块,如强制1000M电模块或者10/100/1000M⾃适应电模块。

SerDes模式通常⽤来接GE光模块,⽀持1000BASE-X光模块。

原理分析

SGMII模式下,GE端⼝速率为1.25Gbps,除去报⽂控制信息,实际传输速率为10Gbps。

SerDes模式下,GE端⼝速率为1.25Gbps,但是需要做8B/10B编解码,因此实际传输速率也是10Gbps。

SGMII模式和SerDes模式的区别在于——SGMII模式下,MAC和电模块之间需要接PHY芯⽚;同时,SGMII模式⽀持⾃协商模式。

SGMII模式的8B/10B编解码⼯作通过PHY芯⽚完成,SerDes模式的8B/10B编解码⼯作由MAC芯⽚完成。

高性能FPGA中的高速SERDES接口

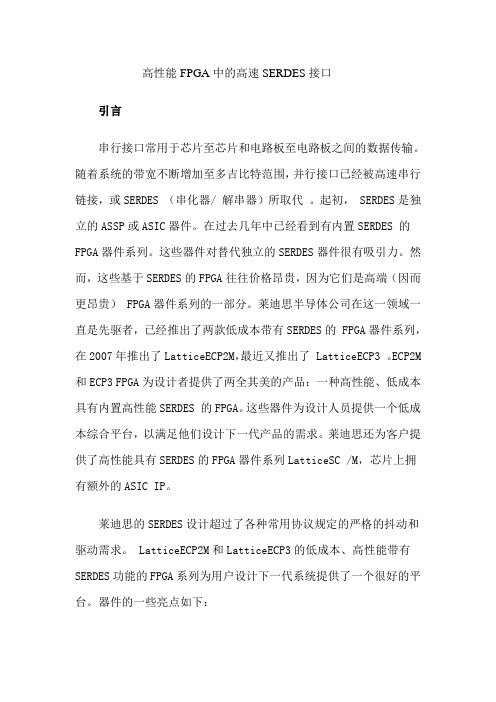

高性能FPGA中的高速SERDES接口引言串行接口常用于芯片至芯片和电路板至电路板之间的数据传输。

随着系统的带宽不断增加至多吉比特范围,并行接口已经被高速串行链接,或SERDES (串化器/ 解串器)所取代。

起初, SERDES是独立的ASSP或ASIC器件。

在过去几年中已经看到有内置SERDES 的FPGA器件系列。

这些器件对替代独立的SERDES器件很有吸引力。

然而,这些基于SERDES的FPGA往往价格昂贵,因为它们是高端(因而更昂贵) FPGA器件系列的一部分。

莱迪思半导体公司在这一领域一直是先驱者,已经推出了两款低成本带有SERDES的 FPGA器件系列,在2007年推出了LatticeECP2M,最近又推出了 LatticeECP3 。

ECP2M 和ECP3 FPGA为设计者提供了两全其美的产品:一种高性能、低成本具有内置高性能SERDES 的FPGA。

这些器件为设计人员提供一个低成本综合平台,以满足他们设计下一代产品的需求。

莱迪思还为客户提供了高性能具有SERDES的FPGA器件系列LatticeSC /M,芯片上拥有额外的ASIC IP。

莱迪思的SERDES设计超过了各种常用协议规定的严格的抖动和驱动需求。

LatticeECP2M和LatticeECP3的低成本、高性能带有SERDES功能的FPGA系列为用户设计下一代系统提供了一个很好的平台。

器件的一些亮点如下:∙低功耗:工作于3.2Gbps的速率时,每个通道功耗额定为90mW 。

∙针对芯片至芯片和小型背板(不超过40英寸的FR - 4 ),能可靠传输和恢复串行信号。

∙嵌入式物理编码子层块,支持流行的串行协议,如1吉比特以太网,10吉比特以太网(XAUI )、PCI Express 、Serial RapidIO SMPTE 。

∙支持无线协议,如CPRI 、OBSAI等,包括用于实现多跳的一个低延迟变化选择。

∙灵活的SERDES模块:多个标准/协议可以混合于单个模块中。

Serdes与SGMII

编码器出来的是TS流,传输接口为asi口,编码器整个作用过程是把模拟信号变成ES,再打包成PES,再打包成TS流输出。

GMII:吉比特媒体独立接口是一种以太网接口,简称GMII(Gigabit Media Independent Interface)。简化的吉比特媒体独立接口称为RGMII(Reduced Gigabit Media Independent Interface)。采用RGMII的目的是降低电路成本,使实现这种接口的器件的引脚数从22个减少到12个。GE接口:指的是 Gigabit Ethernet千兆以太网接口带有GE标记的接口,说明是 1000M 以太网网络接口。这种接口有光纤接口,也有电接口.

SGMII是MAC和PHY之间的接口,它还需要经过PHY进行编码和线路均衡等才能变成GE信号。

Serdes不再需要PHY,它已经进行了编码。

一般情况下,Serdes主要用在芯片和光模块之间或者芯片高速接口连接。

其实,大多数MAC芯片的SGMII接口都可以配置成SerDes接口(在物理上完全兼容,只需配置寄存器即可),直接外接光模块,而不需要PHY层芯片,此时时钟速率仍旧是625MHz,不过此时跟SGMII接口不同,SGMIIห้องสมุดไป่ตู้口速率被提高到1.25Gbps是因为插入了控制信息,而SerDes端口速率被提高是因为进行了8B/10B变换,本来8B/10B变换是PHY芯片的工作,在SerDes接口中,因为外面不接PHY芯片,此时8B/10B变换在MAC芯片中完成了。8B/10B变换的主要作用是扰码,让信号中不出现过长的连“0”和连“1”情况,影响时钟信息的提取

影响EGPRS网络质量的问题及其解决专题方案

影响EGPRS网络质量旳问题及其解决方案(-07-08 11:33:09)1、EDGE(EGPRS)核心技术简介理论上EGPRS单时隙提供旳数据速率是GPRS旳3倍,单时隙最大速率从GPRS旳21.4kbit/s (CS4)提高到59.2kbit/s(MCS9),如果捆绑使用8个时隙,最大数据速率可达473kbit/s。

这种速率可支持如互联网浏览、视频电话会议和高速电子邮件等多种业务,在3G网络之前为顾客提供多媒体通信。

EGPRS承载数据业务旳能力强于GPRS技术旳因素重要在于EGPRS采用了如下几种核心技术。

1.18PSK调制措施——提高了传播速率EGPRS采用先进旳多时隙操作和8PSK调制技术,相比较之下,GPRS采用旳GMSK调制具有良好旳抗干扰能力,但传播速率较低;8PSK调制旳速率是GMSK调制旳3倍,但信号旳顽键性(Robustness)较GMSK差,对频移、噪声、时延等反映敏感,抗频移、噪声、时延能力比GMSK 弱。

1.2混合编码方案——提高了数据吞吐能力MCS调制编码措施将容错保护机制融入了编码方案中,其中MCS1~MCS4采用GMSK调制措施,容错保护能力强,数据吞吐量相对较低;MCS5~MCS9采用8PSK调制措施,数据吞吐能力比较强。

1.3增强旳链路质量控制算法——提高了数据传播和接受效率EGPRS采用了链路自适应和增量冗余旳增强型链路控制算法,达到最大旳信道数据吞吐率,提高接受端对旳接受和对旳解调旳概率。

此外,EGPRS在交错、寻址窗口等方面也采用了先进旳技术,以提供更高、更稳定旳传播速度。

2、工程应用中影响网络质量旳问题分析以及解决方案网络升级EGPRS后,对网络能力旳影响可以从如下几种方面进行探讨。

2.1影响EGPRS无线网络传播质量旳因素分析EGPRS在8时隙绑定期每帧最大可达到473kbit/s旳峰值速率,但是该速率会受到无线传播环境、多时隙绑定以及调制方式旳限制。

QSGMII协议详解讲解学习

自协商寄存器

LSB

D0 D1 D2 D3 D4 D5 D6

MSB

D7 D8 D9 D10 D11 D12 D13 D14 D15

RSV RSV RSV RSV RSV FD HD PS1 PS2 RSV RSV RSV RF1 RF2 ACK NP

/K28.7/用作于误码率和时钟的测试(连续的/K28.7/组合为00000111110000011111..) /K28.5/用在有序集/C/及/I/中。 /K28.1/在802.3中暂未提及使用。

有序集的概念

802.3中定义了8种有序集(order_set),它们由单一的特殊群码 或者由一个特殊群码与数据群码的组合构成。包含/K28.5/的有 序集支持数据对齐和时钟恢复。

FD:全双工指示,如果设置为1,则该设备支持全双工模式; HD:半双工指示,如果设置为1,则该设备支持半双工模式; PS1,PS2:流量控制指示,不同组合有不同的含义,如下:

00:不支持流量控制; 01:针对链路对端的不对称流量控制; 10:对称流量控制; 11:针对本地设备的不对称流量控制。 RF1,RF2:远程错误位,指出远程设备的一些错误发送; 00:设备正常(默认); 01:本地设备离线; 10:链路故障; 11:自协商错误。 ACK:确认指示。如果一台设备成功接收到了对端的基页,则发送自己基页的时候,将 ACK设置为1; NP:下一页指示。如果把该位设置为1,则隐含说明该设备还要发送除基页外的其他页面

8B/10B编码避免了5个连续的“0”或者“1”出现。并且 还可以使接收端从数据中有效地提取时钟。

编码原理

8bit原始数据会分成两部分,其低5位会进行5B/6B编码,高3位则进行 3B/4B编码,这两种映射关系有一个标准化的表格。对于8bit信号作为一 个数据群码时用Dx.y表示,作为特殊群码时用Kx.y表示,其中x是 EDCBA的十进制值,y是HGF的十进制值。例如,一个8bit数据码 110 11101 表示为D29.6。

SGMII和SERDES区别

SGMII和SERDES 这两个是什么?

前者是以太网MAC与PHY之间的媒体接口(单工)

后者是通用可编程串行接口(双工)

serdes是差分输出输入,各一对差分线。

SGMII只是一个普通高速串行信号

SGMII--Serial Gigabit Media Independent Interface

SGMII是PHY与MAC之间的接口,类似与GMII和RGMII,只不过GMII和RGMII都是并行的,而且需要随路时钟,PCB布线相对麻烦,而且不适应背板应用。

而SGMII是串行的,不需要提供另外的时钟,MAC和PHY都需要CDR 去恢复时钟。

另外SGMII是有8B/10b编码的,速率是1.25G

Serdes一般集成在高端FPGA上,或专用加串/解串器IC。

比较通用,如PCI-E,SATA等。

差分结构更稳定,当然规格不同最大速率不同。

如Lattice的FPGA EPC3 是4路serdes 3.25G。

sgmii ieee标准

SGMII IEEE标准SGMII(Serial Gigabit Media Independent Interface)是一种用于千兆位速率以太网通信的接口标准。

它在IEEE标准中的正式名称是IEEE 802.3 Section 22,也被称为IEEE 802.3 Clause 22。

以下是关于SGMII IEEE标准的详细解析:1. SGMII简介SGMII是一种串行接口,用于在千兆以太网系统中连接MAC(Media Access Control)和PHY(Physical Layer)芯片。

它被广泛应用于网络交换机、路由器、服务器等设备中,提供高速、可靠的通信。

2. IEEE标准SGMII的标准是在IEEE 802.3标准的Section 22中定义的,该标准详细描述了SGMII接口的电气和协议规范。

具体来说,SGMII在IEEE标准中包括以下主要方面:2.1 电气特性SGMII的电气特性定义了信号的传输方式、时序要求、电平规范等。

这包括差分信号对、时钟信号、控制信号等的电气特性。

2.2 协议规范SGMII的协议规范定义了MAC和PHY之间的通信协议。

它规定了数据帧的格式、帧同步、时钟同步、控制信号等方面的协议规则。

2.3 时钟要求SGMII在时钟传输方面有严格的要求,其中包括时钟信号的频率、相位对齐、时钟源的选择等方面的规范。

3. 主要特点3.1 速率SGMII的速率为1.25 Gbps,适用于千兆以太网通信。

3.2 差分传输SGMII采用差分信号传输,有助于减小传输中的电磁干扰,提高信号质量。

3.3 独立时钟SGMII支持独立时钟,即MAC和PHY可以使用不同的时钟源,提高了系统的灵活性。

3.4 自适应SGMII具有一定的自适应性,可以根据实际链路情况进行自动调整。

4. 应用领域SGMII广泛应用于以太网交换机、路由器、服务器等设备中,作为MAC和PHY之间的接口标准。

它提供了高速、可靠的数据传输,适用于需要千兆位速率的应用场景。

sgmii分类

sgmii分类

SGMII,即SerDes Gigabit Media Independent Interface,是一种用于高速数据传输的接口标准。

它广泛应用于网络通信领域,为各种设备之间的数据传输提供了高效可靠的解决方案。

SGMII接口是一种串行接口,通过将并行数据转换为串行数据来实现高速传输。

它采用差分信号传输方式,具有抗干扰能力强、传输距离远等特点。

SGMII接口的速率可以达到1.25Gbps,适用于千兆以太网等高速数据传输场景。

在网络通信中,SGMII接口通常用于连接以太网交换机和网卡之间,以及其他网络设备之间的数据传输。

通过SGMII接口,不同厂商生产的设备可以实现互联互通,提高网络的扩展性和兼容性。

SGMII接口的实现通常需要使用PHY芯片来完成。

PHY芯片负责将并行数据转换为串行数据,并进行差分信号的传输。

同时,PHY芯片还负责信号的时钟恢复、信号的编码解码等功能。

通过PHY芯片的配合,SGMII接口可以实现高速的数据传输。

SGMII接口在网络通信中起着重要的作用。

它不仅提供了高速的数据传输能力,还具有较强的抗干扰能力和传输距离远的特点。

通过SGMII接口,不同厂商的设备可以实现高效可靠的数据交换,提高网络的性能和可靠性。

SGMII是一种高速数据传输接口,通过串行传输方式实现高速数据

的传输。

它在网络通信中具有重要作用,为设备之间的数据传输提供了高效可靠的解决方案。

通过SGMII接口,不同厂商的设备可以实现互联互通,提高网络的扩展性和兼容性。

一种千兆以太网SerDes接口与电接口的转换方法

E-mail: jslt@ Computer Khnttopw:/le/hent.oclongy 电脑知识与技术

Tel:+86-551-65690963 65690964

一种千兆以太网 SerDes 接口与电接口的转换方法

徐玉杰,孟博

(中航工业西安航空计算技术研究所,陕西 西安 710065)

摘要:该文针对千兆以太网 SerDes 接口(1000 BASE-X)和电接口(1000 BASE-T)转换的问题,给出了一种基于 FPGA 的千 兆以太网 SerDes 接口和电接口转换的方法。详细介绍了该方法的硬件架构和逻辑设计,工程应用证明该方法稳定可靠, 逻辑设计简单易行,达到了设计的预期目标。 关键词:千兆以太网;高速串行接口;现场可编程门阵列 中图分类号:TP393 文献标识码:A 文章编号:1009-3044(2016)03-0047-02 DOI:10.14004/ki.ckt.2016.0336 A Conversion Method of Gigabit Ethernet SerDes to Copper Inteface XU Yu-jie, MENG Bo ( Aeronautical Computing Technique Research Institute,Xi’an 710065,China) Abstract: Focusing on the conversion of Gigabit Ethernet SerDes interface to copper interface, a conversion method based on FPGA is proposed. This paper describes in detail the method of hardware architecture and FPGA software design. The results prove that the method is stable, and can achieve the expected target of this design. Key words: Gigabit Ethernet; SerDes; Field Programming Gate Array(FPGA)

sgmii结构

sgmii结构SGMII结构简介SGMII(Serial Gigabit Media Independent Interface)是一种高速串行接口,用于连接以太网物理层和以太网MAC层之间的芯片。

它通过将并行数据转换为串行数据,实现了高速数据传输和节省引脚资源的优势。

本文将介绍SGMII结构的原理、特点以及应用领域。

一、SGMII结构原理SGMII结构由PHY和MAC两部分组成。

PHY(Physical Layer)负责物理层的功能,包括电气接口、时钟管理、数据编码和解码等;MAC(Media Access Control)负责媒体访问控制,对数据进行处理和调度。

SGMII结构中的数据传输是通过差分信号实现的,其中TX+和TX-是发送端的差分信号,RX+和RX-是接收端的差分信号。

发送端将并行数据转换为串行数据后,通过差分信号传输到接收端,接收端再将串行数据转换为并行数据。

二、SGMII结构特点1. 高速传输:SGMII支持1.25Gb/s的数据传输速率,可以满足高速数据传输的需求。

2. 节省引脚资源:SGMII使用差分信号传输数据,相比于传统的并行接口,可以节省大量的引脚资源。

3. 低功耗:SGMII结构采用低功耗的差分信号传输方式,能够降低系统的功耗。

4. 抗干扰性强:SGMII结构中的差分信号具有很好的抗干扰性,可以有效减少信号的失真和误码率。

5. 灵活性高:SGMII结构可以适应不同的物理层介质,如光纤、双绞线等,具有很高的灵活性。

三、SGMII结构应用领域1. 以太网交换机:SGMII结构被广泛应用于以太网交换机中,用于连接交换芯片和物理层芯片,实现高速数据传输和网络性能优化。

2. 无线通信设备:SGMII结构可用于连接无线通信设备的基带处理器和射频模块,实现高速数据传输和无线信号的可靠传输。

3. 数据中心:SGMII结构在数据中心中的服务器和网络设备中得到了广泛应用,提供高速、稳定的数据传输,满足大规模数据处理和存储的需求。

QSGMII协议详解

Running Disparity

表中的RD标志,代表编码极性。它的目的就是保持8B/10B编码 中的直流平衡。RD=+1表示1比0多,RD=-1表示0比1多。RD=-1

是上电初始化状态。

每进行一次编码后,都要计算出当前编码的RD值,用于下一个 编码。

Running Disparity

举例说明:假设要传输 D4.0 和 D21.4 该如何编码?

有序集/C/

对于确定的一个R,无论起始的RD正负,初始发送C1,然后与 C2交替发送。

假设用/C?/R1/R2/来表达自协商时传输的四个字节,/R1/代表

Config_Reg[7:0],R2/代表Config_Reg[15:8],那么发送方式 为/C1/R1/R2/C2/R1/R2/C1/…/C2/… 交替发送/C1/,/C2/可以使2个comma+和2个comma-连续交替 发送。

突,后续发送短帧也不必进行填充。但是为了连续占有信道,后续帧之间的 IPG使用/R/填充,一次帧突发的最大长度限制为8192B。

有序集/R/

/R/的第三个功能:/I/偶数对齐

后文结合/T/详细说明。

有序集/R/

/R/的产生:TX_EN低电平,TX_ER高电平

Permissible encodings of TXD<7:0>, TX_EN, and TX_ER

如果在发送载波扩展时,需要请求物理层进行中断,则发送载波扩展错误。由 TX_EN=0,TX_ER=1,TXD=1F表达,PCS层编码为/V/。

有序集/S/,/T/

包起始定界符用来描述数据序列传输的起始边界,由有序集/S/构成。有序

集/S/定义为/K27.7/。

输时间远小于冲突窗口(传输长度为512B帧所需的时间),不能进行正常的CSMA/CD。所以 对于小于512B的帧信号,需要使用/R/填充至512B。

最新23-自协商技术专题汇总

23-自协商技术专题资料编码产品名称使用对象产品版本编写部门资料版本以太网自协商技术专题拟制:日期:审核:日期:审核:日期:批准:日期:华为技术有限公司版权所有侵权必究修订记录目录1自协商技术概述 (5)2自协商技术的功能规范 (5)3自协商技术中的信息编码 (6)41000BASE-X的自协商功能 (10)关键词:脉冲、脉冲序列、寄存器自协商摘要:本文针对以太网的自协商技术的概念、实现方法、典型运用进行了详细的描述。

缩略语清单:无。

参考资料清单无。

以太网自协商技术专题1 自协商技术概述自协商功能允许一个网络设备能够将自己所支持的工作模式信息传达给网络上的对端,并接受对方可能传递过来的相应信息。

它使用修订过的10BASE-T的整合性测试脉冲序列(link integrity test pulse sequence)来传递信息,自协商功能完全由物理层芯片设计实现,因此并不使用专用数据包或带来任何高层协议开销。

自协商功能的基本机制就是将协商信息封装进一连串修改后的“10BASE-T连接测试收发波形”的连接整合性测试脉冲。

这串脉冲被称为快速连接脉冲(FLP)。

每个网络设备必须能够在上电、管理命令发出、或是用户干预时发出此串脉冲。

快速连接脉冲包含一系列连接整合性测试脉冲组成的时钟/数字序列。

将这些数据从中提取出来就可以得到对端设备支持的工作模式,以及一些用于协商握手机制的其他信息。

为了保持与现有10BASE-T设备的互操作性,自协商协议还具有接受与10BASE-T兼容的连接整合性测试脉冲(也被称为普通连接脉冲(NLP)序列)的功能。

当一个设备不能对快速连接脉冲做出有效的反应,而仅返回了一个普通连接脉冲时,它将被作为一个10BASE-T兼容设备对待。

2 自协商技术的功能规范脉冲序列中的第一个脉冲为时钟脉冲,并在其后每隔125us出现一个时钟脉冲,数据脉冲出现的位置在相邻两个时钟脉冲的中点上。

且以正脉冲表示逻辑1,无脉冲表示逻辑0。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

GE电口速率自协商问题

1、问题描述

在某上行扣板的调试过程中,发现上行GE电口与其它GE电口设备对接时,速率都为1000M时,电口可以正常link;但是当与速率强制为100/10M设备对接时,电口不能正确协商,端口link不上。

2、原因分析

电口使用已比较成熟,与以前使用过的单板设计架构也没有太大差异,但是为何会出现此问题呢?开始的时候,大家一致认为是软件配置将速率强制成了1000M,但是经过核对,排除了“软件配置问题”。

难道是硬件问题?

首先对比一下上个版本的硬件设计,硬件连接如下图:

硬件连接图(1)

出现问题版本硬件设计,硬件连接如下图:

硬件连接图(2)

上面的这些接口,都是大家比较熟悉的,硬件设计为了兼容前一版本的上行扣板,在底板上增加了SerDes芯片,使底板出SerDes接口上行。

考虑降成本因素,采用了价格较低

TLK1201芯片。

分别分析TLK1201的对外接口。

首先分析SerDes接口,SerDes接口是大家所较熟悉的,“SerDes”接口自协商大家看来是没有任何问题,但是学习了一下“SerDes”接口,却发现和我们平时的理解有些差异。

查阅bcm5464芯片资料,描述如下:

SerDes: 1000 Mbps operation。

The SerDes interface shares the same differential data pin as the SGMII interface. The BCM5464S can act as a 1-GHz。

media converter by both supporting SerDes fiber and copper line interfaces simultaneously.

很显然SerDes接口仅仅具备1000Mbps数据收发功能,不支持速率的自适应,那么上一版本我们认为的“SerDes”接口是如何进行速率协商的呢?结果发现是我们没有正确的区分

速率自协商的。

区别如下:

SerDes和SGMII,SGMII接口才是支持10/100/1000M

收发数据线以及一个可选择时钟信号。

如果MAC和PHY芯片都带时钟,则可以不需要单独

的时钟信号,只需一对收发差分信号即可。

Bcm5695支持SerDes和SGMII,bcm5464s芯片具有从接收数据中恢复时钟的能力,故SGMII接口模式时,不需要单独的接收时钟。

这样从外部接口看,不管SGMII还SerDes都

是“SerDes”接口,所以实际应用中很容易忽略他们之间的差异,而很容易理解为外部

连接对了,什么都OK。

TLK1201芯片是支持SerDes接口,并且有时钟恢复能力,但是与之连接的是一款PHY (bcm5464s)芯片,双方都不能提供时钟源,故不支持SGMII接口,只能配置成SerDes

模式,所以速率只支持1000M。

问题到此似乎也完全找到了,但是再认真看看另一侧的TBI接口,我们发现也发生了

同样的错误。

查阅bcm5650芯片资料,描述如下:

The BCM5650/BCM5651 interfaces to external physical media interface devices using GMII/TBI interface. GMII mode allows the GE port to interface to external PHYs supporting the GMII specification for 10/100/1000 Mbps operation.

TBI mode allows the GE port to directly connect to external SerDes for 1000BASE-X operation.

如上所述,TBI接口同样仅仅具备1000Mbps数据收发功能,不支持速率的自适应。

而

它同样很容易与另一个与它复用管脚的接口弄混淆——GMII。

GMII与TBI信号对比:

如上表所示,GMII与TBI管脚完全兼容,通过模式选择可以选择合适的模式;但它们两者之中只有GMII才支持10/100/1000M速率。

而TLK1201芯片同样仅仅支持TBI模式,而不能配置为GMII模式,故最终速率只能支持1000M。

众所周知,自协商中的仲裁机制就是在自协商完后,通过优先级解决方案使自协商的两端获得最大最合适的能力配置。

当我们的设备与非1000M速率电口对接时,速率协商结果无效,即端口速率不能适应到协商的结果,从而端口link不上。

3、结论和解决方法

如上面原因分析中所述,SerDes和TBI接口仅仅支持数据速率1000M,如果规格需要

速率自协商,就只能通过修改硬件才能解决。

4、经验总结

1、首先简单列举下平时常见的以太网GE接口自协商情况,以使用最多的Broadcom芯片为代表:

注:Gigabit(1000 Mbps)只配置成Full-duplex 工作模式

速率1000M工作时,一般都是配置成Full工作模式;如上表所示,TBI/RTBI、SerDes接口一般工作在1000/Full模式下,大多用于Fiber模式。

2、简单列举下几个常用的MAC/PHY/SerDes支持的接口,大家可以做个简单对比:

3、一点心得:如前面所述,同样性质的两个错误竟然在大量人员参与的原理图检视中没有发现,或许是开发及检视人员的大意,但是至少说明我们对这些接口的模棱两可的理解。

本来这样的问题在系统设计时就不应该出现,但是还是出现了,说明我们对某些知识细节的掌握还欠缺和以及对知识的大意。

希望这个小小的案例能给大家一点点的启发,不要再跌在细节上。

5、CHECKLIST

1、理解SerDes与SGMII、TBI与GMII的差异,SerDes、TBI接口只支持固定数据速率1000M,不支持速率的自协商,设计和审查时需要注意。